# **Integration of Magnetoresistive Biochips on a CMOS Circuit**

F. A.  $Cardoso^1$ , T.  $Costa^{2,3}$ , J.  $Germano^2$ , S.  $Cardoso^{1,3}$ , J.  $Borme^4$ , J.  $Gaspar^4$ , J. R.  $Fernandes^{2,3}$ , M. S.  $Piedade^{2,3}$ , and P. P.  $Freitas^{1,3}$

<sup>1</sup>INESC Microsistemas e Nanotecnologias (INESC MN), 1000-029 Lisbon, Portugal

<sup>2</sup>INESC Investigação e Desenvolvimento (INESC ID), 1000-029 Lisbon, Portugal

<sup>3</sup>Instituto Superior Técnico (IST), 1000-029 Lisbon, Portugal

<sup>4</sup>INL-International Iberian Nanotechnology Laboratory, 4715-31 Braga, Portugal

Since 2006, fully scalable matrix-based magnetoresistive biochips have been proposed. This integration was initially achieved with thin film switching devices and moved to complementary metal—oxide—semiconductor (CMOS) switching devices and electronics. In this paper, a new microfabrication process is proposed to integrate magnetoresistive sensors on a small CMOS chip (4 mm²). This chip includes a current generator, multiplexers, and a diode in series with a spin valve as matrix element. In this configuration, it is shown that the fabricated spin-valves have similar magnetic characteristics when compared to standalone spin valves. This validates the successfulness of the developed microfabrication process. The noise of each matrix element is further characterized and compared to the noise of a standalone spin valve and a portable electronic platform designed to perform biological assays. Although the noise is still higher, the spin valve integrated on the CMOS chip enables an increase in density and compactness of the measuring electronics.

Index Terms—Biochip, complementary metal-oxide-semiconductor (CMOS), magnetoresistive sensor, spin valve.

### I. INTRODUCTION

INIATURIZED instruments coupled to high sensitivity magnetoresistive sensors, powerful signal and control processors and associated to high level software intelligent systems, are likely to envisage handheld microsystems for biological, clinical, or chemical analysis. The most interesting developments in magnetoresistive biochips were achieved at Naval Research Laboratory [1], INESC-MN [2], Bielefeld University [3], Stanford University [4], Philips Research Laboratories [5], and the University of Minnesota [6]. In order to increase the number of sensors in a single biochip, magnetoresistive biochips in matrix configuration that include thin film diodes as a switching device were first proposed in [7]. The area required for these chips was found to be large due to the size of the commutation device. Furthermore, although presenting good commutation characteristics, thin film diodes also showed large noise values when compared to the noise of the sensor [8]. To overcome some of these limitations, a biochip fabricated in complementary metal-oxide-semiconductor (CMOS) with spin valve (SV) sensors deposited on top was proposed [9]. This implementation integrated a new multiplexing strategy combining frequency (FDM) and time division multiplexing (TDM).

In this work, a new microfabrication technique was developed for processing magnetoresistive sensors onto small CMOS substrates (4 mm<sup>2</sup>). The CMOS integration was pushed forward by including a current generator and TDM for addressing the rows and columns of a matrix of SVs in the same chip. Furthermore, due to the characteristics of the biasing and reading of this matrix, a multiplexer linearization technique [10] was applied in

Manuscript received March 02, 2012; revised April 16, 2012 and April 23, 2012; accepted April 25, 2012. Date of current version October 19, 2012. Corresponding author: F. A. Cardoso (e-mail: fcardoso@inesc-mn.pt).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TMAG.2012.2198449

the TDM. Each matrix element includes a diode (switching element) connected in series with a SV sensor.

A detailed description of the microfabrication technique used for the patterning of SVs on a small CMOS chip is first presented. Then, the characterization of a SV inside the matrix and biased by the integrated current generator is performed. Finally, the noise of the integrated sensor is characterized and conclusions are drawn.

## II. EXPERIMENTAL METHODS

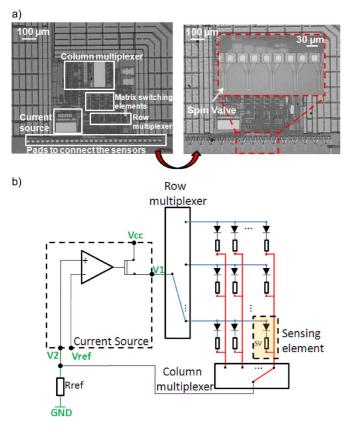

The CMOS chip was designed by INESC-ID and fabricated by Austriamicrosystems (AMS) using AMS 0.35  $\mu m$  3.3 V technology. The SVs were further deposited and microfabricated at INESC-MN clean room [Fig. 1(a)]. Previously to the microfabrication process of the sensors,  $1\times 1~{\rm in}^2$  chip holders were fabricated on a silicon substrate where a cavity with the CMOS chip dimensions  $(2.22\times 1.9~{\rm mm}^2)$  and thickness  $(500\mu m)$  was etched by deep reactive ion etching (DRIE) using Bosch process (at INL). The etch is performed at 20 °C by a plasma of SF $_6$  +  ${\rm O}_2$  during 7 s followed by the deposition of a etch stopper  $({\rm C}_4{\rm F}_8)$  for 4 s. To attain a cavity with the desired 500  $\mu m$ , this process is repeated 170 times.

The 4 mm² CMOS chip was then permanently glued on the cavity, using ultra-low viscosity glue (Ablebond 2025D). In this way, an easy-to-handle chip was engineered, enabling the processing of the SV using standard microfabrication techniques without debonding (spin coating, developer solvents, vacuum handling for material deposition, etc.). The process started with the deposition (by ion beam deposition, on Nordiko 3600 system) and definition by liftoff of a large region where the sensors will be patterned. The deposited structure was: Ta 20 Å/Ni<sub>80</sub>Fe<sub>20</sub> 20 Å/Co<sub>90</sub>Fe<sub>10</sub> 20 Å/Cu 21 Å/Co<sub>90</sub>Fe<sub>10</sub> 20 Å/Mn<sub>78</sub>Ir<sub>22</sub> 60 Å/Ta 20 Å/Ti<sub>10</sub>W<sub>90</sub>(N) 150 Å. The deposition of the magnetic layers (parallel anisotropies) were achieved under a 40 Oe field. Then,  $2.5 \times 80~\mu m^2$  U-shaped SV elements were patterned by ion-milling and connected to CMOS electronics with a 1- $\mu m$ -thick Al<sub>98.5</sub>Si<sub>1</sub>Cu<sub>0.5</sub> layer

Fig. 1. a) Electronic circuitry fabricated in AMS 0.35  $\mu m$  3.3 V technology with integrated SVs processed at INESC-MN facilities. b) Schematic of the electronic circuitry inside the CMOS chip. The resistance  $R_{\rm ref}$  is the only external element.

deposited by sputtering and defined by liftoff. Finally, the chip was wirebonded to a chip carrier so that an electrical characterization could be performed. Fig. 1(a) shows the CMOS chip before and after the microfabrication of the SVs. In this case, 14 SVs elements were microfabricated and included, together with two internal resistors (used for electrical tests), onto a 16 elements matrix. As the electronics is fully and easily scalable, in future runs a matrix with much higher number of elements will be implemented.

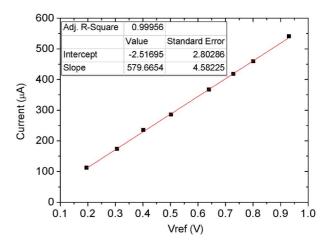

Fig. 1(b) shows the electrical schematic of the chip. The current generated by the current source is defined by an external voltage (V<sub>ref</sub>) and an external reference resistance (V<sub>ref</sub>). This reference resistance was chosen to be external since higher precision resistors can be found in discrete components when compared to resistors fabricated in CMOS. For the characterization,  $V_{\rm cc}$  was set to 3 V (using two 1.5 V batteries) and  $V_{\rm ref}$ was set between 0 and 1 V. In this work, a resistance  $R_{ref}$  of  $1.5 \text{ k}\Omega$  was chosen. Furthermore, the current passing through a matrix element was measured in function of V<sub>ref</sub>. The voltage V<sub>ref</sub> was generated by a low noise voltage reference integrated circuit (LTC6655) followed by a voltage divider composed by a resistance and a potentiometer. As observed in Fig. 2, the current scales linearly with  $V_{\rm ref}$  between 112  $\mu A$  ( $V_{\rm ref} = 195 \, {\rm mV}$ ) and  $540\,\mu\mathrm{A}\,(\mathrm{V_{ref}}=930\,\mathrm{mV})$  and the slope is  $579.7\,\mu\mathrm{A/V}$  . For the experiments performed in this work the current was set to  $500\mu A$  $(V_{ref} = 850 \text{ mV})$ . The output voltage (Vo) of the addressed sensor is measured between points V1 and V2 [Fig. 1(b)].

Fig. 2. Current source calibration. Current scales linearly with  $V_{\rm ref}$  being the slope 579.7  $\mu A/V.$

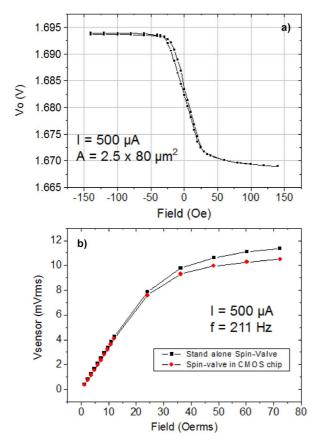

To magnetically characterize the SV included in the CMOS chip, two experiments were performed. First, the sensor transfer curve was measured. To achieve this, Vo was measured by a voltmeter (Keithley 182) for different magnetic fields (ranging from -140 to 140 Oe) applied by an Helmoltz coils. Second, in order to evaluate the sensitivity of the sensors, an increasing external ac field (ranging from 1.2 and 72  $\mathrm{Oe_{rms}}$ ) was applied. The resultant voltage Vo was measured by a lockin amplifier (Signal Recovery 7265). The ac external field (211 Hz) was generated by a horse-shoe electromagnet connected to a voltage generator (Agilent 33220A) and a custom-made power amplifier. To enable comparison, these measurements were also performed on a stand-alone SV sensor with a parallel state resistance (R<sub>min</sub>) of 900  $\Omega$ , a magnetoresistance (MR) of 7% and a sensitivity of 0.08%/Oe. In this case, the current was applied by a (Keithley 220) current source.

Finally, the noise of the stand-alone SV and of the SV integrated in the CMOS chip was measured using a low-noise amplifier Stanford Research System (SRS) SIM910 and a real-time spectrum analyzer (Tektronix RSA 3308A) to respectively amplify and measure the noise spectrum. Bandwidths of 2 and 200 Hz were used for the measurement in 5 Hz–1 kHz and 1–100 kHz ranges, respectively. These measurements were further compared to an electronic portable platform that was developed by INESC-ID for biological measurements using magnetoresistive biochips [11]. The measuring circuit topology in this platform (current source, multiplexers, etc.) is very similar to the one of the CMOS chip [Fig. 1(b)] but is made with discrete components.

#### III. EXPERIMENTAL RESULTS AND DISCUSSION

Each matrix elements fabricated on the CMOS chip were characterized in terms of transfer curve and response to an external ac field. Fig. 3(a) shows a typical voltage response of a matrix element to an applied dc field. As expected, since the electronic circuitry should not vary with respect to an external magnetic field, this response is very similar to the one of a standalone SV. The linearity and the almost inexistent shift of the curve with respect to 0 Oe field demonstrates the compatibility

Fig. 3. a) Transfer curve of a matrix element formed by a SV in series with a diode. b) Response of a matrix element and a stand-alone SV to an increasing external AC field (211 Hz).

of the CMOS surface roughness with the magnetoresistive sensors processing. However, since the only accessible measuring points on the chip are V1 and V2, it is not possible to measure directly the resistance of the SV and therefore its MR.

Nevertheless, for sensing application (i.e., biochips application) an important parameter is the sensitivity of the sensor. In order to evaluate the sensitivity, an increasing external ac field was applied and the resulting voltage Vo was measured by a lockin amplifier. For low fields, the output voltage obtained is proportional to the sensor's sensitivity. On the other hand, for large fields, Vo is proportional to the MR of the sensor. As observed in Fig. 3(b), Vo scales linearly with the applied ac field until reaching the saturation at 25  $\mathrm{Oe}_{\mathrm{rms}}$ .

At the saturation (72  $\mathrm{Oe_{rms}}$ ), the integrated and standalone SV shows a signal of 10.49  $\mathrm{mV_{rms}}$  and 11.37  $\mathrm{mV_{rms}}$ , respectively. Assuming that the SV have approximately the same resistance, since they have the same geometry and structure, and as the bias current is the same, the MR of the integrated SV is found to be approximately 6.5%.

Regarding the sensitivity, the slope of the linear region (<25  $\rm Oe_{rms}$ ) of Fig. 3(b) corresponds to the sensitivity of each SV. In this case, the sensitivities of the integrated and the standalone SV are 0.343  $\rm mV_{rms}/\rm Oe_{rms}$  and 0.355  $\rm mV_{rms}/\rm Oe_{rms}$ , respectively. This is the same to say that the slopes are 0.343 mV/Oe and 0.355 mV/Oe, respectively. Assuming that the SVs have approximately the same resistance and dividing these slopes by the sensor's dc voltage in the parallel state (V = 900  $\Omega$  ×

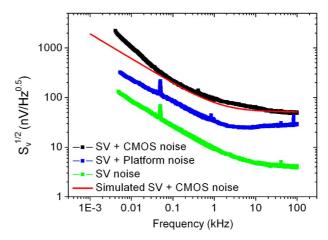

Fig. 4. Noise of a SV in the CMOS chip, a SV in the portable platform and a standalone SV in the range of 5 Hz–100 kHz. The noise of the SV and of the CMOS circuit was modeled in Cadence 6.1 using the libraries provided by AMS for the components used in the circuit.

$0.5~\mathrm{mA}$ ), sensitivities of  $0.076\%/\mathrm{Oe}$  and  $0.079\%/\mathrm{Oe}$  were obtained for the integrated and stand alone SVs, respectively. It can be concluded that both SV show very comparable characteristics, meaning that the sensitivity of the integrated SV was not degraded by being processed on the surface of a complex CMOS chip. This also confirms the correct functioning of the circuitry used to linearize the multiplexers response to the voltage variations depicted in [10].

The noise of the standalone SV and integrated SV were further compared. In Fig. 4, it can be observed that the noise of the integrated SV is much higher than the noise of the standalone SV. This was expected since there is a complex electronic circuitry (current generator, transistors, multiplexers, and diode) associated to each SV.

In order to support this assumption, the CMOS circuit and the SV noise were further modeled in Cadence 6.1 using the libraries provided by AMS for the simulation of the electronic components. The SV noise was included in the simulations using the  $\gamma/{\rm Nc}$  ratio  $(\gamma/{\rm Nc}\approx 1.88\times 10^{-13}$  where  $\gamma$  is the Hooge constant and Nc the number of noise carriers) and thermal noise background  $(S_{\rm th}^{1/2}\approx 3.9~{\rm nV/\sqrt{Hz}})$  obtained on the fitting of the standalone SV noise curve. As observed, the simulated noise fits well the experimental data for frequencies above 40 Hz. Below this frequency, there is an increase of noise which may indicate a dependency with  $1/{\rm f^2}$  of the spectral power density  $(\sqrt{1}/{\rm f^2}$  in Fig. 4). This is usually associated to random telegraph noise. However, as the working frequency usually used in the biochip applications is 211 Hz [11], this extra noise appearing at very low frequency do not affect the measurements.

The noise of the SV integrated in the CMOS chip was further compared to a SV biased and addressed on a portable electronic platform currently used for biological detection [11]. As can be observed in Fig. 4, the noise of the sensor in the CMOS chip is  $\sim$ 2.5 times higher than the already existing platform. This is essentially due to the fact that, up to now, the CMOS electronics was only designed for integrating magnetoresistive sensors on a matrix configuration and to enable the addressing and driving of each elements.

In the past, an alternative to CMOS switching elements was studied and consisted on thin film diodes which showed a noise at 211 Hz of 160 and 433 nV/ $\sqrt{\rm Hz}$  for Schottky and PIN diodes, respectively [8]. This noise corresponded only to the diode and did not include the magnetoresistive sensor, the multiplexers and the current generator. At 211 Hz, the CMOS chip here presented shows a noise of 157 nV/ $\sqrt{\rm Hz}$ . This is already lower than the noise of a matrix element using thin film diodes and in addition it already includes the multiplexing and current biasing circuitries. Therefore, for biological applications needing a large number of sensing sites, the integration of magnetoresistive biochips on a CMOS chip is, at this point, already a better alternative to the integration of thin film diodes with the sensors.

However, ideally, the optimum signal to noise ratio of the device is attained when the noise of the sensor is dominant over the electronic system. As demonstrated in this paper, this is still not the case. Therefore, in further improvements of this approach, the electronic noise, namely the noise produced by the current generator, should be drastically reduced. The main noise contributor in this generator is the amplifier. Its noise can be highly reduced by applying a flicker noise cancellation technique, consisting on a modulation process, in which the amplifier input is translated to higher frequencies, where there is no flicker noise. After amplification, it is modulated back to the baseband, while the flicker noise is modulated to higher frequencies, and can be low-pass filtered [12]. Besides the amplifier, the routing parasitic resistances also generate noise. Thus, it should also be optimized in order to decrease the current source white noise. By doing this, on a biological assay, better limits of detection can be attained. Finally, the number of sensing sites will be increased to 256 on the next generation of this chip.

## IV. CONCLUSION

In conclusion, integrated SV sensors were successfully microfabricated using the technique here presented, which enables processing small CMOS chips (4 mm²). Furthermore, the integrated current generator was calibrated and used to bias a matrix-element. The magnetic response of the integrated SV was further analyzed and compared with a standalone SV. It was found that both sensors had similar sensitivities and MR proving that the microfabrication of SVs over a complex CMOS chip didn't affect the sensor magnetic response.

The noise of a SV sensor on a CMOS chip was also analyzed and compared with a standalone SV and an electronic platform with discrete components. Although its noise is still higher, the CMOS chip has the advantage of being much more compact and fully scalable. Furthermore, in this approach, the full electronic system (including biasing and addressing electronic) show less noise than what have been measured using thin film diodes as commutation devices.

The results reported in this paper have large impact in more compact architectures allowing the implementation of biochips with 256 or more sensors in few square milimeters. Furthermore, the noise from the electronics, namely from the current generator, can still be reduced by using noise reduction techniques. This leads to better signal to noise ratios and therefore, when used in biological applications, better limits of detection can be attained.

#### ACKNOWLEDGMENT

This work was supported by FCT (INESC-ID and Instituto de Nanotecnologias multiannual funding) through the PIDDAC Program funds, the Portuguese national project PTDC/EEA-ELC/108555/2008 and the European project FP7-ICT-2011-7 (IMAGIC-GA288381). T. Costa is grateful to FCT for the grant SFRH/BD/61569/2009.

#### REFERENCES

- S. P. Mulvaney, K. M. Myers, P. E. Sheehan, and L. J. Whitman, "Attomolar protein detection in complex sample matrices with semi-homogeneous fluidic force discrimination assays," *Biosens. Bioelect.*, vol. 24, no. 5, pp. 1109–1115, 2009.

- [2] V. C. Martins, F. A. Cardoso, J. Germano, S. Cardoso, L. Sousa, M. Piedade, P. P. Freitas, and L. P. Fonseca, "Femtomolar limit of detection with a magnetoresistive biochip," *Biosens. Bioelect.*, vol. 24, pp. 2690–2695, 2009.

- [3] H. Bruckl, M. Brzeska, D. Brinkmann, J. Schotter, G. Reiss, W. Shepper, P.-B. Kamp, and A. Becker, "Magnetoresistive logic and biochip," J. Mag. Magn. Mat., vol. 282, pp. 219–224, 2004.

- [4] R. S. Gaster, D. A. Hall, and S. X. Wang, "nanoLAB an ultraportable, handheld diagnostic laboratory for global health," *Lab Chip*, vol. 11, p. 950, 2011.

- [5] M. Koets, T. van der Wijk, J. T. W. M. van Eemeren, A. van Amerongen, and M. W. J. Prins, "Rapid DNA multi-analyte immunoassay," *Biosens. Bioelect.*, vol. 24, pp. 1893–1898, 2009.

- [6] Y. Li, B. Srinivasan, Y. Jing, X. Yao, M. A. Hugger, J.-P. Wang, and C. Xing, "Nanomagnetic competition assay for low-abundance protein biomarker quantification in unprocessed human sera," *J. Am. Chem. Soc.*, vol. 132, pp. 4388–4392, 2010.

- [7] F. A. Cardoso, H. A. Ferreira, J. P. Conde, V. Chu, P. P. Freitas, D. Vidal, J. Germano, L. Sousa, M. S. Piedade, B. A. Costa, and J. M. Lemos, "Diode/magnetic tunnel junction cell for fully scalable matrix-based biochip," *J. Appl. Phys.*, vol. 99, p. 08B307, 2006.

- [8] F. A. Cardoso, R. Ferreira, S. Cardoso, J. P. Conde, V. Chu, P. P. Freitas, J. Germano, T. Almeida, L. Sousa, and M. S. Piedade, "Noise characteristics and particle detection limits in Diode+MTJ matrix elements for biochip applications," *IEEE Trans. Magn.*, vol. 43, no. 6, pp. 2403–2405, Jun. 2007.

- [9] S. Han, H. Yu, B. Murmann, N. Pourmand, and S. X. Wang, "A high-density magnetoresistive biosensor array with drift-compensation mechanism," in *IEEE Int. Solid-State Circuits Conf.*, 2007, pp. 168–594.

- [10] T. Costa, M. S. Piedade, and J. R. Fernandes, "A CMOS circuit for precise reading of matrix addressed magnetoresistive biosensors," in *IEEE Biomed. Circuits Syst. Conf.*, 2011, pp. 389–392.

- [11] J. Germano, V. C. Marins, F. A. Cardoso, T. M. Almeida, L. Sousa, P. P. Freitas, and M. S. Piedade, "A portable and autonomous magnetic detection platform for biosensing," *Sensors*, vol. 9, pp. 4119–4137, 2009

- [12] C. Enz and G. Temes, "Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization," *Proc. IEEE*, vol. 84, no. 11, pp. 1584–1614, Nov. 1996.