# Explanation of the Charge Trapping Properties of Silicon Nitride Storage Layers for NVMs—Part II: Atomistic and Electrical Modeling

Elisa Vianello, Francesco Driussi, P. Blaise, Pierpaolo Palestri, *Member, IEEE*, David Esseni, *Senior Member, IEEE*, Luca Perniola, Gabriel Molas, Barbara De Salvo, and Luca Selmi

Abstract-Based on the material analysis of the SiN lavers presented in part I of this paper, we develop accurate atomistic and electrical models for the silicon nitride (SiN)-based nonvolatile memory devices, taking into account the candidate SiN defects responsible for the memory effect. Our analysis points out the role of the hydrogen atoms and Si dangling bonds in the trapping properties of SiN films with different stoichiometries. The atomistic models provide a comprehensive picture describing the energy level and the occupation number of the different defects in the SiN. The electrical model coupled with the atomistic results, for the first time, demonstrates the ability to describe the program/erase curves of charge-trap memory cells with SiN storage layers with diversified composition. Good agreement between simulations and experimental results coming from the material analysis and the electrical characterization of thin (type-B device) and thick (type-A device) tunnel oxide memory cells is shown.

*Index Terms*—Ab initio, charge trap, metal gate/Al<sub>2</sub>O<sub>3</sub>/ nitride/oxide/silicon (MANOS), nonvolatile memory (NVM), silicon nitride (SiN) composition.

# I. INTRODUCTION

T HE STOICHIOMETRY of silicon nitride (SiN) films used for nonvolatile memory (NVM) applications strongly impacts the performance of cells, such as metal gate/Al<sub>2</sub>O<sub>3</sub>/nitride/oxide/silicon (MANOS) and NROM [1], [2]. In particular, a tradeoff exists between the erase speed and the retention capabilities of MANOS cells. In fact, it has been shown that, by using a silicon-rich (*Si-rich*) SiN trapping layer, it is possible to achieve a faster erase at the expense of shorter

Manuscript received June 18, 2010; revised November 12, 2010, January 20, 2011, March 21, 2011, and May 6, 2011; accepted May 8, 2011. Date of publication June 13, 2011; date of current version July 22, 2011. This work was supported in part by the French Public Authorities through the NANO 2012 program, by the Italian MIUR through the FIRB project RBIP06YSJ, and by the European Union through the FP7 research contract 214431 "GOSSAMER." The review of this paper was arranged by Editor H. S. Momose.

E. Vianello is with the Department of Electrical, Managerial and Mechanized Engineering (DIEGM), University of Udine, 33100 Udine, Italy, and also with CEA-LETI, MINATEC Campus, 38054 Grenoble Cedex 9, France (e-mail: elisa.vianello@uniud.it).

F. Driussi, P. Palestri, D. Esseni, and L. Selmi are with the Department of Electrical, Managerial and Mechanized Engineering (DIEGM), University of Udine, 33100 Udine, Italy.

P. Blaise, L. Perniola, G. Molas, and B. De Salvo are with CEA- LETI, MINATEC Campus, 38054 Grenoble Cedex 9, France.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2011.2156407

retention times with respect to cells featuring stoichiometric (*std*) SiN films [2], [3].

The dependence of the memory operation on the SiN composition has already been documented by many authors [1], [2], [4]–[6], but it should be said that a convincing explanation of the tradeoff between erase and retention performance has not been conclusively addressed. In particular, to explain the faster erase speed and the smaller retention time of Si-rich SiN cells, some authors invoke electron traps that are shallower in energy with respect to those present in cells with std SiN trapping layers [2], [7]. However, the very slight difference in energy depths reported in the literature for Si-rich SiN traps compared to std SiN traps [7], [8] cannot exhaustively explain all the experimental findings on SiN-based memory cells. Furthermore, the Kelvin force microscopy (KFM) measurements on charge diffusion reported in [9] and the retention characteristics of thick tunnel oxide test structures (type-A device) presented in the accompanying paper seem to suggest a similar energy depth for the traps of the std and the Si-rich SiN films, thus demanding a clarification on the effective microscopic nature of the traps in SiN layers with different compositions.

To shed new light on the trapping properties of SiN films and, in particular, to understand the intrinsic nature and physical properties of the SiN traps, we developed atomistic models for the SiN, extending and completing the simulation study presented in [3]. We will show that our analysis is able to grasp the main experimental evidences reported in the literature and provided by the material analysis illustrated in part I of this work [10]. In other words, first, we integrated different experimental and modeling techniques by using the main results of [10] as input to build a theoretical description for the SiN films. In particular, the atomistic models have been used to obtain fundamental information regarding the nature of SiN traps.

In this respect, it is worth pointing out that the oxygen-related defects at the SiN interfaces have been studied by means of atomistic simulations in [11]. Moreover, the hydrogen-related defects in the bulk SiN have been studied by density functional theory (DFT) in [12], whereas the properties of Si dangling bonds have been investigated in [13] and [14]. In this paper, our attention has been focused on the traps located in the bulk of the SiN film, which is justified also by the experimental results of [15], which show that the centroid of the charge trapped in the silicon-oxide-nitride-oxide-silicon (SONOS)/MANOS devices is essentially in the center of the trapping layer, thus suggesting

the important role of bulk SiN traps for the cell operation in the whole range of interest for NVM applications of the SiN thickness [16].

Then, the physical insight obtained from the atomistic simulations has been transferred into a device-level electrical model, and simulations of the program and retention of the charge-trap NVM cells have been compared with the experiments reported in the accompanying paper [10] and with new dedicated experiments devised to verify the trap models for *std* and *Si-rich* SiN films.

## II. ATOMISTIC SIMULATION OF DEFECTS IN SiN LAYERS

## A. Atomic Structure for the SiN Films

As reported in part I of this work, the SiN films of the cells used for the experimental characterization are grown by low pressure chemical vapor deposition (LPCVD) and are likely to incorporate structural disorder [17], [18]. However, the clear presence of a broad bandgap (which is the consequence of a periodic lattice arrangement) suggests a sufficient degree of small range order in the structure to justify starting our atomistic study from the crystalline Si<sub>3</sub>N<sub>4</sub> [19]. In particular, there are three experimentally reported crystalline Si<sub>3</sub>N<sub>4</sub> phases:  $\alpha$ -,  $\beta$ -, and  $\gamma$ -Si<sub>3</sub>N<sub>4</sub>. Among these, the  $\beta$ -Si<sub>3</sub>N<sub>4</sub> structure has been chosen as the starting point because of several reasons.

First, the DFT calculations show that the  $\alpha$  and  $\beta$  phases have a mass density of  $\simeq 3.1$  g/cm<sup>3</sup> [20], in fairly good agreement with the X-ray reflectometry (XRR) experiments (2.8–2.9 g/cm<sup>3</sup>, [10]), while the  $\gamma$  phase has a considerably higher calculated mass density ( $\simeq 4$  g/cm<sup>3</sup>, [21]). Second, the bonding geometry of nitrogen and silicon atoms in nearly stoichiometric LPCVD SiN shows a local chemical order based on the tetrahedral bonding for the silicon atoms (Si-N<sub>4</sub>) and on the planar bonding for the nitrogen atoms (N-Si<sub>3</sub>), which are well identified in  $\beta$ -Si<sub>3</sub>N<sub>4</sub> [22]. Finally, the  $\beta$  phase is thermodynamically more stable at all temperatures with respect to the other phases [20], [23].

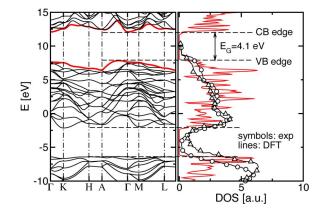

Fig. 1 shows the band structure (left) and the density of states (DOS) (right) of  $\beta$ -Si<sub>3</sub>N<sub>4</sub> calculated with the SIESTA code [24] (lines). For the simulations, the spin-polarized DFT and the local spin density approximation have been adopted. The simulated super cell is of 224 atoms, and the Troullier-Martin pseudopotentials have been used to represent the core electrons. We used the DZP basis with an energy shift of 50 meV for each species and a mesh cutoff of 100 Ha [25], [26]. In Fig. 1, we have also reported the experimental valence band DOS measured on LPCVD SiN layers by means of X-ray photoemission (XPS, circles, [27]) and Bremsstrahlung Isochromat Spectroscopy (BIS, triangles, [28]). It is apparent that the simulated valence band DOS grasps the main features of the experimental valence band, namely, the valence band spectrum is split into two regions with an energy gap of about 3-4 eV, thus validating our approach. The conduction to valence bandgap value calculated as the difference between the highest occupied and the lowest unoccupied electron states is  $E_G = 4.1$  eV, which is smaller than the experimental bandgap ( $\simeq 5.3 \text{ eV}$ , [10]) due to the well-known DFT bandgap underestimation.

Fig. 1. Band structure and DOS of  $\beta$ -Si<sub>3</sub>N<sub>4</sub> simulated with the SIESTA code (lines). Gaussian smearing has been applied to the simulated DOS for clarity. The experimental valence band DOS measured in [27] (circles) and [28] (triangles) are reported as reference.

The electronic properties of the materials (particularly dielectric materials) are often controlled by electrically active defects and impurities that generate energy states inside the bandgap. This is particularly true in the SiN layers for NVM applications, where the presence of defects determines the ability to trap the charge and, therefore, sets the memory behavior. The DOS of the crystalline  $\beta$ -Si<sub>3</sub>N<sub>4</sub> calculated in Fig. 1 does not show states in the bandgap, and thus, to emulate a more realistic SiN structure, we have introduced the most probable defects previously put in evidence by the physical–chemical analysis reported in the accompanying paper as well as in the literature.

## B. Atomic Structure of SiN Defects

The secondary ion mass spectrometry (SIMS) and multi internal reflection (MIR) measurements have shown that a high hydrogen concentration in the LPCVD SiN layers is present. The H atoms are associated with both Si-H and N-H bonds [10], [29]. Moreover, SIMS and ellipsometric measurements have confirmed a significant amount ( $\approx 6\%$ ) of excess silicon in the Si-rich samples [10]. Since the simulated material density of  $\beta$ -Si<sub>3</sub>N<sub>4</sub> ( $\simeq 3.1$  g/cm<sup>3</sup>) is higher than the experimental material density ( $\simeq 2.9$  g/cm<sup>3</sup>), we have neglected possible interstitial species because they tend to increase the material density. Vacancies are not expected to play a major role because they have high formation energy as they involve three or four broken bonds [13]. Therefore, we have mainly focused on substitutional point defects based on the introduction of hydrogen in the  $\beta$ -Si<sub>3</sub>N<sub>4</sub> lattice and the addition of further Si in Si-rich SiN layers [12]. This latter excess silicon may lead to the formation of Si-Si and Si-H bonds or Si dangling bonds [30]. The concentration of H atoms used in the atomistic simulations is close to that measured by the SIMS and MIR experiments [10], and this hydrogen incorporation lowers the mass density of the simulated material to a value of  $\simeq 2.98$  g/cm<sup>3</sup>, which is in good agreement with the XRR results of part I of this work. In this respect, in agreement with the findings of the stress measurements in [10], we have also introduced in the simulated SiN atomic structure a tensile strain that is also contributing to the mass density reduction. Since we verified that the effect of

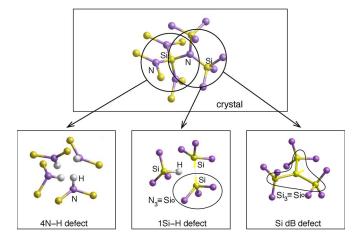

Fig. 2. Relaxed structure of the crystal  $\beta$ -Si<sub>3</sub>N<sub>4</sub> and main defects analyzed in this paper. The defects identified as 1Si–H and Si dB show two types of Si dangling bonds.

strain on the band structure is negligible at least up to the stress values measured in the samples, the stress was not included in the simulation of the band diagrams and of the trap energies.

Starting from  $\beta$ -Si<sub>3</sub>N<sub>4</sub>, we investigate three defects (see Fig. 2) that can be associated with N–H bonds to an ensemble of Si–H and Si–Si bonds and to Si dangling bonds (dB). The N–N bonds have not been considered since they are unstable, hence uncommon in nearly stoichiometric or *Si-rich* SiN layers [22], [31].

The first defect (4N–H in Fig. 2) is obtained by substituting a Si atom with four H atoms: the silicon vacancy leaves four N dangling bonds that can be saturated with four hydrogens, thus generating four N–H bonds.

The second defect (1Si–H in Fig. 2) is the substitution of a N atom with one hydrogen, thus leading to a single Si–H bond and a weak Si–Si covalent bond.

The third defect is a N atom substituted by one Si atom, generating one silicon dangling bond (Si dB in Fig. 2). We have verified by means of chemical potential calculations that these are the most probable hydrogen related configurations, i.e., those with the lowest Gibbs free energy of formation [3], [25], [26]. In addition, we have also verified that the 1Si–H and Si dB defects are the thermodynamically most stable ones in *std* SiN and *Si-rich* SiN, respectively.

Regarding the electrical properties of these defects, the DFT calculations show that the DOS of the 4N–H defect does not exhibit energy states in the bandgap [3]; hence, this defect is unlikely to explain the trapping properties of the SiN layers. On the contrary, as we will see later, both 1Si–H and Si dB defects are electrically active and lead to available energy states in the bandgap of the material. Therefore, in the following paper, we will focus our attention on the 1Si–H and Si dB defects.

Considerable experimental efforts have been made to understand the nature of charge trapping centers in SiN layers, and in this regard, electron spin resonance (ESR) measurements are useful for the detection and identification of dangling (broken) bonds [32]–[37] (see Table I). In particular, ESR identifies paramagnetic centers, i.e., atoms or molecules with one or more unpaired electrons [38]. On the contrary, diamagnetic centers,

TABLE IESR MEASUREMENTS ON SIN LAYERS TAKEN FROM LITERATURE. THE gFACTOR IDENTIFIES DIFFERENT TYPES OF ATOM CONFIGURATIONS [38].ESR EXPERIMENTS MEASURE THE g VALUES CORRESPONDINGTO THE 1SI-H AND SI dB DEFECTS SHOWN IN FIG. 2

| Defects       | 1Si–H                          | Si dB             |

|---------------|--------------------------------|-------------------|

| identified in | std SiN (after UV irradiation) | Si–rich SiN       |

|               | [33, 32, 34, 35, 36]           | [34, 36, 35, 37]  |

| g-factor      | 2.0028                         | 2.0055            |

| origin        | $N_3 \equiv Sio$               | $Si_3 \equiv Sio$ |

which do not contain unpaired electrons, are not observable by ESR.

For a freshly synthesized nearly stoichiometric SiN film, which corresponds to the SiN state in a virgin essentially neutral (nonprogrammed) cell, no ESR signal can be detected [32]. The signal for a Si atom bonded to three nitrogens (N $_3 \equiv Si\circ$ in Table I) can be detected with ESR only after ultraviolet (UV) irradiation [32]-[36]. This evidence is consistent with the 1Si–H defect (see Fig. 2): in the neutral state, the defect is formed by a Si-H bond and a weak Si-Si bond, and therefore, it is diamagnetic and not detectable by ESR. The UV irradiation possibly contributes to the breaking of the weak Si-Si covalent bond, generating Si dangling bonds that can be detected by ESR measurements. These evidences, together with the large concentration of Si-H bonds detected by the MIR measurements in part I of this study (see [10, Tab. 2]), support the choice of investigating the H-related defects as the main cause of the trapping properties of std SiN films.

Instead, the ESR signal corresponding to a Si atom bonded to three other Si atoms (Si<sub>3</sub>  $\equiv$  Si $\circ$  in Table I) has been measured in as deposited *Si-rich* SiN films and such signal increases for increasing concentration of SiH<sub>2</sub>Cl<sub>2</sub> used during fabrication, i.e., for an increasing concentration of Si [34]–[37]. This result supports the assumption, verified by chemical potential calculations [3], [25], [26], that Si dB (see Fig. 2) plays an important role in the trapping properties of *Si-rich* SiN samples.

## C. Electrical Properties of SiN Defects

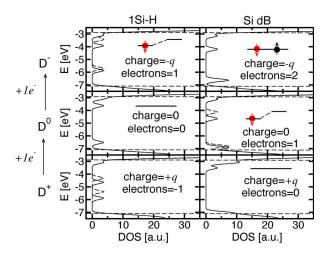

To understand the electrical properties of the aforementioned defects, namely, 1Si-H and Si dB, we reported in Fig. 3 the calculated total DOS for the SiN structure, including the 1Si-H defect (left) and the Si dB (right) in different charge states [3]. A smearing Gaussian function with 0.15-eV width has been convoluted with the DFT results. At this regard, note that the tails at the defect level edges and at the band edges are determined by the foregoing smearing function and do not have a quantitative meaning. The continuous and dashed lines represent the spin-up and -down DOSs, respectively. The defects induce states in the bandgap and, hence, are electrically active [3]. In particular, both defects generate a high energy "shallow" state (corresponding to one or two peaks in the upper part of the bandgap and also with horizontal lines) and a deep state in the SiN bandgap (identified by peaks in DOS). As shown in [3], the deep states are doubly occupied in neutral conditions  $(D^0 \text{ state})$ , and we verified that both defects can assume neutral

Fig. 3. Simulated total DOS and corresponding energy levels showing the electron states for neutral  $(D^0)$ , negatively  $(D^-)$ , and positively  $(D^+)$  charged defects. The charging of the defects is done by adding or subtracting one electron from the neutral state. In the D<sup>-</sup> state, the energy of the electrons trapped in the shallow energy states is similar; however, the 1Si-H defect (left) shows only one electron in the high energy state, while the Si dB (right) has two electrons trapped in the upper part of the bandgap. Note that the additional deep energy states identified by the peaks in the DOS in the lower part of the bandgap are filled by two electrons in neutral  $(D^0)$  and negatively charged  $(D^-)$  conditions and can only contribute to the capture of holes [3].

$(D^0)$ , positively  $(D^+)$ , and negatively  $(D^-)$  charged states,<sup>1</sup> in agreement with the amphoteric trap model [40]. Moreover, we verified by both the approach proposed in [41] and based on the analysis of the electron affinity and the ionization potential of the defects and the calculation of the formation energy of the defects as in [42] that, in neutral conditions (uncharged SiN), the most stable equilibrium configuration for the two defects is the  $D^0$  state.

Instead, when the SiN is charged by electrons, the D<sup>-</sup> state is more probable, and it should be remarked that, in this configuration, the energy level  $E_T$  of the shallow states of the Si dB defect is very similar to that of the 1Si-H defect, namely, both of them are about 1.0-1.2 eV below the SiN conduction band. Note that the D<sup>-</sup> state is the physical state of the majority of traps at the beginning of the erase and retention phases. Although possible corrections to the trap energy depth will be discussed in the following, at this stage, it is worth to note that, since the two defects have similar energy level (within approximately 0.2 eV), they are difficult to discriminate by means of activation energy experiments, as already pointed out in [43]. This evidence is also in qualitative agreement with the results of the KFM measurements in [9] that do not show differences in the detrapping rates of SiN films with different stoichiometries.

The electron occupation number for the same charge state (e.g.,  $D^-$ ) of the two types of defects is instead different: only one electron is present in the shallower state of the 1Si–H defect, while two are available in the Si dB defect. These results suggest that the main difference between the 1Si–H and Si dB defects is the number of trapped electrons for the same charge

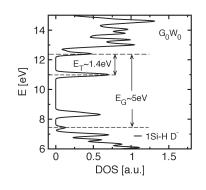

Fig. 4. Total DOS of  $\beta$ -Si<sub>3</sub>N<sub>4</sub> with one 1Si–H defect in the D<sup>-</sup> state calculated with the G<sub>0</sub>W<sub>0</sub> approximation and by using a supercell of 28 atoms. From the curve, it is possible to extract the energy width of the bandgap ( $E_G$ ) and the energy depth of the trapped electron with respect to the bottom of the conduction band ( $E_T$ ). Approximately 1 eV above the top of the valence band, it is possible to note also the presence of deep states always filled by two electrons in the D<sup>0</sup> and D<sup>-</sup> states.

*state and not the trap energy level*, as previously assumed by other authors [2], [7], [8] for traps in *std* and *Si-rich* SiN films.

To improve the level of confidence in our atomistic simulation results, we have validated some of the DFT simulations with calculations based on the many-body perturbation theory in the  $G_0W_0$  approximation.  $G_0W_0$  is the best method of choice for evaluating the energy bandgap with good precision (typically about  $\pm 0.1$  eV). The simulations have been performed with the ABINIT code [44], and for the sake of fair comparison, we have represented the core electrons with the same Troullier-Martin pseudopotentials adopted for the DFT calculations. All the simulations are fully converged (1000 electron bands). Due to the huge computational burden, we have adopted reduced supercells of 28 atoms. In Fig. 4, we report the DOS for the defective  $\beta$ -Si<sub>3</sub>N<sub>4</sub> with the 1Si–H defect in the negatively charged state. The bandgap calculated with the  $G_0W_0$  approximation for this structure is  $E_G = 5 \text{ eV}$ , which is 0.8 eV higher than the value estimated with the DFT calculations, and it is in good agreement with the experimental value extracted in [10] for the std SiN ( $E_G \simeq 5.3$  eV). It is worth noting that the introduction of one defect in a 28-atom supercell alters the ideal crystal lattice by increasing the Si concentration, which can explain the slightly reduced bandgap with respect to the experimental value.

For a similar reason, we could not achieve realistic GW calculations for the Si dB defects. In fact, the addition of excess Si dB defects to a supercell small enough to be computationally manageable results in an excessive increase in the Si concentration compared to the experimental one. Moreover, the Si dBs become so close that artificial mechanical and electronic interactions between the defects, not present for smaller Si concentration, come into play. The situation is much more favorable for the 1Si–H defect, likely because the hydrogen passivates the dangling bonds.

The trap energy depth of the 1Si–H defect extracted from the  $G_0W_0$  calculations is  $E_T = 1.4 \text{ eV}$ , and it is slightly higher than in DFT calculation, consistent with the increase of the calculated bandgap. This value is in fairly good agreement with the values reported in the literature ( $E_T = 1.2-1.7 \text{ eV}$ ) and obtained with different experimental techniques [45]–[49].

<sup>&</sup>lt;sup>1</sup>For the simulation of charged defects, to reach convergence, a uniformly distributed sheet charge was considered for the neutralization of the charge residing into the defect [39].

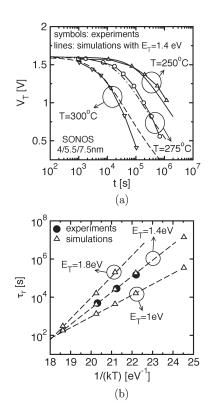

Fig. 5. (a) Experimental and simulated retention transients of a SONOS device at different temperatures. The experiments are taken from [47]. Note the good agreement between the measurements and the model when using  $E_T = 1.4 \text{ eV}$  in the simulations. A thick tunnel oxide (4 nm) prevents electron tunneling toward the substrate. (b) Arrhenius plots of the retention time  $\tau_r$  as a function of temperature for different  $E_T$  values used in the simulations. The model reproduces the experimental activation energy (i.e., the slope of the curve) for  $E_T$  close to 1.4 eV. The experiments are taken from [47].

# III. DEVICE-LEVEL ELECTRICAL MODELING AND EXPERIMENTAL VERIFICATION

#### A. Device-Level Electrical Model

As a first step to verify if the insight obtained by means of atomistic simulations is indeed useful to explain the dependence of cell performance on SiN stoichiometry, we plugged the calculated trap parameters for std SiN in the electrical model described in detail in [46] and then simulated high temperature retention experiments. The model solves the electrostatics self-consistently with the in and out electron tunneling fluxes, the drift-diffusion transport in the SiN conduction band, and the Shockley-Read-Hall generation/recombination (considering Poole–Frenkel emission). We simulated a SONOS cell with std SiN and tunnel and top oxides of 4 and 7.5 nm, respectively, because the thick tunnel oxide strongly reduces the charge loss by direct tunneling, whereas the high temperature favors the thermal emission of the trapped electrons, which results in the main charge loss mechanism [50]. Therefore, in this condition, the retention curves are very sensitive to the energy level of the filled traps. All the main model parameters have been taken from [46], except for the trap energy (in retention conditions), which has been adjusted to the value  $E_T = 1.4 \text{ eV}$ , in agreement with the  $G_0W_0$  calculations. Fig. 5(a) reports the comparison between the model and the experimental data from [47]. As can be seen, good mutual agreement is obtained by

| TABLE II                                                              |  |  |  |

|-----------------------------------------------------------------------|--|--|--|

| MAIN MODIFICATIONS TO THE MODEL IN [46] USED TO DESCRIBE THE          |  |  |  |

| TRAPS IN THE $std$ and $Si$ - $rich$ SiN Samples. $Q_N$ Is the Excess |  |  |  |

| Charge With Respect to the Neutral State $(D^0)$ That Is              |  |  |  |

| Responsible for the $V_T$ Shift. $n^T$ Is the Electron                |  |  |  |

| CONCENTRATION IN THE HIGHER ENERGY LEVEL, AND IT INFLUENCES           |  |  |  |

| THE CHARGE LOSS BY TUNNELING. $N_{ m 1Si-H}^T~(N_{ m SidB}^T)$ Is the |  |  |  |

| CONCENTRATION OF THE $Si-H$ (Si dB) DEFECTS                           |  |  |  |

$N_{\rm ISi-H}^T = 2.5 \cdot 10^{19} \text{ cm}^{-3}$  Is in Agreement With the Experimental Number of Si-H defects [10, Tab. II], While  $N_{\rm SidB}^T = 2.5 \cdot 10^{19} \text{ cm}^3$  Is Obtained by the Fitting of the Experimental Data. t = 0 Is the Beginning of the Program Translent (Neutral State)

| Defects     | Trap density                                 | $n^T(x,t\!=\!0)$ | $Q_N(x,t)$                       |

|-------------|----------------------------------------------|------------------|----------------------------------|

| 1Si-H       | $N_{1\mathrm{Si-H}}^{T}$                     | 0                | $-q[n^T(x,t)]$                   |

| Si dB       | $N_{ m SidB}^T$                              | $N_{ m SidB}^T$  | $-q[n^T(x,t)-N^T_{\text{SidB}}]$ |

| 1Si–H+Si dB | $N_{1\mathrm{Si-H}}^T + N_{\mathrm{SidB}}^T$ | $N_{\rm SidB}^T$ | $-q[n^T(x,t)-N_{\text{SidB}}^T]$ |

using the  $E_T$  value predicted by the  $G_0W_0$  simulations (Fig. 4). In fact, Fig. 5(b) reports the Arrhenius plot of the measured and simulated retention times for the same device, and it is evident that the model can reproduce the experiments by using  $E_T = 1.4$  eV, calculated with the atomistic models.

This result provides an important confirmation that the hydrogen related defects are the plausible responsible for the trapping in *std* LPCVD SiN and that the developed SiN atomistic model is a reliable tool for obtaining important information regarding the electrical behavior of the SiN films. In this respect, to test the impact of SiN composition on cell characteristics and to verify the insight given by the atomistic model on the occupation state of the traps, we modified the device-level electrical simulator to implement traps of both the 1Si–H and the Si dB type and to account for the different occupation numbers of these traps.

As for the 1Si–H defect, since in the  $D^-$  state only one electron occupies the shallowest state (see Fig. 3), we have considered a concentration of traps ( $N_{1Si-H}^T$ ) that can be filled with an electron density  $n^T$ . The charge density responsible for the threshold voltage shift ( $\Delta V_T$ ) is then  $Q_N = -qn_T$ .

In the case of the Si dB defect, instead, the D<sup>0</sup> configuration (see Fig. 3) of the trap has already an electron in the shallowest state. Therefore, considering a Si dB concentration of  $N_{\text{SidB}}^T$ , the uncharged *Si-rich* SiN has a trapped electron density (due to the Si dB defects) of  $n^T = N_{\text{SidB}}^T$ . The charging of the SiN (see Fig. 3) drives the Si dB defects in the D<sup>-</sup> state that presents two electrons trapped in the shallowest energy level. This means that such defects can be charged with an electron density up to  $2 \cdot N_{\text{SidB}}^T$ . However, the net charge responsible for the threshold voltage shift is only  $Q_N = -q(n_T - N_{\text{SidB}}^T)$ .

By using this approach, it is possible to simulate with the same model equations described in [46] a cell featuring a SiN layer with any mixture of 1Si–H and Si dB defects (with a density of  $N_{1\text{Si}-\text{H}}^T$  and  $N_{\text{SidB}}^T$ , respectively). In fact, as summarized in Table II, while considering a unique trapped electron concentration  $(n^T)$ , we simply assume that the initial (corresponding to the neutral state)  $n^T$  value is  $N_{\text{SidB}}^T$ .

To simulate the *std* SiN cells, we have then assumed that only 1Si–H defects are present in the film with a concentration  $N_{1Si-H}^{T}$ . For the *Si-rich* SiN samples, instead, we have assumed the presence of both 1Si–H and Si dB defects. In both devices,

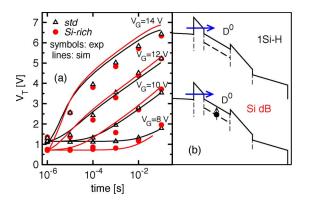

Fig. 6. (a) Comparison between measured and simulated program characteristics for the devices with *std* and *Si-rich* SiN. The devices are the type-B MANOS cells characterized in [10] with a tunnel oxide of 2.2 nm and a SiN layer of 5 nm. (b) Conduction band diagram and trap energy occupation for the 1Si–H and Si dB traps at the beginning of the program transient ( $V_G = 14$  V, virgin device, traps in the neutral state D<sup>0</sup>). Arrows and dashed lines are sketches to represent the charge injection and the trap energy levels, respectively.

we have chosen  $N_{1\rm Si-H}^T = 2.5 \cdot 10^{19} \,\mathrm{cm}^{-3}$ , in agreement with the MIR results of the accompanying paper (see [10, Tab. 2]), while we used  $N_{\rm SidB}^T$  as a fitting parameter in the *Si-rich* SiN case. In this respect, it is worth noting that the obtained  $N_{\rm SidB}^T$  value  $(2.5 \cdot 10^{19} \,\mathrm{cm}^{-3})$  is comparable with the  $N_{1\rm Si-H}^T$ concentration, in agreement with the similar Gibbs free energies calculated for the two defects considering the fabrication conditions in the *Si-rich* recipe [3]. All the other model parameters, and in particular those describing the traps, have been taken as in [46], except for  $E_T = 1.4 \,\mathrm{eV}$ , as previously explained.

#### B. Program and Retention Characteristics

Fig. 6(a) compares the simulations and the experiments of the MANOS devices with both std and Si-rich SiN layers described in the companion paper [10]. There is essentially no difference between the program curves of the two cells with different SiN, and this behavior is well reproduced by the model. As already suggested in part I of this work, this is expected because the programming (charging) phase is limited by the electron injection from the substrate and not by the type or number of traps in the SiN layer, whose concentration is large enough to accommodate all the incoming carriers  $(N_{1\text{Si}-\text{H}}^T > 10^{19} \text{ cm}^{-3})$ . The presence of electrons in the high energy level of the Si dB defect in the neutral state, which is the initial state for the program transient, has negligible effect on the programming. Moreover, since the equivalent oxide thickness (EOT) is the same for std and Si-rich samples (as shown in, Fig. 3[10]), the electric fields across the tunnel oxide [Fig. 6(b)], and hence the electron injection current, are approximately the same for a given gate voltage  $V_G$ . Therefore, the program transients are almost the same in the two samples.

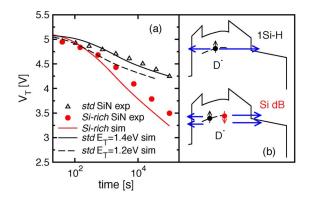

Experiments and simulations show, instead, the different retention characteristics of the *std* and *Si-rich* samples [Fig. 7(a)]. At the beginning of the retention transient, the equal  $\Delta V_T$  corresponds to almost identical distributions of the charge density  $Q_N$  in the SiN layer (not shown) and of the electric field in both gate stacks [Fig. 7(b)]. However, a higher leakage through the

Fig. 7. (a) Comparison between measured and simulated retention characteristics at 25 °C for the devices with *std* and *Si-rich* SiN. The devices are the type-B MANOS cells characterized in [10].  $N_{1\rm Si-H}^T = 2.5 \cdot 10^{19} {\rm ~cm^{-3}}$ , and  $N_{\rm SidB}^T = 2.5 \cdot 10^{19} {\rm ~cm^{-3}}$ . (Filled lines) Model considering the occupation number of the defects. (Dashed line) Model considering only a possible trap energy difference. (b) Conduction band diagram and trap energy occupation for the 1Si–H and Si dB traps at the beginning of the retention transient ( $V_G = 0$ , programmed device, traps in the negatively charged state D<sup>-</sup>). Arrows and dashed lines are sketches to represent the charge emission and the trap energy levels, respectively.

tunnel oxide is present in the Si-rich SiN compared to the std SiN devices because of the larger value of the trapped charge concentration  $n^T$  in the shallow traps of the former device, which is due to the additional electron present in the Si dB defects [Fig. 7(b)]. The main discharge mechanism at room temperature is the direct tunneling of trapped electrons through the tunnel oxide toward the substrate, which is indeed directly proportional to  $n^{T}$ . The faster charge detrapping exhibited mostly by Si-rich samples is thus explained by the extra electron available in the trap in the  $D^-$  state of Si dB defects. It is worth noting that the model cannot reproduce the Si-rich SiN curve by only invoking a shallower trap energy depth for the Si-rich SiN defects, as suggested in the past [2], [7]. In fact, the very small energy difference ( $\approx 0.1-0.2$  eV) between the traps in the std and Si-rich SiN films is not sufficient by itself to explain the large difference in the retention curves of the two SiN compositions (Fig. 7(a), dashed line). These results indicate that the key physical elements revealed by the atomistic trap models are indeed consistent with the electrical behavior of the charge-trap NVM cells.

## C. Gate Stress Experiments

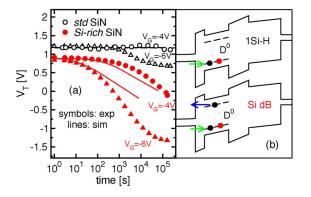

To confirm experimentally the role of the extra electron in the defects of *Si-rich* SiN layers on the retention curves, we devised an *ad hoc* gate stress experiment with negative  $V_G$ . Starting from an approximately neutral sample where most traps are in the D<sup>0</sup> state, we applied a small negative gate voltage. For weak electric fields, the charge exchange with the substrate regards mainly the traps close to the tunnel oxide/SiN interface. Therefore, although the *Si-rich* SiN shows a bandgap reduction, which may partly contribute to modify the overall barrier for tunneling, the energy barrier seen by the holes is essentially due to the tunnel oxide [see Fig. 8(b)]. Since both devices have the same EOT, hence the same voltage drop across the tunnel oxide, the hole injection from the substrate, if any, is thus essentially

Fig. 8. (a) Comparison between measured and simulated  $V_T$  during field accelerated retention experiments at low negative  $V_G$  for devices with *std* and *Si-rich* SiN. The devices are the type-B MANOS cells characterized in [10]. The initial state corresponds to the virgin device.  $N_{1\rm Si-H}^T = 2.5 \cdot 10^{19} \text{ cm}^{-3}$ , and  $N_{\rm SidB}^T = 2.5 \cdot 10^{19} \text{ cm}^{-3}$ . (b) Band diagram and trap energy occupation for the 1Si-H and Si dB traps at the beginning of the experiment ( $V_G = -4$  V, virgin device, traps in the neutral state D<sup>0</sup>). Arrows and dashed lines are sketches to represent the charge injection/emission and the trap energy levels, respectively. In the lower part of the SiN bandgap are indicated also the additional deep energy levels always completely filled in the neutral state D<sup>0</sup>, which can only contribute to the hole capture [3] and that are not explicitly indicated (but nevertheless appear as peaks in the DOS) in Fig. 3.

the same in the two gate stacks. However, if the *Si-rich* sample in the neutral state has high energy states filled with electrons, as shown by the atomistic simulations, then we should observe a charge loss rate also from the uncharged state. Indeed, the experiments show that, while the threshold voltage remains fairly constant in the *std* SiN sample, it drifts remarkably in the *Si-rich* one [Fig. 8(a)]. The electrical model well reproduces the experiments with the same set of parameters used for the program and the retention simulations in Figs. 6 and 7.

The difference in the experimental data of Fig. 8(a) is naturally explained by observing the band diagram in Fig. 8(b): the small  $V_G$  hardly affects the dominant defect (1Si–H) of the *std* SiN sample in the neutral state D<sup>0</sup>, where, on one hand, no electrons are available in the shallowest states, and, on the other hand, hole injection is negligible and cannot discharge appreciably the deeper states. Therefore, the characteristic at  $V_G = -4$  V of the *std* SiN cell remains flat, while at  $V_G =$ -6 V, the small  $\Delta V_T$  shift is presumably due to a small hole injection.

The small  $V_G$  is nevertheless sufficient to cause emission by tunneling of the additional electrons residing in the high energy states of the *Si-rich* samples [Fig. 8(b)], thus causing a net positive charge in the SiN layer and, therefore, the remarkable threshold voltage shift in Fig. 8(a). It is worth to underline that this behavior cannot be explained, once again, by the different trap energy depths for the two defects, as suggested in the past [2], [7], because if both trap types were empty at the beginning of the gate stress experiments, then the electron emission would not take place, and hence, the energy depth of the traps would be irrelevant for the threshold voltage evolution, leading to similar flat  $\Delta V_T$  transients for both of the SiN compositions. For the same reason, also the change of other parameters in the trapping/detrapping model (e.g., the attemptto-escape frequency [46]) would not affect the  $V_T$  evolution. These experimental data provide additional direct evidence confirming that an *extra charge is available to tunnel out of the SiN in the Si-rich samples*. Furthermore, the ability of the electrical model to reproduce the experiments is a direct verification of the SiN physical picture described by atomistic simulations.

## **IV. CONCLUSION**

In this paper, we have derived atomic structures for the LPCVD SiN storage layers exploited in charge-trap NVM devices and for their hydrogen related defects responsible for the memory effect, which are consistent with all the experimental evidences presented in part I of this work. Although oxygen related defects at the interfaces between the SiN and the tunnel and top dielectrics may be present as well [11] and their role cannot be completely excluded, the experimentally validated atomistic simulations suggest that the dominant defects in our std and Si-rich SiN samples are the 1Si-H defects and the Si dangling bonds, respectively. We have shown that these defects have quite similar trap energy depth but different electron occupation numbers for the same charge state. These conclusions are not inconsistent with the findings in [7] and [8], where very similar energy distributions have been proposed for traps in nearly stoichiometric and Si-rich SiN samples. The similar trap energy depth is also in qualitative agreement with KFM measurements of the lateral charge spread in SiN layers [9], [43] and the retention experiments on thick tunnel oxide devices [10]. However, the very small energy difference ( $\approx 0.1-0.2 \text{ eV}$ ) reported for the traps in std and Si-rich SiN films is insufficient to explain the large difference in the retention experiments of the two SiN compositions [see Fig. 7(a)]. Furthermore, the small positive charge in the virgin Si-rich films shown by the CV curves in Fig. 3 of part I corroborates the presence of one electron in the shallow state of the neutral Si dB [10]. Indeed, part of these electrons might be lost during the high temperature steps of the device fabrication, leading to the positive charging of the SiN layer put in evidence in Fig. 3 of part I. However, the extracted charge density  $(2.25 \cdot 10^{18} \text{ cm}^{-3})$ , Fig. 3 in part I) is about 10% of the estimated Si dB density, demonstrating that the charge state of the considered Si dB defects is quite stable. The electrical modeling of the retention experiments on SONOS devices confirmed the main results of G<sub>0</sub>W<sub>0</sub> simulations that calculate a trap energy depth  $E_T \sim 1.4$  eV below the SiN conduction band.

Moreover, a simple technique has been devised to account for the findings of the atomistic simulations in our device-level electrical model for SiN-based memories, and the simulations of the program and retention transients of the MANOS cells provide a consistent explanation of the experiments. *We showed that the different electron occupation numbers of the shallowest energy levels can explain the faster erasing speed and charge loss rate of our Si-rich devices with respect to std SiN samples.* Again, this is essentially not in contrast with the recent findings in [8], where the larger charge loss in the *Si-rich* SiN is reproduced not only with a small difference in the trap energy but also with a larger concentration of electrons available for tunneling at the SiN/tunnel oxide interface.

This physical picture is consistent with the in-depth material analysis, the electrical characterization of cells, and the atomistic and electrical modeling. Indeed, our results pointed out that not only the energy depth but also the occupation state of the different traps is an important parameter for the processes involved in the operation of charge-trapping memory cells. The occupation number in the neutral state should thus be considered, together with the trap energy, as one of the parameters characterizing the SiN traps. Our test structures exhibit accelerated charge loss compared to industrial product quality samples, likely because of a nonoptimized gate stack rather than because of the inherently poor SiN film quality. Therefore, we believe that the physical understanding gained in this study is relevant for interpreting charge trapping and loss in other situations as well. While other physical effects may coexist, our models and experiments show that they do not appear to be mandatory to explain the experiments.

In this paper, to the best of our knowledge for the first time, for charge trapping materials, different scales of modeling have been connected with a deductive "upscaling" approach; in particular, results from a lower-scale calculation (atomistic models for SiN defects) have been used as parameters for a higher-scale simulation method (electrical model for chargetrap memories). This study has allowed us to give a coherent physical picture of our experimental data, including both material analyses and charge-trap memory characteristics. Furthermore, we believe the systematic analytical methodology developed in this work, combining experiments (physical and electrical characterization) and simulations (atomistic and device-level), can also be useful for the investigation of other defect types or trapping materials, possibly clarifying the strategy for the improvement of the performance of charge trapping memory technologies.

#### References

- [1] N. Goel, D. Gilmer, H. Park, V. Diaz, Y. Sun, J. Price, C. Park, P. Pianetta, P. Kirsch, and R. Jammy, "Erase and retention improvements in charge trap flash through engineered charge storage layer," *IEEE Electron Device Lett.*, vol. 30, no. 3, pp. 216–218, Mar. 2009.

- [2] S. Sandhya, U. Ganguly, N. Chattar, C. Olsen, S. M. Seutter, L. D. R. Hung, J. M. Vasi, and S. Mahapatra, "Effect of SiN on performance and reliability of charge trap flash (CTF) under Fowler–Nordheim tunneling program/erase operation," *IEEE Electron Device Lett.*, vol. 30, no. 2, pp. 171–173, Feb. 2009.

- [3] E. Vianello, L. Perniola, P. Blaise, G. Molas, J. Colonna, F. Driussi, P. Palestri, D. Esseni, L. Selmi, N. Rochat, C. Licitra, D. Lafond, R. Kies, G. Reimbold, B. D. Salvo, and F. Boulanger, "New insight on the charge trapping mechanisms of SiN-based memory by atomistic simulations and electrical modeling," in *IEDM Tech. Dig.*, 2009, pp. 83–86.

- [4] G. V. den Bosch, A. Furnémont, M. B. Zahid, R. Degreave, L. Breuil, A. Cacciato, A. Rothschild, C. Olsen, U. Ganguly, and J. V. Houdt, "Nitride engineering for improved erase performance and retention of TANOS NAND flash memory," in *Proc. IEEE NVSMW/ICMTD*, 2008, pp. 128–129.

- [5] C. Sandhya, A. Oak, N. Chattar, A. Joshi, U. Ganguly, C. Olsen, S. Seutter, L. Date, R. Hung, J. Vasi, and S. Mahapatra, "Impact of SiN composition variation on SANOS memory performance and reliability under NAND (FN/FN) operation," *IEEE Trans. Electron Devices*, vol. 56, no. 12, pp. 3123–3132, Dec. 2009.

- [6] D. Gilmer, N. Goel, H. Park, C. Park, S. Verma, G. Bersuker, P. Lysaght, H. Tseng, P. Kirsch, K. Saraswat, and R. Jammy, "Engineering the complete MANOS-type NVM stack for best in class retention performance," in *IEDM Tech. Dig.*, 2009, pp. 439–442.

- [7] T. H. Kim, I. H. Park, J. D. Lee, H. C. Shin, and B.-G. Park, "Electron trap density distribution of *Si-rich* silicon nitride extracted using the modified negative charge decay model of silicon-oxide-nitride-oxide-silicon structure at elevated temperatures," *Appl. Phys. Lett.*, vol. 89, no. 6, p. 063 508, Aug. 2006.

- [8] A. Suhane, A. Arreghini, R. Degraeve, G. van den Bosch, L. Breuil, M. Zahid, M. Jurczak, K. De Meyer, and J. Van Houdt, "Validation of retention modeling as a trap-profiling technique for SiN-based chargetrapping memories," *IEEE Electron Device Lett.*, vol. 31, no. 1, pp. 77–79, Jan. 2010.

- [9] E. Vianello, E. Nowak, D. Mariolle, N. Chevalier, L. Perniola, G. Molas, J. Colonna, F. Driussi, and L. Selmi, "Direct probing of trapped charge dynamics in SiN by Kelvin force microscopy," in *Proc. ICMTS*, 2010, pp. 94–97.

- [10] E. Vianello, F. Driussi, L. Perniola, G. Molas, J.-P. Colonna, B. De Salvo, and L. Selmi, "Explanation of the charge trapping properties of silicon nitride storage layers for NVMs—Part I: Experimental evidences from physical and electrical characterization," *IEEE Trans. Electron Devices*, DOI:10.1109/TED.2011.2140116.

- [11] K. Yamaguchi, A. Otake, K. Kobayashi, and K. Shiraishi, "Atomistic guiding principles for MONOS-type memories with high program/erase cycle endurance," in *IEDM Tech. Dig.*, 2009, pp. 275–278.

- [12] M. Petersen and Y. Roizin, "Density functional theory study of deep traps in silicon nitride memories," *Appl. Phys. Lett.*, vol. 89, no. 5, p. 053 511, Jul. 2006.

- [13] J. Robertson, "Defects and hydrogen in amorphous silicon nitride," *Philos. Mag. B, Phys. Condens. Matter Electron. Opt. Magn. Prop.*, vol. 69, no. 2, pp. 307–326, 1994.

- [14] M.-E. Grillo, C. Freysoldt, and S. Elliot, "Native defects in hexagonal β-Si<sub>3</sub>N<sub>4</sub> studied using density functional theory calculations," *Phys. Rev. B, Condens. Matter*, vol. 83, no. 8, p. 085 208, Feb. 2011.

- [15] A. Arreghini, F. Driussi, E. Vianello, D. Esseni, M. J. van Duuren, D. S. Golubovic, N. Akil, and R. van Schaijk, "Experimental characterization of the vertical position of the trapped charge in Si nitride-based non volatile memory cells," *IEEE Trans. Electron Devices*, vol. 55, no. 5, pp. 1211–1219, May 2008.

- [16] E. Vianello, M. Bocquet, F. Driussi, L. Perniola, G. Molas, and L. Selmi, "Program efficiency and high temperature retention of SiN/high-K based memories," *Microelectron. Eng.*, vol. 86, no. 7–9, pp. 1830–1833, Jul.–Sep. 2009.

- [17] L. Giacomazzi and P. Umari, "First-principles investigation of electronic structural, and vibrational properties of a-Si<sub>3</sub>N<sub>4</sub>," *Phys. Rev. B, Condens. Matter*, vol. 80, no. 14, p. 144 201, Oct. 2009.

- [18] T. Pham, T. Li, S. Shankar, F. Gygi, and G. Galli, "First-principles investigations of the dielectric properties of crystalline and amorphous Si<sub>3</sub>N<sub>4</sub> thin films," *Appl. Phys. Lett.*, vol. 96, no. 6, p. 062 902, Feb. 2010.

- [19] P. Kroll, "Structure and reactivity of amorphous silicon nitride investigated with density-functional methods," J. Non-Cryst. Solids, vol. 293–295, pp. 238–243, Nov. 2001.

- [20] C.-M. Wang, X. Pan, M. Rühle, F. L. Riley, and M. Mitomo, "Silicon nitride crystal structure and observations of lattice defects," *J. Mater. Sci.*, vol. 31, no. 20, pp. 5281–5298, Oct. 1996.

- [21] Y. Ding, H. Zhou, M. Xu, Y. Shen, Q. Chen, W.-J. Zhu, and H. He, "Firstprinciples study of gamma- Si<sub>3</sub>N<sub>4</sub> with generalized gradient approximation and local density approximation," *Int. J. Mod. Phys. B*, vol. 22, no. 13, pp. 2157–2167, 2008.

- [22] E. Bustarret, M. Bensouda, M. Habrard, J. Bruyère, S. Poulin, and S. Gujrathi, "Configurational statistics in a- Si<sub>x</sub>N<sub>y</sub>H<sub>z</sub> alloys: A quantitative bonding analysis," *Phys. Rev. B, Condens. Matter*, vol. 38, no. 12, pp. 8171–8184, Oct. 1988.

- [23] S. Hao, B. Delley, and C. Stampfl, "Structure and properties of TiN(111) interfaces in superhard nanocomposites: First-principles investigations," *Phys. Rev. B, Condens. Matter*, vol. 74, no. 3, p. 035 402, 2006.

- [24] D. Sánchez-Portal, P. Ordejón, E. Artacho, and J. Soler, "Densityfunctional method for very large systems with LCAO basis sets," *Int. J. Quantum Chem.*, vol. 65, no. 5, pp. 453–461, 1997.

- [25] E. Vianello, "Characterization and modelling of silicon-nitride based non volatile memories," Ph.D. dissertation, Univ. Udine, Italy, 2010.

- [26] E. Vianello, P. Blaise, F. Driussi, and L. Selmi, "Electronic structure of defects for a chemically grown silicon nitride: Hydrogen effect, and stressinduced structural disorder," *Phys. Rev. B, Condens. Matter*, submitted for publication.

- [27] A. Iqbal, W. B. Jackson, C. C. Tsai, J. W. Allen, and C. W. Bates, "Electronic structure of silicon nitride and amorphous silicon/silicon nitride band offset by electron spectroscopy," *J. Appl. Phys.*, vol. 61, no. 8, pp. 2947–2954, Apr. 1987.

- [28] Z. A. Weinberg and R. A. Pollak, "Hole conduction and valence-band structure of Si<sub>3</sub>N<sub>4</sub> films on Si," *Appl. Phys. Lett.*, vol. 27, no. 4, pp. 254– 255, Aug. 1975.

- [29] M. Olivier, F. Martin, A. Chabli, G. Lefeuvre, F. Conne, and N. Rochat, "Infrared study of hydrogen in ultra-thin silicon nitride films using multiple internal reflection spectroscopy (MIR) in 200 nm silicon wafers," *Phys. Stat. Sol.* (A), vol. 175, no. 1, pp. 137–143, Sep. 1999.

- [30] F. Habraken, "Characterization of LPCVD and PCVD silicon oxynitride films," *Appl. Surf. Sci.*, vol. 30, pp. 186–196, 1987.

- [31] Z. Yin and F. Smith, "Free-energy model for bonding in amorphous covalent alloys," *Phys. Rev. B, Condens. Matter*, vol. 43, no. 5, pp. 4507–4510, Feb. 1991.

- [32] S. E. Curry, P. M. Lenahan, D. T. Krick, J. Kanicki, and C. Kirk, "Evidence for negative electron–electron correlation energy in the dominant deep trapping center in silicon nitride films," *Appl. Phys. Lett.*, vol. 56, no. 14, pp. 1359–1361, Apr. 1990.

- [33] W. L. Warren, J. Kanicki, J. Robertson, E. H. Poindexter, and P. J. McWhorter, "Electron paramagnetic resonance investigation of charge trapping centers in amorphous silicon nitride films," *J. Appl. Phys.*, vol. 74, no. 6, pp. 4034–4046, Sep. 1993.

- [34] Y. Kamigaki, S. Minami, and H. Kato, "A new portrayal of electron and hole traps in amorphous silicon nitride," *J. Appl. Phys.*, vol. 68, no. 5, pp. 2211–2215, Sep. 1990.

- [35] S. Minami and Y. Kamigaki, "Investigation of charge-trapping centers in low-pressure chemical vapor deposition Si<sub>3</sub>N<sub>4</sub> thin films," *Electron. Commun. Jpn.*, vol. 78, no. 4, p. 101, 1995.

- [36] D. Jousse, J. Kanicki, and J. H. Stathis, "Observation of multiple silicon dangling bond configurations in silicon nitride," *Appl. Phys. Lett.*, vol. 54, no. 11, pp. 1043–1045, Mar. 1989.

- [37] V. Gritsenko, A. Milov, M. Efremov, V. Volodin, H. Wong, N. Pazdnikov, and K. Zhuravlev, "Silicon nanocluster in silicon nitride: Photoluminescence, Raman scattering and ESR studies," in *Proc. IEEE Optoelectron. Microelectron. Mater. Devices*, 1996, pp. 196–199.

- [38] J. Weil and J. Bolton, Electron Paramagnetic Resonance: Elementary Theory and Practical Applications. New York: Wiley-Interscience, 2001.

- [39] C. G. Van de Walle and J. Neugebauer, "First-principles calculations for defects and impurities: Applications to III-nitrides," *Appl. Phys. Rev.*, vol. 95, no. 8, pp. 3851–3879, 2004.

- [40] S. Fujita and A. Sasaki, "Dangling bonds in memory-quality silicon nitride films," J. Electrochem. Soc., vol. 132, no. 2, pp. 398–402, Feb. 1985.

- [41] G. Pacchioni and D. Erbetta, "Charge transfer and charge conversion of K and N Defects Centers in Si<sub>3</sub>N<sub>4</sub>," *Phys. Rev. B, Condens. Matter*, vol. 61, no. 22, pp. 15 005–15 010, Jun. 2000.

- [42] S. Zhang and J. Northrup, "Chemical potential dependence of defect formation energies in GaAs: Application to Ga self-diffusion," *Phys. Rev. Lett.*, vol. 67, no. 17, pp. 2339–2342, Oct. 1991.

- [43] E. Vianello, E. Nowak, L. Perniola, F. Driussi, P. Blaise, G. Molas, B. D. Salvo, and L. Selmi, "A consistent explanation of the role of the SiN composition on the program/retention characteristics of MANOS and NROM like memories," in *Proc. IMW*, 2010, pp. 106–109.

- [44] X. Gonze, J.-M. Beuken, R. Caracas, F. Detraux, M. Fuchs, G.-M. Rignanese, L. Sindic, M. Verstraete, G. Zerah, F. Jollet, M. Torrent, A. Roy, M. Mikami, P. Ghosez, J.-Y. Raty, and D. Allan, "First-principles computation of material properties: The ABINIT software project," *Comput. Mater. Sci.*, vol. 25, no. 3, pp. 478–492, Nov. 2002.

- [45] E. Vianello, F. Driussi, P. Palestri, A. Arreghini, D. Esseni, L. Selmi, N. Akil, M. van Duuren, and D. Golubović, "Impact of the charge transport in the conduction band on the retention of Si-nitride based memories," in *Proc. IEEE ESSDERC*, 2008, pp. 107–110.

- [46] E. Vianello, F. Driussi, A. Arreghini, P. Palestri, D. Esseni, L. Selmi, N. Akil, M. van Duuren, and D. Golubovic, "Experimental and simulation analysis of program/retention transients in silicon nitride-based NVM cells," *IEEE Trans. Electron Devices*, vol. 56, no. 9, pp. 1980–1990, Sep. 2009.

- [47] C. Compagnoni, A. S. Spinelli, and A. L. Lacaita, "Experimental study of data retention in nitride memories by temperature and field acceleration," *IEEE Electron Device Lett.*, vol. 28, no. 7, pp. 628–630, Jul. 2007.

- [48] Y. Rozin, A. Yankelevich, and Y. Netzer, "Novel techniques for data retention and Leff measurements in two bit *microFLASH* memory cells," *AIP Conf. Proc.*, vol. 28, no. 7, pp. 628–630, Jan. 2001.

- [49] M. Naich, G. Rosenman, Y. Roizin, and M. Molotskii, "Exoelectron emission studies on trap spectrum in ultrathin amorphous Si<sub>3</sub>N<sub>4</sub> films," *Solid State Electron.*, vol. 48, no. 3, pp. 477–482, Mar. 2004.

- [50] A. Arreghini, N. Akil, F. Driussi, D. Esseni, L. Selmi, and M. J. van Duuren, "Long term charge retention dynamics of SONOS cells," *Solid State Electron.*, vol. 52, no. 9, pp. 1460–1466, Sep. 2008.

**Elisa Vianello** received the Laurea degree in electronic engineering from the Università degli Studi di Udine, Udine, Italy, and the Ph.D. degree from the Università degli Studi di Udine and the Institut National Polytechnique de Grenoble, Grenoble, France, in May 2010.

Between 2008 and 2009, she was with the Laboratory of Electronics, Technology, and Instrumentation, CEA Grenoble, where she worked on the electrical characterization of charge-trap high-*k*-based memories. She is currently with the

Department of Electrical, Managerial and Mechanized Engineering (DIEGM), University of Udine, and also with CEA-LETI, MINATEC Campus, Grenoble, France Her research interests include modeling, characterization, and reliability of nonvolatile memory, focusing on reliability issues related to the statistical distribution of stress-induced leakage current and on the modeling and characterization of SONOS/TANOS memory cells.

**Francesco Driussi** received the Laurea and Ph.D. degrees in electronic engineering from the University of Udine, Udine, Italy, in 2000 and 2004, respectively.

In 2005, he was a Research Associate with the University of Udine. From October 2002 to September 2003, he held a student position with Philips Research Leuven, Leuven, Belgium. He is currently with the Department of Electrical, Managerial and Mechanized Engineering, University of Udine. His research activities are mainly in the field

of nonvolatile memory cell reliability, and in particular, his interests have been in the characterization of device degradation and gate dielectric reliability. In particular, he has worked on substrate enhanced hot electron phenomena and investigated their implications for Flash EEPROM devices. More recently, he worked on the development of physical and statistical models for the study of SILC in large FLASH memory arrays and of the oxide trap generation and distribution. At the moment, his main activity is on the characterization and modeling of SONOS/TANOS memory cells and on the in-depth investigation of the trapping properties of silicon nitride. Parts of his activities now are also in the field of the experimental characterization and modeling of the carrier mobility in MOSFET devices featuring strained silicon and high-K gate stacks.

P. Blaise, photograph and biography not available at the time of publication.

**Pierpaolo Palestri** (M'05) received the Laurea degree in electronic engineering from the University of Bologna, Bologna, Italy, in 1998 and the Ph.D. degree in electronic engineering from the University of Udine, Udine, Italy, in 2003.

In 1998, he was a Research Assistant with the Department of Electrical, Mechanical and Management Engineering, University of Udine, where he worked in the field of device simulation. From July 2000 to September 2001, he held a post-doctoral position with Bell Laboratories, Lucent Technolo-

gies (now Agere Systems), Murray Hill, NJ, where he worked on high-speed silicon–germanium bipolar technologies. He became an Assistant Professor in October 2001 and has been Associate Professor since November 2005 with the University of Udine. He has coauthored more than 140 papers in refereed journals and conference proceedings and has served as a Technical Program Committee Member for IEDM in 2008 and 2009. His research interests include the modeling of carrier transport in nanoscale devices and the simulation of hot-carrier and tunneling phenomena in scaled MOSFETs and nonvolatile memory cells.

**David Esseni** (SM'06) received the Ph.D. degree in electronic engineering from the University of Bologna, Bologna, Italy, in 1998.

During year 2000, he was a Visiting Scientist with Bell Labs–Lucent Technologies, Murray Hill, NJ. Since 2005, he has been an Associate Professor with the University of Udine, Udine, Italy. His research interests are mainly focused on the characterization, modeling, and reliability of MOS transistors and nonvolatile memories (NVM). In the field of NVM, he has worked on the low voltage and substrate

enhanced hot electron phenomena and on several aspects of Flash EEPROM memories, including innovative programming techniques and reliability issues related to the statistical distribution of the stress-induced leakage current. He is a coauthor of the book "Nanoscale MOS transistors: semi-classical transport and application," published by Cambridge University Press. In the framework of CMOS technologies, he has been involved in several activities concerning experimental characterization and modeling of mobility in silicon, strained silicon, and germanium transistors with both planar and innovative device architectures. More recently, his research interests have extended to beyond CMOS devices, such as graphene-based FETs and tunnel FETs, as well as to quantum transport in NEGF formalism.

Dr. Esseni has served or is serving as a member of the technical committee of the International Electron Devices Meeting (IEDM), the European Solid-State Device Research Conference (ESSDERC), and the International Reliability Physics (IRPS). He is the Chairman for the subcommittee "Modeling and Simulations" of the ESSDERC 2011. He is an Associate Editor of the IEEE TRANSACTIONS ON ELECTRON DEVICES (TED) and has been among the guest editors of two special issues of IEEE TED devoted respectively to the simulation and modeling of nanoelectronics devices and to the characterization and modeling of variability.

Luca Perniola was born in Florence, Italy, in 1978. He received the Laurea degree in nuclear engineering from Politecnico di Milano, Milano, Italy, in 2002 and the Ph.D. degree from the University of Pisa, Pisa, and the Institut National Polytechnique de Grenoble, Grenoble, France, in 2005. His Ph.D. thesis was on the modeling and electrical characterization of discrete-trap nonvolatile memory devices (i.e., nanocrystals).

Since 2005, he has been as Scientist with CEA-LETI, MINATEC Campus, Grenoble, France, and he

has been working on topics related to the nonvolatile memory (NVM) field. In particular, he focused on device architecture impact on memory performances for nitride-based NVM (i.e., SONOS finFET) and on phase-change memories with alternative to GST materials to boost memory performances.

**Gabriel Molas** was born in Paris, France, in 1979. He received the B.S. and M.S. degrees in physics engineering, with microelectronics specialization, in 2001 and the Ph.D. degree in micro- and nanoelectronics from the Polytechnics Institute of Grenoble, Grenoble, France, in 2004. His Ph.D. thesis was on few electron memories.

In 2004, he was a Research Engineer with the Laboratory of Electronics, Technology and Instrumentation of CEA (LETI), Grenoble. From 2004 to 2008, he was a Research Scientist with the Silicon Nano-

Device Laboratory, LETI/CEA, Grenoble, where he worked on the processing of innovative memory devices. Since 2008, he has been a Research Scientist and responsible of the charge trap memory activity in the Advanced Memory Technology Laboratory, LETI MINATEC/CEA. He was responsible from the LETI side of various industrial and institutional projects. He is the author or coauthor of more than 60 publications in international conferences and 20 papers in refereed journals. He is a reviewer of several international journals and a member of the IEDM memory technology subcommittee (2010–2011). His research interests concern the processing, engineering, electrical character-ization, and modeling of innovative nonvolatile memory devices (charge trap memories, TANOS, nanocrystals, high-*k*, SOI FinFlash architectures, single electron memories, etc.).

**Barbara De Salvo** received the B.S. and M.S. degrees in electronics engineering from the University of Parma, Parma, Italy, and the Ph.D. degree in microelectronics from the Polytechnics Institute of Grenoble, Grenoble, France.

From 1995 to 1996, she was with the Department of Information Technology, University of Parma. From 1996 to 1999, she was a Scientist with the Laboratory of Physics of Semiconductor Devices, CNRS/INPG, Grenoble, making research on the reliability of nonvolatile Flash memories. In 1999, she was a Research Scientist with the Laboratory of Electronics and Information Technologies of CEA (LETI), Grenoble. From 2002 to 2004, she was the Coordinator of the ADAMANT project ("Advanced memories based on discrete-traps") funded by the European Commission within the Fifth Framework Programme. She currently manages the "Advanced Memory Technology Laboratory" in LETI, covering several R&D projects funded by industrial partnerships and French/European institutions. She is the author or coauthor of more than 200 articles in international refereed journals and conferences and she has authored a monography on silicon nonvolatile memeories published by John Wiley and Sons Inc. She has supervised several Master and Ph.D. students. Her current research interests include the technological development and physical understanding of innovative memory technologies, such as chargetrap nonvolatile memories (with silicon or metal nanocrystals and new high-kdielectrics/metal gate stacks), SOI-based ultrascaled memory architectures, and new 3-D integration paths. Her research interests also cover the development of alternative technologies, such as phase-change memories, back-end metal oxide resistive memories, such as OxRAM, and conductive-bridge memories.

Dr. De Salvo has been or is part of several technical committees of international conferences (such as ESSDERC, International Memory Workshop, IEDM).

Luca Selmi was born in 1961. He received the Ph.D. degree in electronics from the University of Bologna, Bologna, Italy, in 1992.

In 2000, he became a Full Professor of electronics with the University of Udine, Udine, Italy. During 1989–1990, he was a Visiting Scientist with Hewlett Packard Microwave Technology Division, Santa Rosa, CA. He has been a member of the IEDM technical subcommittees on "modeling and simulation," "circuit and interconnect reliability," and "CMOS devices." He is currently with the

Department of Electrical, Managerial and Mechanized Engineering, University of Udine. He coauthored approximately 200 papers, including more than 30 IEDM papers. His research interests include characterization and simulation of silicon devices, with emphasis on nanoscale CMOS, Monte Carlo transport techniques, hot carrier effects in MOSFETs and nonvolatile memory cells, leakage currents and reliability of ultrathin oxides, and device optimization. These activities have been conducted in cooperation with international research centers, such as Bell Labs, Holmdel, NJ, IBM T. J. Watson Research Center, Yorktown Heights, NY, Philips Res. Labs., NXP, INPG, and LETI Grenoble.

Dr. Selmi is an Associate Editor of IEEE EDL and a TPC member of several international conferences of the electron device community.