# **Roadmap to Gigahertz Organic Transistors**

Ute Zschieschang, James W. Borchert, Michele Giorgio, Mario Caironi, Florian Letzkus, Joachim N. Burghartz, Ulrike Waizmann, Jürgen Weis, Sabine Ludwigs, and Hagen Klauk\*

Despite the large body of research conducted on organic transistors, the transit frequency of organic field-effect transistors has seen virtually no improvement for a decade and remains far below 1 GHz. One reason is that most of the research is still focused on improving the charge-carrier mobility, a parameter that has little influence on the transit frequency of short-channel transistors. By examining the fundamental equations for the transit frequency of field-effect transistors and by extrapolating recent progress on the relevant device parameters, a roadmap to gigahertz organic transistors is derived.

#### 1. Introduction

Thin-film transistors (TFTs) are field-effect transistors manufactured by the sequential deposition of the various device components (e.g., semiconductor, gate dielectric, gate electrode, and source and drain contacts) from the vapor or liquid phase onto a substrate in the form of thin layers.<sup>[1]</sup> This approach distinguishes

Dr. U. Zschieschang, J. W. Borchert, U. Waizmann, Prof. J. Weis, Dr. H. Klauk **Organic Electronics** Max Planck Institute for Solid State Research Heisenbergstraße 1, 70569 Stuttgart, Germany E-mail: H.Klauk@fkf.mpg.de J. W. Borchert, Prof. S. Ludwigs **Functional Polymers** Institute of Polymer Chemistry Universität Stuttgart Pfaffenwaldring 55, 70569 Stuttgart, Germany M. Giorgio Dipartimento di Elettronica Informazione e Bioingegneria Politecnico di Milano via Ponzio 34/5, 20133 Milano, Italy M. Giorgio, Prof. M. Caironi Center for Nano Science and Technology @PoliMi Istituto Italiano di Tecnologia (IIT) via Pascoli 70/3, 20133 Milano, Italy Dr. F. Letzkus, Prof. J. N. Burghartz Institut für Mikroelektronik Stuttgart (IMS CHIPS) Allmandring 30a, 70569 Stuttgart, Germany The ORCID identification number(s) for the author(s) of this article

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/adfm.201903812.

© 2019 The Authors. Published by WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim. This is an open access article under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made.

DOI: 10.1002/adfm.201903812

TFTs from silicon metal-oxide-semiconductor field-effect transistors (MOSFETs), which require single-crystalline wafers serving as both the substrate and the semiconductor. TFTs, in contrast, can be fabricated directly on a wide range of inexpensive, transparent, flexible, stretchable, biodegradable, and/or biocompatible substrates, such as glass, plastics, paper, metal foils, and textiles, to name just a few. A wide range of semiconductors have been employed for the fabrication of TFTs, most

notably metal chalcogenides,  $^{[2,3]}$  hydrogenated amorphous silicon (a-Si:H), $^{[4,5]}$  polycrystalline silicon, $^{[6-8]}$  low-temperature polycrystalline silicon (ITPS) produced by excimer laser annealing (ELA), $^{[9,10]}$  metal nitrides, $^{[11]}$  metal-halide perovskites, $^{[12]}$  metal oxides, $^{[13-15]}$  carbon nanotubes, $^{[16]}$  and single-crystalline silicon. $^{[17]}$

TFTs have found widespread commercial use for the implementation of the pixel circuits in active-matrix displays and large-area image detectors. For example, LTPS TFTs are currently used in 100% of all commercially manufactured active-matrix organic light-emitting diode (AMOLED) displays (600 million in 2018, mostly for smartphones) and in close to 40% of all commercially manufactured liquid-crystal displays (AMLCDs; 2 billion in total in 2018). Hydrogenated amorphous silicon TFTs are used in about 60% of all AMLCDs and in a significant share of large-area X-ray flat-panel detectors for medical, security, and nondestructive-testing applications. InGaZnO TFTs are found in about 2% of AMLCDs and in an increasing share of image detectors.

An important TFT-performance parameter is the transit frequency, which is the highest frequency at which the transistor can be operated. Depending on the panel resolution and the frame rate, the pixel-circuit TFTs need to have transit frequencies of a few megahertz to a few tens of megahertz. If the TFTs are also used for integrated row and column drivers, [18] an even higher transit frequency is required. In general, higher transit frequencies enable a wider range of applications and higher-quality products. Transit frequencies above 1 GHz have been reported for TFTs based on several different semiconductors. [19–22]

Organic TFTs, fabricated using either conjugated polymers or small-molecule semiconductors, are being developed as alternatives to the above-mentioned, mostly, inorganic TFTs. An attractive feature of organic TFTs is that both p-channel and n-channel TFTs can be fabricated at relatively low process temperatures, usually at or near room temperature.<sup>[23]</sup> However, despite more than three decades of intense research, the highest reported transit frequencies of organic TFTs are still well below 1 GHz. The aim of this Progress Report is to develop a roadmap to gigahertz organic TFTs.

# ADVANCED FUNCTIONAL

#### 2. Results and Discussion

The transit frequency of a field-effect transistor is defined as follows

$$f_{\rm T} = f\left(\frac{|i_{\rm D}|}{|i_{\rm G}|} = 1\right) = \frac{g_{\rm m}}{2\pi C_{\rm G}} \tag{1}$$

where  $i_{\rm D}$  is the small-signal drain current (which can be written as  $i_{\rm D}=g_{\rm m}\cdot \nu_{\rm GS}$ , with  $g_{\rm m}$  being the small-signal transconductance and  $\nu_{\rm GS}$  the small-signal gate—source voltage),  $i_{\rm G}$  is the small-signal gate current (which can be written as  $i_{\rm G}=j\cdot 2\pi f\cdot C_{\rm G}\cdot \nu_{\rm GS}$ , with j being the imaginary unit and f the frequency), and  $C_{\rm G}$  is the gate capacitance. By approximating the gate capacitance  $C_{\rm G}$  as the sum of the geometric gate-to-channel and gate-to-contact capacitances, by assuming that the intrinsic and parasitic capacitances have the same unit-area capacitance, and by calculating the transconductance as  $g_{\rm m}=\partial I_{\rm D}/\partial V_{\rm GS}$  either for the linear regime (where  $V_{\rm DS}< V_{\rm GS}-V_{\rm th}$ , with  $V_{\rm DS}$  being the large-signal drain—source voltage,  $V_{\rm GS}$  the large-signal gate—source voltage, and  $V_{\rm th}$  the threshold voltage) or for the saturation regime ( $V_{\rm DS}>V_{\rm GS}-V_{\rm th}$ ), Equation (1) can be written as

$$f_{\rm T} = \frac{\mu_{\rm eff} V_{\rm DS}}{2\pi L \left(L + L_{\rm ov,GS} + L_{\rm ov,GD}\right)} \left(\text{linear regime}, V_{\rm DS} < V_{\rm GS} - V_{\rm th}\right) \quad (2)$$

$$f_{\rm T} = \frac{\mu_{\rm eff} \left( V_{\rm GS} - V_{\rm th} \right)}{2\pi L \left( L + L_{\rm ov,GS} + L_{\rm ov,GD} \right)} \left( \text{saturation regime}, V_{\rm DS} > V_{\rm GS} - V_{\rm th} \right) \tag{3}$$

where  $\mu_{\rm eff}$  is the effective carrier mobility, L is the channel length,  $L_{\rm ov,GS}$  is the parasitic gate-to-source overlap, and  $L_{\rm ov,GD}$  is the parasitic gate-to-drain overlap.

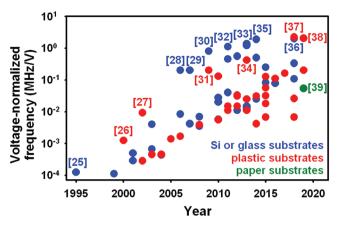

Equations (2) and (3) indicate that the transit frequency increases with increasing gate-source and drain-source voltages, which implies that all field-effect transistors can, in principle, reach a transit frequency of 1 GHz, provided dielectric breakdown and self-heating<sup>[24]</sup> upon application of sufficiently high voltages are avoided. This renders the transit frequency a somewhat meaningless parameter for benchmarking purposes. Instead of the absolute frequency, Figure 1 therefore shows how the supply-voltage-normalized transit frequency of organic TFTs has been improved over the years, from 2.5 kHz at 20 V in 1995 to 20 MHz at 10 V and 6.7 MHz at 3 V in 2018.[25,36,37] (Note that some of the results in Figure 1 were obtained not by measuring the transit frequency  $f_T$  of an individual transistor, but by calculating an equivalent frequency  $f_{\rm eq} = 1/(2 \cdot \tau_{\rm stage})$  from a ring oscillator's stage delay  $\tau_{\rm stage}$ , where the ratio  $f_{\rm eq}/f_{\rm T}$  is usually near 0.5.<sup>[40]</sup> Also note that the proportionality between  $f_T$  and  $V_{DS}$  in Equation (2) is observed only in the limit of zero contact resistance, as will be elaborated later.)

The historic development seen in Figure 1 has come through improvements in virtually every aspect of the materials and technology of organic TFTs. As a result of these combined efforts, the voltage-normalized frequency increased by about an order of magnitude every 4 years between 1995 and 2011.

Ute Zschieschang received a Diplom-Ingenieur degree in mechanical engineering from Mittweida University of Applied Sciences (FH), Germany, in 2000 and a Ph.D. degree in chemistry from the Technical University Bergakademie Freiberg, Germany, in 2006. Since 2005 she has been a senior scientist in the Organic

Electronics group at the Max Planck Institute for Solid State Research in Stuttgart, Germany.

James W. Borchert received a Bachelor of Arts degree in physics from Rutgers University in 2012 and a Master of Science in Engineering degree in materials science and engineering from the University of Pennsylvania in 2013. From 2014 to late 2015 he worked as a Staff Scientist at Innova Dynamics in San Francisco,

CA, USA. Since 2016, he has been working toward a Ph.D. degree in materials science under the advisement of Dr. Hagen Klauk at the Max Planck Institute for Solid State Research and Prof. Sabine Ludwigs at the University of Stuttgart, Germany.

Hagen Klauk received a Diplom-Ingenieur degree in electrical engineering from Chemnitz University of Technology, Germany, in 1995 and a Ph.D. degree in electrical engineering from the Pennsylvania State University, USA, in 1999. From 1999 to 2000 he was a postdoctoral researcher in the group of Prof. Thomas N. Jackson at

the Pennsylvania State University. From 2000 to 2005 he was a technical staff member at Infineon Technologies in Erlangen, Germany. Since 2005 he has been the Head of the Organic Electronics group at the Max Planck Institute for Solid State Research in Stuttgart, Germany.

But once the low-hanging fruits had been picked, the pace slowed to about a factor of 5 per decade. At this pace, it will take another 20 to 30 years for organic TFTs to reach a frequency of 1 GHz at 3 V, which is the nominal cell voltage of lithium-ion batteries and, thus, the maximum supply voltage in most of the

**Figure 1.** Historic development of the transit frequency  $f_{\rm T}$  normalized to either the gate–source voltage or the drain–source voltage (whichever is larger) of organic thin-film field-effect transistors reported in the literature. In case the data were obtained from measurements on ring oscillators, the equivalent frequency  $f_{\rm eq}=1/(2\cdot\tau_{\rm stage})$  normalized to the supply voltage is shown.

mobile or wearable electronic systems for which organic TFTs are primarily being developed.

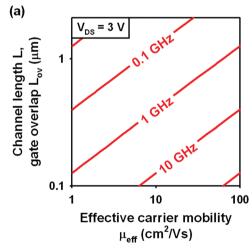

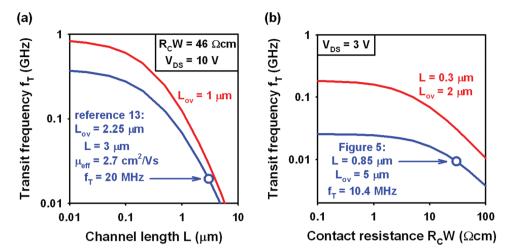

So what can be done in order to reach the goal of gigahertz organic TFTs sooner than that? In **Figure 2**, solutions to Equation (2) are plotted for a drain–source voltage of 3 V and for various effective carrier mobilities ( $\mu_{\rm eff}$ ), channel lengths (L), and gate-to-contact overlaps ( $L_{\rm ov} = L_{\rm ov,GS} = L_{\rm ov,GD}$ ). Figure 2 indicates that a transit frequency of 1 GHz at 3 V is realistic only if the channel length and the gate-to-contact overlaps are smaller than 1  $\mu$ m.

At such small channel lengths, the TFT performance is determined greatly by the contact resistance. This is evident from the following equations for the effective carrier mobility  $\mu_{\rm eff}$  and the transit frequency  $f_{\rm T}$ , derived here for the linear regime of operation<sup>[41–43]</sup>

$$\mu_{\text{eff}} = \frac{\mu_0}{1 + \frac{\mu_0}{I} R_{\text{C}} W C_{\text{diel}} \left( V_{\text{GS}} - V_{\text{th}} - \frac{V_{\text{DS}}}{2} \right)} \tag{4}$$

$$f_{\rm T} = \frac{\mu_0}{1 + \frac{\mu_0}{L} R_{\rm C} W C_{\rm diel} \left( V_{\rm GS} - V_{\rm th} - \frac{V_{\rm DS}}{2} \right)} \frac{V_{\rm DS}}{2\pi L \left( L + L_{\rm ov, GS} + L_{\rm ov, GD} \right)}$$

(5)

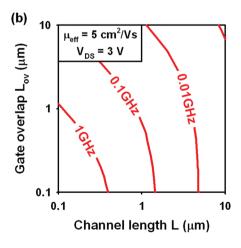

where  $R_{\rm C}$  is the contact resistance (defined here as the sum of the source resistance and the drain resistance, i.e.,  $R_{\rm C}=R_{\rm S}+R_{\rm D}$ , and assumed to be Ohmic, i.e., independent of the voltage drop across the contacts),  $\mu_0$  is the intrinsic channel mobility (i.e., the carrier mobility in the absence of any contact resistance), W is the channel width, and  $C_{\rm diel}$  is the gate-dielectric capacitance per unit area. Solutions to Equation (5) are plotted in **Figure 3**. The term  $C_{\rm diel}(V_{\rm GS}-V_{\rm th}-V_{\rm DS}/2)$  was set to  $10^{-6}$  A s cm<sup>-2</sup>, which is a typical value for the gate-induced charge-carrier density in transistors with conventional (as opposed to electrolyte-based) gate insulators.

Figure 3 shows that at the channel lengths required for gigahertz organic TFTs, the transistor performance is essentially unaffected by the intrinsic channel mobility and is instead determined almost entirely by the contact resistance, which will need to be in the range of about 1–10  $\Omega$  cm. The roadmap to gigahertz organic TFTs is therefore essentially a roadmap to a contact resistance of about 1–10  $\Omega$  cm in sub-micrometer organic TFTs.

When TFTs are fabricated in the staggered device architecture, the contact resistance is determined mainly by the height and the width of the energy barrier at the contact–semiconductor interface, by the gate-to-source and gate-to-drain overlaps, and by the thickness and the conductivity of the semiconductor layer.<sup>[44–48]</sup> Using area-selective contact doping and a very small semiconductor thickness of 7 nm, Yamamura et al.<sup>[36]</sup>

Figure 2. a) Contour plot showing the transit frequency  $(f_T)$  calculated using Equation (2) for a drain–source voltage  $(V_{DS})$  of 3 V, effective carrier mobilities  $(\mu_{eff})$  ranging from 1 to 100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and channel lengths ranging from 0.1 to 2 μm. The channel length, the gate-to-source overlap, and the gate-to-drain overlap are assumed to be identical  $(L = L_{ov} = L_{ov,GD})$ . b) Contour plot showing the transit frequency  $(f_T)$  calculated using Equation (2) for a drain–source voltage of 3 V, an effective carrier mobility of 5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and channel lengths and gate-to-contact overlaps ranging from 0.1 to 10 μm. As can be seen, a transit frequency of 1 GHz at usefully small supply voltages (3 V) will require sub-micrometer channel lengths and gate-to-contact overlaps.

Figure 3. Contour plots showing the transit frequency ( $f_T$ ) calculated using Equation (5) for a drain–source voltage ( $V_{DS}$ ) of 3 V, intrinsic channel mobilities ( $\mu_0$ ) ranging from 10 to 10 000 cm² V<sup>-1</sup> s<sup>-1</sup> and width-normalized contact resistances ( $R_CW$ ) ranging from 1  $\Omega$  cm to 1 k $\Omega$  cm. The channel length, the gate-to-source overlap, and the gate-to-drain overlap are assumed to be identical ( $L = L_{ov} = L_{ov,GS} = L_{ov,GD}$ ). Calculations were performed for a)  $L = L_{ov} = 1$   $\mu$ m and b)  $L = L_{ov} = 0.1$   $\mu$ m. The term  $C_{diel}(V_{GS} - V_{th} - V_{DS}/2)$  was set to  $10^{-6}$  A s cm<sup>-2</sup>. As can be seen, the transit frequency is essentially unaffected by the intrinsic channel mobility. In addition to sub-micrometer dimensions, gigahertz organic TFTs will require a contact resistance of  $\approx 1-10$   $\Omega$  cm.

recently achieved a contact resistance of 46  $\Omega$  cm in inverted staggered (bottom-gate, top-contact) organic TFTs, a record for organic TFTs at the time of publication, aside from the electrochemically doped polymer TFTs reported by Braga et al. [49] For TFTs with a channel length of 3  $\mu$ m and gate-to-source and gate-to-drain overlaps of 2.25  $\mu$ m, this resulted in a transit frequency of 20 MHz at 10 V, or a voltage-normalized transit frequency of 2 MHz V<sup>-1</sup>, also a record for organic TFTs at the time of publication. (Note that Yamamura et al. give the sum of the gate-to-source and gate-to-drain overlaps,  $L_{\rm ov,GS} + L_{\rm ov,GD} = 4.5~\mu$ m.)

It is difficult to predict to what extent it will be possible to reduce the contact resistance further in this device architecture. On the one hand, while Yamamura et al. showed that reducing the semiconductor thickness from two monolavers to one monolayer is detrimental to the lateral charge-carrier transport, a reduction of the semiconductor thickness to about 5 or 6 nm might nonetheless be possible by using a shorter molecule than the one employed by Yamamura et al., provided it lends itself equally well to the coating process. On the other hand, there is no guarantee that this will lead to a further reduction of the contact resistance, considering how small it already is (46  $\Omega$  cm). Also, as discussed previously, a transit frequency of 1 GHz at 10 V will likely require gate-tosource and gate-to-drain overlaps below 1 µm, and for the parameters in ref. [36], this would make the overlaps smaller than the transfer length (which, according to Figure 3c in ref. [36], is slightly greater than 1 µm), which might result in a larger contact resistance. This makes it difficult to predict how much further the contact resistance can be reduced. In Figure 4a, we therefore show solutions to Equation (5) for a contact resistance of 46  $\Omega$  cm and for gate overlaps of 2.25  $\mu$ m (as in ref. [36]) and 1  $\mu m$  (assuming that a contact resistance of 46  $\Omega$  cm can be maintained for this overlap). As can be seen, transit frequencies approaching 1 GHz at 10 V are possible under these assumptions by reducing the channel length to about 0.1 µm.

For organic TFTs fabricated in the coplanar architecture, the situation is completely different. Since the contact–semiconductor interface in coplanar TFTs is permanently shielded from

the gate field, proper management of the energy barrier at this interface, e.g., by chemical modification, is probably even more important than in staggered organic TFTs (where this interface is shielded from the gate field only in the presence of a carrier channel). In bottom-gate coplanar TFTs, an additional requirement is that the semiconductor must form a continuous layer with adequate microstructure along the raised contact edges and on the surface of the contacts.<sup>[50]</sup> Both of these issues can be addressed by functionalizing the contact surface with a monolayer of molecules that induce a favorable semiconductor morphology across the contact edges<sup>[51]</sup> and which have either a large density of electronegative substituents<sup>[52,53]</sup> or a large dipole moment<sup>[54]</sup> to tune the interface energy barrier.

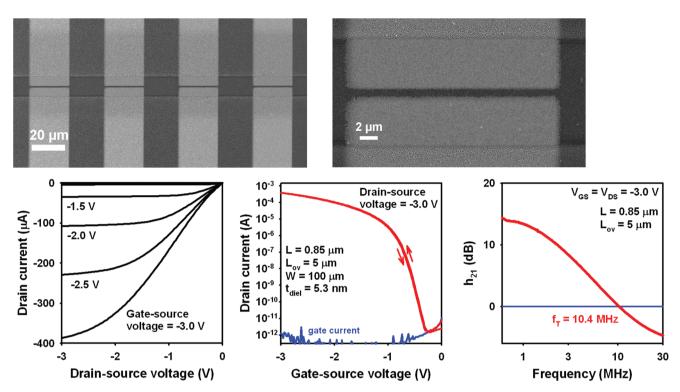

Under these provisions, the coplanar architecture may provide a number of benefits. First of all, the contact resistance in coplanar TFTs is independent of the length of the gateto-source and gate-to-drain overlaps (as long as these overlaps exist and assuming that the contacts extend sufficiently far outside of the area of the gate electrode), which means that the parasitic capacitances can be decreased (and ideally eliminated by self-alignment of the source and drain contacts with respect to the gate electrode) without negatively affecting the contact resistance. Second, the contact resistance is independent of the thickness of the semiconductor layer, which is beneficial whenever precise control of this thickness is difficult, as in the case of vacuum-deposited small-molecule semiconductors. Third, the contact resistance in coplanar TFTs depends strongly on the thickness of the gate dielectric<sup>[55]</sup> and can thus, in principle, be reduced in a direct and systematic manner. For coplanar organic TFTs with a gate-dielectric thickness of 5.3 nm, a contact resistance of 30  $\Omega$  cm was recently reported, [56] resulting in an equivalent frequency of 3.5 MHz at 1.6 V (2.2 MHz V<sup>-1</sup>) in ring oscillators based on TFTs with a channel length of 1 μm and gate overlaps of 2 μm, [37] and a transit frequency of 10.4 MHz at 3 V (3.5 MHz V<sup>-1</sup>) obtained from S-parameter measurements on TFTs with a channel length of 0.85 µm and gate overlaps of 5 µm (see Figure 5). These TFTs were fabricated by stencil lithography,[57] which has a resolution limit of

Figure 4. a) Transit frequency ( $f_T$ ) calculated using Equation (5) and plotted as a function of the channel length (L) for the parameters of the inverted staggered TFTs in ref. [36] ( $R_CW = 46 \Omega$  cm,  $C_{\rm diel} = 60$  nF cm<sup>-2</sup>,  $V_{\rm GS} = V_{\rm DS} = 10$  V,  $V_{\rm th} = 2$  V). The blue curve was calculated for  $L_{\rm ov} = 2.25$  μm, as reported in ref. [36], and the red curve for  $L_{\rm ov} = 1$  μm. The intrinsic channel mobility ( $\mu_0$ ) was set to 3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, as this is the value for which Equation (4) yields an effective mobility of 2.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for L = 3 μm, as reported in ref. [36]. (For TFTs fabricated on silicon substrates, ref. [36] gives an intrinsic channel mobility greater than 10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, but the TFTs considered here were fabricated on glass.) As can be seen, a transit frequency close to 1 GHz at 10 V is possible in staggered organic TFTs by reducing the channel length to about 0.1 μm and the gate-to-contact overlaps to about 1 μm. b) Transit frequency calculated using Equation (5) and plotted as a function of the width-normalized contact resistance for the parameters of the inverted coplanar TFTs fabricated by stencil lithography shown in Figure 5 ( $\mu_0 = 5$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>,  $C_{\rm diel} = 700$  nF cm<sup>-2</sup>,  $V_{\rm CS} = V_{\rm DS} = 3$  V,  $V_{\rm th} = 1$  V). The blue curve was calculated for L = 0.85 μm and  $L_{\rm ov} = 5$  μm, as in Figure 5, and the red curve for L = 0.3 μm and  $L_{\rm ov} = 2$  μm, which is approximately the resolution limit of stencil lithography. As can be seen, the maximum transit frequency achievable using stencil lithography is about 100 MHz at 3 V.

$\approx$ 0.3 μm for the channel length<sup>[58]</sup> and  $\approx$ 2 μm for the gate-to-source and gate-to-drain overlaps.<sup>[59]</sup> Figure 4b shows the transit frequency at a drain–source voltage of 3 V calculated using Equation (5) and plotted as a function of the width-normalized contact resistance for the dimensions of the TFT in Figure 5 (L=0.85 μm,  $L_{\rm ov}=5$  μm) and for the minimum dimensions achievable by stencil lithography<sup>[58,59]</sup> (L=0.3 μm,  $L_{\rm ov}=2$  μm). Figure 4b indicates that the highest transit frequency that can realistically be expected for organic TFTs fabricated by stencil lithography is  $\approx$ 30 MHz at 3 V for a contact resistance of 30  $\Omega$  cm and  $\approx$ 100 MHz at 3 V in the event that the contact resistance can be reduced to about 5  $\Omega$  cm, e.g., by functionalizing the contact surfaces with better-performing molecules<sup>[52–54]</sup> or by reducing the gate-dielectric thickness.<sup>[55]</sup>

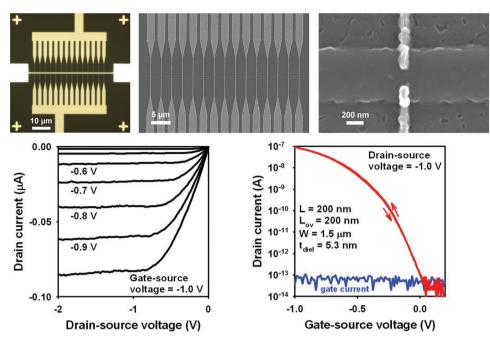

Figure 4 shows that transit frequencies beyond 30 MHz V<sup>-1</sup> will likely require channel lengths and gate-to-contact overlaps well below 1 µm. As a higher-resolution alternative to stencil lithography, we have therefore used electron-beam lithography and fabricated organic TFTs with channel lengths and gate-tocontact overlaps of 200 nm, as shown in Figure 6. Unfortunately, the contact resistance of these TFTs is about 800  $\Omega$  cm, i.e., more than an order of magnitude larger than the contact resistance of the stencil-patterned TFTs (30  $\Omega$  cm). This could be due to contamination of the contact surfaces during the liftoff process or a less favorable microstructure of the organic semiconductor across the edges of the contacts when these are patterned by electron-beam lithography, rather than stencil lithography. As a result of the larger contact resistance, the width-normalized transconductance is more than an order of magnitude smaller than that of the stencil-patterned TFTs in ref. [37] and Figure 5, and the transit frequency estimated using Equation (5) is about 9 MHz at 1 V. In other words, the benefit

of the smaller critical dimensions is partially lost due to the larger contact resistance.

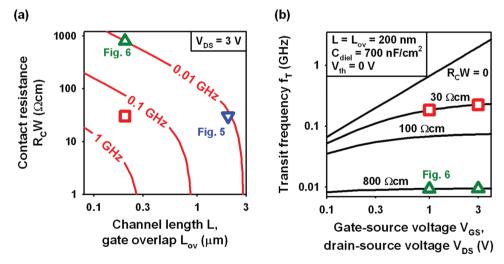

In order to put the results from Figures 4b and 6 into perspective, the transit frequency calculated using Equation (5) for a drain-source voltage of 3 V is plotted in Figure 7a as a function of the critical dimensions and the width-normalized contact resistance. The channel length, the gate-to-source overlap, and the gate-to-drain overlap are assumed to be identical ( $L = L_{ov} = L_{ov,GS} = L_{ov,GD}$ ). Three scenarios are highlighted in Figure 7a. The blue symbol represents the parameters of the TFTs fabricated by stencil lithography shown in Figure 5 (critical dimensions on the order of 2 µm and a contact resistance of 30  $\Omega$  cm), the green symbol represents the parameters of the TFT fabricated by electron-beam lithography shown in Figure 6 (critical dimensions of 200 nm and a contact resistance of 800  $\Omega$  cm), and the red symbol represents a hypothetical TFT that combines critical dimensions of 200 nm with a contact resistance of 30  $\Omega$  cm. Figure 7b illustrates the dependence of the transit frequency on the drain-source voltage for various values of the contact resistance.

According to Figure 7, a TFT with the same contact resistance as the TFTs fabricated by stencil lithography shown in Figure 5 ( $R_{\rm C}W=30~\Omega$  cm) and with the same critical dimensions as the TFT fabricated by electron-beam lithography shown in Figure 6 ( $L=L_{\rm ov,GS}=L_{\rm ov,GD}=200~{\rm nm}$ ) would have a transit frequency of 190 MHz at 1 V and 230 MHz at 3 V (red symbols in Figure 7). A transit frequency of 1 GHz at these voltages will require a further reduction of the contact resistance below about 10  $\Omega$  cm and a further reduction of the channel length and the gate-to-contact overlaps below about 200 nm.

The fundamental scaling laws developed for silicon MOS-FETs in the 1970s<sup>[60,61]</sup> dictate that the ratio between the channel

FUNCTIONAL

www.advancedsciencenews.com www.afm-journal.de

Figure 5. Microscopy images and static and dynamic characteristics of an inverted coplanar TFT with a channel length of 0.85 μm and gate-to-source and gate-to-drain overlaps of 5 μm fabricated on a flexible polyethylene naphthalate (PEN) substrate by stencil lithography using the vacuum-deposited small-molecule semiconductor 2,9-diphenyl-dinaphtho[2,3-b:2′,3′-f]thieno[3,2-b]thiophene (DPh-DNTT) and a gate dielectric based on oxygen-plasmagrown aluminum oxide and an alkylphosphonic acid self-assembled monolayer with a total thickness of 5.3 nm and a capacitance of 700 nF cm<sup>-2</sup>.[<sup>37,56</sup>] The TFT has a contact resistance of 30  $\Omega$  cm (extracted from transmission-line measurements performed on the same substrate), a width-normalized transconductance of 3 S m<sup>-1</sup>, a subthreshold slope of 70 mV decade<sup>-1</sup>, an on/off current ratio of 10<sup>8</sup>, and a transit frequency of 10.4 MHz determined from S-parameter measurements<sup>[33]</sup> performed at gate–source and drain–source voltages of –3 V.

length and the gate-dielectric thickness of a field-effect transistor should be no smaller than about 50, in order to ensure that the electric potential in the semiconductor is controlled by the transverse electric field, rather than the lateral electric field. This implies a maximum gate-dielectric thickness of 20 nm for a channel length of 1 um and a thickness of 2 nm for a channel length of 100 nm. These are the values derived under the assumption that the permittivities of the semiconductor and the gate dielectric are similar. The use of a gate dielectric with a larger permittivity will alleviate the dielectric-thickness requirement. For example, silicon MOSFETs, where high-permittivity gate oxides have been in use since 2007, are currently (10 and 7 nm nodes) manufactured with a channel length of 15-20 nm, and a gate dielectric consisting of SiO2 with a thickness of 0.5-0.8 nm (grown by thermal oxidation) and HfO2 with a thickness of 1–1.5 nm (deposited by atomic layer deposition).<sup>[62]</sup> The concept of a double-layer gate dielectric that combines a high-permittivity dielectric (with a thickness just sufficient to suppress quantum-mechanical tunneling) and a thin layer of a low-permittivity dielectric (to shield the semiconductor from the undesirable polarization effects of the high-permittivity dielectric<sup>[63–65]</sup>) is, in principle, also applicable to organic TFTs, although the choice of the materials, especially for the low-permittivity dielectric interfacing the organic semiconductor, will likely be different.<sup>[66-71]</sup> Nevertheless, the total physical thickness of such a double-layer gate dielectric will need to be no

greater than about 5 nm for a channel length of 100 nm. The main concern with such thin gate dielectrics is the magnitude of the gate current. However, given the necessarily small size of high-frequency TFTs, this is unlikely to be a serious issue. For example, for a channel length and gate-to-contact overlaps of 100 nm, and a channel width of 3 µm, the effective gate area is only 10<sup>-8</sup> cm<sup>2</sup>, so even if the gate-current density was 1 A cm<sup>-2</sup>, the absolute gate current would not exceed 10<sup>-8</sup> A. Gate dielectrics with a thickness of about 5 nm and a gate-leakage current density below 10<sup>-5</sup> A cm<sup>-2</sup> have already been used in the fabrication of organic TFTs,[72] and from these values, a gate current of less than  $10^{-13}$  A is projected for an effective gate area of 10<sup>-8</sup> cm<sup>2</sup> (see also Figure 6). As long as the gate dielectric has a sufficiently small defect density and its thickness is above the value at which leakage currents due to quantum-mechanical tunneling become an issue, the gate dielectric is not expected to pose insurmountable challenges.

#### 3. Conclusions

1) Gigahertz organic TFTs will require channel lengths and gate-to-contact overlaps well below 1  $\mu m$ . At these channel lengths, the transit frequency is essentially unaffected by the charge-carrier mobility and is instead determined mainly by the contact resistance, which will need to be smaller than  $\approx 10~\Omega$  cm.

Figure 6. Microscopy images and measured current–voltage characteristics of an inverted coplanar TFT with a channel length, and gate-to-source and gate-to-drain overlaps of 200 nm fabricated on a glass substrate by electron-beam lithography using the vacuum-deposited small-molecule semiconductor dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) and a gate dielectric based on oxygen-plasma-grown aluminum oxide and an alkylphosphonic acid self-assembled monolayer with a total thickness of 5.3 nm and a capacitance of 700 nF cm<sup>-2</sup>. The TFT has a contact resistance of about 800  $\Omega$  cm (estimated from the linear region of the output curve at  $V_{GS} = -1$  V), a width-normalized transconductance of 0.2 S m<sup>-1</sup>, an intrinsic gain of about 300, a subthreshold slope of 72 mV decade<sup>-1</sup>, and an on/off current ratio of 3  $\times$  10<sup>6</sup>.

Figure 7. a) Contour plot showing the transit frequency ( $f_T$ ) calculated using Equation (5) for an intrinsic channel mobility ( $\mu_0$ ) of 5 cm² V<sup>-1</sup> s<sup>-1</sup> and a drain–source voltage ( $V_{DS}$ ) of 3 V. The channel length, the gate-to-source overlap, and the gate-to-drain overlap are assumed to be identical ( $L = L_{ov} = L_{ov,GS} = L_{ov,GD}$ ). The term  $C_{diel}(V_{GS} - V_{th} - V_{DS}/2)$  was set to 10<sup>-6</sup> A s cm<sup>-2</sup>. The blue symbol represents the TFT fabricated by stencil lithography shown in Figure 5. (The true dimensions of the TFT in Figure 5 are  $L = 0.85 \, \mu m$ ,  $L_{ov} = 5 \, \mu m$ ; for the purpose of the graph shown here, this has been approximated as  $L = L_{ov} = 2 \, \mu m$ . The width-normalized contact resistance is 30 Ω cm.) The green symbol represents the TFT fabricated by electron-beam lithography shown in Figure 6 ( $L = L_{ov} = 200 \, nm$ ,  $R_CW = 800 \, \Omega$  cm; calculated here for  $V_{GS} = V_{DS} = 3 \, V$ , instead of 1 V), and the red symbol represents a hypothetical TFT combining  $L = L_{ov} = 200 \, nm$  and  $R_CW = 30 \, \Omega$  cm. b) Transit frequency calculated using Equation (5) and plotted as a function of the applied gate–source and drain–source voltages, assuming  $V_{GS} = V_{DS}$  and  $V_{th} = 0 \, V$ , so that the TFT is always in the linear regime, which is one of the assumptions underlying Equation (5). If the contact resistance is dominated by the contact resistance, the weaker is the dependence of the transit frequency on the drain–source voltage. For the TFT in Figure 6, transit frequencies of 9.3 MHz at 1 V and 9.4 MHz at 3 V are calculated (green symbols). For the hypothetical TFT with  $L = L_{ov} = 200 \, nm$  and  $R_CW = 30 \, \Omega$  cm, the calculated transit frequencies are 190 MHz at 1 V and 230 MHz at 3 V (red symbols).

www.advancedsciencenews.com www.afm-journal.de

- 2) In the event that the transit frequency is limited not by the ratio between the transconductance and the gate capacitance, but by the saturation of the charge-carrier velocity in the semiconductor  $(f_T = v_{sat}/(2\pi L))$ , [73] the channel length may have to be even smaller than indicated above. For example, if the carrier velocity were to saturate at  $10^5$  cm s<sup>-1</sup>, a transit frequency of 1 GHz might require a channel length below 100 nm.

- 3) Regarding the question of how to fabricate nanoscale organic TFTs on flexible, large-area substrates with sufficient yield and uniformity in a scalable and cost-effective manner, a number of techniques have been developed over the past few years; one of these is nanoimprint lithography,<sup>[74–79]</sup> which has been used to demonstrate functional organic TFTs with channel lengths as small as 70 nm and which can be combined with self-alignment techniques to define nanoscale gate-to-contact overlaps.<sup>[80,81]</sup>

# Acknowledgements

The authors would like to thank Kazuo Takimiya (RIKEN Center for Emergent Matter Science, Wako, Saitama, Japan) as well as Koichi Ikeda, Yuichi Sadamitsu, and Satoru Inoue (Nippon Kayaku, Tokyo, Japan) for providing world-class organic semiconductors. This work was partially funded by the German Research Foundation (DFG) under the grants KL 2223/6-1 and KL 2223/6-2 (SPP FFlexCom), and KL 2223/7-1 and INST 35/1429-1 (SFB 1249).

# **Conflict of Interest**

The authors declare no conflict of interest.

### **Keywords**

contact resistance, nanoscale transistors, organic thin-film transistors

Received: May 13, 2019 Revised: September 2, 2019 Published online:

- [1] S. D. Brotherton, Introduction to Thin Film Transistors: Physics and Technology of TFTs, Springer, Dordrecht 2013.

- [2] P. K. Weimer, Proc. IRE 1962, 50, 1462.

- [3] T. P. Brody, F. C. Luo, Z. P. Szepesi, D. H. Davies, IEEE Trans. Electron Devices 1975, 22, 739.

- [4] P. G. LeComber, W. E. Spear, A. Ghaith, Electron. Lett. 1979, 15, 179.

- [5] C.-L. Lin, P.-C. Lai, P.-T. Lee, B.-S. Chen, J.-H. Chang, Y.-S. Lin, IEEE Trans. Electron Devices 2019, 66, 1789.

- [6] S. W. Depp, A. Juliana, B. G. Huth, in Int. Electron Device Meeting (IEDM) Technical Digest, IEEE, New York, NY 1980, p. 703.

- [7] Y. Oana, H. Kotake, N. Mukai, K. Ide, Jpn. J. Appl. Phys. 1983, 22-1, 493.

- [8] M. Matsui, J.-I. Owada, Y. Shiraki, E. Maruyama, H. Kawakami, Jpn. J. Appl. Phys. 1983, 22-1, 497.

- [9] T. Sameshima, S. Usui, M. Sekiya, IEEE Electron Device Lett. 1986, 7, 276.

- [10] J. Lee, T. T. Nguyen, J. Bae, G. Jo, Y. Lee, S. Yang, H. Chu, J. Kwag, J. Soc. Inf. Disp. 2018, 26, 200.

- [11] S. Kobayashi, S. Nonomura, K. Abe, K. Ushikoshi, S. Nitta, J. Non-Cryst. Solids 1998, 227–230, 1245.

- [12] C. R. Kagan, D. B. Mitzi, C. D. Dimitrakopoulos, Science 1999, 286, 945

- [13] Y. Ohya, T. Niwa, T. Ban, Y. Takahashi, Jpn. J. Appl. Phys. 2001, 40, 297.

- [14] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, H. Hosono, *Nature* 2004, 432, 488.

- [15] N. Münzenrieder, G. Cantarella, L. Petti, ECS Trans. 2019, 90. 55.

- [16] E. S. Snow, J. P. Novak, P. M. Campbell, D. Park, Appl. Phys. Lett. 2003, 82, 2145.

- [17] T. Shimoda, Y. Matsuki, M. Furusawa, T. Aoki, I. Yudasaka, H. Tanaka, H. Iwasawa, D. Wang, M. Miyasaka, Y. Takeuchi, *Nature* 2006, 440, 783.

- [18] Y. Kubota, T. Matsumoto, H. Tsuji, N. Suzuki, S. Imai, H. Kobayashi, IEEE Trans. Electron Devices 2012, 59, 385.

- [19] S. D. Brotherton, C. Glasse, C. Glaister, P. Green, F. Rohlfing, J. R. Ayres, Appl. Phys. Lett. 2004, 84, 293.

- [20] Y.-J. E. Chen, Y.-J. Lee, Y.-H. Yu, IEEE Trans. Microwave Theory Tech. 2010, 58, 3444.

- [21] B. Bayraktaroglu, K. Leedy, R. Neidhard, IEEE Electron Device Lett. 2009, 30, 946.

- [22] D. Zhong, Z. Zhang, L. Ding, J. Han, M. Xiao, J. Si, L. Xu, C. Qiu, L.-M. Peng, *Nat. Electron.* 2018, 1, 40.

- [23] S. Abdinia, T.-H. Ke, M. Ameys, J. Li, S. Steudel, J. L. Vandersteen, B. Cobb, F. Torricelli, A. van Roermund, E. Cantatore, J. Disp. Technol. 2015, 11, 564.

- [24] B. Kheradmand-Boroujeni, M. P. Klinger, A. Fischer, H. Kleemann, K. Leo, F. Ellinger, Sci. Rep. 2018, 8, 7643.

- [25] A. R. Brown, A. Pomp, C. M. Hart, D. M. de Leeuw, Science 1995, 270, 972.

- [26] C. D. Sheraw, J. A. Nichols, D. J. Gundlach, J. R. Huang, C. C. Kuo, H. Klauk, T. N. Jackson, in 2002 IEEE Int. Electron Device Meeting (IEDM) Technical Digest, IEEE, Piscataway, NJ 2002, p. 619.

- [27] W. Fix, A. Ullmann, J. Ficker, W. Clemens, Appl. Phys. Lett. 2002, 81, 1735

- [28] V. Wagner, P. Wöbkenberg, A. Hoppe, J. Seekamp, Appl. Phys. Lett. 2006, 89, 243515.

- [29] Y.-Y. Noh, N. Zhao, M. Caironi, H. Sirringhaus, Nat. Nanotechnol. 2007, 2, 784.

- [30] M. Kitamura, Y. Arakawa, Appl. Phys. Lett. 2009, 95, 023503.

- [31] a) P. Heremans, J. Genoe, S. Steudel, K. Myny, S. Smout, P. Vicca, C. Grillberger, O. R. Hild, F. Furthner, B. van der Putten, A. K. Tripathi, G. H. Gelinck, in 2009 IEEE Int. Electron Device Meeting (IEDM) Technical Digest, IEEE, Piscataway, NJ 2009, p. 371; b) K. Myny, S. Steudel, S. Smout, P. Vicca, F. Furthner, B. van der Putten, A. K. Tripathi, G. H. Gelinck, J. Genoe, W. Dehaene, P. Heremans, Org. Electron. 2010, 11, 1176.

- [32] M. Kitamura, Y. Arakawa, Jpn. J. Appl. Phys. 2011, 50, 01BC01.

- [33] a) T. Zaki, R. Rödel, F. Letzkus, H. Richter, U. Zschieschang, H. Klauk, J. N. Burghartz, *IEEE Electron Device Lett.* 2013, 34, 520; b) T. Zaki, R. Rödel, F. Letzkus, H. Richter, U. Zschieschang, H. Klauk, J. N. Burghartz, *Org. Electron.* 2013, 14, 1318.

- [34] U. Zschieschang, R. Hofmockel, R. Rödel, U. Kraft, M. J. Kang, K. Takimiya, T. Zaki, F. Letzkus, J. Butschke, H. Richter, J. N. Burghartz, H. Klauk, Org. Electron. 2013, 14, 1516.

- [35] K. Nakayama, M. Uno, T. Uemura, N. Namba, Y. Kanaoka, T. Kato, M. Katayama, C. Mitsui, T. Okamoto, J. Takeya, Adv. Mater. Interfaces 2014, 1, 1300124.

- [36] A. Yamamura, S. Watanabe, M. Uno, M. Mitani, C. Mitsui, J. Tsurumi, N. Isahaya, Y. Kanaoka, T. Okamoto, J. Takeya, Sci. Adv. 2018, 4, eaao5758.

- [37] J. W. Borchert, U. Zschieschang, F. Letzkus, M. Giorgio, M. Caironi, J. N. Burghartz, S Ludwigs, H. Klauk, in 2018 IEEE Int'l. Electron Device Meeting (IEDM) Technical Digest, IEEE, Piscataway, NJ 2018, p. 883

- [38] A. Perinot, M. Caironi, Adv. Sci. 2019, 6, 1801566.

www.advancedsciencenews.com www.afm-journal.de

\_\_\_\_ MATERIALS

- [39] U. Kraft, T. Zaki, F. Letzkus, J. N. Burghartz, E. Weber, B. Murmann, H. Klauk, Adv. Electron. Mater. 2019, 5, 1800453.

- [40] J.-O. Plouchart, J. Kim, N. Zamdmer, M. Sherony, Y. Tan, M. Yoon, M. Talbi, A. Ray, L. Wagner, in 2003 European Solid-State Circuits Conf. (ESSCIRC) Technical Digest (Eds. J. Franca, R. Koch), IEEE, Piscataway, NJ 2003, p. 357.

- [41] M. Marinkovic, D. Belaineh, V. Wagner, D. Knipp, Adv. Mater. 2012, 24, 4005.

- [42] A. Risteska, K. Myny, S. Steudel, M. Nakamura, D. Knipp, Org. Electron. 2014, 15, 461.

- [43] H. Klauk, Adv. Electron. Mater. 2018, 4, 1700474.

- [44] T. J. Richards, H. Sirringhaus, J. Appl. Phys. 2007, 102, 094510.

- [45] F. Ante, D. Kälblein, U. Zschieschang, T. W. Canzler, A. Werner, K. Takimiya, M. Ikeda, T. Sekitani, T. Someya, H. Klauk, Small 2011, 7, 1186.

- [46] T. Minari, P. Darmawan, C. Liu, Y. Li, Y. Xu, K. Tsukagoshi, Appl. Phys. Lett. 2012, 100, 093303.

- [47] B. Lüssem, C.-M. Keum, D. Kasemann, B. Naab, Z. Bao, K. Leo, Chem. Rev. 2016, 116, 13714.

- [48] A. Fischer, H. Zündorf, F. Kaschura, J. Widmer, K. Leo, U. Kraft, H. Klauk, Phys. Rev. Appl. 2017, 8, 054012.

- [49] D. Braga, M. Ha, W. Xie, C. D. Frisbie, Appl. Phys. Lett. 2010, 97, 193311.

- [50] D. J. Gundlach, L. Zhou, J. A. Nichols, T. N. Jackson, P. V. Necliudov, M. S. Shur, J. Appl. Phys. 2006, 100, 024509.

- [51] K. Asadi, Y. Wu, F. Gholamrezaie, P. Rudolf, P. W. M. Blom, Adv. Mater. 2009, 21, 4109.

- [52] M. M. Payne, S. R. Parkin, J. E. Anthony, C.-C. Kuo, T. N. Jackson, J. Am. Chem. Soc. 2005, 127, 4986.

- [53] S. Nicht, H. Kleemann, A. Fischer, K. Leo, B. Lüssem, Org. Electron. 2014, 15, 654.

- [54] A. Petritz, M. Krammer, E. Sauter, M. Gärtner, G. Nascimbeni, B. Schrode, A. Fian, H. Gold, A. Cojocaru, E. Karner-Petritz, R. Resel, A. Terfort, E. Zojer, M. Zharnikov, K. Zojer, B. Stadlober, Adv. Funct. Mater. 2018, 28, 1804462.

- [55] K. Zojer, E. Zojer, A. F. Fernandez, M. Gruber, Phys. Rev. Appl. 2015, 4, 044002.

- [56] J. W. Borchert, B. Peng, F. Letzkus, J. N. Burghartz, P. K. L. Chan, K. Zojer, S. Ludwigs, H. Klauk, Nat. Commun. 2019, 10, 1110

- [57] T. Zaki, F. Ante, U. Zschieschang, J. Butschke, F. Letzkus, H. Richter, H. Klauk, J. N. Burghartz, IEEE J. Solid-State Circuits 2012, 47, 292.

- [58] U. Zschieschang, J. W. Borchert, M. Geiger, F. Letzkus, J. N. Burghartz, H. Klauk, Org. Electron. 2018, 61, 65.

- [59] U. Zschieschang, F. Letzkus, J. N. Burghartz, H. Klauk, IEEE Trans. Nanotechnol. 2017, 16, 837.

- [60] R. H. Dennard, F. H. Gaensslen, H.-N. Yu, V. L. Rideout, E. Bassous, A. R. LeBlanc, IEEE J. Solid-State Circuits 1974, 9, 256.

- [61] G. Baccarani, M. R. Wordeman, R. H. Dennard, IEEE Trans. Electron Devices 1984, 31, 452.

- [62] J. Robertson, R. M. Wallace, Mater. Sci. Eng., R 2015, 88, 1.

- [63] M. V. Fischetti, D. A. Neumayer, E. A. Cartier, J. Appl. Phys. 2001, 90, 4587.

- [64] J. Veres, S. D. Ogier, S. W. Leeming, D. C. Cupertino, S. M. Khaffaf, Adv. Funct. Mater. 2003, 13, 199.

- [65] A. F. Stassen, R. W. I. de Boer, N. N. Iosad, A. F. Morpurgo, Appl. Phys. Lett. 2004, 85, 3899.

- [66] O. Acton, G. Ting, H. Ma, J. W. Ka, H. L. Yip, N. M. Tucker, A. K. Y. Jen, Adv. Mater. 2008, 20, 3697.

- [67] C. H. Lee, T. Schiros, E. J. G. Santos, B. Kim, K. G. Yager, S. J. Kang, S. Lee, J. Yu, K. Watanabe, T. Taniguchi, J. Hone, E. Kaxiras, C. Nuckolls, P. Kim, Adv. Mater. 2014, 26, 2812.

- [68] X. Jia, C. Fuentes-Hernandez, C. Y. Wang, Y. Park, B. Kippelen, Sci. Adv. 2018. 4, eaao1705.

- [69] T. Yokota, T. Kajitani, R. Shidachi, T. Tokuhara, M. Kaltenbrunner, Y. Shoji, F. Ishiwari, T. Sekitani, T. Fukushima, T. Someya, *Nat. Nanotechnol.* 2018, 13, 139.

- [70] U. Zschieschang, V. P. Bader, H. Klauk, Org. Electron. 2017, 49, 179.

- [71] R. Acharya, B. Peng, P. K. L. Chan, G. Schmitz, H. Klauk, ACS Appl. Mater. Interfaces 2019, 11, 27104.

- [72] U. Zschieschang, H. Klauk, Org. Electron. 2015, 25, 340.

- [73] K. K. H. Smithe, C. D. English, S. V. Suryavanshi, E. Pop, *Nano Lett.* 2018, 18, 4516.

- [74] M. D. Austin, S. Y. Chou, Appl. Phys. Lett. 2002, 81, 4431.

- [75] U. Haas, H. Gold, A. Haase, G. Jakopic, B. Stadlober, Appl. Phys. Lett. 2007, 91, 043511.

- [76] P. F. Moonen, B. Vratzov, W. T. T. Smaal, B. K. C. Kjellander, G. H. Gelinck, E. R. Meinders, J. Huskens, Org. Electron. 2012, 13, 3004.

- [77] J. John, Y. Y. Tang, J. P. Rothstein, J. J. Watkins, K. R. Carter, Nanotechnology 2013, 24, 505307.

- [78] M. Leitgeb, D. Nees, S. Ruttloff, U. Palfinger, J. Götz, R. Liska, M. R. Belegratis, B. Stadlober, ACS Nano 2016, 10, 4926.

- [79] S. V. Sreenivasan, Microsyst. Nanoeng. 2017, 3, 17075.

- [80] H. Gold, A. Haase, A. Fian, C. Prietl, B. Striedinger, F. Zanella, N. Marjanovic, R. Ferrini, J. Ring, K. D. Lee, R. Jiawook, A. Drost, M. König, R. Müller, K. Myny, J. Genoe, U. Kleb, H. Hirshy, R. Pretot, J. Kraxner, R. Schmied, B. Stadlober, Org. Electron. 2015, 22, 140.

- [81] S. G. Higgins, B. V. O. Muir, G. Dell'Erba, A. Perinot, M. Caironi, A. J. Campbell, Appl. Phys. Lett. 2016, 108, 023302.