#### ACCEPTED MANUSCRIPT • OPEN ACCESS

# Ultra-scaled MoS<sub>2</sub> transistors and circuits fabricated without nanolithography

To cite this article before publication: Kishan Ashokbhai Patel et al 2019 2D Mater. in press https://doi.org/10.1088/2053-1583/ab4ef0

#### Manuscript version: Accepted Manuscript

Accepted Manuscript is "the version of the article accepted for publication including all changes made as a result of the peer review process, and which may also include the addition to the article by IOP Publishing of a header, an article ID, a cover sheet and/or an 'Accepted Manuscript' watermark, but excluding any other editing, typesetting or other changes made by IOP Publishing and/or its licensors"

This Accepted Manuscript is © 2019 IOP Publishing Ltd.

As the Version of Record of this article is going to be / has been published on a gold open access basis under a CC BY 3.0 licence, this Accepted Manuscript is available for reuse under a CC BY 3.0 licence immediately.

Everyone is permitted to use all or part of the original content in this article, provided that they adhere to all the terms of the licence <u>https://creativecommons.org/licences/by/3.0</u>

Although reasonable endeavours have been taken to obtain all necessary permissions from third parties to include their copyrighted content within this article, their full citation and copyright line may not be present in this Accepted Manuscript version. Before using any content from this article, please refer to the Version of Record on IOPscience once published for full citation and copyright details, as permissions may be required. All third party content is fully copyright protected and is not published on a gold open access basis under a CC BY licence, unless that is specifically stated in the figure caption in the Version of Record.

View the article online for updates and enhancements.

### Ultra-scaled $MoS_2$ transistors and circuits fabricated without nanolithography

## Kishan Ashokbhai Patel,<sup>1</sup> Ryan W. Grady,<sup>2</sup> Kirby K. H. Smithe,<sup>2</sup> Eric Pop,<sup>2</sup> and Roman Sordan<sup>1</sup>

<sup>1</sup> L-NESS, Department of Physics, Politecnico di Milano, Via Anzani 42, 22100 Como, Italy

$^2$  Department of Electrical Engineering, Stanford University, Stanford, CA 94305, USA

E-mail: roman.sordan@polimi.it

September 2019

#### Abstract.

The future scaling of semiconductor devices can be continued only by the development of novel nanofabrication techniques and atomically thin transistor channels. Here we demonstrate ultra-scaled MoS<sub>2</sub> field-effect transistors (FETs) realized by shadow evaporation method which does not require nanofabrication. The method enables large-scale fabrication of MoS<sub>2</sub> FETs with fully gated 10-nm long channels. The realized ultra-scaled MoS<sub>2</sub> FETs exhibit very small hysteresis of current-voltage characteristics, record high drain currents of ~ 560 A/m, very good drain current saturation for such ultra-short devices, subthreshold swing ~ 120 mV/dec, and drain current on/off ratio ~ 10<sup>6</sup> in air ambient. The fabricated ultra-scaled MoS<sub>2</sub> FETs are also used to realize logic gates in n-type depletion-load technology. The inverters exhibit a voltage gain of ~ 50 at a power supply voltage of only 1.5 V and are capable of in/out signal matching.

Keywords: MoS<sub>2</sub>, field-effect transistors, short-channel effects, logic gates, transistor scaling

Ultra-scaled MoS<sub>2</sub> transistors and circuits fabricated without nanolithography

2

#### 1. Introduction

Scaling of Si field-effect transistors (FETs) in integrated circuits is rapidly approaching physical limits [1–3]. The negative impact of the short-channel effects [4] on the performance of aggressively scaled Si FETs (with channel lengths ~ 20 nm) is currently mitigated by the use of very thin (< 10 nm) Si channels, typically etched in the shape of fins [5]. Further downscaling of FETs would require even thinner channels, imposing a demand for atomically thin homogeneous semiconductor channels [6–8]. Two-dimensional semiconductor materials (e.g., monolayer MoS<sub>2</sub>) are good candidates for such channels, because they are inherently atomically thin, have a uniform thickness, and are free from dangling bonds. Their application in the ultra-scaled FETs is limited mainly by the fabrication challenges because both the channel length ( $L_{ch}$ ) and gate length (L) of such FETs should be at the 10-nm scale. Ideally, the entire channel should be gated ( $L_{ch} = L$ ) to eliminate the ungated (access) parts of the channel.

After the first demonstration of the exfoliated monolayer  $MoS_2$  FETs [9], there have been several attempts to integrate atomically thin  $MoS_2$  channels in ultra-scaled FETs. Monolayer  $MoS_2$  grown by chemical vapor deposition (CVD) have been used in FETs with  $L \sim 10$  nm exhibiting drain currents  $I_{\rm D} \sim 400$  A/m (normalized by the channel width W), but with  $L_{\rm ch} \sim 50$  nm [10]. Even shorter gate lengths ( $L \sim 1$  nm) have been demonstrated in exfoliated multilayer  $MoS_2$  FETs with carbon nanotube gates, albeit with  $L_{\rm ch} \sim 500$  nm [11]. The technological challenge of realizing ultra-scaled FETs with  $L_{\rm ch} \sim L$  could be overcome by fabricating FETs with self-aligned contacts in which the gate overlaps the source/drain contacts and covers the entire channel [12]. In this case, the physical gate length >  $L_{\rm ch}$ , but it allows gating of the entire channel because  $L_{\rm ch} = L$ . Although such FETs are unsuitable for very high-frequency applications due to the overlap capacitances between the contacts, they could provide an insight into the operation of the ultra-scaled  $MoS_2$  FETs. However, all ultra-scaled  $MoS_2$  FETs which have been realized in this way so far were based on technologies which cannot be implemented on a large scale. Self-assembly of block copolymers have been used to fabricate back-gated MoS<sub>2</sub> FETs with L = 7.5 nm, but required guiding Au lines and produced only multiple FETs connected in series [13]. Sub-10 nm top-gated  $MoS_2$  FETs have also been realized, but only on top of cracks in  $Bi_2O_3$  [14] or grain boundaries of graphene [15].

Here we demonstrate 10-nm MoS<sub>2</sub> FETs fabricated on a large scale without highresolution patterning. This was achieved by fabricating the long-channel MoS<sub>2</sub> FETs by conventional lithography, and then reducing the length of the channel down to 10 nm by a shadow evaporation [16–21] of Au. The devices were fabricated on a local Al back gate with an ultra-thin high-k oxide (AlO<sub>x</sub>) in order to efficiently gate the entire channel ( $L_{ch} = L$ ). Both exfoliated MoS<sub>2</sub> and monolayer MoS<sub>2</sub> grown by CVD were used in fabrication. The realized 10-nm MoS<sub>2</sub> FETs exhibit very small hysteresis of current-voltage characteristics, drain current  $I_D \sim 560$  A/m, and subthreshold swing  $S_{th} \sim 120$  mV/dec in air ambient. We also realized the n-type depletion mode digital

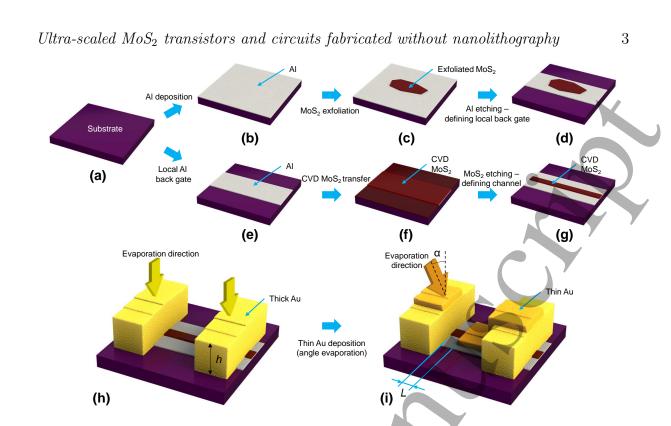

Figure 1. Schematic of the fabrication steps used to realize 10 nm MoS<sub>2</sub> FETs. (a) The devices were fabricated on standard SiO<sub>2</sub>/Si substrates. (b) In the case of exfoliated MoS<sub>2</sub>, the entire surface of the substrate was covered by a thin layer of Al deposited by electron-beam (e-beam) evaporation. A thin native oxide (AlO<sub>x</sub>) layer was formed on the top surface of Al after the sample was exposed to ambient air. (c) MoS<sub>2</sub> was exfoliated on top of the AlO<sub>x</sub>/Al layer. (d) A local back gate was defined after etching the AlO<sub>x</sub>/Al gate stack around the exfoliated MoS<sub>2</sub> flakes. (e) In the case of CVD MoS<sub>2</sub>, the gate structure was defined in the first step by patterning and lift off of Al. As in (b), the gate stack was formed by exposing the samples to air ambient. (f) CVD MoS<sub>2</sub> was transferred to the entire chip. (g) CVD MoS<sub>2</sub> was etched to define the channel. (h) Patterning and lift off were used to define thick source and drain Au contacts on top of the structures realized in (d) or (g). (i) A nanogap was formed next to the contact which shadows the MoS<sub>2</sub> channel from the material evaporated under angle  $\alpha > 0$  with respect to the vertical axis of the sample.

inverters with 10-nm MoS<sub>2</sub> FETs which exhibited high voltage gain  $(A_v \sim -50)$  and input/output signal matching.

#### 2. Results and Discussion

Fabrication of ultra-scaled MoS<sub>2</sub> FETs is schematically depicted in Fig. 1. In the case of exfoliated MoS<sub>2</sub>, a thin (25 nm) Al layer was initially evaporated on a standard SiO<sub>2</sub>/Si substrate (Fig. 1(a)-(b)). The atomic force microscopy (AFM) image of one such substrate is shown in Supporting Information Fig. S1. The substrate was then exposed to air ambient to form a native oxide (AlO<sub>x</sub>) at the top surface of Al [10, 12]. The native oxide layer had a thickness  $t_{ox} \sim 4$  nm and was used as a gate insulator. In the next step, MoS<sub>2</sub> was exfoliated on top of the AlO<sub>x</sub>/Al gate stack (Fig. 1(c)). In

#### Ultra-scaled MoS<sub>2</sub> transistors and circuits fabricated without nanolithography

order to reduce the overlap between the gate and source/drain contacts, the gate stack was then etched away, apart from the areas supporting the  $MoS_2$  flakes (Fig. 1(d)). In the case of CVD-grown  $MoS_2$  FETs, the gates were already patterned in the first step (Fig. 1(e)) and then CVD  $MoS_2$  was deposited on top (Fig. 1(f)). The FET channel was then defined by etching CVD  $MoS_2$  (Fig. 1(g)).

In both cases, the source and drain contacts, separated by ~ 1 µm, were subsequently fabricated by standard lithography, evaporating a thick layer (thickness h = 60 nm) of Au (Fig. 1(h)). In the final step, a thin (22 nm) layer of Au was evaporated under tilt in order to create a small gap next to the contacts [18–21] which shadow the MoS<sub>2</sub> channels (Fig. 1(i)). The size of the gap was controlled by the evaporation angle  $\alpha$  and the thickness of initial source and drain contacts (h). Therefore, the resolution of the initial lithographic process used to fabricate the initial source and drain contacts did not have any influence on the gap size. Gaps with the lengths  $L_{ch}$  between 10 and 20 nm were realized in this way.

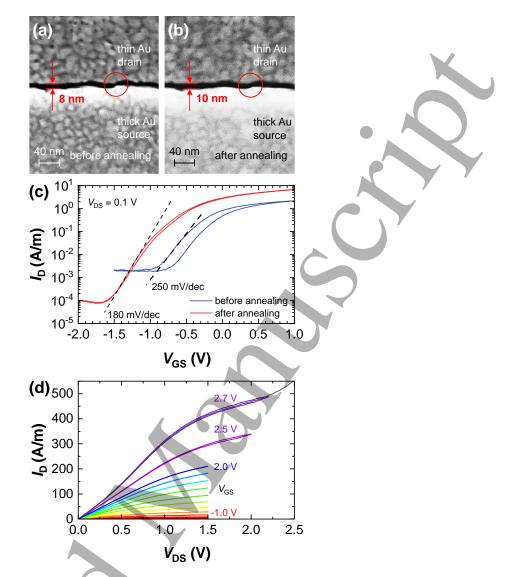

Fig. 2(a) shows a nanogap between the source and drain contacts in one of the exfoliated multilayer  $MoS_2$  FETs, immediately after the shadow evaporation (large area images are shown in Fig. S2 and Fig. S3 and tilted images in Fig. S4). The edges of the contacts, defining the gap, are not perfectly smooth due to unavoidable imperfections in the profile of the developed resist (used in the lithographic process to define the initial source and drain contacts) and finite grain size of the evaporated Au film. These imperfections limit the minimum gap size to ~ 8 nm in contacts realized on exfoliated  $MoS_2$ . At smaller gap sizes (Fig. S5 shows a 5-nm gap), the material protruding across the gap (as in the encircled part of the gap shown in Fig. 2(a)) may coalesce and short circuit the contacts. Even if not connected (as in Fig. 2(a)), such protrusions deteriorate the electrical properties of the FETs due to parasitic tunneling currents flowing between them. This is typically manifested in the reduction of the on/off ratio (Fig. 2(c)).

The electrical properties of the FETs were improved by thermal annealing. Fig. 2(b) shows the same section of the nanogap from Fig. 2(a) after annealing in vacuum. The protrusions which are not connected tend to recede to the corresponding contacts upon annealing, as evidenced by the encircled part of the gap in Fig. 2(b). Although this slightly increases the minimum gap size to ~ 10 nm on exfoliated MoS<sub>2</sub>, it also significantly reduces the tunneling currents and improves the electrical properties of the FETs, as shown in Fig. 2(c). Annealed FETs exhibited ~ 10 times smaller drain off-current (due to reduced tunneling) but also higher drain on-current as annealing reduces the source and drain contact resistances [9]. This resulted in ~ 100 larger drain on/off current ratio (which increased from  $10^3$  to  $10^5$ ) and a smaller subthreshold swing after annealing.

The output curves of the nonannealed FETs exhibited very poor drain current saturation (Fig. S6) due to parasitic tunneling currents which flow in parallel to the channel drain current. On the other hand, the annealed FETs exhibited a very good saturation for such short devices, with output conductance  $g_d \sim 10$  S/m (normalized by the channel width W), as shown in Fig. 2(d) for  $V_{\rm GS} < 1$  V. The highest measured

Ultra-scaled MoS<sub>2</sub> transistors and circuits fabricated without nanolithography

Figure 2. Nanogap in exfoliated  $MoS_2$  FETs. (a) A scanning electron microscopy (SEM) image of an  $\sim 8$  nm long nanogap separating the source and drain contacts. The top (thin) contact was obtained by e-beam evaporation of Au shadowed by the bottom (thick) contact creating the nanogap. The circle indicates protrusions responsible for tunneling across the gap. The FET was made on a  $\sim 6$  nm thick exfoliated MoS<sub>2</sub> (Fig. S3). (b) The same nanogap after thermal annealing. The annealing melts sharp protrusions which defuse towards bulk metal, making the nanogap more uniform, as can be seen in the encircled area. (c) The transfer characteristics of the FET shown in (a) and (b) before (blue line) and after (red line) annealing, measured at  $V_{\rm DS} = 0.1$  V. Despite the removal of the tunneling sites, the on current increases almost three times due to the reduction of contact resistance [9]. The drain current on/off ratio improves by two orders of magnitude and subthreshold swing reduces from 250 mV/dec to 180 mV/dec after thermal annealing. (d) The output characteristics of the same 10 nm  $MoS_2$  FET after annealing. The gate-source voltage values are 2.7 V (two measurements shown), 2.5 V, and in the range from -1 V to 2 V (with a step of 0.2 V). Despite large  $V_{\text{GS}}$  and  $V_{\text{DS}}$ , the gate leakage current did not influence the drain current (Fig. S7).

#### Ultra-scaled MoS<sub>2</sub> transistors and circuits fabricated without nanolithography

drain current was  $I_{\rm D} = 560$  A/m, which is the highest demonstrated drain current in MoS<sub>2</sub> FETs in air ambient so far [10, 15, 22–29]. The largest transconductance was  $g_{\rm m} = 662$  S/m at  $V_{\rm DS} = 2$  V and  $V_{\rm GS} = 2.5$  V (Fig. 2(d)), while the highest intrinsic transistor gain was  $A = g_{\rm m}/g_{\rm d} \sim 11$  on all output curves. The measured transconductance results in the highest extrinsic electric field mobility  $\mu = 3$  cm<sup>2</sup>/Vs. The obtained extrinsic mobility is small because it includes the contribution of the contact resistance, as discussed in the Methods section. Despite small extrinsic mobility, the transconductance is comparable to that of graphene field-effect transistors with a gate length of ~ 1 µm [30] due to a very short gate.

The obtained extrinsic electric field mobility in exfoliated multilayer MoS<sub>2</sub> FETs is comparable to that of short-channel devices comprising exfoliated monolayer MoS<sub>2</sub> [14]. However, multilayer MoS<sub>2</sub> cannot fully follow the surface roughness of the gate (Fig. S8). This reduced the direct contact between the MoS<sub>2</sub> channel and the gate which reduced the gate capacitance. The reduced gate capacitance leads to larger than expected [10, 13, 14, 31] subthreshold swing ( $S_{\rm th} \sim 180$  mV/dec) and drain induced barrier lowering (~ 230 mV/V).

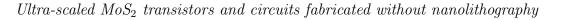

The ultra-scaled FETs were also made of CVD-grown monolayer MoS<sub>2</sub> [32]. The minimum gap size in such FETs was between 10 and 20 nm (Fig. 3(a) and Fig. S9), which was larger than that of the exfoliated MoS<sub>2</sub> FETs. We found that use of CVD MoS<sub>2</sub> required larger initial gaps because annealing was not very effective in eliminating the protrusions on CVD MoS<sub>2</sub>. This is probably due to the pinning of protrusions on the imperfections in the CVD grown material and underlying roughness of the gate (which has more influence on the surface roughness of the CVD monolayer compared to the exfoliated multilayer MoS<sub>2</sub>). However, CVD monolayer MoS<sub>2</sub> FETs were found to have larger drain current on/off ratio (~ 10<sup>6</sup>) and smaller subthreshold swing ( $S_{\rm th} \sim 120 \text{ mV/dec}$ ) compared to the exfoliated multilayer MoS<sub>2</sub> FETs (Fig. 3(a)). This is because of the larger bandgap in monolayer MoS<sub>2</sub> with respect to multilayer MoS<sub>2</sub> and slightly larger gate length in CVD FETs. Use of CVD-grown material also allowed a large-scale fabrication of FETs, which was not possible with the exfoliated material. However, there are limitations in the large-scale fabrication of the FETs, as discussed in the Methods section and Fig. S10.

The largest measured drain current in CVD monolayer MoS<sub>2</sub> FETs was  $I_{\rm D} = 360$  A/m (Fig. 3(b)), which is comparable to the highest drain current reported for such FETs [10], even though the latter were obtained by pulsed measurements in vacuum; here, the measurements were performed in air ambient without pulsing voltages. The largest transconductance was  $g_{\rm m} = 170$  S/m at  $V_{\rm DS} = 2$  V and  $V_{\rm GS} = 1.6$  V (Fig. 3(b)), which resulted in the highest extrinsic electric field mobility  $\mu = 1.2$  cm<sup>2</sup>/Vs. In this case, the mobility was lower than that of the exfoliated FETs due to the additional processing step used to transfer MoS<sub>2</sub> from the growth substrate to the substrate on which the local back gates were prefabricated. This process (described in the Methods section) is not required for top-gated FETs, which were fabricated directly on the growth substrate [10], and it deteriorated the quality of the transferred CVD monolayer MoS<sub>2</sub>.

Figure 3. The electrical characteristics of 20 nm CVD monolayer  $MoS_2$  FETs. (a) The transfer characteristic of the FET shown in the inset, measured at  $V_{DS} = 0.1$  V. The gate leakage current did not influence the subthreshold swing but it was responsible for the constant drain current for  $V_{GS} < -1$  V (Fig. S11). The inset shows an SEM image of a CVD monolayer  $MoS_2$  FET with a channel length of 20 nm. (b) The output characteristics of the same FET measured at gate-source voltages in the range from -0.8 V to 2.8 V with a step of 0.4 V.

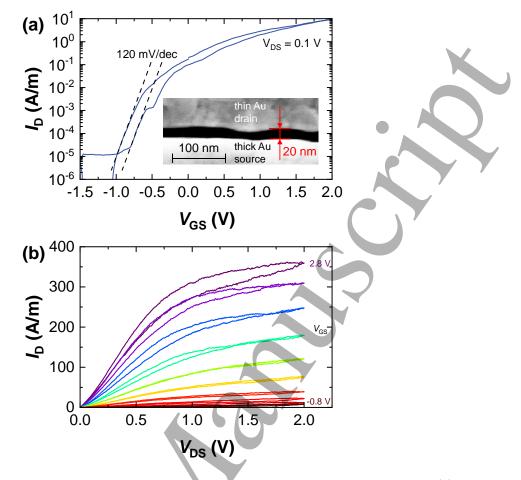

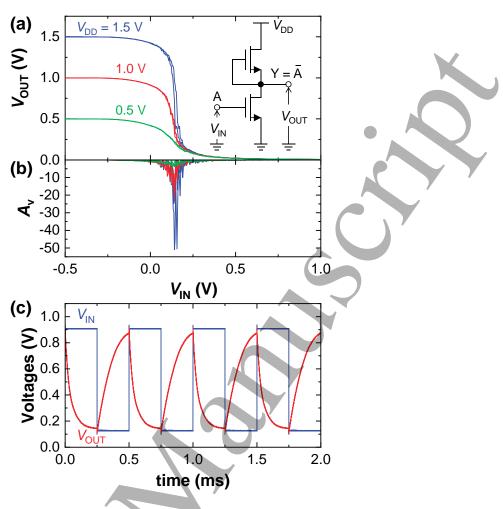

The ultra-scaled MoS<sub>2</sub> FETs were used to realize logic gates in the n-type depletionload technology. Fig. 4(a) shows the static voltage transfer characteristics of an MoS<sub>2</sub> inverter. In most of the realized FETs, the threshold voltage was slightly negative  $(V_{\rm th} \sim -0.2 \text{ V})$  leading to a weak conduction of the load FET (the top FET in the inverter in Fig. 4(a)) in which  $V_{\rm GS} = 0$  V. Besides,  $V_{\rm th} \sim -0.2$  V results in the threshold voltage of the logic gates  $\langle V_{\rm DD}/2$ . At large enough positive input voltages  $(V_{\rm IN} > 0.4 \text{ V})$ , the driver FET (the bottom FET in the inverter) was therefore much more conductive than the load FET and the output voltage was approximately equal to zero, leading to a rail-to-rail operation. Small conductivity of the load FET and good saturation of the FETs led to a steep drop of the output voltage  $V_{\rm OUT}$  as the input voltage  $V_{\rm IN}$  is increased (at  $V_{\rm IN} \sim 0.15$  V). This resulted in a large voltage gain  $A_{\rm v} - 50$ (Fig. 4(b)), which is remarkably high for such short devices.

The threshold voltage of the logic gates, which was below  $V_{\rm DD}/2$ , prevented

Ultra-scaled  $MoS_2$  transistors and circuits fabricated without nanolithography

Figure 4. The ultra-scaled MoS<sub>2</sub> inverters in depletion-load technology. (a) The static voltage transfer characteristics (the output voltage  $V_{\rm OUT}$  vs. the input voltage  $V_{\rm IN}$ ) of an inverter at three different power supply voltages  $V_{\rm DD}$  of 0.5 V, 1 V, and 1.5 V. The inset shows the schematic of an inverter. (b) The calculated low-frequency voltage gain  $A_{\rm v} = dV_{\rm OUT}/dV_{\rm IN}$ . (c) The digital waveforms measured in an inverter whose static voltage transfer characteristic is shown in Fig. S12. The waveforms demonstrate in/out signal matching capabilities of the inverter. The clock rate of the input signal is 2 kHz.

matching between the input and output signals, despite very high voltage gain. In addition, the current drive capabilities of the load FET were significantly reduced due to its poor conductivity. As a consequence, the realized logic gates could not be clocked above a few Hz, which is typical for this type of the load FETs [33]. This problem was overcome by using more conductive load FETs at  $V_{\rm GS} = 0$  V, i.e., the load FETs with a more negative threshold voltage. This is demonstrated in Fig. 4(c) which shows the digital waveforms measured in one of the inverters in which the load FET had  $V_{\rm th} = -0.4$  V. Due to better conductivity of the load FET, the output voltage decreased slower as the input voltage was increased, effectively shifting the threshold voltage of the logic gates to ~  $V_{\rm DD}/2$  (Fig. S12). Although this reduced the voltage gain and output voltage swing (and therefore increased the static power dissipation), it allowed signal

#### Ultra-scaled $MoS_2$ transistors and circuits fabricated without nanolithography

matching, as shown in Fig. 4(c). In addition, a higher operating frequency was reached compared to that of the high-gain logic gates with low-conductivity load FETs [33], as demonstrated in Fig. 4(c). However, this frequency is still much smaller than the cutoff frequency of the highly conductive FETs (Fig. S13).

#### 3. Conclusion

We have demonstrated facile and scalable technique for the fabrication of ultrashort channel MoS<sub>2</sub> FETs which does not require nanolithography. The technique is general (i.e., it can be applied to any semiconductor transistor channel) and based on shadowing evaporated material by the standard prefabricated source and drain contacts. We realized both exfoliated and CVD MoS<sub>2</sub> FETs in which the entire transistor channel, with a length between 10 and 20 nm, was gated. The realized MoS<sub>2</sub> FETs exhibit good drain current saturation demonstrating the suppression of the short-channel effects in atomically thin transistors. The ultra-scaled MoS<sub>2</sub> FETs were used to realize logic gates in the n-type depletion-load technology with a voltage gain of  $\sim -50$ . The load FETs with a higher current drive were used to improve the operating frequency and signal matching of the logic gates at the expense of the voltage gain. The tradeoff between the speed and voltage gain demonstrates a need for the implementation of the ultra-scaled FETs in future complementary metal-oxide-semiconductor (e.g., MoS<sub>2</sub>) technology.

#### 4. Methods

Degenerately doped Si chips with thermally grown 290 nm thick SiO<sub>2</sub> were used in the fabrication of the ultra-scaled MoS<sub>2</sub> FETs. Prior to the deposition of Al, the substrates were thoroughly cleaned in an acetone bath and rinsed with isopropanol. The gates were fabricated by thermal evaporation of 25 nm of Al in an e-beam evaporator at a base pressure of  $1.2 \times 10^6$  mbar. After Al deposition, the samples were kept in air for one day to oxidize the top surface of Al. This created an Al/AlO<sub>x</sub> gate stack with a gate oxide capacitance  $C_{\rm ox} = 1.4 \,\mu {\rm F/cm^2}$  [10,34]. Although such native gate oxide has larger surface roughness than the underlying SiO<sub>2</sub> substrate (Fig. S1), we found that the gate leakage current did not have influence on the drain current (Fig. S7 and Fig. S11) if the gate oxide voltage was kept below 2.8 V. The typical gate oxide breakdown voltage was  $\sim 2.9 {\rm V}$ .

Both exfoliated and CVD  $MoS_2$  were used in fabrication. Micromechanical exfoliation of  $MoS_2$  (SPI supplies) was performed by a Scotch tape method directly on the substrates on which 25 nm of Al was previously evaporated (Fig. 1(c)). After exfoliation,  $MoS_2$  flakes were located by an optical microscope and then characterized by an AFM (Veeco Innova) to find the thickness of the flakes. Due to a poor contrast of  $MoS_2$  on Al, it was not possible to locate monolayer  $MoS_2$  and therefore the flakes with thicknesses between 5 and 15 nm were used in device fabrication.

$MoS_2$  was grown directly on  $SiO_2$  via solid-source CVD [27]. In particular,  $SiO_2$  was

#### Ultra-scaled $MoS_2$ transistors and circuits fabricated without nanolithography

treated with hexamethyldisilazane, and then decorated  $\sim 25 \ \mu L$  of 100  $\mu M$  perylene-3,4,9,10 tetracarboxylic acid tetrapotassium salt. The substrate was placed face down on an alumina crucible with  $\sim 0.5 \text{ mg}$  of MoO<sub>3</sub> powder, and loaded in to a tube furnace 30 cm downstream of  $\sim$  100 mg of S powder. The tube was evacuated and flushed with Ar gas and brought back to atmospheric pressure. Temperature was ramped to 850 °C and held for 15 min with 30 sccm Ar flow, before being cooled to room temperature. After the growth, CVD MoS<sub>2</sub> was transferred from the growth substrate to the final substrate containing pre patterned gates (Fig. 1(f)). Due to a strong adhesion of the CVD grown  $MoS_2$  to the growth substrate, the transfer to the final substrate required evaporation of 60 nm of Au [35, 36] on MoS<sub>2</sub> and spin coating of a poly(methyl methacrylate) (PMMA) layer on top of Au. The resulting PMMA/Au/MoS<sub>2</sub> stack was picked up from the growth substrate by a polydimethylsiloxane (PDMS) stamp. Once the PMMA/Au/MoS<sub>2</sub> stack was detached from the growth substrate, it was placed on the final substrate. There, the entire stack was heated to  $160 \, {}^\circ\mathrm{C}$  for 5 min to remove the PDMS stamp. PMMA was removed then in the acetone bath, followed by Au etching using KI:I solution (Sigma Aldrich). After etching of Au, the  $MoS_2$  channel was defined by plasma etching using  $SF_6$  (base pressure 80 mbar, flow rate 10 sccm, and power 50 W) for 25 sec. A larger hysteresis and smaller mobility in CVD  $MoS_2$  FETs were attributed to the damaging effect of the transfer procedure.

All patterning was performed by e-beam lithography (Raith eLINE) at 10 kV using different types of PMMA (molecular weights between 250,000 and 950,000) as e-beam resists. However, high-resolution patterning was not required because the initially fabricated contacts had dimensions  $\sim 1 \mu m$ . Any other low-resolution method (e.g., conventional optical lithography) could have also been used in the fabrication of the initial contacts.

In the case of exfoliated  $MoS_2$ , Al surrounding the  $MoS_2$  flakes was etched away (Fig. 1(d)) to reduce the overlap between the gate and source/drain contacts, i.e., to reduce the gate leakage current and parasitic components. Tetramethylammonium hydroxide was used for 15 s to completely etch away 25 nm of Al. After etching, Al sample was kept in acetone for 2 hours to remove the PMMA mask.

The initial 60-nm thick Au source and drain contacts (Fig. 1(h)) were fabricated by evaporating Au at a normal incidence in the e-beam evaporator at a base pressure  $\sim 1.2 \times 10^{-6}$  mbar. After fabricating the initial thick Au contacts, the second lithography process was used to define the pattern for thin Au contacts (Fig. 1(i)). A thin layer of Au (22 nm) was deposited in the same e-beam evaporator, but this time the samples were tilted by  $\alpha = 15^{\circ}$  with respect to the direction of the evaporated Au. The directionality of the e-beam evaporation process effectively increases shadowing [37,38] both from the resist and thick contacts resulting in an oblique profile of the contacts, as discussed in Fig. S4.

The device fabrication was performed in parallel, i.e., all FETs on a wafer were fabricated at the same time. However, successful large-scale fabrication of the FETs also requires maintaining a constant gate length across a wafer. The gate length uniformity

#### Ultra-scaled $MoS_2$ transistors and circuits fabricated without nanolithography

is affected by the thickness uniformity of the initial thick contacts deposited by e-beam evaporation [39]. The gate length uniformity of our process technology is discussed in Fig. S10 which demonstrates that smoother substrate is required for better uniformity. Therefore, the successful large-scale fabrication of the FETs would require very smooth deposition of the gate material, e.g., by atomic layer deposition.

After the fabrication of nanogaps, the samples were annealed at 250 °C in vacuum (pressure  $< 5 \times 10^{-6}$  mbar) for 1 hour. Annealing cleaned the nanogaps from protrusions and improved metal contact to MoS<sub>2</sub>. Thermal annealing was performed in vacuum to prevent any damage to MoS<sub>2</sub> due to oxygen or humidity at higher temperature. The samples were heated to 250 °C at a rate of 10 °C/min. After annealing, the samples were allowed to spontaneously cool down to room temperature in vacuum.

The extrinsic electric-field mobility was calculated from the measured transfer curves. We fabricated both long  $(L \sim 1 \ \mu\text{m})$  and short  $(L \sim 10 \ \text{nm})$  channel FETs on a global SiO<sub>2</sub>/Si back gate as a reference. We found that typical extrinsic mobility in long channel FETs on SiO<sub>2</sub> was ~ 55 cm<sup>2</sup>/Vs reducing down to ~ 4 cm<sup>2</sup>/Vs in short channel FETs. The reason for such small extrinsic mobility in short-channel devices is the contact resistance which is comparable to the resistance of short channels. The obtained value of ~ 4 cm<sup>2</sup>/Vs on SiO<sub>2</sub> was close to ~ 3 cm<sup>2</sup>/Vs obtained in short-channel devices on AlO<sub>x</sub>.

All electrical measurements were performed in air ambient in FormFactor probe stations EP6 and Summit 11000. The electrical characterizations of the FETs and inverters were performed by Keithley 2611B source-measure units, a function generator (Tektronic AFG 3022B), and an oscilloscope (Keysight DS09064A). The small hysteresis in the samples was a consequence of adsorption of water from humidity in air [40–42] and charge traps in the gate oxide [43]. The SEM imaging was performed in Raith eLINE at 10 kV. The inverters were realized by externally connecting the fabricated FETs.

#### Acknowledgments

We thank Alexey Fedorov for support with thermal annealing. This research was supported by the EU H2020 Graphene Flagship Core 2 Grant No. 785219. R.W.G. acknowledges support from the NSF Graduate Research Fellowship under Grant No. DGE-1656518.

- [1] Moore G E 2006 IEEE Solid-State Circuits Society Newsletter 11 36–37

- [2] 2015 International technology roadmap for semiconductors (ITRS)

- [3] Bohr M T and Young I A 2017 IEEE Micro 37 20–29

- [4] Chaudhry A and Kumar M J 2004 IEEE Trans. Device Mater. Rel. 4 99-109 ISSN 1530-4388

- [6] Mak K F, Lee C, Hone J, Shan J and Heinz T F 2010 Phys. Rev. Lett. 105(13) 136805

[7] Cao W, Kang J, Sarkar D, Liu W and Banerjee K 2015 IEEE Trans. Electron Devices 62 3459–3469

#### Ultra-scaled $MoS_2$ transistors and circuits fabricated without nanolithography

12

- $[8]\,$  Liu H, Neal A T and Ye P D 2012 ACS Nano 6 8563–8569

- [9] Radisavljevic B, Radenovic A, Brivio J, Giacometti V and Kis A 2011 Nature Nanotech. 6 147–150

- [10] English C D, Smithe K K, Xu R and Pop E 2016 Approaching ballistic transport in monolayer MoS<sub>2</sub> transistors with self-aligned 10 nm top gates Int. El. Devices Meet. (San Francisco, CA, USA) pp 5.6.1–5.6.4

- [11] Desai S B, Madhvapathy S R, Sachid A B, Llinas J P, Wang Q, Ahn G H, Pitner G, Kim M J, Bokor J, Hu C, Wong H S P and Javey A 2016 Science 354 99–102

- [12] Guerriero E, Polloni L, Rizzi L G, Bianchi M, Mondello G and Sordan R 2012 Small 8 357–361

- [13] Nourbakhsh A, Zubair A, Sajjad R N, Tavakkoli K G A, Chen W, Fang S, Ling X, Kong J, Dresselhaus M S, Kaxiras E, Berggren K K, Antoniadis D and Palacios T 2016 Nano Lett. 16 7798–7806

- [14] Xu K, Chen D, Yang F, Wang Z, Yin L, Wang F, Cheng R, Liu K, Xiong J, Liu Q and He J 2017 Nano Lett. 17 1065–1070

- [15] Xie L, Liao M, Wang S, Yu H, Du L, Tang J, Zhao J, Zhang J, Chen P, Lu X, Wang G, Xie G, Yang R, Shi D and Zhang G 2017 Adv. Mater. 29 1702522

- [16] Niemeyer J 1974 PTB-Mitt. 84 251

- [17] Dolan G J 1977 Appl. Phys. Lett. **31** 337–339

- [18] Philipp G, Weimann T, Hinze P, Burghard M and Weis J 1999 Microelectron. Eng. 46 157–160

- [19] Naitoh Y, Tsukagoshi K, Murata K and Mizutani W 2003 E-j. Surf. Sci. Nanotechnol. 1 41-44

- [20] Javey A, Qi P, Wang Q and Dai H 2004 Proc. Natl. Acad. Sci. USA 101 13408-13410

- [21] Miao J, Zhang S, Cai L, Scherr M and Wang C 2015 ACS Nano 9 9236–9243

- [22] Das S, Chen H Y, Penumatcha A V and Appenzeller J 2013 Nano Lett. 13 100–105

- [23] English C D, Shine G, Dorgan V E, Saraswat K C and Pop E 2016 Nano Lett. 16 3824–3830

- [24] Leong W S, Luo X, Li Y, Khoo K H, Quek S Y and Thong J T L 2015 ACS Nano 9 869-877

- [25] Lembke D and Kis A 2012 ACS Nano 6 10070–10075

- [26] Liu W, Kang J, Cao W, Sarkar D, Khatami Y, Jena D and Banerjee K 2013 High-performance few-layer-MoS<sub>2</sub> field-effect-transistor with record low contact-resistance 2013 IEEE International Electron Devices Meeting pp 19.4.1–19.4.4

- [27] Smithe K K H, English C D, Suryavanshi S V and Pop E 2016 2D Mater. 4 011009

- [28] Smithe K K H, English C D, Suryavanshi S V and Pop E 2018 Nano Lett. 18 4516-4522

- [29] McClellan C J, Yalon E, Smithe K K H, Suryavanshi S V and Pop E 2017 Effective n-type doping of monolayer MoS<sub>2</sub> by AlO<sub>x</sub> 2017 75th Annual Device Research Conference (DRC) pp 1–2

- [30] Guerriero E, Pedrinazzi P, Mansouri A, Habibpour O, Winters M, Rorsman N, Behnam A, Carrion E A, Pesquera A, Centeno A, Zurutuza A, Pop E, Zirath H and Sordan R 2017 Sci. Rep. 7 2419

- [31] Liu L, Lu Y and Guo J 2013 IEEE Trans. Electron Devices 60 4133-4139

- [32] Smithe K K H, Suryavanshi S V, Muñoz Rojo M, Tedjarati A D and Pop E 2017 ACS Nano 11 8456–8463

- [33] Wachter S, Polyushkin D K, Bethge O and Mueller T 2017 Nat. Commun. 8 14948

- [34] Guerriero E, Polloni L, Bianchi M, Behnam A, Carrion E, Rizzi L G, Pop E and Sordan R 2013 ACS Nano 7 5588–5594

- [35] Magda G Z, Peto J, Dobrik G, Hwang C, Biró L P and Tapasztó L 2015 Sci. Rep. 5 14714

- [36] Desai S B, Madhvapathy S R, Amani M, Kiriya D, Hettick M, Tosun M, Zhou Y, Dubey M, Ager III J W, Chrzan D and Javey A 2016 Adv. Mater. 28 4053–4058

- [37] Barabási A L and Stanley H E 1995 Fractal Concepts in Surface Growth (Cambridge University Press)

- [38] Sordan R, Miranda A, Traversi F, Colombo D, Chrastina D, Isella G, Masserini M, Miglio L, Kern K and Balasubramanian K 2009 Lab Chip **9**(11) 1556–1560

- [39] Ohring M 1992 The Materials Science of Thin Films (San Diego: Academic Press)

- [40] Late D J, Liu B, Matte H S S R, Dravid V P and Rao C N R 2012 ACS Nano 6 5635–5641

- [41] Li T, Wan B, Du G, Zhang B and Zeng Z 2015 AIP Adv. 5 057102

- [42] Illarionov Y Y, Smithe K K H, Waltl M, Knobloch T, Pop E and Grasser T 2017 IEEE Electron

58

59 60