Florida International University FIU Digital Commons

**FIU Electronic Theses and Dissertations**

University Graduate School

3-28-2022

# Thermal Aware Design Automation of the Electronic Control System for Autonomous Vehicles

Ajinkya Bankar abank013@fiu.edu

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

Part of the Computer and Systems Architecture Commons, and the Electrical and Electronics Commons

#### **Recommended Citation**

Bankar, Ajinkya, "Thermal Aware Design Automation of the Electronic Control System for Autonomous Vehicles" (2022). *FIU Electronic Theses and Dissertations*. 4922. https://digitalcommons.fiu.edu/etd/4922

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fiu.edu.

#### FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

# THERMAL AWARE DESIGN AUTOMATION OF THE ELECTRONIC CONTROL SYSTEM FOR AUTONOMOUS VEHICLES

A dissertation submitted in partial fulfillment of the

requirements for the degree of

# DOCTOR OF PHILOSOPHY

in

# ELECTRICAL AND COMPUTER ENGINEERING

by

Ajinkya Bankar

2022

To: Dean John L. Volakis College of Engineering and Computing

This dissertation, written by Ajinkya Bankar, and entitled Thermal Aware Design Automation of the Electronic Control System for Autonomous Vehicles, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

Nezih Pala

Ou Bai

Kemal Akkaya

Deng Pan

Gang Quan, Major Professor

Date of Defense: March 28, 2022

The dissertation of Ajinkya Bankar is approved.

Dean John L. Volakis College of Engineering and Computing

Andrés G. Gil Vice President for Research and Economic Development and Dean of the University Graduate School

Florida International University, 2022

© Copyright 2022 by Ajinkya Bankar All rights reserved.

# DEDICATION

I dedicate this dissertation to my younger brother, the late Abhijit (Pappu). I am grateful that I could complete your wish. May you find peace and happiness in Paradise!

#### ACKNOWLEDGMENTS

First and foremost, I would like to thank my master H. H. Sri Sri Ravi Shankar, for giving me the strength and patience to accomplish my late younger brother's dream of getting a Ph.D. degree.

Next, I would like to express my deepest gratitude to my advisor, Dr. Gang Quan. I consider myself fortunate and blessed to have Dr. Quan as my advisor for the last four years of my Ph.D. study, who provided constant supervision, personal attention, suggestions, unending encouragement, and strong support. I respect his determination, breadth of knowledge, and unwavering commitment to students and high-quality research. Dr. Quan's ideas and suggestions have aided me in successfully completing this dissertation.

I am very grateful to my Ph.D. committee members, Dr. Nezih Pala, Dr. Ou Bai, Dr. Kemal Akkaya, and Dr. Deng Pan, for their thoughtful insights and suggestions in improving my dissertation. I am incredibly proud to have such knowledgeable people serving on my dissertation committee. I want to give my heartfelt thanks to collaborators, Dr. Vivek Chaturvedi and Dr. Shi Sha for their endless encouragement and support in accomplishing my career objectives. I am thankful to Dr. Gustavo Chaparro-Baquero and Dr. Somar Homsi for their help and insightful suggestions throughout the stay in Miami.

I am also thankful to the ECE department for creating an impactful research environment and providing financial support. I especially thank University Graduate School, Florida International University, for awarding Dissertation Year Fellowship for Fall 2021 and Spring 2022 semesters, which helped me to laser-focus on my doctoral research.

Finally, I want to thank my Bankar family, relatives, friends, the Art of Living family, and extended family of the United States for their unlimited love, faith, encouragement, blessings, and prayers. My life-long gratitude goes to my dearest mother, Mrs. Jayashree Bankar, and my loving father, Mr. Suryakant Bankar, for all the love and affection they have showered. I am grateful to my wife, Mrs. Diksha Bankar, for accompanying me during my Ph.D. journey. And, cute thanks to my loving daughter, Advika, for bringing moments of joy and happiness. I want to thank my uncle, late Mr. Chandrakant Bankar, for being a great wall of support and inspiration in my life. May you find peace and happiness in Paradise!

# ABSTRACT OF THE DISSERTATION THERMAL AWARE DESIGN AUTOMATION OF THE ELECTRONIC CONTROL SYSTEM FOR AUTONOMOUS VEHICLES

by

Ajinkya Bankar

Florida International University, 2022

Miami, Florida

Professor Gang Quan, Major Professor

The autonomous vehicle (AV) technology, due to its tremendous social and economical benefits, is transforming the entire world in the coming decades. However, significant technical challenges still need to be overcome until AVs can be safely, reliably, and massively deployed. Temperature plays a key role in the safety and reliability of an AV, not only because a vehicle is subjected to extreme operating temperatures but also because the increasing computations demand more powerful IC chips, which can lead to higher operating temperature and large thermal gradient. In particular, as the underpinning technology for AV, artificial intelligence (AI) requires substantially increased computation and memory resources, which have been growing exponentially through recent years and further exacerbated the thermal problems. High operating temperature and large thermal gradient can reduce the performance, degrade the reliability, and even cause an IC to fail catastrophically.

We believe that dealing with thermal issues must be coupled closely in the design phase of the AVs' electronic control system (ECS). To this end, first, we study how to map vehicle applications to ECS with heterogeneous architecture to satisfy peak temperature constraints and optimize latency and system-level reliability. We present a mathematical programming model to bound the peak temperature for the ECS. We also develop an approach based on the genetic algorithm to bound the peak temperature under varying execution time scenarios and optimize the systemlevel reliability of the ECS. We present several computationally efficient techniques for system-level mean-time-to-failure (MTTF) computation, which show severalorder-of-magnitude speed-up over the state-of-the-art method. Second, we focus on studying the thermal impacts of AI techniques. Specifically, we study how the thermal impacts for the memory bit flipping can affect the prediction accuracy of a deep neural network (DNN). We develop a neuron-level analytical sensitivity estimation framework to quantify this impact and study its effectiveness with popular DNN architectures. Third, we study the problem of incorporating thermal impacts into mapping the parameters for DNN neurons to memory banks to improve prediction accuracy. Based on our developed sensitivity metric, we develop a bin-packingbased approach to map DNN neuron parameters to memory banks with different temperature profiles. We also study the problem of identifying the optimal temperature profiles for memory systems that can minimize the thermal impacts. We show that the thermal aware mapping of DNN neuron parameters on memory banks can significantly improve the prediction accuracy at a high-temperature range than the thermal ignorant for state-of-the-art DNNs.

# TABLE OF CONTENTS

| CHAPTER PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GE                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 1. INTRODUCTION1.1 About the Autonomous Vehicle Technology1.2 Artificial Intelligence Technology for Autonomous Vehicle Design1.3 Thermal Challenges for Autonomous Vehicles1.4 Research Problem and Our Contributions1.5 Structure of the Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $     \begin{array}{c}       1 \\       2 \\       7 \\       10 \\       15 \\       18 \\     \end{array} $ |

| 2. PRELIMINARIES2.1 Heterogeneous Architecture and Behavioral Model2.2 Power and Thermal Models2.3 Lifetime Reliability Model2.4 Deep Neural Network Architecture2.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21<br>23<br>24                                                                                                |

| <ol> <li>THERMAL AWARE LIFETIME RELIABILITY OPTIMIZATION FOR AUTOMOTIVE DISTRIBUTED COMPUTING APPLICATIONS</li> <li>Introduction</li> <li>Related Work</li> <li>Related Work</li> <li>Preliminary</li> <li>Architecture and Application Models</li> <li>Architecture and Application Models</li> <li>Ifetime Reliability Model</li> <li>Lifetime Reliability Model</li> <li>Arbitecture and Programming Approach</li> <li>Mathematical Programming Approach</li> <li>Motivation Examples</li> <li>Accurate peak temperature identification algorithm</li> <li>Accurate peak temperature identification algorithm</li> <li>A Computing Efficient Approach for MTTF Calculation</li> <li>Fast System-Level MTTF Calculation for PUs with different degrada-</li> </ol> | $\begin{array}{c} 28\\ 29\\ 32\\ 34\\ 35\\ 36\\ 37\\ 41\\ 42\\ 46\\ 50\\ 52 \end{array}$                      |

| tion rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54<br>56<br>53<br>74<br>J-<br>76<br>77                                                                        |

| 4.3 Preliminary                                                                                            | . 88  |

|------------------------------------------------------------------------------------------------------------|-------|

| 4.3.1 DNN Architecture                                                                                     | . 89  |

| 4.3.2 Temperature Impact on STT-MRAM Cell                                                                  | . 89  |

| 4.3.3 Floating-point and Fixed-point Number Representation                                                 | 92    |

| 4.3.4 Errors for Parameter Representation                                                                  | 94    |

| 4.3.5 Random Error Model                                                                                   | 95    |

| 4.4 Sensitivity Estimation                                                                                 | 95    |

| 4.4.1 Motivation                                                                                           | 95    |

| 4.4.2 Neuron-level Sensitivity Estimation                                                                  | 98    |

| 4.4.3 Regularization Impact on Sensitivity                                                                 | 100   |

| 4.5 Experimental Results                                                                                   | 102   |

| 4.5.1 Experimental Set-up                                                                                  | 102   |

| 4.5.2 Experimental Results and Discussion                                                                  | 104   |

| 4.6 Conclusion                                                                                             | . 113 |

|                                                                                                            |       |

| 5. THERMAL AWARE MAPPING OF DEEP NEURAL NETWORK NEU                                                        |       |

| RONS ON 3D MEMORY OF ECS                                                                                   |       |

| 5.1 Introduction $\ldots$ |       |

| 5.2 Related Work                                                                                           |       |

| 5.3 Preliminary                                                                                            |       |

| 5.3.1 DNN Architecture                                                                                     |       |

| 5.3.2 3D IC Architecture                                                                                   |       |

| 5.3.3 Problems Formulation                                                                                 |       |

| 5.4 Thermal Aware Mapping of Neuron Parameters on Memory Banks                                             |       |

| 5.5 Optimal Temperature Profile of the Memory Banks                                                        |       |

| 5.5.1 Convex Optimization-Based Approach                                                                   |       |

| 5.5.2 Bin-Packing and Convex Optimization-Based Heuristic                                                  |       |

| 5.6 Experimental Results                                                                                   |       |

| 5.6.1 Experimental Set-up                                                                                  |       |

| 5.6.2 Experimental Results and Discussion                                                                  |       |

| 5.7 Conclusion                                                                                             | . 144 |

| 6. CONCLUSIONS AND FUTURE WORK                                                                             | 146   |

| 6.1 Summary                                                                                                |       |

| 6.2 Future Work                                                                                            |       |

|                                                                                                            | - 10  |

| BIBLIOGRAPHY                                                                                               | 151   |

| VITA                                                                                                       | . 173 |

# LIST OF TABLES

| TAB | LE PAGE                                                                                                                                                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1 | A case study for temperature bound's effectiveness using the step-up theory                                                                                            |

| 3.2 | PU parameters for the experiment [71,118]                                                                                                                              |

| 3.3 | Benchmark parameters                                                                                                                                                   |

| 3.4 | Average CPU time                                                                                                                                                       |

| 3.5 | Average MTTF error percentage                                                                                                                                          |

| 3.6 | Results of Real-Life Benchmark                                                                                                                                         |

| 3.7 | Results of ACC Benchmark                                                                                                                                               |

| 3.8 | Results of ACC Benchmark for diff degradation rate                                                                                                                     |

| 3.9 | Results of Real-Life Benchmark for diff degradation rate                                                                                                               |

| 4.1 | Integer and decimal bits in the signed 16-bit fixed-point representation . 104                                                                                         |

| 4.2 | Parameter Distribution                                                                                                                                                 |

| 4.3 | Parameter Disturbance Distribution                                                                                                                                     |

| 5.1 | Memory Bank Size $(z)$ for DNNs $\ldots \ldots \ldots$ |

| 5.2 | LeNet-MNIST accuracy with the random temperature profile of the 4<br>memory banks                                                                                      |

| 5.3 | Conv6-Cifar10 accuracy with the random temperature profile of the 4<br>memory banks                                                                                    |

| 5.4 | ResNet20-Cifar10 accuracy with the random temperature profile of the 4 memory banks                                                                                    |

| 5.5 | DenseNet40-Cifar10 accuracy with the random temperature profile of<br>the 4 memory banks                                                                               |

| 5.6 | ResNet56-Cifar100 accuracy with the random temperature profile of the 4 memory banks                                                                                   |

| 5.7 | DenseNet40-Cifar100 accuracy with the random temperature profile of<br>the 4 memory banks                                                                              |

# LIST OF FIGURES

| FIGURE PA |                                                                                                                                                                                                                                                           | GE |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

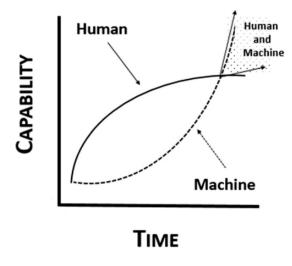

| 1.1 F     | Progress rates in the capability of humans and machines [7]. The learn-<br>ing capability of the machines increase exponentially, but the capa-<br>bility of human beings saturate with time                                                              | 3  |

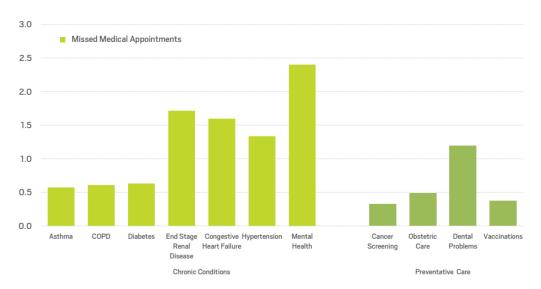

| 1.2 N     | Missed health care appointments (in million) due to lack of transporta-<br>tion for disabled persons [12].                                                                                                                                                | 4  |

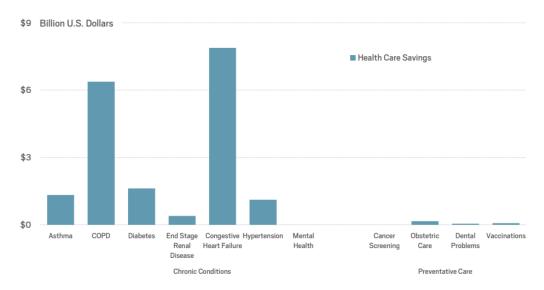

| 1.3 H     | Health care savings due to adequate transportation for elderly and dis-<br>abled persons [12]                                                                                                                                                             | 5  |

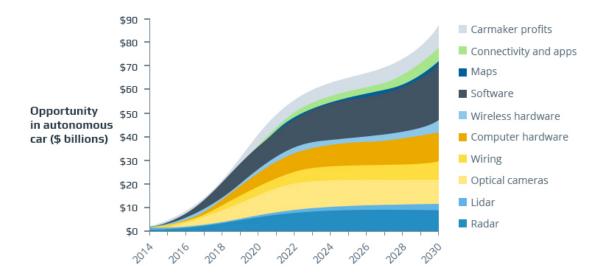

| 1.4 E     | Economical opportunity in Autonomous Cars [19]. The software has the largest portion.                                                                                                                                                                     | 6  |

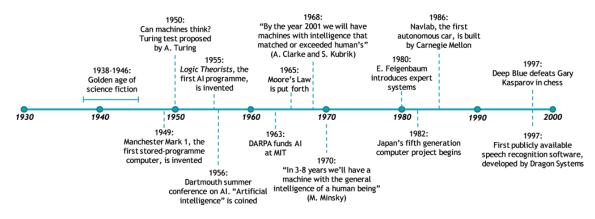

| 1.5 A     | Artificial Intelligence technology development history [22]. The first AV was built in 1986.                                                                                                                                                              | 8  |

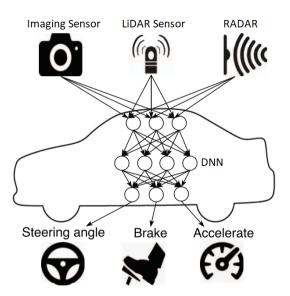

| 1.6 F     | Role of DNN to control the AV [26]. As a representative, only one LiDAR, RADAR, imaging sensor, and DNN are shown. Practically, an array of sensors and DNNs are required on the AV to accomplish all vision-related tasks.                               | 9  |

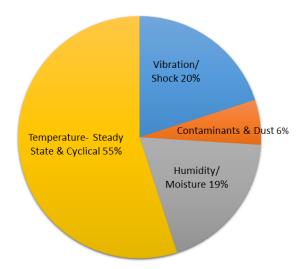

| 1.7 F     | Fault distribution in Automotive electronics [40]. 55% of failures in automotive electronics are due to the temperature, significantly higher than counterparts.                                                                                          | 11 |

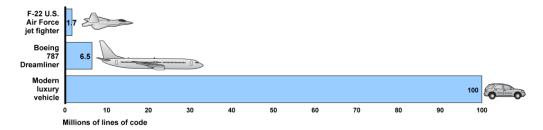

| 1.8 N     | Modern vehicle and Aircraft software size comparison [43]. Modern vehicle software is huge in size than aircraft.                                                                                                                                         | 12 |

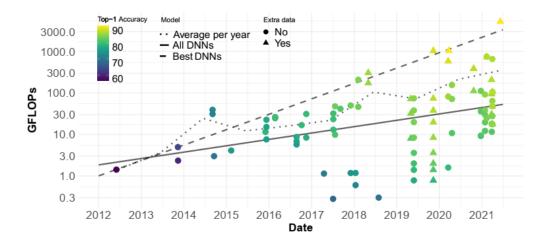

| 1.9 C     | Compute complexity (GFLOPs) over the years [44]. Y-axis is a logarithmic scale; hence we can see an exponential rise in the complexity for models with the best accuracy.                                                                                 | 12 |

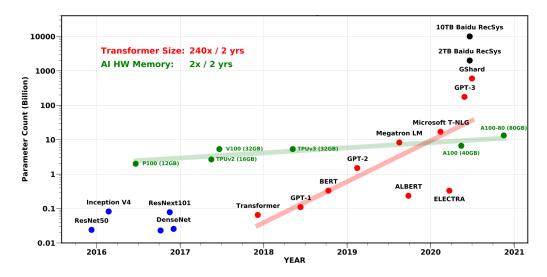

| 1.10 (    | Growth pattern of AI accelerator memory size and number of param-<br>eters in neural network models [1]. The parameter count increased<br>by $240 \times / 2$ years, whereas the accelerator memory size is linearly<br>increased as $2 \times / 2$ years | 13 |

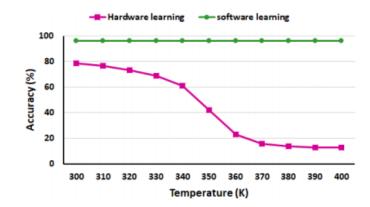

| 1.11 Т    | The temperature effect on the classification accuracy of ReRAM-based accelerator [49]. The accuracy drops with the temperature                                                                                                                            | 14 |

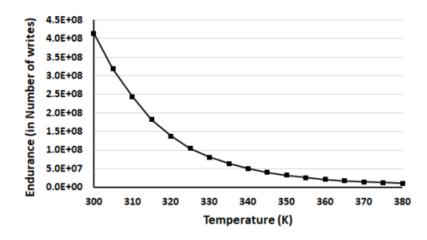

| 1.12 Т    | Irade-off between endurance and temperature of ReRAM [51]. The endurance of ReRAM cell drops by $0.026 \times$ as temperature increases from $300 - 380^{\circ}K$ .                                                                                       | 14 |

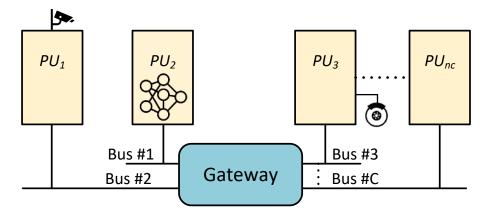

| 2.1 H     | Heterogeneous ECS Architecture. Different processing units communi-<br>cate through a network of buses interconnected by the central Gateway.                                                                                                             | 20 |

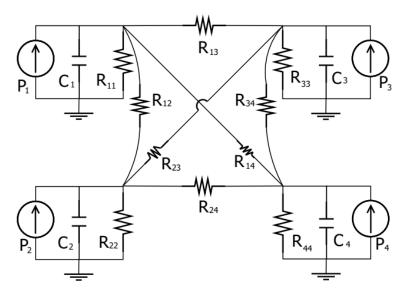

| 2.2 | Thermal model for 4-core processing unit [74]. Each processing core is<br>represented by the equivalent power source, thermal resistance, and<br>thermal capacitance.                                                                           | 23 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

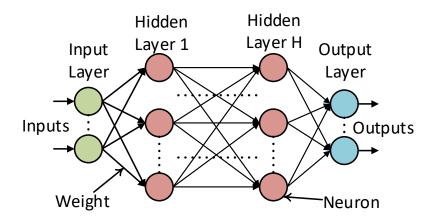

| 2.3 | Feed Forward Neural Network containing input layer, multiple hidden layers, and an output layer.                                                                                                                                                | 25 |

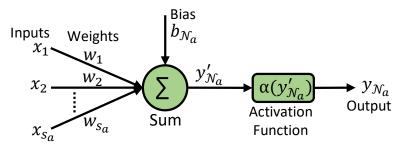

| 2.4 | Structure of the Neuron. All inputs of the neuron are associated with trainable network parameters                                                                                                                                              | 25 |

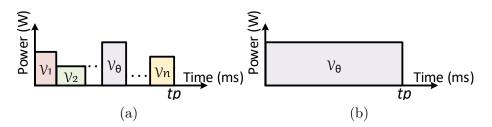

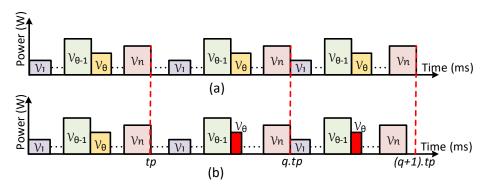

| 3.1 | (a) The WCET schedule with period $t_p$ . (b) A hypothetical schedule with only task $\mathcal{V}_{\theta}$ for the entire period $t_p$                                                                                                         | 39 |

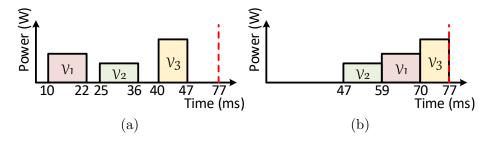

| 3.2 | An example of the step-up schedule. (a) Original schedule. (b) All tasks in the given schedule are arranged in the increasing order of their power.                                                                                             | 42 |

| 3.3 | A motivational example. (a) Two periods of the step-up schedule of two tasks. (b) The modified schedule after the execution time of the task $\mathcal{V}_1$ is zero in the second period.                                                      | 43 |

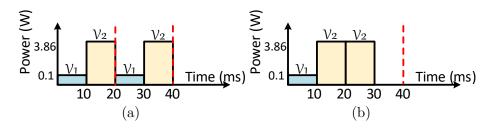

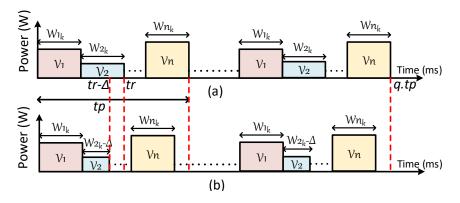

| 3.4 | (a) The WCET schedule with an ending temperature of $T_m(q \cdot t_p)$ in the stable status. (b) The schedule with a varied execution time with an ending temperature of $T(q \cdot t_p)$ in the stable status.                                 | 46 |

| 3.5 | (a) The WCET schedule. (b) The schedule with a varied execution time of tasks $\mathcal{V}_{\theta}$ in a stable state                                                                                                                          | 49 |

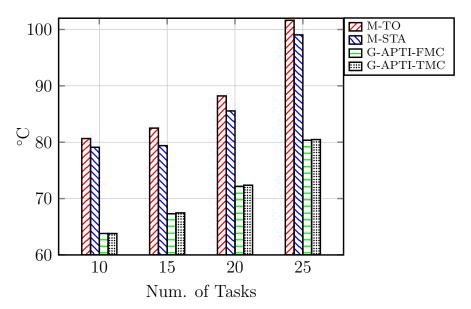

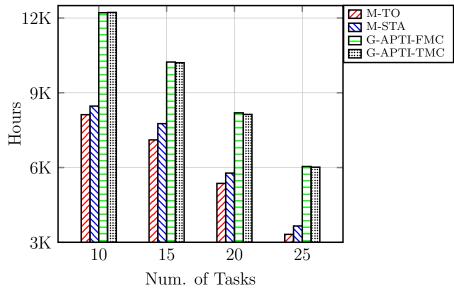

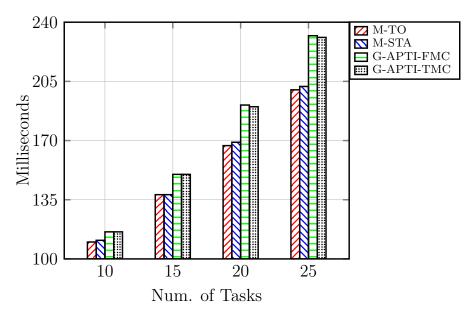

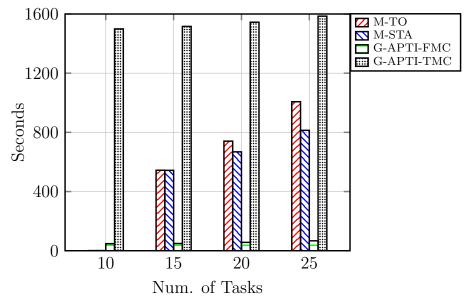

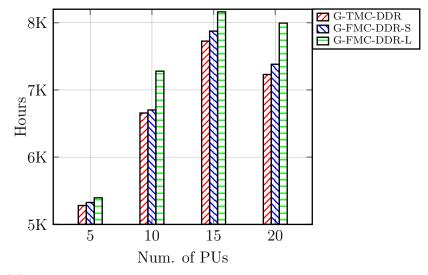

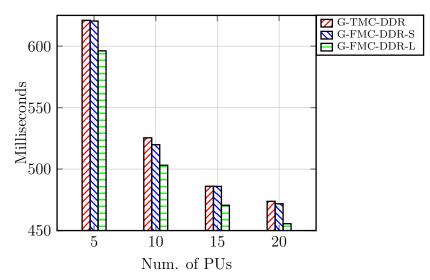

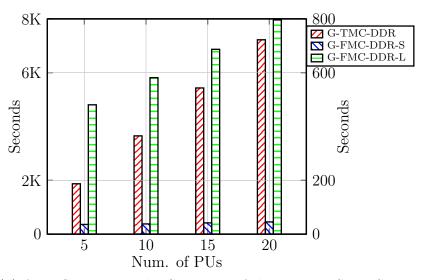

| 3.6 | Experimental results for 3-Processing Unit system                                                                                                                                                                                               | 64 |

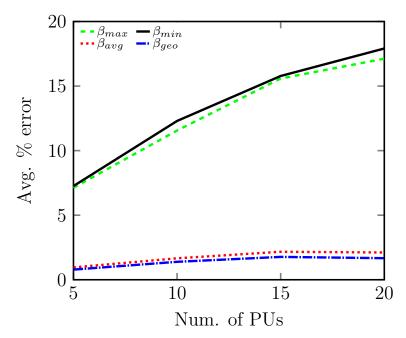

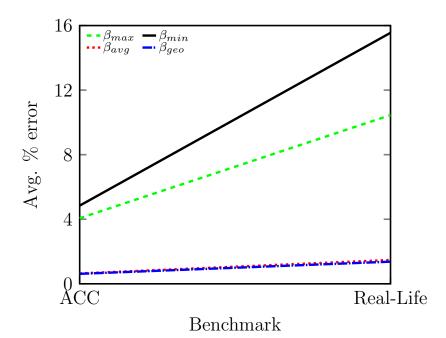

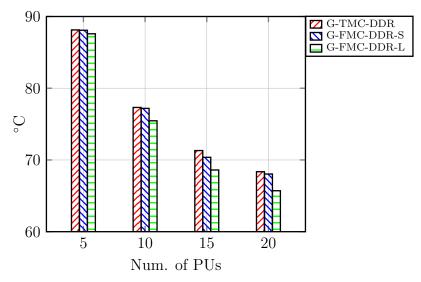

| 3.7 | Average error percentage                                                                                                                                                                                                                        | 70 |

| 3.8 | Experimental results for 100-Tasks system                                                                                                                                                                                                       | 71 |

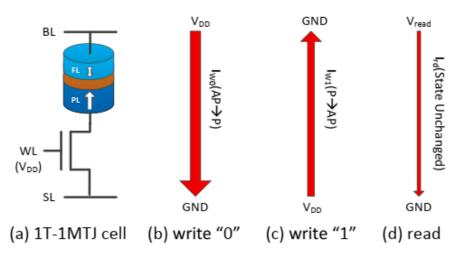

| 4.1 | STT-MRAM cell with read-write current directions [134]                                                                                                                                                                                          | 90 |

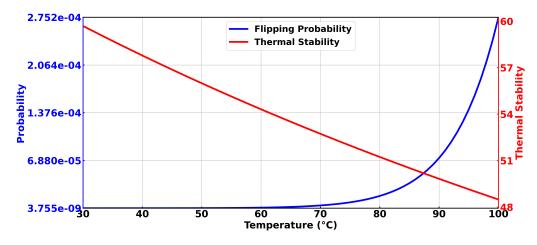

| 4.2 | Temperature impact on STT-MRAM's Thermal Stability and Flipping<br>Probability. As the temperature rises, there is a gradual decrease in<br>the thermal stability, and flipping probability exponentially increases.                            | 92 |

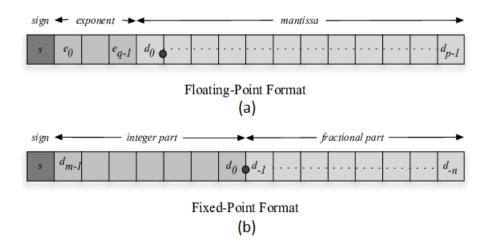

| 4.3 | Fixed-point and floating-point number representation.                                                                                                                                                                                           | 93 |

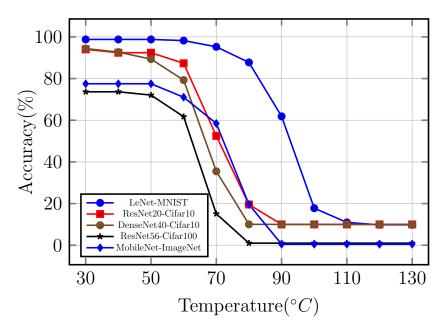

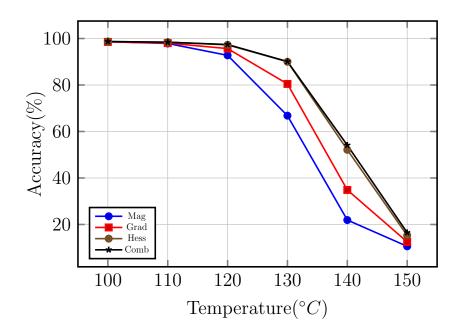

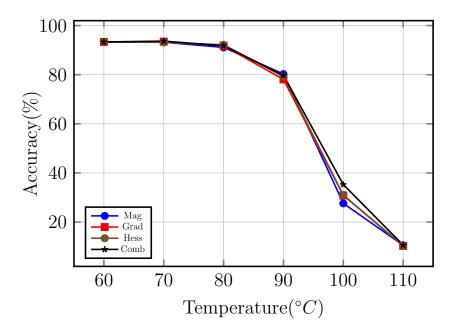

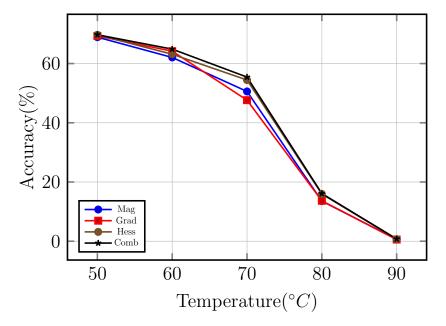

| 4.4 | Effect of temperature on classification accuracy for parameters stored<br>as a single-precision floating-point representation. The classification<br>accuracy of all the DNNs under consideration drops sharply with<br>increasing temperature. | 96 |

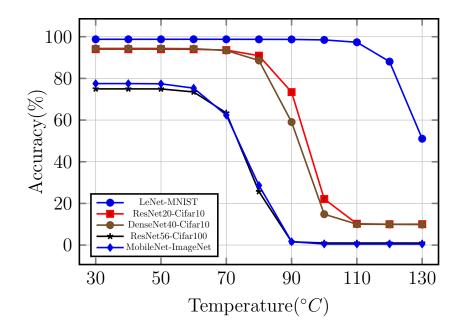

| 4.5 | Effect of temperature on classification accuracy for parameters stored<br>as a 16-bit fixed-point representation. The classification accuracy<br>of all the DNNs under consideration drops sharply with increasing<br>temperature.              | 97 |

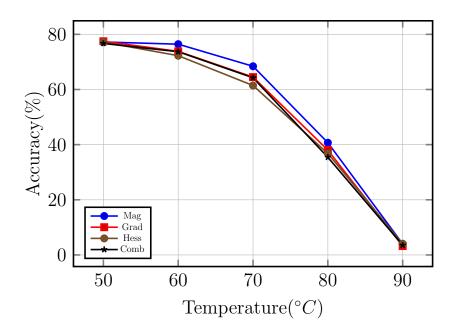

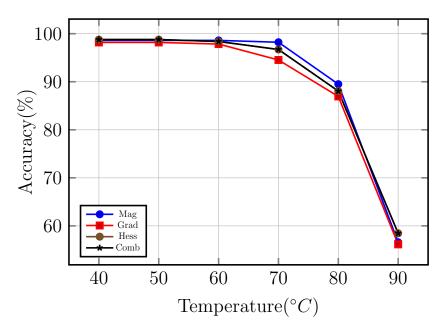

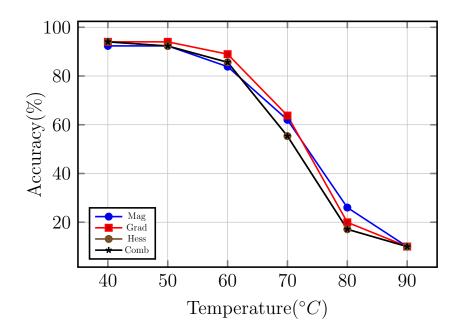

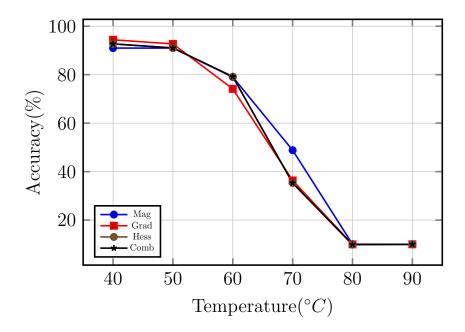

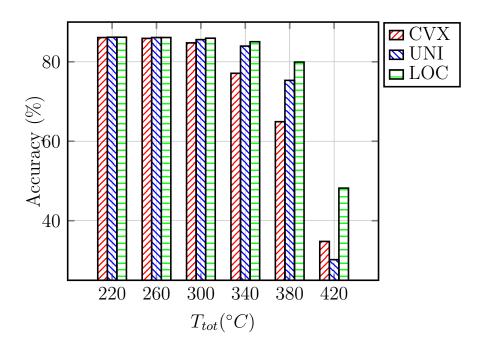

| 4.6  | Accuracy with the protection of top-5% sensitive parameters for LeNet-<br>MNIST                                                                                     | . 105 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.7  | Accuracy with protecting top-5% sensitive parameters for ResNet20-<br>Cifar10                                                                                       | . 105 |

| 4.8  | Accuracy with protecting top-5% sensitive parameters for ResNet56-<br>Cifar100                                                                                      | . 106 |

| 4.9  | Accuracy with protecting top-5% sensitive parameters for DenseNet40-<br>Cifar10.                                                                                    | . 106 |

| 4.10 | Accuracy with protecting top-5% sensitive parameters for MobileNet-<br>ImageNet                                                                                     | . 107 |

| 4.11 | Accuracy with protecting top-5% sensitive parameters for LeNet-MNIST using single-precision floating-point representation.                                          | . 110 |

| 4.12 | Accuracy with protecting top-5% sensitive parameters for ResNet20-<br>Cifar10 using single-precision floating-point representation                                  | . 111 |

| 4.13 | Accuracy with protecting top-5% sensitive parameters for DenseNet40-<br>Cifar10 using single-precision floating-point representation                                | . 111 |

| 4.14 |                                                                                                                                                                     | . 112 |

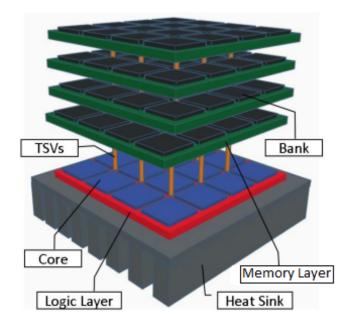

| 5.1  | 3D IC Architecture [194]. The logic layer with processing cores is at the bottom, and memory banks are on the upper layers.                                         | . 122 |

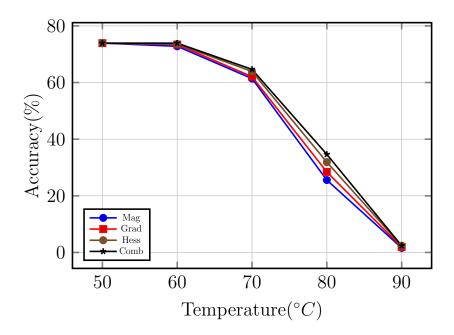

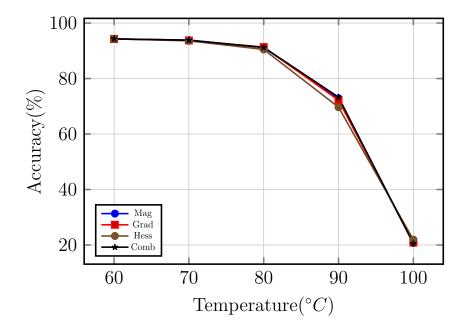

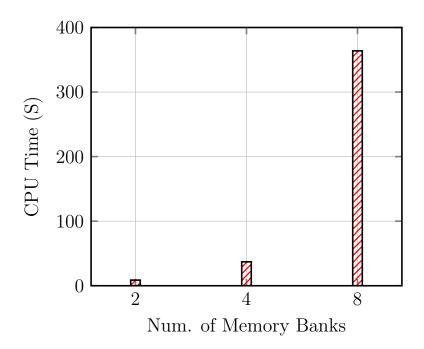

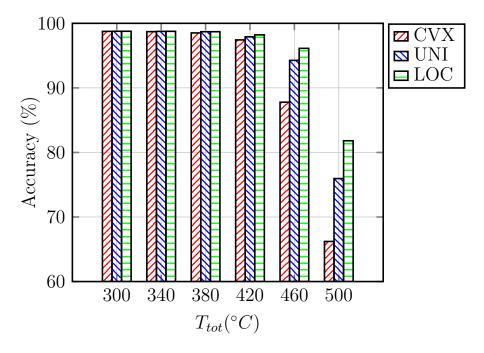

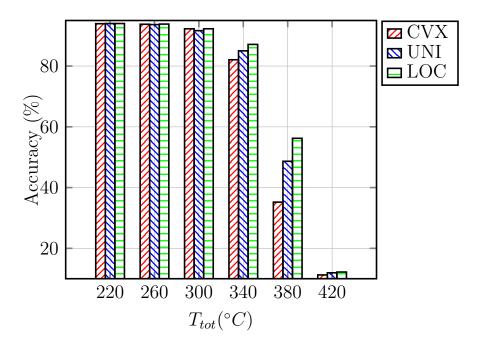

| 5.2  | Computational cost of the Convex Optimization Approach for ResNet20-<br>Cifar10. The computational cost increases exponentially with the<br>number of memory banks. | . 139 |

| 5.3  | Accuracy of LeNet-MNIST for increasing values of the total temperature of the memory system.                                                                        | . 141 |

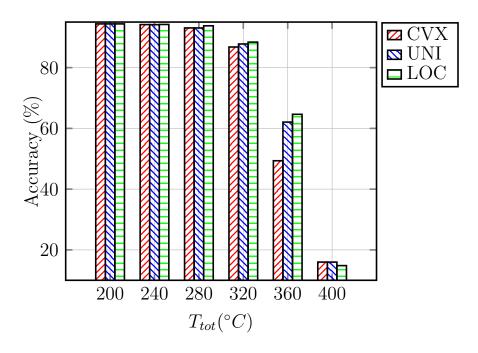

| 5.4  | Accuracy of Conv6-Cifar10 for increasing values of the total temperature of the memory system.                                                                      | . 142 |

| 5.5  | Accuracy of ResNet20-Cifar10 for increasing values of the total temper-<br>ature of the memory system.                                                              | . 142 |

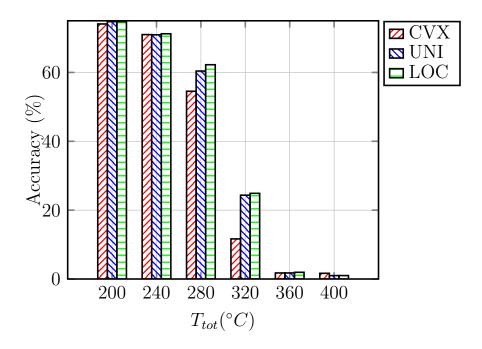

| 5.6  | Accuracy of DenseNet40-Cifar10 for increasing values of the total temperature of the memory system                                                                  | . 143 |

| 5.7  | Accuracy of DenseNet40-Cifar100 for increasing values of the total tem-<br>perature of the memory system                                                            | . 143 |

| 5.8  | Accuracy of ResNet56-Cifar100 for increasing values of the total tem-<br>perature of the memory system                                                              | . 144 |

#### CHAPTER 1

#### INTRODUCTION

Self-driving cars, also known as autonomous vehicles (AVs), have the potential to transform transportation mobility and safety if they are mass-produced. The advancements in the automotive transportation area have been substantial over the years, with the most notable being the one related to autonomous vehicles, which considers numerous factors such as performance, comfort, low emissions, and, most important, safety. With the emergence of AVs, the electronic control system (ECS) design has become very complex, which plays a crucial role in reliable vehicle operation.

As a critical enabling technology, Artificial Intelligence (AI) provides human brain-like functionality to drive the AVs on the road, simultaneously presenting safety and reliability challenges. The accuracy of AI methods, such as artificial deep neural networks (DNNs), mainly depends on the data from various sensors installed in the AV, and the size of DNNs used for processing sensor data is growing exponentially [1], demanding massive compute and storage resources. Besides the significant heat generated from the computing devices, which can lead to high temperature and large thermal gradients across IC chips and thus deteriorate the lifetime and safety conditions of ECS, AVs must be operated reliably under extreme environmental conditions, which make a thermal impact a critical issue in the design of ECS for AVs. Therefore, the substantially increased computation and memory capability demanded by AV technology have presented tremendous challenges in the ECS design optimization to satisfy rapidly elevated latency, throughput, reliability, and other safety-critical requirements [2].

In this chapter, we first discuss the current status and future of AVs and their potentially great social and technological impact. Further, we discuss the current artificial intelligence technique and its role in AV design. Later, we discuss the thermal challenges posed by the evolving data-centric AI-based vehicle technology. At last, we present our research problem with contributions.

## 1.1 About the Autonomous Vehicle Technology

Autonomous Vehicle Technology is a promising technology that will fundamentally transform transportation and mobility with a range of great social and economic benefits. Specifically, lowering the cost associated with traffic accidents, reducing fuel consumption and carbon emissions, and enabling far greater access to mobility for numerous elderly, disabled adults, and children will bring substantial potential market opportunities and has thus attracted enormous interest from numerous industrial sectors and companies.

Autonomous vehicle technology can significantly minimize road accidents caused due to human mistakes, which can bring substantial social benefits. According to international data, roadway accidents are among the top ten causes of worldwide mortality [3], and human errors are the most common cause of accidents [4]. According to the U.S. Department of Transportation, human error and negligence account for 94% of all road accidents, which cause approximately 35,000 deaths in the United States per year [5]. While at the global level, 1.35 million deaths are reported annually, and it is estimated that every year 20 to 50 million people suffer injuries [6]. As shown in Figure 1.1, over the period of recent industrialization, it is believed that machines can outperform the capabilities of human beings if trained with enough data. Therefore, AVs have the promising ability to eliminate the majority of traffic accidents by perceiving the road conditions better than human beings. Besides minimizing road accidents, AVs can help cut down the expenses caused due to crashes.

Figure 1.1: Progress rates in the capability of humans and machines [7]. The learning capability of the machines increase exponentially, but the capability of human beings saturate with time.

For example, in 2010, motor vehicle accidents cost the economy \$242 billion, which includes \$57.6 billion in lost workplace efficiency and \$594 billion in impaired life quality because of severe injuries [5]. Moreover, worldwide, costing at least 90% of global GDP (gross domestic product) [6].

AV technology can be a boon for an eco-friendly revolution. AVs can help to improve the stream of traffic and minimize traffic congestion. In 2014, Americans wasted approximately 6.9 billion hours in traffic, limiting work time while increasing fuel costs and pollution [5]. AVs might free up to 50 minutes of drive every day [8], significantly reducing emissions. Moreover, people can work during the commute in the AVs, which can save \$1.3 trillion in the US and \$5.6 trillion in the global economy [9]. AVs would help to solve the parking problem as the shared autonomous taxis can minimize the parking space requirement by 80% in dense cities and reduce the emission by 5-11% in search of the parking space. Similarly, shared autonomous vehicles are anticipated to be more energy efficient with a 35% emission reduction

Figure 1.2: Missed health care appointments (in million) due to lack of transportation for disabled persons [12].

[10]. AVs can minimize traffic congestion by choosing to cruise on the streets where they can travel the slowest [11].

Millions of elderly adults, disabled, and children may have new mobility alternatives because of AVs. In the United States, there are 49 million people over the age of 65 and 53 million people with a disability [5]. In many parts of the world, the ability to drive is required for employment or independent life. Hence, a large portion of the demographics could benefit from independence due to AV technology. More important, as shown in Figure 1.2, due to a lack of transportation for disabled citizens, approx. 11 million medical appointments are missed annually. AV technology is beneficial for such elderly and disabled people, and it has the potential to save billions due to medical care at the right time, as shown in Figure 1.3.

Due to its potentially high social and market impacts, the automotive industry is keenly focusing on AV development. Google's Waymo has already begun testing a completely driverless taxicab service in the Phoenix suburbs of Arizona [13]. Tesla has offered an Autopilot driving system, which is mainly suitable for highway

Figure 1.3: Health care savings due to adequate transportation for elderly and disabled persons [12].

driving. Other top auto giants, like, General Motors (GM) and Ford, have a similar capability in their newly launched vehicles with additional fully-automated lanechanging systems only in the GM models. While, Mercedes and Honda are cruising ahead in the technology innovation by introducing semi-autonomy, in which the drivers have to control the vehicle only in aberrant situations [14]. In the meantime, Argo AI is focusing on developing a fully autonomous driving system that can be integrated with Ford and Volkswagen models [15]. Oxbotica is collaborating with ZF, a German vehicle systems company, over the next five years to make the self-driving shuttle a true mainstay for European cities [16]. Recently, a tech giant, Apple, announced that it would launch fully autonomous cars within the next four years, making this race of innovation more competitive.

It is estimated that by 2025, automated mobility could be a \$120 billion industry in the US [17]. Similarly, it is predicted that from 2018 through 2030, the market for autonomous vehicles will expand dramatically. By 2030, fully automated cars are estimated to generate \$13.7 billion in revenue, and one out of every ten automo-

Figure 1.4: Economical opportunity in Autonomous Cars [19]. The software has the largest portion.

biles will be self-driving [18]. It is believed that the software in AVs would yield a significant opportunity among all the design variables, as shown in Figure 1.4. By 2035, it is predicted that the number of autonomous vehicles will increase by 75%, resulting in a \$71 billion economic impact on the automotive sector by 2030, with a global market of 44 million vehicles [6].

Along with the development in AV technology, global demand for Advanced Driver Assistance Systems (ADAS) is expected to propel the automotive semiconductors and sensors industry forward. When robots take over control, these systems will be critical in assisting AI-powered driverless vehicles in navigating and detecting impediments on the road. As the AV technology heavily depends on the sensors deployed in the vehicle, eventually, the sensor market is projected to expand from \$3 billion to \$35 billion by 2030 [20].

Altogether, the AV technology can significantly mitigate human errors while driving, resulting in fewer fatalities and corresponding reduced expenses; assist in navigating the traffic flow smoothly, saving emissions; provide alternative mobility for children, elderly and disabled people. Such transforming capabilities have drawn tremendous investment into AV development by the automotive industry.

# 1.2 Artificial Intelligence Technology for Autonomous Ve-

# hicle Design

While AVs represent an enormous market opportunity, critical challenges must be overcome to fulfill their great social and economic benefits. As an underpinning technology, the autonomous vehicle industry has invested significant resources in researching advanced AI technology. As of today, there is no automotive company with complete autonomy in its matured commercial vehicle products to offer to the customers; instead, they need human vigilance in the loop. The most difficult challenge for those working in the self-driving technology industry is ensuring that vehicles can operate safely, reliably, and efficiently in complex and unexpected human-animal contexts.

The roots of artificial intelligence can be found in the late 1940s. As shown in Figure 1.5, the mathematical and logical theories of AI were evolved up to 1960, and the research was propelled after the Defense Advanced Research Projects Agency (DARPA) funded several institutions [21]. In 1986, the Navlab from Carnegie Mellon University developed the first autonomous van, and a large community of researchers was intrigued after the Deep Blue chess machine of IBM defeated the world champion in 1997. In recent times, AI research gained momentum due to the emergence of high-performance computing platforms and extensive storage, which were major bottlenecks in the previous century [22].

Figure 1.5: Artificial Intelligence technology development history [22]. The first AV was built in 1986.

The artificial intelligence paradigm deals with making machines smart. Artificial intelligence can be defined as an intelligent behavior in which a computer achieves tasks using a set of principles to tackle a given problem. Machine learning is a type of artificial intelligence that enables computers to learn and build intelligence based on their prior experiences. In contrast, deep learning is a category of machine learning that is inspired by the information processing mechanism of the human brain. It uses complex deep neural networks to extricate comprehensive attributes as they learn and assess their training data. However, machine learning differs significantly from deep learning because it requires input data attributes to be labeled manually using more rigid rulesets [23]. In contrast, deep learning can automatically identify the features to be utilized for classification in unsupervised exercises [24].

Deep learning has favored automotive companies to accelerate AV development as they rely on deep neural networks (DNNs) for more efficient sensor data processing. The LiDAR (Light Detection And Ranging), Imaging, and RADAR (Radio Detection And Ranging) sensors provide the surrounding environment's snapshot while traveling on the road, as shown in Figure 1.6. DNNs utilize all these sensors' data for object detection, object recognition, image classification, scene segmentation, driving lane detection, etc., vision-related tasks, which are based on the human

Figure 1.6: Role of DNN to control the AV [26]. As a representative, only one LiDAR, RADAR, imaging sensor, and DNN are shown. Practically, an array of sensors and DNNs are required on the AV to accomplish all vision-related tasks.

brain analogy [25]. It is required to build multiple DNNs for safe autonomous driving, each dedicated to a unique task. The signals generated by each DNN must be processed in real-time to drive the car, which is accomplished by a high-performance computing platform involving an array of CPUs and neural network accelerators. This network of processing units (PUs) commands the actuators, as shown in Figure 1.6, to control the steering angle, brake pedal, and speed-accelerator to drive the car on the road without human assistance.

The AV technology in the current state is not a safe and reliable mobility option as there have been several crashes and fatality incidents reported [27]. For example, in 2016, Google's autonomous Waymo car crashed with another transit vehicle, and several faults were detected in the safety-critical components like steering and brakes [28]. Similarly, Tesla's autonomous cars have been found in several accidents. In 2018, Uber's self-driving car accident killed a pedestrian, and the company has previously been engaged in 37 accidents. In another incident, Google's self-driving Waymo taxi muddled on the street and went off on its own [29]. There are several malicious security attacks on the AV communication [19, 30, 31] and deliberate attacks on the perception systems [32, 33], raising the safety and reliability concerns for end-users [34, 35], which is beyond the scope of this dissertation.

The human brain-like functionality imitated by one of AI techniques, i.e., deep learning, assist in driving the car autonomously on the road. However, currently, AVs are not entirely reliable, and thermal impact is one of the major factors that threaten its safety and reliability, especially with the significant computing and memory requirement of the DNN execution.

## **1.3** Thermal Challenges for Autonomous Vehicles

Extreme environmental conditions and growing demand for computing and memory resources for highly accurate control decisions of the DNNs in the AVs bring severe thermal impact to the performance and lifetime reliability of the PUs as well as memory.

Thermal issues are one of the major sources of faults for automotive ECS. The electronics in modern automotives are more complicated than ever due to a combination of safety, luxury, and entertainment features. With the addition of more electronics for AI computation and memory, vehicles will inevitably emit more heat, resulting in unexpected thermal issues. According to one study, the temperature is the leading cause of failures in automotive electronics, as shown in Figure 1.7. For example, high temperatures impact the LiDAR sensors by causing deviation in the measured distance [36], imaging sensors' quality, and smart headlights' performance deteriorate [37]. While, the ambient temperature of the automotive PUs may vary

Figure 1.7: Fault distribution in Automotive electronics [40]. 55% of failures in automotive electronics are due to the temperature, significantly higher than counterparts.

significantly, as high as  $90 - 155^{\circ}C$  [38], increasing electronics failure probabilities and deteriorating the lifetime reliability of the ECS rapidly [39].

The complexity in AI computation and limited memory capacity introduces thermal challenges in AV design. The AVs are a highly complex system as they interact with unpredictable dynamic situations on the road, like other motor vehicles, motorbikes, cyclists, pedestrians, and wildlife. As a result, the software for vehicles is much larger, even  $15\times$  greater than that necessary for the aircraft, as shown in Figure 1.8. Besides, AVs process roughly 3 GB/s and 40 GB/s data at lower and higher levels of autonomy, respectively, generated by various sensors [41]. Moreover, in an effort to improve the prediction accuracy of the DNNs, there has been exponential growth in the Giga floating-point operations per second (GFLOPs), indicating a dramatic change in the computational complexity, as shown in Figure 1.9. Similarly, the number of parameters in different DNNs has increased exponentially, as shown in Figure 1.10. Contrarily, the memory space of the AI accelerators has scaled linearly, as observed in the figure. Altogether, soaring computational

Figure 1.8: Modern vehicle and Aircraft software size comparison [43]. Modern vehicle software is huge in size than aircraft.

Figure 1.9: Compute complexity (GFLOPs) over the years [44]. Y-axis is a logarithmic scale; hence we can see an exponential rise in the complexity for models with the best accuracy.

complexity, storage requirements, and harsh environmental conditions increase the operating temperature along with thermal gradients across the PUs, which can be severe across 3D ICs [42].

High temperatures impact the performance of the PUs and memory of the ECS platform. When the temperature exceeds a certain threshold, it may cause PUs to reduce the operating speed or shut off automatically for self-protection purposes during the run-time [45], which can affect the performance of mission-critical tasks causing catastrophic events for AVs. Similarly, the performance of the conventional memory, i.e., Dynamic random-access memory (DRAM), degrades with the temper-ature due to an increase in memory refresh rate [46]. Whereas emerging non-volatile

Figure 1.10: Growth pattern of AI accelerator memory size and number of parameters in neural network models [1]. The parameter count increased by  $240 \times / 2$  years, whereas the accelerator memory size is linearly increased as  $2 \times / 2$  years.

memories, such as Resistive RAM (ReRAM) and Spin-Transfer Torque Magnetoresistive RAM (STT-MRAM), eliminate the need for refreshing along with high density to alleviate the memory bottleneck problem, low power, and improved read latency [47]. In particular, for STT-MRAM, read access latency and read power consumption are reduced by 8.4% and 66.2%, respectively, compared to typical DRAM [48]. However, emerging non-volatile memories suffer from temperatureinduced random errors. For example, the classification accuracy of the AI applications executing on ReRAM-based accelerators drops at high temperatures due to deviation in the cell conductances, as shown in Figure 1.11. Similarly, the switching probability of the STT-MRAM cells increases with the temperature, adversely impacting the classification accuracy of the AI applications, as later observed in the motivation example in Chapter 4. Therefore, it is critical that the run-time temperature of the underlying computing infrastructure for ECS should be well controlled.

The reliability challenges in the PUs and memory exacerbate more due to thermal impact. The  $10-15^{\circ}C$  rise in the temperature accelerates aging rapidly and reduces

Figure 1.11: The temperature effect on the classification accuracy of ReRAM-based accelerator [49]. The accuracy drops with the temperature.

Figure 1.12: Trade-off between endurance and temperature of ReRAM [51]. The endurance of ReRAM cell drops by  $0.026 \times$  as temperature increases from  $300 - 380^{\circ}K$ .

the processing unit's lifetime by half [50]. On the other hand, for emerging memory, i.e., ReRAM, the latency improves with increasing temperatures, but it degrades the endurance of the cells, as shown in Figure 1.12. As the automotive ECS is subjected to high thermal conditions, the operating temperature of the PUs and memory should be optimized to enhance lifetime reliability.

Providing only mechanical cooling for ECS design in AVs can not solve the thermal problems. The emerging 3D ICs are a promising alternative for improving the performance of AI applications [52–54], but they suffer from high thermal gradients [42]. The existing active and passive cooling techniques [55, 56] utilized in modern automotives are ineffective in managing the thermal problems of 3D ICs. Liquid cooling is suggested in the literature to control the thermal problems for 3D ICs [42,57,58], but it does not guarantee reliability and adequate functionality [59]. Moreover, the mechanical design of the cooling system requires thermal characteristics and impacts of the ECS for better design trade-offs. Furthermore, a pessimistic design of the cooling system can be extremely costly and infeasible with its large operating temperature range. Hence, thermal-aware resource management and/or protection of delicate neural network parameters across ECS platform can help to minimize the temperature impact along with mechanical cooling solutions.

The elevated thermal profile of the PUs and memory due to the harsh environment of AVs and the complexity of computations degrades their performance and lifetime reliability. Simultaneously deteriorating the AI applications' accuracy can lead to catastrophic events in the AVs.

## **1.4** Research Problem and Our Contributions

ECS design for AVs is a very complex problem. It requires consideration of heterogeneity of the PUs and vehicle control applications, along with strict real-time latency requirements, throughput, power, safety, and reliability constraints. The resource management and workload distribution play a crucial role in achieving high performance, power efficiency, thermal conditions, and hardware utilization for the applications running on the PUs, which will lead to higher system-wide lifetime reliability. As such, for a given automotive application, we seek to design and develop efficient and effective resource management strategies on the heterogeneous distributed ECS architecture such that design constraints like timing, power consumption, peak temperature can be satisfied, and other criteria such as system-level lifetime reliability, Quality of Service (QoS), etc., can be optimized.

The major contributions of this dissertation are summarized as follows:

- 1. We study the problem of mapping periodic distributed automotive applications on a heterogeneous architecture to meet the temperature constraint, minimize the latency and temperature-induced system-level reliability degradation. The key challenges are effective and compute efficient temperature bounding as well as lifetime reliability estimation frameworks. In our approach, first, we propose a mathematical programming model to bound the peak temperature for the periodic automotive applications using an existing method [60], which is found to be a very pessimistic bound. Second, we prove a series of lemmas and theorems to find the effective and time-efficient framework to bound the peak temperature by considering the variance of vehicle applications' execution time. Next, we propose two compute-efficient system-level lifetime reliability analytical methods. In the first method, all the PUs of ECS are assumed to have the same degradation rate, while, in another method, we consider different degradation rates. We use a genetic algorithm to minimize the application latency, peak temperature estimated by the proposed framework, and maximize the system-level reliability using proposed models. The developed peak temperature algorithm is more accurate by  $17-40^{\circ}C$  than the existing method [60, 61] for practical benchmarks. Based on both synthesized test cases and practical benchmarks, the experimental results show that the proposed system-level reliability estimation approach can achieve  $54 \times$  to  $110 \times$ speed-up over the state-of-the-art approach [62] for design space exploration.

- 2. The temperature impacts to ECS can be substantial due to environmental conditions and the growing complexity of the PUs along with memory re-

quirements, which threatens to degrade the DNN classification accuracy significantly and even cause an AV to fail catastrophically. The challenge is how to quantify the thermal impact in a quantitative way for DNNs, which may demonstrate drastically different architectures and meta parameters. First, using the emerging memory, i.e., STT-MRAM, as a case study, we find that when DNNs are stored in it, their baseline accuracy can drop to as low as below 10% when the temperature rises above  $110^{\circ}C$ , as a result of data bit flipping error in memory due to temperature variation. Then, we develop an analytical method to quantify the sensitivity of neurons under thermal impact. We validate the sensitivity analysis with standard datasets and DNNs. Our experiment results for LeNet, ResNet20, DenseNet40, and ResNet56 improve the accuracy by 0.5-4.2% than the state-of-the-art sensitivity method [63]. Further, we present the limitation of the proposed sensitivity framework when the error is large for other DNNs, such as the MobileNet.

3. We study the problem of mapping neuron parameters to memory systems when incorporating thermal impacts in designing DNN applications for ECS. We first study the thermal aware mapping problem of DNN parameters to memory banks with different temperature profiles. Based on the quantitative sensitivity metric for DNN neurons we developed before, we develop a bin-packing-based approach to map neuron parameters to memory banks with different temperatures with the goal to maximize the DNN prediction accuracy. The experiment results demonstrate that the thermal aware mapping improves the accuracy by 0.18-47.91% than the thermal ignorant approach for a range of common DNNs, such as LeNet, Conv6, ResNet20, DenseNet40, and ResNet56 networks. We also study the problem of how to identify the optimal temperature profiles in terms of maximizing the prediction accuracy when im-

plementing DNN applications with the same energy consumption. Here, a key challenge is the computational complexity of the mapping problem due to its NP-hard nature. In our approach, we develop the method by combining the traditional bin packing algorithm with convex optimization. From experiment results, we find that the developed method performs well at low temperatures, while it shows inconsistencies at high temperatures due to large discrepancies resulting from the sensitivity analysis. Furthermore, we also find that the traditional approach to having temperature distributed uniformly across the memory system does not seem to be an optimal solution when mapping neuron parameters to memory.

## 1.5 Structure of the Dissertation

The rest of this dissertation is organized as follows. In Chapter 2, we introduce several pertinent preliminary models used in this dissertation. We present a mathematical programming method and another framework to bound the peak temperature for periodic automotive applications in Chapter 3. This chapter also presents two system-level lifetime reliability methods for ECS. In Chapter 4, we present the neuron-level sensitivity analysis method along with its limitation. We present the importance of thermal awareness while mapping DNN on memory banks and present a convex optimization-based heuristic to find the optimal temperature profile of the memory banks to maximize the AI application classification accuracies in Chapter 5. Finally, in Chapter 6, we discuss the conclusions of this dissertation and present possible future works.

#### CHAPTER 2

#### PRELIMINARIES

This chapter covers the background and pertinent preliminaries of our research. We first introduce the heterogeneous architecture of the ECS and behavioral model of automotive applications. Then, we introduce power and thermal models in detail. Afterward, we present the lifetime reliability model used in this research. At last, we introduce the deep neural network architecture.

#### 2.1 Heterogeneous Architecture and Behavioral Model

In this dissertation, we assume integrating multiple processing units (PUs) as an ECS, which can be Central Processing Units (CPUs), Graphical Processing Units (GPUs), Field Programmable Gate Arrays, and Processing-In-Memory (PIM) accelerators. The safety-critical automotive applications will be executed on the heterogeneous distributed architecture of the ECS.

We assume an ECS consists  $n_c$  heterogeneous PUs interconnected by a network of C buses through a central gateway [64,65] as  $\mathbf{PU} = \{PU_1, PU_2, ..., PU_{n_c}\}$ , as shown in Figure 2.1. Each PU can be interfaced with various sensors and actuators required for vehicle control operations. For example, the imaging sensor interfaced with  $PU_1$ scans the vehicle surrounding periodically. The captured images are sent to  $PU_2$ through a communication bus to classify the objects from captured images, and the brake control signal can be sent to  $PU_3$  if required in real-time [66]. The ambient temperature of the PU is a cumulative effect of the environmental temperature and the surrounding electronics/mechanical devices heat transfer. We assume different ambient temperatures for each PU,  $\mathbf{T}_{amb} = \{T_{amb_1}, T_{amb_2}, ..., T_{amb_{n_c}}\}$ , as the PUs

Figure 2.1: Heterogeneous ECS Architecture. Different processing units communicate through a network of buses interconnected by the central Gateway.

have different ambient temperatures according to their mounting location in the vehicle [38].

The automotive tasks follow sequential behavior, where the current task execution depends on the data from the completion of the predecessor task. Hence, we use Directed Acyclic Graph (DAG),  $\mathcal{G} = \{\mathcal{V}, \mathcal{E}\}$  to model the automotive applications, which will be mapped on the heterogeneous ECS architecture. We assume that the node-set  $\mathcal{V}$  consists of total  $n_v$  nodes for sensing/control tasks in an ECS as  $\mathcal{V} = \{\mathcal{V}_1, \mathcal{V}_2, ..., \mathcal{V}_{n_v}\}$ . Each task may require different computation times due to the heterogeneity of the PUs. Therefore, we construct a 2-D matrix for worst-case execution time (WCET) of the task set on different PUs as,

$$\mathbf{W}_{n_v \times n_c} = \{ w_{ik}, i = 1, ..., n_v; \ k = 1, ..., n_c \},$$

(2.1)

where  $w_{ik}$  represents the worst-case execution time of the *i*-th task  $(\mathcal{V}_i)$  executed on the *k*-th PU  $(PU_k)$ . We assume that the overhead for administering task executions can be reckoned by calibrating each task's execution times, and the WCET of the tasks is not affected by the thermal profile. The edge set  $\mathcal{E} = \{e_{ij}, \text{ with } \mathcal{V}_i, \mathcal{V}_j \in \mathcal{V}\}$ represents the worst-case communication cost between different task nodes in a system.

# 2.2 Power and Thermal Models

The power consumption of a CMOS IC chip is an aggregate of dynamic power  $(P_d)$ and leakage power  $(P_s)$

$$P_{total} = P_d + P_s. (2.2)$$

The dynamic power depends on switching activities of the underlying transistors in a CMOS IC, which depends on the supply voltage  $(V_{dd})$  and operating frequency  $(f_r)$  as

$$P_d = C_s \cdot V_{dd}^2 \cdot f_r, \tag{2.3}$$

where  $C_s$  is the switching capacitance. The leakage power is observed in the absence of switching activity and represented as [67]

$$P_s = N_g \cdot I_l \cdot V_{dd}, \tag{2.4}$$

where  $N_g$  is the number of gates in an IC, and  $I_l$  is the leakage current responsible for leakage power given as [67]

$$I_{l} = I_{r}(A_{l} \cdot T^{2} \cdot e^{((\alpha_{l}V_{dd} + \beta_{l})/T)} + B_{l} \cdot e^{(\gamma_{l}V_{dd} + \delta_{l})}), \qquad (2.5)$$

where  $I_r$  is the reference leakage current, T is the temperature, and  $A_l$ ,  $B_l$ ,  $\alpha_l$ ,  $\beta_l$ ,  $\gamma_l$ ,  $\delta_l$ are technology-dependent constants. As the leakage current depends on T and  $V_{dd}$ , the correlation between leakage power and temperature can be imprecisely considered as a linear behavior [68]

$$P_s = \phi_1 \cdot T + \phi_0, \tag{2.6}$$

where  $\phi_0$  and  $\phi_1$  are technology-dependent constants. Therefore, the total power is

$$P_{total} = C_s \cdot V_{dd}^2 \cdot f_r + \phi_1 \cdot T + \phi_0.$$

$$(2.7)$$

Equation (2.7) models the power consumption of the processing unit.

We consider a thermal model similar to [61,68–73], in which thermal phenomenon is represented as an R-C lumped circuit. The thermal model for a PU with 4 processing cores is shown in Figure 2.2. Let  $P_m$ ,  $R_{mm}$ , and  $C_m$  represent the power (*Watt*), thermal-resistance (*Joule*/°*C*), and thermal-capacitance (*W*/°*C*) for the processing core *m*. Whereas  $R_{mn}$  is the thermal-resistance between  $m^{th}$  and  $n^{th}$ processing cores, respectively, to consider the heat transfer effect among neighboring processing cores. Let  $T_{a_m}$  denote the ambient temperature for processing core *m*, then the thermal behavior of the core at time instant *t* be

$$C_m \cdot \frac{dT_m(t)}{dt} + \frac{T_m(t) - T_n(t)}{R_{mm}} + \sum_{n \neq m} \frac{T_m(t) - T_n(t)}{R_{mn}} = P_m(t).$$

(2.8)

Let  $\delta_m = \frac{T_{a_m}}{Rmm}$  and

$$g_{mn} = \begin{cases} \sum_{n=1}^{M} \frac{1}{R_{mn}}, & \text{if } n=m \\ \frac{-1}{R_{mn}}, & \text{otherwise.} \end{cases}$$

(2.9)

Then we have

$$C_m \cdot \frac{dT_m(t)}{dt} + \sum_{n=1}^{M} g_{mn} \cdot T_n(t) = P_m(t) + \delta_m.$$

(2.10)

Similarly, the thermal model for the entire system is

$$\mathbf{C}_{p}\frac{d\mathbf{T}(t)}{dt} + \boldsymbol{g}_{p}\mathbf{T}(t) = \mathbf{P}_{total}(t) + \boldsymbol{\delta}_{p}, \qquad (2.11)$$

where

$$\mathbf{C}_{p} = \begin{bmatrix} C_{1} & \cdots & 0 \\ \vdots & \ddots & \vdots \\ 0 & \cdots & C_{M} \end{bmatrix} \boldsymbol{g}_{p} = \begin{bmatrix} g_{11} & \cdots & g_{1M} \\ \vdots & \ddots & \vdots \\ g_{M1} & \cdots & g_{MM} \end{bmatrix} \boldsymbol{\delta}_{p} = \begin{bmatrix} \delta_{1} \\ \vdots \\ \delta_{M} \end{bmatrix}$$

The parameters  $\mathbf{C}_p$ ,  $\mathbf{g}_p$ , and  $\boldsymbol{\delta}_p$  depend on the architecture of the processing units. We can find transient and stable state temperatures using equation (2.7) in equation (2.11), which are required for the thermal-aware reliability design of the ECS.

Figure 2.2: Thermal model for 4-core processing unit [74]. Each processing core is represented by the equivalent power source, thermal resistance, and thermal capacitance.

#### 2.3 Lifetime Reliability Model

The reliability of a component is the probability of the component performing its intended operation for a specific time duration. Usually, reliability is characterized as a mean-time-to-failure (MTTF) [75]. If X be the lifetime of the component and  $f_p(t)$  be the probability density function (PDF), then its reliability is

$$\mathbb{R}(t) = P(X > t) = \int_{t}^{\infty} f_p(t)dt.$$

(2.12)

Hence,  $\mathbb{R}'(t) = -f_p(t)$ . Then, MTTF of the component is specified as

$$MTTF = \int_0^\infty t \cdot f_p(t)dt = -\int_0^\infty t \cdot \mathbb{R}'(t)dt.$$

(2.13)

After solving the integration, we have

$$MTTF = -t \cdot \mathbb{R}(t)|_0^\infty + \int_0^\infty \mathbb{R}(t)dt.$$

(2.14)

Finally, we get

$$MTTF = \int_0^\infty \mathbb{R}(t)dt.$$

(2.15)

According to equation (2.15), we can estimate the MTTF if the reliability of the component is available.

Failures in the processing units are classified as hard and soft faults. The permanent and unrepairable damage to the IC chips is caused by hard faults, whereas latter faults can be recovered from temporary failures. The temperature-dependent hard failures in ICs are time-dependent dielectric breakdown, thermal cycling, hot carrier injection, negative bias temperature instability, and electromigration (EM). In this dissertation, we focus on the electromigration phenomenon to characterize the thermal-aware system-level MTTF of the automotive ECS. However, our framework can be readily used for other hard failures.

At the higher temperature and current density, the electromigration causes displacement of the mass in the conductors of inadequate cross-section, leading to the vacancies in the chip geometry, which can not be recovered. This can be correlated with the mean-time-to-failure as [76],

$$MTTF(T) \propto A_c \cdot J^{-n} \cdot e^{\frac{E_a}{K \cdot T}},$$

(2.16)

where  $A_c$  is a cross-section area of the conductor-related constant; J is the current density  $(Amp/cm^2)$ ;  $E_a$  is the activation energy (*electron-volts*); K is the Boltzmann's constant; T is the temperature (*Kelvin*), and n = 2 unless otherwise specified. From equation (2.16), the lifetime reliability of the device is inversely dependent on the peak temperature, and it would be improved if the peak temperature is reduced.

#### 2.4 Deep Neural Network Architecture

The deep neural networks are used in AVs as they mimic the human brain's functionality of taking complex decisions on the road. A neuron is the fundamental

Figure 2.3: Feed Forward Neural Network containing input layer, multiple hidden layers, and an output layer.

Figure 2.4: Structure of the Neuron. All inputs of the neuron are associated with trainable network parameters.

block of the deep neural network, arranged in different layers as shown in Figure 2.3. Each layer in the figure has multiple neurons, and the layers are categorized as the input layer, hidden layers (1, ..., H), and an output layer [77]. External input is pre-processed and applied to the input layer. The outputs of the input layer are fed to the number of hidden layers to extract features from the input data. The number of neurons in a layer and the number of hidden layers in a network are application-dependent, required to extricate attributes from the input. The neurons are interconnected through the links known as weights or parameters, and the structure of the neuron is shown in Figure 2.4.

Let the DNN parameters be  $\boldsymbol{W} \in \mathbb{R}^N$ , where N is the size of the parameter space. Let the neuron set be  $\boldsymbol{\mathcal{N}} = \{\mathcal{N}_1, \mathcal{N}_2, ... \mathcal{N}_{n_e}\}$ , where the DNN has  $n_e$  neurons with sizes  $s_1, s_2, ..., s_{n_e}$  respectively, such that,  $s_1 + s_2 + ... + s_{n_e} = N$ . The neuron shown in Figure 2.4 has connection weights  $W_{\mathcal{N}_a} = \{w_1, w_2, ..., w_{s_a}\}$  from the previous layer neuron outputs  $(x_1, x_2, ..., x_{s_a})$  and the *bias*  $(b_{\mathcal{N}_a})$ . It performs weighted summation of the input feature maps:

$$y'_{\mathcal{N}_a} = \sum_{i=1}^{s_a} x_i \ w_i + b_{\mathcal{N}_a}.$$

(2.17)

In this dissertation, we refer to weights and bias as parameters if not explicitly specified. The weighted sum  $(y'_{z_a})$ , also known as the activation, is passed through a nonlinear activation function. Finally, we get the output of the neuron as

$$y_{\mathcal{N}_a} = \alpha(y'_{\mathcal{N}_a}). \tag{2.18}$$

The nonlinear activation functions such as Sigmoid, Tanh, and ReLU are commonly employed in neural networks [78]. The activations pass layer-by-layer through the network sequentially and reach the output layer.

#### 2.5 Summary

In this chapter, we present several pertinent preliminary models and architectures for our research. We first introduce the distributed heterogeneous architecture of the processing units in the ECS of the AVs. Later, discuss the automotive application behavior as a directed acyclic graph. Then, we present the thermal and power models required for considering the thermal-aware behavior of the PUs. Since temperature affects the reliability, we present electromigration-based lifetime reliability of the PU in terms of the MTTF metric. Afterward, we discuss the basic deep neural network architecture and associated neuron terminology.

In this dissertation, our research aims to optimize the automotive mission-critical latency and system-level lifetime reliability of the ECS design by satisfying thermal constraints, simultaneously maximizing the accuracy of the AI applications under thermal variations. In the following chapter, i.e., Chapter 3, we present our contributions on latency, system-level lifetime reliability, and thermal constraint design.

#### CHAPTER 3

### THERMAL AWARE LIFETIME RELIABILITY OPTIMIZATION FOR AUTOMOTIVE DISTRIBUTED COMPUTING APPLICATIONS

As the automotive industry is shifting the paradigm towards autonomous driving, safety guarantee has become a paramount consideration in design. Temperature plays a crucial role in the system-wide reliability of the ECS used in the automotive. A vehicle is usually subjected to harsh temperature conditions from its operating environment. The increasing power density of ICs in the ECS further exacerbates the operating temperature and thermal gradient condition on the chip, thereby significantly impacting the vehicle's reliability. In this chapter, we study how to map a periodic distributed automotive application on a heterogeneous multiplecore processing architecture with temperature and system-level reliability issues in check. We first present a mathematical programming model to bound the peak operating temperature for the ECS. Then we propose a sophisticated method using genetic algorithm to effectively bound the peak temperature and optimize the system-wide reliability of the ECS by maximizing its MTTF. We present an algorithm to guarantee the peak temperature for periodic applications with variable execution times to ensure our approach's effectiveness. We present several computationally efficient techniques for system-wide MTTF computation, which show several-order-of-magnitude speed-up over the state-of-the-art method when tested using synthetic cases and practical benchmarks.

#### 3.1 Introduction

The mainstream innovation in the automotive industry is driven by electronic systems that have transformed automobiles from a mechanical-only system to a sophisticated network of embedded systems. Today, roughly 1/3 of a car's cost is for automobile electronics, and the Electronic Control Units' costs can reach 50% to 60% in self-driving cars. To this end, the global Electronic Control Unit (ECU) market is continuing to grow by approx. 24% from 2020 to 2024 [79]. Utilizing innovative electronics technologies provides safer integration systems, which reduce human failure in driving, e.g., from traditional GPS positioning to inter-vehicle communication, from the traditional CAN bus to Automotive Ethernet and Media Oriented Serial Transport [80]. Meanwhile, consolidating auto-electronics and enhancing ECS reliability becomes more important as endorsed by ISO-26262 standard [81] because more and more life-critical control decisions are made electronically on the roads.

The automotive callbacks had tripled in the previous decade due to critical safety failures and faulty components [82]. Notably, in 2018, electronic defects have led to the highest percentage of vehicle recalls [83], and temperature plays a key role in terms of reliability for automotive systems. Among various failure mechanisms in an automotive ECS, the temperature-induced fault can reach as high as 55% [40]. It is because the aggressive scaling of transistor sizes soars the chip power density and runtime temperature, and the ever-increasing computing complexity dramatically exaggerates the chip thermal gradient, which could harm the system reliability [84]. Moreover, the vehicles undergo stringent environmental conditions with the temperature of ECUs ranging from  $90^{\circ}C$  to  $155^{\circ}C$  [38]. As a result, it is subjected to rapid aging due to temperature-induced failure phenomena such as electromigration (EM), time-dependent dielectric breakdown, thermal cycling, negative bias temperature instability, and hot carrier injection [85]. Also, exceeding the temperature threshold can automatically shut off the ECU [45] during runtime and may cause catastrophic consequences due to latency violations of the control decisions. Therefore, the runtime temperature should be carefully managed for reliability concerns to meet the safety requirements for the automotive [81].

In addition, to runtime thermal solutions, automotives use various active and passive cooling methods to restrict the ECU temperature, such as convection heat sinks and spreaders in low-end ECUs [55] or passive cooling for high-end ECUs, e.g., Tesla Model 3 [56]. However, for such systems, it requires non-trivial efforts to tightly bound the peak temperature for effective cooling system design. As shown later in the chapter, our proposed algorithm (in Section 3.5.2) can tighten the peak temperature bound by  $15^{\circ}C - 20^{\circ}C$  compared with the *thermal ignorant approach*, resulting in cost, area, and energy savings of the cooling system design.