#### Florida International University

## **FIU Digital Commons**

FIU Electronic Theses and Dissertations

**University Graduate School**

11-9-2021

## Non-invasive Techniques Towards Recovering Highly Secure Unclonable Cryptographic Keys and Detecting Counterfeit **Memory Chips**

Bashir Mohammad Sabquat Bahar Talukder Florida International University, bbaha007@fiu.edu

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Bahar Talukder, Bashir Mohammad Sabquat, "Non-invasive Techniques Towards Recovering Highly Secure Unclonable Cryptographic Keys and Detecting Counterfeit Memory Chips" (2021). FIU Electronic Theses and Dissertations. 4862.

https://digitalcommons.fiu.edu/etd/4862

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fiu.edu.

#### FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

## NON-INVASIVE TECHNIQUES TOWARDS RECOVERING HIGHLY SECURE UNCLONABLE CRYPTOGRAPHIC KEYS AND DETECTING COUNTERFEIT MEMORY CHIPS

A dissertation submitted in partial fulfillment of the requirements for the degree of  ${\color{blue} {\rm DOCTOR~OF~PHILOSOPHY}}$

in

ELECTRICAL AND COMPUTER ENGINEERING

by

Bashir Mohammad Sabquat Bahar Talukder

To: Dean John Volakis

College of Engineering and Computing

This dissertation, written by Bashir Mohammad Sabquat Bahar Talukder, and entitled Non-invasive Techniques Towards Recovering Highly Secure Unclonable Cryptographic Keys and Detecting Counterfeit Memory Chips, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

|                                       | Ou Bai                                                                                |

|---------------------------------------|---------------------------------------------------------------------------------------|

|                                       | A. Selcuk Uluagac                                                                     |

|                                       |                                                                                       |

|                                       | Ananda Mohan Mondal                                                                   |

|                                       | Md Tauhidur Rahman, Major Professor                                                   |

| Date of Defense: November 09, 2021    |                                                                                       |

| The dissertation of Bashir Mohammad S | Sabquat Bahar Talukder is approved.                                                   |

|                                       | Dean John Volakis                                                                     |

|                                       | College of Engineering and Computing                                                  |

|                                       | Andrés G. Gil                                                                         |

|                                       | t for Research and Economic Development<br>and Dean of the University Graduate School |

Florida International University, 2021

$\ \, \bigcirc$  Copyright 2021 by Bashir Mohammad Sabquat Bahar Talukder  $\mbox{All rights reserved}.$

#### **DEDICATION**

To my parents, Mohammad Faizur Rahman Talukder and Anjuman Ara Begum, my sister, Taieba Fatima Faizun,

and my high school teacher, Ms. Fahmida Sultana, who continuously inspired me to pursue engineering at my early age.

#### ACKNOWLEDGMENTS

Firstly, I want to thank my advisor Dr. Md Tauhidur Rahman, for his precious guidance, mentorship, and continuous motivation throughout my doctoral research. Without his advice and endless support, this dissertation would never have been pulled off. I am extremely grateful to him for consciously supporting me for the last four and half years and understanding me in my difficult times. I would also like to thank Dr. Ou Bai, Dr. A. Selcuk Uluagac, and Dr. Ananda Mohan Mondal for their insightful comments, guidance, encouragement, and important technical feedback to take this research to the next level. I want to thank my wife and colleague Farah Ferdaus for her emotional support and technical advice, which easily saved many of my days. I would also like to thank Prof. Dr. Aleksandar Milenković, Dr. Biswajit Ray, Dr. Emil Jovanov, Dr. Huaming Zhang, and Dr. Vineetha Menon from the University of Alabama in Huntsville. Their continuous inspiration and technical advice are highly motivating and helped me learning many aspects of Computer Engineering. Lastly, I would like to show my gratitude towards two of my closest friends, Mr. Adnan Jahangir and Mr. Rakibul Kabir Rifat, for their constant support and encouragement. I would also like to express my gratitude towards FIU University Graduate School and the Department of Electrical and Computer Engineering at Florida International University for their continuous administrative support. I would also like to acknowledge the support provided by National Science Foundation; this dissertation is mostly based upon the work supported by National Science Foundation under the grant number CNS-1850241.

#### ABSTRACT OF THE DISSERTATION

# NON-INVASIVE TECHNIQUES TOWARDS RECOVERING HIGHLY SECURE UNCLONABLE CRYPTOGRAPHIC KEYS AND DETECTING COUNTERFEIT MEMORY CHIPS

by

Bashir Mohammad Sabquat Bahar Talukder Florida International University, 2021 Miami, Florida

Professor Md Tauhidur Rahman, Major Professor

Due to the ubiquitous presence of memory components in all electronic computing systems, memory-based signatures are considered low-cost alternatives to generate unique device identifiers (IDs) and cryptographic keys. On the one hand, this unique device ID can potentially be used to identify major types of device counterfeitings such as remarked, overproduced, and cloned. On the other hand, memory-based cryptographic keys are commercially used in many cryptographic applications such as securing software IP, encrypting key vault, anchoring device root of trust, and device authentication for could services. As memory components generate this signature in runtime rather than storing them in memory, an attacker cannot clone/copy the signature and reuse them in malicious activity. However, to ensure the desired level of security, signatures generated from two different memory chips should be completely random and uncorrelated from each other. Traditionally, memory-based signatures are considered unique and uncorrelated due to the random variation in the manufacturing process. Unfortunately, in previous studies, many deterministic components of the manufacturing process, such as memory architecture, layout, systematic process variation, device package, are ignored. This dissertation shows that these deterministic factors can significantly correlate two memory signatures if those two memory chips share the same manufacturing resources (i.e., manufacturing facility, specification set, design file, etc.). We demonstrate that this signature correlation can be used to detect major counterfeit types in a non-invasive and low-cost manner. Furthermore, we use this signature correlation as side-channel information to attack memory-based cryptographic keys. We validate our contribution by collecting data from several commercially available off-the-shelf (COTS) memory chips/modules and considering different usage-case scenarios.

#### TABLE OF CONTENTS

| CHAPTER                                                  | PAGE      |

|----------------------------------------------------------|-----------|

| 1. INTRODUCTION                                          |           |

| 1.1 Research Objectives                                  |           |

| 1.1.1 Research Objective 1: Anti-counterfeiting Solution |           |

| 1.1.2 Research Objective 2: Attacking on mPUF keys       |           |

| 1.2 Significance of Study                                |           |

| 1.3 Organization of the Dissertation                     | 7         |

| 2. BACKGROUND AND LITERATURE REVIEW                      | 9         |

| 2.1 Overview of PUFs                                     | 9         |

| 2.2 PUF Taxonomy                                         | 11        |

| 2.3 Memory-based PUFs (mPUFs)                            | 13        |

| 2.3.1 Memory Organization and Memory Technologies        | 14        |

| 2.3.2 Basic Principle of Memory-based PUFs (mPUFs)       | 19        |

| 2.4 mPUF Applications                                    | 23        |

| 2.4.1 Anti-counterfeiting Solution                       | 23        |

| 2.4.2                                                    | 27        |

| 3. IMPACTS OF DETERMINISTIC FACTORS ON mPUF SIGNA        | ATURES 34 |

| 3.1 Introduction                                         |           |

| 3.2 Architectural Variation                              |           |

| 3.3 Layout Variation                                     |           |

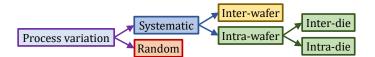

| 3.4 Process Variation                                    |           |

| 3.5 IC packaging                                         |           |

| 3.6 Device Aging                                         |           |

| 4. IDENTIFYING DRAM ORIGIN                               | 42        |

| 4.1 Introduction                                         |           |

| 4.2 Objectives and Assumptions                           |           |

| 4.3 Proposed Method                                      |           |

| 4.4 Performance Evaluation of Proposed Framework         |           |

| 4.5 Limitations                                          |           |

| 4.6 Conclusion                                           |           |

| 4.0 Conclusion                                           | 01        |

| 5. IDENTIFYING SRAM ORIGIN                               |           |

| 5.1 Introduction                                         |           |

| 5.2 Differences from Prior Works                         |           |

| 5.3 Proposed Method                                      |           |

| 5.3.1 Feature Selection                                  |           |

| 5.3.2 Identifying Authentic Memory Chips                 |           |

| 5.3.3 Proposed Framework                                 | 71        |

| 5.3.4 Identifying Recycled Memory Chips                     |

|-------------------------------------------------------------|

| 5.4 Performance Evaluation of Proposed Framework            |

| 5.4.1 Visualizing Features                                  |

| 5.4.2 Labeling Test Memory Chips                            |

| 5.4.3 Identifying Recycled Memory Chips                     |

| 5.4.4 Evaluation Time                                       |

| 5.5 Limitations                                             |

| 5.6 Conclusion                                              |

| 6. NON-INVASIVE HEURISTIC ATTACK ON mPUF 91                 |

| 6.1 Vulnerabilities of mPUFs and weakness of PUF Metrics 91 |

| 6.1.1 Deterministic Components of mPUF keys                 |

| 6.1.2 Acceptance of Errors in PUF Protocol                  |

| 6.1.3 Weakness of PUF Metrics                               |

| 6.2 Threat Model                                            |

| 6.3 Proposed Method                                         |

| 6.3.1 Analyzing PUF Vulnerabilities                         |

| 6.3.2 Attacking an SRAM PUF                                 |

| 6.4 Performance Evaluation of Proposed Attack               |

| 6.4.1 Error Characterization of SRAM Signature              |

| 6.4.2 Attacking an SRAM PUF                                 |

| 6.4.3 Attacking in the Presence of a Fuzzy Extractor        |

| 6.5 Mitigation                                              |

| 6.5.1 Avoiding Error Correction Scheme                      |

| 6.5.2 Using Properly Designed Fuzzy extractor               |

| 6.5.3 Pattern Distribution-aware CRPs                       |

| 6.5.4 Locality-aware CRPs                                   |

| 6.6 Conclusion                                              |

| 7. CONCLUSION AND FUTURE WORK                               |

| BIBLIOGRAPHY                                                |

| APPENDICES                                                  |

| VITA                                                        |

## LIST OF TABLES

| TAB | LE PAGE                                                                  |

|-----|--------------------------------------------------------------------------|

| 2.1 | Different types of IC counterfeitings                                    |

| 2.2 | Summary of counterfeit chip detection/identification methods 28          |

| 4.1 | Memory modules used in the data set                                      |

| 4.2 | Results from the one-class classifier                                    |

| 5.1 | List of SRAM chips in experiment                                         |

| 5.2 | Identifying SRAM manufacturer                                            |

| 5.3 | Identifying SRAM part number                                             |

| 5.4 | Mean accuracy, precision, recall, and $F_1$ score at high temperature 85 |

| 6.1 | List of SRAM chips used as train devices                                 |

| 6.2 | 16-bit pattern characteristics and vulnerability to heuristic attack 106 |

| 6.3 | Fuzzy min-entropy for SRAM chips                                         |

## LIST OF FIGURES

| FIG | URE PAG:                                                                            | Е |

|-----|-------------------------------------------------------------------------------------|---|

| 2.1 | single bit arbiter PUF with $m$ -bit challenge                                      | 1 |

| 2.2 | Memory organization in modern computer system                                       | 4 |

| 2.3 | A $4 \times 4 \times 4$ memory array                                                | 5 |

| 2.4 | Basic memory cell structure                                                         | 7 |

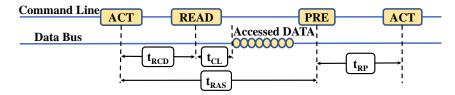

| 2.5 | DRAM timing at read cycle                                                           | 7 |

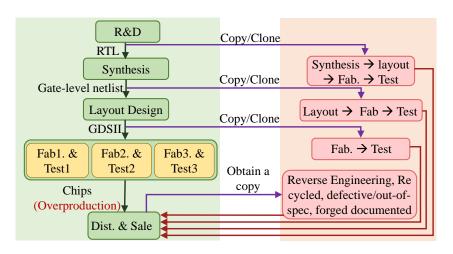

| 2.6 | IC design flow vs possible covert channels to introduce counterfeit ICs 2           | 4 |

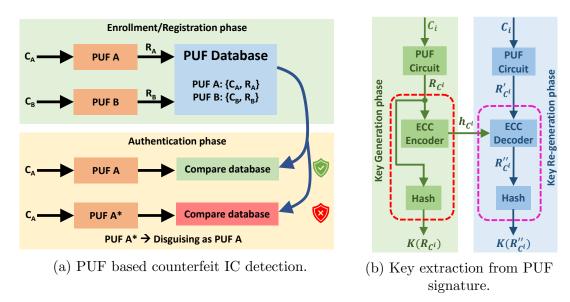

| 2.7 | PUF applications                                                                    | 7 |

| 2.8 | Rep and Gen block of fuzzy extractor                                                | 9 |

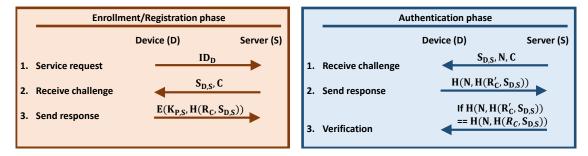

| 2.9 | Simplified mPUF-based IOT device authentication protocol                            | 1 |

| 3.1 | Different types of process variation                                                | 8 |

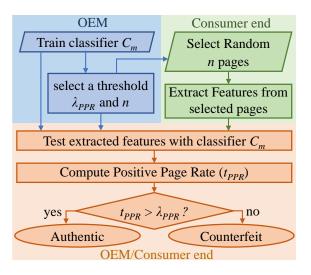

| 4.1 | Proposed framework for identifying the origin of the DRAM 5                         | 2 |

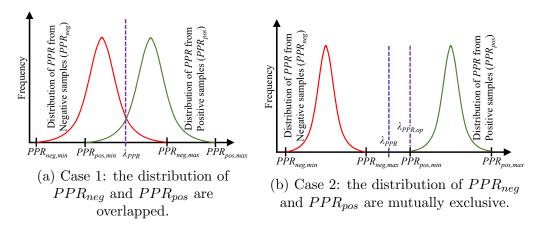

| 4.2 | Selection of $\lambda$ with different distribution of $PPR_{neg}$ and $PPR_{pos}$ 5 | 3 |

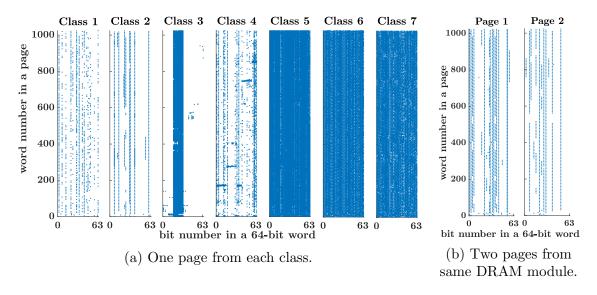

| 4.3 | Spatial locality of failed bits from randomly chosen DRAM pages 5                   | 6 |

| 4.4 | Visualizing data in feature-space                                                   | 7 |

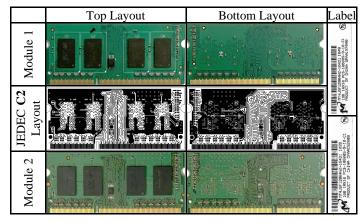

| 4.5 | Visual representation of DRAM modules from Class 6                                  | 0 |

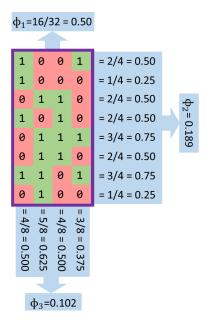

| 5.1 | Illustration of $\Phi_1$ , $\Phi_2$ , and $\Phi_3$                                  | 5 |

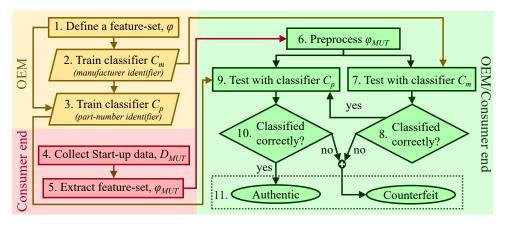

| 5.2 | Proposed protocol to identify counterfeit SRAM                                      | 2 |

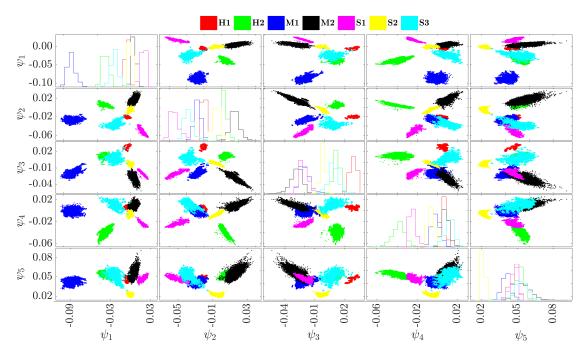

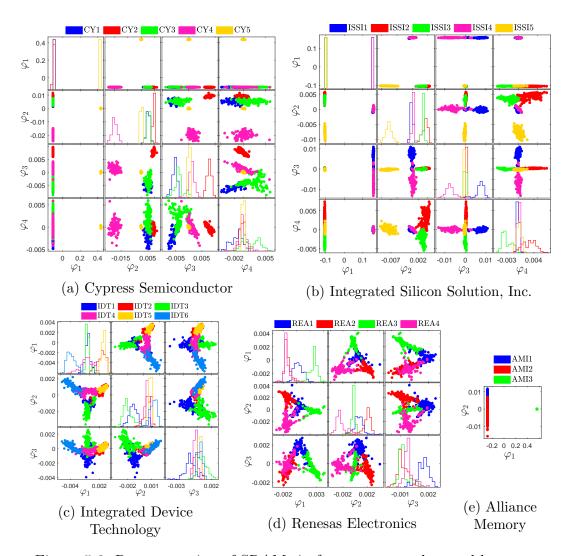

| 5.3 | Visualizing feature distribution by manufacturer                                    | 6 |

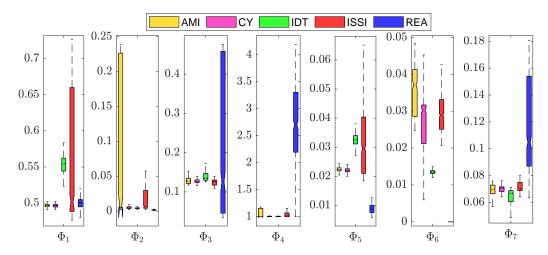

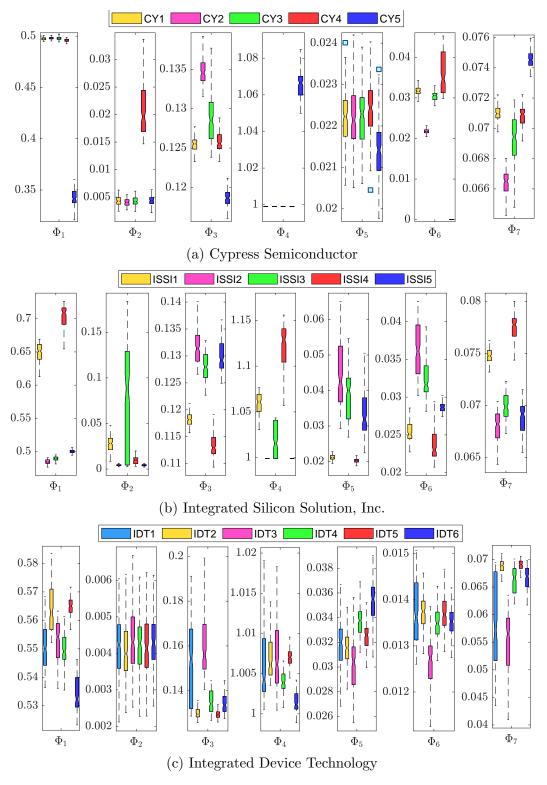

| 5.4 | Visualizing feature distribution by part number                                     | 8 |

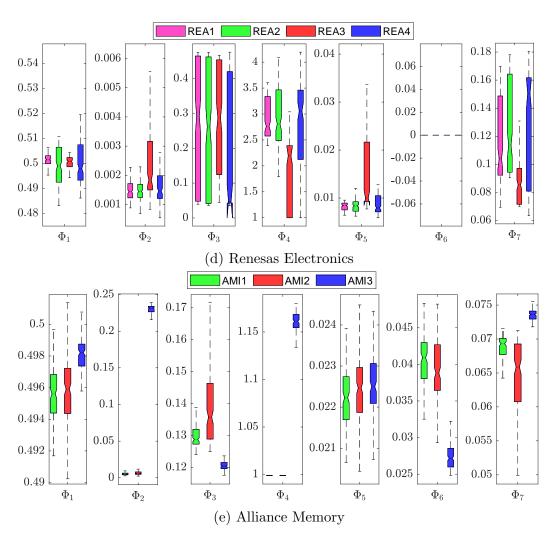

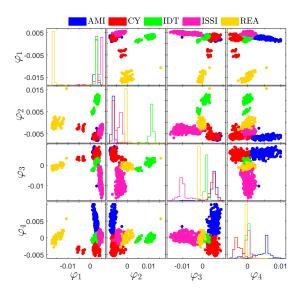

| 5.5 | Representation of SRAMs in feature-space, clustered by manufacturer $7$             | 9 |

| 5.6 | Representation of SRAMs in feature-space, clustered by part number 8                | 0 |

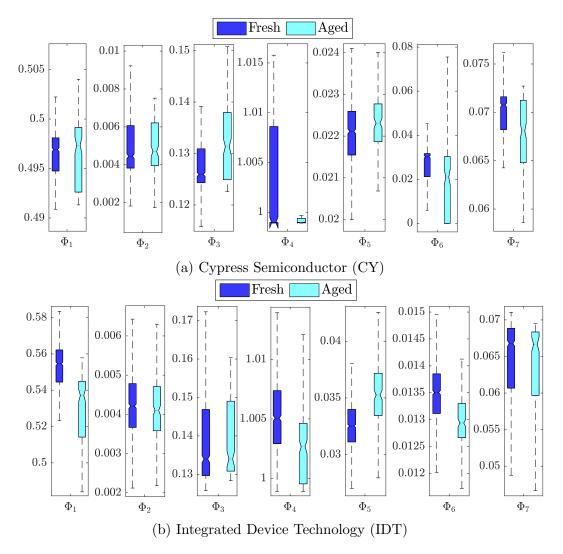

| 5.7 | Visualizing feature distribution: fresh vs. aged                                    | 7 |

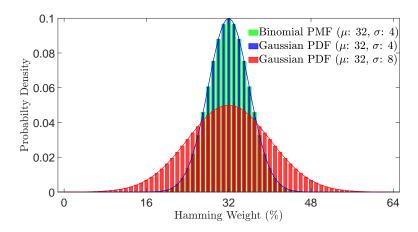

| 6.1 | Binomial vs. Gaussian distribution                                                  | 3 |

| 6.2 | Constructing <i>n</i> -bit key from $n'$ -bit word                                  | 2 |

| 6.3 | SRAM chip error characterization                                     |

|-----|----------------------------------------------------------------------|

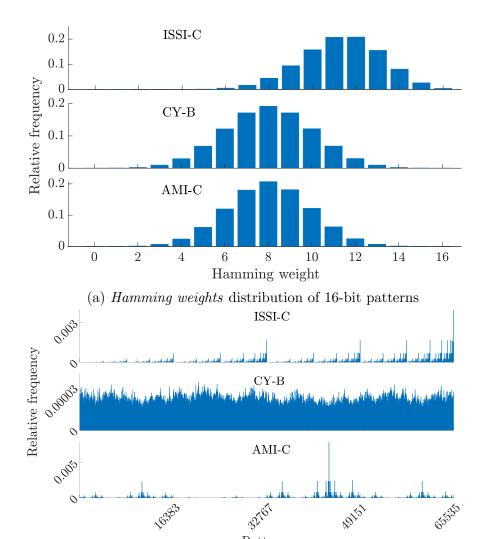

| 6.4 | Visualizing 16-bit pattern distribution                              |

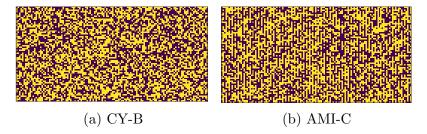

| 6.5 | Spatial distribution of 0's and 1's                                  |

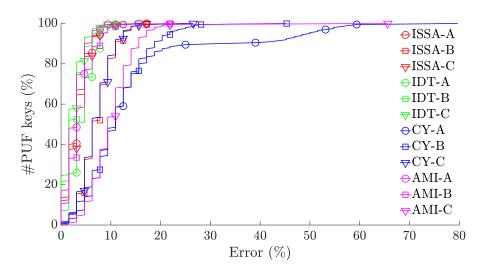

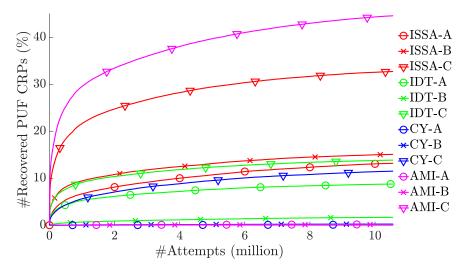

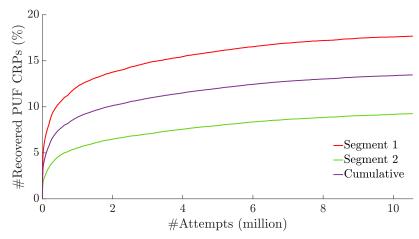

| 6.6 | Number of attempts vs. recovered CRPs                                |

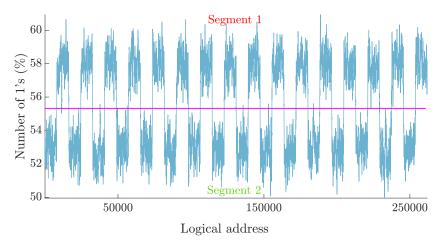

| 6.7 | Dependency of pattern heuristics with respect to logical address 111 |

#### CHAPTER 1

#### INTRODUCTION

The field of cybersecurity has predominantly focused on the security of the soft-ware and the communication network due to the assumption that the underlying hardware is trustworthy and reliable. However, emerging attack vectors on hardware originating from the untrusted global supply chain, along with unintentional design and integration-caused hardware vulnerabilities, questions the well-regarded notion of hardware "root of trust". In the era of secure computing, many hardware-based security primitives use memory-based signatures to ensure device security, authenticity, and users privacy. These memory signatures are comparable to silicon fingerprints due to their reproducible nature. Currently, memory-based signatures are commercialized to generate device identifiers (IDs) for chip authentication or counterfeit chip detection and generating keys for various cryptographic applications.

From the application perspective, memory-based signatures are considered as the physical unclonable functions (PUF) [SRR16, SMRR20, KPHM18, G<sup>+</sup>07]. By definition, PUF is a circuit that can generate a unique signature ("response") depending on its input pattern ("challenge") [RSS<sup>+</sup>10]. However, unlike traditional PUFs (such as Arbiter PUF and Ring Oscillator PUF), memory-based PUFs (mPUFs) are only capable of generating a limited number of challenge-response pairs (CRPs) [RH14]. Therefore, traditional PUFs are also known as strong PUF, whereas mPUFs are known as weak PUF [RH14]. Although strong PUFs are the preferred choice for many cryptographic applications, the mPUFs provide a low-cost alternative solution as they do not require any additional hardware. Moreover, mPUF can replace strong PUFs in all possible applications with necessary adjustments in the PUF protocol [HYKD14]. Nevertheless, to ensure a similar level of security as strong PUFs,

mPUFs must have the following three properties- (i) reproducibility (reliability), (ii) uniqueness, and (iii) randomness (uniformity) [MGS13]. The reproducible property of mPUFs comes from the fact that electronics properties of mPUFs are immutable once it is fabricated. On the other hand, the uniqueness and the randomness of the mPUFs signature are believed to be a direct consequence of the random variation of the memory manufacturing process. However, we observe that mPUF signatures may have a significant correlation if they share the same manufacturing resources (fabrication facility and design specifications) due to similarities in their architecture, layout, and die packaging. unfortunately, these observations have been ignored in all previous research, which leads us to two distinct research opportunities- (i) exploiting mPUF correlation to simplify the mPUF-based counterfeit IC (Integrated circuit) detection technique, and (ii) using this same signature correlation as side-channel information to attack the mPUF key.

### 1.1 Research Objectives

## 1.1.1 Research Objective 1: Anti-counterfeiting Solution

Electronic counterfeiting is a longstanding problem with adverse long-term effects for many sectors, remaining on the rise. Globalization of the semiconductor supply chain has allowed worldwide fabrication of both authentic and counterfeit chips. In an established global semiconductor supply chain, several untrusted parties (foundry, assembly, third-party IPs, market distributor, etc.) are involved, any of whom can clone IP (intellectual property), insert hardware trojan, and/or include recycled, remarked, overproduced, out-of-spec/defective, and forge-documented chips [BB15, GHD+14, FC18]. Without question, the presence of counterfeit or inferior compo-

nents in commercial or military cyber-infrastructure could have catastrophic and far-reaching consequences on security and reliability domains because of their substandard quality, poor performance, and shorter life span [BB15, GHD<sup>+</sup>14, FC18]. Current techniques to detect and prevent major counterfeit types (e.g., recycled, remarked, etc.) are either invasive or expensive [GHD<sup>+</sup>14, FC18]. Furthermore, existing countermeasures target only a single counterfeit type.

Recently, mPUF-based anti-counterfeiting solutions gained a lot of attention as they can identify the major types of counterfeit chips (e.g., recycled, remarked, cloned, etc.) by tagging each authentic chip with a unique identifier [GHD<sup>+</sup>14, FC18]. As memory components are the essential part of most electronic chips, the mPUF-based solution does not incur additional hardware costs. Unfortunately, this solution is still not suitable for low-cost hardware as it requires an exhaustive registration process and maintains a centralized database of authentic chips' identifiers. In this dissertation, we will try to answer following three research questions (RQs) in order to simplify mPUF-based anti-counterfeiting solutions-

- RQ1: Can we avoid the exhaustive device registration phase? Can we use a statistical model to identify a group of memory chips instead of using a unique identifier for each chip?

- **RQ2:** Can we avoid the interactive communication protocol of mUF-based device authentication? Can we authenticate the device in offline mode?

- RQ3: What type of device counterfeitings can we identify?

To answer the above questions, this dissertation will explore the following three goals-

- 1. Extraction of salient features: We need a set of features that reliably classify memory manufacturer and memory specification, which is a non-trivial task and one of the novelties of our research. The objective is to extract a set of features

from memory-based signatures, which can uniquely correlate to a group of memory chips if they share the same architecture, layout, systematic process variation, and die packaging (i.e., sharing the same manufacturer and part number).

- 2. Development of machine-learning-based framework: An efficient machine-learning-based framework is required to learn manufacturer and part number-specific information from the extracted features. We use this statistical model (offline or online) to identify the manufacturer and part number for an unknown chip. It is worth mentioning that identifying the manufacturer and part number can provide almost the same level of protection against counterfeit memory chips as mPUF-based identifiers.

- 3. Detection of other counterfeit types: As the recycled chips share the same manufacturing resources and design specifications as the fresh chips, identifying the manufacturer and part number might not be sufficient to detect recycled chips. However, some electrical properties of recycled chips deviate due to the device age [KBTS<sup>+</sup>18], which might be observed from the feature distribution of the recycled chips. Therefore, distinctive distribution of one or multiple features can potentially identify recycled memory chips.

## 1.1.2 Research Objective 2: Attacking on mPUF keys

In order to be useful in practical security applications, the fingerprint or key generated by the PUF should be reliable and attack-resistant. Due to the open-access nature of the strong PUFs, numerous successful attacks have been proposed against those PUFs where the attacker does not require any physical access to the PUF [RSS+10, RvD13, RJA12]. On the contrary, mPUFs (more generally, weak PUFs) are resistant to such attacks as their protocol does not support accessing them di-

rectly from the outside world [RH14]. While most research focuses on low-cost techniques that generate reliable signatures from mPUFs, this dissertation will focus on security aspects of mPUFs that have been widely overlooked and answer the following four research questions (RQs).

- RQ4: What are the major challenges of mPUFs from using to generate low-cost keys or unique identifiers? Can we avoid expensive key generation schemes (e.g., fuzzy extractor [FRS20, FRS16]) for generating high-quality identifiers or keys for low-cost applications?

- RQ5: Do mPUFs have any weaknesses that can lead to non-invasive attacks? For example, can we exploit the correlation between to mPUF signature as side-channel information?

- **RQ6:** There have been several PUF metrics that are reliable and used to quantify the security of PUFs. Do any of these metrics have any weaknesses?

- RQ7: Can we develop invasive attack methodologies that do not need physical access to the target system?

Below is the four specific aims of this dissertation that will answer the above research questions.

- 1. Discovering the weaknesses of memory-based signatures: We will discover the vulnerabilities of an mPUF that can be exploited to recover or model the PUF responses in non-invasive ways without any physical access to the target device.

- 2. Discovering the weaknesses of existing PUF quality metrics: With the support of current PUF metrics, the mPUF is considered secure. This dissertation will aim to discover the weakness of existing PUF metrics and show that they do not always guarantee the security of mPUF signatures.

- 3. Recovering/predicting memory-based PUF outputs: The mPUFs are

considered robust against non-invasive attacks because of their limited CRPs. This dissertation will develop techniques to predict or model PUF outputs in non-invasive ways by exploiting the mPUF vulnerabilities.

4. Developing attack-resistant mPUFs at a low cost: An expensive fuzzy extractor generates high-quality keys/identifiers, which is not viable for low-cost systems [FRS20, FRS16]. Furthermore, other low-cost alternatives to fuzzy extractors can also be vulnerable to our new non-invasive attack. We will develop low-cost techniques for generating attack-resistant mPUFs from memory chips.

### 1.2 Significance of Study

Recent studies show that the global market share of counterfeit integrated circuits (ICs) is worth \$169 billion [Kar20]. Among different counterfeit ICs, memory chips share the most considerable portion of the counterfeit IC market (~17%) [FC18]. Moreover, another 28% of the fake chips are contributed by memory-integrated microprocessors, microcontrollers, and FPGAs [FC18], which are the most expensive components of any system. Hence, identifying counterfeit memory elements might be able to element those counterfeit components as well. Recent statistics showed that counterfeit chips incidents are growing at a rate of 25% each year [FC18]. The Senate Armed Services Committee confirmed more than 1,800 counterfeit electronic components incidents in U.S. military hardware in the early 2010's decade, and most of them are associated with counterfeit memory [Dep11]. The inclusion of counterfeit memory in an electronic system can endanger personal and national privacy, sabotage critical infrastructure, and damage the viability of entire business sectors because of their sub-standard quality, poor performance, and shorter lifespan. Section 818 of the U.S. National Defense Authorization Act (NDAA) requires defense

counterfeit risk [U.S18]. Although industry and academic researchers developed several methods to combat counterfeit memories, none of them are suitable for low-cost memory chips or memory integrated embedded devices. Hence, this research can benefit- individuals and the semiconductor industry from potential financial loss and the government from compromising national security and privacy. Additionally, Identifying the manufacturer and the specification is also essential to- (i) enforce the license agreement, (ii) tracking the chip quality, and (iii) ranking the memory products and worthiness [BTMR+20].

In addition to identifying counterfeit memory chips, it is also essential to determine the vulnerability of mPUF-based cryptographic applications. The mPUF-based cryptographic key has become very popular as they do not require any additional cost, and consequently, they have been deployed in many commercial embedded devices. Hence, analyzing the vulnerability to mPUFs is essential to ensure the risk-free application in privacy-, safety- and security-critical operations.

## 1.3 Organization of the Dissertation

The rest of this dissertation is organized as follows. Chapter 2 provides necessary backgrounds on different memory technologies, the detailed construction of mPUFs using different memory technologies, and PUF applications on counterfeit device identification and cryptographic key generation. We also compare other existing anti-counterfeiting solutions with PUFs and known vulnerabilities of the mPUF key. In Chapter 3, we discuss different non-deterministic factors that can impact mPUFs' signature during the manufacturing process. In Chapters 4 and 5, we proposed a new anti-counterfeiting solution by extracting a feature-set from mPUF-based signatures.

Our proposed technique is much simpler than the PUF-based solution, which is demonstrated by two different types of memory technologies (DRAM and SRAM). Chapter 6 assesses new possible vulnerabilities of the mPUF key and demonstrates our idea on SRAM-based silicon data. Finally, we conclude our dissertation and propose the future direction of our research in Chapter 7.

#### CHAPTER 2

#### BACKGROUND AND LITERATURE REVIEW

This dissertation starts where other research works on memory-based PUF (mPUFs) have been called off. This chapter will provide an overview of PUFs, the fundamental difference between mPUFs and other PUFs, the construction of mPUFs, and PUF-based anti-counterfeiting solution and cryptographic key extraction.

#### 2.1 Overview of PUFs

A PUF is a hardware security primitive that can translate a input ("challenge" or "stimuli") to a unique sequence ("signature" or "response") which is specific to the electrical characteristics of that system [RSS+10, MGS13, MBW+19, HYKD14]. The key idea behind a PUF is, although one can use the same architecture and manufacturing process to fabricate multiple PUF circuitry, the random variability in the manufacturing process impacts the electrical characteristics (e.g., timing path delay) randomly [HYKD14]. PUF utilizes this random variation on the electrical property to create a unique sequence. In general, an ideal PUF should have following three properties for reliable operations [RRFT15, MGS13, BTRFR19]-

1. Uniqueness: The PUF response should be unique and should not collide if multiple PUF devices are stimulated with the same challenge. In other words, if the responses generated from two PUFs (with the same challenge) are properly random, the *Hamming distance*<sup>1</sup> between two PUF responses should be ~ 50%. However, if the number of test devices is large, then one-to-one *Hamming distance* becomes a very expensive metric to test (due to a large number of possible combinations). Furthermore, a single PUF is usually capable of producing multi-

<sup>&</sup>lt;sup>1</sup> Hamming distance (or simply "distance") is defined as the number of bit difference between two binary strings.

ple challenge-response pairs. Consequently, assessing *Hamming distance* for each CRP makes it computationally expensive. Fortunately, *bit-aliasing* is a cheaper alternative to test uniqueness. For this metric, we create a binary string using all memory-bits from a specific bit-location of all PUF devices and measure the *Hamming weight* [MGS13, RHG<sup>+</sup>17] (Equation 2.1).

$$\beta_{l,C} = \frac{1}{k} \sum_{i=1}^{k} b_{l,C}^{i} \tag{2.1}$$

Here,  $\beta_{l,C}$  is the bit-aliasing computed at the lth bit using k PUF devices with a unique challenge C, and  $b_{l,C}^{i}$  is the lth bit response generated from the ith PUF device. Hence, for the n-bit responses generated from all k PUF devices, we have a set of  $\beta$ s. To make it simpler, researchers only focus on the average bit-aliasing defined by the Equation 2.2.

$$\beta_C = \frac{1}{n} \sum_{l=1}^{n} \beta_{C,l}$$

(2.2)

For a set of ideal PUFs,  $\beta_C$  (with unique challenge C) should be close to 0.5. This condition suggests that the probability of getting "0" (or "1") from a specific bit location over multiple PUFs is exactly 50%.

2. **Uniformity:** The PUF response should have a uniform distribution of "0" and "1". To satisfy this condition, the average *Hamming weight* of the PUF responses should be close to 50% [MGS13, RHG<sup>+</sup>17]. Mathematically, the uniformity can be expressed with Equation 2.3.

$$U_C = \frac{1}{n} \sum_{l=1}^{n} b_{l,C} \tag{2.3}$$

Here,  $b_{l,C}$  is the *l*th bit of the response, which corresponds to challenge C. For a uniform response, the uniformity,  $U_C$  should be close to 50%.

3. **Reproducibility:** An ideal PUF device should produce the exact same response while assessed with the same challenge [MGS13]. Alternatively, two responses

produced by the same PUF with the same challenge should have a *Hamming distance* of 0. Ideally, A robust PUF should retain this property even with extreme variations in operating conditions.

#### 2.2 PUF Taxonomy

The strength of PUF mainly depends on the number of challenge-response pairs (CRPs) that it can produce. Based on the number of CRPs, PUFs are categorized into two major types [MBW<sup>+</sup>19, HYKD14, RH14]-

1. **Strong PUF:** Strong PUFs typically support a large number of CRPs; more precisely, the number of CRPs grows exponentially with respect to the growth of strong PUF resources [MBW<sup>+</sup>19]. One of the popular architectures of strong PUF is MUX-controlled Arbiter PUF and Ring Oscillator PUF [SD07]. A single-

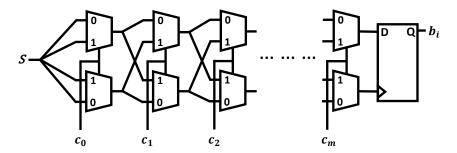

Figure 2.1: single bit arbiter PUF with m-bit challenge.

bit m-stage arbiter PUF is shown in Figure 2.1. In arbiter PUF, each bit of the challenge sequence  $(c_j)$  controls a pair of MUXes, and each pair of MUXes uses the output of the previous pair of MUXes. For any MUX, if the selector,  $c_j$  is 0, the top and bottom MUX conduct the same signal from the previous stage's top and bottom MUX, respectively. However, if  $c_j$  is 1, the top and bottom signals switch the side. If the source S generates a rising signal, the D flip-flop latches "0" if the delay at the D pin is higher than the delay at the clock pin;

otherwise, it latches "1" at the output. Note that a multi-bit arbiter PUF is constructed by cascading multiple single-bit arbiter PUFs. Due to the random process variation, each MUX consists of slightly different delay characteristics. Hence, the latched value at the D flip-flop is completely random and depends on the signals applied on each selector pin of each stage. Note that if we increase the Arbiter PUF structure by one pair MUXes (i.e., adding one more stage), it will support (m+1)-bit challenge, and the number of CRPs will be increased two-fold. As a strong can produce a large number of CRPs, only a randomly chosen subset of CRPs are used in real applications.

2. Weak PUF: Weeks PUFs can only produce a limited number of CRPs (in the extreme case, only one CRP). Unlike the strong PUF, the number of CRPs grows linearly with respect to the weak PUF resources [MBW+19]. Note that most of the mPUFs are considered weak PUF, which are discussed in Section 2.3. In such mPUFs, the address of the memory is used as the challenge while the content of that address location (with some special arrangement) is fetched as the response. Due to the array-like structure of the memory chips, the number of CRPs linearly grows with the growth of the memory size (i.e., the number of CRPs is doubled if the number of the memory cell is also doubled).

Aside from the number of CRPs, there are other differences between the strong PUF and the Weak PUF. For example, the strong PUF uses an open-access protocol as opposed to the weak PUF [MBW<sup>+</sup>19, HYKD14, RH14]. In an open-access protocol, anyone can challenge the strong PUF and collect corresponding responses. However, an attacker cannot feasibly collect the whole set of CRPs from a strong because of its enormous size. Furthermore, for a strong PUF, a randomly sampled subset of CRPs ( $S_{used,CRP}$ ) is used in real applications. Hence, even if an attacker succeeds to collect a subset of the CRPs ( $S_{attacker,CRP}$ ), the probability of  $S_{used,CRP} \cap S_{attacker,CRP}$

to be a non-empty set is very negligible. Moreover, as the number of CRP in strong PUF is very large, strong PUF uses a particular CRP only once to prevent reply attacks [MS09] and simplify the PUF protocol. On the other hand, memory-based weak PUFs are a cheaper solution compared to strong PUFs as a device can utilize its existing memory components without incurring any additional hardware cost. However, Weak PUF might require complex protocol to support some special application (e.g., IOT device authentication for cloud services) [HYKD14].

This dissertation mainly focuses on memory-based weak PUFs (or simply mPUFs) as they are more common than strong PUFs and are available in many commercial devices. In the next couple of sections, we will discuss different types of mPUFs and their typical applications.

### 2.3 Memory-based PUFs (mPUFs)

Memory chips are the ubiquitous component of modern computer systems. Typically, a modern computer system consists of multiple memory components. Interestingly, most types of memory chips are capable of generating PUF-like signatures without making any design modifications. However, generally, they require some non-standard memory operations (e.g., reducing read/write latency, latching start-up state, etc.) to function like a PUF [G+07, HBF07, BTRFR19, SRR16, KPHM18, TKYC16, SMRR20, JXW+15, MRFA15]. Fortunately, those operations can be performed by only OS/firmware level manipulation without making any hardware modification. Hence, except for some software overhead, the cost associated with mPUFs is very negligible. To understand the operation of mPUFs in more detail, here, we present the modern memory organization briefly and the basic principle of different types of memory components.

#### 2.3.1 Memory Organization and Memory Technologies

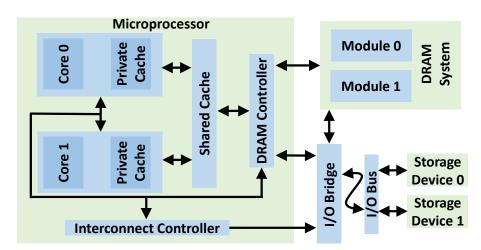

Most of the modern computer system maintains a hierarchical memory organization to read and write data efficiently (see fig. 2.2). As technology does not allow a memory to be fast and cost-effective at the same time [Eve], different types of memories are used at each level of memory hierarchy to balance between cost and performance. In most of computer system, memory organization maintains the following hierarchy [PH16, BO16]- CPU  $\rightarrow$  registers  $\rightarrow$  private cache  $\rightarrow$  shared cache  $\rightarrow$  main memory  $\rightarrow$  storage memory. Note that, in many smaller embedded systems, one or more components from this hierarchy might be fused together; for example, smaller micro-controllers may use a single SRAM (static random access memory) chip as both cache and main memory. Nevertheless, starting from the beginning down to the end of this hierarchy, each memory component is slower but bigger and cheaper than the previous one.

Figure 2.2: Memory organization in modern computer system.

In general, most of the memory components are analogous to a 2-D array structure [vdGS02]. Selecting the appropriate row and column provides one-bit data. Usually, memory chips contain multiple memory arrays to produce a multi-bit data

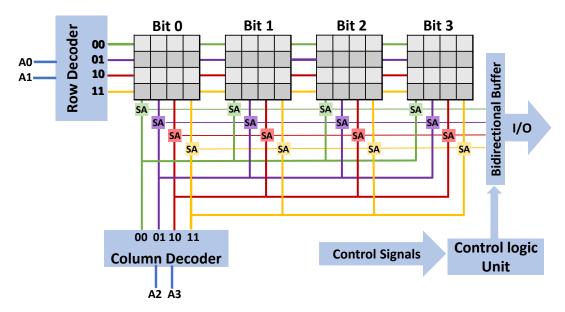

Figure 2.3: A  $4 \times 4 \times 4$  memory array.

word. In Figure 2.3, we present a  $4 \times 4 \times 4$  memory<sup>2</sup> chip with a 4-bit address (two bits each for row addressing and column addressing) [vdGS02, JWN10, GWHS19]. The appropriate row and column addresses are selected via a row address decoder and a column address decoder. Note that rows and columns are also called wordline and bitline, respectively. Sometimes, memory cells connected in a single row are called a page. Each bitline on a memory array is connected with a series of sense amplifiers (SA). A series of sense amplifiers is also known as the row-buffer. During a read operation, the bitlines are precharged to a certain voltage level. Once the appropriate row is selected, the bitline voltage is interrupted. The sense amplifier senses this voltage perturbation and latches the corresponding data. Then the appropriate selection of the columns drives the sense amplifier data to the output. On the other hand, the sense amplifier acts as a buffer to hold the write data during the write operation. Once the target memory cell is activated via appropriate address selection, the memory cell latches the data from the row-buffer. Depending

<sup>&</sup>lt;sup>2</sup>memory size is expressed as  $r \times c \times w$ , where, r = number of rows, r = number of columns, and w = word size in bits.

on memory type, each memory cheap may have different memory cell structures. In following subsequent paragraph we discuss necessary details of different memory cell structure associated with the memory hierarchy-

- 1. **Registers:** In multi-core microprocessors, each core has its own set of private registers (not shown in fig. 2.2) and can be directly accessed. Registers are very fast, but only a small amount of data can be stored. Usually, modern CPUs' registers are implemented with specially designed high speed SRAM cells.

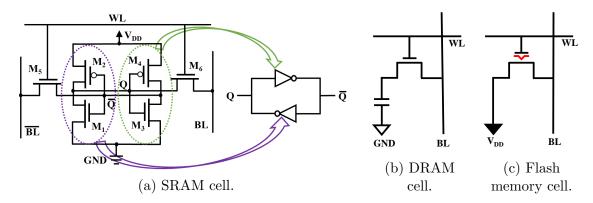

- 2. Cache memory: Cache memory is made of SRAM and usually divided into multiple levels; some of the levels are private to the individual CPU core, and some can be shared among the cores [JWN10]. The size of the cache memory can be ranged between a few hundred bytes to a few Mbytes. Although many different structures of SRAM cell exists [RSS17, AKJ+13, CMK+07, CMN+08], the 6-transistor (6T) SRAM cell is the most popular form among them (shown in Figure 2.4a). A 6T SRAM cell is made of two coupled inverters along with two access transistors. The access transistors are controlled by wordline (WL) and connect the memory cell to the bitleines (BL and BL). The BL and BL provide a complementary logic pair during the read (or write) operation. After the write operation, the memory cell maintains the desired logic by creating a logic-loop between the coupled inverter-pair.

- 3. Main memory: In most of the computer system, DRAM (dynamic random-access memory) serves as the main memory. DRAMs are cheaper and larger (a couple of hundred Mbytes to a couple of TBytes) than SRAMs. Although the smaller DRAM cell structure reduces silicon die cost, the DRAM operations are more complex, slower, and energy-consuming than the SRAM. A DRAM cell consists of two components- an access transistor and a capacitor to hold the charge (Figure 2.4b). The access transistor connects the capacitor with a bitline and

Figure 2.4: Basic memory cell structure.

Figure 2.5: DRAM timing at read cycle.

is controlled by the wordline. The state of charge in the capacitor determines the memory content (i.e., "1" or "0"). Depending on the DRAM design, DRAM memory cells can be categorized into true-cell and anti-cell [LJK+13]. A true-cell stores logic '1' with a fully charged capacitor and "0" with an empty capacitor. On the other hand, an anti-cell stores "0" with a fully charged capacitor and "1" with an empty state. Nonetheless, the stored charge in the capacitor leaks away, which leads to an incorrect reading after a certain amount of time. So, to ensure the integrity, the content of a DRAM cell needs to be refreshed periodically before the memory contents flip. This time interval is known as the Retention time, which is 32 or 64 milliseconds (ms) [JED12]. A failure to refresh before the retention time can alter the memory content. To write/access the cell content, the column (or bitline) voltage need to be precharged at a specific reference voltage  $(V_{ref} = \frac{V_{DD}}{2})$ . Figure 2.5 presents a simplified version of DRAM read operation [CKH+16]. A read operation starts with an ACTIVATE (ACT) command ex-

ecuted by the memory controller.  $t_{RCD}$  is called the Activation latency which is required to activate (turn ON) the access transistor properly. The activated access transistor creates a conducting path between the storage capacitor and the bitline. The charge stored in the capacitor perturbs the bitline voltage. The sense-amplifier senses the perturbed voltage and amplifies it to an appropriate binary value. At this moment, the memory controller applies the READ command to read the data and fetch it to the data bus. The minimum time latency between the READ command and the first data bit to appear in data-bus is called Column Access Strobe latency or CAS latency  $(t_{CL})$ . DRAM's read operation is a destructive process. Therefore, the charge on the DRAM storage capacitor needs to be restored after each successful reading. The time required to activate an access transistor and to restore the charge on the corresponding storage capacitor is known as the Row Active latency or Restoration latency  $(t_{RAS})$ . At the end of the restoration process, the memory controller again applies the PREcommand to re-initiate all the bitlines for the next read/write operation. The PRE command precharges all bitlines to  $V_{ref}$ . The time required to precharge all bitlines properly is called *Precharge* time  $(t_{RP})$ . The *PRE* command also deactivates all previously activated access transistor. The  $t_{RAS} + t_{RP}$  is the total time required to read a DRAM row properly; this total time is called Row Cycle Time  $(t_{RC})$ .

4. Storage memory: Storage memory is a non-volatile memory (e.g., flash memory, magnetic hard drive) which is used to store and recall information that is previously used. The storage memories are very cheap and large in volume. However, they are extremely slow, energy consuming, and their endurance (i.e., number of write cycles) is very limited. Usually, storage memories are integrated with a controller that evenly distributes the writing operation on all memory

blocks (wear-leveling |Cha07|) to maximize the service life of the storage memory. Although many forms of storage memory devices exist, flash memories have become very popular in past decade as they are faster and more reliable than the traditional hard disk drive. A basic structure of a flash memory cell is shown in Figure 2.4c [KBTS<sup>+</sup>18]. The flash memory cells consist of only one specially designed access transistor. Unlike a regular transistor, this transistor has a floating gate (red marked in Figure 2.4c) underneath the main control gate. When a high voltage is applied to the control gate, electrons tunnels through the oxide layer and accumulate on the floating gate. This process results in the transistor being non-conductive while the regular voltage is applied to the control gate. A charged floating gate represents logic "0" (program state), whereas the noncharge state represents logic "1" (erase state) in the Flash memory cell. A large negative voltage is applied to the control gate to erase the data (i.e., converting "0" to "1") from the flash memory cell. The negative voltage on the control gate removes the electrons from the floating gate. During the read operation, the active wordline causes the bitline to be shorted with  $V_{DD}$  if logic "1" is stored (consequently, sense amplifier senses the logic "1"). Otherwise, the bitline retains its initial voltage, and the sense amplifier latches logic "0".

## 2.3.2 Basic Principle of Memory-based PUFs (mPUFs)

Almost all types of memory chips can be performed as a standalone PUF. In this section we discuss the basic principle of few popular mPUFs using different types of memory technologies.

SRAM PUFs: Among different mPUFs, SRAM PUF is the most popular type and commercially available in many commodity devices. The SRAM PUF takes

advantage of the slight asymmetricity of the coupled inverters, which is arisen from the random variation of the manufacturing process. Ideally, the cross-coupled inverters are symmetrically laid out to maximize the static noise margin (SNM)[G<sup>+</sup>18, CDHS12]. SNM is defined as the maximum allowable noise that can tolerate an SRAM cell without flipping its value [MMR10]. However, the inevitable random dopant fluctuation (RDF) effect leads to threshold voltage variation and introduces asymmetricity between SRAM inverters [KCL+12]. Therefore, during power-up, these two inverters race each other and settle to "1" or "0" [G+18, CDHS12]. In SRAM PUF, this random power-up (or start-up) is used as the PUF signature. Although SRAM PUFs are very cheap and robust compared to other mPUFs, the disadvantage of SRAM PUF is, it requires an entirely new power cycle for evaluation. **DRAM PUFs** (**DPUFs**): Recently, DPUFs have also gained a lot of attention as modern computers are equipped with large DRAM systems. Due to the large capacity, DRAM PUFs can produce a very large set of CRPs and almost provide a similar capability of strong PUFs. Researchers have been proposed multiple approaches to produce DRAM-based signatures-

1. Retention-based DPUFs: Signatures are generated by disabling the refresh interval for a certain and sufficient amount of time [SRR16, KPHM18]. The DRAM cells are leaky, and therefore, the DRAM contents need to be refreshed periodically, usually 64ms or 32ms according to the JEDEC specification [JED12], to ensure the data integrity [SRR16]. Failing to refresh periodically within this time interval introduces errors due to the leaky property of DRAM cells. The error pattern generated from the retention failure is unique from chip to chip and is used to generate device signatures [SRR16, KPHM18]. Although, Retention-based DRAM PUFs are robust, they are significantly slow compared to other DPUFs and take in order of a minute to evaluate.

- 2. Latency-based DPUFs: The reduction in  $t_{RCD}$  introduces erroneous read/write operation (see Section 2.3.1), which can be used to generate device signatures [KPHM18]. This latency-based PUF generates signature at a much faster rate [KPHM18]. The reported result shows that the mean evaluation time is  $\sim 88.2$ ms (outperforms all previously proposed retention-based DPUF [SRR16, XSA+16, KGKF14]). However, it still requires multiple row cycles to evaluate the PUF response. This latency-based DPUF also needs a filtering mechanism in each access that adds both hardware and computational overheads. To overcome this problem, we have proposed a novel technique to evaluate DPUF by reducing the precharge time  $(t_{RP})$  [BTRFR19]. Reducing  $t_{RP}$  also causes erroneous output. Our experimental result showed that a subset of DRAM cells (which can be selected in the early characterization phase) generates a reproducible signature with reduced  $t_{RP}$ . Our proposed technique is much straight-forward and faster than previous latency-based DPUF (i.e., by reducing  $t_{RCD}$ ).

- 3. Start-up-based DPUFs: In start-up based DPUF [TKYC16], the device signature is generated from the start-up states of DRAM cells. Initially, the bitlines are charged to  $\frac{V_{DD}}{2}$ . But the process variations on the storage capacitor and bitline capacitance slightly deviate the bitline voltage to  $\frac{V_{DD}}{2} + \delta$  or  $\frac{V_{DD}}{2} \delta$ , where δ represents a small voltage. The sense-amplifier senses the voltage difference and latches "1" or "0". Consequently, upon power-up, the DRAM cells generate "1"s and "0"s randomly. Similar to SRAM PUF, start-up-based DPUFs also require a new power cycle. Unfortunately, adding a new DRAM power cycle is expensive, as it requires storing the whole DRAM data to a secure memory location at each cycle. Hence, in practice, start-up-based DPUFs have very limited use.

- 4. Rowhammer DPUFs: The errors caused by the rowhammer disturbance are used to generate device signatures [SXA<sup>+</sup>17, AAF<sup>+</sup>18]. Rowhammer is a pro-

cess where a DRAM cell is repeatedly accessed. Such repeated operation causes partial activation to its adjacent rows (due to the coupling capacitance) and may cause data corruption at adjacent rows. The average evaluation time of a rowhammer PUF is in order of minutes and has an almost similar performance of Retention-based DPUFs. However, all DRAMs are not vulnerable to rowhammer [SXA+17]; hence, it is not a universal method to generate DRAM signature.

Flash PUFs: Recently, many researchers have proposed efficient implementation using flash memory chips. The most popular form of flash memory PUFs relies on three different techniques- (i) partial programming, (ii) partial erasing, and (iii) program disturbance [SMRR20, JXW<sup>+</sup>15]. Due to the random process variation, the program time and erase time vary from cell to cell. In partial programming and partial erasing methods, the program or erase voltage is applied on the control gate (Figure 2.4c) for a shorter time. However, the time period is selected in such a way so that it causes random bit failure in the flash chip. This erroneous output of the flash chip can be used as the device signature. In the program disturbance method, random bit failures are induced by repeatedly programming adjacent cells. It has been observed that if a memory cell is repeatedly programmed with high voltage, the adjacent cell also might get programmed (i.e., "1" to "0") due to the parasitic coupling (or parasitic capacitance) between these two cells. As the random process variation affects the parasitic capacitance, the bit flipping due to the program disturbance also creates a random pattern, which can be essentially used as the PUF signature. Although the flash chips are capable of producing a very large set of CRPs, the flash chips are much slower. Furthermore, flash memories have much smaller endurance (wears out with a small number of program-erase cycles); hence, using flash memory chips as a PUF causes the device's early failure.

#### 2.4 mPUF Applications

mPUFs can potentially be used in two different applications- (i) counterfeit IC detection on semiconductor supply chain and (ii) as a secure key generator in different cryptographic applications [MBW<sup>+</sup>19, HYKD14].

#### 2.4.1 Anti-counterfeiting Solution

Semiconductor Supply Chain Vulnerability: In recent times, IC counterfeiting has become a global problem due to the globalization of the semiconductor supply chain. In this model, a chip is designed in one place while fabricated in a different place and involves several parties to reduce the fabrication cost and time to market. Because of traveling IPs in different formats and involvement of untrusted parties, the modern semiconductor supply chain suffers from counterfeiting (such as hardware trojan or malicious change in third-party IP or chip layout, cloning IPs/ICs, remarking, etc.) [FC18, GHD<sup>+</sup>14, BTMR<sup>+</sup>20, BB15, RFS<sup>+</sup>14, CRT13]. Figure 2.6 shows the IC design flow for authentic-chip and pirated-chip production cycle. The untrusted party (the third-party IP developer, the foundry, the assembly, the distributor, etc.) can perform counterfeiting at different phases of the manufacturing process. An untrusted party can send out overproduced, and out-of-spec/defective ICs to the market. The untrusted party also can clone the original chip by stealing IPs or by reverse-engineering (from a post-fabricated product) to avoid research and development (R&D) costs. Table 2.1 defines each type of counterfeiting more elaborately.

To avoid/detect counterfeit chips, researchers proposed many countermeasures, such as SST, hardware metering, blockchain-based traceability, split manufacturing, IC camouflaging, Electronic Chip ID (ECID), On-chip sensor, DNA marking, etc.,

Figure 2.6: IC design flow vs possible covert channels to introduce counterfeit ICs.

| Counterfeit<br>Type       | Definition [FC18, GHD <sup>+</sup> 14]                                                                                                                                                                                                                         |  |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Recycled                  | Recycling chips from old PCB and selling them as new. In a more sophisticated recycling process, the plastic/ceramic encapsulation of the chip die is removed and repackaged to make its appearance new. Recycled chips shares >80% of the counterfeit market. |  |  |  |  |  |

| Remarked                  | Inferior quality chips are marked as the superior one.                                                                                                                                                                                                         |  |  |  |  |  |

| Forged                    | Faking the chip documentation (e.g., faking safety and security                                                                                                                                                                                                |  |  |  |  |  |

| documented                | certification).                                                                                                                                                                                                                                                |  |  |  |  |  |

| Reverse<br>Engineered     | Recover the functional netlist from the chip by an electrochemical process. Counterfeiter may use this netlist to avoid the R&D cost.  A untrusted party (e.g., physical design house) can copy the chip                                                       |  |  |  |  |  |

| Cloned                    | design (netlist, GDSII); later, they can produce unauthorized chips.                                                                                                                                                                                           |  |  |  |  |  |

| Overproduced              | Untrusted fabrication facility can produce and market chips outside of the contract, i.e., without authorization of the IP (intellectual properties) owner.                                                                                                    |  |  |  |  |  |

| Tampered                  | Tampering the original chip design. For example, untrusted physical design house can insert hardware trojan in the netlist and create a security backdoor.                                                                                                     |  |  |  |  |  |

| Out-of-<br>spec/defective | Selling chips that are failed in the functionality test.                                                                                                                                                                                                       |  |  |  |  |  |

Table 2.1: Different types of IC counterfeitings.

might be used to prevent counterfeiters [GHD<sup>+</sup>14, FC18, RFS<sup>+</sup>14, RSK13, KQP01, AEM18, GFT16, ZT14, HHT15, HCM13, AK07, ZTT12, HM11, EBM12, IPK18, RSSK13, WGR<sup>+</sup>17, ZWRT18]; however, these techniques suffer from different drawbacks. For example, SST and hardware metering techniques provide control over post-fabrication, but it requires a change in traditional fabrication flow. Furthermore, this technique requires exhaustive communication between the foundry and the manufacturer. On the other hand, ECID tags each chip with a unique ID by adding a one-time programmable (OTP) memory. Nevertheless, this method is not suitable for all kinds of chips. For example, the overhead of adding an extra OTP memory component will be very high for an small microcontroller. With an on-chip sensor, each chip is equipped with an additional hardware component, which modifies its properties due to aging. These properties can be used to detect recycled chips. However, on-chip sensor-based countermeasures need additional hardware overhead and are not feasible for inexpensive systems. In DNA marking, each memory component is marked with a unique DNA sequence. DNA marking suffers from impracticality as it requires a complex authentication scheme. Other techniques, such as blockchain-based traceability, split manufacturing, IC camouflaging, etc., require modified fabrication flow or design techniques that are not suitable for lowcost memory chips.

Physical inspection-based schemes [GHD+14, WKP14, ABN+16, H+16], such as X-Ray imaging and scanning electron, can detect counterfeit/recycled chips. However, these techniques require expensive equipment and not viable for low-cost chips. Moreover, expensive equipment and complex authentication schemes are also not suitable for general users who want to verify their purchased products' authenticity. **PUF-based Anti-counterfeiting Solutions:** PUF based anti-counterfeiting solution is quite straightforward; the simplified PUF-based anti-counterfeit solution

is shown in Figure 2.7a [MBW<sup>+</sup>19]. This authentication technique is a two-step process. The first step is known as the enrollment or registration process, where the manufacturer creates a database by recording a pair of CRP from each device. This step must be completed before releasing devices into the market, and the databases must be maintained by the manufacturer or by a trusted third party. In the authentication phase, the device sends an authentication request to the manufacturer; in reply, the manufacturer sends the same challenge (as of the enrollment phase) to the manufacturer. Now, the device generates the PUF signature corresponds to the challenge and sends it to the manufacturer. The manufacturer verifies the response by comparing the response with the database. For an authentic device the response should be matched with the database within a small threshold.

PUFs can directly identify overproduced, remarked, cloned, reverse engineered IC [GHD<sup>+</sup>14, GFT13]. Additionally, with a typical usage pattern, bit error in mPUF signature usually increases with device age (see Section 3.6 for more details). Hence, recycled IC can be easily identified by analyzing the degree of signature mismatch with the manufacturer's database [GMAS<sup>+</sup>17]. Moreover, the PUF-based key can also identify the device's integrity as a root-of-trust (discussed in Section 2.4.2) and potentially identify tampered devices [vH18, ZZH<sup>+</sup>14]. Although both traditional strong PUFs and mPUFs can be used to identify counterfeit chips, the advantage of mPUF is that it can be readily used for any device which contains a memory chip. Although PUF based technique is simple, it requires maintaining a large database which is expensive. Besides, it adds an extra step in the supply chain and increases market lead time. Furthermore, as described in Figure 2.7a, many small devices are not configured to maintain a network protocol; hence, they cannot be authenticated by this protocol.

Table 2.2 summarizes different types of available anti-counterfeit solutions, their applicability, relative complexity and cost.

Figure 2.7: PUF applications.

## 2.4.2 Cryptrographic Key Extraction from PUF Signature

mPUF are capable of generating cryptrographic key on fly. Almost all PUFs follow a similar key extraction scheme as shown in Figure 2.7b [CSP15, SD07, CZZ17]. PUF-based key extraction consists of two phases. In the key enrollment/generation phase, the PUF device generates a response  $R_{C^i}$  depending on a given challenge  $C_i$ . Then, an ECC (Error Correction Code) encoder computes the corresponding error correction code/helper data  $h_{C^i}$  and generates the key,  $K(R_{C^i})$  (e.g., using hash). Although the final key is not stored, the  $C_i$  and corresponding helper data  $h_{C^i}$  is stored in a storage device. In the key re-generation phase, the PUF circuits again receive the same challenge  $C_i$ , and generates the corresponding response  $R'_{C^i}$ . Due to the different internal and external noises (variations in operating condition, device aging, etc.), some errors are always expected in the generated response  $R'_{C^i}$

| ability           | Non-memory                    | Yes                                         | Yes                             | Yes                             | Yes                  | Yes        | Yes                                          | Yes                              | Yes                                                      | Yes                                   | Yes                                | $ m Yes^{\S}$                       |

|-------------------|-------------------------------|---------------------------------------------|---------------------------------|---------------------------------|----------------------|------------|----------------------------------------------|----------------------------------|----------------------------------------------------------|---------------------------------------|------------------------------------|-------------------------------------|

| Applicability     | Memory<br>chips               | Yes                                         | Yes                             | Yes                             | Yes                  | Yes        | Yes                                          | Maybe                            | Yes                                                      | Yes                                   | Yes                                | Yes                                 |

| Cost <sup>∇</sup> |                               | High                                        | High                            | High                            | Low-High             | Low        | Medium                                       | High                             | High                                                     | High                                  | High                               | High                                |

| Complexityr       |                               | High                                        | Low                             | Medium                          | Low-High             | High       | High <sup>‡</sup>                            | Medium                           | Medium                                                   | Medium                                | Medium                             | Medium                              |

|                   | gisəb əriupəA<br>noitsəfiibom | Yes                                         | Yes                             | Yes                             | $Yes^*$              | Yes        | $\mathrm{No}^2$                              | Yes                              | No                                                       | No                                    | No                                 | No                                  |

|                   | \osque-fo-tuO<br>evitoeled    | Yes                                         | No                              | No                              | No                   | No         | No                                           | No                               | No                                                       | Maybe Maybe                           | Maybe                              | Yes Maybe Maybe                     |

|                   | Tampered                      | No                                          | No                              | No                              | No                   | No         | No                                           | No                               | No                                                       | Maybe                                 | No                                 | Maybe                               |

| ing               | Overproduced                  | Yes                                         | No                              | Yes                             | Yes                  | No         | Yes                                          | No                               | No                                                       | No                                    | No                                 | Yes                                 |

| of counterfeiting | Cloned                        | Yes                                         | No                              | Yes                             | Yes                  | Maybe      | Yes                                          | No                               | No                                                       | No                                    | No                                 | Yes                                 |

| ot cou            | Reverse<br>Engineered         | No                                          | No                              | No                              | Yes                  | Yes        | No                                           | Yes                              | No                                                       | No                                    | No                                 | Yes                                 |

| Types             | Forged<br>Documented          | No                                          | No                              | No                              | No                   | Yes        | No                                           | No                               | No                                                       | No                                    | No                                 | No                                  |

|                   | Remarked                      | No                                          | Yes                             | No                              | Yes                  | No         | No                                           | No                               | Maybe Maybe                                              | Maybe                                 | Maybe                              | Yes                                 |

|                   | Recycled                      | No                                          | Yes                             | No                              | No                   | No         | No                                           | No                               | Maybe                                                    | Maybe Maybe                           | Maybe                              | Yes                                 |

| Methods           |                               | SST [RFS <sup>+</sup> 14]                   | On-chip sensor<br>[HHT15, ZT14] | Hardware metering [KQP01, AK07] | Chip tagging [EBM12] | Blockchain | Others Split-<br>[IPK18] manufacturing       | [RSK13] IC [RSSK13] camouflaging | Physical Inspection-<br>based test [GHD <sup>+</sup> 14] | Electrical test [GHD <sup>+</sup> 14] | burn-in test [GHD <sup>+</sup> 14] | PUF-based<br>authentication [GFT13] |

|                   |                               | Counterfeit-resilient<br>chip manufacturing |                                 |                                 |                      |            | Post-fabrication<br>chip<br>characterization |                                  |                                                          |                                       |                                    |                                     |

Table 2.2: Summary of counterfeit chip detection/identification methods.

<sup>T</sup>Combined complexity of supply chain, communication protocol, and IC fabrication flow. <sup>V</sup>Combined cost of extra computation, hardware, and infrastructure (e.g., server).

<sup>§</sup>PUF circuits are required to be integrated. \*Might Require special packaging. <sup>†</sup>Requires complex supply management.

(compared to  $R_{C^i}$ ). However, corrected response  $R''_{C^i}$  is computed using the helper data  $h_{C^i}$ . Subsequently, the key,  $K(R''_{C^i})$ , is generated from the  $R''_{C^i}$ . If the PUF circuit is not altered in between these two phases, the  $K(R_{C^i})$  and  $K(R''_{C^i})$  should be the same.

Fuzzy Extractor: The Fuzzy extractor is used to enhance the security of the PUF-based key [FRS20, FRS16, CFP<sup>+</sup>16, Boy04, KHK<sup>+</sup>14]. The security enhancement is performed by (i) removing noise without leaking significant information and (ii) extracting the entropy (i.e., increase the entropy density on fuzzy extractor's output) [FRS20]. Theoretically, the fuzzy extractor combines an ECC encoder/decoder (secure sketch) and a hash function [DGV<sup>+</sup>16]. However, instead of using a fixed-sized hash output, the length of the output depends on the entropy of the fuzzy extractor's input. If the input has smaller entropy, it reduces the output size and increases the entropy density of the key.

$$R_{\mathcal{C}^i} \longrightarrow \begin{matrix} \mathsf{Gen} & \to & K(R_{\mathcal{C}^i}) & & R_{\mathcal{C}^i}' & \\ & \to & h_{\mathcal{C}^i} & & h_{\mathcal{C}^i} & \end{matrix} \longrightarrow K(R_{\mathcal{C}^i}')$$

Figure 2.8: Rep and Gen block of fuzzy extractor.

The fuzzy extractor has two major blocks: (i) a generate algorithm (Gen) in the key generation phase and (ii) a reproduce algorithm (Rep) in the re-generation phase (Figure 2.8). The Gen and Rep replace the components from the red and magenta boxes of Figure 2.7b, respectively. The Gen takes the raw PUF response  $R_{C^i}$  and produces the output key  $K(R_{C^i})$  and  $h_{C^i}$ . In the re-generation phase, the Rep takes the noisy input  $R'_{C^i}$  and  $h_{C^i}$  and produces the corrected key  $K(R''_{C^i})$ . The noisy behavior of PUFs requires to allow some errors, which reduce the entropy of the input PUF key (R). A well-designed fuzzy extractor can avoid this problem by adding a penalty on output key length. Mathematically, it can be shown that the output key is secured as long as the length of the output key does not exceed

the fuzzy min-entropy [FRS20, FRS16]. The fuzzy min-entropy  $(H_{\infty}^{fuzzy})$  of a fuzzy extractor is defined as follows-

$$H_{\infty}^{fuzzy}(\mathcal{R}) = -\log \max_{R'} \{ Pr[\mathcal{R} \in B_q(R')] \}$$

(2.4)

Here,  $\mathcal{R}$  is the distribution of the original response R and q is the number of allowed erroneous bits. To maximize the chance; the attacker would select R' that maximize the total probability mass of all responses (drawn from distribution  $\mathcal{R}$ ) within the ball  $B_q(R')$  of radius q around R' [FRS20, FRS16]. The main difficulty of designing the fuzzy extractor is to estimate  $Pr[\mathcal{R} \in B_q(R')]$ . For a reasonable estimation of the probability distribution, one might require a large number of sample sources. Moreover, an attacker can always make a better probabilistic estimation with a larger set of samples [FRS20, FRS16].

Application of mPUF Key: There are two possible scenarios of mPUF applications. In the first type of application, mPUF is used inside the device and is not accessible from outside. Example of such application is software IP protection, securing key vault, and establishing the root of trust [MBW+19, HYKD14, ZZH+14]. For software IP protection and securing key vault, the PUF key is used to encrypt/decrypt the storage device while the storage device is being used to store the software IP or the users' key. As the PUFs generate the key on the fly, an attacker cannot clone the encrypted storage memory and use the content in another device. Similarly, the mPUF key can also be used to check the software and hardware integrity of the device at the boot-up stage (i.e., establishing the root of trust or a trusted execution environment) [ZZH+14, vH18]. In the most simplest technique, the security module of the computing system (e.g., trusted platform module) hashes the software and hardware information by salting with the PUF key. Then, the security module compares this hash value with the hash value of the previous boot

and identifies if there is any unauthorized hardware or software tampering between these two boots.

Figure 2.9: Simplified mPUF-based IOT device authentication protocol.