# Southern Methodist University

# SMU Scholar

**Electrical Engineering Theses and Dissertations**

**Electrical Engineering**

Fall 2022

# An Efficient Integrated Circuit Simulator And Time Domain Adjoint Sensitivity Analysis

Jiahua Li Southern Methodist University, li\_jiahua\_java@163.com

Follow this and additional works at: https://scholar.smu.edu/engineering\_electrical\_etds

Part of the Computational Engineering Commons, and the Electrical and Electronics Commons

#### **Recommended Citation**

Li, Jiahua, "An Efficient Integrated Circuit Simulator And Time Domain Adjoint Sensitivity Analysis" (2022). *Electrical Engineering Theses and Dissertations*. 62. https://scholar.smu.edu/engineering\_electrical\_etds/62

This Dissertation is brought to you for free and open access by the Electrical Engineering at SMU Scholar. It has been accepted for inclusion in Electrical Engineering Theses and Dissertations by an authorized administrator of SMU Scholar. For more information, please visit http://digitalrepository.smu.edu.

# AN EFFICIENT INTEGRATED CIRCUIT SIMULATOR AND TIME DOMAIN ADJOINT SENSITIVITY ANALYSIS

Approved by:

Dr. Ronald Rohrer – Committee Chairman Professor of ECE department

Dr. Duncan Macfarlane Professor of ECE department

Dr. Jennifer Dworak Professor of ECE department

Dr. Peter Raad Professor of ME department

Dr. Prasanna Rangarajan Assistant Professor of ECE department

#### AN EFFICIENT INTEGRATED CIRCUIT SIMULATOR AND TIME DOMAIN ADJOINT SENSITIVITY ANALYSIS

A Dissertation Presented to the Graduate Faculty of the

Lyle School of Engineering

Southern Methodist University

in

Partial Fulfillment of the Requirements

for the degree of

Doctor of Philosophy

with a

Major in Electrical and Computer Engineering

by

Jiahua Li

B.S., ME, Harbin Institute of Technology, 2012 M.S., ECE, Southern Methodist University, 2016

December 17, 2022

Copyright (2022)

Jiahua Li

All Rights Reserved

#### ACKNOWLEDGMENTS

During the past five years, a lot of things changed my life. On the way of proceeding the research, my doubt, hesitation, anxiety, and uncertainty became confidence, creativity, and hope. Now, I know I made the best decision to be a PhD student at SMU and I know I could not make it without a great deal of help.

First of all, I would like to express my sincere appreciation to my advisor Dr. Ron Rohrer for his advice, support and confident attitude that guided me through the development of the research work presented here. His insight in discovering the topic of research that not only triggers the interest of academics but also the industries, and his connections secured my intellectual curiosity so that I always had access to the correct source of knowledge.

I would like to thank Kiran Gullapalli and Brian Mulvaney for providing the internship opportunity at NXP and leading me to appreciate the industrial approach to the production of EDA tools.

Finally, I would like to thank all my family members for their encouragement and patience. Their support that crossed the Pacific Ocean means a lot to my abroad life.

#### STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of the requirements for an advanced degree at Southern Methodist University and is deposited in the university library to be made available for borrowers under the rules of the library.

Brief quotations from this dissertation are allowable without special permission, provided that an accurate acknowledgement of the source is made. Request for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the copyright holder.

B.S., Harbin Institute of Technology, 2016M.S., Southern Methodist University, 2018

#### An Efficient Integrated Circuit Simulator and Time Domain Adjoint Sensitivity Analysis

Advisor: Ron Rohrer

Doctor of Philosophy conferred: December 17, 2022

Dissertation completed: December 17, 2022

Electronic Design Automation (EDA) algorithms provide irreplaceable support for the definition, design, implementation, and verification of semiconductor integrated circuits because modern designs require novel analysis tools. The complexity of state-of-the-art devices makes the run times unaffordable unless accurate and efficient simulations are provided.

This dissertation proposes a static-driven integration method which enhances the efficiency and accuracy of transient analysis and a time domain adjoint sensitivity method which in only a single simulation calculates the sensitivities of all the node voltages with respect to all the designated parameters. The applications of both methods include pseudo transient direct current biasing convergence and time domain noise analysis are explored. The error analysis of the time domain adjoint sensitivity is thoroughly studied to ensure the accuracy of the transient sensitivity responses. The proposed method has been developed as an extension of XYCE, which is an opensource derivative of Simulation Program with Integrated Circuit Emphasis (SPICE). Various circuit examples which are constructed with industry standard models are tested on the platform.

## TABLE OF CONTENTS

| LIST OF FIGURES xx                              |

|-------------------------------------------------|

| LIST OF TABLES xii                              |

| LIST OF ABBREVIATIONS xiviii                    |

| CHAPTER 1 1                                     |

| 1.1 Research Motivation and Contribution1       |

| 1.2 Dissertation Organization                   |

| CHAPTER 2                                       |

| 2.1 Device Modelling                            |

| 2.2 Nodal Analysis7                             |

| 2.3 System Matrix Forming                       |

| 2.4 Steady State Analysis                       |

| 2.5 Forward/Backward Euler Transient Analysis14 |

| 2.6 Background Summary 17                       |

| CHAPTER 3 19                                    |

| 3.1 Step Response                               |

| 3.2 Static-driven Algorithm                     |

| 3.3 Integration Error Control                   |

| 3.4 Performance Evaluation                      |

| 3.5 Pseudo transient DC convergence applying static driven method |    |

|-------------------------------------------------------------------|----|

| CHAPTER 4                                                         |    |

| 4.1 DC/AC Adjoint Sensitivity Analysis                            |    |

| 4.2 Forward-In-Time Adjoint Analysis                              | 53 |

| 4.3 Examples And Error Accumulation Analysis                      | 57 |

| 4.4 Time domain noise analysis applying adjoint sensitivity       |    |

| CHAPTER 5                                                         | 72 |

| 5.1 Summary                                                       | 72 |

| 5.2 Future work                                                   | 73 |

| APPENDIX                                                          | 74 |

| BIBLIOGRAPHY                                                      | 75 |

# LIST OF FIGURES

| Figure 2.1 Branch information for a generic two-terminal device                                  |

|--------------------------------------------------------------------------------------------------|

| Figure 2.2 MOSFET and its abstracted branch information                                          |

| Figure 2.3 A simple circuit example7                                                             |

| Figure 2.4 The topology abstraction of Fig.2.3                                                   |

| Figure 2.5 Element stamps: (a) for $\partial f / \partial v$ matrix; (b) for <i>e</i> vector     |

| Figure 2.6 Circuit example for explaining steady state analysis                                  |

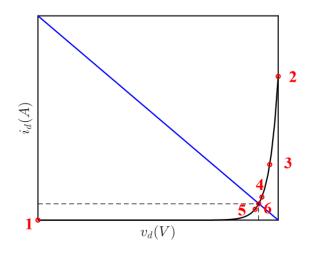

| Figure 2.7 Simple nonlinear circuit ( $v_1$ =0.7 $volt$ ; $r_1$ =1 $ohm$ )                       |

| Figure 2.8 Load line of simple nonlinear circuit shown in Fig. 2.7                               |

| Figure 2.9 NR iteration process of simple nonlinear circuit shown in Fig. 2.7                    |

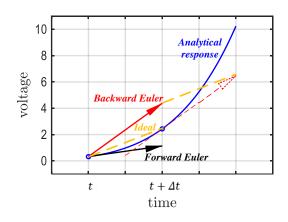

| Figure 2.10 Difference between Forward/Backward Euler integrations from t to $t+\Delta t$        |

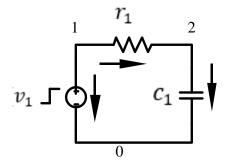

| Figure 2.11 RC circuit with step function as excitation ( $v_1=1volt$ ; $r_1=1ohm$ ; $c_1=1F$ )  |

| Figure 2.12 Transient analysis powered by Forward-Euler with different time steps $\Delta t$     |

| Figure 2.13 Transient analysis powered by Backward-Euler with different time steps $\Delta t$ 16 |

| Figure 3.1 RC example for explanation of step response calculation                               |

| Figure 3.2 Step function response versus steep ramps with various rise times                     |

| Figure 3.3 Step function excitation for general circuit schematic                                |

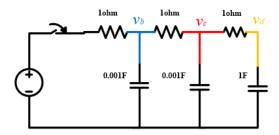

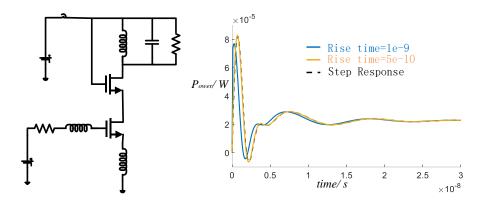

| Figure 3.4 Example stiff system                                                                  |

| Figure 3.5 The gross response of a stiff system in Fig. 3.4                                      |

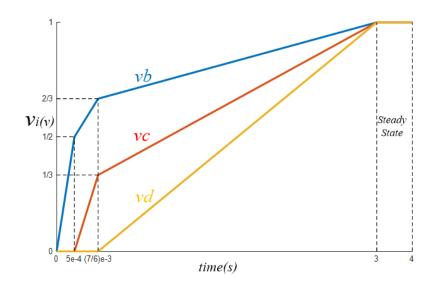

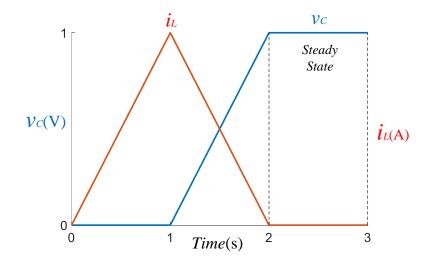

| Figure 3.6 Example underdamped system                                                            |

| Figure 3.7 The gross response of the underdamped system in Fig. 3.6                             | 32   |

|-------------------------------------------------------------------------------------------------|------|

| Figure 3.8 The depiction of the Excursion-limit accuracy control mechanism                      | 34   |

| Figure 3.9 The refined response of $v_b$ for the stiff system shown in Fig. 3.4                 | 34   |

| Figure 3.10 The refined response of $i_L$ for the underdamped system in Fig. 3.6                | 35   |

| Figure 3.11 The refined response of $i_L$ for the underdamped system in Fig. 3.6                | 36   |

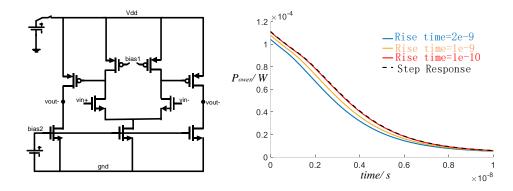

| Figure 3.12 Operational amplifier circuit and its transient response                            | 37   |

| Figure 3.13 Bandgap circuit and its transient response                                          | 37   |

| Figure 3.14 An underdamped nonlinear circuit and its response                                   | 37   |

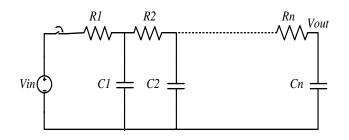

| Figure 3.15 Schematic of an RC ladder circuit                                                   | 38   |

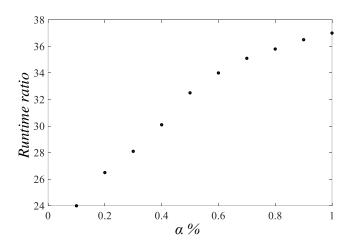

| Figure 3.16 Run-time ratio versus accuracy control parameter with 1000 node RC ladder           | 39   |

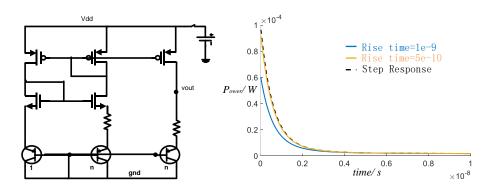

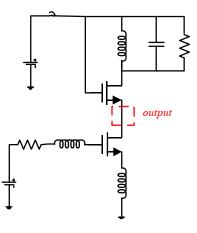

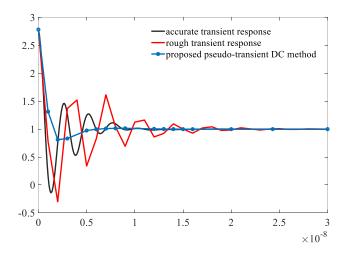

| Figure 3.17 Circuit schematic for an LNA                                                        | 42   |

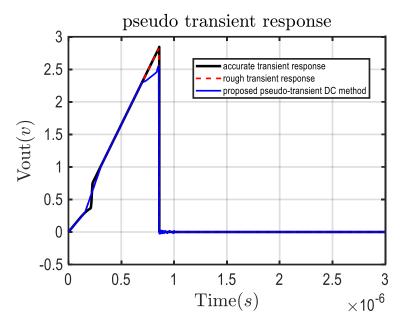

| Figure 3.18 Accurate, rough, and pseudo transient response of the LNA of Fig. 3.17              | 42   |

| Figure 3.19 RC example for explanation of step response calculation                             | 44   |

| Figure 3.20 Accurate, rough, and pseudo transient response of comparator                        | 45   |

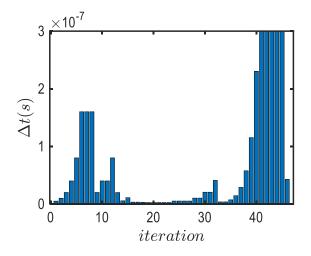

| Figure 3.21 Time step size history of the proposed pseudo transient method                      | 45   |

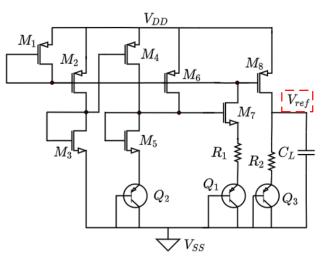

| Figure 3.22 Schematic of the bandgap circuit                                                    | 46   |

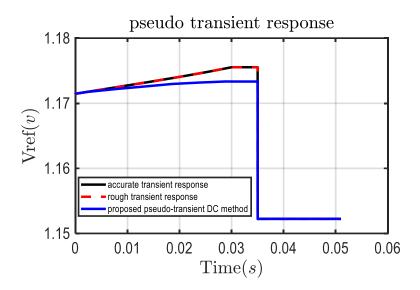

| Figure 3.23 Accurate, rough, and pseudo transient response of the bandgap circuit               | 47   |

| Figure 3.24 Time step size history of the bandgap circuit                                       | 47   |

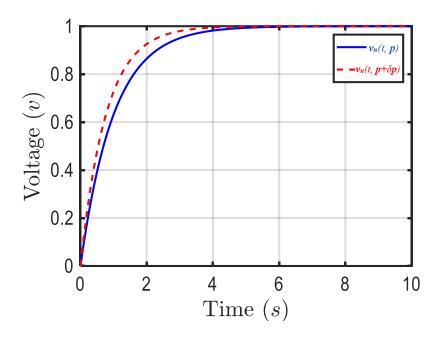

| Figure 4.1 Transient response with parameters $p$ and $(p+\delta p)$                            | 49   |

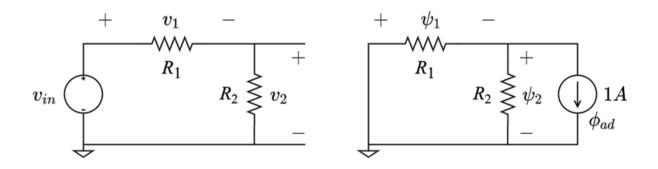

| Figure 4.2 Illustration of original circuit and its corresponding adjoint version               | 50   |

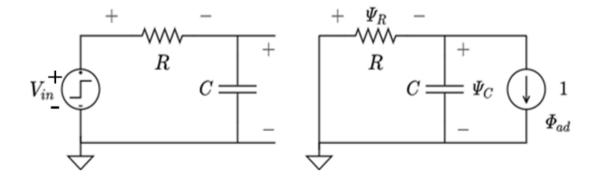

| Figure 4.3 Illustration of the original RC circuit and its adjoint circuit in the frequency dom | nain |

|                                                                                                 | 52   |

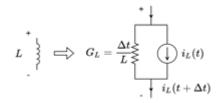

| Figure 4.4 Illustration of the BE companion model for a capacitance                             | 54   |

| Figure 4.5 Illustration of the BE companion model for an inductance                             | 54 |

|-------------------------------------------------------------------------------------------------|----|

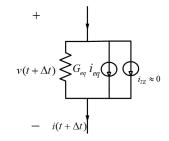

| Figure 4.6 Illustration of the linearized BE companion model for a nonlinear device             | 54 |

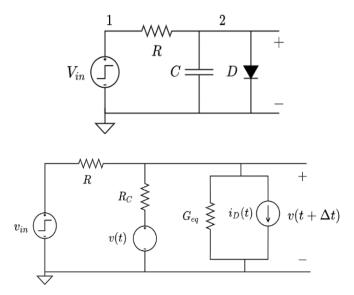

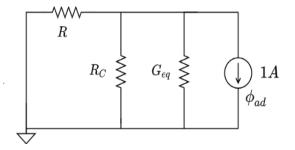

| Figure 4.7 Illustration of an RC Diode circuit and its linearized version at $t+\Delta t$       | 56 |

| Figure 4.8 RC Diode circuit's adjoint version at $t+\Delta t$                                   | 56 |

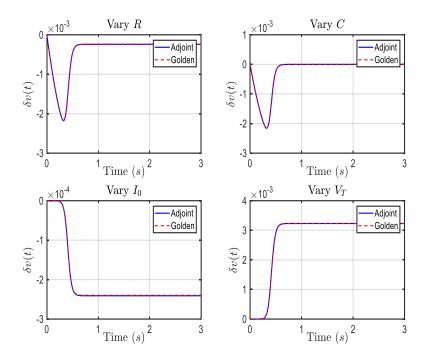

| Figure 4.9 Sensitivities obtained by two methods, the adjoint curve is calculated from (68) and | l  |

| the dashed curve is calculated from the incremental sensitivity                                 | 57 |

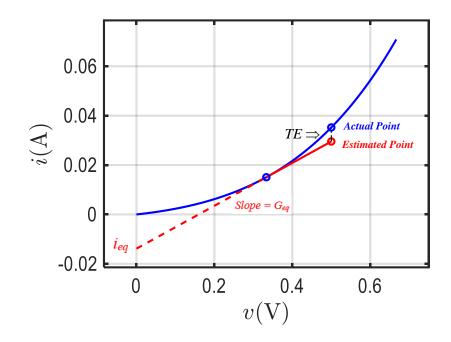

| Figure 4.10 Hypothetical characteristic curve of a nonlinear element                            | 58 |

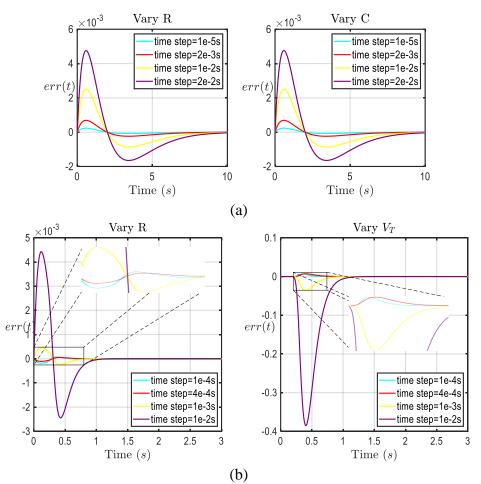

| Figure 4.11 sensitivity error curve for an RC circuit and RCD circuit with different time steps | 60 |

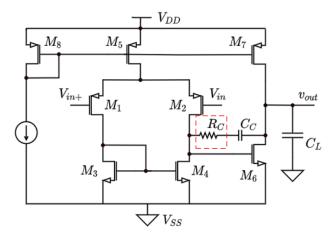

| Figure 4.12 Schematic of an operational amplifier circuit                                       | 60 |

| Figure 4.13 Output voltage sensitivities w/o correction excited by a step function input        | 61 |

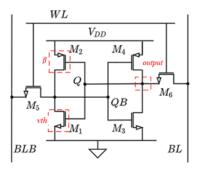

| Figure 4.14 Schematic for an SRAM cell                                                          | 63 |

| Figure 4.15 Sensitivity response for an SRAM cell                                               | 63 |

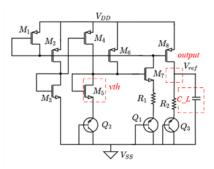

| Figure 4.16 Schematic for a bandgap circuit                                                     | 63 |

| Figure 4.17 Sensitivity response for a bandgap circuit                                          | 64 |

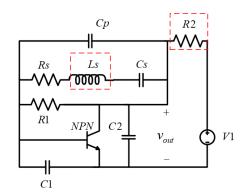

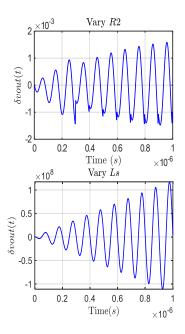

| Figure 4.18 Schematic for an oscillator                                                         | 64 |

| Figure 4.19 Sensitivity response for an oscillator                                              | 65 |

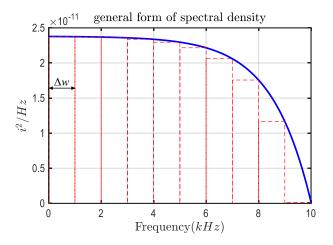

| Figure 4.20 General form of power spectral density                                              | 66 |

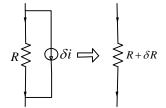

| Figure 4.21 Equivalent noise model representation                                               | 67 |

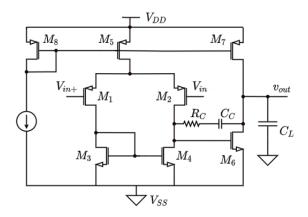

| Figure 4.22 Circuit schematic for a two stage OPAMP                                             | 69 |

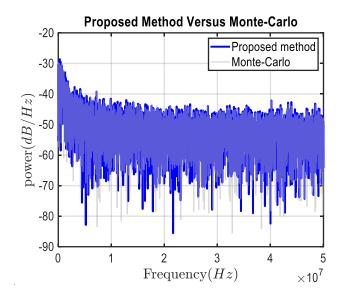

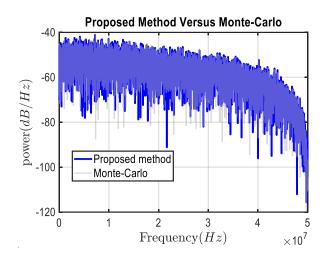

| Figure 4.23 Output noise response of a two stage OPAMP                                          | 70 |

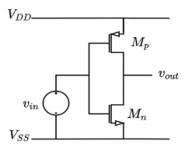

| Figure 4.24 Circuit schematic for an inverter                                                   | 71 |

| Figure 4.25 Output noise response of an inverter                                                | 71 |

## LIST OF TABLES

| Table 2.1 | Characteristic function of two-terminal devices.           | 5  |

|-----------|------------------------------------------------------------|----|

| Table 3.1 | Peak comparisons between ideal step & steep ramp functions | 22 |

| Table 3.2 | Static-driven Pseudo Transient Method                      | 43 |

| Table 3.3 | Pseudo transient performance summary.                      | 46 |

## LIST OF ABBREVIATIONS

| Electronic Design Automation                         | EDA    |

|------------------------------------------------------|--------|

| Simulation Program with Integrated Circuit Emphasis. | SPICE  |

| Direct Current.                                      | DC     |

| Ordinary Differential Equation.                      | ODE    |

| metal-oxide-semiconductor field-effect transistor    | MOSFET |

| Kirchhoff's Voltage Law.                             | KVL    |

| Kirchhoff's Current Law                              | KCL    |

| Forward Euler.                                       | FE     |

| Backward Euler                                       | BE     |

| Voltage Source                                       | vsrc   |

| Current Source.                                      | isrc   |

| Newton-Raphson                                       | NR     |

| Integrated Circuit.                                  | IC     |

| Very Large-scale Integration.                        | VLSI   |

| Truncation Error                                     | TE     |

This is dedicated to my parents.

#### CHAPTER 1

#### **1.1 Research Motivation and Contribution**

The techniques of the integrated circuit (IC) simulation were introduced in the 1960s to supplement the circuit design engineer's hand calculations. Back then, the design of an integrated circuit with tens of transistors was too cumbersome to be affordable because of the complicated nonlinearity and each new generation of circuit has become ever more complex. Based on that, a computer-aided pre-manufacturing circuit simulator had been developed to keep up with the blooming demands. Such a simulator solves a set of nonlinear ordinary differential equations (ODE's) that describe a circuit's behavior. With the availability of parallel processors [1], hierarchical modeling [2], fast storage element [3] and the advent of nano scale transistors [4], circuit simulators run much faster than they did then. In the final analysis, circuit simulators become an indispensable aid to the design process, and they have even become the only thing to be trusted.

However, circuit simulators still barely keep pace with the increasing number of transistors and the complexity of modern IC. As the semiconductor processes are upgraded, the modelling of a device's physical properties has become more sophisticated than ever [5-7] which requires considerable run time in model evaluation. Take a single metal-oxide-semiconductor field-effect transistor (MOSFET) for example. The basic physical variables of its characteristic modelling are not enough to describe the short-channel effect [8] as it enters nano scale and supplemental parameters must be introduced to fit the experimental data [9]. Also, the parasitic elements [10] brought by MOSFET can easily boost the computation and memory cost in post-layout simulation which may slow down or lead to failure of simulations.

As the circuits become more vulnerable to process variations, multiple verification tools have been developed to ensure the reliability of designs [11-13]. Circuit designers need to statistically simulate the probability that a circuit does not meet the performance metric. Circuit testers run simulations over all potential faulty/nominal responses to improve the fault detection coverage. Some of the testers proceed to diagnose the physical location of those potential faults. Circuit manufacturers allocate enormous computational resources to estimate/improve the yield. Circuit machine learning players [14-15] also abuse the simulator to build their databases. It is not rare to experience simulations that take a few days or even weeks to finish.

In the meanwhile, more Electronic Design Automation (EDA) tools have been applied to help efficiently deliver a circuit design from idea to product, such as, auto-layout tool, design transfer tool, design rule check tool, etc. Unlike other general tools, they are facing challenges every time when a new process is released which means more ancillary patches are added.

Yet, the numerical technique scheme has not evolved with the scaling of circuits and the same ODE solver has been used to resolve a matrix with size of one hundred by one hundred in the past and now one million by one million [16]. Necessary statistical simulation directly deploys a few thousands of independent threads and the whole statistical simulation fails if one of the threads does not achieve convergence. Thus, a competitive integrated circuit simulator should enable more practical functionalities and upgrade the existing algorithms. This dissertation shows a novel way of running DC analysis, transient analysis, time domain sensitivity analysis and related applications. The content includes the capability of applying step functions as input excitations instead of steep ramp functions. The remaining transient simulation is supported by the static-

driven integration method [17] after the step response as initial state is obtained; a time domain adjoint sensitivity analysis is performed along with the transient progression and all the node voltages' sensitivity with respect to all the parameters of interest are available in one simulation. Insight into the proposed algorithms, their efficiency improvement, numerical error analysis [18] and potential applications are provided. Simulations accommodate industry standard devices, and even customized devices in terms of the SPICE [19-21] format.

#### **1.2 Dissertation Organization**

This chapter provides an overview of IC simulation including the motivations, challenges, and a brief introduction to the proposed simulator. More details will be elaborated in the following chapters. In chapter II, the technical background of an industry standard simulator is introduced in the sequence of device modelling, netlist formation, system matrix construction and fundamental DC, AC, Transient algorithms for various analyses. An efficient transient methodology is proposed with a step function as input excitation in chapter III which uses the static driven method as the time integration approximation and the application of using the proposed static driven method to calculate the DC convergence point is discussed. In chapter IV, the proposed time domain adjoint sensitivity analysis shows the possibility of attaining all parameters' time domain sensitivities to be available withing one simulation. Related discussions of its complexity and error are compared with the incremental sensitivity, and a novel time domain noise analysis based on adjoint sensitivity is explored. Chapter V concludes the dissertation.

#### CHAPTER 2

Traditional integrated circuit simulation starts with the modeling of devices which is abstractly represented by the current as a function of voltage i=f(v) or the voltage as a function of current v=f(i). After all devices are declared in the circuit, an abstracted topology relationship of these devices called a netlist is formed. As the availability of each device's branch function and each branch's connectivity, the next step is combining all the independent branch functions to form the corresponding system matrix in terms of nodal analysis. Different analyses (time domain/frequency domain) employ different representations of the system matrix. During this process, nonlinear elements become linearized, and a great deal of matrix manipulations are applied to the linearized system until the result converges. Normally, most of the computational power entailed is spent on matrix manipulations.

This chapter will focus on introducing how the conventional analysis being generated in industrial standard IC simulator. The process starts with the definition of devices, and the potential method of improvement will be touched upon during the introduction.

#### **2.1 Device Modelling**

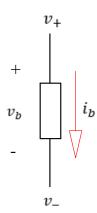

Figure 2.1 Branch information for a generic two-terminal device with associated reference directions.

In general, there are two types of devices: memory devices (capacitor/inductor) and memoryless devices (resistor/transistor), we use q and f to represent their voltage-current functions correspondingly. The voltage-current relations for any two-terminal devices are shown in Fig. 2.1 and the positive (+) reference for the branch voltage  $(v_b)$ /branch current  $(i_b)$  is with the tail of the reference arrow, the negative (-) reference is with the head of the reference arrow. As the direction being defined, branch current  $i_b$  can be represented by the function of branch voltage  $v_b$  as  $i_b=f(v_b)$ or  $i_b=q(v_b)$ . The voltage-current relations of typical two-terminal devices are summarized as follows.

Table 2.1 Characteristic function of two-terminal devices

| Types of devices           | Resistor              | Capacitor                         | Inductor                          | Diode                                            |

|----------------------------|-----------------------|-----------------------------------|-----------------------------------|--------------------------------------------------|

| Characteristic<br>function | $i_b = \frac{v_b}{R}$ | $i_b = C \cdot \frac{d(v_b)}{dt}$ | $v_b = L \cdot \frac{d(i_b)}{dt}$ | $i_b = I_s \cdot [e^{\frac{v_b}{\eta v_T}} - 1]$ |

It should be noted that with the associated reference directions power.  $p_b=v_b\cdot i_b$ , is delivered to the element from the rest of the circuit if  $p_b>0$ ; if  $p_b<0$  power is being delivered to the rest of the circuit from the element.

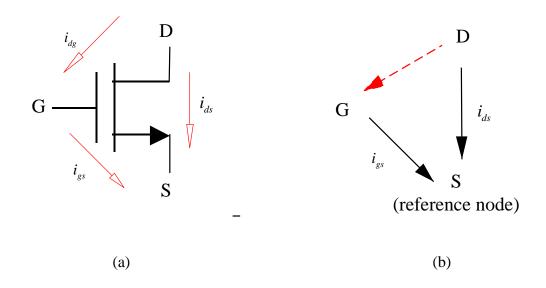

For multiple-terminal devices, such as the N-channel MOSFET shown in Fig.2.2(a), the abstracted voltage-current branch function is shown in Fig.2.2(b) with the source node being the reference node. The equation for the branch current from the gate node to the source node is zero and the branch current from the drain node to the source node  $i_{ds}$  is described as follows according to the Schichman and Hodges model [22].

$$i_{ds} = 0 \qquad \text{cutoff region } (v_{gs} < v_{th}) (1a)$$

$$i_{ds} = \beta \cdot [(v_{gs} - v_{th}) \cdot v_{ds} - \frac{v_{ds}^{2}}{2}] \cdot (1 + \lambda \cdot |v_{ds}|) \qquad \text{Triode region } (0 < v_{ds} < v_{gs} - v_{th}) (1b)$$

$$i_{ds} = \frac{\beta}{2} \cdot [v_{gs} - v_{th}]^{2} \cdot (1 + \lambda \cdot |v_{ds}|) \qquad \text{saturation region } (0 < v_{gs} - v_{th} < v_{ds}) (1c)$$

Figure 2.2 N-channel MOSFET and its abstracted branch information.

As a reference node of any multi-terminal devices is defined, a *n*-terminal device can be described in terms of (n-1) branches with the currents of such branches from every node to the defined reference node. For example, if the source node in Fig. 2.2(a) is selected to be the reference node, then the branch currents  $i_{gs}$  and  $i_{ds}$  are sufficient to describe this three-terminal device and the branch current  $i_{dg}$  becomes redundant.

#### 2.2 Nodal Analysis

Now, any *n*-terminal devices can be described by (n-1) branch functions, and nodal analysis is used to represent the connectivity of those branches. Any device can be simplified in terms of multiple branches, in general, these branches have a positive (+) reference node called the 'from node' and a negative (-) reference node called the 'to node'.

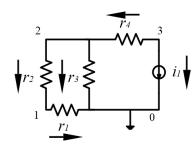

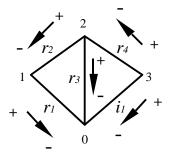

Figure 2.3 A simple circuit example.

Figure 2.4 The topology abstraction of Fig.2.3.

Consider a simple circuit shown in Fig. 2.3, its connections of all the branches can be abstracted as in Fig. 2.4 after the global/local reference node is determined; the ground node is always the global reference node. Based on the pre-defined 'from node' and 'to node' of every branch, the equivalent netlist description is shown in Table 2.2. Now, all the connectivity of all of branches is available.

| Branch type/name      | From node | To node | Value |

|-----------------------|-----------|---------|-------|

|                       |           |         |       |

| <i>r</i> <sub>1</sub> | 1         | 0       | 1.0   |

|                       |           |         |       |

| $r_2$                 | 2         | 1       | 1.0   |

|                       |           |         |       |

| <i>r</i> <sub>3</sub> | 2         | 0       | 1.0   |

|                       |           |         |       |

| <i>r</i> 4            | 3         | 2       | 1.0   |

|                       |           |         |       |

| $i_1$                 | 3         | 0       | 1.0   |

|                       |           |         |       |

Table 2.2 The netlist representation of circuit shown in Fig.2.3

#### 2.3 System Matrix Forming

Now that we have all necessary information to solve the circuit in Fig. 2.3, including the voltage-current function of each device and their connections. Before attaining the algebraic matrix and solving it, we first need each individual algebraic expression which are derived from Kirchhoff's Voltage Law (KVL) and Kirchhoff's Current Law (KCL). If a branch current leaves a node is positive and vice versa, then, based on KCL, each node's expression of the circuit in Fig. 2.3 can be represented in (2). But the global reference node's expression in (2) is a linear combination of the rest, thus, after taking out the ground node, the rest (2b), (2c)&(2d) can be

expressed in matrix form in (3) where f is a vector which stores each nodal expression [ $f_0, f_1, f_2, ...$ ,  $f_n$ ], v and e are the vectors of node voltages and input excitations.

node0:

$$f_0 = -i_{r_1} - i_{r_3} - i_1 = -\frac{v_1 - v_0}{r_1} - \frac{v_2 - v_0}{r_3} - i_1$$

(2a)

node1:

$$f_1 = i_{r_1} - i_{r_2} = \frac{v_1 - v_0}{r_1} - \frac{v_2 - v_1}{r_2}$$

(2b)

node2:

$$f_2 = i_{r_2} + i_{r_3} - i_{r_4} = \frac{v_2 - v_1}{r_2} + \frac{v_2 - v_0}{r_3} - \frac{v_3 - v_2}{r_4}$$

(2c)

node3:

$$f_3 = i_{r_4} + i_1 = \frac{v_3 - v_2}{r_4} + i_1$$

(2d)

$$\frac{\partial \mathbf{f}}{\partial \mathbf{v}} \cdot \mathbf{v} = \mathbf{e} = \begin{bmatrix} \frac{1}{r_1} + \frac{1}{r_2} & -\frac{1}{r_2} & 0\\ -\frac{1}{r_2} & \frac{1}{r_2} + \frac{1}{r_3} + \frac{1}{r_4} & -\frac{1}{r_4}\\ 0 & -\frac{1}{r_4} & \frac{1}{r_4} \end{bmatrix} \cdot \begin{bmatrix} v_1\\ v_2\\ v_3 \end{bmatrix} = \begin{bmatrix} 0\\ 0\\ -i_1 \end{bmatrix}$$

(3)

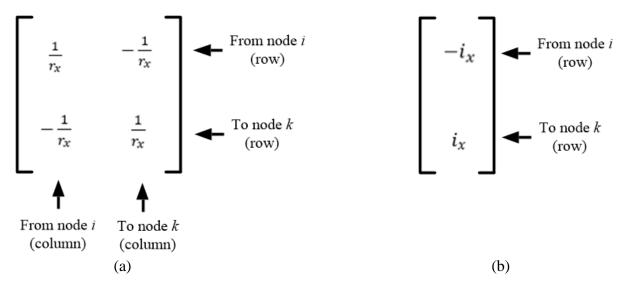

Figure 2.5 Element stamps: (a) for  $\partial f / \partial v$  matrix; (b) for *e* vector.

For a resistor of value  $r_x$  from node *i* to node *k* as shown in Fig. 2.3, a positive conductance value  $1/r_x$  is added to matrix locations (i,i) and (k,k), respectively,  $-1/r_x$  is added to matrix locations (i,k) and (k,i). For an independent current source with from node *i* and to node *k*, a negative current source value  $-i_x$  is added to the  $i_{th}$  element of the *e* vector and a positive value  $i_x$  is added to the  $k_{th}$  element.

Only this simple circuit example is provided from schematic netlist to the algebraic matrix form. Nonlinear device modelling and memoryless elements will be reviewed when DC analysis and transient analysis is introduced.

#### 2.4 Steady State Analysis

DC analysis is also known as steady state analysis. Steady state analysis calculates the stabilized state vector of a circuit when constant voltage sources and/or current source input excitations are applied to it. In most cases, the results of the DC analysis are intermediate values for further analysis, thus, its accuracy is essential to the next analysis. A simple DC analysis is shown in section 2.3, and after inverting the  $\partial f/\partial v$  matrix in (3), the DC operating point vector v is available. But the example in section 2.3 only has resistors and a current sour.

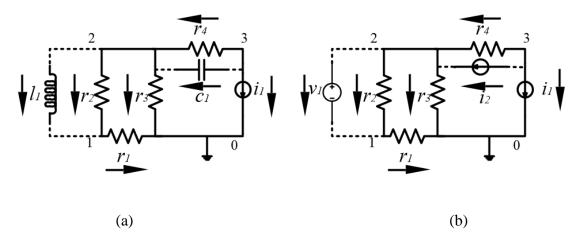

Figure 2.6 Circuit example for explaining steady state analysis: (a) capacitor/inductor is added to circuit shown in Fig. 2.3 and its equivalent replacement (b).

Since DC operating point analysis does not consider any time dependence on any of the devices, the capacitor becomes an open circuit and inductor becomes a short circuit in steady state. If one capacitor and inductor is added to circuit of Fig. 2.3, the new schematic is shown in Fig. 2.6 and corresponding KCL&KVL equations are

$$\begin{bmatrix} \frac{1}{r_{1}} + \frac{1}{r_{2}} & -\frac{1}{r_{2}} & 0 & -1 \\ -\frac{1}{r_{2}} & \frac{1}{r_{2}} + \frac{1}{r_{3}} + \frac{1}{r_{4}} & -\frac{1}{r_{4}} & 1 \\ 0 & -\frac{1}{r_{4}} & \frac{1}{r_{4}} & 0 \\ -1 & 1 & 0 & 0 \end{bmatrix} \cdot \begin{bmatrix} v_{1} \\ v_{2} \\ v_{3} \\ i_{vsrc} \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ -i_{1} \\ v_{1} \end{bmatrix}$$

(4)

where  $i_{vsrc}$  represents the current goes through voltage source (vsrc).

As one voltage source is added to the original circuit shown in Fig. 2.3, one more unknown enters the algebraic equations because the branch current of voltage source is balanced by the known value of the voltage source, and the number of current unknowns equals the number of voltage source branches. Thus, one more column and row are needed in matrix  $\partial f/\partial v$  which is also known as modified nodal analysis. For a circuit with multiple independent voltage sources and the *m*<sub>th</sub> voltage source is the one with 'from node' *i* and 'to node' *k*, a positive unit is added to modified matrix locations (n+m,k)&(i,n+m) and a negative unit is added to (n+m,i)&(k,n+m).

Devices in the aforementioned circuit are linear and the steady state can be obtained after inverting the  $\partial f/\partial v$  matrix once. But it is not practical to attain nonlinear device's steady state analytically and Newton-Raphson method (NR) is the most straight forward and well-known solution [23-24] for it.

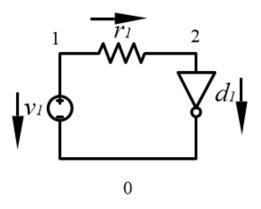

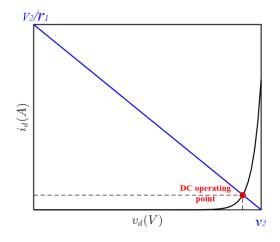

Figure 2.7 Simple nonlinear circuit ( $v_1$ =0.7volt;  $r_1$ =1ohm).

Consider the problem of determining the DC operating point for the simple nonlinear circuit shown in Fig. 2.7. The steady state of this single loop circuit can be easily formulated in terms of a loop equation as

$$f:\frac{0.7-v_2}{r_1}-I_s\cdot[e^{\frac{v_2-v_0}{\eta v_T}}-1]=0$$

(5)

and the DC operating point can be easily found if a load line is drawn on the plot of the characteristic curve as shown in Fig. 2.8.

But unfortunately, not all circuits can be formulated in a single loop equation and a universal load line is seldom available. Thus, KCL&KVL equations for each node are necessary and listed as

$$f_1 = \frac{v_1 - v_2}{r_1} + i_{vsrc}$$

(6a)

$$f_2 = -\frac{v_1 - v_2}{r_1} + I_s \cdot [e^{\frac{v_2 - v_0}{\eta v_T}} - 1]$$

(6b)

$$f_{vsrc} = v_1 - v_0 - v_{vsrc} \tag{6c}$$

Figure 2.8 Load line of simple nonlinear circuit shown in Fig. 2.7.

Figure 2.9 NR iteration process of simple nonlinear circuit shown in Fig. 2.7.

In steady state, those equations should have f=0. Now, if NR is applied to solve the DC operating point problem shown in Fig. 2.7, an initial state vector  $v_{1st}$  as the starting point of the iteration is necessary to kick start the NR, and the initial state vector have  $f(v_{1st})\neq 0$ . At each iteration of NR, the partial derivative of function  $\partial f/\partial v$  becomes a gradient and the next state  $v_{(n+1)th}$  is updated by following the local minimum of this gradient as

$$\boldsymbol{v}_{(n+1)th} = \boldsymbol{v}_{nth} - \left[\frac{\partial f}{\partial \boldsymbol{v}}\right]^{-1} \boldsymbol{f}(\boldsymbol{v}_{nth})$$

(7)

The full NR iteration process is shown in Fig. 2.9 and the initial state vector is assumed to be zero, which is the default setting of the NR method.

Based on the above, the initial guess is critical to the NR-derived algorithms because fewer iterations are needed if the initial guess is close enough to the steady state. NR does not guarantee convergence because it can be easily trapped in the local minimum of the function [24], thus, more backups are needed if NR fails steady state analysis [25-26].

#### 2.5 Forward/Backward Euler Transient Analysis

A transient analysis first needs a point of departure for simulating time-varying behavior and mostly the point of departure is selected to be the result of DC analysis. Once the initial state v(t=0) is attained, the time-dependent aspects of circuit are reevaluated, and the simulation solves for the state vector at the next time point. Forward/Backward Euler are the numerical integration approximation algorithms used to approximate the analytical response of the transient. More advanced transient algorithms are available, but we confine attention to these two to avoid uselessly cluttering the ensuing exposition.

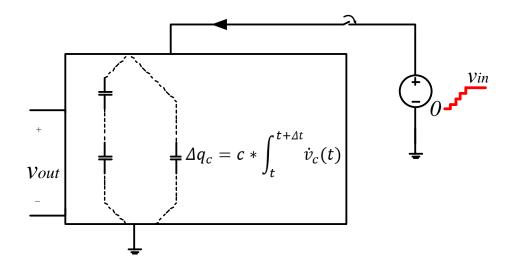

Figure 2.10 Difference between Forward/Backward Euler integrations from t to  $t+\Delta t$ .

Suppose both Forward-Euler and Backward-Euler start at the same point of departure, the analytical time varying behavior of capacitor voltage can be represented as

$$\boldsymbol{v}_{c}(t+\Delta t) = \boldsymbol{v}_{c}(t) + \int_{t}^{t+\Delta t} \frac{i_{c}(\tau)}{c} d\tau$$

(7)

Here we consider a numerical approximation of the integration from t to  $t+\Delta t$  in (7) as

$$\mathbf{v}_{c}(t + \Delta t) = \mathbf{v}_{c}(t) + \begin{cases} \frac{i_{c}(t)}{c} \cdot \Delta t & Forward - Euler\\ \frac{i_{c}(t + \Delta t)}{c} \cdot \Delta t & Backward - Euler \end{cases}$$

(8)

Figure 2.11 RC circuit with step function as excitation ( $v_1=1volt$ ;  $r_1=1ohm$ ;  $c_1=1F$ ).

Forward Euler integration method applies the time derivative at time *t*, Backward Euler integration method selects the time derivative at time  $(t+\Delta t)$  as shown in Fig. 2.10. Note that the slope of the BE integration approximation is that of the tangent to the nonlinear characteristic curve at time  $(t+\Delta t)$ . More details about Forward/Backward-Euler integration methods are discussed in terms of an RC circuit shown in Fig. 2.11. In Fig. 2.11, if a step function is applied as the input excitation, the analytical transient response can be represented as

$$\mathbf{v}_{c}(t) = 1 - e^{\frac{-t}{r_{1}c_{1}}}$$

(9)

If the transient analysis is in terms of Forward Euler (FE), then its excursion from time t to  $t+\Delta t$  is

$$\Delta v_{c} = c_{1}^{-1} \cdot \frac{v_{1}(t) - v_{2}(t)}{r_{1}} \cdot \Delta t$$

(10)

If the transient analysis is in terms of Backward Euler (BE), then its same excursion is

$$\Delta \boldsymbol{v}_c = \left(\frac{\Delta t}{r_1} + c_1\right)^{-1} \cdot \frac{v_1(t) - v_2(t)}{r_1} \cdot \Delta t \tag{11}$$

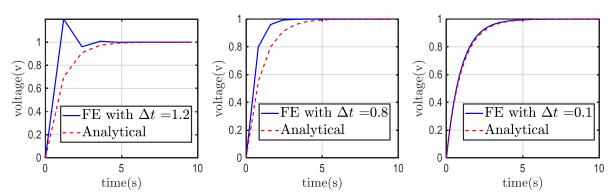

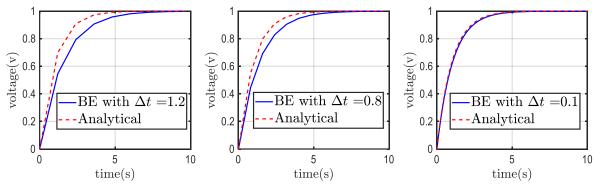

The circuit in Fig. 2.11 is simulated in terms of both Forward-Euler and Backward-Euler with different time steps, and the simulation results are shown in Fig. 2.12 and Fig. 2.13.

Figure 2.12 Transient analysis in terms of the Forward-Euler integration approximation with different time steps  $\Delta t$ .

Figure 2.13 Transient analysis in terms of the Backward-Euler integration approximation with different time steps  $\Delta t$ .

Based on (10), (11) and the simulations result above, Forward-Euler is a fast explicit integration approximation and Backward-Euler is a stable implicit integration approximation. If a very small time step is applied, then both FE and BE provide essentially the same result.

#### 2.6 Background Summary

The above briefly explains how steady state analysis and Forward/Backward-Euler transient analysis works but with simple examples. This section will focus on revisiting DC and transient analysis again in a general circuit example and the form of vectors/matrices will be carried over to the entire dissertation.

Suppose a general integrated circuit netlist contains b branches and n nodes, the KCL&KVL functions for all memoryless elements at each node form a vector as

$$\boldsymbol{f} = \begin{bmatrix} f_1 \\ f_2 \\ \cdots \\ f_n \end{bmatrix}$$

(12)

where  $f_n$  is the KCL function at node *n*. In steady state, circuit has f(v)=0 where *v* is the state vector of the circuit. If the NR method is applied to solve for the steady state, the state vector of the next iteration  $v_{(n+1)th}$  is

$$\boldsymbol{v}_{(n+1)th} = \boldsymbol{v}_{nth} - \left[\frac{\partial \boldsymbol{f}}{\partial \boldsymbol{v}}\right]^{-1} \boldsymbol{f}(\boldsymbol{v}_{nth})$$

(13)

Before the discussion of FE and BE in terms of matrices. It should be noted that there is a vector q being defined in the same manner as f shown in (12), but it only includes the memory elements, capacitors and inductors. Vector f contains the sums of the currents leaving each node

and vector q contains similar sums of charge/flux. The matrix  $\partial f/\partial v$  is abbreviated as G and the matrix  $\partial q/\partial v$  is abbreviated as C in the following chapters.

In Forward-Euler transient analysis, the integration from time *t* to  $t+\Delta t$  is

$$\mathbf{v}(t+\Delta t) = \mathbf{v}(t) - \left[\frac{\partial q}{\partial \mathbf{v}}\right]^{-1} \mathbf{f}(\mathbf{v}(t)) \cdot \Delta t$$

(14)

In Backward-Euler transient analysis, the integration from time *t* to  $t+\Delta t$  is

$$\mathbf{v}(t+\Delta t) = \mathbf{v}(t) - \left[\frac{\partial f}{\partial \mathbf{v}} + \frac{\partial q}{\partial \mathbf{v}} / \Delta t\right]^{-1} f(\mathbf{v}(t+\Delta t))$$

(15)

As shown above, all circuit analysis entails the inversion of a Jacobian matrix which takes more than 90% of the simulation run time and the rest of 10% is mostly spent on device evaluation.

#### **CHAPTER 3**

The Backward Euler integration method and its variants are widely employed in SPICE [27] which is a well-known, general-purpose, open-source electronic circuit simulator. Those integration methods are able to provide utmost accuracy and stability, but they are a primary cause of slowing simulation time. To improve efficiency, various approaches have been developed either to incorporate multi-rate estimation [28] or to apply model simplification such as piecewise linear [29]. In any case a great deal of computational power is consumed to iterate and invert (LU-factor) a Jacobian matrix at each time step. This chapter shows the possibility of applying Forward-Euler integration approximation to underline transient analysis with an adaptively controlled time step, algorithmic stability, and user-defined accuracy control.

Also, SPICE was not initially designed to handle step function excitations directly. To avoid discontinuity, SPICE-derived transient simulators substitute inefficient steep ramps for step function excitations. As the rise time of a steep ramp is reduced to better approximate a step function, more iterations are required to maintain accuracy and stability, thereby consuming substantial computation time. To account for digitally dominated circuits with rapid turn on/off or the abstraction of the simulation environment to switch level [30], applying step functions as input excitations and generalizing any input functions to step functions are discussed in this chapter.

#### 3.1 Step Response

As mentioned earlier, DC analysis requires an initial state vector to kick start the NR and a step response is a suitable candidate to attain the initial state vector because it represents the natural starting point after the input excitations are switched on. Also, the step response, once it has settled, can provide the departure point for simulating time-varying behavior. Usually, the point of departure is selected to be the result of DC operating point NR iteration if it converges. But NR convergence to the steady state is not guaranteed.

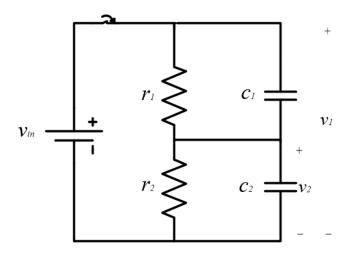

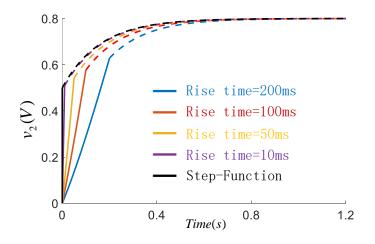

Figure 3.1 RC example for explanation of step response calculation ( $v_1$ =0.8V; r1=100ohm;  $r_2$ =400ohm;  $c_1$ = $c_2$ =10<sup>-3</sup>F).

The initial state  $v(t=0_+)$  of a capacitor array excited by a step function is its charge-voltage equilibrium point.

$$\boldsymbol{q}_c = c \cdot \boldsymbol{v}_c (t = 0_+) \tag{16}$$

To illustrate its computation, we consider a simple series connection of two resistors and capacitors in parallel shown in Fig. 3.1. The input excitation function to the circuit is a step function

$$\begin{cases} v_{in}(t=0_{-}) = 0\\ \int_{0_{-}}^{0_{+}} v_{in}(t) dt = 0.8\\ v_{in}(t=0_{+}) = 0.8 \end{cases}$$

(17)

Initially at the exact time of the step function excitation, t=0, the voltage source provides an impulse of current and the capacitors in the circuit instantaneously equilibrate their charges and voltages. The remaining elements are indifferent to this impulse of current, so it can be ignored for such analysis. In practical cases, because of highly elaborated transistor models, capacitors are everywhere. Thus, we assume that capacitors probably connect to all nodes, and the general case will be discussed later. The capacitor responses to the impulses of current which determines the state at  $t=0_+$ , and the calculation of the impulse response and the effective charge is equivalent to DC analysis with charge equilibrium replacing current equilibrium. To represent (16) in terms of matrices, we use  $v_n(t=0_+)$  as the node voltage vector representing the voltage source specifying the initial step response and *C* as the capacitance matrix. For the circuit of Fig. 3.1, the matrix equation is

$$\begin{bmatrix} c_1 & -c_1 & 1 \\ -c1 & c_1 + c_2 & 0 \\ 1 & 0 & 0 \end{bmatrix} \cdot \begin{bmatrix} v_1(t=0+) \\ v_2(t=0+) \\ q_{vsrc}(t=0+) \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ v_{in}(0_+) \end{bmatrix}$$

(18)

where  $q_{vsrc}$  is the electric charge flowing through the voltage source that initializes the capacitor voltages.

In simulators employing the BE integration method, if a circuit contains capacitor loops, then a great deal of computational resource must be devoted to climbing an approximating steep ramp to determine the peak current that charges the capacitors. Instead, the proposed simulator computes the peak directly by instantaneously charging all capacitors to their initial equilibria. This is a one-time DC-like computation that inverts (LU-factors) the *C* matrix, an operation that also needs be performed anyway to compute the remainder of the transient.

|                       | $v_2(t_{rise})$ /v or $v_2(0_+)$ /v |                                    |                          |  |

|-----------------------|-------------------------------------|------------------------------------|--------------------------|--|

| t <sub>rise</sub> /ms | Backward Euler                      | Trapezoidal                        | GEAR2                    |  |

| 200                   | 0.6295                              | 0.6319                             | 0.6273                   |  |

| 100                   | 0.5769                              | 0.5880                             | 0.5648                   |  |

| 50                    | 0.5375                              | 0.5493                             | 0.5213                   |  |

| 10                    | 0.5092                              | 0.5149                             | 0.5064                   |  |

| 5                     | 0.5046                              | 0.5088                             | 0.5027                   |  |

| Ideal step            | 0.5                                 |                                    |                          |  |

| • Pa                  | art B: Comparisons amo              | ong $q_{eff}$ and $q_{vsrc}$       |                          |  |

| t <sub>rise</sub> /ms | $q_{eff}$ /C or $q_{vsrc}$ /C       |                                    |                          |  |

| rise/ms               | Backward Euler                      | Trapezoidal                        | GEAR2                    |  |

| 200                   | 0.77543*10 <sup>-3</sup>            | 0.77989*10 <sup>-3</sup>           | 0.73981*10 <sup>-3</sup> |  |

| 100                   | $0.64408*10^{-3}$                   | 0.64591*10 <sup>-3</sup>           | 0.64087*10-3             |  |

| 50                    | $0.57584*10^{-3}$                   | 0.59013*10 <sup>-3</sup>           | 0.55698*10-3             |  |

| 10                    | 0.51622*10 <sup>-3</sup>            | 0.52319*10 <sup>-3</sup>           | 0.51326*10-3             |  |

| 5                     | 0.50883*10-3                        | 0.51011*10 <sup>-3</sup>           | 0.50491*10 <sup>-3</sup> |  |

| Ideal step            | 0.5*10 <sup>-3</sup>                |                                    |                          |  |

| • Pa                  | art C: Error from climb             | ing samples with t <sub>rise</sub> | = 5 <i>ms</i>            |  |

| Number of             | Absolute integration error          |                                    |                          |  |

| samples in            | Backward Euler                      | Trapezoidal                        | GEAR2                    |  |

Table 3.1 Peak comparisons between ideal step & steep ramp functions

A comparison has been made between step function excitation and steep ramps with different rise times in the Model and Algorithm Prototyping Platform (MAPP) [31], a MATLAB<sup>TM</sup>

$5.802*10^{-9}$

5.877\*10<sup>-9</sup>

6.179\*10<sup>-9</sup>

$6.955*10^{-9}$

9.735\*10<sup>-9</sup>

$3.353*10^{-9}$

7.756\*10-9

7.77\*10<sup>-8</sup>

3.198\*10<sup>-7</sup>

1.227\*10-6

$1.101*10^{-7}$

2.281\*10<sup>-7</sup>

$5.956*10^{-7}$

1.252\*10-6

2.731\*10-6

100

50

20 10

5

based open-source simulation framework which is able to execute SPICE-derived transient analysis. The comparison results based on the above circuit example are shown in Table. 3.1 & Fig. 3.2. The effective electric charge flowing through voltage source  $q_{eff}$  from t=0 to  $t=t_{rise}$  with the input excited by a steep ramp is

$$q_{eff} = \int_0^{t_{rise}} \dot{i}_{vsrc}(t) dt \tag{19}$$

and its corresponding state vector at  $t=t_{rise}$  is defined as  $v_n(t=t_{rise})$ .

Figure 3.2 Step function response versus steep ramps with various rise time.

The end point of climbing  $v_n(t=t_{rise})$  is the initial state for the remainder of the transient. The overall accuracy compared with the step response is determined by both rise times and time samples. No matter what integration method is employed, as the steep ramp becomes more steplike,  $v_n(t=t_{rise})$  and the effective charge  $q_{eff}$  become closer to  $v_n(t=0_+)$  and  $q_{vsrc}$ , respectively, and the response becomes more accurate. The same experiment is to be performed on the upcoming nonlinear circuits examples, and the same conclusion obtains. For the above, increasing computational power is consumed to maintain accuracy when the input is excited by steeper and steeper ramps, but the step response solver does not climb such a hill to calculate  $v_n(t=0_+)$ ; hence, no extra effort is entailed.

The circuit in Fig. 3.1 shows how the step response is calculated for a simple example. The solution of the step response for a general circuit can be represented by

$$C \cdot \mathbf{v}_{n}(t=0+) = \mathbf{q}(\mathbf{v}_{n}(t=0)) \tag{20}$$

It should be noted, (20) is the same as (15) after the time step of (15) is set to be infinitesimal. Practically, a circuit may have nodes which not tied directly to a capacitor or are excited with a step function current source. To address such issues a two-step process is required, and modification of matrix in (20) is necessary. Charge-voltage equilibrium (flux-current equilibrium for inductors if it applies) of memory elements (capacitors/inductors) is the solution with priority and should be achieved at  $t=0_+$ , then, for those internal nodes which are not tied directly to memory elements, current equilibrium (KCL) must be obtained for them as a secondary solution. To clear the residue of charge and current for both memory elements and memoryless elements, modification of the matrix is established as

$$\begin{bmatrix} G & 0 \\ 0 & C \end{bmatrix} \cdot \boldsymbol{v}_n(t=0+) = \begin{bmatrix} \boldsymbol{f}(\boldsymbol{v}_n(t=0)) \\ \boldsymbol{q}(\boldsymbol{v}_n(t=0)) \end{bmatrix}$$

(21)

In (21), G and f stands for the linearization of memoryless elements which are not tied directly to memory elements, and their unbalanced current. C and q stand respectively for the linearization of memory elements and their unbalanced charge or flux.

In real integrated circuit, characteristics of memory elements could also be nonlinear, and the linearization of memory elements C which is the foundation of charge-voltage equilibrium also

depends on the state of the circuit. The solution for such a situation is by splitting one step function into multiple step functions and acquiring charge-voltage equilibrium at each end of the step function to smooth the effect of nonlinearity as is shown in Fig. 3.3.

Figure 3.3 Step function excitation for general circuit schematic.

# 3.2 Static-driven Algorithm

After the initial state is attained, the remainder of the transient is taken over by the proposed explicit static-driven method which is inspired by Adaptively Controlled Explicit Simulation (ACES) [32]. State variables approach their static equilibria with different time constants. By partitioning state variables into a quiescent group and a dynamic group, the simulator naturally and adaptively differentiates the fast/slow state variables in the circuit. This static-driven method is developed to drive the dynamic state variables to be quiescent in order, and those quiescent state variables to remain quiescent until all state variables become quiescent when the system is in steady state. A state variable is set to quiescence by equating its second order time derivative to zero [32].

With Backward-Euler integration approximation for large stiff systems, a Jacobian matrix must be inverted at each iteration and ill-conditioning can occur. Quiescence automatically differentiates the state variables into a fast group and a slow group which enables it to iterate adaptively with larger time steps and no ill-conditioning.

At first, all state variables are dynamic. The explicit first and second order time derivative of a general state space system [33] can be described in terms of

$$\dot{\boldsymbol{x}} = \boldsymbol{A} \cdot \boldsymbol{x} + \boldsymbol{B} \cdot \boldsymbol{u} \tag{22a}$$

$$\ddot{\boldsymbol{x}} = \boldsymbol{A} \cdot \dot{\boldsymbol{x}} + \boldsymbol{B} \cdot \dot{\boldsymbol{u}} \tag{22b}$$

where u represents the vector of input functions. For simplicity, if the circuit system is excited by step functions, then at any time point the time derivatives of input functions are zero, so

$$\dot{\boldsymbol{x}} = \boldsymbol{A} \cdot \boldsymbol{x} + \boldsymbol{B} \cdot \boldsymbol{u} \tag{23a}$$

$$\ddot{\boldsymbol{x}} = \boldsymbol{A} \cdot \dot{\boldsymbol{x}} \tag{23b}$$

On the way of driving dynamic state variables into quiescence, for the  $k^{th}$  state variable, an adaptive step size controller is defined to be

$$\Delta t_k = -\dot{x}_k(t) / \ddot{x}_k(t) \tag{24}$$

It provides an estimation of the real parts of time constants for those dynamic state variables. At each iteration, the smallest  $\Delta t_k$  is chosen to be the step size in order to ensure stability. At the end of the estimated time step, the  $k^{th}$  dynamic state variable with the smallest  $\Delta t_k$  then is set to be quiescent. For practicality, the  $\Delta t_k$  of those state variables which are close to the smallest one should be set to quiescence concurrently, because they display close time constants especially for symmetrical nodes which exists in mirror topology and perform the same response.

The second order time derivative of quiescent terms should be zero. Thus, for the quiescence terms in (23b), we have

$$\ddot{x}_{q} = A_{11}\dot{x}_{q} + A_{12}\dot{x}_{nq} = 0 \tag{25}$$

where the state vector  $\mathbf{x}$  includes a q-dimensional quiescent state sub-vector  $\mathbf{x}_q$  and an (n-q)dimensional dynamic state sub-vector  $\mathbf{x}_{nq}$ ,  $A_{11}$  and  $A_{12}$  are the sub-matrices of state space matrix A.  $x_i$  represents the  $i^{th}$  element of the quiescent state variables where i=1,2,...,q;  $x_j$  represents the  $j^{th}$  element of dynamic state variables where j=q+1,q+2,...n. Based on (25) the time derivative for the quiescent state variables can be derived to be

$$\dot{\boldsymbol{x}}_{q} = -\boldsymbol{A}_{11}^{-1} \boldsymbol{A}_{12} \dot{\boldsymbol{x}}_{nq} \tag{26}$$

Essentially, the time derivatives of quiescent state variables are controlled by the time derivatives of dynamic state variables. From the application of such control, the second order time derivatives of those quiescent state variables with small time constants are forced to be zero. Thus, the potential instability problem associated with explicit integration is properly addressed. Such control is applied for all subsequent iterations, so those quiescent state variables remain quiescent.

Based on (26) the modified state space equation can be written as

$$\begin{bmatrix} \dot{\boldsymbol{x}}_{\boldsymbol{q}}(t) \\ \dot{\boldsymbol{x}}_{\boldsymbol{nq}}(t) \end{bmatrix} = \begin{bmatrix} -A_{11}^{-1}A_{12}A_{21} & -A_{11}^{-1}A_{12}A_{22} \\ A_{21} & A_{22} \end{bmatrix} \begin{bmatrix} \boldsymbol{x}_{\boldsymbol{q}}(t) \\ \boldsymbol{x}_{\boldsymbol{nq}}(t) \end{bmatrix} + \begin{bmatrix} -A_{11}^{-1}A_{12}(B\boldsymbol{u})_{\boldsymbol{nq}} \\ (B\boldsymbol{u})_{\boldsymbol{nq}} \end{bmatrix}$$

(27)

Fast state variables enter quiescence earlier than slow state variables and eventually all state variables enter quiescence. During the integration process, the fastest state variable leads the rest to update before it enters quiescence. After they become quiescent, those quiescent state variables essentially are followers of the next fastest state variable. When there is only one dynamic

state variable waiting to join the quiescent group at the last iteration, the second order time derivative of the last dynamic state variable can be evaluated according to (26), thus, according to (24) the final time step size is

$$\Delta t = -\dot{\boldsymbol{x}}_{nq} / \ddot{\boldsymbol{x}}_{nq} = \frac{-1}{A_{22} - A_{21}A_{11}^{-1}A_{12}}$$

(28)

where the size of the submatrix  $A_{22}$  is one by one. After this final time step  $\Delta t$ , the former quiescent state variables and dynamic state variable at  $t+\Delta t$  can be described independently as

$$\boldsymbol{x}_{q}(t + \Delta t) = \boldsymbol{x}_{q}(t) - A_{11}^{-1} A_{12} \dot{\boldsymbol{x}}_{nq}(t) \cdot \Delta t$$

(29a)

$$\boldsymbol{x}_{nq}(t + \Delta t) = \boldsymbol{x}_{nq}(t) + \dot{\boldsymbol{x}}_{nq}(t) \cdot \Delta t$$

(29b)

From (29), the time derivatives of the dynamic state variable at  $t+\Delta t$  can be calculated based on (23), and its value will be equal to zero

$$\dot{\mathbf{x}}_{nq}(t + \Delta t) = A_{21}\mathbf{x}_{q}(t + \Delta t) + A_{22}\mathbf{x}_{nq}(t + \Delta t) + (B\mathbf{u})_{nq}$$

$$= A_{21}\mathbf{x}_{q}(t) - A_{21}A_{11}^{-1}A_{12}\dot{\mathbf{x}}_{nq}(t) \cdot \Delta t + A_{22}\mathbf{x}_{nq}(t) + A_{22}\dot{\mathbf{x}}_{nq}(t) \cdot \Delta t + (B\mathbf{u})_{nq}$$

$$= 0$$

(30)

The time derivative of quiescent state variables which are controlled by the dynamic state variable is equal to zero as well

$$\dot{\boldsymbol{x}}_{q}(t+\Delta t) = A_{11}^{-1} A_{12} \dot{\boldsymbol{x}}_{nq}(t+\Delta t) = 0$$

(31)

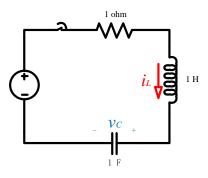

Figure 3.4 Example stiff system.

Figure 3.5 The gross response of a stiff system in Fig. 3.4.

So far, all state variables become quiescent, and the system is in steady state at  $t+\Delta t$ . To better explain the proposed method above, an inevitable linear stiff system and an underdamped RLC system are employed as examples. A classic stiff system and its transient response simulated based on proposed simulator are shown in Figs. 3.4&3.5, respectively. For the stiff circuit in Fig. 3.4, its state equation can be derived according to (22a) as follows

$$\begin{cases} \dot{v}_{b} = (u - 2 \cdot v_{b} + v_{c}) \cdot 1000 \\ \dot{v}_{c} = (v_{b} - 2 \cdot v_{c} + v_{d}) \cdot 1000 \\ \dot{v}_{d} = (v_{c} - v_{d}) \end{cases}$$

(32)

At the initial state, none of these state variables is quiescent. Thus, for those dynamic state variables

$$\dot{v}_i^+(t) = \dot{v}_i(t)$$

(33)

where left hand side of (33) represents the time derivative from (32) and the right hand side represents the time derivative from (27). The state equation and modified state equation deliver the same result as

$$\begin{cases} \dot{v}_{b}^{+}(0) = 1000 \\ \dot{v}_{c}^{+}(0) = 0 \\ \dot{v}_{d}^{+}(0) = 0 \end{cases}$$

(34)

from (23b) we obtain

$$\begin{cases} \ddot{v}_{b}^{+}(0) = [-2 \cdot \dot{v}_{b}^{+}(0) + \dot{v}_{c}^{+}(0)] \cdot 1000 \\ \ddot{v}_{c}^{+}(0) = [\dot{v}_{b}^{+}(0) - 2 \cdot \dot{v}_{c}^{+}(0) + \dot{v}_{d}^{+}(0)] \cdot 1000 \\ \ddot{v}_{d}^{+}(0) = [\dot{v}_{c}^{+}(0) - \dot{v}_{d}^{+}(0)] \end{cases}$$

(35)

After the calculation of the time derivative and the second order time derivative, the safe time step is calculated according to (24)

$$\Delta t = \Delta t_h = 5e^{-4} \tag{36}$$

thus, the simulation proceeds with

$$\mathbf{v}(5e^{-4}) = \mathbf{v}(0) + \dot{\mathbf{v}}^{+}(0) \cdot \Delta t_{b}$$

(37)

In the second iteration,  $v_b$  is set to be quiescent and the time derivative and the second order time derivative can be calculated based on (23b)&(27) to be

$$\begin{cases} \dot{v}_{b}^{+}(5e^{-4}) = 250 \\ \dot{v}_{c}^{+}(5e^{-4}) = 500 \\ \dot{v}_{d}^{+}(5e^{-4}) = 0 \end{cases}$$

$$\begin{cases} \ddot{v}_{b}^{+}(5e^{-4}) = 0 \\ \ddot{v}_{c}^{+}(5e^{-4}) = -7.5e^{5} \\ \ddot{v}_{d}^{+}(5e^{-4}) = 500 \end{cases}$$

(38a)

(38b)

and the safe time step is

$$\Delta t = \Delta t_c = \frac{2}{3}e^{-3} \tag{39}$$

For the third iteration,  $v_b$  and  $v_c$  are quiescent and the time derivative and the second order time derivative can be calculated based on (23b)&(27) to be

$$\begin{cases} \dot{v}_{b}^{+}(\frac{7}{6}e^{-3}) = \frac{1}{9} \\ \dot{v}_{c}^{+}(\frac{7}{6}e^{-3}) = \frac{2}{9} \\ \dot{v}_{d}^{+}(\frac{7}{6}e^{-3}) = \frac{1}{3} \end{cases}$$

$$\begin{cases} \ddot{v}_{b}^{+}(\frac{7}{6}e^{-3}) = 0 \\ \ddot{v}_{c}^{+}(\frac{7}{6}e^{-3}) = 0 \\ \ddot{v}_{d}^{+}(\frac{7}{6}e^{-3}) = 0 \\ \ddot{v}_{d}^{+}(\frac{7}{6}e^{-3}) = \frac{1}{9} \end{cases}$$

(40a)

$$(40b)$$

and the safe time step is

$$\Delta t = \Delta t_d = 3 \tag{41}$$

After the third iteration, all state variables have become quiescent, and circuit has attained the steady state with all capacitor state variables equal to one volt. Notice that the time step size increased by one order of magnitude between the first and second iteration and by three orders of magnitude between the second and third. Classical FE approximation would have been stuck at a step size roughly equal to the first throughout the transient simulation, so instead of three time steps there would have been thousands for such a stiff system.

Figure 3.6 Example underdamped system.

Figure 3.7 The gross response of the underdamped system in Fig. 3.6.

A classic underdamped system and its transient response simulated based on the proposed simulator are shown in Fig. 3.6&3.7, respectively. The state equation of the underdamped system can be represented as

$$\begin{cases} \dot{v}_c = i_L \\ \dot{i}_L = -v_c - i_L + u \end{cases}$$

(42)

At the initial state, none of these state variables is quiescent, thus the time derivatives and second order time derivatives can be calculated to be

$$\begin{cases} \dot{v}_{c}^{+}(0) = 0 \\ \dot{i}_{L}^{+}(0) = 1 \end{cases}$$

$$\begin{cases} \ddot{v}_{c}^{+}(0) = 1 \\ \dot{i}_{L}^{+}(0) = -1 \end{cases}$$

(43b)

and the safe time step based on (24) is  $\Delta t=1$ .

In the second iteration, state variable  $i_L$  becomes quiescent. Thus, the time derivative and second order time derivative can be calculated based on (23b) & (27)

$$\begin{cases} \dot{v}_{c}^{+}(1) = 1 \\ \dot{i}_{L}^{+}(1) = -1 \\ \ddot{v}_{c}^{+}(1) = -1 \\ \ddot{i}_{L}^{+}(1) = 0 \end{cases}$$

(44a)

The safe time step for the second iteration is  $\Delta t=1$  and after the second iteration, all state variables have become quiescent with the circuit in steady state. The steady state is correct, but the

ringing of this underdamped system is greatly suppressed. The property of ringing suppression is because the quiescent state variables are forced to have zero second order time derivative and is applicable for finding steady state which is discussed in following chapter.

The whole of this section has focused on illustrating how the proposed simulator works for linear circuits and drives them all the way to their steady states. The drawbacks are obvious since accuracy control has yet to be applied. But there are advantages over the BE, or any other implicit integration method as follow. Applying the proposed static-driven algorithm, we need not perform an *n* by *n* matrix inversion at each iteration as with the BE integration method. As the number of quiescent state variables increases, the size of submatrix  $A_{11}$  gradually expands to become the entire state space matrix *A*. (Of course, this is not an efficient mechanism to invert a matrix *A* if one does not want to approximate the trajectories of the state variables.) Thus after *n* iterations, the simulation ceases at the steady state. Furthermore, the time constant approximation in the proposed algorithm groups all the close time constants in the matrix which needs to be inverted, thus, no ill-conditioned matrix inversion is entailed.

### **3.3 Integration Error Control**

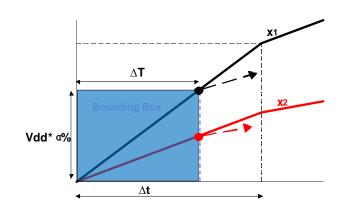

Figure 3.8 The depiction of the Excursion-limit accuracy control mechanism.

Figure 3.9 The refined response of  $v_b$  for the stiff system shown in Fig. 3.4.

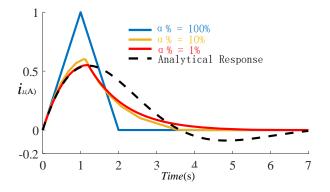

Figure 3.10 The refined response of  $i_L$  for the underdamped system in Fig. 3.6.

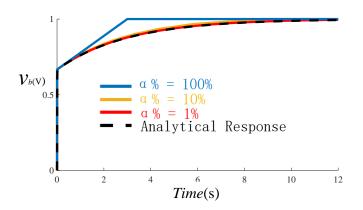

From the gross response of the stiff system and the underdamped system in Fig. 3.4&3.6, respectively, the proposed algorithm without error control drives the state variables to steady state, but very coarsely and therefore inaccurately. The time intervals calculated from (23) are not small enough to smooth the transient response. Thus, a refined step size is required. To address this issue, an excursion-limited accuracy control mechanism is applied. This mechanism employs a user defined accuracy control parameter  $\alpha$ % introduced below to restrain the maximum excursion  $\Delta \mathbf{x}$  at every iteration

$$\Delta T = \frac{V dd \cdot \alpha \%}{\max(\dot{\boldsymbol{x}}^+)} \tag{45}$$

When  $\Delta T > \min(\Delta t_{nq})$ , a direct transition towards quiescence following  $\min(\Delta t_{nq})$  is employed. When  $\Delta T <= \min(\Delta t_{nq})$ , then  $\Delta T$  should be considered to be the safe time step for the present iteration. With  $\Delta T <= \min(\Delta t_{nq})$  as illustrated in Fig. 3.8, the accuracy control technique in (45) creates a bounding box for the excursions of all state variables. All state variables which are programed to follow the solid line should be reevaluated at the edge of the bounding box depicted by the dashed arrows. At each iteration, this technique limits the maximum change for the leading state variable. The refined responses for the stiff system and the underdamped system with various accuracies  $\alpha$ % are shown in Fig. 3.9&3.10, respectively.

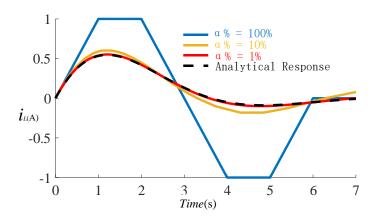

Even with the availability of excursion-limited accuracy control mechanism, the property of ringing suppression for the RLC circuit is still there as shown in Fig. 3.10. To attain utmost accuracy, underdamping must be captured by the proposed algorithm, thus, extra tolerance control for these quiescent state variables is needed when the excursion-limited accuracy control mechanism is only required by these dynamic state variables. The tolerance control function can be expressed as

$$err_{q}(\mathbf{x}) = \frac{q_{q}(\mathbf{x}(t+\Delta t)) - q_{q}(\mathbf{x}(t))}{\Delta t} + f_{q}(\mathbf{x}(t+\Delta t))$$

(46)

where  $err_q$  represents the error of quiescent state variables, if quiescent state variables with errors larger than the default tolerance value  $tol=1e^{-6}$ , then quiescent state variables rejoin the dynamic group and the circuit gets reevaluated. If we set the accuracy control parameter  $\alpha$ % to be the coefficient of the default tolerance value as ( $tol \cdot \alpha$ %) and re-simulate the circuit in Fig. 3.6, we have the transient response as shown in Fig. 3.11.

Figure 3.11 The refined response of  $i_L$  for the underdamped system in Fig. 3.6.

# **3.4 Performance Evaluation**

Figure 3.12 Operational amplifier circuit and its transient response.

Figure 3.13 Bandgap circuit and its transient response.

Figure 3.14 An underdamped nonlinear circuit and its response.

An operational amplifier, a bandgap circuit and an underdamped nonlinear circuit, are shown, respectively, in Figs. 3.12 to 3.14. These classic circuit examples are chosen because they are, respectively, sensitive to the input signal, insensitive to the input signal and underdamped. They are all simulated with BE integration method and with the proposed algorithm.

The transient response differences between the two integration methods, with  $\alpha$ %=0.1% for the proposed algorithm, and multiple rise times to maximally mimic step-like functions are performed with the BE integration approximation method in MAPP. In MAPP, simulation starts when the input has already climbed to VDD. Thus, the latter suppresses stiff system information. The power flowing into that node VDD versus time is shown in Figs. 3.12 to 3.14, respectively.

As the rise time of the steep ramp becomes faster, the power curve becomes closer to the response of a step function. When high accuracy  $\alpha$ % is specified, the proposed algorithm generates simulation results that are essentially identical to those of BE integration methods.

In order to illustrate the computational effort of static driven method, a large-scale linear circuit is presented in Fig. 3.15 where  $R1=R2=\dots=1$  and C1=Cn/n;  $C2=2\cdot Cn/n$ ; Cn=1. To render

this example a stiff system, n is selected to be 1000. The run time is defined as the CPU time spent on matrix manipulation for both algorithms and the run time ratio between the proposed method and BE with the same accuracy is shown in Fig. 3.16.

Figure 3.15 Schematic of an RC ladder circuit.

Figure 3.16 Run-time ratio versus accuracy control parameter with 1000 node RC ladder.

# 3.5 Pseudo transient DC convergence applying static driven method

Pseudo transient continuation is the most reliable method for computing the DC convergence point when other presumably faster DC convergence methods fail. Unlike the NR method, which ignores the effects of capacitance and inductance memory elements, the pseudo transient method approaches the steady state by roughly following the transient trajectory.

Moreover, following the exact physical transient may not be necessary as the intermediate states are not of interest.

Underdamped/oscillating and stiff systems are the main cause of slowing the transient progress [34-35]. Overcoming the underdamped/oscillating and stiff system aspects of circuit behavior, while retaining the stability of the transient process, is the key to improving the efficiency of pseudo transient simulation. Based on above, applying the static-driven method not only shortens the run time, but also suppresses the oscillating as shown in Fig. 3.7 when the second order time derivatives are controlled. The proposed pseudo transient method and its performance are discussed as follows.

The general form of the first and second order time derivatives of the system can be represented as

$$\dot{\boldsymbol{v}}_n = \boldsymbol{g}(\boldsymbol{v}_n, \boldsymbol{u}) \tag{47a}$$

$$\ddot{v}_n = \frac{\partial g}{\partial v_n} \cdot \dot{v}_n + \frac{\partial g}{\partial u} \cdot \dot{u}$$

(47b)

where u stands for the input functions, and for simplicity step function excitations are presumed. If the node voltage vector  $v_n$  is decomposed into two groups  $v_{st}$  and  $v_{dy}$ , then (5b) can be rewritten as

$$\begin{bmatrix} \vec{\boldsymbol{v}}_{st} \\ \vec{\boldsymbol{v}}_{dy} \end{bmatrix} = \begin{bmatrix} J_{11} & J_{12} \\ J_{21} & J_{22} \end{bmatrix} \cdot \begin{bmatrix} \vec{\boldsymbol{v}}_{st} \\ \vec{\boldsymbol{v}}_{dy} \end{bmatrix}$$

(47c)

and according to the indices of the two groups, the matrix is decomposed into submatrices. To force the quiescent group to have zero second order time derivatives, the first order time derivative needs to be modified accordingly as

$$\ddot{\mathbf{v}}_{st} = \mathbf{J}_{11} \cdot \dot{\mathbf{v}}_{st}^{+} + \mathbf{J}_{12} \cdot \dot{\mathbf{v}}_{dy} = 0 \tag{48a}$$

$$\dot{\mathbf{v}}_{st}^{+} = -J_{11}^{-1} \cdot J_{12} \cdot \dot{\mathbf{v}}_{dy} \tag{48b}$$

and the dynamic group retains the same time derivative.

As the node voltages step to the next time point at different rates, the node voltage with the smallest approximated time constant enters the quiescent group earlier than other node voltages. Sequentially, all node voltages join the quiescent group and approach the universal steady state.

The static-driven method provides accurate transient analysis with proper error control [36]. But in the pseudo transient method, intermediate accuracy is not of concern, thus, sending the node voltages with the same order of magnitude approximated time constants to the quiescent group at the same time is acceptable. Based on the above, the new goal here is to set the quiescent group to have zero time derivative at the next time point, thus, the time derivative of the next time point can be represented as

$$\dot{\mathbf{v}}_{n}(t + \Delta t) = \mathbf{g}(\mathbf{v}_{n}(t) + \dot{\mathbf{v}}_{n}^{+} \cdot \Delta t, \mathbf{u}) = 0$$

$$= \mathbf{g}(\mathbf{v}_{n}(t), \mathbf{u}) + \frac{\partial \mathbf{g}}{\partial \mathbf{v}_{n}} \cdot \dot{\mathbf{v}}_{n}^{+} \cdot \Delta t$$

$$= \dot{\mathbf{v}}_{n}(t) + \frac{\partial \mathbf{g}}{\partial \mathbf{v}_{n}} \cdot \dot{\mathbf{v}}_{n}^{+} \cdot \Delta t$$

(49a)

and the modified time derivative of the quiescent group can be calculated as

$$\dot{\mathbf{v}}_{st}^{+} = -[J_{11}]^{-1} \cdot [\frac{\dot{\mathbf{v}}_{st}(t)}{\Delta t} + J_{12} \cdot \dot{\mathbf{v}}_{dy}]$$

(49b)

Unlike (48a) which forces the second order time derivative to be zero to constrain the quiescent group at the next time point, (49b) minimizes the time derivatives of the quiescent group at the next time point. If the time derivatives of quiescent elements have already been successfully minimized, then (49b) becomes essentially the same as (48b) as

$$\dot{\mathbf{v}}_{st}^{+} = -[J_{11}]^{-1} \cdot [\frac{\dot{\mathbf{v}}_{st}(t) \approx 0}{\Delta t} + J_{12} \cdot \dot{\mathbf{v}}_{dy}] = -[J_{11}]^{-1} \cdot [J_{12} \cdot \dot{\mathbf{v}}_{dy}]$$

(50)

Finally, all node voltages are occupied in the quiescent group and the time derivative calculated from (49a) remains zero.

Figure 3.17 Circuit schematic for an LNA.

Figure 3.18 Accurate, rough, and pseudo transient response of the LNA of Fig. 3.17.

# Algorithm Flow:

| Input:                                                                                     | Circuit netlist S; Excitation function <b>u</b> ; |

|--------------------------------------------------------------------------------------------|---------------------------------------------------|

|                                                                                            | Accuracy parameter α%;                            |

| Output                                                                                     | Time points vector tpts;                          |

| :                                                                                          | Converged node vector $v_n$ ;                     |

| Find the first and second order time derivative of node vector based on chosen integration |                                                   |

| method;                                                                                    |                                                   |

|                                                                                            |                                                   |

Add the node with opposite sign of first and second order time derivative to the quiescent group and the rest to dynamic group;

$\boldsymbol{v}_n = [\boldsymbol{v}_{st} ; \boldsymbol{v}_{dy}];$

*While*  $F(v_n(t)) >= le-6$

Calculate  $\dot{v}_{st}^{+}$  and  $\dot{v}_{dy}$  based on (49b) and (47a);

Remove  $\dot{v}_{st}^{+}$  and  $\dot{v}_{dy}$  that equal zero to avoid being divided by zero in the following calculations;

Get

$$\Delta t_{st} as \frac{Vdd \cdot \alpha\%}{\dot{\mathbf{v}}_{st}^{+}}$$

for every quiescent element;

Get  $\Delta t_{dy} as \frac{Vdd \cdot \alpha\%}{\dot{\mathbf{v}}_{dy}}$  for every dynamic element;

$\Delta t = \min(\Delta t_{st}, \Delta t_{dy})$ ;

$\mathbf{v}_{dy}(t + \Delta t) = \mathbf{v}_{dy}(t) + \dot{\mathbf{v}}_{dy} \cdot \Delta t \ \mathbf{v}_{st}(t + \Delta t) = \mathbf{v}_{st}(t) + \dot{\mathbf{v}}_{st}^{+} \cdot \Delta t$ ;

End

Return tpts, v<sub>n</sub>;

Incidentally, no matter whether (48a) or (49a) is applied, the control technique of the second order time derivative suppresses ringing [36] which is beneficial for dealing with the underdamped region of the pseudo transient response. An illustrative underdamped circuit example is shown in Fig. 3.17 and its pseudo transient response applying (49a) is shown in Fig. 3.18.

For summary purposes, the general flow is presented as in Table 3.2 above. It is general and admits any pseudo transient integration approximation method.

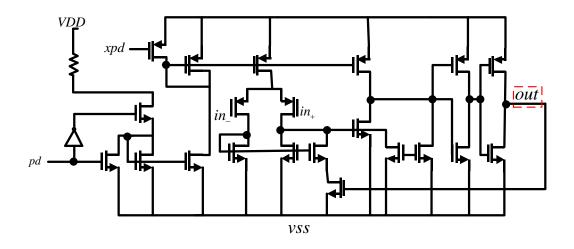

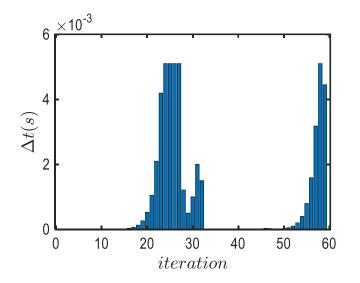

Based on the algorithm flow, two more circuit examples including a comparator and a bandgap are tested in terms of both the proposed pseudo transient method and the conventional pseudo transient method. Fig. 3.19 shows the schematic of the comparator and Fig. 3.20 shows the response of the proposed pseudo transient response compared against the accurate and rough transient response. The time step size of the entire pseudo transient process is monitored and shown in Fig. 3.21.

Figure 3.19 Schematic of the comparator circuit.

Figure 3.20 Accurate, rough, and pseudo transient response of comparator.

Figure 3.21 Time step size history of the comparator circuit.