Low Temperature Pure Boron Layer Deposition for Silicon Diode and Micromachining Applications

Xingyu Liu

# LOW TEMPERATURE PURE BORON LAYER DEPOSITION FOR SILICON DIODE AND MICROMACHINING APPLICATIONS

Xingyu Liu

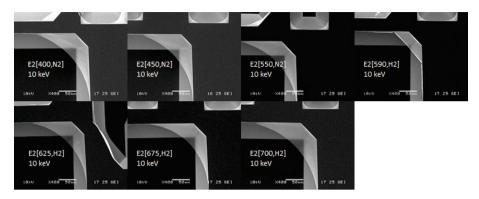

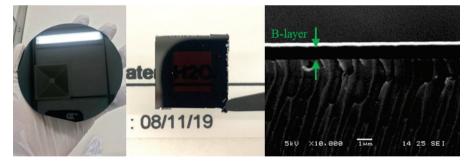

#### **Graduation Committee:**

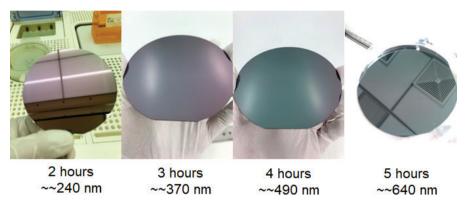

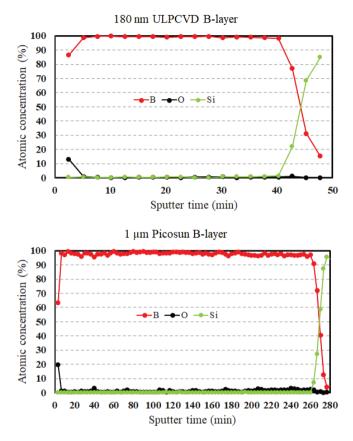

| prof.dr. J.N. Kok           | University of Twente (chairman/secretary) |

|-----------------------------|-------------------------------------------|

| prof.dr. J. Schmitz         | University of Twente (supervisor)         |

| prof.dr. L.K. Nanver        | University of Twente (supervisor)         |

| prof.dr. S.M. García Blanco | University of Twente                      |

| dr.ir. Y. Zhuang            | Wright State University, USA              |

| prof.dr. K. Pedersen        | Aalborg University, Denmark               |

| dr.ir. S. Put               | Mirion Technologies, Belgium              |

| dr.ir. E. Hijzen            | Philips, Eindhoven                        |

| dr.ir. R.J.E. Hueting       | University of Twente                      |

This work was funded by the Netherlands Organization for Scientific Research (NWO), project "silicon-based detector/imager/LED technology" (nr. 13535), and carried out at MESA+ Institute for Nanotechnology, University of Twente.

Cover design: Bo Zhang Printed by: Gildeprint, Enschede, the Netherlands ISBN: 978-90-365-5254-7 DOI: 10.3990/1.9789036552547 URL: https://doi.org/10.3990/1.9789036552547

© 2021 Xingyu Liu, The Netherlands. All rights reserved. No parts of this thesis may be reproduced, stored in a retrieval system or transmitted in any form or by any means without permission of the author. Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd, in enige vorm of op enige wijze, zonder voorafgaande schriftelijke toestemming van de auteur.

# LOW TEMPERATURE PURE BORON LAYER DEPOSITION FOR SILICON DIODE AND MICROMACHINING APPLICATIONS

DISSERTATION

to obtain the degree of doctor at the Universiteit Twente, on the authority of the rector magnificus, prof. dr. ir. A. Veldkamp, on account of the decision of the Doctorate Board to be publicly defended on Friday 8 October 2021 at 12.45 hours

by

### Xingyu Liu

born on the 21st of March, 1988 in Liaoning, China This dissertation has been approved by:

Supervisors: prof. dr. ir. J. Schmitz prof. dr. ir. L.K. Nanver

(supervisor) (supervisor)

To my family

# Contents

| Chapter 1 Introduction                                      |    |

|-------------------------------------------------------------|----|

| 1.1 Conventional Si p-n Photodiodes                         | 7  |

| 1.2 Low-Penetration-Depth Light Detection                   |    |

| 1.3 PureB Si Photodiode Features                            | 13 |

| 1.4 PureB Photodiode Fabrication and Applications           |    |

| 1.5 Outline of the Thesis                                   |    |

| Chapter 2 Pure Boron Deposition Technology                  |    |

| 2.1 Background                                              |    |

| 2.1.1 Elemental boron                                       |    |

| 2.1.2 Boron purification and preparation                    |    |

| 2.1.3 Boron doping technology in the semiconductor industry |    |

| 2.2 Chemical Vapor Deposition of Pure Boron on Si           |    |

| 2.2.1 Surface reaction                                      |    |

| 2.2.2 Relationship to electrical behavior of PureB diodes   |    |

| 2.3 Boron Layer deposited at 400°C or 700°C                 |    |

| 2.4 Deposition Equipment and Pre-deposition Procedures      |    |

| 2.4.1 Deposition reactors                                   |    |

| 2.4.2 Surface cleaning prior to deposition                  |    |

| 2.5 Analysis Techniques                                     |    |

| 2.5.1 Ellipsometry for thickness measurement                |    |

| 2.5.2 Electrical characterization with test structures      |    |

| 2.5.3 Wet-etch tests of bulk B-layers                       |    |

| 2.6 Conclusion                                              |    |

| Chapter 3 Electrical Test Structures                        |    |

| 3.1 Metallized Diode Test Structures                        |    |

| 3.1.1 Vertical pnp transistors                                | 48    |

|---------------------------------------------------------------|-------|

| 3.1.2 Lateral pnp transistors                                 | 50    |

| 3.1.3 2-diode measurement techniques                          | 54    |

| 3.2 Non-metallized Test Structures                            | 59    |

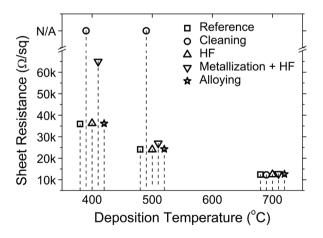

| 3.2.1. Sheet resistance measurements: van der Pauw structures | 60    |

| 3.2.2. Sheet resistance measurements: ring structures         | 61    |

| 3.2.3. Extraction of electron current                         | 63    |

| 3.3 Conclusions                                               | 64    |

| Chapter 4 Material Analysis Using TMAH/KOH Wet-Etching        | 67    |

| 4.1 Conventionally Used Si Anisotropic Wet-Etch Masks         | 68    |

| 4.2 Wet Chemical Etch Mechanism for Silicon in TMAH or KOH    | 69    |

| 4.3 Experimental Procedures                                   | 70    |

| 4.3.1 Sample overview                                         | 70    |

| 4.3.2 Analysis techniques                                     | 71    |

| 4.4. Silicon Cavity Etching on Patterned Wafers               | 71    |

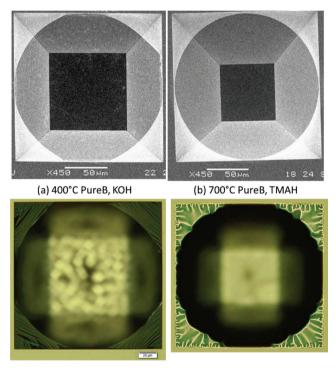

| 4.4.1. Dependence on B-deposition temperature                 | 71    |

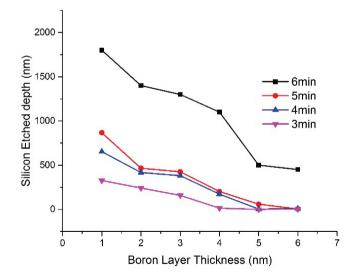

| 4.4.2 Dependence on thickness for 400°C B-deposition          | 72    |

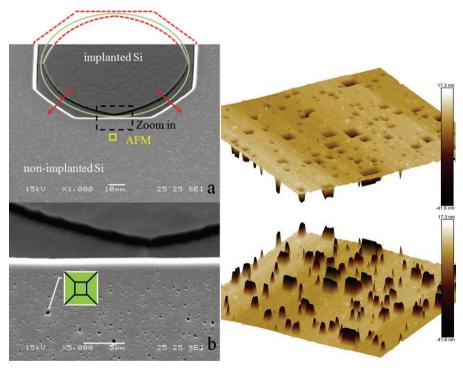

| 4.4.3. Non-implanted regions with 1-nm-thick B-layers         | 76    |

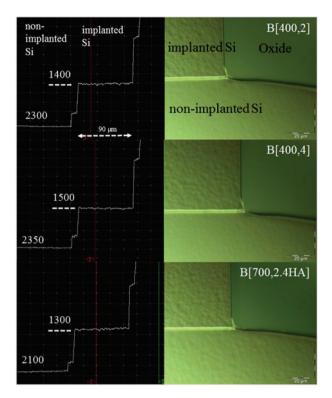

| 4.5 Patterning with B-Layers                                  | 79    |

| 4.5.1 Si etching after B removal                              | 79    |

| 4.5.2. Localized B-layer removal                              | 81    |

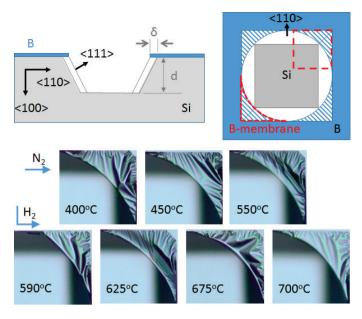

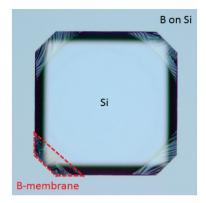

| 4.6 Overhanging B-Membranes                                   | 84    |

| 4.7 Conclusions                                               | 87    |

| Chapter 5 Low Temperature Boron Depositions                   | 89    |

| 5.1 Si Surface Preparation Before B-Deposition                | 89    |

| 5.2 Picosun B-Layers                                          | 95    |

| 5.3 MBE Boron Deposition                                      | 99    |

| 5.4 B-Deposition in the ULPCVD System                         | . 103 |

| 5.5 Back-Etching of B-Layers to the B-Si Interface |     |

|----------------------------------------------------|-----|

| 5.6 Conclusions                                    | 110 |

| Chapter 6 B-Membrane Development and Reliability   | 111 |

| 6.1 Membranes on Semiconductors                    | 111 |

| 6.2 Experimental procedures                        | 113 |

| 6.3 Stress Measurements                            | 114 |

| 6.3.1 Epsilon B-layer samples                      | 114 |

| 6.3.2 Picosun B-Layer Samples                      | 118 |

| 6.4 Overhanging Membranes                          | 119 |

| 6.5 Closed Membranes                               |     |

| 6.6 Conclusions                                    |     |

| Chapter 7 Conclusions and Recommendations          | 131 |

| 7.1 Conclusions                                    | 131 |

| 7.2 Recommendations for Future Work                |     |

| Bibliography                                       | 135 |

| List of Abbreviations and Variables                | 149 |

| Summary                                            | 155 |

| Samenvatting                                       |     |

| List of Publications                               |     |

| Acknowledgement                                    |     |

### **Chapter 1 Introduction**

The evolution towards smaller devices for integrated circuits (ICs) has triggered the development of 2D materials, which in theory could lead to a new generation of high-performance devices of only a few nanometers in size. For example, graphene, a 2D sheet of well-organized honevcomb carbon atoms, has very promising properties such as high mobility and high material strength [1]. However, disappointments with respect to manufacturability and bandgap engineering have shifted much of the research efforts to a series of other, electronically promising, 2D materials, some of which have been successfully fabricated [2], such as silicene [3], germanene [4], monolayer molybdenum disulfide (MoS<sub>2</sub>) [5], phosphorene [6], and borophene [7-11]. Although the properties of these 2D materials are exciting, they all face major challenges as far as manufacturability is concerned [2]. Mechanical exfoliation as a fabrication method only renders poor efficiency and small sample sizes [12]. Liquid exfoliation suffers from a lack of control of the layer thickness, so the potential device material is mainly confined to layered structures with weak van der Waals forces between the layers [13]. Chemical vapor deposition (CVD) in theory can make the highest quality of 2D materials. However, it requires a catalytical substrate, usually metal, which brings with it another difficulty since damage free transfer is not trivial. Nevertheless, the desire to replace 3D doped regions by 2D layers with comparable electrical functionality is commanding. Therefore, attention is now also being directed towards the electrical properties of interfaces where 2D sheets of compounds are created with special bonding structures that do not occur in the bulk form [2]. For example, the newly discovered topological insulators, where the bulk behaves as an insulator but the surface has exotic metallic states [14], have aroused widespread research interest. The stable surface state and high light-absorption rate make them promising candidates for photodetection [15]. Bismuth selenide ( $Bi_2Se_3$ ) is one of the most popular materials [16, 17] but, as for the other electrically promising 2D materials, topological insulators are facing many practical challenges mostly due to their fragility. Thus, also for these materials, there is a growing interest in looking at interface layers [2] where (1) the 2D electrical functions are formed by inherently more stable interface bonding, and (2) the "2D bulk" material works naturally as a protection layer, making the interface less susceptible to damage from varying environmental conditions.

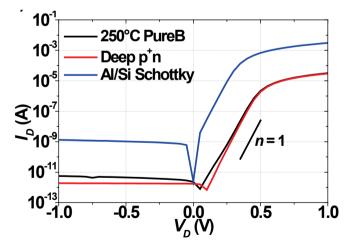

This thesis puts focus on an example of a such an electrically interesting 2D interface layer, the boron-to-silicon interface, and presents a further investigation and development of what has been called PureB technology, including the "2D bulk" material itself. The term PureB was introduced almost a decade ago [18] to describe that pure boron (B) depositions on silicon created p<sup>+</sup>-like regions without actually doping the bulk silicon. At the time, the B deposition was performed at 700°C by CVD in a commercially available ASM Epsilon Si or SiGe epitaxy system, using diborane  $(B_2H_6)$  as a precursor. When deposited on n-type Si, p<sup>+</sup>n-like diodes were created with saturation currents as low as those obtained with conventional deep junction diodes. The light B doping of a few nm of the Si surface at 700°C was not enough to explain the diode characteristics and experiments with deposition temperatures down to 400°C showed that even at such low temperatures, where no bulk doping of the Si can be expected, there was an effective suppression of electron injection into the PureB regions. The junction depth at 700°C was already exceptionally low, only a few nm, but the low temperature p<sup>+</sup>n-like diodes were realized with a metallurgical junction depth of zero nanometer. The exact origin of this special PureB diode behavior is still under investigation but overwhelming experimental evidence has suggested that the B-to-Si bonds created acceptor states where negative fixed charge was trapped, thus attracting holes to the interface [18- 20]. The resulting hole concentration was shown to be so high that a steep electrical field gradient up to the interface efficiently repelled the electrons, reducing recombination in the p-type region [21, 22].

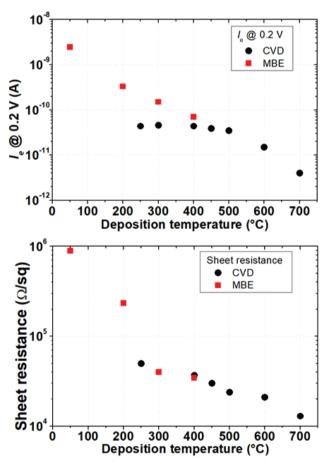

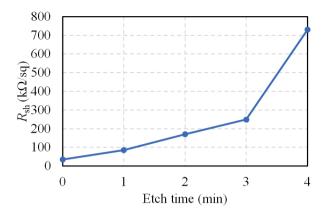

In this thesis work, the investigation of PureB diodes, in particular those fabricated at temperatures below 500°C was continued. There were several indications in earlier work that the quality of the PureB diodes degraded as the deposition temperature decreased. This was seen as a decrease in the conduction through the hole layer along the B-to-Si interface [19, 23], and as an increase of the roughness of the B-layer itself, as the temperature decreased [24]. To gain more information on the properties of the PureB diodes as a function of deposition conditions, several new experimental methods were developed in this thesis work to enable an evaluation of the diode and associated B-layer quality directly after the deposition, i.e., without any metal contacts or isolation layers on the B. A dedicated electrical characterization method was developed to separate the hole and electron currents in the diodes so that the suppression of the electron injection could be monitored and minimized in a controlled manner. The electron current density,  $J_e$ , and the

sheet resistance,  $R_{\rm sh}$ , of the interfacial hole layer, became the main "figures of merit" (FOM) used to develop the new B layers. At the start of this thesis work, ellipsometry, TEM and AFM imaging had clearly exposed the increasing roughness of the B-layers and connected it to a reduction in the completeness of the B coverage of the Si surface as the temperature decreased, implying a lower concentration of the desirable acceptor states at the surface and an increase of  $R_{\rm sh}$ .

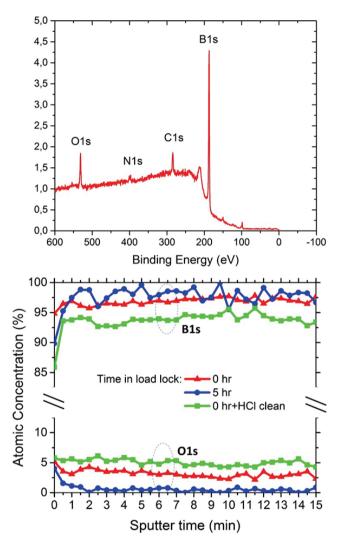

In this thesis work, effort was put into also developing wet etch methods to analyze the B-layers. They were resistant to etchants like hydrofluoric acid (HF), tetramethylammonium hydroxide (TMAH) and potassium hydroxide (KOH), but could be slowly removed in an aluminum (Al) metal etch. The latter property was used to estimate the compactness of the deposited layers, and the integrity of the B-layers was evaluated by immersion in TMAH, that would attack the underlying Si only through weak spots in the layers. These electrical and material analysis methods gave a fast-turnaround-time way of evaluating the as-deposited B-layers. The compactness of the B layer was used to make predictions of what the reliability of the PureB diodes would be in different device applications, and the B-coverage of the Si surface was linked to the ability to form the B-Si bonds responsible for the desired interfacial layer of holes.

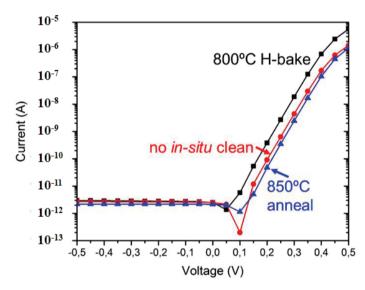

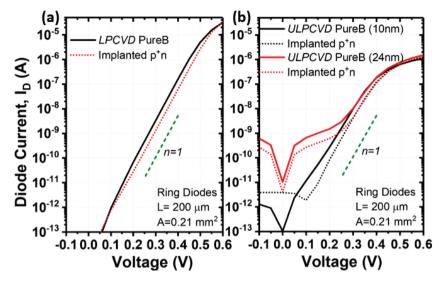

One of the attractive features of 700°C PureB technology is that it is not only very manufacturable, but also fully front-end CMOS compatible [25]. With the reduction of the B deposition temperature to values below 500°C, it also becomes back-end compatible, which considerably increases the applicability [18]. Therefore, the main goal of this thesis work was to explore this deposition regime, and the search was on for finding deposition methods that would result in minimal values of  $J_{e}$ , and  $R_{sh}$  at as low as possible deposition temperatures. Experiments were performed on 5 different deposition systems. High-quality B-layers were regularly donated by the epitaxy company Lawrence Semiconductor Research Laboratory (LSRL) in Tempe, Arizona (US). LSRL provides a Si/SiGe epitaxy service to industry, using ASM Epsilon reactors, and have included PureB in their portfolio. Such epitaxy systems are not widely available in industry, and if they are available, the B-deposition is often deemed incompatible with the existing epitaxy processes being run on the systems. Therefore, it was also of interest to investigate the use of more commonly-used and less contaminationsusceptible equipment. In the UTwente MESA+ NanoLab, it was possible to experiment with the Picosun atomic layer deposition (ALD) system operated in CVD mode, and a Tempress CVD furnace equipped with a turbo pump. In addition, molecular beam epitaxy (MBE) B-deposition was made available in a cooperation with the Institut für Halbleitertechnik (IHT) at the University of Stuttgart. All these methods had their own advantages and disadvantages, but they all resulted in the fabrication of diodes that could be characterized as PureB diodes, even with deposition at room temperature. An issue which is common to all these alternative deposition methods is that, for a "perfect" deposition, the surface of the Si also needs to be clean with no particle or native-oxide contamination. This was achieved in the Epsilon by diluted HF dipping, Marangoni drying, Bernoulli wand handling, etc. Here several other methods were tested and verified.

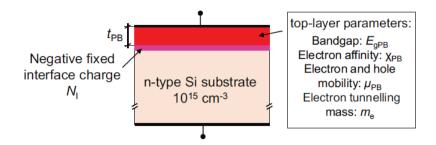

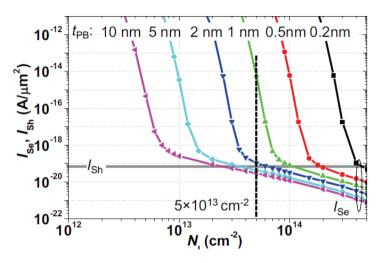

Parallel with this thesis work, the theory behind the PureB diode performance was being examined by Tihomir Knežević (University of Zagreb) using TCAD software. This work indicated that the first monolayer of B bonded to the Si would be sufficient for achieving the very low  $J_e$ . Confirming this directly via experiments by actually depositing only a monolayer of B on the Si became one of the goals for the deposition research. In fact, it did demonstrate that the thickness of the bulk B-layer could be as thin as one nanometer [18] and still deliver attractive  $J_e$  values. However, it proved very difficult to achieve a complete B-coverage of less than 1 nm thick. This is basically because the B deposition is not self-limiting, and boron atoms will inevitably attach to already deposited boron atoms before a complete first monolayer is formed. To overcome this issue, there are two possibilities: (1) to develop an extremely conformal PureB deposition that may promote a selflimiting condition, or (2) to remove the "bulk" boron without damaging the B-Si interface. In this thesis work, both methods were investigated. The simulation work was also instrumental in achieving an understanding of the effects that metallizing on the B layer may have. Many experiments had already showed that  $J_{e}$  would increase upon metallization if the B-layer was only a nm or so thin [18]. This was particularly problematic for the rough, low-temperature B layers. The simulations predicted that the metal would lower the barrier to electrons formed by the interfacial hole layer, if it was brought close enough to the Si surface [21]. This would be the case even without having pinholes in the B layer where the metal could actually touch the Si and form a Schottky diode. This was one of the reasons that the development of B-layer deposition methods performed here was focused almost entirely on non-metallized layers.

The original 700°C PureB technology was very rapidly developed and commercialized for use in photodiode detectors for lithography systems based on both the wavelengths 193 nm (DUV: deep ultraviolet) and 13.5 nm (EUV: extreme ultraviolet) [26, 27], where the former is challenging due to the short attenuation length (~ 4.5 nm) for the light in Si, and the latter gives a high demand on robustness due to the harsh application conditions. The success of these PureB photodiode detectors was not only due to the exceptionally low dark currents achieved with a diode where the photosensitive region extended essentially to the Si surface. Equally important was the optoelectrical stability of the critical B-to-Si interface when subjected to high-dose exposure, and the robustness of the bulk B-layer itself when subjected to aggressive cleaning procedures [28, 29]. However, for the final product, the detector processing also included that the B-layer should be covered, and thus protected, by other layers for functions such as specific wavelength absorption, filtering, or antireflection.

Parallel with the development of the light detectors, PureB photodiodes are also being applied in detectors for low-energy electrons used in scanning and transmission electron microscopy (SEM/TEM) systems [30, 31]. These detectors are particularly demanding with respect to the chemical resilience of the B-layer. Firstly, since electrons are absorbed by all materials, the Si surface of the photodiodes was only covered with the bulk B-layer and there was no further protection of the front-entrance window [22, 32]. Hence, the thinnest possible B-layer, 2 nm for 700°C deposition, was used for detecting electrons of only 200 eV in energy [33]. In this respect, B has the advantage of a low atomic number which minimizes the scattering of electrons [34]. Nevertheless, there was a clear interest in thinning the B entrance window even further to reach a good signal gain even for 100 eV electrons, so this also was an incentive for studying methods that might lead to a complete Bmonolayer coverage of the Si. Secondly, the detectors were comprised of photodiode segments that were several millimeters large which yielded a high series resistance. To lower this, Al grids were processed directly on the Blayer surface. Importantly, the B formed a chemical barrier that protected the Si from reactions with the Al, and the Al could be removed selectively to the B by wet etching in HF [32, 35]. Thirdly, the wafers were exposed to bulk Si micromachining after the B-deposition. In the course of this work, it became clear that the B layers were resistant to Si wet etching in TMAH and KOH.

In view of the chemically resilient nature of the B-layers, including a resistance to etching in the commonly-used wet Si etchants, it became

compelling to perform experiments in the context of Si micromachining and this is also one of the topics of this thesis. For bulk Si micromachining, anisotropic wet etching is commonly achieved by using alkaline solutions such as KOH and TMAH [36]. Traditionally, thin films of materials like silicon nitride or silicon dioxide are mainly used as a hard mask since they offer high etch selectivity to Si and can be deposited with production-ripe equipment for processes such as low-pressure CVD (LPCVD) or plasmaenhanced CVD (PECVD) [37]. For SiO<sub>2</sub>, it is also possible to thermally grow if on the Si, which has the advantage of forming a better-quality material that is highly conformal and an excellent etch barrier. However, this requires temperatures above about 900°C. For processing at 700°C, LPCVD is applicable and also has good conformality, in contrast to PECVD that can be applied below 400°C. In general, the lower the processing temperature of these materials the lower the etch selectivity and a thicker layer is needed as a hard mask. Much research has been dedicated to improving the quality of low temperature oxides and nitrides but still for wet etching of deep cavities the etch rates and/or the presence of pinholes can mean that micrometer-thick layers must be used [38, 39]. This can in turn entail problems with mechanical stress, particularly if thin membranes are to be fabricated. Sputtered metals can also offer a low temperature solution to masking. Etch selectivity is in several cases extremely high, e.g., Ta, Ti, Au, Cr, and Ag, but mask etching/removal, poor adhesion, stress and process compatibility often become issues [40]. All these issues were examined here for B-layers deposited by different CVD methods with thicknesses from a few nm to tens of nm. The B proved to be an excellent masking material, even in the case of loosely-bound low temperature layers, and considering that it is fully CMOScompatible, it could be of great interest for micro-electromechanical systems (MEMS).

The fabrication of closed membranes was also investigated. They are of commercial interest for the systems that are already using PureB detectors. For example, in SEM systems commercial protection membranes are today made of SiN, SiC, SiO<sub>2</sub> and polyimide, but materials such as graphene are being studied due to the low atomic number, the monolayer thickness, the high mechanical stiffness, and high electrical conductivity which would eliminate parasitic charging effects and artifacts common for standard dielectric membranes [41, 42]. B-membranes would also have many of these advantages: B has an even lower atomic number than C and the CVD layers are conductive, albeit with very high resistivity. Also, for application as

membranes, an important advantage with respect to graphene is that B thin films are highly manufacturable [18, 43, 44]. The XUV group at University of Twente was also devoting some time to studying boron as a material for capping EUV pellicles for EUV lithography systems [45]. These pellicles are preferably made of polysilicon due to the high transmissivity and mechanical strength. To ensure resistance to EUV exposure and cleaning plasmas, coatings are necessary. Boron is one of the materials that has been proven resistant to both treatments [46]. For high-volume EUV exposure, the infrared emission needed for preventing overheating of the pellicle requires capping of the poly-Si with layers of suitable emissivity. Capping layers incorporating boron were found to have both good transmissivity [47] and emissivity [45]. To extend this to using pure B-membranes for pellicles, high demands on the mechanical strength and stiffness need to be met. Tensile stress is needed to prevent sagging but film shrink due to densification during exposure/heating gives a risk of excess tension and consequent deformation/breakage. Films with maximum material density are therefore preferred. In this thesis, the investigation is directed towards an analysis of the stress in PureB layers grown with different deposition conditions and fabrication methods for obtaining strong closed membranes.

#### 1.1 Conventional Si p-n Photodiodes

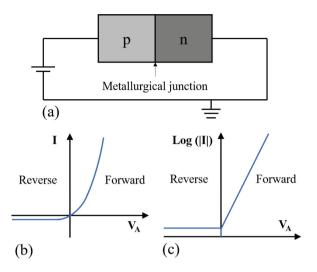

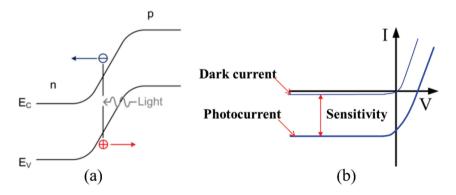

Silicon p-n junctions are elementary "building blocks" used in semiconductor electronic devices such as diodes, transistors, etc. To establish a p-n junction inside a layer of single-crystal Si, one region is doped with acceptor impurities to form the p region and the adjacent region is doped with donor atoms to form the n region. In such a junction, the current in theory only flows in one direction when the diode is contacted as illustrated schematically in Fig. 1.1 where also the corresponding *I-V* characteristics are shown. The interface formed by the transition from a p-doped to an n-doped region is referred to as the metallurgical junction. When the diode is under forward bias, the current increases exponentially with the voltage, whereas the current almost stays constant as a saturation current in reverse bias.

Figure 1.1. (a) Simplified geometry of a p-n diode, and corresponding idealized I-V characteristics; in (b) a linear, and (c) a semi-logarithmic scale.

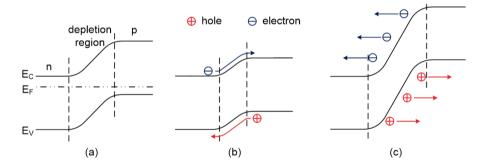

**Figure 1.2.** Band diagram of a p-n junction under (a) zero bias, (b) forward bias and (c) reverse bias [48].

The band diagrams of the p-n junction under zero bias, forward bias and reverse bias are shown in Fig. 1.2. If there is no voltage applied across the pn junction, the junction is in thermal equilibrium, where a potential difference called "built-in voltage" is formed. The built-in voltage is established due to the diffusion of free holes in the p-region and electrons in n-region to cross the junction, making the p-region near the junction negatively charged and nregion positively charged, respectively. This charged region has almost no free carriers, so that it is referred to as space charge region or depletion region. The electric field created by the space charge region forms a barrier to repel the further diffusion for both holes and electrons. When under forward bias, the holes in the p-region and the electrons in the n-region are pushed toward the junction and neutralize the depletion region, resulting in a narrower depletion width and a lower barrier height. Free holes and electrons in the neutral region are able to continuously cross the junction, forming a forward current flow. When under reverse bias, on the contrary, the holes and electrons near the depletion region are pulled away, leaving charged ions which causes the depletion region to increase, as does the barrier height. The high electric field drives minority holes and electrons that have diffused to the edge of the depletion region, into the non-depleted p- and n-regions, respectively. This gives a minimal current flow. Holes and electrons generated inside the depletion region will also be driven by the high electric field to the p and n regions, causing a generation current.

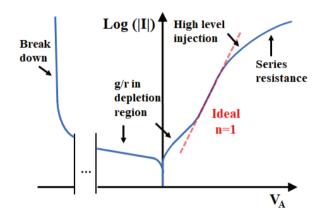

In reality, several sources of deviations from the ideal pn junction diodes are present. This is illustrated in Fig. 1.3. For example, defects in the Si crystal structure will form generation/recombination (g/r) centers so that leakage current appears especially at small reverse/forward bias. In reverse bias, the total current is the sum of the ideal saturation current  $I_s$  and the generation current  $I_{g-r}$ . The  $I_s$  is independent of the reverse-bias voltage and for an ideal diode the total diode current is written as

$$I_{\rm D} = I_{\rm s} \left( {\rm e}^{\frac{qV_{\rm D}}{kT}} - 1 \right),$$

(1.1)

where  $I_D$  and  $V_D$  are the diode current and voltage, respectively, k is Boltzman's constant, T is the temperature in Kelvin, q is the elementary charge. The  $I_{g,r}$ , however, is a function of the depletion width W, which in turn is a function of the reverse-bias voltage. Thus, the actual reverse-biased current increases with the applied voltage. When the voltage increases even further, the electric field across the depletion region also increases and can become so high that sufficient energy is available for a carrier to kick out another carrier from the atomic bond. Thus, an electron-hole pair is generated and it is immediately accelerated in the depletion region, forming even more carriers. This exponential carrier creation causing avalanche breakdown consequently increases the reverse current to, in theory, infinity, but in reality, it will be limited by the series resistance of the device. At low forward bias, the parasitic g-r current may still be important because the depletion region is still wide and the ideal current level is low. At higher forward currents the ideal diode current may start to dominate. However, series resistance from the doped bulk quasi-neutral region and the diode contacts series resistance,  $R_{\rm s}$ , will finally attenuate the current. If the series resistance is low enough, the diode current may also be attenuated by high injection effects because the current starts to contain so many carriers that the minority charge is comparable to the doping level of the region into which it is injected.

Figure 1.4. Illustration of electron-hole pair generation induced by an incident photon (a) [48] and corresponding I-V characteristics (b).

A generation current could also be triggered from outside by, for example, an incident photon or electron. When a photon with sufficient energy is absorbed by the diode, it can elevate a valence electron into the conduction band, creating an electron-hole pair. When the electron-hole pair is generated inside the depletion region or within about one diffusion length from the edge of depletion region, it can contribute to the light-induced current. In this way, photodetection is achieved, normally with the diode under reverse bias. Fig. 1.4 illustrates the band diagram and *I-V* characteristics when the photocurrent is induced by incident light. The photocurrent is composed of the dark current and the photo-induced current, which is proportional to the photo flux. However, light can only be detected when the photocurrent is measurable with respect to the dark current. Thus, to achieve a photodiode with high sensitivity, the dark current should be reliably low.

In a simple 1-D approximation, the current is the sum of the electron current  $I_e$  and hole current  $I_h$ , given by

$$I_{\rm D} = I_{\rm e} + I_{\rm h} = qAn_{\rm i}^2 \left(\frac{D_{\rm n}}{N_{\rm A}W_{\rm p}} + \frac{D_{\rm p}}{N_{\rm D}W_{\rm n}}\right) \left(\frac{qV_{\rm D}}{nkT} - 1\right), \tag{1.2}$$

where *n* is the ideality factor (n = 1 in the ideal case, but n > 1 is used to account for non-idealities), *A* is the diode area,  $D_n$ ,  $D_p$  are the diffusion coefficients of electrons and holes, respectively,  $n_i$  is the intrinsic carrier concentration,  $N_A$ ,  $N_D$  are the acceptor and donor concentrations on the p side and n side, respectively,  $W_p$ ,  $W_n$  are the width of p-type and n-type region, respectively [49]. It is worth noting that when the minority carrier diffusion length (*L*) is shorter than the width, in (1.2)  $W_p$  and  $W_n$  will be replaced by  $L_n$ and  $L_p$ , respectively, which is defined as the average distance a minority carrier moves before recombining.  $D_n$ ,  $D_p$  and  $n_i$  are determined by the temperature and nature of the semiconductor. Thus, the decisive parameters are  $N_A$ ,  $N_D$ ,  $W_p$  and  $W_n$ , which are defined by the doping process. The terms  $N_A W_p$  and  $N_D W_n$  are the integral doping per unit area (or "dose"), for p-type and n-type regions, respectively, when the doping concentration is uniform. When the doping concentration is not uniform, the integral doping can be calculated as

$$N_{\rm A}W_{\rm p} = \int_0^{W_{\rm p}} N_{\rm A}(x) \, \mathrm{d}x, N_{\rm D}W_{\rm n} = \int_0^{W_{\rm n}} N_{\rm D}(x) \, \mathrm{d}x.$$

(1.3)

The terms  $N_A W_p / D_n$  and  $N_D W_n / D_p$  are called the Gummel number [49] of pregion ( $G_A$ ) and n-region ( $G_D$ ), and are inversely proportional to the electron and hole currents, respectively, so the equation (1.2) can be written as

$$I_{\rm D} = I_{\rm e} + I_{\rm h} = \left(\frac{qAn_{\rm i}^2}{G_{\rm A}} + \frac{qAn_{\rm i}^2}{G_{\rm D}}\right) \left(e^{\frac{qV_{\rm D}}{nkT}} - 1\right).$$

(1.4)

Thus, the electron current is determined by the doping profile of the p-type region and hole current by that of the n-type region. To achieve a minimum saturation current, the Gummel number has to be maximized, that is, the

doping concentration and/or width of the doped region should be as large as possible.

### **1.2 Low-Penetration-Depth Light Detection**

The interest in the development and fabrication of highly-sensitive extreme- and vacuum-ultraviolet (EUV and VUV) detectors for the wavelength range 10 nm - 200 nm has been increasing. This is mainly driven by the development of advanced lithography systems that employ these detectors to monitor beam position and/or intensity [48]. Generally, the light absorption in a material increases when the wavelength is short. And the mechanism of light penetration follows the Beer-Lambert law, given by [50]

$$I_1 = I_0 e^{-k_1 l}, (1.5)$$

where  $I_1$  is the transmitted light intensity, after being absorbed by the material,  $I_0$  is the incident light intensity,  $k_1$  is the absorption coefficient, l is the thickness of the material. Thus the intensity of the transmitted light decreases exponentially with the thickness of the absorbing medium.

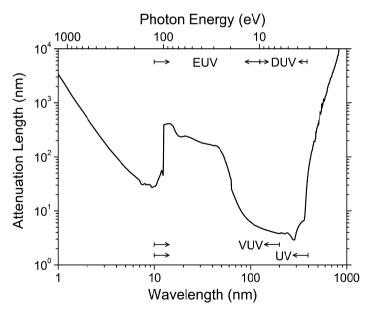

Figure 1.5. Attenuation length in Si as a function of wavelength [51, 52].

Fig. 1.5 shows the attenuation length in Si as a function of wavelength, where attenuation length is defined as the distance at which the intensity of

the beam has dropped to 1/e or about 63% of the light has been absorbed. For near-UV to deep-UV light around 190 nm to 300 nm, the attenuation length in Si is only a few nanometers. At 193 nm, used in high-volume ArF-laser lithography, the attenuation length is only about 5 nm. To detect this lowpenetration-depth light in Si, the depleted region of the junction should be located very close to the Si surface, to maximize the collectable electron-hole pairs. This is extremely challenging in a conventional CMOS process, because to obtain a low saturation current a high Gummel number is also needed and this is difficult to obtain in an ultrashallow junction made by conventional doping methods. The doping concentration in Si is limited by solid solubility that is only high enough at high temperatures where also the dopant diffusivity is high, so hundreds of nanometers deep junctions are usually formed to guarantee the doping levels needed for a low saturation (dark) current. Thus, there is a trade-off between high Gummel number and junction depth.

#### **1.3 PureB Si Photodiode Features**

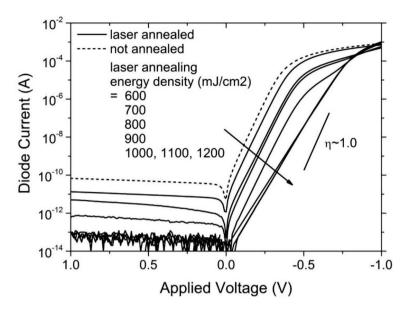

Leading up to the period in which PureB diodes were being investigated, there were other studies that attempted to use pure dopant depositions to make ultrashallow, low-saturation-current junctions [53- 61], but they were all focused on driving the dopants into the Si to create a counter-doping of the Si surface. One of the drive-in techniques that promised to deliver highly-doped, ultrashallow junctions was laser annealing. Attempts were made to activate well-controlled depositions of pure dopants by exposure to excimer-laser melting of the Si surface, thus reducing the dopant diffusion time to microseconds and freezing-in very high doping levels, even above 10<sup>20</sup> atoms/cm<sup>3</sup>. In this way, a highly-doped yet very shallow junction could be achieved. For example, in [62-64] a monolayer of CVD arsenic deposited on a p-type substrate was exposed to 308-nm excimer laser annealing with energy densities from 600 to 1200 mJ/cm<sup>2</sup>. The resulting junctions were contacted by Al/Si (1%) sputtering and diode I-V characteristics going from Schottky-like current levels to deep-junction-like levels were obtained as shown in Fig. 1.6.

Figure 1.6. Measured I-V characteristics of laser-annealed diodes [62, 63].

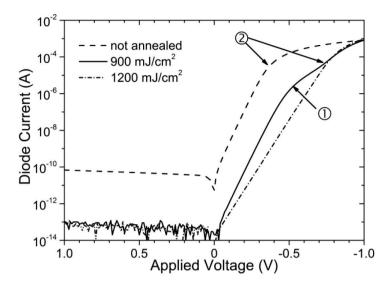

The electron current in these diodes was the same for all anneals, being determined by the total doping of the p-type substrate that was so wide that the Gummel number was not influenced by a few-nm-deep melting and counter-doping of the Si surface. Therefore, the varying diode currents seen in Fig. 1.6 were dominated by the hole current injected from the p-Si substrate into the metal contacts for most anneals. Without laser annealing, a metal/p-Si Schottky diode was obtained and the hole injection was at its highest. With increasing laser energy levels, the saturation current of the diodes decreased. The current saturates at an anneal energy of 1000 mJ/cm<sup>2</sup>, at which point a heavily doped n-region was created with a high doping concentration and an estimated doping depth less than 20 nm. Thus an n<sup>+</sup>p junction diode was formed. It is interesting to note that in this experiment, anomalous I-V characteristics were observed at intermediate energies, which is particularly clear for the 900 mJ/cm<sup>2</sup> curve shown separately in Fig. 1.7. The kink in this curve, starting at about 0.4 V forward bias, marks a transition from a high current level to the same level as the n<sup>+</sup>p diodes. This behavior was explained as having an n-doping that was so light that it was completely depleted when the bias was low enough. This was shown in simulations to pull down the barrier to holes normally set by the built-in voltage of the n<sup>+</sup>p junction because the depletion in the metal/n-Si/p-Si junction then terminates at the metal instead of in the n<sup>+</sup>-region.

Figure 1.7. *I-V* characteristics for diodes that were either not annealed, or annealed at 900 mJ/cm<sup>2</sup> or 1200 mJ/cm<sup>2</sup> [62, 63].

In [63] an example was simulated, assuming the doping concentration  $N_D$  to be  $10^{19}$  cm<sup>-3</sup> with a doping depth of 5.1 nm. The n-region was then fully depleted under small forward bias and reverse bias, and the current in that voltage region was about 2 decades higher than that of the n<sup>+</sup>p junctions and more than 2 decades lower than the pure Schottky case. The current increase before the kink had an ideality factor n = 1, because a potential barrier, which is lowered exponentially with the voltage, was formed across the depleted n-region. In Fig. 1.7, it is seen that the current saturation at point (1) is lower than at the points (2) where the series resistance starts to limit the current. This substantiated the idea that (1) was the point where the fully-depleted n<sup>+</sup> region started to become only partially depleted, and the diode current started to follow the n<sup>+</sup>p diode current.

In the fabrication of photodiodes for DUV/EUV light, the use of a fullydepleted counter doping of the diode surface has been studied as a means of bringing the photo-sensitive Si region up to the surface [65]. However, the passivation of the surface was always a problem since most interfaces with Si are not stable with respect to high-dose irradiation. The high energy, particularly in EUV light, easily damages the interface, thus creating more generation/recombination sites. With respect to laser annealing of deposited dopant layers, which could have been a means of creating such extremely shallow fully-depleted junctions on p-type Si, the technique suffers from a strong pattern dependence and surface rippling, as well as often being destructive to other structures on the wafer. Therefore, it has never really become a production technique in Si IC technology.

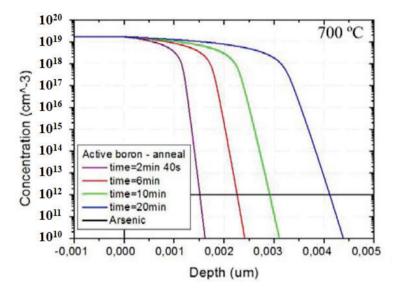

**Figure 1.8.** Simulated B doping profiles in c-Si for B-layer deposition at 700°C as a function of deposition time [66].

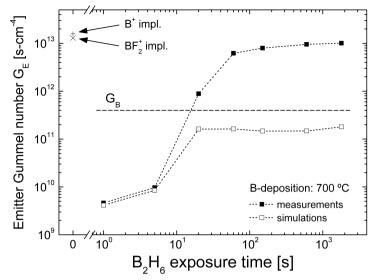

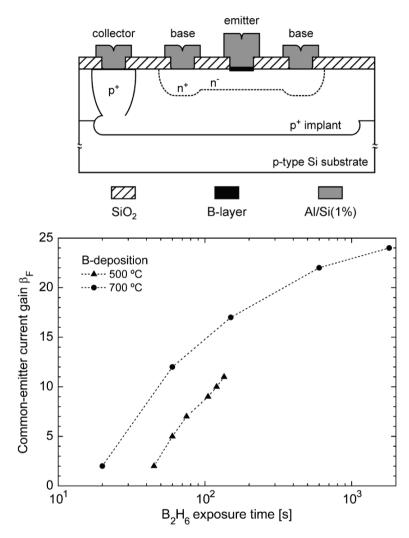

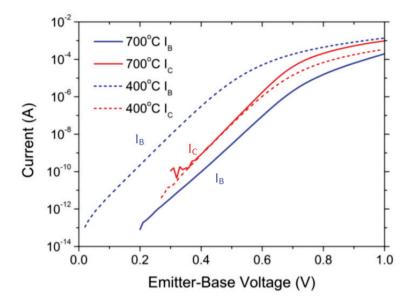

PureB technology, on the other hand, proved to be attractive on all accounts for making p<sup>+</sup>n-like diodes, and PureB photodiodes were fabricated with extremely shallow, robust, optoelectrically stable junctions that also had low dark currents. The first diodes that were studied in depth made use of B-layers that were deposited by CVD in the ASM Epsilon at 700°C, where inevitably some of the Si became B-doped. Fig. 1.8 [66] shows a set of simulated B-doping profiles for B-deposition at 700°C, where the maximum doping level is limited by the solid solubility of ~  $2 \times 10^{19}$  cm<sup>-3</sup>. The diffusion coefficient in c-Si is then also very low so the resulting junction depth is small. The calculated integral doping  $N_AW_A$  is in the range of ~ $10^{12}$  atm/cm<sup>2</sup> for a 30-min deposition time. However, there was a more than 2 decades difference between the measured and simulated Gummel numbers, as shown in Fig. 1.9 [67].

**Figure 1.9.** Measured and simulated emitter Gummel numbers extracted for vertical bipolar transistors fabricated with 700°C PureB emitters [67].

The actual Gummel number of a 700°C PureB emitter region was extracted from the current gain measured for a vertical bipolar transistor structure, given by

$$\frac{I_{\rm C}}{I_{\rm B}} = \frac{G_{\rm E}}{G_{\rm B}} \quad , \tag{1.6}$$

where  $I_{\rm C}$  and  $I_{\rm B}$  are the collector and base current, respectively, and  $G_{\rm E}$  and  $G_{\rm B}$  are the Gummel numbers of the PureB emitter and the base region, respectively. The  $G_{\rm E}$  saturates after about 1 min deposition time, which is equivalent to an integral doping level of  $10^{14} - 10^{15}$  atm/cm<sup>2</sup>. In fact, despite limits set by the B solid solubility and diffusivity, these p<sup>+</sup>n-like diodes behaved just like conventional implanted p<sup>+</sup>n diodes with a junction depth of more than 300 nm. Therefore, the bulk doping is only contributing a negligible amount to the PureB Gummel number. More elaborate representations of the  $G_{\rm E}$ , taking into account the properties of the B-layer itself and the surface recombination velocity at the metal interface,  $S_{\rm A}$ , were also considered by defining it as

$$G_{\rm E} = \int_{W_{\rm QNA}} \frac{N_{\rm A}(z)n_{\rm i0}^2}{D_{\rm n}(z)n_{\rm ie}^2(z)} \, \mathrm{d}z + \frac{N_{\rm A}}{S_{\rm A}} \frac{n_{\rm i0}^2}{n_{\rm iecontact}^2} \,, \tag{1.7}$$

where  $W_{\text{QNA}} = W_{\text{PureB}} + W_{\text{BxSiy}} + W_{\text{c-Si}}$  is the width of p-type region composed of the B-layer, about a nanometer of  $B_x \text{Si}_y$  layer, and the B-doped c-Si. The  $n_{\text{ie}}$  is the effective intrinsic carrier concentration, given by

$$n_{\rm ie}(z) = n_{\rm i} e^{\frac{-\Delta E_{\rm G}(Z)}{2kT}} , \qquad (1.8)$$

where  $\Delta E_G(z)$  is the bandgap difference with respect to c-Si. The silicidation process was inhibited at 500 °C, at which temperature bipolar transistors with the same current gains as the 700°C devices were fabricated, so this suggested that the B<sub>x</sub>Si<sub>y</sub> layer had no significant contribution to  $G_E$  [67].

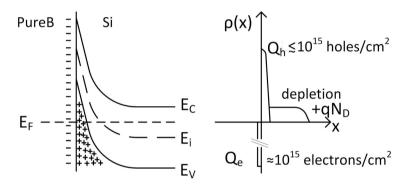

Furthermore, it was not possible to connect the  $G_E$  to the bulk properties of the B-layer since the 1-min B-deposition was so thin, less than 2 nm, that it could not be attributed with a well-defined bandgap that would be constant as the layer thickness was increased. The overall consensus in the literature is also that bulk B is a narrow bandgap semiconductor, which would not promote a high  $G_{\rm E}$ . The influence of a constant  $S_{\rm A}$ , if it was low enough to give a high  $G_{\rm E}$ , would also be reduced as the B-layer thickness increased which is not observed in the experiments. Simulations were also performed to evaluate the influence of possible B-layer electrical parameters on the  $G_{\rm E}$ but did also not lead to a model that fitted with the experiments [68]. Therefore, it is assumed that almost all the p<sup>+</sup>-like characteristics were provided by a B-Si interface interaction. Being an acceptor in Si, it was proposed that the B on the Si surface also created acceptor states that could bind an interfacial layer of fixed negative charge and thus attract holes to the interface [19, 20]. The experimentally determined  $G_E$  corresponded to a pdoping of about  $5 \times 10^{14}$  cm<sup>-2</sup> which coincided well with the density of Si surface atoms,  $6.8 \times 10^{14}$  atm/cm<sup>2</sup>, suggesting an almost fully activated 2D B-Si bonding that would be close to the physical limit.

The extremely high acceptor states in such a confined 2D space gives a unique way of achieving high Gummel numbers and bringing the metallurgical junction to a theoretical level of zero at the same time. The bulk materials (B and Si) on both sides have little influence to the electron suppression: (1), on the Si side, the bulk B doping, if there is any, only contributes approximately a factor of 1% to the effective p-doping, and (2), on the B side, a saturation of the electron suppression can be achieved when the layer reaches a certain thickness, usually less than 2 nm [18], which can also be seen in Fig. 1.9. The exact chemical origin of this behavior remains unclear but the model assuming the monolayer of acceptors states was able to

explain all the experimental data [19]. When the equilibrium is reached at the interface, the acceptor states are filled with electrons, resulting in a layer of fixed negative charge. The high charge gradient at the interface gives a very high electric field. Similar to the field under the gate of a MOS transistor, an inversion layer of holes is built up with the difference that the B layer is not isolating but conductive with very high resistivity. This model of the interface condition, illustrated by the energy band diagram in Fig. 1.10 [19], is supported by overwhelming experimental evidence [18, 19]. Later a more complete TCAD model of PureB diodes was developed and was also supported by the experimental work performed within the present thesis work [21, 68]. This will be discussed further in Chapter 5.

**Figure 1.10.** Energy band diagram (left) and charge distribution (right) illustrating the proposed model that a monolayer of acceptor states is formed at the B-Si interface. The fixed electrons at the interface are indicated with (-) and the inversion layer distribution of holes with (+) [19].

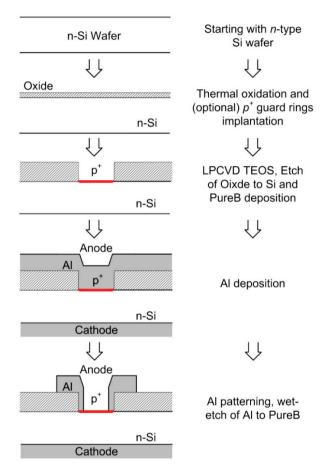

#### **1.4 PureB Photodiode Fabrication and Applications**

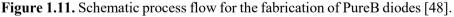

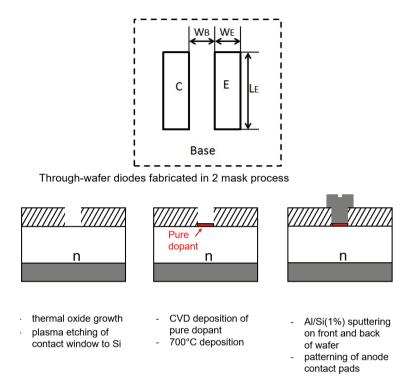

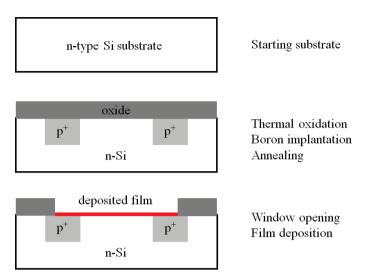

As described in detail in the thesis of L. Qi [48], the basic process flow used in the development of PureB photodiodes is shown in Fig. 1.11. The starting substrates were n-type (100) 1-10  $\Omega$ cm Si wafers having a doping range of about 6×10<sup>14</sup> cm<sup>-3</sup> to 5×10<sup>15</sup> cm<sup>-3</sup>. In some cases, a thick (10 µm or more), n<sup>-</sup>Si epitaxial layer was grown on the n-type starting wafer to lower the diode capacitance [69]. During photodiode operation, the epi-layer was designed to be fully depleted to avoid the series resistance being determined by the high-ohmic epi-layer. A thermal oxide was grown, either 30 nm or 300 nm thick, through which heavily-doped p<sup>+</sup> guard rings were optionally implanted and annealed at 950°C for 20 min in argon gas (Ar). The wafers

with 30 nm oxide were then covered with 300 nm LPCVD TEOS oxide. The anode/illumination window was opened in the oxide by plasma etching with soft- or wet-landing.

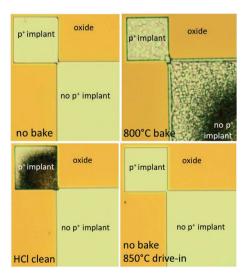

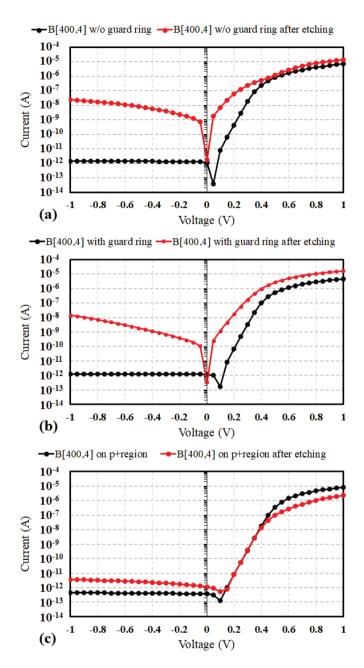

Prior to PureB deposition, the exposed Si was treated with HF dip and Marangoni drying to guarantee a clean and oxide-free Si surface [18]. The CVD deposition was performed at temperatures from 400°C to 700°C, right after which in-situ drive-in/annealing was possible in the same reactor without breaking the vacuum. For contacting, a 675-nm-thick pure Al layer was sputtered at 350 °C on the front of the wafer to form the anode contacts. On the back of the wafer Al (1%) Si was sputtered as contact to the cathode. After anode interconnect patterning, the entrance windows to the

photosensitive areas were opened first by plasma etching the Al back to 100-200 nm. This thin Al layer was then removed by wet etching in HF 0.55% for 3 min to 5 min, selectively to the PureB layer. At last, a 400 °C alloy step in forming gas was performed to passivate the Si/SiO<sub>2</sub> interface at the perimeter of the diodes, thus reducing perimeter leakage.

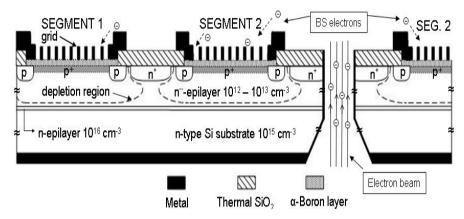

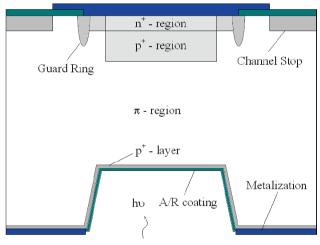

**Figure 1.12.** Schematic cross-section of two neighboring segments of a Blayer detector with a through-wafer hole as aperture for the electron beam. The depletion of the typically 40  $\mu$ m deep n<sup>--</sup> epitaxial layer is indicated. Segments are also isolated by the n<sup>+</sup>-channel-stop and the undepleted n<sup>--</sup> layer [32].

A more sophisticated PureB detector application is given in the thesis of A. Šakić [32]. The basic structure shown in Fig. 1.12 was developed and fabricated for use in advanced SEM systems to enhance performance by detecting electrons with energies below 1 keV. Record-high electron-signalgain for electron energies as low as 200 eV was achieved with 2 nm - 3 nm thick boron layers. Several important features are indicated in the crosssection. For example, low capacitance is achieved by epitaxial growth of a very lightly-doped, tens-of-micron thick n-layers on low-ohmic substrates. Low series resistance combined with a large sensitive front-window area was achieved by patterning a fine aluminum grid directly on the boron surface. With a width of the grid of 2  $\mu$ m, it covered less than 2% of the sensitive area. The series resistance dropped more than 10 times, from  $\sim 280 \Omega$  without metal grid, to  $\sim 20 \Omega$  with the metal grid. The combination of these features lowered the RC time, giving a faster response time for SEM imaging. Compact segmented anode layouts were achieved with lateral junction isolation of the segments using an n-channel stop to eliminate conductive inversion channels

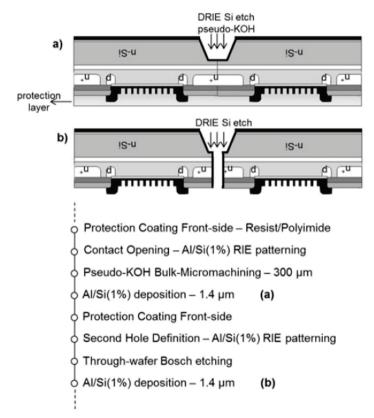

and limit the lateral expansion of the depletion layer. Through-wafer apertures were etched close to the anode regions for detectors designed to monitor back-scattered electrons (BSE). To be able to micromachine the through-wafer holes from the back of the wafer, it was important that the photosensitive surface is protected from both chemical and mechanical damage. Fig. 1.13 exhibits the process flow of back-etch through-wafer apertures.

The bulk-micromachining is performed in two plasma etch steps with resist masking: the first that etches around 300  $\mu$ m that mimics the anisotropic KOH profile, and the second that etches the remaining 250  $\mu$ m with vertical sidewalls using a Bosch process [70]. In general, the bulk micromachining has to be performed when the front-end process is finished, which limits the choice of bulk process including etching, masking and cleaning. Since KOH

is an efficient photoresist stripper, in the first step the pseudo-KOH plasma etching was a more suitable way than wet etching, but it had the drawback of hardening the photoresist so that aggressive cleaning treatment was necessary for the removal, for which oxygen plasma stripping was used. During all this back-of-the-wafer processing, there was a risk of damaging the front-side circuitry, in particular the photosensitive anode regions. To minimize this risk, the PureB regions were protected by 100 nm Al that was left unetched during the grid patterning step. At the end of the micromachining steps, but before the final alloying step, this Al was removed by HF dip-etching. The discovery of boron layers as efficient Si anisotropic wet-etch masking layers could potentially have led to simplifications of the fabrication process. This micromachining application was investigated in detail in the present thesis work and is discussed in Chapter 4. It would be of particular interest in situations where only back-end-of-line temperatures are permitted, but both a  $p^+$  surface region and a KOH masking layer are needed.

**Figure 1.14.** Silicon reach-through avalanche photodiode (RAPD) developed by Laser Components Inc. **(R)** [71].

Another example of how PureB p<sup>+</sup>-regions have been employed in UV detectors, is the silicon reach-through avalanche photodiode (RAPD) with back illumination described in [71] and illustrated in Fig. 1.14. The light-entrance window was located in a wet-etched trench at the back of the wafer. The bulk silicon was anisotropically etched so that the depth of light-absorption  $\pi$  region was carefully controlled. In this design, the boron layer was considered as a means of achieving both masking and p<sup>+</sup>-region

fabrication on the non-etched regions that were metallized and served as contacts to the anode. In these types of configurations, the availability of low-temperature B deposition, the development of which is discussed in Chapter 5, can significantly simplify the process flow.

### **1.5 Outline of the Thesis**

This thesis focuses on further exploring the applicability of pure B depositions in Si technology, among other things by investigating B deposition at lower temperatures to enhance the process compatibility, especially CMOS. Various process conditions are investigated to optimize the tradeoff between manufacturability and functionality. Several characterization techniques were developed to determine the properties of the as-deposited B-layer and to predict the performance of PureB diodes fabricated with these layers. Lastly, the application in MEMS processing was studied with the B-layer functioning as a silicon wet etch mask and membrane.

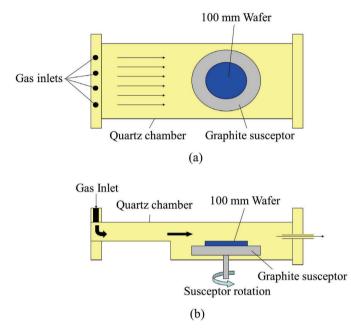

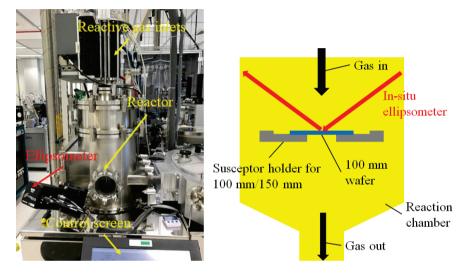

In Chapter 2, the basic principles of boron deposition by diborane decomposition are introduced. The B-Si interface properties found previously for boron deposited at high temperature (700°C) and relatively low temperature (400°C) are described, showing the trends found when going towards lower temperature deposition. An introduction to the three CVD systems used for boron deposition in this thesis is given, including the basic specifications, limitations, and advantages. The electrical and physical characterization techniques practiced in this thesis are summarized.

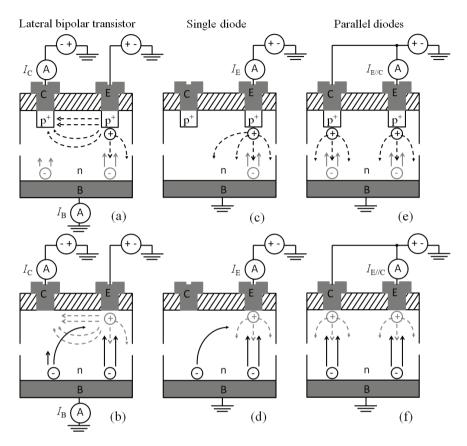

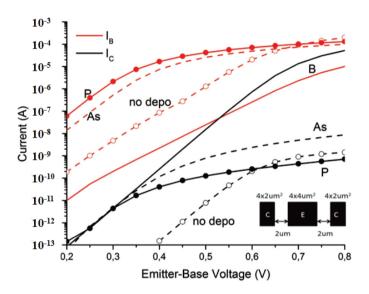

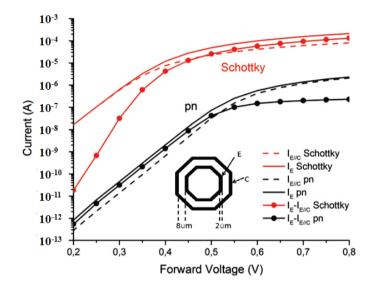

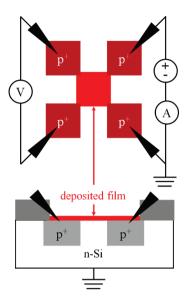

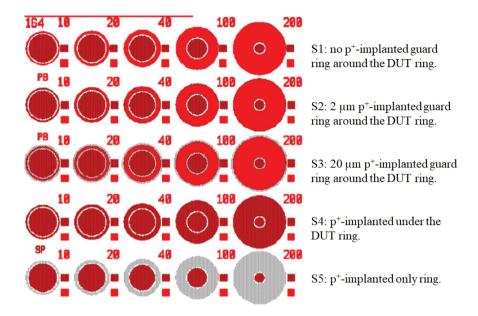

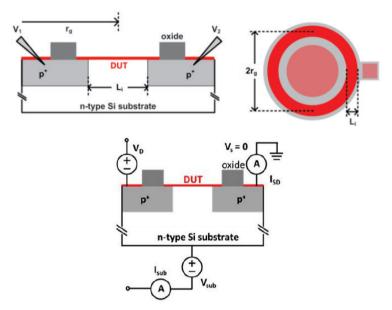

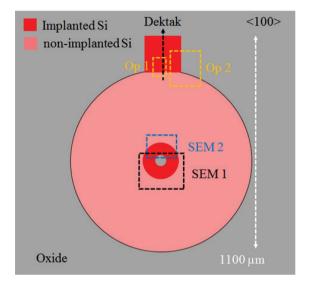

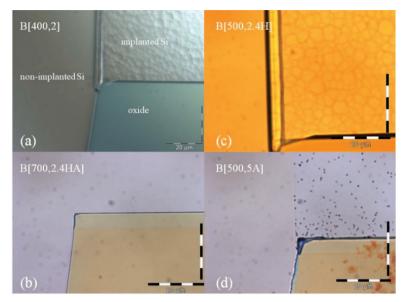

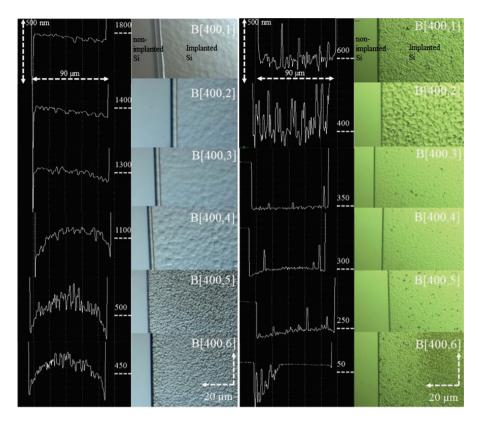

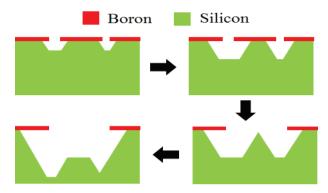

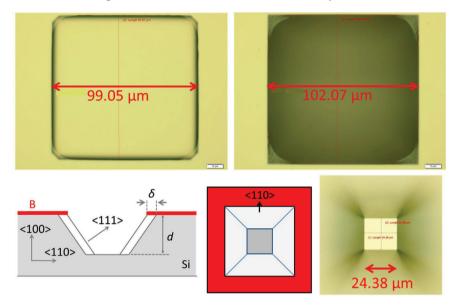

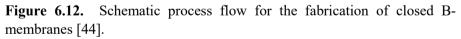

In Chapter 3, the electrical characterization methods are explained in more detail. The 2-diode test structure gives an easy-to-process, fast turnaround-time method of comparing process-dependent current flows when developing ultrashallow/Schottky junction technologies. Differential diode current characteristics and lateral transistor operation of the same 2-diode test structure were used to reliably identify the diode type and variations in metal-Si interfacial properties, independent of parasitic leakage currents. Test structures that required no metallization of the B-layers, such as Van der Pauw structures and sets of ring-structures, were used to measure the conductance along the B-Si interface, which gives a quick way to monitor the degree to which the desired interfacial B-Si bonds were achieved. Sets of non-metallized ring-structures were also designed to allow the extraction of the electron injection into the p-type region of PureB diodes, which also gives an important measure of the degree to which these critical bonds have been made. In Chapter 4, the properties of nanometer-thin pure boron layers deposited by CVD were investigated for use as a barrier against tetramethyl ammonium hydroxide (TMAH) and potassium hydroxide (KOH) etching of Si. The boron layers used were deposited from 400°C to 700°C with thickness down to 1 nm. The topographical differences of implanted and non-implanted Si after TMAH and KOH etching for various times are compared. Boron-layer patterning, fabrication of overhanging boron membranes, and layer stress evaluation are briefly introduced and will be discussed further in Chapter 6. The focus of this chapter is to validate that boron layers under certain deposition conditions are effective as anisotropic wet-etch masks on Si. The etching method is also considered as a way to quickly evaluate the bonding strength of the B-Si and B-B bonds. The former is important for PureB diode fabrication and the latter for B-membrane fabrication.

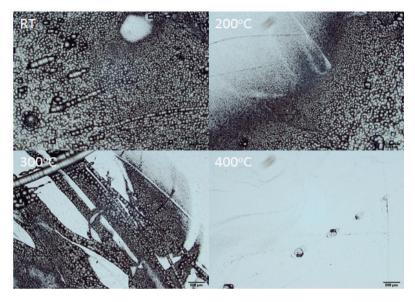

In Chapter 5, the evaluation methods mentioned in Chapter 3 and 4 are applied to B layer deposited from 450°C down to room temperature (RT) in order to characterize these layers with respect to the electrical properties when incorporated in PureB diodes, and for the physical properties when used as wet-etch masks. The lowest possible Si substrate temperatures were tested in the different deposition systems. With MBE, RT deposition was possible and this method is also advantageous in having high surface coverage and low oxygen contamination as compared to other physical vapor deposition (PVD) systems. In this chapter, an investigation is also presented of the effects of several cleaning procedures prior to deposition and annealing after deposition.

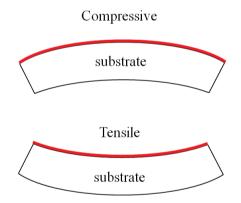

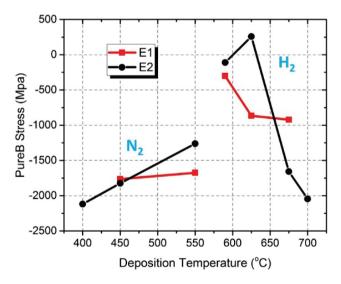

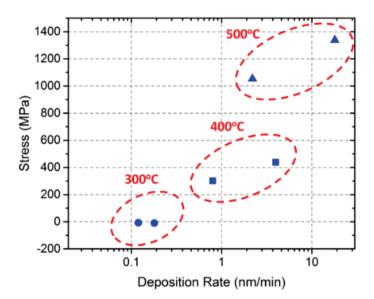

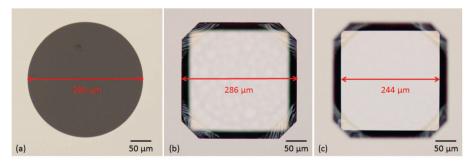

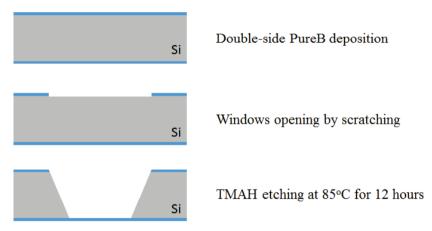

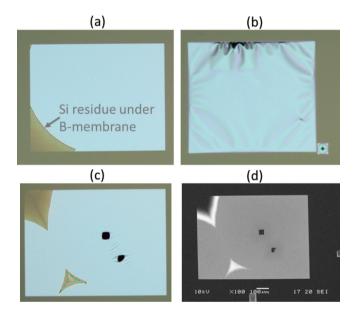

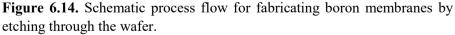

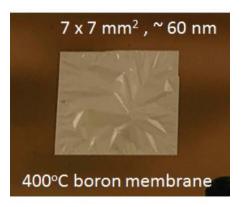

In Chapter 6, a more detailed investigation of B-layers as wet-etch masks and free-stand membranes is given. Stress measurements were performed on a set of B-layers deposited in CVD mode under different conditions (temperature, deposition rate, etc.). Thus, the correlation between processing conditions and layer stress are better understood, leading the way to stress free B-film fabrication. Overhanging B-membranes deposited from various temperatures were fabricated and studied with respect to defects and transparency. Closed B-membranes were fabricated by etching through the Si substrate, using the B-layers simultaneously as Si etch mask and membrane material. The reliability of membranes made of thick boron-layers was tested for layers grown in different reactors.

Finally, Chapter 7 summarizes the main conclusion of the work in this thesis and gives recommendations for the future work.

# **Chapter 2 Pure Boron Deposition Technology**

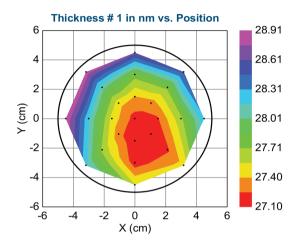

This chapter focuses on the basics of boron: the B element itself, the properties already established for deposition on Si at temperatures from 400 °C to 700 °C, and the methods used in the present research to deposit B on Si and to analyze the results. The deposition equipment used here includes the Picosun and ULPCVD (ultra LPCVD) systems, which are both available in the MESA+ Nanolab at the University of Twente. In addition, the settings for B-deposition by MBE, as made available through a cooperation with the University of Stuttgart, are also described. In Section 2.5 an introduction is given to the boron film analysis techniques that received extra attention/development in order to make them suitable as cost-efficient, rapid methods for examining the B-layers fabricated here. This includes ellipsometry for film thickness measurement, electrical test structures, and wet-etch tests to compare the compactness and robustness of the layers. In addition to these methods, several standardized analysis techniques were also employed such as atomic force microscopy (AFM), X-ray photoelectron spectroscopy (XPS), TEM, SEM, profilometer (Dektak), secondary ion mass spectrometry (SIMS), Nomarski interference contrast microscopy (NICM), and they will be introduced as needed in connection with the results presented in the following chapters. Moreover, a more detailed treatment of the electrical test structures will be given in Chapter 3 in relationship to the development of PureB diodes, and in Chapter 4 the wet-etch tests are also put in the context of the MEMS applications of B-layers.

# 2.1 Background

#### 2.1.1 Elemental boron

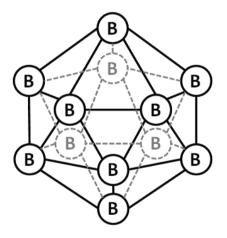

Boron is the fifth element in periodic table, situated between the metal beryllium and the semiconductor carbon (shown in Fig. 2.1), categorized as the lightest of the semi-metals. Boron has only three valence electrons, which would be in favor of metallicity. However, these electrons are sufficiently localized so that boron tends towards insulating behavior. This would explain the poor electrical conductivity at low temperatures. Boron forms highly delocalized bonds, sharing electron pairs among three (or more) atoms, in which the B-B bonds have high strength. Crystalline boron is the second hardest of all elements, only behind diamond, and has a melting temperature over 2000  $^{\circ}$ C [72]. Bulk boron (non-pulverous) is known to have at least

sixteen polymorphs, but only a few of the crystal structures have been identified [9], for example, the  $\alpha$ -B<sub>12</sub> (an icosahedral structure with 12 atoms in a unit cell),  $\beta$ -B<sub>105-108</sub> (rhombohedral structure), tetragonal T-192 [73] and  $\gamma$ -B<sub>28</sub> [74]. In fact, all these crystal structures are dominated by the icosahedral B<sub>12</sub> cluster (shown in Fig. 2.2), which can be interlinked by strong covalent bonds in different ways to form polymorphs [75]. Amorphous and  $\beta$ -rhombohedral structures are closely related with icosahedron being the sub-unit, but disorder occurs in the linking between these icosahedra. [76].

| <sup>4</sup> Be | 5<br>B | <sup>6</sup> C | 7<br>N |

|-----------------|--------|----------------|--------|

|                 | 13     | <sup>14</sup>  | 15     |

|                 | Al     | Si             | P      |

Figure 2.1. The position of boron in periodic table.

#### 2.1.2 Boron purification and preparation

On earth, boron mostly exists in the form of borax, also known as sodium borate, which is a salt of boric acid. Borax has been known and used in ceramic glazes and in metallurgy for centuries, but no one isolated the elements from borax until 1808, when English chemist Sir Humphry Davy used electrolysis on a borax solution and observed a brown mass forming at one electrode [77]. In the same year, French chemists Joseph Louis Gay-Lussac and Louis Jacques Thénard reduced boric acid with iron at high temperatures [78]. Boron was identified as an element by Swedish chemist Jöns Jakob Berzelius in 1824 [79]. The earliest route towards massive boron production was established as boron oxide reduction with alkali metals such as calcium, magnesium, aluminum. However, this product is contaminated with borides of these metals [80]. Boron prepared by fused salt electrolysis is in granular form and is contaminated with the electrolyte, oxide, and possibly with high melting nonvolatile borides [80]. The demand of boron with higher purity in the semiconductor industry has enhanced the use of the reduction of gas-phase boron halides with hydrogen. Not only hydrogen is an easily purified gas, but also BCl<sub>3</sub>, and mostly BBr<sub>3</sub> and BI<sub>3</sub>, are compounds that can be made with very high purity by fractional distillation, by chromatography in gas phase, or by zone melting [79]. However, there are several disadvantages: (1) the BX<sub>3</sub> boron halides are characterized by very low B/BX<sub>3</sub> weight ratios [81], (2) the reaction product HX is corrosive [82], and (3) it requires a high substrate temperature (800°C - 1200°C) [83]. Ultrapure boron for use in the semiconductor industry is produced by the decomposition of diborane at high temperatures followed by a further purification by zone melting or Czochralski processes [84].

#### 2.1.3 Boron doping technology in the semiconductor industry

Boron is well known as the main p-type dopant in silicon IC technology. The conventional and most mature doping techniques are either diffusion from an external source of B, or B implantation and annealing. For both methods the doping level is limited by the solubility of the B in Si, and in many situations not all dopants will be electrically activated. High temperature diffusion from a dopant-containing compound generally suffers from the lack of doping uniformity and dose control. With the continual downsizing of Si devices, the required junction depth has become smaller and smaller. The more than a micron deep diffused junctions were gradually replaced by implanted/annealed junctions with depths in the hundred nanometer range. Implantation, however, suffers from stochastic spatial distribution of the implanted ions and severe Si crystal damage. Therefore, it has always been a challenge to achieve a sufficiently damage-free, highlydoped but shallow p-region that also could meet stringent requirements for the abruptness of the doping profile. Later, p-type Si epitaxy was developed where a thin layer of p-Si is fabricated by adding gas-phase dopants during the Si deposition. For a high B doping concentration, a deposition temperature

above 1000°C is usually implemented, which inevitably causes the diffusion of dopants in both the p and n regions. Despite cross doping, a highly-doped p-region with a metallurgical junction depth as shallow as 10 nm can be achieved. However, the dopant aggregation remains a problem. Since the 80s, efforts have been dedicated to a so-called delta-doping technique [53- 60], where, for example, pure dopants are deposited and capped with another layer before being annealed in order to diffuse and incorporate the dopants. This technique is named after the delta-function-like doping profile with a sharp spike shape. In 2007, C. Ho et al. claimed the invention of monolayer doping (MLD) [61], where they replaced the pure dopants used in delta-doping with self-limiting dopant-containing molecules exposed to rapid thermal annealing (RTA), to enhance the spatial distribution and dose control.

# 2.2 Chemical Vapor Deposition of Pure Boron on Si

#### 2.2.1 Surface reaction

In the semiconductor field, ultrapure amorphous boron (a-B) is mostly prepared either by CVD [25, 85], where it is common to decompose the molecule vapor of boron hydrides  $(B_xH_y)$  on the wafer surface and in the vacuum, or by PVD [86, 87], where the solid phase elemental boron target is vaporized by plasma or electron beam, and boron atoms will subsequently land on the surface. In the chemical approach, the decomposition of boranes is usually realized by plasma or pyrolysis, such as direct current (DC)/radio frequency (RF)/electron cyclotron resonance (ECR) PECVD or LPCVD. Besides the compositional and compactness difference which will be discussed in Chapter 4, chemical-based deposition can be selective with respect to substrate material, which has often been found to be an advantage in electrical device production. However, the substrate temperature needed to realize the decomposition can limit the applicability and compatibility with substrates and other processing steps that do not tolerate the required thermal budget. PVD, on the other hand, is more sensitive to surface topography since it is very directional. In this thesis, we use diborane  $(B_2H_6)$  as the precursor for CVD. B was deposited by CVD and PVD in various types of reactors. The pure boron layers can be deposited on silicon, or any other type of surface, by exposing the substrate to B<sub>2</sub>H<sub>6</sub> while heating it to elevated temperatures. The activation energy of the chemical reaction is then purely provided by thermal energy. In previous studies, the deposition temperature was in the range from 400°C to 700°C, for deposition performed in a commercial Si/SiGe epitaxial reactor ASM Epsilon [18]. Hydrogen  $(H_2)$  was used as the carrier gas to dilute the diborane source. The overall chemical reaction is:

$$B_2H_6(g) \longrightarrow 2B(s)+3H_2(g),$$

(2.1)

where (g) indicates the gas phase and (s) the solid phase. The whole point of this reaction is to release hydrogen molecules from the diborane. The dominating pathway is the generation of borane (BH<sub>3</sub>), which is produced from  $B_2H_6$  in a reversible reaction [88]:

$$B_2H_6(g) \longleftrightarrow 2BH_3(g). \tag{2.2}$$

At a temperature as low as 545 K, diborane is the exclusive product of borane loss, while at higher temperatures another reaction channel is built for the loss of BH<sub>3</sub> [89], namely

$$BH_3 \xrightarrow{\text{surface}} B(s) + \frac{3}{2} H_2(g).$$

(2.3)

The silicon surface reaction mechanism will be explained more thoroughly in the following.

Crystalline silicon forms an FCC (cubic crystal system) structure, in which each Si atom is bonded to four other Si atoms. This is the most stable state for silicon because all the bonds are fulfilled. At the Si (100) surface, silicon atoms bond with two atoms below but lack two atoms above to complete the structure, leaving two available unpaired valence electrons. To achieve an energetically more favorable state, each Si atom is spontaneously bonded to another atom with one electron, forming a row of silicon pairs, namely dimers. This leaves the surface atoms with one available valence electron, which will form electrically active interface traps, known as dangling bonds. BH<sub>3</sub> is a strong Lewis acid, since it is an electron-deficient compound with a low-lying unoccupied orbital, resulting in a facile surface dimer buckling with Si daggling bonds [90]. Low temperature deposition processes are generally controlled by surface reactions, where boron atoms in boron hydrides either form direct bonds with Si surface, or Si-B dimers with Si adatoms and trapped by the following growth of B to become part of the lattice [91]. The silicon surface is usually treated with HF solution dipping prior to boron deposition to remove the native oxide and to terminate the dangling bonds with hydrogen. This hydrogen termination is of great importance because it passivates the dangling bonds of surface silicon atoms to prevent unwanted reactions with other species, especially from carbon and

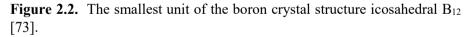

oxygen contamination. Assuming Si-H are hydrogen terminated silicon atoms and Si<sup>o</sup> are silicon atoms with dangling bonds, a simplified model of surface reaction was proposed by [92] as shown in Fig. 2.3 [93], where BH<sub>3</sub> is the dominant reactant. The mechanism is:

Figure 2.3. Reaction model of Si surface and BH<sub>3</sub>[93].

- (1) Physisorption and reflection Si-H+BH<sub>3</sub>  $\longleftrightarrow$  Si-HBH<sub>3</sub> (2.4)

- (2) Migration Si-HBH<sub>3</sub>+Si-H  $\longrightarrow$  Si-H+Si-HBH<sub>3</sub>, (2.5)

- (3) Recombination Si-HBH<sub>3</sub>+Si-HBH<sub>3</sub>  $\longrightarrow$  2Si-H+B<sub>2</sub>H<sub>6</sub>, (2.6)

- (4) Chemisorption  $Si^{\circ}+BH_3 \longrightarrow SiBH+H_2$ , (2.7)

- (5) Diffusion SiB  $\longrightarrow$  Si<sup>o</sup>+B (diffused). (2.8)

After chemisorption between  $Si^{\circ}$  and  $BH_3$ , the incomplete release of hydrogen makes the surface boron naturally passivated. Same mechanism also applies to  $BH_3$  decomposition at boron surface, where in both cases the chemical bond formation between boron atoms and surface dangling bonds (either Si<sup>o</sup> or B<sup>o</sup>) is essential. Those dangling bonds will be exposed by

$$H(g)+Si-H(s) \longleftrightarrow H_2(g)+^{\circ}Si(s), \qquad (2.9)$$

$$H(g)+B-H(s) \longleftrightarrow H_2(g)+{}^{\circ}B(s), \qquad (3.0)$$

where the presence of hydrogen will suppress the forward reaction [85]. In reality, higher orders of boron hydrides ( $B_3H_6$ ,  $B_4H_{10}$ ,  $B_5H_{11}$ , etc.) were found

by mass spectrometry in the gas phase, meaning the mechanism of intermediate reactants and their reactions are rather complex [94]. In the deposited layer, possible cross linking happens between adjacent B-H bonds [85]:

$$B-H(s)+B-H(s) \longleftrightarrow B-B(s)+H_2(g). \tag{3.1}$$

Thus, boron deposition is a process that eventually releases the hydrogen with respect to a serial reaction of gas-phase and surface reaction.

## 2.2.2 Relationship to electrical behavior of PureB diodes

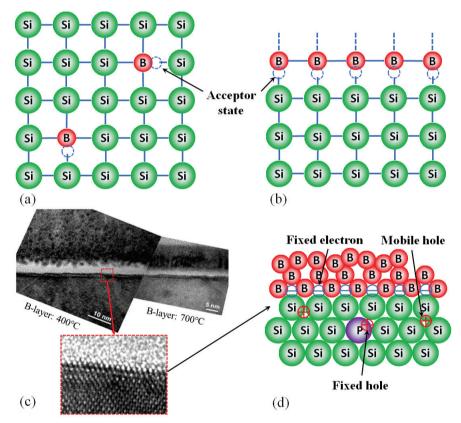

**Figure 2.4.** (a) Schematic of B-doping in a Si lattice. (b) Simplistic model showing how acceptor states between the B and Si dangling bonds possibly could be formed at the Si surface. (c) HRTEM images of CVD B-layers deposited at 400°C and 700°C [24]. (d) Interfacial B-Si acceptor states filled with negative charge attracting holes from an n-doped Si substrate.

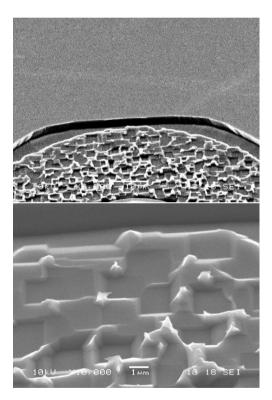

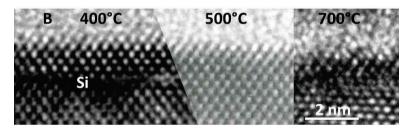

The chemical mechanisms discussed in Section 2.2.1 focus on the creation of covalent bonds between the B and Si surface atoms, and do not give any information on the formation of acceptor states that could be created at or near the B-Si interface and possibly account for the electrical behavior. In an earlier study, the density of a complete monolayer (ML) of boron on Si (100),  $6.78 \times 10^{14}$  cm<sup>-2</sup> [25], corresponded well with the p-doping concentration at the surface that would be needed to fit the 700°C PureB diode characteristics to simulations. Fig. 2.4 (b) gives a very simplistic, speculative model of B-Si interface bonding, where every B-atom connects to a Si-atom by binding the Si dangling bond in much the same way as it would if it was incorporated in the bulk Si lattice as a dopant atom, as shown in Fig. 2.4 (a). A hole that can move freely in the Si lattice is then created. For 700°C Bdeposition there is significant penetration of the B into the Si, with an about a 1-nm-thick B<sub>x</sub>Si<sub>x-1</sub> layer being observed [25]. Therefore, it seems plausible that the observed high surface concentration of fixed negative charge is a result of a high surface concentration of disordered but "normal" B-doping of the Si. However, at 400°C where no bulk doping of the Si is expected, TEM images also showed that the B-Si interface is flat. This is seen in the TEM images of Fig. 2.4 (c) where CVD boron deposited on Si at 400°C is compared to a 700°C deposition [24]. In the 400°C case the B is seen to be deposited epitaxially with the first few atoms following the crystalline structure of Si. In the course of this work, more information was gained about the electrical performance of such low temperature B-deposition. In addition, the challenge of achieving a complete surface coverage with the desired B-Si bonds at these temperatures was given attention. In the past, researchers have presented different views on whether boron would form a complete surface coverage of silicon or nucleate as isolated islands regardless of deposition conditions [85, 95]. In any case, it would always be a challenge to guarantee the surface coverage when the layer is extremely thin (< 1 nm). The exposed surface of silicon would eventually be oxidized in air and this has been found to be detrimental to the electrical performance of PureB diodes. Electrically, the oxidized regions become generation/ recombination sites that are a source of leakage current, while mechanically, they are weak spots when B is exposed to chemicals, which will be discussed in detail in Chapter 4. Thus, the critical boron thickness for surface coverage is of great importance especially for low temperature deposition where the boron atom migration over the substrate surfaces is negligible. Then the immediate surroundings, with the available Si or B bonding possibilities, of the deposited B-atoms will be decisive for the final deposition location. Therefore, depending on the application, it may be favorable to deposit excessive boron (> 2 nm thick), either to extend boron islands until they finally meet, or to overgrow the unsaturated silicon surface until it is fully covered and protected.

## 2.3 Boron Layer deposited at 400°C or 700°C

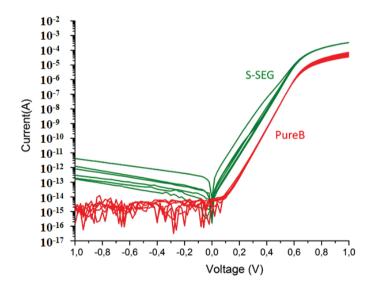

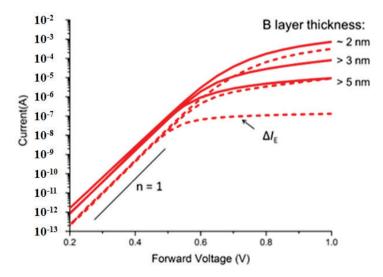

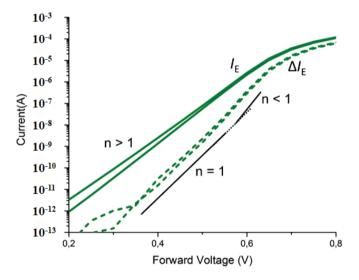

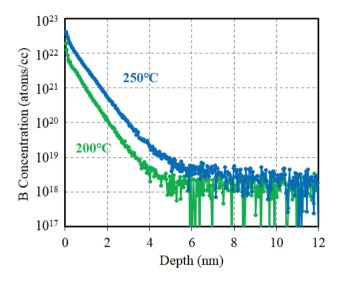

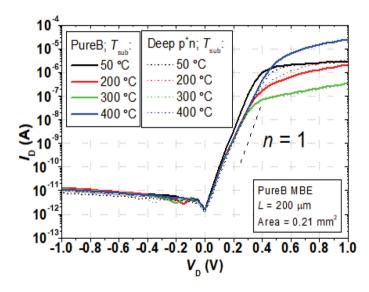

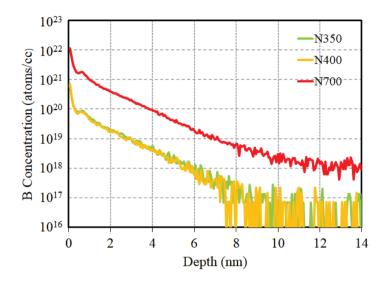

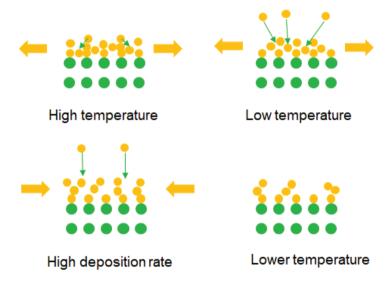

This section gives a review, based on the reference [43] that was published as part of the present thesis research, of the properties of boron layers that are known from earlier work on PureB diode fabrication. So far, the 400°C and 700°C depositions in the Epsilon reactor have been the most interesting layers for electrical applications. They both form diodes with similar p<sup>+</sup>n-junction-like characteristics but the 700°C layers are chemically more robust while the 400°C layers have the advantage of being suitable for integration in post-metal back-end-CMOS process modules [18]. In Fig. 2.5 [43] the main structural and electrical differences between the layers are illustrated. Both layers were deposited in the ASM Epsilon CVD reactor. Five regions have been identified:

- (1) A uniform, compact layer of amorphous boron is seen to be deposited directly on the Si surface.

- (2) The surface of the compact B layer is covered with a rough increasingly incomplete layer of non-compact B. This layer is quite thick for 400°C layers but barely noticeable for 700°C layers. At this temperature uniform layers with low surface roughness are formed as a result of the high diffusion length of the boron atoms along both Si and SiO<sub>2</sub> surfaces [85, 96]. As the deposition temperature is lowered the mobility along the surface diminishes and the layers become rougher.

- (3) For the 700°C layer the Si surface is roughened, and some mixing of the B and Si is visible in a region less than 1 nm wide at the interface. The 400°C deposition leaves the Si surface flat.

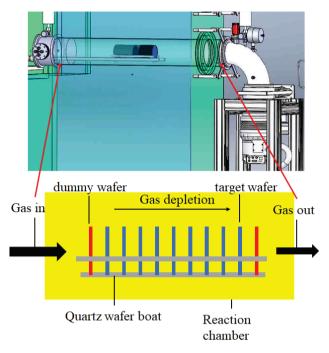

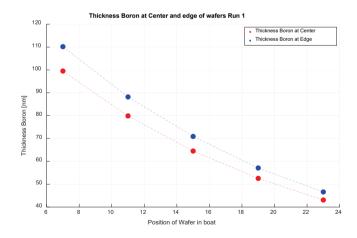

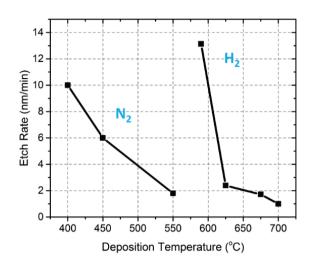

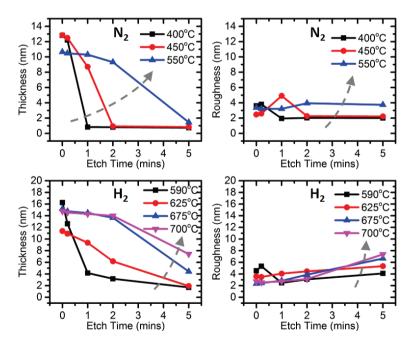

- (4) At 700°C the boron can diffuse a few nm into the bulk Si, doping it to the solid solubility of  $2 \times 10^{19}$  cm<sup>3</sup>. At 400°C no bulk doping is expected.