Victor Blatt was born in Cordoba, Argentina, on December 29, 1943. He received the maximum degree of Ingeniero Electricista Electronico from the University of Cordoba, Cordoba, Argentina, in 1970.

While at the University of Cordoba, he was engaged in research on system automation. From 1970 to 1971 he was employed at Lennox, Cordoba, as a Development Engineer in industrial electronics and system automation. He was with Philips, Eindhoven, The Netherlands,

from 1971 to 1973 where he designed integrated circuits in  $I^2L$ . In 1973 he joined the Allen Clark Research Centre, The Plessey Company Ltd., Caswell, Towcester, Northants., England, working on research and development in the field of monolithic integrated circuits. At present he is Head of a Digital Design Group there.

Geoffrey W. Sumerling, for a photograph and biography, see this issue, p. 127.

# Polycrystalline Silicon as a Diffusion Source and Interconnect Layer in I<sup>2</sup>L Realizations

JAN MIDDELHOEK AND ARIE KOOY

Abstract—Boron-doped polycrystalline silicon is applied as a diffusion source for the p-type regions of I<sup>2</sup>L devices. The polysilicon also serves as a conductive level which requires no contact windows in the p-type regions. Compared to conventional processing a higher fan-out, size reduction, and a greater layout flexibility are reported.

# I. THE STRUCTURE OF THE I<sup>2</sup>L DEVICE WITH POLYSILICON

polycrystalline silicon layer doped during the deposition with boron, can be applied as a diffusion source while it serves, at the same time, as a conductive layer to the diffusion area. IC processes which are based on this combined use of polycrystalline silicon result in a considerable size reduction of the p-type region [1]. This is mainly due to the fact that the interconnections of the diffusion areas require no contact windows. The performance of the devices also benefits from this size reduction. The design of the layout of an IC is greatly facilitated by the extra conduction level.

The principle of self-alignment is applicable in the fabrication because oxide regions adjacent to the polysilicon are formed simultaneously with the indiffusion from the polysilicon after the polysilicon layer has been etched. A technique, known as IDOPOS [2], has in principle the same possibilities as the technique reported in this paper.

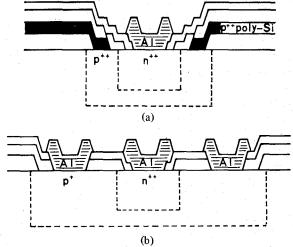

Fig. 1 compares the cross sections of the base regions of two n-p-n bipolar transistors. One is a conventional type, the other is made with polysilicon. The area of the base region and the

Manuscript received November 1, 1976; revised November 30, 1976. The authors are with the Solid State Electronics Group, Twente University of Technology, Enschede, The Netherlands.

Fig. 1. Cross sections of the base region of a bipolar transistor. (a) Polysilicon technique (poly-Si base). (b) Conventional processing (standard base).

base-collector capacitance of the polysilicon type are smaller. The base surface remains partly covered with highly boron-doped polysilicon, resulting in a boron concentration under the polysilicon which is higher than directly around the emitter. The polysilicon on the surface forms more or less an aequipotential ring around the emitter. The polysilicon track connecting the base may be led in any direction independent of the aluminum track from the emitter.

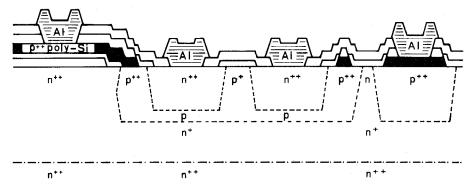

Fig. 2 shows a cross section of an I<sup>2</sup>L device. The use of polycrystalline silicon helps to increase the number of collectors, which may be accommodated in the base regions in two

Fig. 2. Cross section of an I<sup>2</sup>L device in the polysilicon technique.

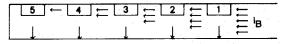

Fig. 3. Top view of an I<sup>2</sup>L gate with five collectors and an external base contact.

ways. First the area which is normally needed for a base contact window is now available for a collector and secondly the polysilicon which remains on the surface of the base region reduces the series resistance in the lateral direction. The performance of the p-n-p transistor may benefit from the polysilicon because the concentration in the p-region is higher than that in the conventional processing.

Fig. 3 shows a photograph of a device with five collectors. The contact windows are  $10 \times 10 \ \mu m^2$ . Further size reduction would appear possible.

# II. THE DEVICE TECHNOLOGY

The deposition of polycrystalline silicon on monocrystalline silicon differs from the deposition on silicondioxide as applied in the silicon gate MOST technique. It is extremely difficult to completely avoid whisker growth on the monocrystalline surface. Reduction of the deposition temperature to 625°C [1] proved to be a good solution in the case of boron-doped polysilicon. In the case of phosphorus-doped polysilicon the deposition rate becomes very low at 625°C [2].

The etching of the polycrystalline silicon just as far as the monocrystalline substrate can be carried out reproducibly by calibration of the etching rate.

# III. PROCESS DESCRIPTION

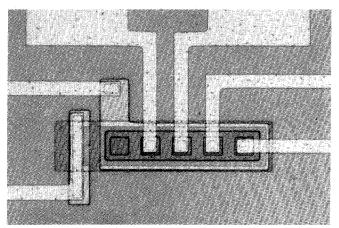

Fig. 4 illustrates the process description.

Starting material: an n-type epitaxial layer of 0.6  $\Omega$  · cm and 6- $\mu$ m thickness on an n<sup>++</sup> substrate of (100) orientation.

Fig. 4. Illustration of the polysilicon I<sup>2</sup>L process.

- 1) Phosphorus doped silane-oxide deposition;  $PH_3/SiH_4 = 0.064$ ;  $T_{deposition} = 325$ °C;  $t_{ox} = 2000$  Å (doped) + 1000 Å (pure)

- 2) Mask 1 for the isolated area; negative resist; [HF (49 percent), sat.  $NH_4F$ ]:  $H_2O = 1:20$ .

- 3) Deposition of pure silane-oxide;  $T_{\text{deposition}} = 325^{\circ}\text{C}$ ;  $t_{ox} = 1500 \text{ Å}$ .

- 4) Deep n<sup>++</sup> type diffusion in N<sub>2</sub> ambient.  $T_{\text{dif}} = 1150^{\circ}\text{C}$ ;  $t_{\text{dif}} = 30 \text{ min}$ .

- 5) Mask 2 for the active area; negative resist; HF (buf.):  $H_2O = 1:6$ .

- 6) Doped polysilicon deposition:  $B_2H_6/SiH_4 = 4 \cdot 10^{-4}$ .  $T_{\text{deposition}} = 625^{\circ}\text{C}$ ;  $t_{\text{poly}} = 3500 \text{ Å}$ .

- 7) Deposition of pure silane-oxide.  $T_{\text{dep}} = 325^{\circ}\text{C}$ ;  $t_{ox} = 4000 \text{ Å}$ .

- 8) Mask 3 for the outer edges of the polysilicon layer. Positive resist; HF (buf.): $H_2O = 1:20$ ; poly-Si etchant [300 ml HNO<sub>3</sub> (65 percent), 10 ml HF (49 percent), 100 ml CH<sub>3</sub> COOH, 150 ml  $H_2O$ ];  $t_{\text{etching poly}} = 2$  min.

- 9) Indiffusion in oxygen ambient.  $T_{\rm dif} = 1150^{\circ} \rm C$ ;  $t_{\rm dif} = 15 \, \rm min$ ;  $t_{ox p-n-p \ base \ region} = 700 \, \rm \AA$ ;  $x_{j \ mono} = 1.0 \, \mu m$ ;  $R_{s \ mono} = 219 \, \Omega$ .

- 10) Mask 4 for the inner edges of the polysilicon layer. Negative resist; HF (buf.):  $H_2O = 1:6$ ; poly-Si etchant [see 8)];  $t_{\text{etching}} = 2 \text{ min.}$

- 11) Drive-in diffusion in oxygen ambient.  $T_{\rm dif} = 1150^{\circ} \rm C$ ;  $t_{\rm dif} = 75$  min.  $t_{\rm ox}$  collector region = 2000 Å;  $x_{\rm j~mono} = 3.4~\mu \rm m$ ;  $R_{\rm s~mono} = 200~\Omega$ .

- 12) Mask 5 for the collector areas. Negative resist; HF (buf.):  $H_2O = 1:6$ .

- 13) Deposition of phosphorus doped silane-oxide.  $PH_3/SiH_4 = 5.1 \ 10^{-2}$ ;  $T_{dep} = 325^{\circ}C$ ;  $t_{ox} = 2000 \ Å (doped) + 1000 \ Å (pure).$

- 14) Indiffusion in N<sub>2</sub> ambient.  $T_{\text{dif}} = 1100^{\circ}\text{C}$ ;  $t_{\text{dif}} = 120$  min;  $x_i = 2.7 \,\mu\text{m}$ ;  $R_s = 5.9 \,\Omega$ .

- 15) Mask 6 for contact windows. Negative resist; HF (buf.):  $H_2 O = 1:6$ .

- 16) Al evaporation (E-gun).  $t_{Al} = 1.3 \mu m$ .

- 17) Mask 7 for metal delineation. Positive resist; [75 ml H<sub>3</sub>PO<sub>4</sub>, 15 ml CH<sub>3</sub>COOH, 5 ml HNO<sub>3</sub> (65 percent), 15 ml H<sub>2</sub>O].

- 18) Anneal in wet N<sub>2</sub>.  $T = 450^{\circ}$ C; t = 60 min. Sheet resistances.  $R_{s \text{ poly on SiO}_2} = 115 \Omega$ ;  $R_{s \text{ poly on Si}} = 51 \Omega$ .

### IV. RESULTS AND DISCUSSION

The current amplification factors have been determined with the structure, as shown in Fig. 3. The results should not be considered as the optimum, which can be reached with this poly-Si technique, but as proof of the feasibility of the process.

First the collector currents into each of the four connected collectors were measured at a constant base current of  $100 \,\mu\text{A}$  and with the injector grounded.

| Collector        | $I_C(\mu A)$                                                           | Ratio                   | log ratio × 60 mV/n                                      |

|------------------|------------------------------------------------------------------------|-------------------------|----------------------------------------------------------|

| 2<br>3<br>4<br>5 | $\left\{ egin{array}{c} 726 \\ 661 \\ 620 \\ 598 \end{array} \right\}$ | 1.098<br>1.066<br>1.037 | 2.44/3 = 0.81 mV<br>1.66/2 = 0.83 mV<br>0.94/1 = 0.94 mV |

In the first place these measurements show that the upward current gain per collector is about 7. The collector current decreases when the collector is at a greater distance from the base contact. If it is assumed that the base current is equally divided over the base region, then the voltage drop from collector to collector in the base region can be estimated. The collector current may be expressed as

$$I_C = \beta_{up} I_{BO} \exp((qV - nI_B R_{cc})/kT)$$

.

n depends on the position of the collector and can be found with the help of Fig. 5.

The resistance from collector to collector  $R_{cc}$  can be estimated as 0.86 mV divided by the fifth part of the total base current. This gives  $R_{cc} = 43~\Omega$ . The same measurement on a conventionally made device gives  $R_{cc} = 220~\Omega$ . This result is a clear indication that the polysilicon process reduces the lateral series resistance in the base region.

Even for a high base current of  $100 \,\mu\text{A}$  the collector current ratio of the first to the fifth collector is only 1.40. The conventional process gives a factor 4.

The inverse current gain of the p-n-p transistor  $\beta_{I, p-n-p}$  of the perpendicular gate (see Figs. 3 and 6) is 0.76. The inverse current gain of the p-n-p transistor of the parallel gate (see Fig. 6) is 2.05. The downward  $\beta_d$  of the n-p-n transistor was determined to be 280. A more profound study of the current amplification and of the contributions to base current has not yet been made. It requires a large variety of test structures [3].

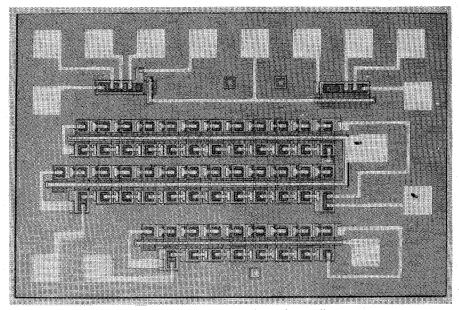

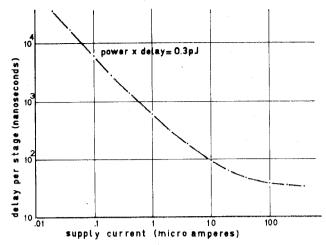

Fig. 6 shows a photograph of two ring oscillators. The largest oscillator has 49 stages, the other 17. From the oscillating period T as a function of the supply current  $I_{\text{supply}}$ , the plot of Fig. 7 is determined. The delay time per stage was calculated according to the expression  $T/2 \times n$ . The power-delay pro-

Fig. 5. Schematic representation of the base current distribution.

Fig. 6. Photograph of the test chip, which contains two gates and two ring oscillators. The number of stages are 17 and 49, respectively.

Fig. 7. Average propagation delay per gate versus the supply current per single collector gate.

duct per stage is  $I_{\text{supply}} \times n^{-1} \times V_{\text{supply}} \times T \times (2n)^{-1}$ , where n is the number of inverters, 49 or 17.

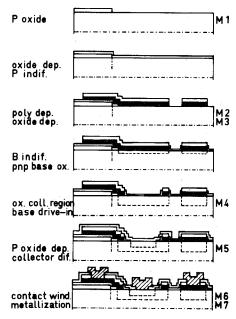

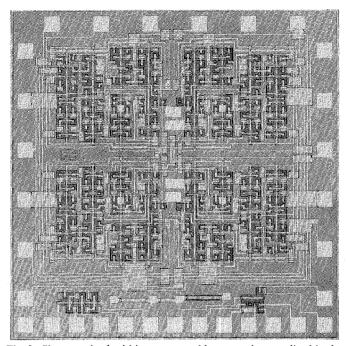

At last we show in Fig. 8 a photomicrograph of a 4-bit programmable accumulator [5], successfully realized in the new technology. It contains 172 gates on a chip area of 4 mm<sup>2</sup>.

### ACKNOWLEDGMENT

The authors wish to thank O. W. Memelink for helpful discussions and R. Wassenaar for his assistance in circuit design and testing.

#### REFERENCES

- [1] J. Middelhoek and A. Kooy, "A polysilicon source and drain MOS transistor (P.S.D. MOST)," *IEEE Trans. Electron Devices*, vol. ED-23, pp. 523-525, May 1976.

- [2] Y. Akasaka, K. Tsukamoto, M. Kawaguchi, H. Sato, K. Horie, and H. Komiya, "Application of a diffusion from implanted polysilicon to bipolar transistors," in *Proc. 7th Conf. Solid State Devices*, Tokyo, Sept. 1975.

- [3] F. C. Eversteyn and B. H. Put, "Influence of AsH<sub>3</sub>, PH<sub>3</sub> and B<sub>2</sub>H<sub>6</sub> on the growth rate and resistivity of polycrystalline silicon films deposited from a SiH<sub>4</sub>-H<sub>2</sub> mixture," *J. Electrochem. Soc.*, vol. 120, pp. 106-110, Jan. 1973.

- [4] H. E. J. Wulms, "Base current of I<sup>2</sup>L transistors," *IEEE J. Solid-State Circuits*, this issue, pp. 143-150.

- [5] R. M. M. Oberman, "Programmed accumulator," De Ingenieur, vol. 83, pp. ET 155-166, Nov. 1971.

Fig. 8. Photograph of a 4-bit programmable accumulator realized in the polysilicon I<sup>2</sup>L technique. The chip of 4 mm<sup>2</sup> contains 172 gates and two test devices.

Jan Middelhoek was born in Rotterdam, The Netherlands, in 1935. He received the Drs. degree from the Free University, Amsterdam, The Netherlands, in 1961 and the D.Sc. degree from the State University, Leiden, The Netherlands, in 1967.

He joined the staff of the Physical Chemistry Laboratory of the State University of Leiden in 1961, where he worked on the dielectric behavior of liquids. In 1967 he became a member of the staff of the Solid State Electronics

Group at the Twente University of Technology, Enschede, The Netherlands, where he has been in charge of the IC processing laboratory and where he also teaches IC technology.

Arie Kooy was born in Leerdam, The Netherlands, in 1938. He joined the staff of the Solid State Electronics Group at the Twente University of Technology, Enschede, The Netherlands, in 1966 where he is responsible for the fabrication of the integrated circuits and the laboratory tuition of students.