## INVITATION

to attend the public defense of my PhD thesis

AGEING AND

EMBEDDED

INSTRUMENT

MONITORING OF

ANALOGUE/

MIXED-SIGNAL IPS

Jinbo Wan

on Friday 1st November 2019 at 10:45 in Waaier,

4 - Prof.dr. G. Berkhoff-zaal, University of Twente

Afterwards there will be a reception to which you are also cordially invited.

#### **PARANYMPHS**

Mark Theodoridis Digeorgia Natalie Da Silva

# AGEING AND EMBEDDED INSTRUMENT MONITORING OF ANALOGUE/MIXED-SIGNAL IPS

Jinbo Wan

# AGEING AND EMBEDDED INSTRUMENT MONITORING OF ANALOGUE/MIXED-SIGNAL IPS

#### DISSERTATION

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof.dr. T.T.M. Palstra,

on account of the decision of the Doctorate Board,

to be publicly defended

on the 1<sup>st</sup> of November 2019 at 10:45am

by

### Jinbo Wan

born on the 2<sup>nd</sup> of February 1979 in Linyi, China This dissertation has been approved by:

Supervisor:

dr.ir. H.G. Kerkhoff

Cover design: Ilse Modder Photo by: Adi Goldstein Printed by: Gildeprint BV Lay-out: Jinbo Wan

ISBN: 978-90-365-4829-8

DOI: 10.3990/1.9789036548298

© 2019 Jinbo Wan, The Netherlands. All rights reserved. No parts of this thesis may be reproduced, stored in a retrieval system or transmitted in any form or by any means without permission of the author. Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd, in enige vorm of op enige wijze, zonder voorafgaande schriftelijke toestemming van de auteur.

#### **GRADUATION COMMITTEE:**

Chairman/secretary prof.dr.ir. J.N. Kok

Supervisor dr.ir. H.G. Kerkhoff

Members prof.dr.ir. G.J.M. Smit

prof.dr.ir. A. Pras

prof.dr. J. Figueras Pamies prof.dr.ir. S. Hamdioui prof.dr. J.L. Hurink dr. J. Bisschop

#### Acknowledgements

My sincere thanks go to my wife, Jifeng Tang, for her countless efforts and time spent on taking care of family during my thesis writing. Without her help, I could not have made it. Also appreciation for my parents for their understanding when i was busy with my thesis and could not go back to visit them.

I would like to show my gratitude particularly to my supervisor Hans Kerkhoff for his mentorship and support throughout my PhD work. Furthermore for his great patience and tremendous amount of time spent on reviewing my thesis. Also thanks to Prof. Gerard Smit for his reviewing of my thesis. I also would like to thank my colleagues at the University of Twente: Andreina Zambrano, Yong Zhao, Aamir Khan, Ahmed Ibrahim, Hassan Ebrahimi, Ghazanfar Ali, Bert Helthuis, Marlous Weghorst, and so on. I keep great memories to know them and work with them at the University of Twente.

Great acknowledgements to Jaap Bisschop for providing me with the opportunity to cooperate with NXP Semiconductors during my PhD project. A lot of thanks to my colleagues from NXP Semiconductors for their understanding during my thesis writing: Johan Knol, Wim Nijland, Mari Vogels, Mark Theodoridis, Louis Zheng, Jeroen Jalink, Lei Peters Wu, Claud van Oers, Mary Ann C. Bautista, Peter Vullings etc.

Thank you everyone!

#### **Abstract**

(Dutch)

Door de toename van het aantal SoCs in veiligheidskritische applicaties zoals in zelfrijdende autos, is onderzoek naar de betrouwbaarheid van elektronische circuits een belangrijk onderzoeksonderwerp geworden. De meeste inspanning is tot op heden vooral gericht geweest op puur digitale blokken. Het meest kritische deel, namelijk het analoge voorste stuk (AFE) is echter tot op heden nauwelijks onderzocht. Om deze reden ligt de nadruk van dit promotie onderzoek op betrouwbare analoog/mixed-signal (AMS) AFEs in veiligheidskritische applicaties zoals in autos.

Dit promotieonderzoek geeft een overzicht van de betrouwbaarheid van CMOS AMS circuits. De nadruk ligt op betrouwbaarheidsverschijnselen op nanometer schaal CMOS transistoren (kleiner dan 65nm). Meer specifiek op de overheersende NBTI betrouwbaarheidseffecten: fysische mechanismen, modellen en simulaties worden in detail behandeld.

NBTI modellering, metingen en validatie worden in detail bediscussieerd. Twee originele bijdragen worden er in beschreven. Een bijdrage betreft een compact NBTI model. Dit model wordt gebruikt voor de simulatie van NBTI degradatie van analoog/mixed-signal schakelingen. Dit nieuwe compacte NBTI model is gebaseerd op het iteratief oplossen van reactie-diffusie vergelijkingen. Dit model kan overweg met willekeurige signalen en is hierdoor geschikt voor analoog/mixed-signal simulaties. Het model is geëvalueerd voor een (NXP) 140nm CMOS technologie. Hierbij is gebruik gemaakt van zowel een blok golf als willekeurige signaal belasting. Het model is geïmplementeerd in de Cadence ADE omgeving met behulp van Verilog-A. Het is geschikt voor het simuleren van zowel deterministische als ook stochastische NBTI verouderingseffecten. De simulatie snelheid is ongeveer duizendmaal sneller dan voor andere reactie-diffusie gebaseerde modellen en is op ongeveer hetzelfde snelheidsniveau als transient simulaties.

Een andere originele bijdrage is het MOS drain-stroom model. Dit model is gebruikt om een eenvoudig te ontwerpen low cost on-chip drempel-spanning ( $V_{th0}$ ) meetinstrument te maken en grote hoeveelheden NBTI degradatie data te verzamelen. Het nieuwe gesloten vorm drain-stroom model maakt het mogelijk MOS  $V_{th0}$  metingen uit te voeren in nanometer CMOS technologie. Een embedded meetinstrument met een lage overhead geschikt voor het meten van veroudering geïnduceerde  $V_{th0}$  verschuiving wordt voorgesteld. Langdurige stress tests laten zien dat de on-chip  $V_{th0}$  meting een  $V_{th0}$  verschuiving kan karakteriseren met een nauwkeurigheid van 3mV.

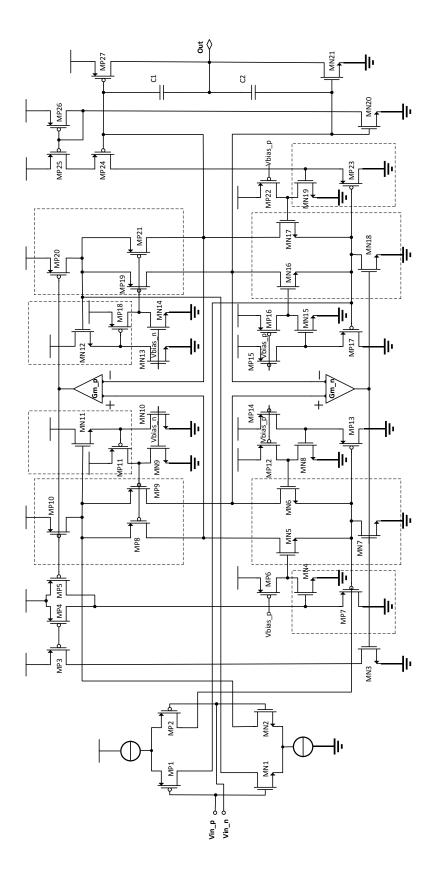

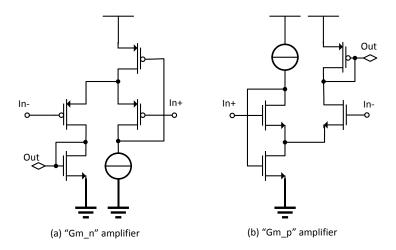

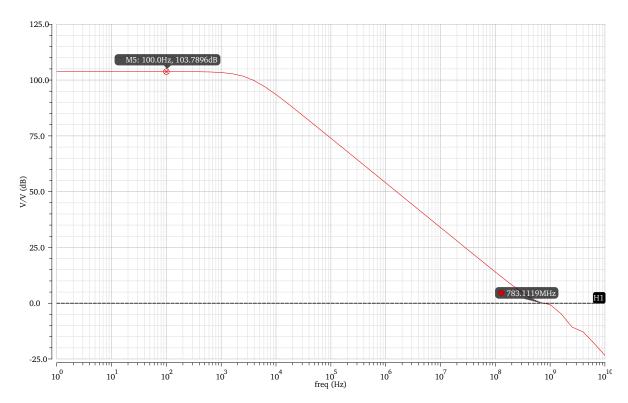

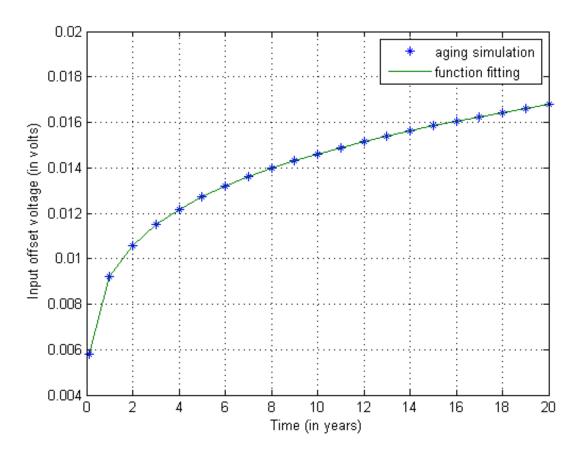

Na het opzetten van een reliability model en simulatie methode worden verschillende IP-blokken gesimuleerd en bediscussieerd voor het betrouwbaar maken van analoge circuits. Het eerste test vehicle is een in een 65nm MOS technologie ontworpen analoge versterker (OpAmp). Deze OpAmp bevat een nieuwe gain-boost methode waarmee de OpAmp een versterking haalt van 104dB en een unity gain bandwith van 783MHz. NBTI simulaties tonen aan dat de versterker offset de meest verouderingsgevoelige parameter is. Embedded instrumentatie gebaseerd op een nieuwe meet theorie is ontwikkeld voor de versterker offset en gain. Het instrument beschikt over een digitale interne kalibratie functie voor interne offset. Het is ontworpen in een 65nm LP digitaal CMOS proces en beschikt over een IEEE 1687 interface. Voor het besparen van kosten is het mogelijk het instrument te gebruiken voor meerdere analoge OpAMPs. Als het instrument niet wordt gebruikt kan het worden uitgeschakeld voor het beperken van het stroomverbruik.

Na OpAmps behandeld dit promotieonderzoek het gebruik van embedded instrumentatie in actieve filters voor AFEs voor autos. Experimenten laten zien dat de in actieve filters gebruikte feed back in veel gevallen voldoende bescherming bied tegen betrouwbaarheidsproblemen van AFEs onder zware auto missie profielen. In sommige gevallen is het echter mogelijk dat de filter karakteristiek dusdanig veranderd dat dit leid tot een foutieve sensor uitlezing. Dit kan aanleiding geven tot mogelijke veiligheidsproblemen van het betreffende voertuig. Een voorbeeld hiervan is het beschreven voorbeeld van een OTA-C laagdoorlaat filter. Het gedurende de levensduur observeren van filters met behulp van embedded instrumenten maakt het mogelijk om te waarschuwen met een dashboard melding of direct corrigerende maatregelen te nemen.

Afsluitend is een 10-bits volledig differentieel SAR ADC ontworpen in 65nm CMOS technologie. Hiervan zijn aansluitend de NBTI betrouwbaarheidseffecten gesimuleerd. Deze simulaties tonen aan dat NBTI gerelateerde veroudering aanleiding kan geven tot vertragingen

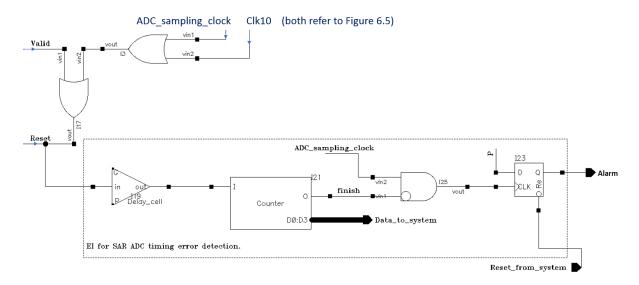

in de asynchrone SAR logica met mogelijke timing fouten als gevolg. De laatste bits van de ADC zijn hierdoor zinloos. NBTI degradatie van de SAR ADC comparator kan leiden tot een extra offset met als mogelijk gevolg offset fouten in de ADC. Twee embedded instrumenten worden voorgesteld om zowel timing als offset problemen in de SAR ADC te detecteren. Dit maakt de beschikbaarheid van betrouwbare ADCs mogelijk.

Het verouderingsgedrag van alle essentiële IP blokken binnen een AFE zijn voor dit promotie onderzoek onderzocht. Aansluitend worden nieuwe methoden beschreven gebaseerd op embedded instrumentatie voor het betrouwbaar maken van deze systemen. Enkele algemene conclusies worden getrokken op basis van de hierboven beschreven informatie. Beperkingen van het huidige en toekomstig onderzoek worden ook aangestipt. Afsluitend is een lijst bijgesloten van alle door de auteur geschreven publicaties.

#### **Abstract**

(English)

With an increasing number of SoCs being used in safety-critical applications like automotive, highly dependable circuits become an important research topic. However, most of the effort until now was spend on pure digital blocks. The most critical part, the analogue-front-ends are hardly being dealt with. Therefore the focus of this thesis is on dependable Analogue/mixed-signal Front-Ends in safety-critical applications like automotive.

In this thesis, an overview of the dependability of CMOS AMS circuits is provided. Emphasis is put on the reliability phenomena of nano-meter CMOS transistors (65nm and below), especially on the dominating NBTI reliability effects. Since this thesis is dominated by NBTI simulations, NBTI physical mechanisms, modelling and simulations are treated in detail. The target AFE in the thesis is also introduced. Two main directions to improve dependability are discussed.

Subsequently, NBTI modelling, measurements, validation and simulation are discussed in detail. Two original works are described, dealing with models. One original contribution is a NBTI compact model, which is later on used to simulate NBTI degradation of analogue/mixed-signal circuits. This new compact NBTI model is based on iteratively solving the Reaction-Diffusion equations. This model can accurately handle arbitrary stressed waveforms for the up-limit envelope and is thus very suitable for analogue/mixed-signal simulations. It is subsequently evaluated for a (NXP) CMOS 140nm technology with square-wave stresses and arbitrary wave stresses. The model is implemented in the Cadence ADE environment with Verilog-A, and can simulate both deterministic as well as stochastic NBTI ageing effects. The simulation speed is about thousand times faster than for other Reaction-Diffusion-based models, and is at the same speed level as transient simulations.

Another original result is the MOS drain-current model which is used to build an on-chip  $V_{th0}$  measurement Embedded Instrument and gather a large amount of NBTI degradation data

which is more convenient to design as well as featuring low costs. The new closed-form model for the MOS drain current is provided to facilitate MOS threshold-voltage measurements in nanometer CMOS technologies. A low overhead on-chip Embedded Instrument for ageing-induced threshold-voltage shift measurement is proposed. Long-time stress tests show that the on-chip  $V_{th0}$  test can characterize a threshold-voltage shift with 3mV accuracy.

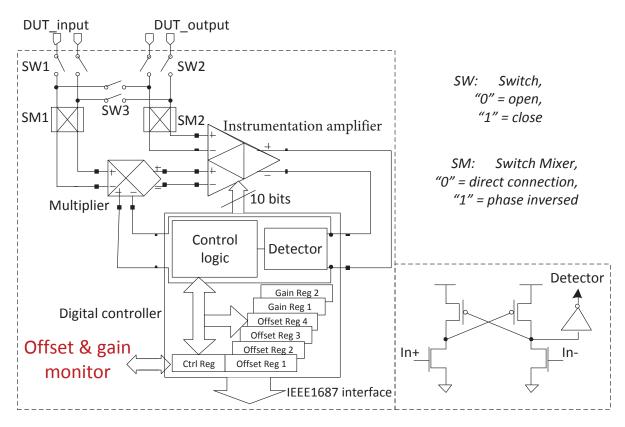

After setting up the reliability model and simulation method, different analogue IP blocks are simulated and discussed to make the analogue IPs dependable. The first vehicle is an analogue OpAmp. A test bench OpAmp is designed in 65nm CMOS technology. It incorporates a new gain-boosting method. Based on the method, the test bench OpAmp reaches 104dB with 783MHz as the unity-gain bandwidth. The NBTI effect is simulated next; based on the simulation results, we observed that the most ageing-sensitive parameter in the OpAmp is the offset. An offset and gain Embedded Instrument for OpAmp IPs is subsequently designed based on a new measurement theory. This Embedded Instrument can self-calibrate its resident offsets in the digital domain after each measurement. The monitor is designed in 65nm LP digital CMOS process and provides an IEEE 1687 interface. It can be shared with other analogue OpAmp IPs to reduce the cost and shut down in the case of an idle situation to save power.

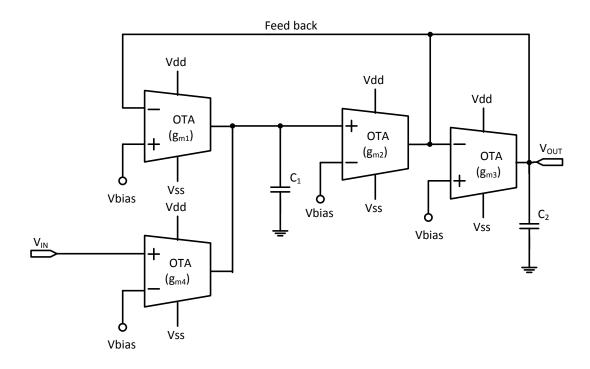

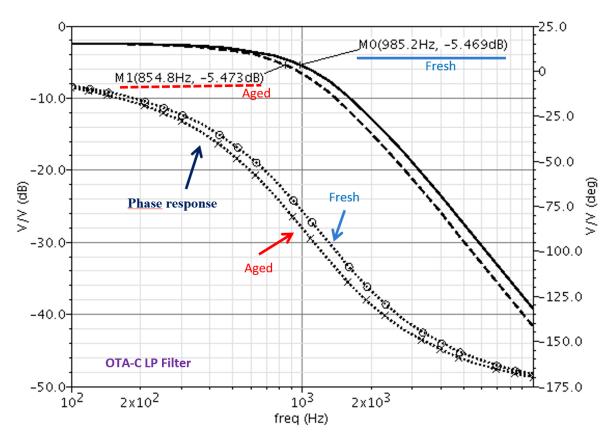

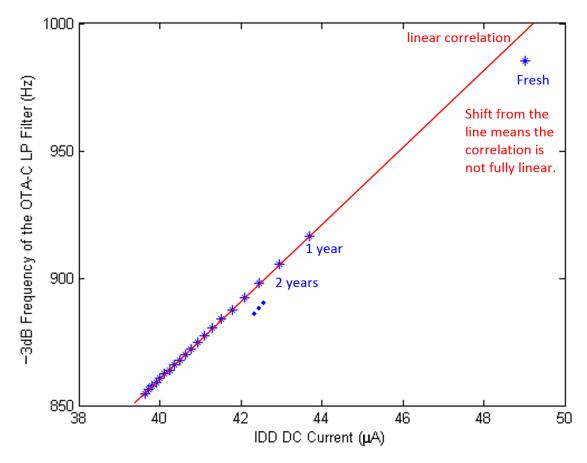

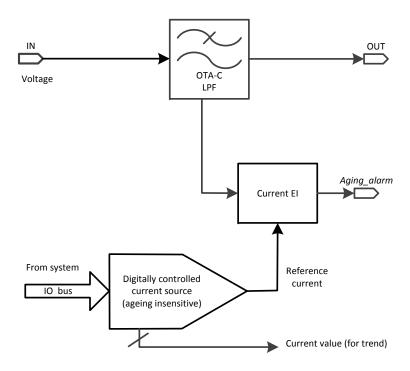

After OpAmps, the thesis continues dealing with dependable active filters in automotive analogue front-ends in SoCs by using an embedded instrument. It is shown by experiments that the feed-back in many active filters provides sufficient protection against reliability issues in analogue front-ends even under harsh automotive mission profiles. However in some cases, like the second-order OTA-C low-pass filter example, the filter characteristics may change to the extend that they give erroneous sensor readings. This can potentially endanger the car safety. By monitoring the filter during lifetime using an Embedded Instrument, either car-console flagging or direct corrective counter actions can be taken.

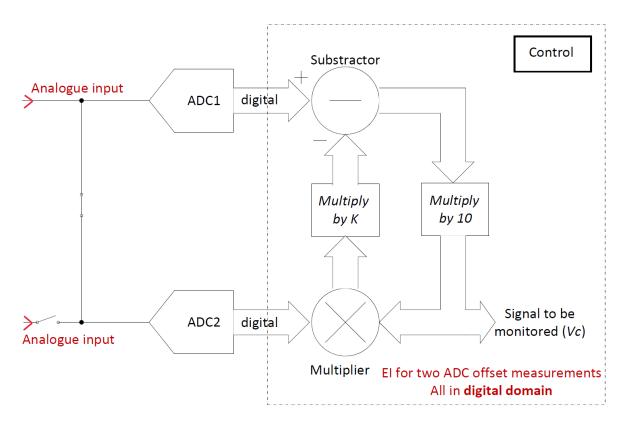

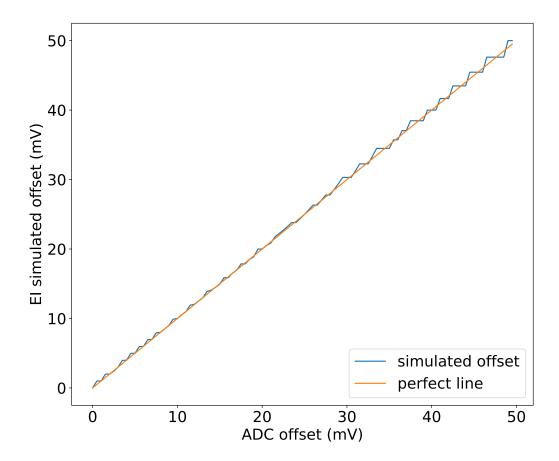

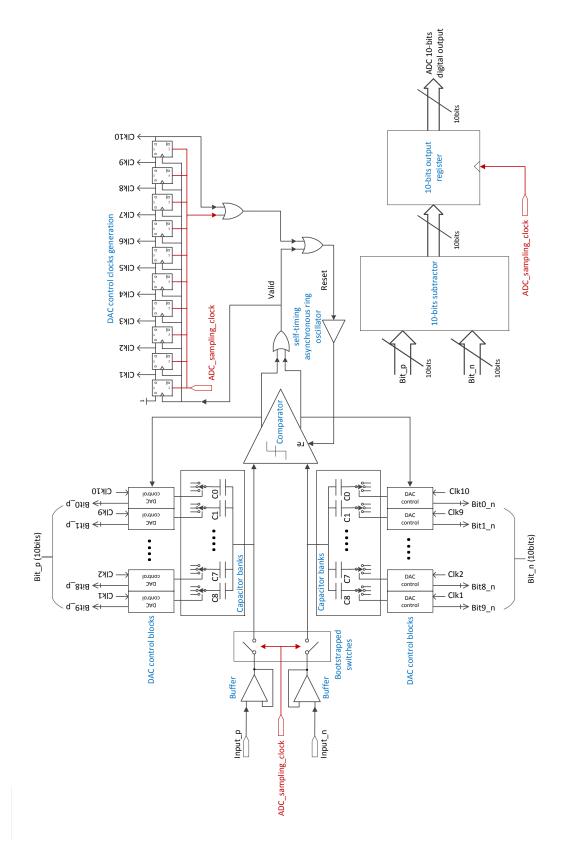

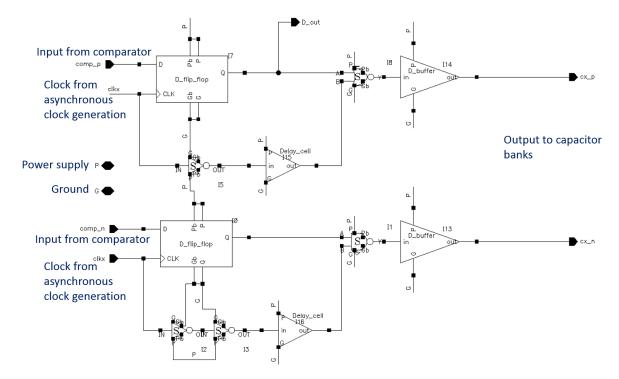

Finally, a 10-bits fully differential SAR ADC is designed in 65nm CMOS technology. Next, the NBTI reliability effects are simulated. The NBTI simulations show that the NBTI can increase the delay in the asynchronous SAR logic and generate timing errors which can make the last bits of the ADC meaningless. For the comparator, NBTI degradation can induce an extra offset and cause offset errors in the ADC. Two embedded instruments are introduced to detect both timing as well as offset errors in the SAR ADC, which enable the availability of dependable ADCs.

All the essential IP blocks inside an AFE are investigated in this thesis for their ageing behaviour and subsequently new methods with Embedded Instruments are described to make them dependable. Based on the information above, some general conclusions are drawn. Limitations of the current and future research are also addressed. At the end of the thesis, all publications written by the author are listed.

## **Table of Contents**

| Li                        | ist of I | Figures       | xi                                                  | X |  |  |

|---------------------------|----------|---------------|-----------------------------------------------------|---|--|--|

| Li                        | st of T  | <b>Fables</b> | xx                                                  | V |  |  |

| List of Abbreviations xxv |          |               |                                                     |   |  |  |

| 1 Introduction            |          |               | n                                                   | 1 |  |  |

|                           | 1.1      | Introdu       | action                                              | 1 |  |  |

|                           |          | 1.1.1         | Dependable Systems                                  | 3 |  |  |

|                           |          | 1.1.2         | Mission Profiles                                    | 4 |  |  |

|                           | 1.2      | Motiva        | ation                                               | 6 |  |  |

|                           | 1.3      | Industr       | rial Platform in the TOETS and ELESIS Framework     | 7 |  |  |

|                           | 1.4      | Resear        | rch Questions                                       | 8 |  |  |

|                           | 1.5      | Outline       | e of the Thesis                                     | 8 |  |  |

|                           | Refe     | erences.      |                                                     | Э |  |  |

| 2                         | Dep      | endabil       | ity Overview of CMOS Analogue/Mixed-Signal Circuits | 3 |  |  |

|                           | 2.1      | Introdu       | action                                              | 3 |  |  |

|                           |          | 2.1.1         | Reliability                                         | 4 |  |  |

|                           |          | 2.1.2         | Maintainability                                     | 6 |  |  |

|                           |          | 2.1.3         | Availability                                        | 7 |  |  |

|                           |          | 2.1.4         | Safety                                              | 7 |  |  |

|                           | 2.2      | State-o       | of-the-Art in NBTI                                  | 8 |  |  |

|                           |          | 2.2.1         | NBTI measurement                                    | 8 |  |  |

|                           |          | 2.2.2         | Physics of NBTI                                     | 0 |  |  |

|                           |          | 2.2.3         | Reaction-Diffusion Theory                           | 2 |  |  |

|                           |          | 2.2.4         | Reaction-limited Theory                             | 3 |  |  |

|                           |          | 2.2.5         | NBTI Simulation for Analogue/Mixed-signal Circuits  | 4 |  |  |

|                           | 2.3      | Improv        | ving the AFE Dependability                          | 5 |  |  |

**xvi** Table of Contents

|   |      | 2.3.1    | The Targeted AFE                                                 | 26 |

|---|------|----------|------------------------------------------------------------------|----|

|   |      | 2.3.2    | Different Approaches to Improve Circuit/IP Dependability         | 26 |

|   | 2.4  | Conclu   | isions                                                           | 27 |

|   | Refe | erences. |                                                                  | 28 |

| 3 | NBT  | I Mode   | elling, Measurement and Simulation                               | 33 |

|   | 3.1  | Introdu  | action                                                           | 34 |

|   | 3.2  | NBTI :   | Modelling                                                        | 36 |

|   |      | 3.2.1    | A new compact NBTI model                                         | 36 |

|   | 3.3  | NBTI :   | Model Validation                                                 | 41 |

|   |      | 3.3.1    | Validation of Our NBTI Model with the Original RD Theory         | 42 |

|   |      | 3.3.2    | Fitting the Up-limit Envelope Only                               | 42 |

|   |      | 3.3.3    | Measurement Set-up                                               | 44 |

|   |      | 3.3.4    | Unavoidable Uncertainties                                        | 45 |

|   |      | 3.3.5    | Extraction of Model Parameters                                   | 47 |

|   |      | 3.3.6    | Model Results versus Silicon Measurement Results                 | 47 |

|   | 3.4  | NBTI     | Simulation in Cadence                                            | 52 |

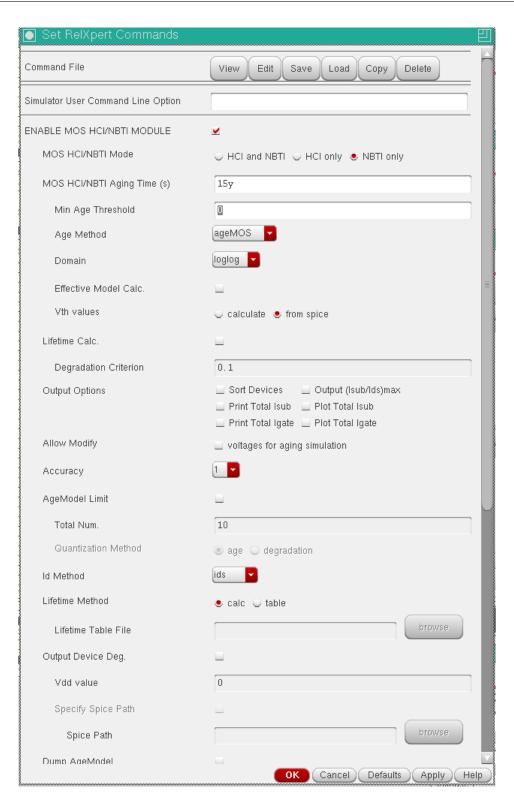

|   |      | 3.4.1    | Cadence RelXpert Simulation with Power-Model                     | 53 |

|   |      | 3.4.2    | Cadence Verilog-A Simulation with our Compact NBTI Model         | 54 |

|   | 3.5  | A New    | EI for Threshold Voltage Measurements                            | 58 |

|   |      | 3.5.1    | MOST Threshold-Voltage Extraction by Traditional Instruments     | 59 |

|   |      | 3.5.2    | A New MOST Drain-current Model                                   | 62 |

|   |      | 3.5.3    | Accuracy                                                         | 66 |

|   |      | 3.5.4    | Realization of the new EI                                        | 68 |

|   |      | 3.5.5    | EI Experimental Results                                          | 73 |

|   | 3.6  | Conclu   | nsions                                                           | 77 |

|   | Refe | erences. |                                                                  | 78 |

| 4 | Desi | gn and   | Aging Evaluation of Analogue Operational Amplifier IPs           | 81 |

|   | 4.1  | Introdu  | action                                                           | 81 |

|   | 4.2  | The Te   | est Vehicle OpAmp                                                | 83 |

|   |      | 4.2.1    | OpAmp Challenges in 65nm Low-Power CMOS Technology               | 84 |

|   |      | 4.2.2    | New Gain-boosting Technique for High Gain, High Bandwidth OpAmps | 87 |

|   |      | 4.2.3    | A 100dB Gain, 700MHz Unity-gain Bandwidth OpAmp in 65nm          |    |

|   |      |          | CMOS Technology                                                  | 91 |

|   |      | 4.2.4    | OpAmp Performance Simulation Results without Aging               | 93 |

|   | 4.3  | Reliab   | ility Issues of the Test Vehicle OpAmp                           | 93 |

Table of Contents xvii

|   |      | 4.3.1    | Reliability Simulation Conditions for Test Vehicle OpAmp     | 93  |

|---|------|----------|--------------------------------------------------------------|-----|

|   |      | 4.3.2    | OpAmp Performance Degradation with Ageing                    | 94  |

|   |      | 4.3.3    | Reliability Issues for a General OpAmp                       | 96  |

|   | 4.4  | Highly   | Dependable OpAmp via Reliability-aware Designs               | 96  |

|   | 4.5  | Highly   | Dependable OpAmp via Employing Embedded Instruments          | 98  |

|   |      | 4.5.1    | Offset Measurements and Self-Calibration Issues              | 99  |

|   |      | 4.5.2    | The New Offset EI Theory                                     | 99  |

|   |      | 4.5.3    | Self-Calibration for Resident Offsets                        | 102 |

|   |      | 4.5.4    | Gain Monitor Theory                                          | 104 |

|   |      | 4.5.5    | System Configuration and Design                              | 104 |

|   |      | 4.5.6    | Simulation Results                                           | 109 |

|   | 4.6  | Conclu   | usions                                                       | 111 |

|   | Refe | rences.  |                                                              | 111 |

| _ | ъ.:  |          | A ' E I 4' CA 4' E'H ID                                      | 115 |

| 5 |      | _        | Aging Evaluation of Active Filter IPs                        | 115 |

|   | 5.1  |          | action                                                       | 116 |

|   | 5.2  |          | ehicle Active Filters                                        | 117 |

|   | 5.3  |          | geing of Active Filters                                      |     |

|   |      | 5.3.1    | The Active RC LP Filter and its Ageing Behaviour             | 118 |

|   |      | 5.3.2    | The Switched-Capacitor LP Filter and its Ageing Behaviour    | 120 |

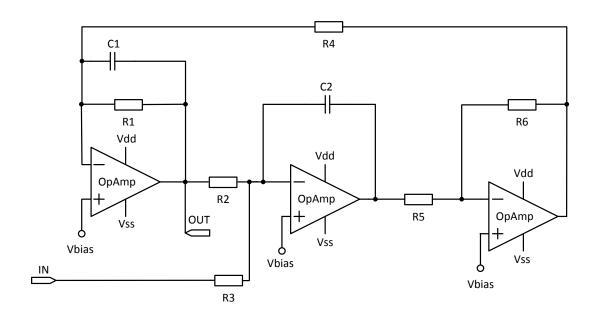

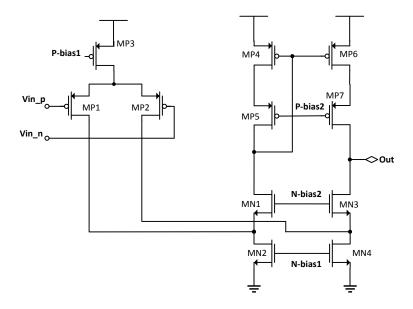

|   |      | 5.3.3    | The OTA-C LP Filter and its Ageing Behaviour                 | 121 |

|   | 5 A  | 5.3.4    | Ageing Issues for General Active Filters                     | 125 |

|   | 5.4  | 5.4.1    | Dependable Active Filters                                    |     |

|   |      | 5.4.1    | Highly Dependable Filters Based on Extra Design Effort       |     |

|   |      | 5.4.3    | Highly Dependable Filters using EI                           |     |

|   | 5.5  |          | isions                                                       | 130 |

|   |      |          |                                                              | 130 |

|   | Kere | ichees . |                                                              | 132 |

| 6 | Desi | gn and   | Aging Evaluation of Analogue-to-Digital Converter IPs        | 135 |

|   | 6.1  | Introdu  | action                                                       | 135 |

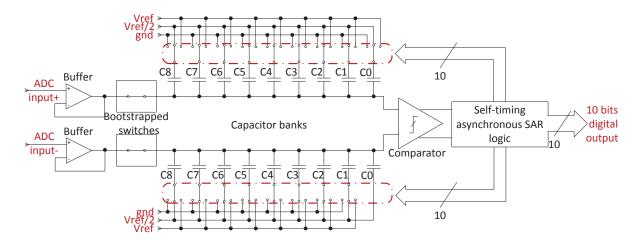

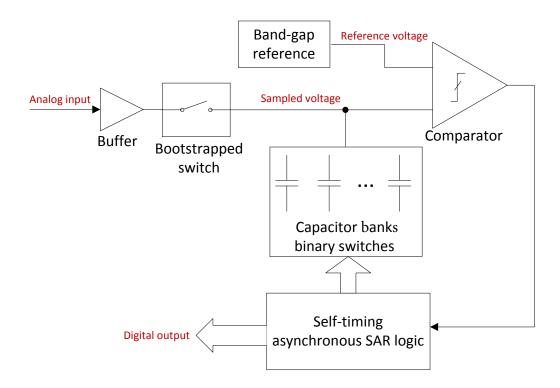

|   | 6.2  | Design   | of 10-bits 50MS/s SAR ADC in 65nm LP Digital CMOS Technology | 136 |

|   |      | 6.2.1    | The Input Buffer                                             | 138 |

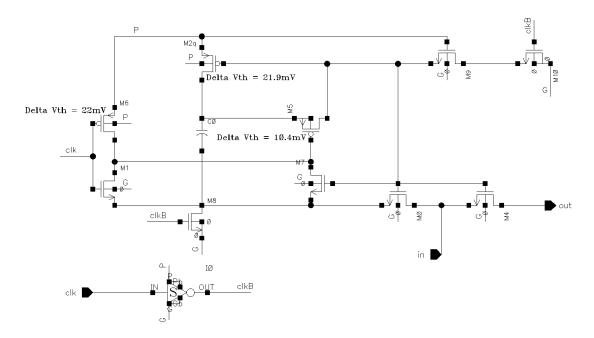

|   |      | 6.2.2    | The Bootstrapped Switch                                      | 139 |

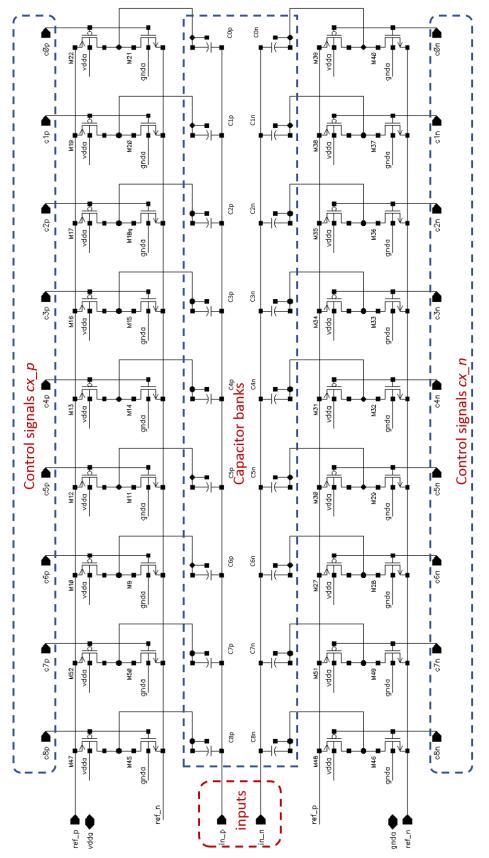

|   |      | 6.2.3    | The Capacitor Bank                                           | 139 |

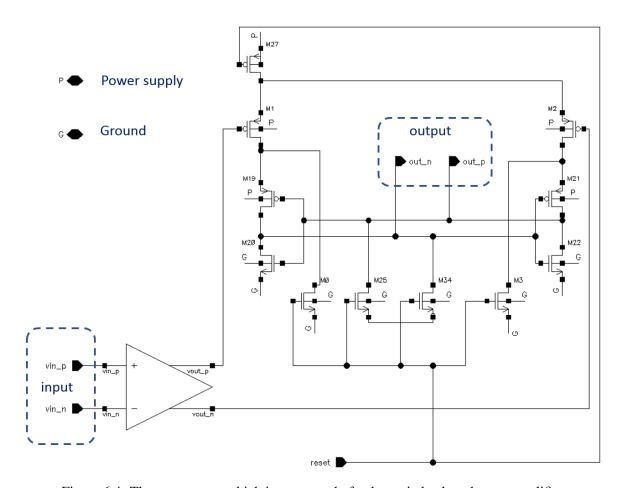

|   |      | 6.2.4    | The Dynamic-Latch Comparator                                 | 142 |

|   |      | 6.2.5    | The Asynchronous SAR Logic                                   | 143 |

xviii Table of Contents

|    |      | 6.2.6    | ADC Fresh Performance Simulation Results                          | 145 |

|----|------|----------|-------------------------------------------------------------------|-----|

|    | 6.3  | Reliabi  | ility Issues for the Aged ADC                                     | 147 |

|    |      | 6.3.1    | Reliability Simulations for the Ageing SAR ADC                    | 147 |

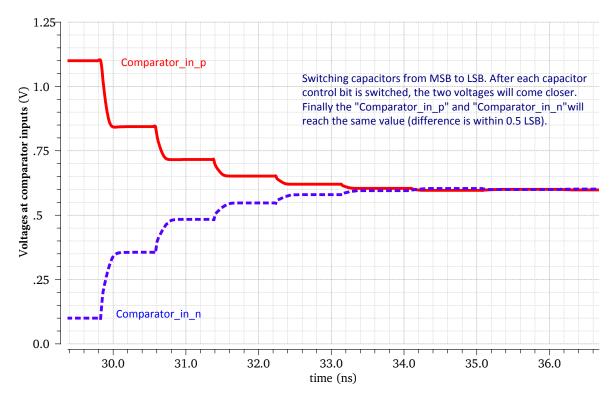

|    |      | 6.3.2    | Input Buffer Ageing                                               |     |

|    |      | 6.3.3    | The Ageing of the Bootstrapped Switches                           | 148 |

|    |      | 6.3.4    | The Ageing of the Capacitor Banks                                 | 149 |

|    |      | 6.3.5    | The Ageing of the Dynamic-Latch Comparator                        | 150 |

|    |      | 6.3.6    | The Ageing of the Asynchronous SAR Logic                          | 150 |

|    |      | 6.3.7    | The Overall SAR ADC Ageing                                        | 151 |

|    |      | 6.3.8    | Ageing Issues for SAR ADCs in General                             | 152 |

|    | 6.4  | Highly   | Dependable ADCs                                                   | 153 |

|    |      | 6.4.1    | Additional Effort During the Design Phase                         | 154 |

|    |      | 6.4.2    | The Usage of Embedded Instruments                                 | 154 |

|    |      | 6.4.3    | Comparison of the Two Approaches                                  | 158 |

|    | 6.5  | Conclu   | isions                                                            | 158 |

|    | Refe | rences.  |                                                                   | 159 |

| 7  | Con  | clusions | s, Limitations and Recommendations                                | 161 |

|    | 7.1  | Introdu  | action                                                            | 161 |

|    | 7.2  | Conclu   | sions from this Research                                          | 161 |

|    | 7.3  | Contrib  | outions                                                           | 162 |

|    |      | 7.3.1    | A Compact Arbitrary-stressed NBTI Model                           | 162 |

|    |      | 7.3.2    | A Drain Current Model for Nano-meter MOSTs                        | 163 |

|    |      | 7.3.3    | An Embedded Instrument to Measure MOST's Threshold Voltage        | 164 |

|    |      | 7.3.4    | A Gain-Boosting Method for OpAmps                                 | 164 |

|    |      | 7.3.5    | An Embedded Offset and Gain Instrument for OpAmps                 |     |

|    |      | 7.3.6    | An Embedded Instrument to Detect Ageing of OTA-C Filters          | 165 |

|    |      | 7.3.7    | Embedded Instruments to Detect Offset Errors and Timing Errors in |     |

|    |      |          | SAR ADCs                                                          | 165 |

|    | 7.4  | Limita   | tions and Recommendations for Future Research                     | 166 |

|    | List | of Our F | Publications                                                      | 168 |

| Aį | pend | ix A T   | he RelXpert Algorithm and AgeMOS model in Cadence ADE             | 169 |

| Aį | pend | ix B V   | erilog-A Programme for the New NBTI Model in Cadence ADE          | 173 |

| Aj | pend | ix C T   | he SAR ADC logic                                                  | 185 |

# **List of Figures**

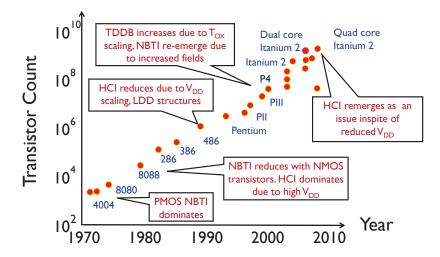

| 2.1  | History of reliability issues in CMOS technologies [Ala13b]                      | 14 |

|------|----------------------------------------------------------------------------------|----|

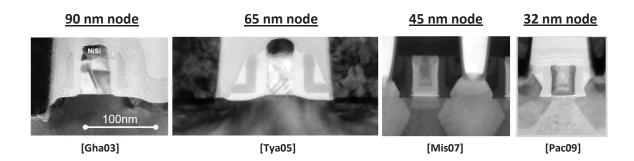

| 2.2  | CMOS technology scaling in four technology nodes illustrated by Transmission     |    |

|      | Electron Microscopy (TEM) images [Gha03, Tya05, Mis07, Pac09]. They are          |    |

|      | scaled in the same dimensions [Sun08]                                            | 16 |

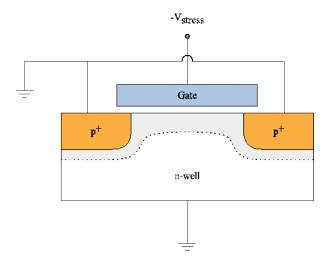

| 2.3  | The PMOST NBTI stress conditions                                                 | 18 |

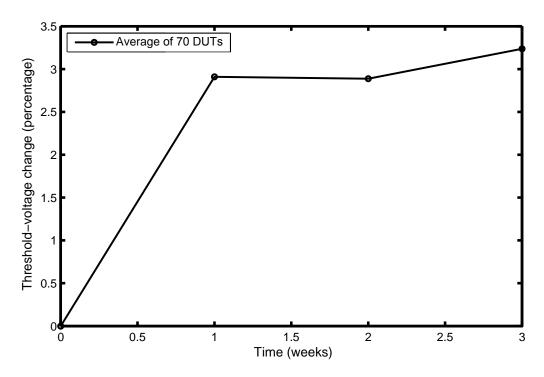

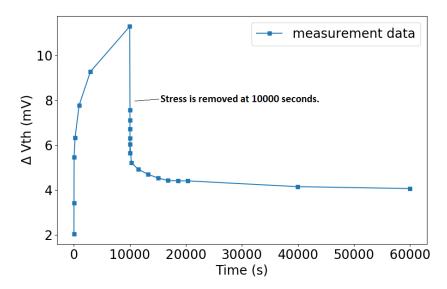

| 2.4  | The 90nm PMOS transistor threshold increases due to NBTI. Our NBTI mea-          |    |

|      | surements have been carried out at $V_{GS} = 1.15V$ and $127^{\circ}$ C          | 19 |

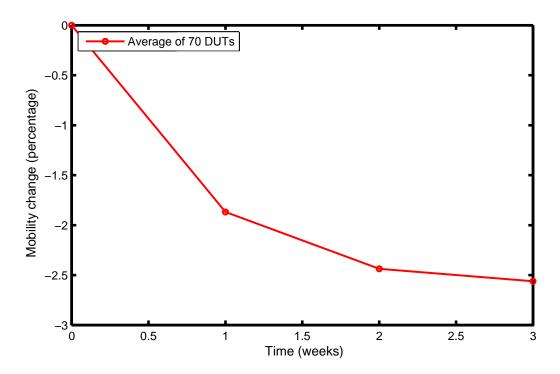

| 2.5  | The 90nm PMOS transistor mobility decreases due to NBTI. Our NBTI mea-           |    |

|      | surements have been carried out at $V_{GS} = 1.15V$ and $127^{\circ}$ C          | 20 |

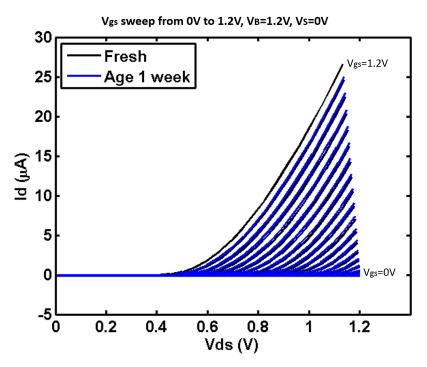

| 2.6  | The 90nm PMOS transistor drain current decreases due to NBTI. Our NBTI           |    |

|      | measurements have been carried out at 127°C. The gate source voltage $V_{GS}$ is |    |

|      | the parameter                                                                    | 21 |

| 2.7  | The NBTI induced threshold voltage change can recover quite fast after the       |    |

|      | stress voltage is removed. In the figure, the stress is applied from 0 to 10000  |    |

|      | seconds and is removed after 10000 seconds                                       | 21 |

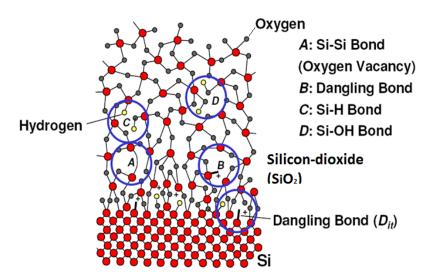

| 2.8  | The silicon-dioxide interface under the transistor gate [Com09]                  | 22 |

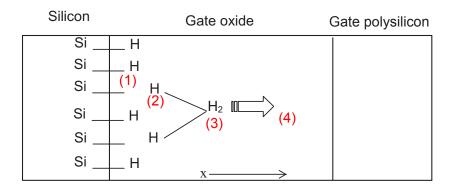

| 2.9  | The RD theory for NBTI degradation [Ala05]. (1) broken $Si - H$ bond, (2) $H$    |    |

|      | ion, (3) recombination to $H_2$ , (4) diffusion to gate polysilicon              | 23 |

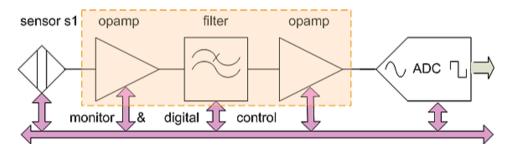

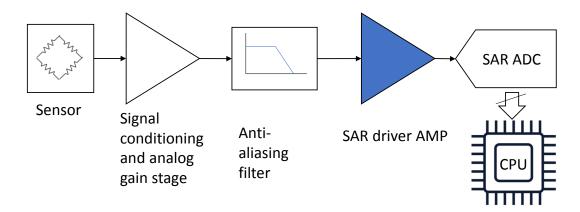

| 2.10 | Generic setup of a sensor and a programmable AFE [Ker10a]                        | 26 |

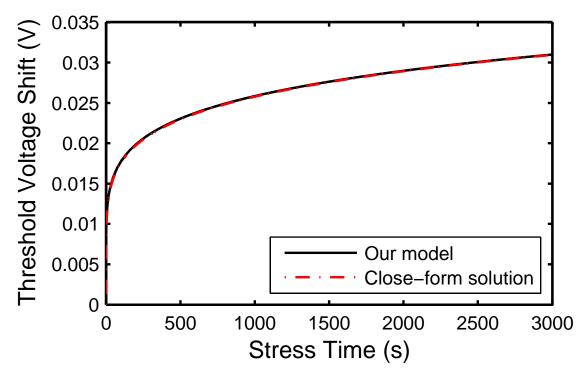

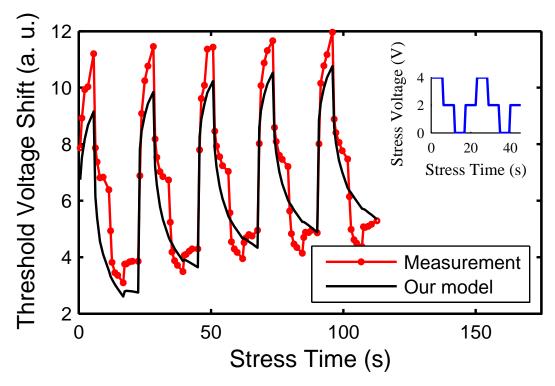

| 3.1  | Comparison of our model with the closed-form solution of RD equations (DC        |    |

|      | voltage stressed situation) [Wan16]                                              | 43 |

| 3.2  | Relative error of our model in Figure 3.1 (DC voltage-stressed situation)        | 44 |

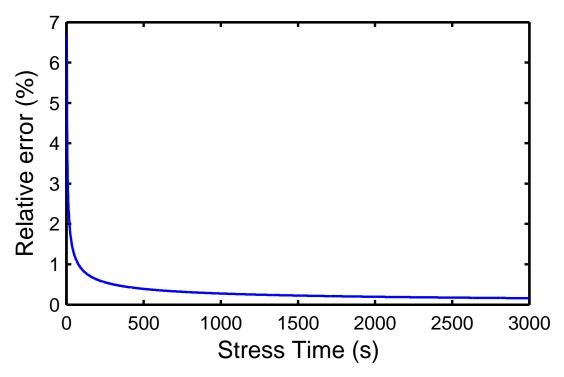

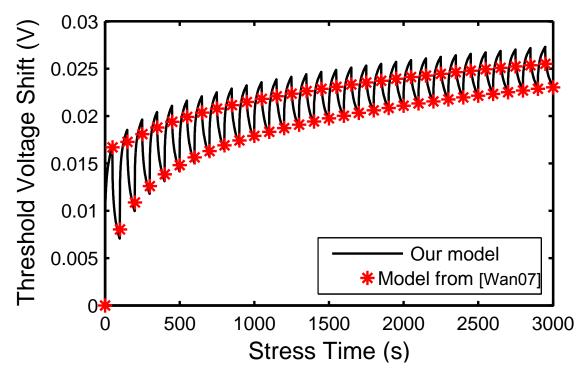

| 3.3  | Comparison of our model with the RD theory based model in [Wan07] for            |    |

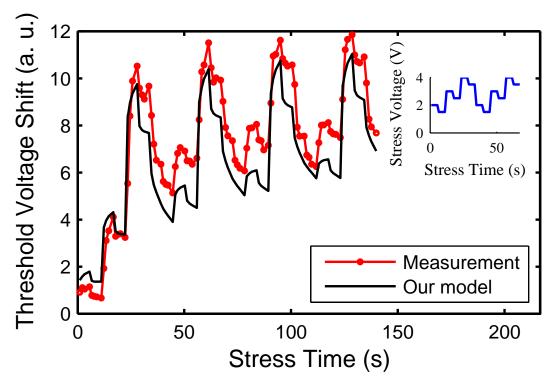

|      | square-wave voltage stress                                                       | 45 |

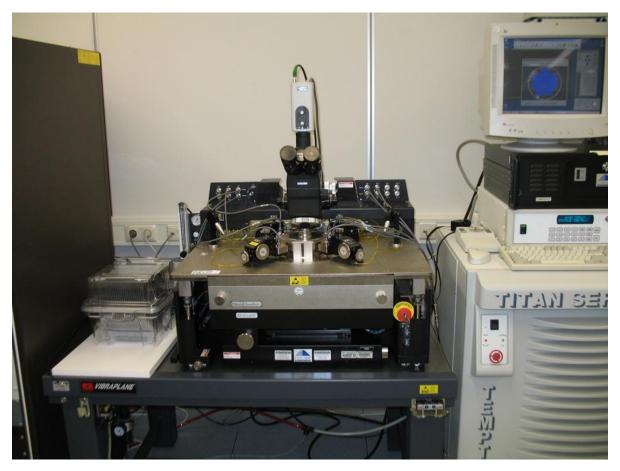

| 3.4  | Used NBTI measurement equipment: Probe Station Summit 12000-Series/              |    |

|      | Titan Series Temptronic, and HP 4155B Semiconductor Parameter Analyzer           | 46 |

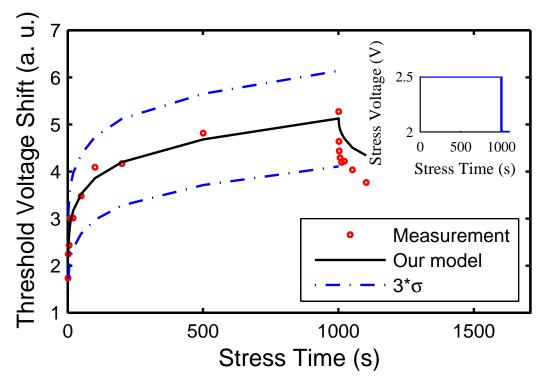

| 3.5  | Stress at 2.5V DC voltage for 1000 seconds                                       | 48 |

**xx** List of Figures

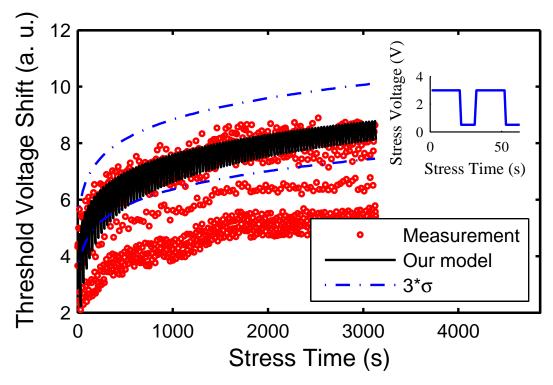

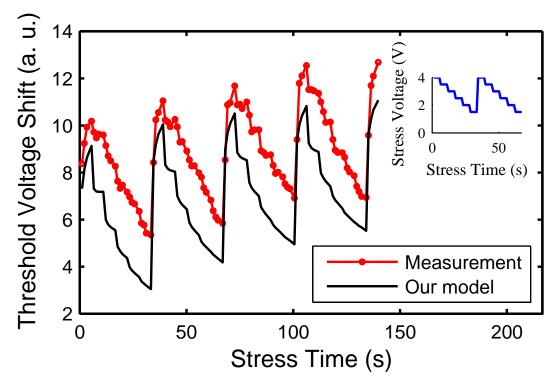

| 3.6  | Stress by a square-wave: high voltage $3V$ for 20 seconds, low voltage $0.5V$ for    |    |

|------|--------------------------------------------------------------------------------------|----|

|      | 10 seconds, duty-cycle 66.7%, 100 cycles (3000 seconds)                              | 49 |

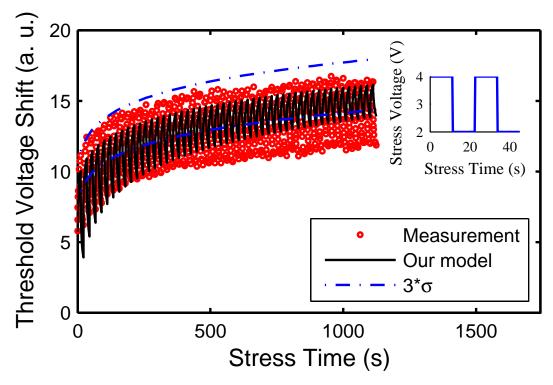

| 3.7  | Stress by a square-wave: high voltage 4V for 10 seconds, low voltage 2V for          |    |

|      | 10 seconds, duty-cycle 50%, 50 cycles (1000 seconds)                                 | 50 |

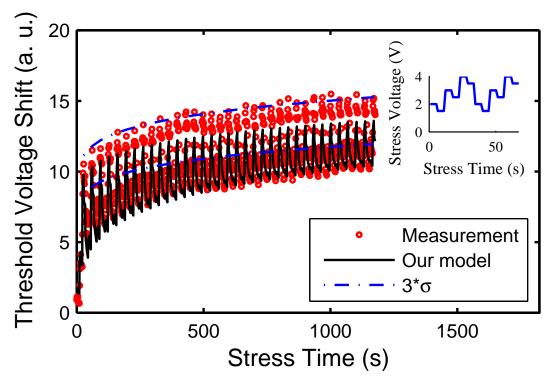

| 3.8  | Stress by a stair-wave: 2V, 1.5V, 3V, 2.5V, 4V, 3.5.V Each step continues for 5      |    |

|      | seconds and is then repeated for 35 cycles (1050 seconds)                            | 51 |

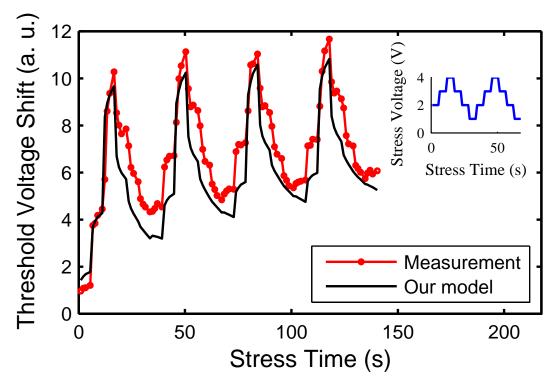

| 3.9  | A few cycles detail in the beginning of Figure 3.8                                   | 52 |

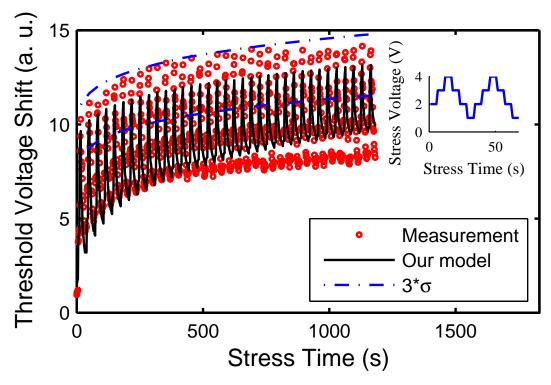

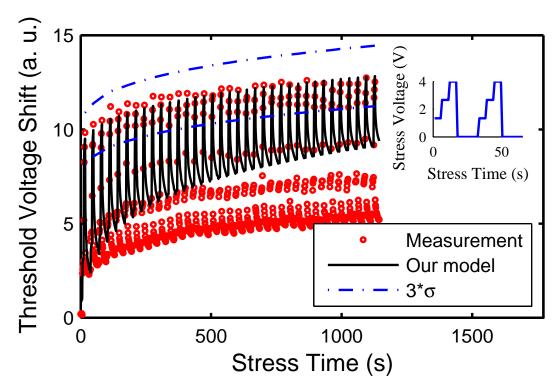

| 3.10 | Stress by a stair-wave: 2V, 3V, 4V, 3V, 2V, 1V. Each step continues for 5            |    |

|      | seconds and is then repeated for 35 cycles (1050 seconds)                            | 53 |

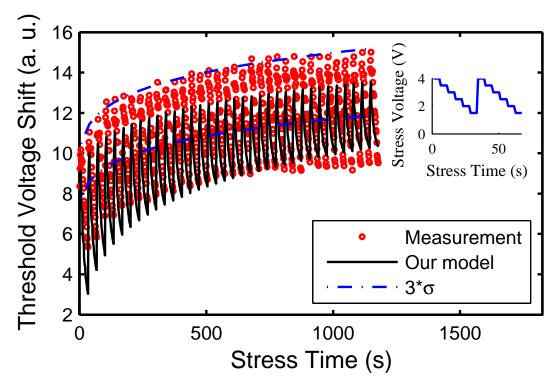

| 3.11 | A few cycles detail in the beginning of Figure 3.10                                  | 54 |

| 3.12 | Stress by a stair-wave: 4V, 3.5V, 3V, 2.5V, 2V, 1.5V. Each step continues            |    |

|      | for 5 seconds and is then repeated for 35 cycles (1050 seconds). It can be           |    |

|      | observed that the simulated top-envelope is lower than the measurement. The          |    |

|      | measurement is almost out of the $3\sigma$ area. It is probably because the average  |    |

|      | stress voltage is high. As already explained, if the stress voltage is too high,     |    |

|      | our model will become less accurate                                                  | 55 |

| 3.13 | A few cycles detail in the beginning of Figure 3.12                                  | 56 |

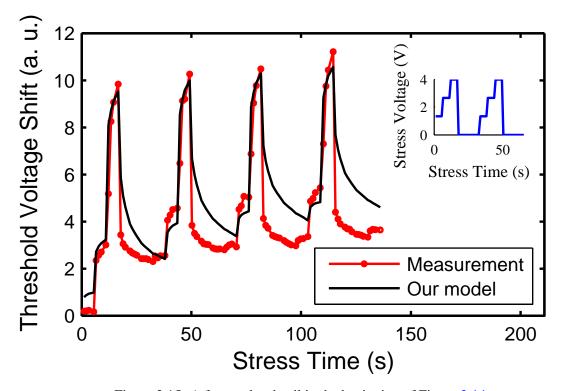

| 3.14 | Stress by a stair-wave: 1.33V, 2.67V, 4V, 0V, 0V, and 0V. Each step continues        |    |

|      | for 5 seconds and is then repeated for 35 cycles (1050 seconds). The simulated       |    |

|      | top-envelope matched the measurement quite good in this case. The bottom             |    |

|      | envelope is much higher in simulation than in the measurement. It is because         |    |

|      | the RD theory cannot model the fast recovery well enough which causes                |    |

|      | the simulation to be always much higher in the bottom envelop than in the            |    |

|      | measurements. It is also the reason why we use the top-envelope to match the         |    |

|      | measurement                                                                          | 57 |

| 3.15 | A few cycles detail in the beginning of Figure 3.14                                  | 58 |

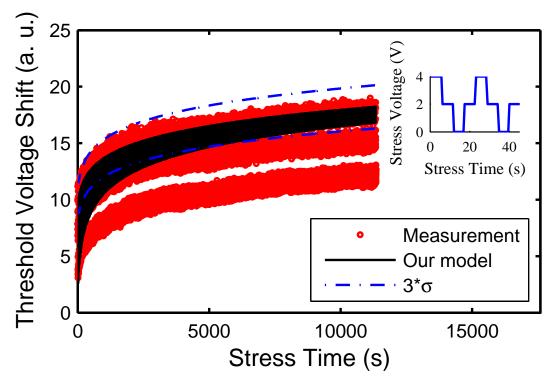

| 3.16 | Stress by a stair-wave: 4V, 2V, 0V, and 2V. Each step continues for 5 seconds        |    |

|      | and is then repeated for 500 cycles ( $10^4$ seconds)                                | 59 |

| 3.17 | A few cycles detail in the beginning of Figure 3.16                                  | 60 |

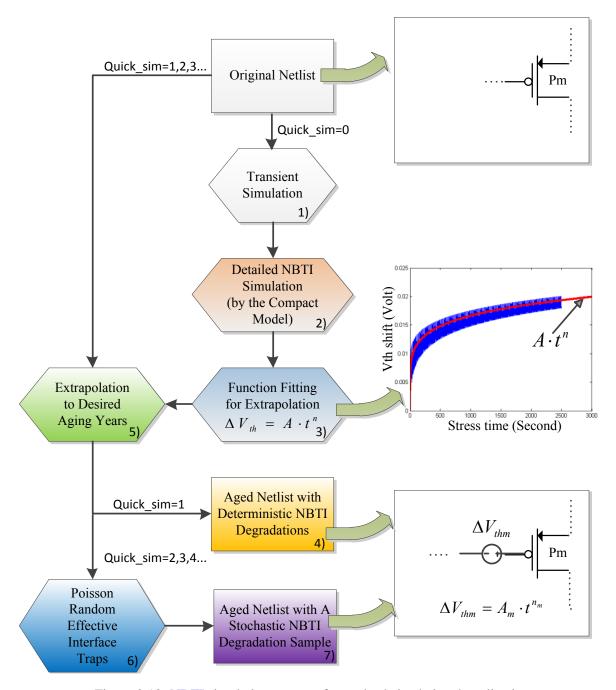

| 3.18 | NBTI simulation strategy for analog/mixed-signal applications                        | 61 |

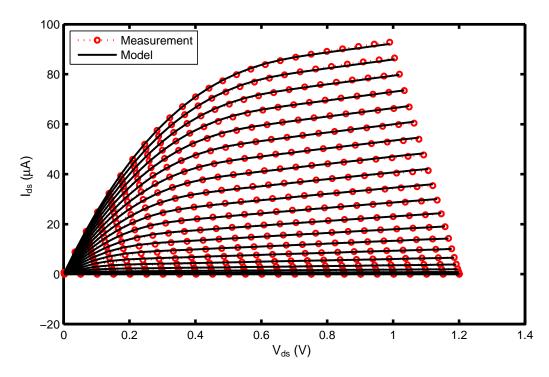

| 3.19 | Comparison of our new model with the measured drain current of a 90nm                |    |

|      | NMOS transistor. $V_s = 0$ , $V_g$ and $V_d$ are swept from 0 to 1.2V with a step of |    |

|      | 0.05V [Wan16]                                                                        | 67 |

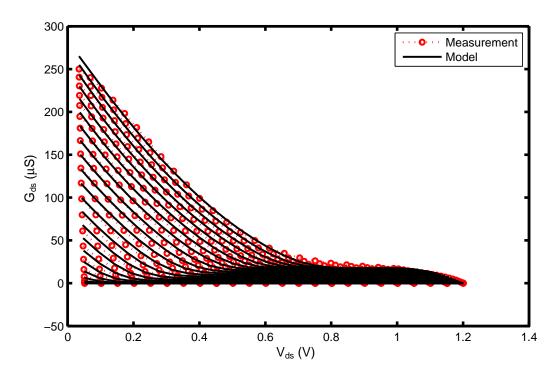

| 3.20 | Comparison of our new model with the measured drain conductance of the               |    |

|      | same 90nm NMOS transistor as shown in Figure 3.19                                    | 68 |

List of Figures xxi

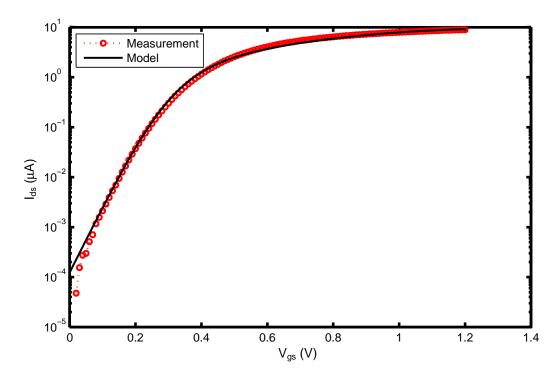

| 3.21 | Comparison of our new model with the measured drain current $I_{ds}$ in the sub-   |     |

|------|------------------------------------------------------------------------------------|-----|

|      | threshold regime of the same 90nm NMOS transistor in Figure 3.19. Parameters       |     |

|      | $V_s = 0$ , $V_d = 0.05V$ , $V_{gs}$ is swept from 0 to 1.2V with a step of 0.01V  | 69  |

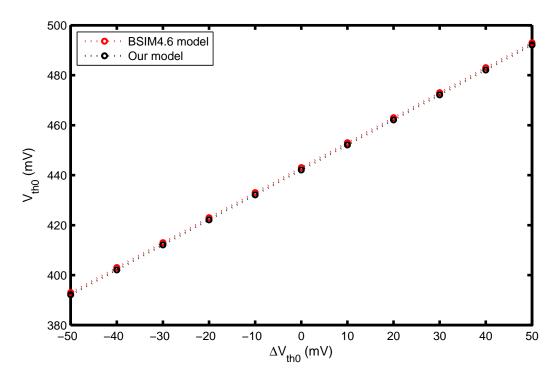

| 3.22 | Comparison of our new MOST model with BSIM4.6 model from the TSMC65nm              |     |

|      | PDK for the $V_{th0}$ shift. The $V_{th0}$ value in the BSIM model is shifted from |     |

|      | $-50mV$ to $+50mV$ . Originally the $V_{th0}$ value in the BSIM model is $443mV$ . | 70  |

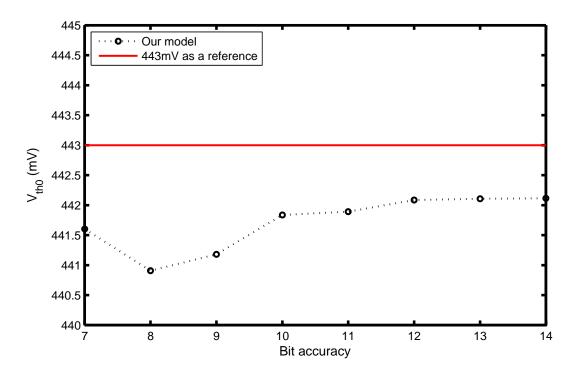

| 3.23 | Comparison of our new MOST model with BSIM4.6 model from the TSMC                  |     |

|      | 65nm PDK for different bit accuracy of the drain current. Original $V_{th0}$ value |     |

|      | in BSIM model of $443mV$ is shown as a red solid line for reference                | 71  |

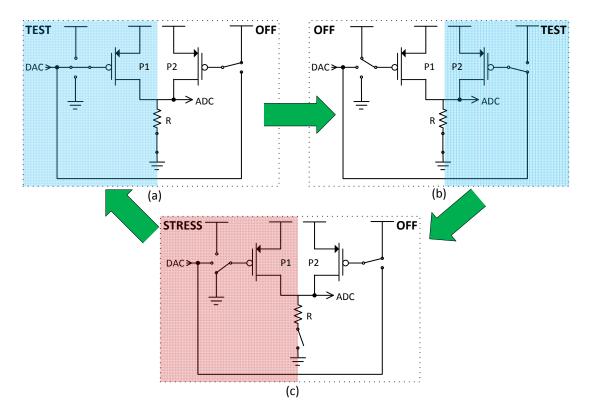

| 3.24 | Proposed on-chip test scheme for measuring $V_{th0}$ ageing behaviour inside a     |     |

|      | SoC. (a) measurement of the P1 transistor, (b) measurement of the P2 transistor,   |     |

|      | (c) no measurements, P1 is under NBTI stress                                       | 72  |

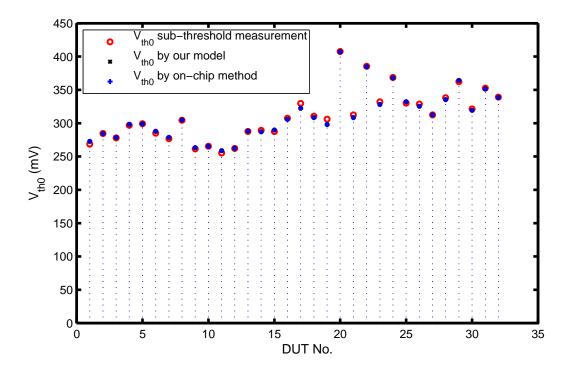

| 3.25 | Comparison of the fresh $V_{th0}$ between the three methods in the 90nm PMOS       |     |

|      | DUT transistors. There are 32 PMOS transistors in total. The black stars are       |     |

|      | overlapped by the blue crosses                                                     | 73  |

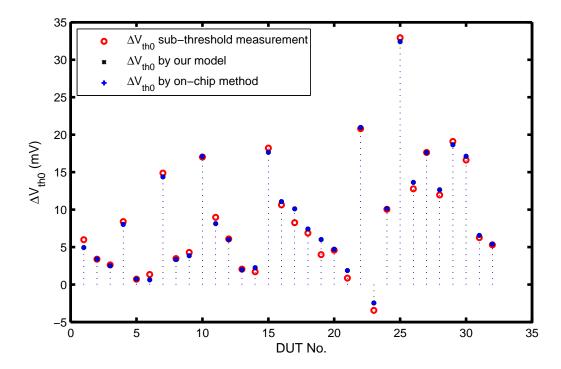

| 3.26 | After stress for 167 hours, comparing the aged $V_{th0}$ between the three methods |     |

|      | in 90nm PMOS DUT transistors. They are the same 32 PMOS transistors as             |     |

|      | used in Figure 3.25. Again the black stars are overlapped by the blue crosses.     | 74  |

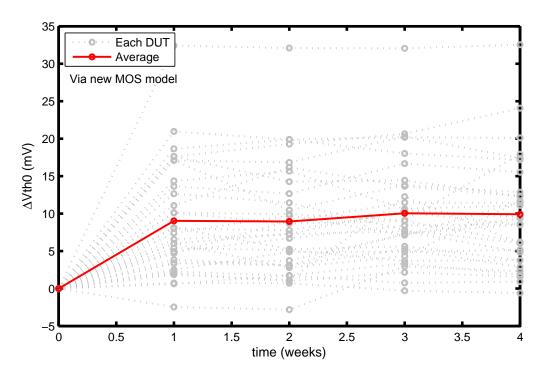

| 3.27 | The $V_{th0}$ change over time during 4 weeks of stress of 32 PMOS DUTs. Ob-       |     |

|      | tained by using the our MOS model                                                  | 75  |

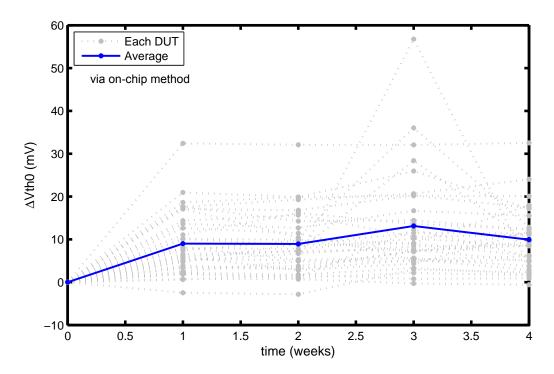

| 3.28 | The $V_{th0}$ change over time in 4 weeks stress of 32 PMOS DUTs. Obtained by      |     |

|      | using the on-chip method                                                           | 76  |

| 4.1  | Possible AFE employing a SAR ADC                                                   | 83  |

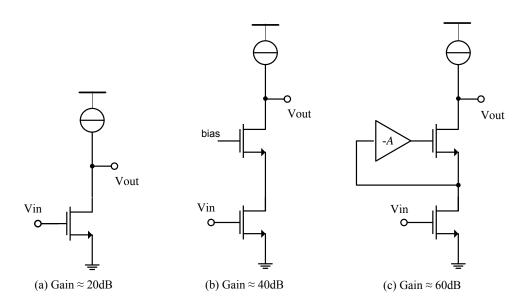

| 4.2  | The commonly used gain-boosting methods                                            | 86  |

| 4.3  | The problem and solution of repeating the previous boosting technique              | 88  |

| 4.4  | Our new gain-boosting method                                                       | 89  |

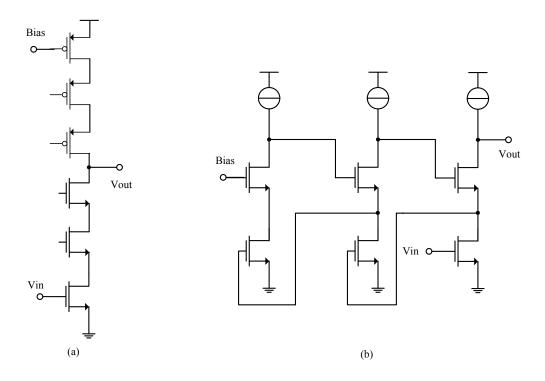

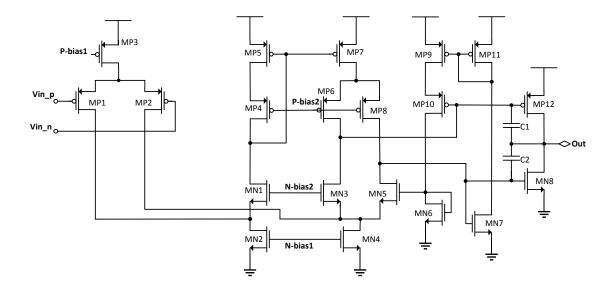

| 4.5  | The schematic of the test-vehicle OpAmp in 65nm                                    | 92  |

| 4.6  | The " $Gm_p$ " and " $Gm_n$ " amplifier transistor schemes as used in Figure 4.5 . | 93  |

| 4.7  | The simulated open-loop gain for the test-vehicle OpAmp in Cadence Spectre.        | 94  |

| 4.8  | The simulation result of input offset for the aging test-vehicle OpAmp in          |     |

|      | Cadence Spectre                                                                    | 95  |

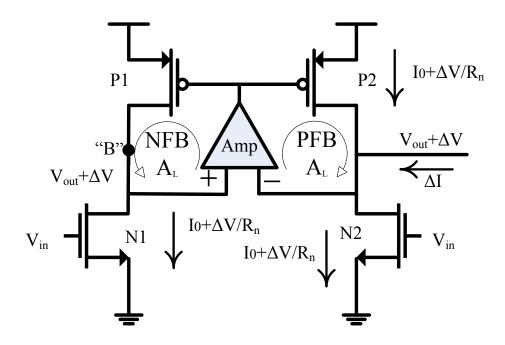

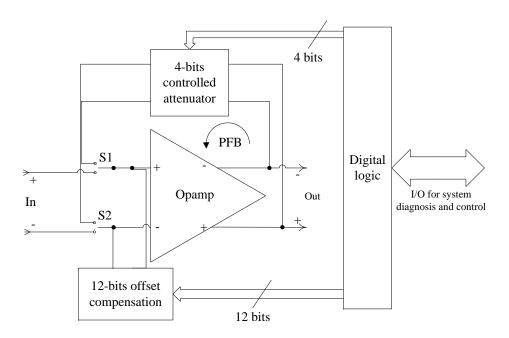

| 4.9  | The designed self-calibrating OpAmp. PFB is the abbreviation of Positive-          |     |

|      | Feedback                                                                           | 98  |

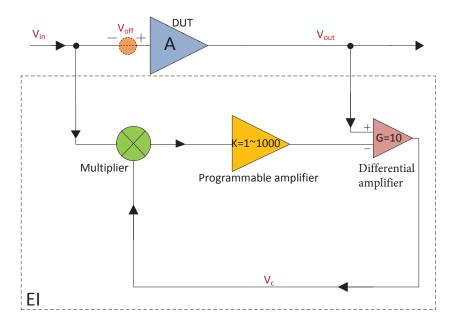

| 4.10 | Block diagram of the new EI for offset and gain measurements                       | 99  |

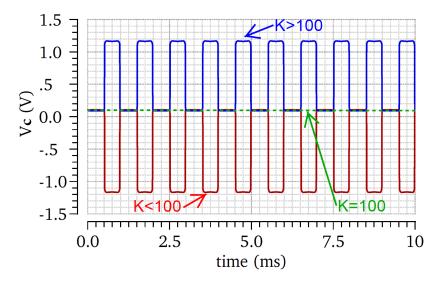

| 4.11 | The simulation for $V_c$ vs. time for two adjacent programmable $K$ values         | 101 |

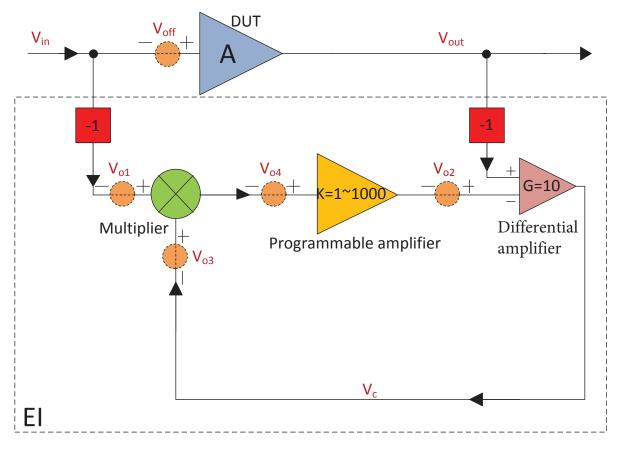

| 4.12 | Self-calibration for resident offsets inside the EI                                | 103 |

**xxii** List of Figures

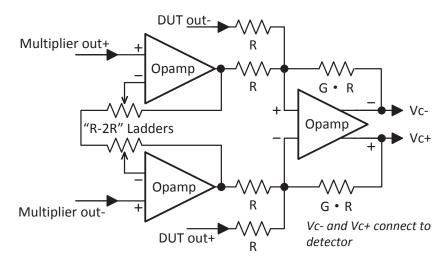

| 4.13            | System-level architecture of the designed embedded offset and gain embedded                                         |                                   |

|-----------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|                 | instrument as well as the detector used in the EI                                                                   | 105                               |

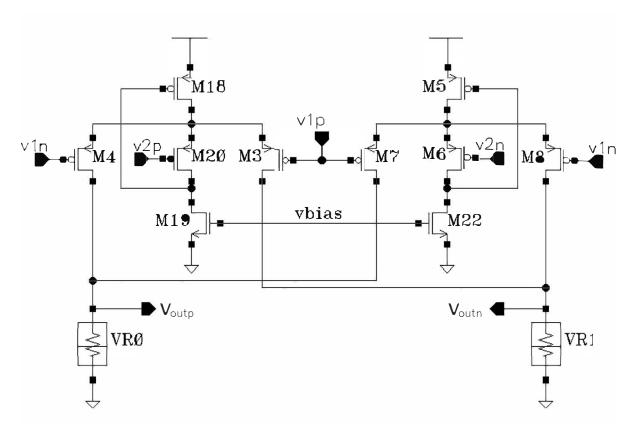

| 4.14            | The four-quadrant trans-conductance multiplier based on the Flipped-Voltage-                                        |                                   |

|                 | Follower (FVF) technology [Car05]. The load resistors VR0 and VR1 are not                                           |                                   |

|                 | real resistors but realized as shown in Figure 4.15                                                                 | 107                               |

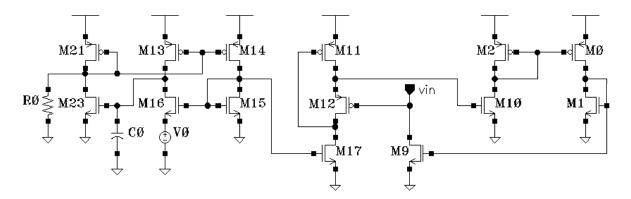

| 4.15            | The circuit to realize the load resistors (VR0 and VR1). Vin is connected to                                        |                                   |

|                 | $V_{outp}$ and $V_{outn}$ in Figure 4.14                                                                            | 107                               |

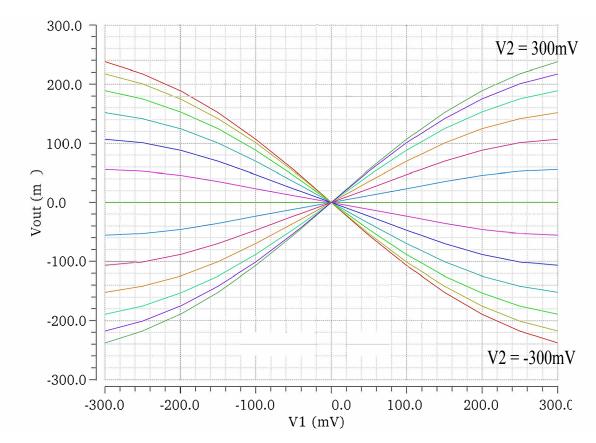

| 4.16            | Simulation results of the multiplier, Vout (Voutp-Voutn) versus V1 (V1p-V1n).                                       |                                   |

|                 | Different lines are stepping with different V2 (V2p-V2n) values                                                     | 108                               |

| 4.17            | Combination of the digital programmable amplifier and the differential ampli-                                       |                                   |

|                 | fier into an instrumentation amplifier. See Figure 4.13                                                             | 109                               |

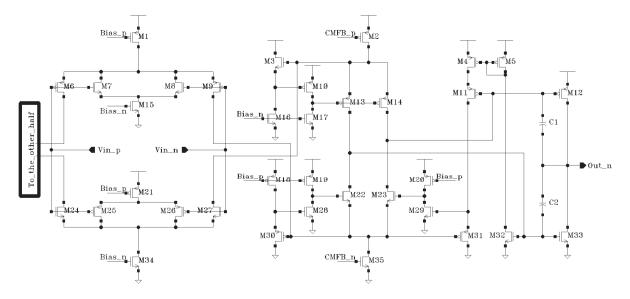

| 4.18            | A fully differential version OpAmp as used in Figure 4.17 (only half is shown).                                     | 109                               |

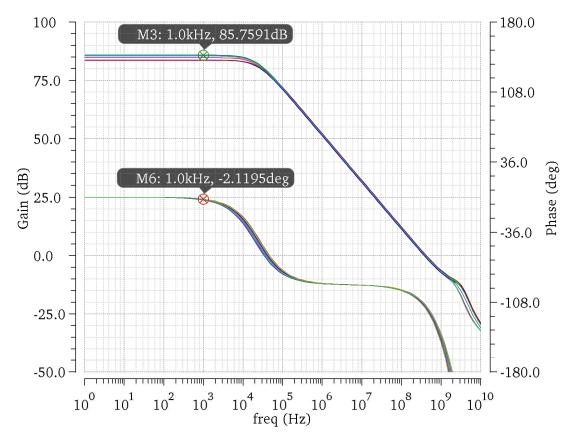

| 4.19            | The gain and phase of the OpAmp with common-mode input voltage varying                                              |                                   |

|                 | from 0 to 1.2V                                                                                                      | 110                               |

| 5.1             | Circuit design of a second-order active RC LP filter                                                                | 119                               |

| 5.2             | -                                                                                                                   | 119<br>119                        |

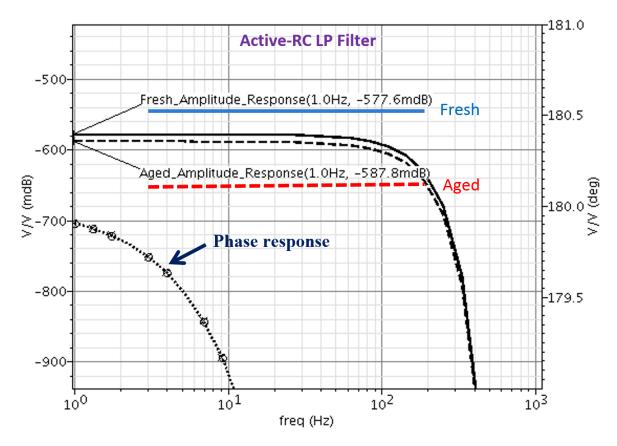

| 5.3             | Simulated transfer function of the active RC LP filter circuit in the case of a                                     | 11)                               |

| 3.3             |                                                                                                                     | 120                               |

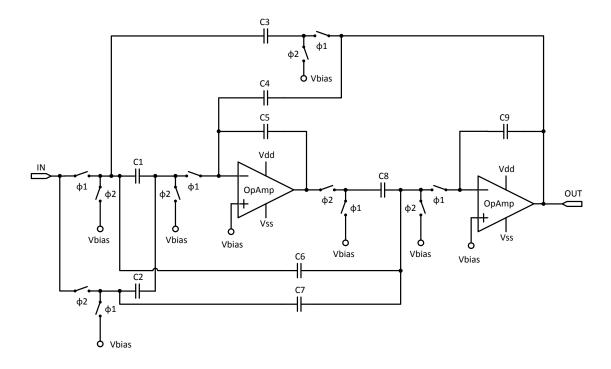

| 5.4             | Circuit design of the second-order switched-capacitor LP filter. The OpAmp is                                       | 120                               |

| Э. <del>т</del> |                                                                                                                     | 121                               |

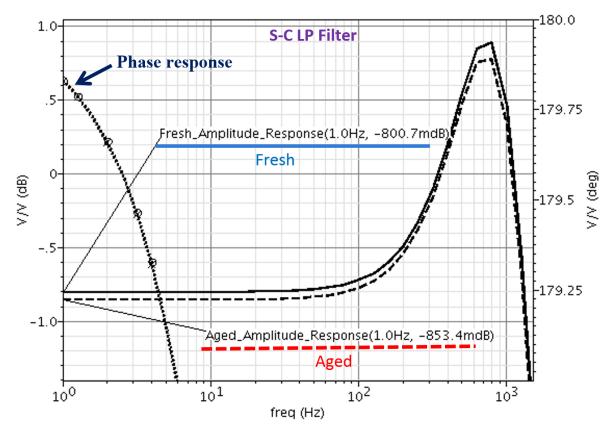

| 5.5             | Simulated transfer function of the switched-capacitor second-order LP filter                                        | 121                               |

| 3.3             | •                                                                                                                   | 122                               |

| 5.6             | •                                                                                                                   | 122<br>123                        |

| 5.7             |                                                                                                                     | 123<br>123                        |

| 5.8             | Simulated transfer function of the OTA-C second-order LP filter circuit in the                                      | 123                               |

| 3.6             |                                                                                                                     | 124                               |

| 5.9             | ·                                                                                                                   | 124                               |

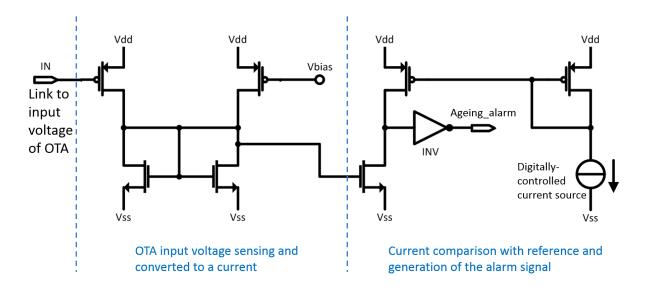

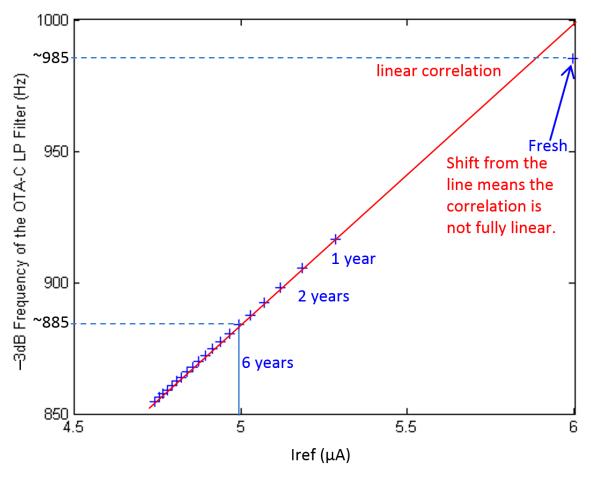

| 3.9             | Simulated differential pair DC current versus the filter $-3dB$ frequency under NBTI ageing showing the correlation | 127                               |

| 5 10            |                                                                                                                     | <ul><li>127</li><li>128</li></ul> |

|                 |                                                                                                                     |                                   |

|                 |                                                                                                                     | 129                               |

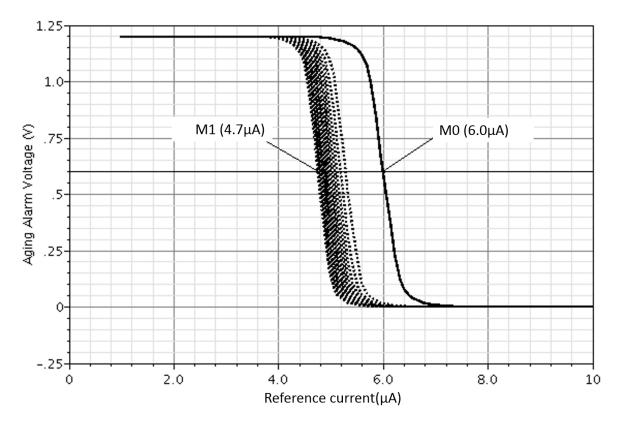

| 5.12            | Ageing alarm signal versus the reference current. The markers M0 and M1 in                                          |                                   |

|                 | Figure 5.12 are the simulated reference current when <i>Ageing_alarm</i> voltage is                                 |                                   |

|                 | on the threshold $(0.6V)$ . It indicates that the OTA differential pair current is                                  |                                   |

|                 | reduced by ageing. Thus the transconductance of the OTA is also reduced by                                          |                                   |

|                 | ageing which will result in a filter bandwidth reduction as shown in Figure 5.8.                                    | 130                               |

List of Figures xxiii

| 5.13 | Correlation of the reference current setting in the EI with the filter $-3dB$ |     |  |  |  |

|------|-------------------------------------------------------------------------------|-----|--|--|--|

|      | bandwidth                                                                     | 131 |  |  |  |

| 6.1  | The block diagram of our 10-bits fully differential SAR ADC                   | 137 |  |  |  |

| 6.2  | The bootstrapped switch [Aks06] and threshold voltage changes in its PMOSTs.1 | 40  |  |  |  |

| 6.3  | The SAR ADC capacitor banks                                                   | 141 |  |  |  |

| 6.4  | The comparator which is composed of a dynamic latch and a pre-amplifier 1     | 142 |  |  |  |

| 6.5  | The asynchronous SAR logic                                                    | 144 |  |  |  |

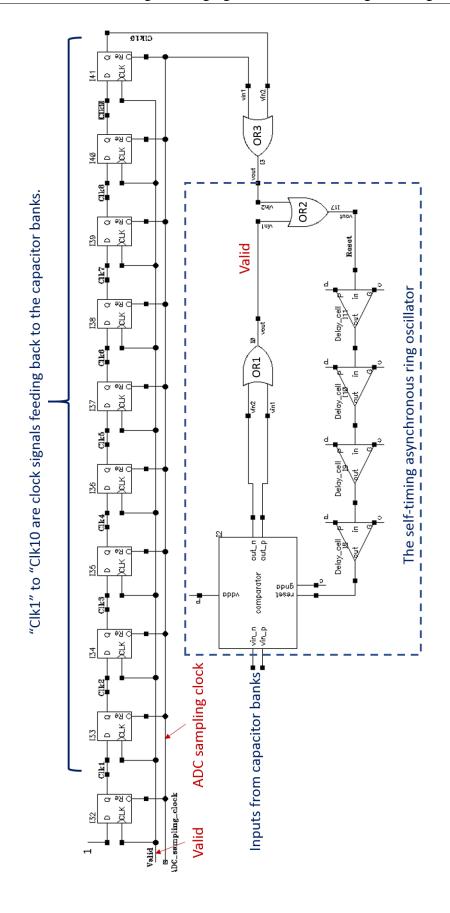

| 6.6  | The asynchronous SAR logic signals generated by the circuits in Figure 6.5 1  | 145 |  |  |  |

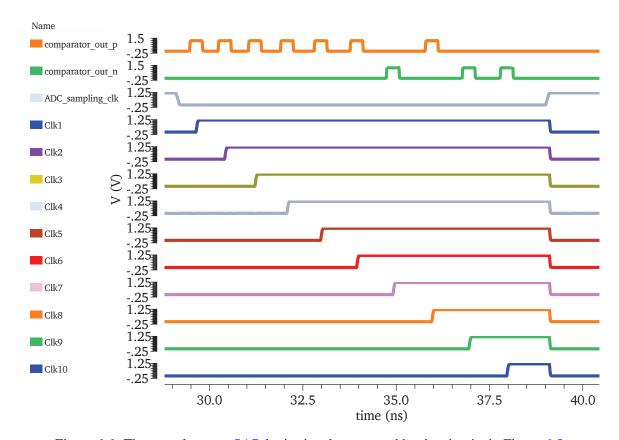

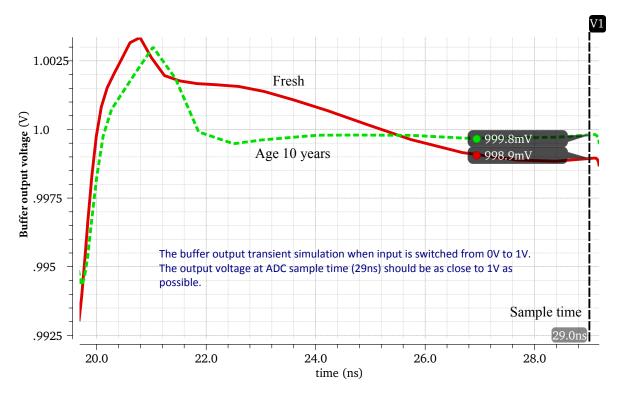

| 6.7  | The voltage waveforms in the SAR ADC comparator inputs                        | 146 |  |  |  |

| 6.8  | The buffer output voltage before and after ageing                             | 148 |  |  |  |

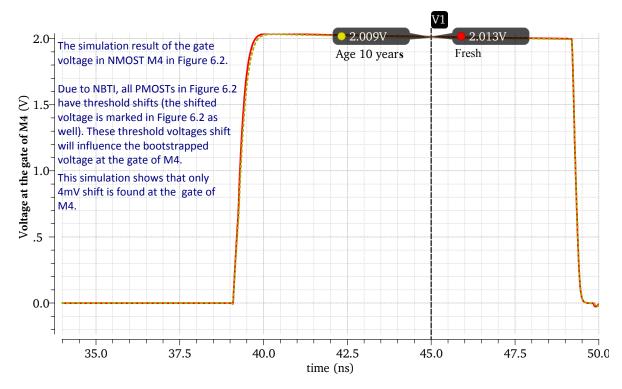

| 6.9  | The simulated gate voltage on NMOST M4 in the bootstrapped switch which       |     |  |  |  |

|      | is shown in Figure 6.2 under fresh and aged conditions                        | 149 |  |  |  |

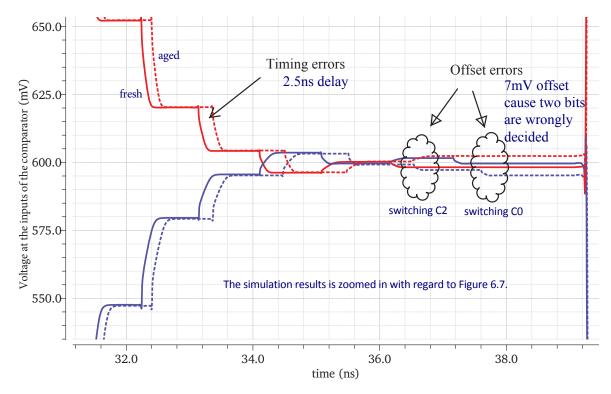

| 6.10 | The SAR ADC voltage wave forms at the input of the comparator. Fresh          |     |  |  |  |

|      | simulation results and ageing simulation results are both provided            | 151 |  |  |  |

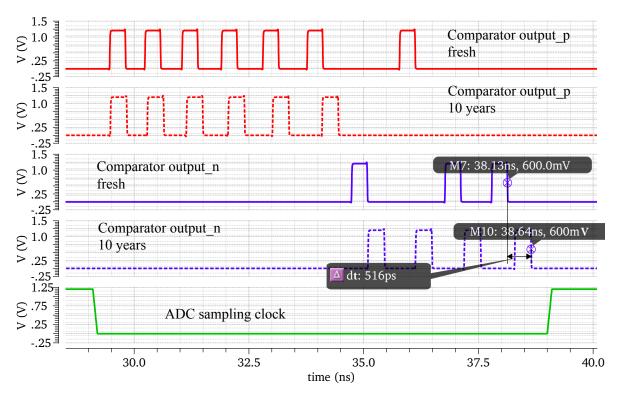

| 6.11 | The SAR ADC voltage wave forms at the output of the comparator. Fresh         |     |  |  |  |

|      | simulation results and ageing simulation results are both provided            | 152 |  |  |  |

| 6.12 | The general non-differential SAR ADC block diagram                            | 153 |  |  |  |

| 6.13 | The EI for detecting timing errors in the asynchronous SAR logic              | 155 |  |  |  |

| 6.14 | Two SAR ADCs are configured for an EI detecting both ADCs' offset errors.     | 156 |  |  |  |

| 6.15 | Matlab simulation of ADC offset EI                                            | 157 |  |  |  |

| A.1  | The Cadence RelXpert Commands Menu and relevant parameters                    | 171 |  |  |  |

| C.1  | The top-level schematics of the designed SAR ADC                              | 187 |  |  |  |

| C.2  | The DAC control block in detail                                               | 88  |  |  |  |

# **List of Tables**

| 1.1 | An example mission profile for a semiconductor device used in vehicles [Pre15].   | 5   |

|-----|-----------------------------------------------------------------------------------|-----|

| 3.1 | The new compact NBTI model with <i>Non-Uniform</i> Time Step $\Delta t_n$ [Wan16] | 40  |

| 3.2 | Applied stress types in the NBTI measurements                                     | 47  |

| 3.3 | Final evaluation results                                                          | 52  |

| 3.4 | The model simulation time in Cadence ADE vs. reference [Kuf10]                    | 57  |

| 4.1 | Test vehicle OpAmp ageing performance                                             | 94  |

| 4.2 | EI simulation results                                                             | 110 |

## **List of Abbreviations**

```

\Delta\Sigma

Delta-Sigma. 136

ABS

Anti-lock Braking System. 116

AC

Alternating-Current. 34, 49, 51, 77, 102, 163

ADC

Analogue-to-Digital Converter. xii, xvii, xviii,

xxi, xxiii, 8, 9, 17, 26, 27, 33, 62, 68, 69, 70, 72,

77, 83, 84, 85, 99, 116, 125, 128, 135, 136, 137,

138, 139, 140, 141, 142, 143, 145, 146, 147, 148,

149, 150, 151, 152, 153, 154, 155, 156, 157, 158,

159, 162, 163, 165, 166, 185, 186, 187, 188

ADE

Analogue Design Environment. xi, xxv, 9, 35, 41,

52, 54, 56, 57, 77, 163

AFE

Analogue/mixed-signal Front-End. xi, xiii, xix,

xxi, 1, 2, 3, 4, 6, 8, 13, 17, 25, 26, 28, 77, 83, 84,

115, 116, 125, 135, 136, 138, 161, 162, 165, 166,

167

AMS

Analogue/Mixed-Signal. xi, 3, 6, 7, 13, 24, 25,

26, 27, 28, 33, 34, 35, 36, 52, 77, 81, 82, 98, 161,

162, 163, 166

BIST

Built-in-Self-Test. 17, 27

BSIM

Berkeley Short-channel IGFET Model. xxi, 63,

66, 67, 68, 70, 71

CHC

Channel Hot-Carrier. 166, 167

```

**xxviii** List of Abbreviations

```

CMOS

Complementary Metal Oxide Semiconductor. xi,

xii, xvi, xvii, xix, 6, 8, 9, 13, 14, 15, 16, 17, 18,

24, 27, 33, 34, 35, 36, 38, 43, 44, 47, 58, 62, 77,

81, 82, 84, 85, 87, 91, 104, 108, 111, 116, 117,

118, 128, 135, 136, 137, 139, 141, 143, 145, 147,

149, 158, 161, 163, 164, 165, 166

CPS

Cyber-Physical System. 1, 2, 4

CPU

Central Processing Unit. 17, 57, 69, 185

DAC

Digital-to-Analogue Converter. xxiii, 62, 69, 70,

72, 97, 127, 129, 136, 137, 143, 145, 185, 186,

188

DC

Direct-Current. xix, xxii, 34, 37, 39, 42, 43, 44,

48, 49, 51, 53, 60, 77, 82, 84, 88, 89, 94, 106, 117,

118, 124, 125, 126, 127, 163

DNL

Differential Non-linearity. 147

DSP

Digital signal processor. 185

DUT

Device Under Test. xxi, 36, 58, 62, 73, 74, 75, 76,

99, 100, 102, 103, 104, 109, 111, 164

EDA

Electronic Design Automation. 117

ΕI

Embedded Instrument. xi, xii, xiii, xvi, xvii, xviii,

xxi, xxii, xxiii, xxv, 9, 13, 26, 27, 28, 33, 36, 58,

59, 61, 63, 65, 67, 68, 69, 71, 73, 75, 77, 81, 82,

96, 98, 99, 100, 102, 103, 104, 105, 106, 109, 110,

111, 115, 116, 117, 125, 126, 127, 128, 129, 131,

135, 154, 155, 156, 157, 158, 161, 162, 164, 165,

166, 167

EKV

C. C. Enz, F. Krummenacher and E. A. Vittoz. 63,

European Library-based flow of Embedded Sili-

ELESIS

con test Instruments. xv, 7, 8, 9, 25

ENOB

Effective-Number-of-Bits. 84

Equivalent Oxide Thickness. 41

EOT

EPS

Electric Power Steering system. 116

```

List of Abbreviations xxix

```

FinFET

Fin Field-Effect Transistor. 16, 166, 167

Flipped-Voltage-Follower. xxii, 91, 106, 107

FVF

HAST

Highly Accelerated Temperature/Humidity Stress

Test. 3, 158

HCI

Hot-Carrier Injection. 15, 24, 34, 71, 118

HTOL

High Temperature Operating Life. 3, 158

HTSL

High Temperature Storage Life. 3, 158

IC

Integrated Circuit. 1, 2, 3, 4, 6, 14, 117, 167

INL

Integral Non-linearity. 147

IoT

Internet of Things. 1, 2

ΙP

Intellectual Property. xii, xiii, 2, 4, 6, 7, 8, 16,

17, 25, 26, 27, 28, 81, 82, 98, 111, 135, 154, 161,

162, 164, 165, 166

JEDEC

Joint Electron Device Engineering Council. 3, 44,

60, 63

Lightly-Doped-Drain. 15

LDD

Low-Pass. xvii, xxii, 116, 117, 118, 119, 120,

LP

121, 122, 123, 124

LSB

Least Significant Bit. 138, 142, 145, 147, 148,

150, 152, 157, 158, 185

Least Squares Method. 47, 66

LSM

MOS

Metal Oxide Semiconductor. xi, xii, xxi, 58, 64,

75, 116

MOST

Metal-Oxide-Semiconductor Field-Effect Transis-

tor. xvi, xviii, xxi, 8, 9, 15, 27, 33, 35, 36, 58, 59,

62, 63, 66, 67, 68, 69, 70, 71, 72, 73, 74, 76, 77,

87, 89, 137, 149, 163, 164

MSB

Most Significant Bit. 138, 146

Measurement-Stress-Measurement. 35, 59

MSM

MTBF

Mean Time Between Failures. 3

```

**XXX** List of Abbreviations

```

NBTI

Negative Bias Temperature Instability. xi, xii, xvi,

xviii, xix, xx, xxi, xxii, xxv, 9, 13, 14, 15, 16, 17,

18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 33, 34,

35, 36, 37, 38, 39, 40, 41, 42, 43, 44, 45, 46, 47,

48, 49, 50, 51, 52, 53, 54, 55, 56, 57, 58, 59, 60,

61, 62, 64, 66, 68, 70, 71, 72, 74, 75, 76, 77, 81,

82, 84, 93, 94, 96, 102, 111, 115, 118, 119, 120,

124, 125, 126, 127, 128, 135, 136, 147, 148, 149,

150, 151, 153, 154, 158, 161, 162, 163, 164, 165,

166, 167, 169

NMOS

N-type Metal Oxide Semiconductor. xx, xxi, 15,

66, 67, 68, 69, 149

n-type Metal-Oxide-Semiconductor Transistor.

NMOST

15, 85, 87, 88, 89, 90, 106, 139, 148

OpAmp

Operational Amplifier. xii, xvi, xvii, xviii, xxi,

xxii, xxv, 7, 8, 9, 26, 27, 81, 82, 83, 84, 85, 86,

87, 89, 90, 91, 92, 93, 94, 95, 96, 97, 98, 99, 101,

102, 103, 105, 107, 108, 109, 110, 111, 117, 118,

119, 120, 121, 125, 126, 129, 138, 139, 147, 155,

162, 164, 165, 166

OTA

Operational Transconductance Amplifier.

xvii, xviii, xxii, 115, 116, 117, 121, 122, 123,

124, 125, 126, 127, 128, 129, 131, 162, 165

On-The-Fly. 22, 35, 44, 59, 60

OTF

PBTI

Positive Bias Temperature Instability. 15, 16, 148,

149, 152, 166, 167

PC

Personal Computer. 1

PDK

Process Design Kit. 117

PFB

Positive-Feedback. xxi, 90, 97, 98

PLL

Phase-Lock-Loop. 17, 155

PMOS

P-type Metal Oxide Semiconductor. xix, xxi, 14,

18, 19, 20, 21, 34, 35, 43, 44, 45, 48, 55, 57, 69,

73, 74, 75, 76, 118, 124, 148, 163

```

List of Abbreviations xxxi

```

p-type Metal-Oxide-Semiconductor Transistor.

PMOST

xix, xxiii, 9, 14, 15, 18, 19, 20, 44, 82, 87, 118,

120, 121, 139, 140, 142, 148, 161

PPM

Parts per Million. 3

PSP

Philips Surface Potential. 63

PVT

Process, Voltage and Temperature. 86, 129

RD

Reaction-Diffusion. xi, xvi, xix, 22, 23, 24, 33,

35, 36, 37, 41, 42, 43, 45, 47, 50, 51, 57, 77, 163,

166, 167

RL

Reaction-Limited. 22, 23, 24

SAR

Successive-Approximation Register. xii, xvii,

xviii, xxi, xxiii, 9, 83, 135, 136, 137, 138, 139,

140, 141, 142, 143, 144, 145, 146, 147, 148, 150,

151, 152, 153, 154, 155, 156, 158, 159, 162, 165,

166, 185, 186, 187, 188

SC

Switched-Capacitor. 115, 116, 117, 120, 126, 131

SNR

Signal-to-Noise Ratio. 146

SoC

System-on-Chip. xi, xii, xxi, 2, 4, 6, 7, 8, 25, 36,

62, 63, 68, 69, 70, 72, 77, 81, 98, 106, 115, 116,

135, 155, 162, 163, 164, 165, 166, 167

SPICE

Simulation Program with Integrated Circuit Em-

phasis. 34, 35, 54, 60, 163

TC

Temperature Cycle. 3

TDDB

Time-Dependent Dielectric Breakdown. 15, 34,

71, 118

Transmission Electron Microscopy. xix, 15, 16

TEM

THB

Temperature Humidity Bias. 3, 158

Towards One European Test Solution. xv, 7, 8, 9,

TOETS

25

TSMC

Taiwan Semiconductor Manufacturing Company.

xxi, 9, 66, 67, 70, 71, 85, 111, 164, 165

```

University of Twente. 7

UT

## **Chapter 1**

### Introduction

Abstract- Moore's law has driven the developments of Integrated Circuits (ICs) for more than 50 years. Not only the density of ICs has increased enormously, but also the computational power of ICs has improved dramatically. Due to these improvements, more and more functions are integrated into a single chip together with embedded software. The application areas have been extended beyond Personal Computers (PCs). Examples are smart phones, electrical cars, Internet of Things (IoT) and so on. Among these new application areas, many of them contain safety-critical applications. Therefore the ICs used in these safety-critical areas are required to be dependable, which include reliability but more than just reliability as will be described later. This thesis takes a first step in developing dependable Analogue/mixed-signal Front-Ends (AFEs). Being the starting chapter of this thesis, the background of the thesis is introduced first. Then the motivations for research are presented with several questions raised. The research frameworks which include two European projects are discussed next. Finally the outline of the thesis is presented.

#### 1.1 Introduction

Not so long ago, electric cars were still not yet driving on the road. IoT and Cyber-Physical System (CPS) were also not yet defined. Medical electronics such as implantable hearing-aids and internal temperature sensor capsules were still in their prototype phase. However, from the introduction of the smart phone, the development of the electronics already showed some trends, which is making more and more things smart and connected.

One of the examples is the automotive industry. More and more sensors are implemented in new cars, such as tyre-pressure sensors, wheel-rotation sensors, car radars, visual cameras and so on. To process the data from these sensors, more and more ICs are used in cars. Even

2 Introduction

highly complicated chips like many processor System-on-Chip (SoC) are starting to be used in the automotive industry. These ICs or SoCs are required to be very dependable and have a long lifetime (10 to 15 years) [Ker10].

At the same time, the major market for semiconductor companies is the consumer market. The most important requirements of the consumer market are price, power consumption and performance. The dependability has a lower priority. A lifetime of 5 years is sufficient for most consumer products. These requirements have driven the semiconductor process into the nanometer range and heavy competition pushes the time-to-market period to a minimum [Ely14].

With the semiconductor process technology entering the nanometer region, many of the processing techniques are approaching their limits, like lithography and doping. ICs produced in the latest technology have many more failures than before and thus have lower yield [Pre15]. To find and analyse all failure modes, extra efforts and sufficient failure cases are required. These all take much time and hence increase costs.

Normally a semiconductor process technology for mass production needs at least two years to reach sufficient high yield, to be matured [Sas03]. Another few years are required to gather sufficient in-field returned failure samples for improving the process. Here the difference between consumer products and for instance automotive products becomes clear. For consumer products, one will not wait for the semiconductor process to be matured. Time-to-market has the highest priority. While for automotive products, quality and dependability are the most important considerations. Hence the safety-critical automotive products normally use older semiconductor process technologies than consumer products [Pel13]. The main reason is because they are required to be highly reliable and thus more dependable.

With time progressing, the automotive markets have become more and more attractive. Many semiconductor companies have entered this field. The competition becomes hot and time-to-market is critical. Using the latest semiconductor process (means small area and thus lower cost) for an automotive grade 0 product [Aut07], which means safety-critical products like all kinds of sensors in a car, while keeping the high dependability has become a very attractive topic. The same is also true nowadays for medical electronics, IoT and CPS. Most of the research in highly dependable ICs is focused on digital IP blocks, like microcontrollers, microprocessors and logical function blocks. Very little related work can be found on dependable analogue/mixed-signal IPs, especially the AFE. In automotive ICs, the AFEs are a critical part because they directly interact with the outside physical world.

1.1 Introduction 3

In this thesis, the focus is on AFE blocks for safety-critical ICs in automotive applications. This chapter will introduce dependable systems, mission profiles, thesis motivation, project framework, the research questions, and thesis outline. In the following chapters, the author will subsequently deal in detail with the Analogue/Mixed-Signal (AMS) building blocks of dependable AFEs.

#### 1.1.1 Dependable Systems

For a chip used in a safety-critical system, common sense is that the quality of the chip is required to be very high. *Quality* refers to the number of chips which can deliver its specification when they reach customers (at 0 hour). It uses the number of failing samples in 1 million samples as an indication. For example, a 1 Parts per Million (PPM) quality means that on average there is one sample failing within one million chips delivered.

It is worth to mention that quality is used to describe a product at 0 operational hours (fresh state), not during the lifetime. To describe a product during its operational lifetime, another term called reliability is used instead. *Reliability* is the ability of a system or component to perform its required functions under stated conditions for a specified time [Int06]. The reliability can be characterized by the Mean Time Between Failures (MTBF). It is of vital importance for safety-critical systems. A product failure after a few years of usage is very difficult to predict during a fresh product test. Resulting from the efforts of the Joint Electron Device Engineering Council (JEDEC) [Str08], a lot of reliability tests have been developed and standardized to help estimating and improving the product reliability. These reliability tests include Temperature Cycle (TC) test, High Temperature Operating Life (HTOL) test, Temperature Humidity Bias (THB) test, Highly Accelerated Temperature/Humidity Stress Test (HAST) and High Temperature Storage Life (HTSL) test. With the help of these reliability tests, the silicon chip's early infant-failure rate can be reduced dramatically [Pre15].

On the other hand, reliability tests can be destructive and usually help to filter out the infant-failure samples. For improving the lifetime of products, especially wear-out time, these reliability tests only provide limited help [Pre15]. The samples used for reliability tests cannot be sold to customers anymore. They are used for study and improving the reliability of the product and process, but cannot guarantee that all products shipped to customers will have no reliability issues.

With the developments in technology, especially with the help of new smart and connected systems, one can even improve the product lifetime (wear-out) by self-monitoring or self-repair. *Dependability* is a kind of umbrella that spans several attributes (or views) like reliability,

4 Introduction

availability, maintainability as well as safety and security [Int06]. A dependable system is often a fault-tolerant system. It is not only reliable but also knows how to proceed if the system (potentially) fails. Due to the computational capability of systems nowadays, the dependable system can not only adapt to changes in the outside world but also detect the failure in the system itself. If a failure occurs within the system, the dependable system could carry out a simple failure analysis to find the fault location. Corresponding counter actions (maintenance) like isolation, bypass, and replacing IPs with redundant resources can be implemented to emulate repair. The repair time is linked to the system availability [Int06].

A dependable CPS will totally change the way people interact with engineered systems – just as the Internet has transformed the way people interact with information [Nat16]. It will drive innovation and competition in many fields like autonomous driving, smart agriculture, smart energy grids, artificial intelligence robots, building design and automation, healthcare, and manufacturing.

In this thesis, our work is focussed on how to design dependable AFEs for automotive SoCs.

#### 1.1.2 Mission Profiles

What are the requirements for a device in a dependable system? A simple answer is that it depends on the application domain. An IC used for smart phones has a totally different working environment as compared to an IC used for automotive safety purposes. The required lifetime is also different. If a failure occurs in the IC, the consequence will be totally different for a smart phone than for a safety system in a car.

In the semiconductor industry, these application differences are summarized and simplified into so-called mission profiles. A mission profile is a collection of relevant environmental stress and operational conditions. These conditions are the ones an IC is being exposed to during its full-life cycle [Pre15].

A mission profile could include:

- Lifetime in years.

- On-time in hours.

- Number of on-off cycles.

- Operational temperature.

1.1 Introduction 5

Table 1.1: An example mission profile for a semiconductor device used in vehicles [Pre15].

| Lifetime                  | On-time      | On-off cycles | Temperature | Humidity |

|---------------------------|--------------|---------------|-------------|----------|

| 15 years (=131,400 hours) | 12,000 hours | 54,000        | 125°/ 150°C | 95%      |

#### • Relative humidity.

The lifetime is defined as the time period between the completion of the manufacturing process of the product and the end-of-life of the system. For a portable device like smart phones, the lifetime is only considered to be 5 years. For a home applications like TVs, computers, radios and DVDs, the lifetime can be up to 10 years. For automotive applications, the lifetime is 15 years [Ely14, Pre15].

The on-time is defined as the total time during which the device is operating. The power-down mode is considered to be the case where the device is not operating and is thus not taken into account in the on-time. For a smart phone and TVs, the on-time is considered to be 6 hours per day. For a car, the on-time is assumed to be 2 hours per day [Ely14, Pre15].

The on-off cycles are defined as the times of switching on and switching off the device per day. For a portable device and home applications, the on-off cycles are counted as 4 times per day. For automotive products, the on-off cycles are defined as 10 times per day [Ely14, Pre15]. The previous data is coming from statistics of a large number of user cases.

The operational temperature is defined as the environmental temperature under which the device is operating. For portable devices, the operational temperature is set from -20°C to 55°C. For indoor home applications, the operational temperature is between 0°C to 40°C. For automotive products, the operational temperature is defined as -55°C to 125°C. Some extreme applications in automotive can go up to 150°C [Pre15].

The relative humidity is defined as the environmental humidity in which the device is working. For portable devices, home applications, automotive products, a humidity of 95% can be used for all.

Table 1.1 shows an example of the mission profile for a semiconductor device used in cars. The parameters in the profile will be normally used to determine the acceleration (reliability)

6 Introduction

test conditions, like how many different reliability tests are required and what the temperature and time period are for each reliability test.

In our research, the target vehicles are the automotive AFEs. The focus is on the reliability behaviour during its lifetime and how to make it dependable under the automotive mission profile. The most important parameters in Table 1.1 are the lifetime and operational temperature.

#### 1.2 Motivation

Most of the research in highly dependable SoCs are focussed on digital IP blocks, like microcontrollers, microprocessors and logic function blocks. The way of validation is normally assuming a special kind of failure happened or injecting an artificial fault into digital blocks. Subsequently it is verified if the proposed dependable system can handle the fault. Reliability simulations are rarely used. Even when implementing reliability simulations, it is normally carried out with a simple DC model without dynamic signals for the sake of simplicity [Kuf10].

However, in automotive ICs, the AFEs are the most critical (versus digital tolerancy) part because they directly interact with the outside physical world. Little publications can be found on dependable AMS IPs, especially for the AFEs.

The reason is that the study of the reliability behaviour over time, which is referred to as *ageing* in this thesis, are very difficult in analogue circuits as compared to digital circuits. It requires accurate reliability models which can handle arbitrary waveforms for analogue circuits. It also requires the simulation tools to support this kind of reliability models. One will need a transistor-level AFE design in advanced CMOS technologies to simulate ageing. And the parameters for the reliability model in advanced CMOS technologies are very difficult to obtain because they are often company-confidential information. As a result, dependable AMS IPs, especially the AFEs, are still open areas which are rarely touched.

The previous issues are our motivation to make a firm step in this area by studying the ageing of AFEs, finding weaknesses in AFE circuits and proposing solutions for designing highly dependable AFEs.

## 1.3 Industrial Platform in the TOETS and ELESIS Framework

Basis of this thesis is a European research project named "Towards One European Test Solution (TOETS)". The TOETS project had the ambition to create a breakthrough in methods and flows used by the test technologies in terms of considering test in the whole value chain from design to application [Cat09].

The University of Twente was involved in two tasks defined in TOETS to develop dependable heterogeneous circuits and systems at both circuit level and system level. This thesis is partly the result of the project which targeted at the *circuit level*.

The TOETS project generated a lot of fruitful achievements. A dependable OpAmp has been designed and demonstrated in the project which can self-monitor and self-repair its ageing degradations. However, the solution that was demonstrated consumed a lot of power and much area overhead as the resulting circuits were complex. It is less attractive if an SoC has multiple of these dependable OpAmps. As a result it remained the question whether there was a better solution to reduce the overhead and make the solution both simple as well as generic.

The Eniac "European Library-based flow of Embedded Silicon test Instruments (ELESIS)" European project was successor of TOETS and provided a good opportunity to elevate the previous problems. The ELESIS European project was aimed to define and standardise built-in chip test features with a common interface that will enable the identification of faults relatively inexpensively and thus reduce production costs. The primary targets were IPs containing analogue, radio frequency and sensor components, as they are particularly difficult to isolate for an analysis of the test parameters [Eni12].

The University of Twente had a task in ELESIS which was the creation of embedded dependability instruments and their models operating on Analogue/Mixed-Signal (AMS) IPs. The instruments targeted the ageing monitoring of critical AMS blocks in SoCs. The instrument outputs could be used for adaptive correction of the building block performances over their operational lifetime.

Our contribution has been on circuit design, simulation and advancements in dependability technology methods as treated in this thesis. Three new embedded instruments developed by us have been added to the open European library for embedded instruments. They monitor 8 Introduction

the ageing behaviour of an OpAmp (offset shift), MOST ageing behaviour (threshold shift) and ADC ageing (timing and offset shifts). The designed embedded instruments are general purpose IPs which not only can be used as online ageing monitor but can also be used in a final product test. The designed embedded instruments can be shared by several IPs in the SoC (IP level) and solve the power and area overhead problem as resulted from the TOETS project. The final results of the ELESIS project turned out to be very successful [Wan15].

#### 1.4 Research Questions

Since there are only a few references to dependable AFEs, the project research is required to start from scratch. First, the ageing simulation platform for analogue circuits has to be established to evaluate analogue circuit-reliability. Furthermore, an AFE target vehicle (test circuit) is required to be designed for evaluation purposes. Next, solutions for highly dependable AFEs have to be proposed based on the previous evaluation results.

Overall, the following research questions have to be answered:

- What is the dominating ageing effect in advanced CMOS technologies?

- Can a ageing model be developed which can handle arbitrary stress waveforms in analogue circuits? How to obtain the model parameters?

- Is there a ageing simulation tool/environment which can incorporate our ageing model and how to perform validation?

- What should be is our target-vehicle AFE for carrying out ageing simulations and exploring weaknesses?

- What is best solution to construct a highly dependable AFE?

These questions will be answered in the remaining of this thesis and in particular in Chapter 7.

#### 1.5 Outline of the Thesis

The organization of this thesis is now described in more detail.

Chapter 1 provided an introduction to the thesis: background, definition of dependable systems, and mission profiles of automotive products. The motivation for our research has been presented and this has distilled into a number of research questions. Two European projects, TOETS and ELESIS, were the enablers for this thesis.

In the following Chapter 2, a thorough overview with respect to the current status of dependable analogue/mixed-signal research is given. The limitations and critical parts are being discussed. Based on chapter 2, the lack of tools for analogue circuit ageing simulation is seen as a major limitation for dependable analogue/mixed-signal circuit design.

As a result, a new Negative Bias Temperature Instability (NBTI) model is proposed to assist analogue circuit NBTI simulation in Chapter 3. A new simulation tool based on the proposed NBTI model is implemented in the Cadence Analogue Design Environment (ADE) while using the Verilog-A language. In order to measure p-type Metal-Oxide-Semiconductor Transistor (PMOST) threshold voltages and extract NBTI parameters, a new model for the nanometer MOST drain current is proposed. This new drain current model makes it possible to design an Embedded Instrument (EI) for on-line monitoring the MOST threshold voltage.

Chapter 4 focusses on analogue OpAmps. Reliability simulations are carried out on a target OpAmp which is designed in Taiwan Semiconductor Manufacturing Company (TSMC) 65nm low power digital CMOS technology. Two repair strategies are shown in Chapter 4. The first one is by a programmable OpAmp, while the second is employing an offset and gain Embedded Instrument (EI).

Chapter 5 deals with analogue active filters. The ageing simulations are carried out on three kinds of active filters in TSMC 65nm low power digital CMOS technology. The same two repair strategies as discussed in chapter 4 are demonstrated. We show the design of an active filter circuit and as well as an EI for enhancing its reliability.

In Chapter 6, mixed-signal Successive-Approximation Register (SAR) ADCs are the subject of interest. The ageing simulations are carried out on an own designed 10-bits SAR ADC and each of the sub blocks. All circuits are designed in TSMC 65nm low power digital CMOS technology. The circuit design effort for the ADC repair strategy as well as the EI effort are presented and the results are demonstrated.

Chapter 7 will provide the conclusions with respect to the research. The research questions as posed in Chapter 1 will be answered. Original contributions resulting from this research will be provided too. Also limitations of the current work will be dealt with. Recommendations for future works are also provided. Finally, all papers published by the author are listed explicitly.

#### References

- [Aut07] Automotive Electronics Council. "Failure mechanism based stress test qualification for integrated circuits". *Available at http://www.aecouncil.com/Documents/AEC\_Q100\_Rev\_G\_Base\_Document.pdf*, 2007.

- [Cat09] Catrene. "TOETS Towards one European test solution". *Available at http://www.catrene.org/web/downloads/profiles\_catrene/CT302-TOETS-projectprofile-final*(7-6-11).pdf, 2009.

- [Ely14] C. Ely. "The life expectancy of electronics". *Available at https://www.cta.tech/News/Blog/Articles/2014/September/The-Life-Expectancy-of-Electronics.aspx*, 2014.

- [Eni12] Eniac. "ELESIS European library-based flow of embedded silicon test instruments". *Available at https://cordis.europa.eu/project/rcn/201958\_en.html*, 2012.

- [Int06] International Electrotechnical Commission. "Guidance on system dependability specifications", 2006. IEC Standard 62347.