# Gate Oxide Reliability of Poly-Si and Poly-SiGe CMOS devices

Vincent E. Houtsma

#### CIP-GEGEVENS KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Title : Gate Oxide Reliability of Poly-Si and Poly-SiGe CMOS devices

Author : Houtsma, Vincent Etienne

ISBN : 90-365-1391-X

Keywords : IC-Technology, Semiconductors, Gate Oxide Reliability, Silicon-Germanium, Stress-Induced Leakage Current(SILC), Gate Oxide Breakdown, Light Emission

©1999 by Vincent E. Houtsma, Enschede, The Netherlands.

This research was financially supported by the Dutch Foundation for Fundamental Research on Matter (FOM).

### GATE OXIDE RELIABILITY OF POLY-SI AND POLY-SIGE CMOS DEVICES

### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, Prof.dr. F.A. van Vught, volgens besluit van het College voor Promoties in het openbaar te verdedigen op vrijdag 14 januari 2000 te 16.45 uur.

$\operatorname{door}$

### Vincent Etienne Houtsma

geboren op 12 september 1970 te Sneek

Dit proefschrift is goedgekeurd door: de promotor: Prof. dr. P.H. Woerlee de assistent promotor: Dr. J. Holleman

'There's Plenty of Room at the Bottom' Richard P. Feynman (1918-1988) Samenstelling van de promotie commissie :

| <i>Voorzitter</i> :          |                                                |

|------------------------------|------------------------------------------------|

| Prof. dr. J. Greve           | Universiteit Twente                            |

| Secretaris:                  |                                                |

| Prof. dr. J. Greve           | Universiteit Twente                            |

| Promotor :                   |                                                |

| Prof. dr. P.H. Woerlee       | Universiteit Twente/Philips Research           |

| $Assistent\ promotor$ :      |                                                |

| Dr. J. Holleman              | Universiteit Twente                            |

| Leden:                       |                                                |

| Prof. dr. H. E. Maes         | IMEC, Leuven, Belgie                           |

| Prof. dr. ir. J. W. Slotboom | Philips Research/Technische Universiteit Delft |

| Prof. dr. ir. F. G. Kuper    | Philips Semiconductors/Universiteit Twente     |

| Prof. dr. ir. A. J. Mouthaan | Universiteit Twente                            |

| Dr. ir. V. Zieren            | Philips Research                               |

|                              |                                                |

#### Cover Design :

Picture taken by W. Faber in co-operation with VEROMCO Saint-Gobain Glass Solutions.

O1999 by Vincent E. Houtsma, Enschede, The Netherlands.

### Voorwoord

De kwaliteit van een proefschrift hangt voor een groot gedeelte af van de beschikbare middelen en de aanwezigheid van stimulerende mensen. De afgelopen vier jaar wist ik mij omringd door mensen die ieder op hun eigen manier tot de kwaliteit van dit proefschrift hebben bijgedragen. Velen hebben bovendien een actief aandeel gehad in het onderzoek en de totstandkoming van dit proefschrift.

Een aantal van hen wil ik hier graag speciaal noemen :

- In de eerste plaats mijn promotor Pierre Woerlee. Zijn inzet, enthousiasme en goede kennis op het vakgebied hebben in hoge mate de kwaliteit van dit proefschrift bevorderd. Bovendien gaf hij mij de 'artistieke' vrijheid om mijn eigen ideeën te ontwikkelen en om mij als zelfstandig onderzoeker te kunnen ontplooien. Pierre bedankt !

- Jisk Holleman, mijn assistent promotor. Mede door zijn enthousiasme is er een samenwerking ontstaan tussen ICE en TDM micro-mechanica en worden de lichtemissie metingen aan nanometer-schaal diodes voortgezet. Zijn onvermoeibaar opbouwende kritische houding aan het eind van mijn promotie hebben er toe geleid dat het geheel, en met name de conclusies, nog eens kritisch onder de loep genomen werden.

- Victor Zieren, die onmiddellijk bereid was om zijn opstelling en tijd beschikbaar te stellen voor lichtemissie metingen. En in een later stadium bereid was mijn papers nog eens kritisch door te lezen en deel te nemen in mijn promotiecommissie.

- Carolien de Graaf, waar ik vooral in het begin van mijn onderzoek naar antifuses en diode-antifuses mee te maken had. Haar bereidwilligheid om op al mijn vragen snel en duidelijk antwoord te geven zijn van groot belang geweest voor de resultaten in hoofdstuk 5 van dit proefschrift.

- De studenten Priscilla Boos (antifuses), Andre Hof (SILC), Izaäk de Haan (p<sup>+</sup>-poly gates) en Johan Ditmar (t<sub>bd</sub> dunne oxides) voor de plezierige samenwerking en bijdragen aan het onderzoek.

- De mensen van Philips Nat. Lab. voor het beschikbaar stellen van wafers : Jurriaan Schmitz, Peter Stolk, Anja van Brandenburg, Andre Montree en Herbert Lifka. Zonder jullie wafers was veel van dit werk virtual reality gebleven !

- Tom Aarnink, Gerrit Boom, Arie Kooy, Eddy Ruiter en Ronald Dekker voor hun assistentie bij het vervaardigen van mijn devices in de MESA cleanroom.

- Cora Salm voor het beschikbaar stellen van 'haar poly-GeSi' wafers.

- Henk de Vries voor het oplossen van allerlei meet problemen.

- Frans Widdershoven voor de tip om eens te kijken naar Minority Carrier Tunneling.

- Marcel van den Berg, Jan Slotboom en Lis Nanver met wie ik de afgelopen vier jaar heb samengewerkt op het gebied van antifuses en diode-antifuses.

- Jaap Glas voor het verzorgen van de planten en Jip, Janneke, Floppy, Amiga en Remi als wij weer eens op 'vakantie' waren.

- Alle vrienden, collega's en familie die mij omringden met goede zorgen.

- Het voordeel van een dubbelpromotie is dat de ander precies begrijpt wat je doormaakt. Echter het is daardoor soms ook lastig om de spirit erin te houden als je beide druk bezig bent met je eigen promotie. Ik wil daarom Dora extra bedanken voor de steun en bemoedigende woorden, ondanks het feit dat ze zelf ook moest promoveren. Dora dubbel bedankt !

Víncent Houtsma

Enschede, December 1999.

### Samenvatting

Dit proefschrift behandelt de betrouwbaarheid van silicium-oxide lagen in moderne CMOS transistoren met polykristallijn silicium (poly-Si) en polykristallijn silicium-germanium (poly-SiGe) als gate materiaal. De lekstromen en degradatie van deze oxide lagen met zowel p-type als n-type gate materiaal is onderzocht. Poly-SiGe is gebruikt vanwege de mogelijkheid om de werkfunctie van de gate te kunnen varieëren. De invloed van de werkfunctie op de lekstromen en degradatie van de oxide lagen kan hierdoor onderzocht worden. Belangrijk hierbij te noemen is dat poly-SiGe verenigbaar is met de reeds bestaande Si technologie.

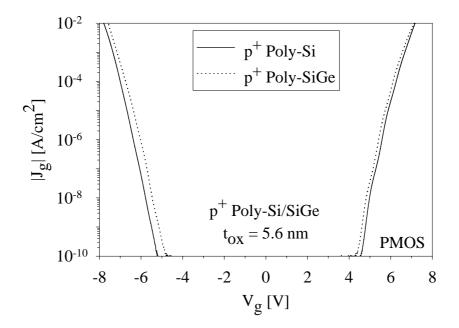

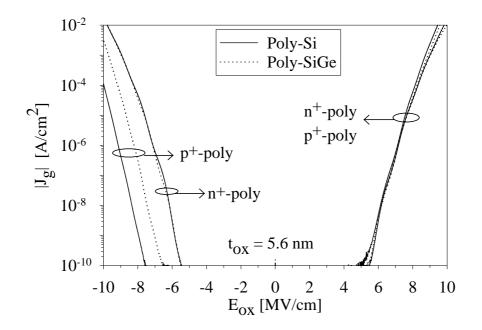

Hoofdstuk 2 laat zien dat de lekstromen voor p-type gates significant anders zijn dan voor n-type gates. Een nieuw model is ontwikkeld dat is gebaseerd op tunneling van minderheidsladingsdragers uit de geleidingsband van de gate om de gemeten stroom-spannings karakteristieken (I-V) van p-type gates te kunnen verklaren.

In hoofdstuk 3 wordt de stress-geïnduceerde lekstroom (SILC) van deze componenten onderzocht. Het verschil in lekstroom tussen p-type en n-type gates heeft ook invloed op de SILC karakteristieken. Voor p-type gates is gevonden dat de SILC asymmetrisch van aard is. Verder is een lagere stress-geïnduceerde lekstroom voor p-type poly-SiGe gevonden in vergelijking met de poly-Si gates. Voor silicium-oxide lagen met een dikte kleiner dan 4 nm is een nieuw geleidingsmechanisme vastgesteld. Voor kleine negatieve gate spanningen wordt de SILC stroom in deze dunne oxides zeer waarschijnlijk bepaald door trap geassisteerd tunnelen van gaten (HTAT). Een inelastisch trap geassisteerd tunnel model is ontwikkeld voor zowel p-type als n-type gates. Dit model kan de gemeten karakteristieken na SILC goed beschrijven.

De doorslag van de silicium-oxide lagen is onderzocht in hoofdstuk 4. Het is vastgesteld dat voor zeer dunne oxides (2.5 nm) de tijd tot doorslag significant afneemt (4 ordes van grootte) als de omgevings-temperatuur toeneemt van 25°C naar 200°C. Dit heeft een grote invloed op de betrouwbaarheid van dunne silicium-oxide lagen. Verder is gevonden dat voor n-type gates de aangelegde gate spanning zich goed verhoudt met de tijd tot doorslag van dunne oxide lagen. Voor p-type gates is een toename van de tijd tot doorslag met toenemende gate temperatuurbudget gevonden. Dit wordt waarschijnlijk veroorzaakt door de afname van de lekstroom met toenemende gate temperatuurbudget voor een constante gate spanning. Dit geeft aan dat zowel de energie van de elektronen als de elektronen stroom van belang zijn voor de tijd tot doorslag van zeer dunne oxide lagen. In hoofdstuk 5 worden de stroom-spannings karakteristieken (I-V) van n-type poly-Si capaciteiten na doorslag onderzocht. Het is vastgesteld dat na hardedoorslag de I-V karakteristieken volledig bepaald worden door de afmetingen van de verbinding die gevormd wordt tussen de gate en het substraat tijdens doorslag. De totale hoeveelheid vrijgekomen energie tijdens doorslag is hiervoor bepalend. Een elektrisch-thermisch model is ontwikkeld welke de gemeten I-V karakteristieken na doorslag goed kan verklaren. Voor zeer lage vermogens dissipatie kan zachte-doorslag optreden. De I-V karakteristieken na zachte-doorslag duiden erop dat het geleidingsmechanisme na zachte-doorslag asymmetrisch van aard is. Echter het geleidingsmechanisme na zachte doorslag is nog niet volledig begrepen.

Tenslotte zijn in hoofdstuk 6 lichtemissie metingen gedaan aan n-type poly-Si gate capaciteiten na doorslag. Deze licht emissie metingen geven belangrijke informatie over de verbinding die gevormd is tussen de gate en het substraat na doorslag.

### Abstract

This thesis focuses on the gate oxide reliability of poly silicon (poly-Si) and poly Silicon-Germanium(poly-Si<sub>0.7</sub>Ge<sub>0.3</sub>) dual gate CMOS devices. The conduction mechanism (I-V), Stress-Induced Leakage Current (SILC) and time-tobreakdown ( $t_{bd}$ ) of these devices on (ultra-)thin gate oxides is studied. P<sup>+</sup> and n<sup>+</sup>-gates with poly-Si and poly-SiGe are used to study the influence of gate workfunction on gate current and SILC current. Poly-SiGe is chosen since its allows modification of the workfunction of the gate for p<sup>+</sup>-poly gate devices. Moreover, it is fully compatible with (poly-)Si technology.

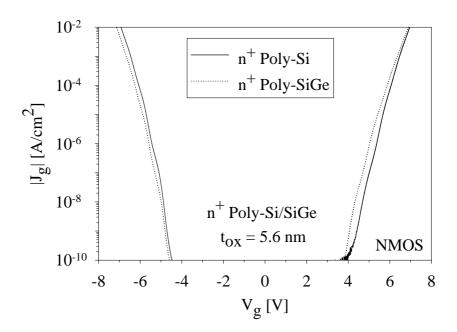

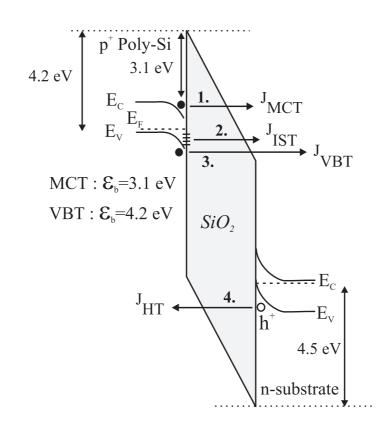

In chapter 2 it is observed that for  $p^+$  gate devices the conduction mechanism is significantly different than for  $n^+$  gate devices. A new model based on Minority Carrier Tunneling(MCT) from the conduction band of the gate is proposed for  $p^+$ -poly gate devices under gate injection conditions  $(-V_g)$ . This model describes the observed I-V curves and gate bias asymmetry for  $p^+$ -poly gate devices.

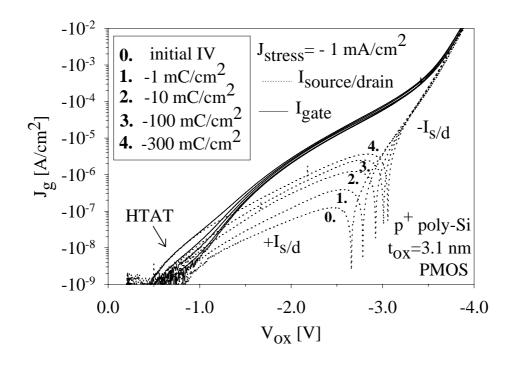

Next in chapter 3 the Stress-Induced Leakage Current of these devices is studied. The difference in conduction mechanism for  $n^+$  and  $p^+$  gate devices influences the SILC characteristics. For  $p^+$ -poly gate devices, asymmetric SILC (gate bias polarity) and reduced SILC for  $p^+$  poly-SiGe compared to the  $p^+$  poly-Si reference devices is observed. For very thin oxides ( $t_{ox} < 4$  nm) the SILC current at low  $-V_g$  voltages is most likely caused by trap assisted hole tunneling (HTAT) from the substrate to the gate. An inelastic trap assisted tunneling model is developed to evaluate the SILC current for both  $n^+$  and  $p^+$  gate devices under substrate as well as gate injection conditions. This model is successful in describing the experimental I-V characteristics after SILC.

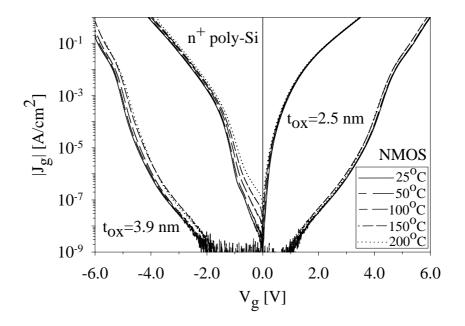

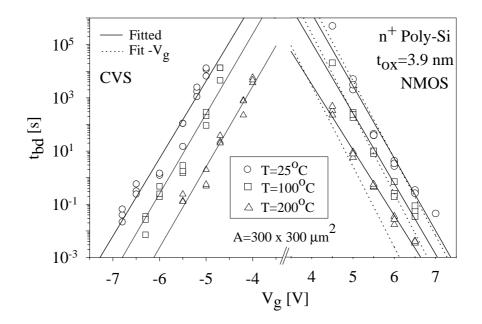

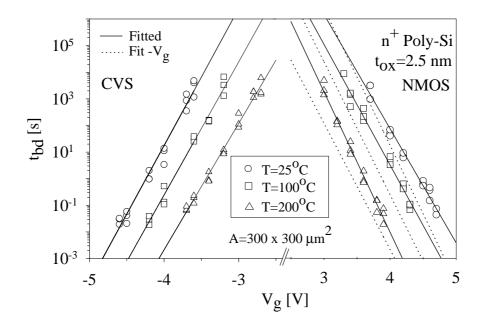

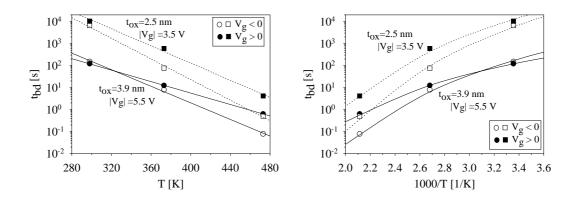

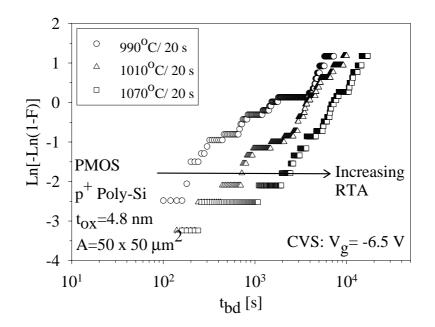

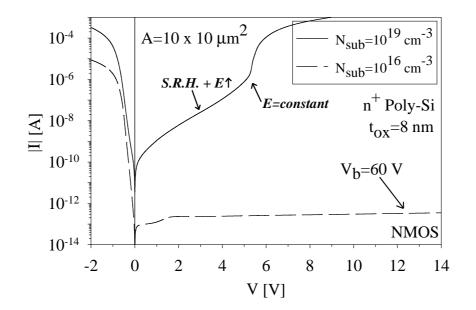

The time-to-breakdown of both  $n^+$  and  $p^+$  poly-Si gate devices on ultra-thin gate oxides is studied in chapter 4. A decrease in  $t_{bd}$  of nearly 4 orders of magnitude is observed when the ambient temperature is increased from  $25^{\circ}$ C to  $200^{\circ}$ C for  $n^+$  poly-Si gate devices on 2.5 nm oxides. It is observed that for  $n^+$  gate devices the applied gate voltage  $V_g$  correlates well with  $t_{bd}$  under substrate as well as gate injection conditions. For  $p^+$ -poly Si gate devices an increase of  $t_{bd}$ with increasing active gate doping is observed. This is most likely related to a decrease in tunneling current during stress at a fixed gate voltage. This indicates that both the total energy release at the anode and the electron fluence are important parameters for  $t_{bd}$  of ultra-thin oxides.

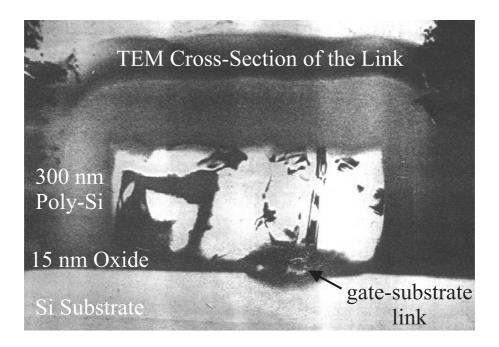

In chapter 5 the post-breakdown I-V characteristics of  $n^+$  poly-Si NMOS gate devices are studied. It is observed that the I-V characteristics after hard-breakdown are determined by the filament cross-section formed through the emission of en-

ergy stored in the MOS capacitor before breakdown. An electro-thermal model is developed which is successful in explaining the measured post hard-breakdown I-V characteristics. The dependence on the physical parameters involved in the breakdown process is also examined. At very low power dissipation softbreakdown may occur. The I-V characteristics after low power breakdown suggest that the conduction mechanism is asymmetric with respect to gate bias polarity. However the conduction mechanism after low power breakdown is still poorly understood.

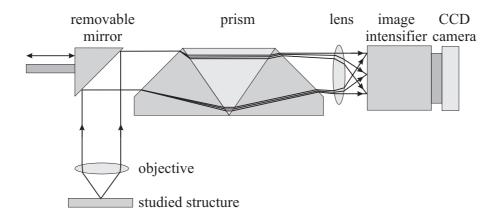

Finally, in chapter 6 light emission measurements are performed on  $n^+$  poly-Si NMOS gate devices after breakdown. These light emission measurements reveal important information about the physical properties of the link formed after breakdown.

# Contents

| No       | omen  | lature                                                         | $\mathbf{V}$ |

|----------|-------|----------------------------------------------------------------|--------------|

| Li       | st of | acronyms                                                       | ix           |

| 1        | Intr  | oduction                                                       | 1            |

|          | 1.1   | Introduction                                                   | 1            |

|          | 1.2   | Oxide degradation, reliability and lifetime                    | 2            |

|          | 1.3   | Physical mechanisms of oxide degradation                       | 4            |

|          | 1.4   | Problem definition: Basic principles                           | 7            |

|          | 1.5   | Research objectives                                            | 10           |

|          | 1.6   | Outline of this thesis                                         | 12           |

| <b>2</b> | The   | poly-Si and poly-SiGe CMOS I-V characteristics                 | 15           |

|          | 2.1   | Introduction                                                   | 15           |

|          | 2.2   | Experimental Procedures                                        | 17           |

|          | 2.3   | C-V measurements on poly-Si and poly-SiGe MOS capacitors       | 18           |

|          | 2.4   | Charge carrier transport through thin oxides                   | 23           |

|          |       | 2.4.1 I-V measurements on poly-Si and poly-SiGe MOS capacitors | 24           |

|          |       | 2.4.2 Minority Carrier Conduction Model for $p^+$ gate devices | 35           |

|          | 2.5   | Conclusions                                                    | 42           |

| 3        | SIL   | C in poly-Si and poly-SiGe CMOS capacitors                     | 43           |

|          | 3.1   | Introduction                                                   | 43           |

|          | 3.2   | Physical nature of SILC                                        | 45           |

|          |       | 3.2.1 Dependence of SILC on stress conditions                  | 46           |

|          | 3.3   | SILC in $n^+$ poly-Si and poly-SiGe gate devices               | 49           |

|          |       | 3.3.1 Experimental Procedures                                  | 49           |

|          |       | 3.3.2 Gate and substrate injection conditions                  | 49           |

|          |       | 3.3.3 Field dependence of SILC in $n^+$ -poly gate devices     | 51           |

|          |       | 3.3.4 Summary                                                  | 52           |

|          | 3.4   | SILC in $p^+$ poly-Si and poly-SiGe gate devices               | 54           |

|          |       | 3.4.1 Experimental Procedures                                  | 54           |

|          |       | 3.4.2 Gate and substrate injection conditions                  | 54           |

|          |     | 3.4.3 Stress injection bias polarity dependence                                     | 56 |

|----------|-----|-------------------------------------------------------------------------------------|----|

|          |     | 3.4.4 SILC generation rate in $p^+$ gate devices $\ldots \ldots \ldots$             | 58 |

|          |     | 3.4.5 Field dependence of SILC in $p^+$ -poly gate devices                          | 60 |

|          |     | 3.4.6 Trap assisted hole tunneling(HTAT) in p <sup>+</sup> -poly gate devices       | 62 |

|          |     | 3.4.7 Gate injection conditions                                                     | 62 |

|          |     | 3.4.8 Summary                                                                       | 62 |

|          | 3.5 | SILC in F implanted $n^+$ poly-Si gate devices $\ldots \ldots \ldots \ldots \ldots$ | 64 |

|          |     | 3.5.1 Experimental Procedures                                                       | 64 |

|          |     | 3.5.2 Effect of F on the gate oxide thickness                                       | 65 |

|          |     | 3.5.3 Gate injection conditions                                                     | 66 |

|          |     | 3.5.4 Summary                                                                       | 69 |

|          | 3.6 | Modeling of the SILC characteristics                                                | 69 |

|          |     | 3.6.1 A simple two-step tunneling model                                             | 73 |

|          |     | 3.6.2 Model verification                                                            | 75 |

|          | 3.7 | Conclusions                                                                         | 81 |

| 4        | Gat | te oxide breakdown of $n^+$ and $p^+$ poly-Si gate devices                          | 83 |

|          | 4.1 | _                                                                                   | 83 |

|          | 4.2 |                                                                                     | 84 |

|          | 4.3 | -                                                                                   | 85 |

|          |     |                                                                                     | 85 |

|          |     |                                                                                     | 87 |

|          | 4.4 |                                                                                     | 90 |

|          | 4.5 |                                                                                     | 92 |

| <b>5</b> | I-V | characteristics of $n^+$ poly-Si gate devices after breakdown                       | 93 |

| 0        | 5.1 | _                                                                                   | 93 |

|          | 5.2 |                                                                                     | 95 |

|          | 5.3 |                                                                                     | 95 |

|          | 5.4 | I-V characteristics after breakdown                                                 | 00 |

|          | 0.1 |                                                                                     | 97 |

|          | 5.5 |                                                                                     | 98 |

|          | 0.0 |                                                                                     | 99 |

|          |     |                                                                                     | 05 |

|          |     |                                                                                     | 07 |

|          |     | 0                                                                                   | 10 |

|          | 5.6 | I-V characteristics after breakdown                                                 |    |

|          |     | Part II: non-linear characteristics                                                 | 10 |

|          |     |                                                                                     | 11 |

|          |     |                                                                                     | 15 |

|          |     | 5.6.3 Summary                                                                       |    |

|          | 5.7 | I-V characteristics after soft breakdown                                            |    |

|    |       | 5.7.1 Summary                                           | 123 |

|----|-------|---------------------------------------------------------|-----|

|    | 5.8   | Conduction mechanism after soft and low power breakdown | 123 |

|    |       | 5.8.1 Summary                                           |     |

|    | 5.9   | Antifuses versus diode-antifuses                        |     |

|    | 5.10  | Conclusions                                             |     |

| 6  | Ligh  | nt emission from diode-antifuses                        | 131 |

|    | 6.1   | Introduction                                            | 131 |

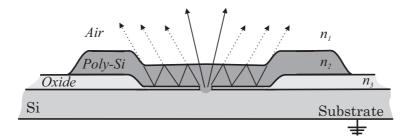

|    | 6.2   | Experimental Procedures                                 | 133 |

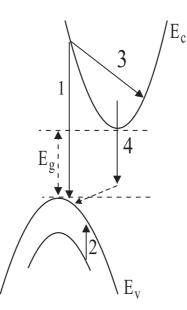

|    | 6.3   | Principle of Operation                                  |     |

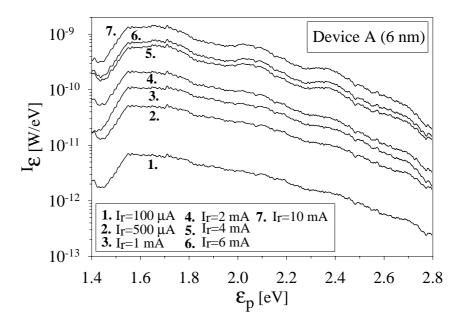

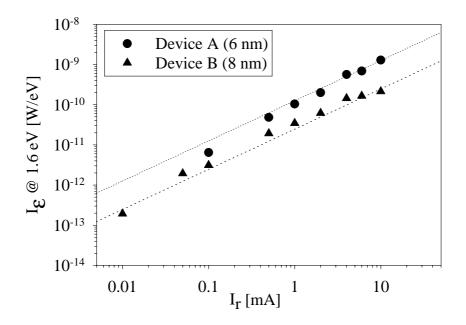

|    | 6.4   | Reverse biased emission spectrum                        |     |

|    | 6.5   | Modeling of the reverse emission spectrum               |     |

|    | 6.6   | Forward biased emission spectrum                        |     |

|    | 6.7   | Stability of the reverse emission spectrum              |     |

|    | 6.8   | Conclusions                                             |     |

| 7  | Con   | clusions and Recommendations                            | 145 |

|    | 7.1   | Summary                                                 | 145 |

|    | 7.2   | Conclusions and Directions for further research         |     |

|    |       | 7.2.1 Conduction mechanism for $p^+$ gate devices       |     |

|    |       | 7.2.2 Lifetime prediction of $SiO_2$                    |     |

|    |       | 7.2.3 Conduction mechanism after breakdown              |     |

|    |       | 7.2.4 SiO <sub>2</sub> the final frontier ?             |     |

| Li | st of | publications                                            | 171 |

#### iii

## Nomenclature

| $\operatorname{symbol}$ | description                                               | unit                           |

|-------------------------|-----------------------------------------------------------|--------------------------------|

|                         |                                                           |                                |

| А                       | capacitor area                                            | $[cm^{-2}]$                    |

| A                       | pre-exponential factor in the FN-tunneling expression     | $[A/MV^2]$                     |

| $\mathrm{A}'$           | pre-exponential factor in the direct tunneling expression | $[A/MV^2]$                     |

| a                       | pre-power law factor in the soft-breakdown                |                                |

|                         | I-V characteristics expression                            | [A/V]                          |

| В                       | exponential factor in the FN-tunneling expression         | $[\mathrm{cm/MV}]$             |

| $\mathbf{B}'$           | exponential factor in the direct tunneling expression     | $[\mathrm{cm/MV}]$             |

| b                       | power law factor in the soft-breakdown                    |                                |

|                         | I-V characteristics expression                            | [-]                            |

| С                       | capacitance per unit area                                 | [F/cm]                         |

| $C_{gate}$              | gate surface capacitance per unit area                    | [F/cm]                         |

| $\tilde{C}_{MOS}$       | total capacitance of the MOS structure,                   |                                |

|                         | $C_{MOS} = C_{ox} + C_{par}$ per unit area                | [F/cm]                         |

| $C_{ox}$                | oxide layer capacitance per unit area                     | [F/cm]                         |

| $C_{par}$               | parasitic capacitance of the MOS structure per unit area  | [F/cm]                         |

| $\hat{\mathbf{C}_{it}}$ | interface trap capacitance                                | $[cm^{-2}eV^{-1}]$             |

| $C_{sub}$               | substrate surface capacitance per unit area               | [F/cm]                         |

| $\mathrm{C}_t$          | heat capacity per unit volume                             | $[J/K \cdot cm^3]$             |

| $D_{it}$                | density of oxide interface traps                          | $[{\rm cm}^{-2}{\rm eV}^{-1}]$ |

| $D_{ot}$                | volume density of neutral electron traps in the oxide     | $[\mathrm{cm}^{-3}]$           |

| $\mathbf{D}_{ot,crit}$  | critical volume density of neutral electron traps         |                                |

|                         | in the oxide                                              | $[\mathrm{cm}^{-3}]$           |

| $\mathrm{D}_{th}$       | thermal diffusivity of silicon                            | $[{\rm cm}^2 {\rm s}^{-1}]$    |

| $\mathbf{E}_{c}$        | electric field strength across the gate-substrate link    | [V/cm]                         |

| $E_{bd}$                | breakdown electric field                                  | [MV/cm]                        |

| $E_{ox}$                | electric field strength across the dielectric layer       | [MV/cm]                        |

| f                       | occupation probability of the neutral traps in the oxide  | [-]                            |

| Η                       | heat generation per unit volume                           | $[W/cm^3]$                     |

| $I_p$                   | programming current                                       | [mA]                           |

| $I_s$                   | stress current                                            | [mA]                           |

| $I_{bd}$                | current during breakdown of the gate oxide                | [mA]                           |

| $I_{cap}$               | capacitor discharge current during breakdown              |                                |

|                         | of the gate oxide                                         | [mA]                           |

| $I_{\mathcal{E}}$       | optical intensity of the spectrum                         | [W/eV]                         |

| $J_c$                   | electron current density inside the gate-substrate link   | $[A/cm^2]$                     |

| $\mathbf{J}_{DT}$       | Direct Tunneling current density                          | $[A/cm^2]$                     |

| $J_{et}$                | Esaki-Tsu formula for tunneling current density           | $[A/cm^2]$                     |

| $\mathbf{J}_{FN}$       | Fowler-Nordheim tunneling current density                 | $[A/cm^2]$                     |

|                         |                                                           |                                |

| $\mathrm{J}_g$           | gate current density                                          | $[\mathrm{A/cm^2}]$             |

|--------------------------|---------------------------------------------------------------|---------------------------------|

| $J_{in}$                 | electron current density per unit film thickness              | 2                               |

|                          | flowing into a neutral trap in the oxide                      | $[A/cm^3]$                      |

| $\mathbf{J}_{IST}$       | Interface State Tunneling current density                     | $[A/cm^2]$                      |

| $\mathbf{J}_{MCT}$       | Minority Carrier Tunneling current density                    | $[A/cm^2]$                      |

| $\mathbf{J}_{out}$       | electron current density per unit film thickness              |                                 |

|                          | flowing out of a neutral trap in the oxide                    | $[A/cm^3]$                      |

| ${ m J}^{ac}_{silc}$     | transient component of the Stress-Induced Leakage             |                                 |

|                          | Current density                                               | $[A/cm^2]$                      |

| ${ m J}^{dc}_{silc}$     | steady-state component of the Stress-Induced Leakage          |                                 |

|                          | Current density                                               | $[A/cm^2]$                      |

| $\mathrm{J}_{silc}$      | Stress-Induced Leakage Current density                        | $[A/cm^2]$                      |

| $\mathbf{J}_{stress}$    | electrical stress current density                             | $[A/cm^2]$                      |

| $\mathbf{J}_{VBT}$       | Valence Band Tunneling current density                        | $[A/cm^2]$                      |

| k                        | Boltzmann's constant ( $k=8.62 \cdot 10^{-5} \text{ eV/K}$ )  | [eV/K]                          |

| $k_2$                    | extinction coefficient (absorption) of                        | - , -                           |

|                          | the poly-silicon layer                                        | [-]                             |

| $L_{th}$                 | dimension of the volume being heated during breakdown         | [nm]                            |

| m                        | electron rest mass $(m=9.11 \cdot 10^{-31} \text{ kg})$       | [kg]                            |

| $\mathbf{m}_d$           | density-of-state mass in the gate material                    | [kg]                            |

| $\mathbf{m}^*$           | electron effective mass in $SiO_2$ (m <sup>*</sup> =0.34 · m) | [kg]                            |

| n                        | the p-n junction quality factor                               | [-]                             |

| $n_v$                    | valley degeneracy in the gate material                        | [-]                             |

| $n_{1,2,3}$              | refractive index of resp. air, poly-silicon and oxide layer   | [-]                             |

| N <sub>poly</sub>        | electrically active doping concentration of gate              | $[\mathrm{cm}^{-3}]$            |

| $N_{sub}$                | substrate doping concentration                                | $\left[\mathrm{cm}^{-3}\right]$ |

| Р                        | total electrical power                                        | [W]                             |

| $P_{g}$                  | defect generation rate of neutral oxide traps                 | $[cm^{-1}/C]$                   |

| $P_g^{g}(silc)$          | Stress Induced Leakage Current generation rate                | $\left[ cm^2/C \right]$         |

| q                        | elementary charge (q=1.60 $\cdot$ 10 <sup>-19</sup> C)        | [C]                             |

| Q                        | total charge stored on the capacitor                          | [C]                             |

| $\mathbf{Q}_{bd}$        | total injected electron fluence at breakdown                  | $[C/cm^2]$                      |

| $\mathbf{Q}_f$           | fixed oxide trapped charge                                    | $[cm^{-2}]$                     |

| $\mathbf{Q}_{g}$         | gate charge per unit area                                     | $[C/cm^2]$                      |

| $\mathbf{Q}_{inj}$       | total injected electron fluence during stress                 | $[C/cm^2]$                      |

| r <sub>c</sub>           | core radius of the breakdown site                             | [nm]                            |

| $\ddot{\mathrm{R}}_{bd}$ | total post breakdown resistance                               | $[\Omega]$                      |

| $R_c$                    | resistance of the core of the breakdown site                  | $\left[\Omega\right]$           |

| $\mathbf{R}_{l}$         | total resistance of the gate-substrate link                   | $\left[\Omega\right]$           |

| $\mathrm{R}_{s,tot}$     | total spreading resistance of the gate-substrate link         | $\left[\Omega\right]$           |

| $\vec{S}$                | heat flux per unit area                                       | $[W/cm^2]$                      |

| $T_{amb}$                | ambient temperature                                           | [°C]                            |

| ÷ umu                    | anister omperadi                                              | [~]                             |

| -                   | - · · ·                                                                                          |                |

|---------------------|--------------------------------------------------------------------------------------------------|----------------|

| $T_e$               | effective electron temperature of the electrons                                                  | $[^{\circ}C]$  |

| $T_{inj}$           | temperature during electrical stress                                                             | [°C]           |

| $T_L$               | lattice temperature of silicon                                                                   | [°C]           |

| $T_{meas}$          | temperature during measurement                                                                   | [°C]           |

| $T_{Si}$            | melting temperature of silicon                                                                   | [°C]           |

| $T_{SiO_2}$         | melting temperature of silicon dioxide                                                           | $[^{\circ}C]$  |

| $T^* \cdot T_{in}$  | transmission probability for tunneling into                                                      | r 1            |

| <b>—</b> * <b>—</b> | a neutral trap in the oxide                                                                      | [-]            |

| $T^* \cdot T_{out}$ | transmission probability for tunneling out of                                                    | r 1            |

| <b>T</b> * <b>T</b> | a neutral trap in the oxide                                                                      | [-]            |

| $T^* \cdot T_{WKB}$ | tunneling probability under the WKB approximation                                                | [-]            |

| $\mathrm{t}_{bd}$   | time to breakdown                                                                                | $[\mathbf{s}]$ |

| $\mathrm{t}_{eff}$  | effective thickness over which the TAT tunneling                                                 | r 7            |

|                     | current flows mainly                                                                             | [nm]           |

| $t_{ox}$            | thickness of the dielectric oxide layer                                                          | [nm]           |

| $t_{poly}$          | thickness of the poly-silicon layer                                                              | [nm]           |

| $V_b$               | reverse breakdown voltage of the diode-antifuses                                                 | [V]            |

| V <sub>bd</sub>     | voltage during breakdown of the gate oxide                                                       | [V]            |

| $\mathbf{V}_{c}$    | voltage across the gate-substrate link                                                           | [V]            |

| $V_{fb}$            | flatband voltage                                                                                 | [V]            |

| $V_g$               | gate voltage                                                                                     | [V]            |

| $V_{gate}$          | voltage drop in the gate due to gate depletion                                                   | [V]            |

| Vox                 | voltage across the oxide                                                                         | [V]            |

| $\mathbf{V}_s$      | voltage at stress current $I_s$                                                                  | [V]            |

| $V_{sub}$           | voltage drop in the Si-substrate due to band bending                                             | [V]            |

| $V_t$               | threshold voltage                                                                                | [V]            |

| $X_T$               | most favourable trap position in the oxide                                                       | [nm]           |

| $\alpha$            | oxide quality parameter, $\alpha = \partial ln(D_{ot})/\partial ln(Q_{inj})$                     | [-]            |

| eta                 | oxide quality parameter, $\beta = \partial ln(D_{ot})/\partial ln(J_{stress})$                   | [-]            |

| $\epsilon_{ox}$     | permitivity of SiO <sub>2</sub> ( $\epsilon_{ox}$ =3.45 · 10 <sup>-13</sup> F/cm)                | [F/cm]         |

| $\epsilon_{si}$     | permitivity of Si ( $\epsilon_{si}$ =1.05 · 10 <sup>-12</sup> F/cm)                              | [F/cm]         |

| $\epsilon_r$        | relative permitivity                                                                             | [-]            |

| $\gamma$            | quantum yield of electron impact ionization in Si                                                | [-]            |

| $\kappa$            | thermal conductivity coefficient of silicon                                                      | [W/K·cm]       |

| $\lambda$           | wavelength of the light                                                                          | [nm]           |

| $E_{th}$            | energy threshold marking the boundary between                                                    | r _ 1          |

| _                   | soft-breakdown and hard-breakdown                                                                | [J]            |

| ${\cal E}_a$        | effective anode barrier height, defined as                                                       |                |

| _                   | $\mathcal{E}_a = \mathcal{E}_b + \mathcal{E}_{relax}$ - $\mathrm{qE}_{ox} \cdot \mathrm{t}_{ox}$ | [eV]           |

| $\mathcal{E}_{act}$ | temperature activation energy                                                                    | [eV]           |

| ${\cal E}_b$        | energy barrier height at the $Si/SiO_2$ interface or <i>effective</i>                            | r 1            |

|                     | barrier height to describe SILC as FN tunneling                                                  | [eV]           |

|                     |                                                                                                  |                |

| ${\cal E}_c$                                                      | conduction band edge of Si, SiGe or $SiO_2$                                                          | [eV]                           |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------|

| $E_{dis}$                                                         | total energy released during breakdown                                                               | L J                            |

| are                                                               | of the MOS capacitor                                                                                 | [J]                            |

| ${\mathcal E}_{f}$                                                | fermi level                                                                                          | [eV]                           |

| $\mathcal{E}_{a}$                                                 | band gap of Si, SiGe or $SiO_2$                                                                      | [eV]                           |

| $egin{array}{c} {\cal E}_f \ {\cal E}_g \ {\cal E}_p \end{array}$ | photon energy                                                                                        | [eV]                           |

| ${\mathcal E}_{tr}$                                               | trap energy level with respect to the conduction band                                                | [2,1]                          |

| • 11                                                              | of the $SiO_2$                                                                                       | [eV]                           |

| ${\cal E}_{tr}^*$                                                 | effective trap barrier height, defined as $\mathcal{E}_{tr}^* = \mathcal{E}_b$ - $qE_{ox} \cdot X_T$ | [eV]                           |

| ${\cal E}_v$                                                      | valence band edge of Si, SiGe or $SiO_2$                                                             | [eV]                           |

| ħ                                                                 | reduced Planck constant ( $\hbar$ =6.58 · 10 <sup>-16</sup> eV·s)                                    | $[eV \cdot s]$                 |

| $\phi_{ms}$                                                       | metal-to-semiconductor workfunction difference                                                       | [eV]                           |

| $\rho_{c,g,s}$                                                    | electrical resistivity of resp. the core material of the                                             |                                |

|                                                                   | breakdown site, the polysilicon layer and the substrate                                              | $[\Omega \cdot cm]$            |

| $\sigma_{in}$                                                     | neutral trap capture cross section                                                                   | $[cm^2]$                       |

| $\sigma_{out}$                                                    | neutral trap emission cross section                                                                  | $\left[\mathrm{cm}^{2}\right]$ |

| $	au_{bd}$                                                        | discharging time of the capacitor during breakdown                                                   | [s]                            |

| $	au_{th}$                                                        | time necessity to reach thermal equilibrium                                                          |                                |

|                                                                   | during breakdown                                                                                     | $[\mathbf{s}]$                 |

| $\mathcal{T}(\lambda)$                                            | transmission factor for normal incidence light                                                       |                                |

| × /                                                               | in a three layer system                                                                              | [-]                            |

| χ                                                                 | electron affinity                                                                                    | [eV]                           |

|                                                                   | v                                                                                                    | L J                            |

# List of acronyms

| AC-SILC              | transient component of Stress-Induced Leakage Current    |

|----------------------|----------------------------------------------------------|

| AHI                  | Anode Hole Injection                                     |

| BBT                  | Band to Band Tunneling                                   |

| $\operatorname{BGN}$ | Band Gap Narrowing                                       |

| CCD                  | Charged Coupled Device                                   |

| $\mathbf{CCS}$       | Constant Current Stress                                  |

| CMOS                 | Complementary Metal-Oxide-Semiconductor                  |

| C-V                  | Capacitance - Voltage                                    |

| CVS                  | Constant Voltage Stress                                  |

| DC-SILC              | steady-state component of Stress-Induced Leakage Current |

| DHT                  | Direct Hole Tunneling                                    |

| DOS                  | Density of States                                        |

| DPROM                | Diode Programmable Read Only Memory                      |

| DT                   | Direct Tunneling                                         |

| EEPROM               | Electrically-Erasable Programmable Read-Only Memory      |

| $\operatorname{EL}$  | Electroluminescence                                      |

| $_{\rm FN}$          | Fowler-Nordheim                                          |

| FOM                  | Figure Of Merit                                          |

| HB                   | (Hard) Breakdown                                         |

| $\mathrm{HT}$        | Hole Tunneling                                           |

| HTAT                 | Trap Assisted Hole Tunneling                             |

| IC                   | Integrated Circuit                                       |

| IR                   | Infrared                                                 |

| IST                  | Interface State Tunneling                                |

| ITAT                 | Inelastic Trap Assisted Tunneling                        |

| ITRS                 | International Technology Roadmap for Semiconductors      |

| I-V                  | Current - Voltage                                        |

| J-E                  | Current density - Electric field strength                |

| J-V                  | Current density - Voltage                                |

| LPCVD                | Low Pressure Chemical Vapor Deposition                   |

| MCT                  | Minority Carrier Tunneling                               |

| MOS                  | Metal-Oxide-Semiconductor                                |

| MOSFET               | Metal-Oxide-Semiconductor Field Effect Transistor        |

| NA                   | Numerical Aperture                                       |

| NMOS                 | n-channel Metal-Oxide-Semiconductor                      |

| NVM                  | Non-Volatile Memory                                      |

| OTP                  | One Time Programmable                                    |

| PE                   | external Power Efficiency                                |

| P/E                  | Program/Erase                                            |

| PL                   | Photoluminescence                                        |

| p-channel Metal-Oxide-Semiconductor |

|-------------------------------------|

| Rapid Thermal Anneal                |

| Random Telegraph Noise              |

| Soft Breakdown                      |

| Semiconductor Industry Association  |

| Stress-Induced Leakage Current      |

| Shockley-Read-Hall                  |

| Trap Assisted Tunneling             |

| Transmission Electron Microscopy    |

| Ultraviolet                         |

| Valence Band Tunneling              |

| Variable Range Hopping              |

| Wentzel-Kramers-Brillouin           |

|                                     |

## Chapter 1

# Introduction

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year. Certainly over the short term this rate can be expected to continue, if not increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000.

I believe that such a large circuit can be built on a single wafer."

Gordon E. Moore (1965) [1]

### 1.1 Introduction

The down-scaling of CMOS device dimensions has been the main stimulation for the continuing growth of the microelectronics industry over the past two decades. This trend of steady down-scaling was first formulated by Gordon E. Moore and is better known as Moore's law [1]. In 1965 G. Moore published a semi-log plot of the number of components on a silicon chip versus the date of first availability. The result was a straight line representing almost a doubling per year. In the later years, the rate relaxed somewhat to a doubling every 18 months. This is still the rate of today and it is expected to prevail for some time.

Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs) have been around quite some time now. The main success of these silicon based devices is, apart from the possibility to reduce their dimensions down to almost nanometer scale dimensions, the stable high quality silicon-silicon dioxide interface and their ability to interconnect millions to billions of devices on a single chip to form an integrated circuit (IC). The basic concept of the MOSFET and its operation was already formulated almost seventy years ago [2], even before the experimental discovery of the bipolar junction transistor on December 16, 1947 by J. Bardeen, W. H. Brattain and W. Shockley [3, 4] for which they later received the Nobel Price. However, it was not until 1960 that the first silicon MOSFET was actually realized by Kahng and Atalla [5]. Ironically enough, the main reason for the rather late realization of a functioning MOSFET was that at those days it was very hard to realize an interface between a dielectric layer and a semiconductor which was of very high quality, a requirement for proper MOSFET action.

Today, after many generations of scaling the smallest feature in CMOS devices, that is the gate oxide thickness, is approaching atomic dimensions and fundamental limits imposed by quantum mechanics as off-state leakage current close in on technology. Tunneling currents larger than 1 A/cm<sup>2</sup> are predicted for SiO<sub>2</sub> dielectric layers of 1.5-2 nm thickness. Also the reliability of the gate oxide is becoming a major problem. If the scaling trend continues as predicted by the International Technology Roadmap for Semiconductors (ITRS) [6](see Table 1.1), SiO<sub>2</sub> may not be able to meet future reliability requirements under (normal) operation conditions [7].

| Year of First Shipment    | 1997              | 1999      | 2002      | 2005      | 2008      | 2011             |

|---------------------------|-------------------|-----------|-----------|-----------|-----------|------------------|

| Technology Node           | $250~\mathrm{nm}$ | 180  nm   | 130  nm   | 100  nm   | 70  nm    | $50 \mathrm{nm}$ |

| Eq. Oxide thickness [nm]  | 4-5               | 3-4       | 2-3       | 1.5-2     | <1.5      | <1.0             |

| Maximum Field [MV/cm]     | 4-5               | 5         | 5         | >5        | $>\!5$    | $>\!5$           |

| Supply (gate) voltage [V] | 1.8 - 2.5         | 1.5 - 1.8 | 1.2 - 1.5 | 0.9 - 1.2 | 0.6 - 0.9 | 0.5 - 0.6        |

**Table 1.1:** Equivalent gate oxide thickness, electrical field and largest allowable gate<br/>voltage corresponding to the indicated year of first manufacture and<br/>technology generation. Data taken from the International Technology<br/>Roadmap for Semiconductors (1998 Update version) [6].

A fundamental understanding of the degradation mechanism of ultra-thin  $SiO_2$  layers is therefore of great importance to allow accurate predictions of the reliability for future MOS devices under device operation conditions. Early in the next century state-of the-art MOSFETs will have 1-2 nm gate oxide thickness and will work at supply voltages of 1 V. The reliability of these devices is becoming a major issue. This creates some interesting research challenges to be solved in the near future. Some of them will be addressed in this thesis.

"Fortunately there is still some margin left in today's devices for perhaps a few generations, but how much longer can CMOS scaling continue ?"

### 1.2 Oxide degradation, reliability and lifetime

$SiO_2$  is still beyond any doubt one of the key factors in the success of CMOStechnology. The main reason for this is that for the reliable production of largescale integrated circuits(ICs) it is necessarily to produce by compatible technologies both a semiconductor and an insulator that have superb electrical and mechanical properties. In fact, SiO<sub>2</sub> is a very good insulator with a very large bandgap of around  $\mathcal{E}_g=8-9$  eV [8, 9] and it can be grown very easily and well-controlled on a Si-substrate.

The properties of the oxide-silicon system are fundamental to the performance of integrated-circuit devices and knowledge about these properties has been around for quite a long time know. At present, SiO<sub>2</sub> layers as thin as 1.5 nm can already be made and are used as a gate dielectric in a fully functioning MOSFET with a gate length of 0.1  $\mu$ m [10, 11]. This also displays some of the most powerful properties of SiO<sub>2</sub>, namely its scalebility and process integration capabilities. Nevertheless SiO<sub>2</sub> is not perfect and still suffers from some degradation. Aggressive down-scaling of the gate oxide thickness for future MOS devices however requires that, among other concerns, the gate oxide can still meet requirements for reliability. A fundamental understanding of the degradation mechanism of SiO<sub>2</sub> is therefore of great importance to allow accurate predictions of the reliability for future MOS devices at device operation conditions.

Gate oxide reliability has always been a major issue in determining the feasibility of MOS devices. Especially the reliability of ultra-thin gate dielectrics  $(t_{ox} < 5 \text{ nm})$  is of increasing concern because of the significant direct tunneling currents flowing during normal device operation. The exponentially increase in tunnel current with decreasing oxide thickness will increase the standby power and seriously degrade the gate oxide reliability at operation conditions if the gate voltage is not simultaneously reduced sufficiently. This direct tunneling(DT) current poses a serious problem onto the further down-scaling of the gate oxide thickness for sub-100 nm feature-size technologies. If the scaling trend continues, SiO<sub>2</sub> may not be able to meet future reliability requirements [7, 6]. This means that another material with higher reliability and lower standby tunneling current will be needed <sup>1</sup>.

Ultra-thin gate oxide reliability is therefore a major research topic, but in spite of the large amount of knowledge already gathered on this subject a number of issues are still not resolved. Gate oxide reliability was studied mainly for n-doped polycrystalline silicon (poly-Si) gate material up till now. With the down-scaling of the gate oxide thickness below 10 nm, p<sup>+</sup> poly-Si gate electrodes have been proposed for deep sub-micron gates to replace n<sup>+</sup> poly-Si gates. The main reason for this is that n<sup>+</sup> gate p-channel devices need an additional p-type implantation in the Si-substrate for threshold voltage adjustment. When a voltage is applied between the source and drain it is observed that the minimum in potential barrier is no longer at the surface indicating a buried channel operation [12]. However, p<sup>+</sup> gate p-channel devices do not require an additional implant for threshold

<sup>&</sup>lt;sup>1</sup>To overcome this problem, the Semiconductor Industry Association (SIA) mentions high-  $\epsilon$  dielectrics like Ta<sub>2</sub>O<sub>5</sub> as a possible candidate to replace SiO<sub>2</sub> in sub-100nm feature-size technologies, which should enter production around the year 2006 (1997 version) [6].

voltage adjustment and thus remains a surface channel device.

Surface channel pMOSFETs with  $p^+$  poly-Si gate have several advantages over conventional  $n^+$  poly-Si gate buried-channel pMOSFETs, such as reduced short-channel effects and improved turn-off characteristics [12]. Therefore, for CMOS devices with ultra-thin gate oxides,  $p^+$  gates have been proposed for pchannel MOSFETs to convert the buried channel operation to surface channel operation.

The degradation of  $p^+$  gate devices with ultra-thin gate oxides is therefore also a major concern. However, before studying the degradation of  $p^+$  gate devices it may be instructive to recall the most important models for explanation of oxide degradation as reported in literature and to review the different stages in the breakdown process.

### **1.3** Physical mechanisms of oxide degradation

In literature, many models have been suggested in order to explain the physical mechanism of oxide degradation under electrical stress conditions. A common assumption in all these models is that if some parameter reaches a critical value it triggers the breakdown of the oxide. The three most prevailing models reported in literature are :

#### 1. Electric Oxide Field model

According to this thermodynamic model [13, 14, 15, 16], the electric field itself induces sufficient damage in the oxide due to local field enhancement to cause electron trap generation. Since this model is solely based on the applied electrical field, it means that the electron flux does not influence the oxide degradation at all. This model is therefore commonly referred to as the  $E_{ox}$ -model. It has however been observed by Degraeve et al. [17] that both the electron fluence and the electric field determines the oxide breakdown. It was shown that electron trap generation is identical for all stress fields and that the electric field merely acts as an acceleration factor for the degradation process. This strongly suggests that the breakdown process is current driven, which means that the time-to-failure data should show a  $1/E_{ox}$  dependence due to Fowler-Nordheim (FN) current conduction. This is known as the  $1/E_{ox}$  model and will be explained next. However it should be noted that there are also reports which indicate that the  $E_{ox}$ -model gives a better fit to long-term and low-field data than the  $1/E_{ox}$  model [18, 19]. These data suggests strongly that it is field, not current, which causes the time-dependent degradation of the oxide.

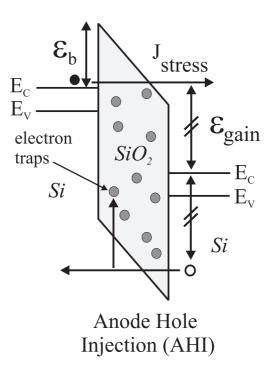

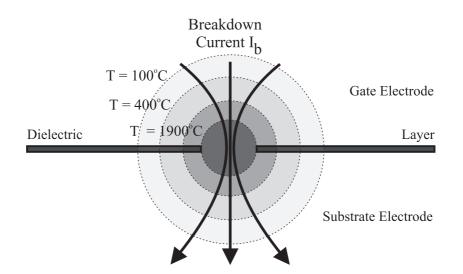

Figure 1.1: Schematic representation of Anode Hole Injection (AHI) model.

#### 2. Anode Hole Injection model (AHI)

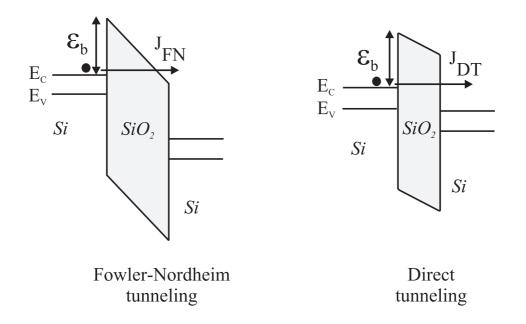

In the Anode Hole Injection model(AHI) [20, 21, 22, 23, 24] the injected electrons gain kinetic energy as they travel through the conduction band of the  $SiO_2$  layer. Upon reaching the anode these high-energetic electrons release part of their energy as they fall back to the conduction band in the anode. Thereby having a probability of creating a *hot-hole* which can tunnel back into the oxide (see Fig. 1.1). These holes are suspected to damage the oxide layer, i.e. creating electron traps and will eventually trigger the breakdown process as soon as a critical hole fluence is reached. This model is commonly referred to as the  $1/E_{ox}$  model, since the time-to-failure data should show a  $1/E_{ox}$  dependence due to Fowler-Nordheim (FN) current conduction. This model assumes that trap generation is directly linked to hole generation, since holes are needed to create traps in the oxide. Indeed, a unique relationship between hole fluence and electron trap generation is found, independent of stress field and oxide thickness [17]. Furthermore, it was demonstrated that breakdown in thin oxide layers occurs as soon as a critical density of (neutral) electron traps in the oxide is reached.

According to Schuegraf *et al.* [22] the AHI model proves to be valid for a large thickness range varying between 2.5 nm and at least 13 nm and can predict  $Q_{bd}$  and  $t_{bd}$  behavior for low oxide voltages down to 2.4 V.

However, DiMaria *et al.* [25, 26, 27] observed that anode hole injection is important, but only for gate voltages larger than  $V_g \approx 7.6$  V. They observed a threshold energy for trap creation of about 2.3 eV with respect to the bottom of the oxide conduction band, while they stated that for anode hole injection a threshold energy of at least 5 eV is needed. So they concluded that degradation of the gate oxide is not related to *hot-holes* but to hydrogen-induced defects, as will be explained in the next model.

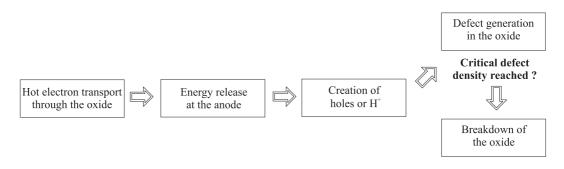

3. Hydrogen-release model

This model is very similar to the AHI injection model. According to the hydrogen release model oxide degradation is due to  $H^+$  instead of holes [28, 29, 26]. A large amount of hydrogen is present at the interface, since passivation of the  $Si/SiO_2$  interface defects with hydrogen is performed in standard CMOS-processing. In this model the energy of the high-energetic electrons is released by releasing hydrogen from the  $Si/SiO_2$ interface. When the  $H^+$  enters the oxide it is believed to create damage. This is supported by experimental evidence. DiMaria *et al.* [26, 30, 31] demonstrated that SiO<sub>2</sub> degrades in a similar manner when exposed to H<sup>+</sup>. From these studies it was also concluded that the generation of neutral oxide traps in thin oxides is the dominant cause of oxide degradation and will eventually lead to oxide breakdown. So electron trap creation can be observed as soon as the electron energy exceeds 2 eV with respect to the bottom of the oxide conduction band. However, it has been observed that in the direct tunneling(DT) regime, where the electrons do not enter the oxide conduction band, defect generation still occurs.

The  $E_{ox}$  versus  $1/E_{ox}$  controversy has continued for many years now, since both models can fit the time-to-failure data rather well over the measured (limited) field ranges. Although the latter two models are the most prevailing ones in explaining the degradation of the oxide, no model has been proven to be unambiguously correct up until now.

Figure 1.2: Schematic illustration of gate oxide breakdown due to positive species (holes or  $H^+$ ).

Nevertheless, from the models above it can be concluded that the degradation mechanism of the oxide is most likely related to positive species as is illustrated in Fig. 1.2 and that breakdown occurs as soon as a critical neutral electron trap density  $D_{ot,crit}$  is reached.

### 1.4 Problem definition: Basic principles

In the previous section it was stated that oxide degradation proceeds with the generation of neutral electron traps in the bulk of the oxide. In this section the different stages of oxide degradation as a function of the density of generated electron traps in (ultra-)thin gate oxides is briefly evaluated. Up until a few years ago the focus was mostly on the occurrence of defect-related i.e. *extrinsic* breakdown, while *intrinsic* breakdown never posed any real reliability problem. However, with the further down-scaling of the oxide thickness to only a few nanometers, intrinsic related breakdown has become a major reliability problem. Since this intrinsic related breakdown eventually limits the scaling of the gate oxide thickness for future generation MOS devices it seems natural to investigate its properties in more detail. First however a brief overview of the different stages of oxide degradation is given.

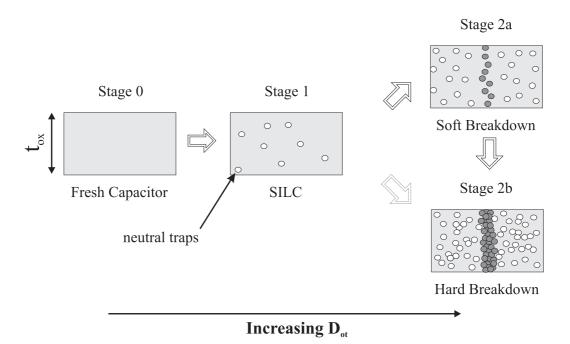

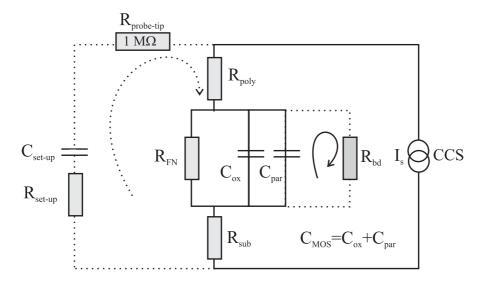

Figure 1.3: Schematic illustration of oxide degradation. Roughly 3 stages can be distinguished, which are 1) SILC, 2a) soft breakdown and 2b) (hard) breakdown.

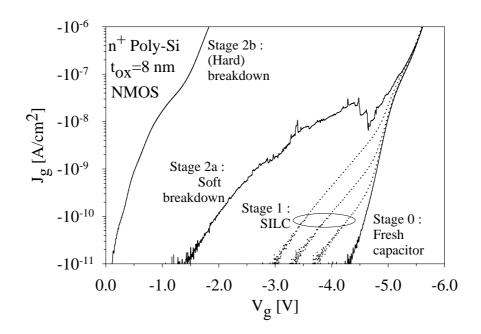

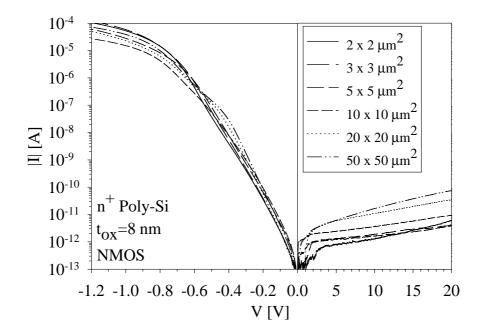

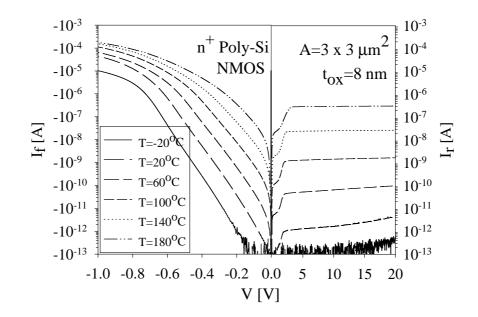

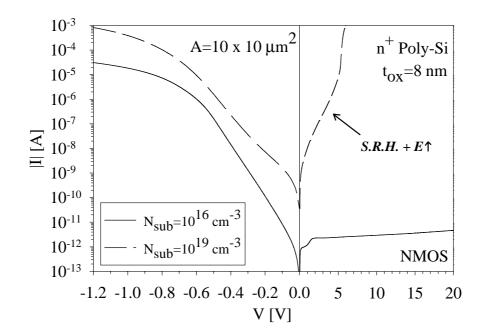

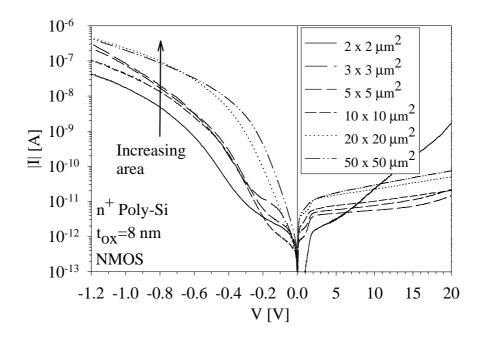

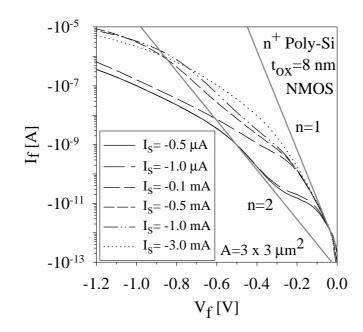

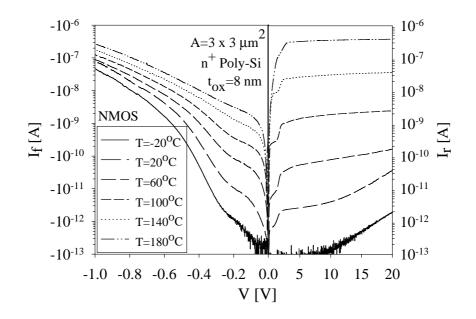

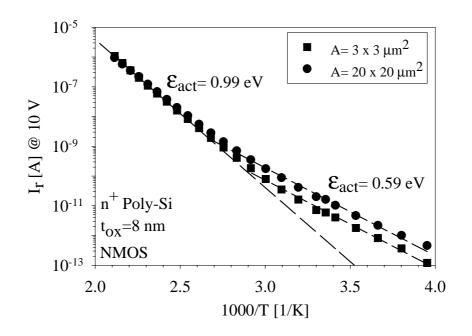

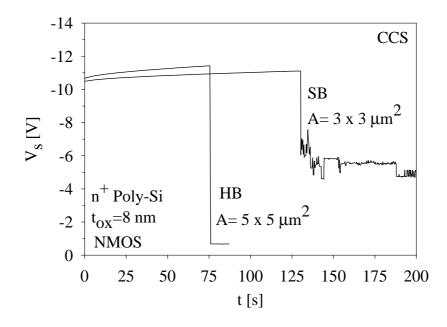

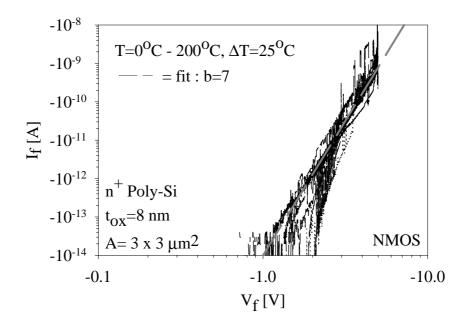

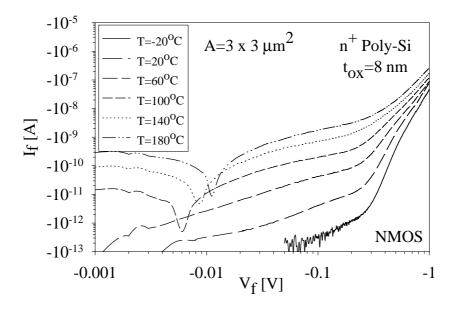

**Figure 1.4:**  $J_g$ - $V_g$  measurements of n<sup>+</sup> poly-Si NMOS capacitors on 8 nm gate oxide thickness showing the different stages of oxide degradation, which are 1) SILC, 2a) soft breakdown and 2b) (hard) breakdown.

Electrical stressing the oxide leads to continuous degradation of its insulating properties. Roughly 3 different stages of oxide degradation can be distinguished, which are depicted in Fig. 1.3.

The occurrence of these stages depend on the density of (neutral) electron traps present in the bulk of the oxide  $D_{ot}$ . The current-voltage(I-V) characteristics which belong to each of these stages are displayed in Fig. 1.4.

• Stage 1: Stress-Induced Leakage Current(SILC)

In sub-10 nm oxides high field stressing of the oxide generates a low field leakage current, which is referred to as Stress-Induced Leakage Current(SILC). Stress-Induced Leakage Current or SILC is the increase in low-level leakage through thin silicon dioxide(SiO<sub>2</sub>) layers after the oxide has been subject to high electrical-field stressing. This phenomenon was first observed in the early eighties by Maserjian *et al.* [32] and will be treated in more detail in chapter 3.

#### • Stage 2a: Soft breakdown(SB)

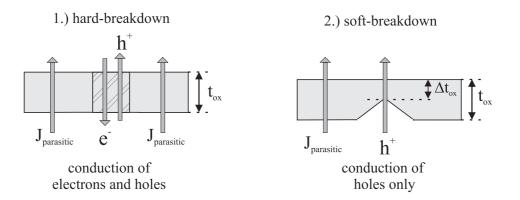

At a higher amount of neutral traps in the oxide, Soft-Breakdown(SB) may occur. Soft, quasi, early, non-destructive breakdown or B-mode SILC is the sudden increase in gate current density at low fields on top of the SILC current to extremely high current levels. It was first observed by Lee *et al.* [33]. This sudden increase in gate current is accompanied by an increase in gate signal noise. Soft breakdown is (only) observed when the power dissipation after breakdown is limited as happens for instance in ultra-thin oxides and small area MOS capacitors [34, 35]. An important difference between SILC and soft breakdown(SB) is that the conduction mechanism of SILC is uniform, i.e. it occurs over the whole capacitor area, while SB conduction occurs at a localized area.

The question however whether soft breakdown corresponds to a real oxide failure is still to be resolved [36]. For ultra-thin oxides it has been reported that the (soft)breakdown of such oxides is difficult to detect, since the post breakdown I-V characteristics are not significantly different from the initial I-V characteristics. The conduction mechanism after breakdown is therefore an important issue and will be treated in more detail in chapter 5.

#### • Stage 2b: (Hard) breakdown(HB)

Further stressing of the gate oxide will eventually lead to termination of the oxide degradation by the occurrence of breakdown of the oxide. This is the final stage of oxide breakdown, where thermal run-away effects lead to a complete loss of insulating properties of the oxide. Hard breakdown occurs if the power dissipation during breakdown is high enough to locally melt the oxide over a small volume centered around the point of breakdown. So hard breakdown is often observed in large area MOS capacitors and thick oxides. It is believed that breakdown is characterized by a maximum amount of electron traps in the gate oxide  $D_{ot,crit}$ , which is known as the critical defect density at breakdown [17, 7].

Oxide breakdown can be characterized by two parameters, the amount of time which is stressed before the device breaks down and the amount of charge fluence which passed through it. The first is the time-to-breakdown  $t_{db}$  and the second the charge-to-breakdown  $Q_{bd}$ .

The definition of time-to-breakdown is straightforward, while the charge-

to-breakdown is defined by Eq. 1.1 as [37, 38]:

$$Q_{bd} = \int_0^{t_{bd}} J_g(t) \mathrm{d}t \tag{1.1}$$

The charge-to-breakdown is a well-known and widely-used tool to evaluate the gate oxide reliability of MOS structures and study the influence of processing conditions on the  $Q_{bd}$ , such as anneal temperature, gate materials and gate implants. The  $Q_{bd}$  can be related to the electron trap density  $D_{ot}$ , where  $Q_{bd}$  is reached as soon as  $D_{ot}=D_{ot,crit}$ . This implies that the density of neutral traps present in the bulk of the oxide  $D_{ot}$  and the generation rate of them  $(P_g=\Delta D_{ot}/\Delta Q_{inj})$  are important parameters for gate oxide reliability.

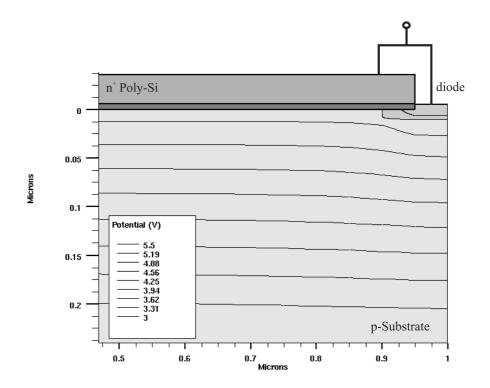

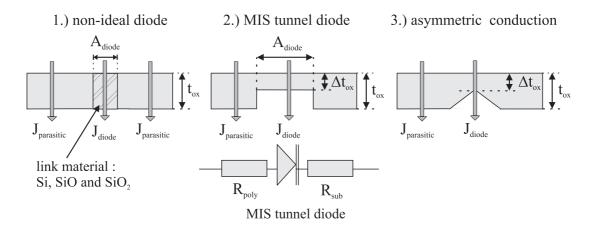

After breakdown a link of electron traps is formed in the gate oxide which connects the gate with the substrate. The post (hard) breakdown I-V characteristics of carefully designed MOS capacitors are studied in chapter 5 as well.

### **1.5** Research objectives

In this thesis the conduction mechanism, oxide degradation and breakdown of (ultra-)thin gate oxides with  $n^+$  and  $p^+$  gates, which are subject to electrical stress are studied. The aim is to obtain a better fundamental knowledge about oxide degradation and breakdown in both  $p^+$  and  $n^+$  gate devices, which can eventually be used to accurately predict the reliability of CMOS devices with ultra-thin gate oxides at operation conditions.

Recently a larger tunnel barrier height and a different conduction mechanism for gate injection  $(-V_g)$  have been proposed for p<sup>+</sup>-poly gate devices [39, 40, 41]. This might have a large impact on the reliability of future CMOS devices with p<sup>+</sup> gates. However a complete understanding is still not available. The research objectives of this thesis can essentially be split up into four parts.

First the conduction (I-V), degradation mechanism (SILC) and time-to-breakdown  $t_{bd}$  of (ultra-)thin gate oxides is investigated. P<sup>+</sup> and n<sup>+</sup>-gates with poly silicon (poly-Si) and poly Silicon-Germanium(poly-Si<sub>0.7</sub>Ge<sub>0.3</sub>) are used to study the influence of gate workfunction on gate current and SILC current. Poly-SiGe is chosen since its allows modification of the workfunction of the gate for p<sup>+</sup> gate devices. Moreover, it is fully compatible with (poly-)Si technology.

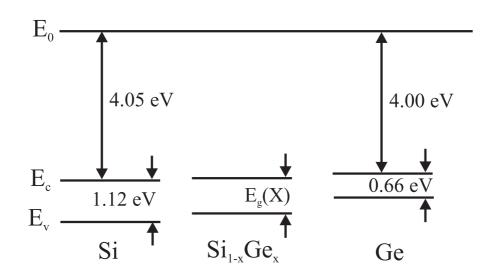

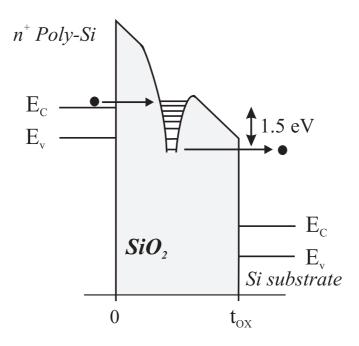

Fig. 1.5 displays the energy band diagram of Si, SiGe and Ge. From Fig. 1.5 it can be observed that  $Si(\chi=4.05 \text{ eV})$  and  $Ge(\chi=4.00 \text{ eV})$  have comparable electron affinity  $\chi$ . However, the bandgap of  $Ge(\mathcal{E}_q=0.66 \text{ eV})$  is much smaller

Figure 1.5: Energy band diagram of Si, SiGe and Ge. It can be observed that the bandgap of SiGe can be tuned by changing the Ge fraction.

than Si( $\mathcal{E}_g=1.12 \text{ eV}$ ). This allows modification of the valence band edge position of the gate by varying the Ge fraction x in poly-Si<sub>1-x</sub>Ge<sub>x</sub> gate devices and therefore influence the gate workfunction for p<sup>+</sup> gate devices. This workfunction engineering by exploiting the difference in valence band edge can in principle be applied for all Ge contents. Moreover, poly-Si<sub>1-x</sub>Ge<sub>x</sub> is a promising alternative to poly-Si as a gate material due to its process compatibility and favorable electrical properties, such as higher dopant activation, lower sheet resistance, superior hole mobility and tunable work function [42, 43, 44, 45, 46, 47]. However the gate oxide reliability of poly-SiGe gate devices has not been studied in detail yet.

The impact of gate current and gate workfunction on the reliability of the gate oxide is also briefly investigated. The physical models for oxide degradation presented in the previous section will be critically reviewed based on our findings.

Next, the post-breakdown I-V characteristics of  $n^+$  poly-Si NMOS gate devices are studied. The I-V characteristics after breakdown can give important information of the breakdown process, which will eventually lead to a better understanding of the degradation mechanism leading to (catastrophic) breakdown.

Finally, light emission measurements are performed on the post breakdown I-V characteristics of  $n^+$  poly-Si NMOS gate devices. These light emission measurements may also reveal important information about the physical properties of the link formed after breakdown.

### **1.6** Outline of this thesis

In this thesis the oxide degradation mechanisms of CMOS devices with (ultra)thin gate oxides is studied. The conduction mechanism, oxide degradation and breakdown of (ultra-)thin gate oxides with  $n^+$  and  $p^+$  poly-Si and poly-SiGe gates have been studied.

The outline of this thesis and main conclusions of every chapter are given in more detail below.

#### Chapter 2

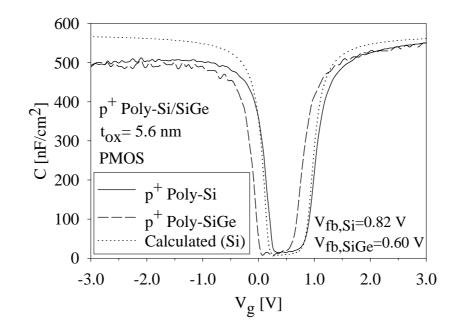

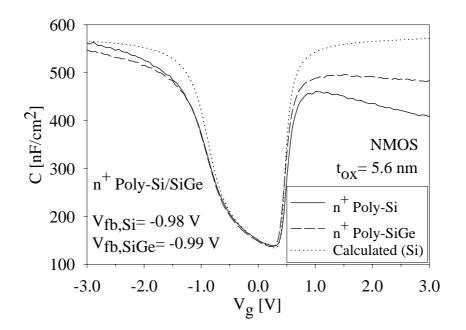

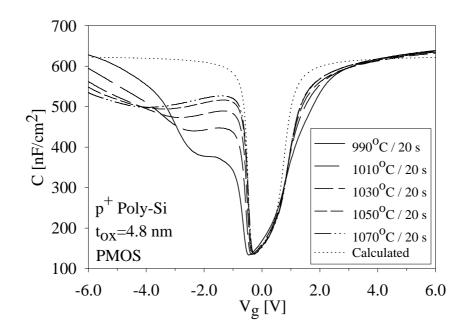

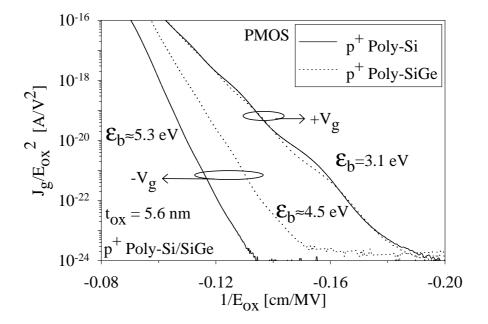

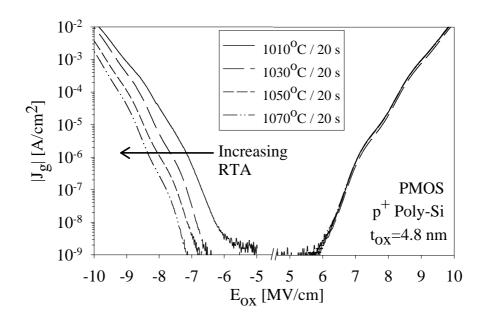

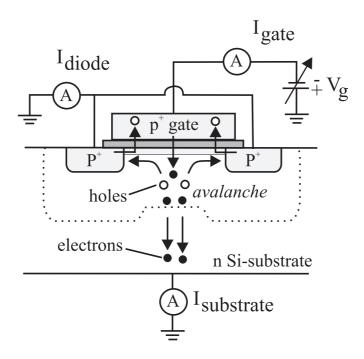

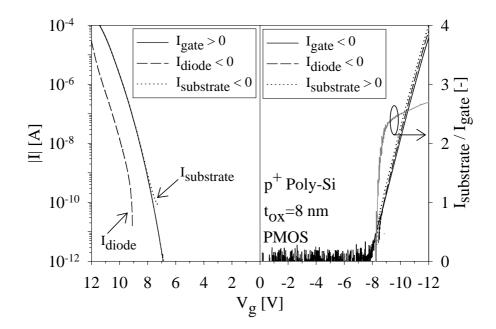

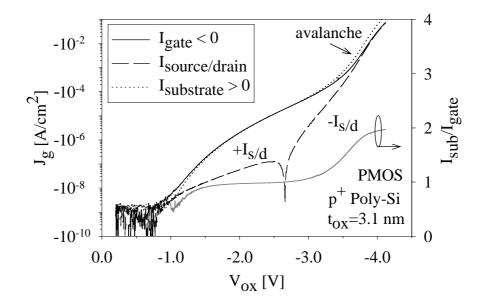

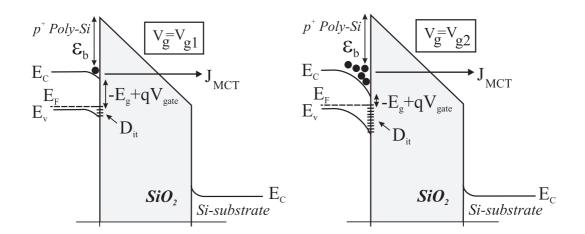

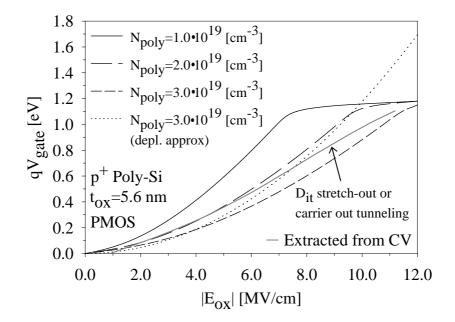

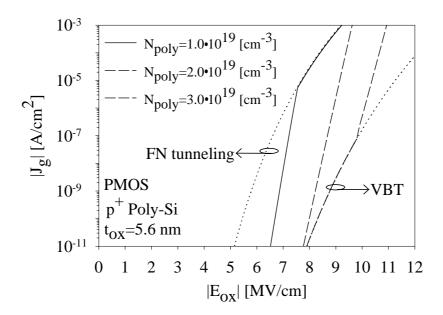

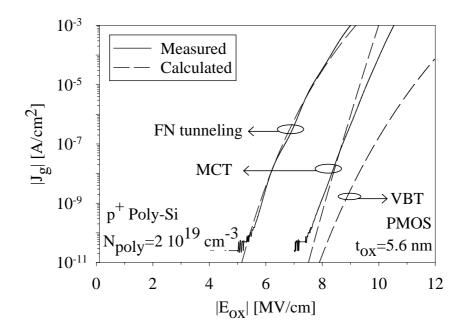

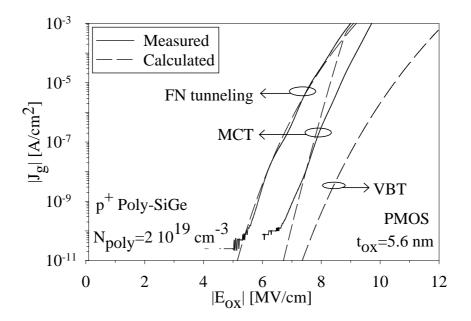

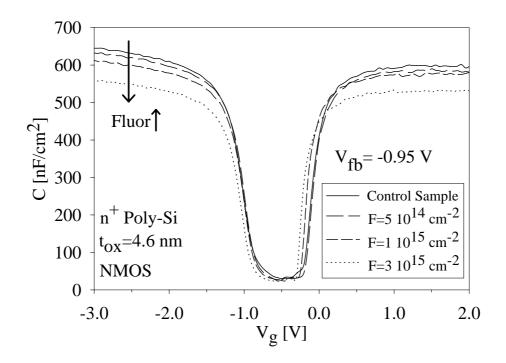

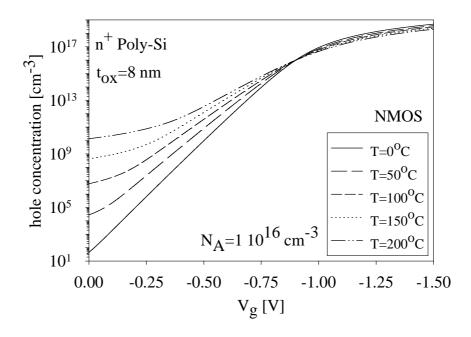

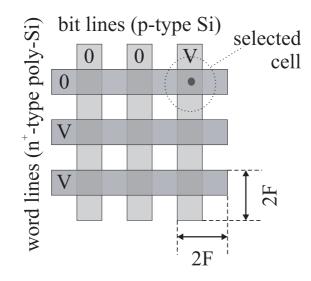

In this chapter the C-V and I-V characteristics of NMOS and PMOS capacitors are studied.  $P^+$  and  $n^+$ -gates with poly silicon(poly-Si) and poly Silicon- $Germanium(poly-Si_{0.7}Ge_{0.3})$  were used to study the influence of gate workfunction on gate current. C-V<sub>q</sub> measurements on  $p^+$  gate devices show a shift of the flatband voltage from  $V_{fb}=0.82$  V(poly-Si) to  $V_{fb}=0.60$  V(poly-SiGe) which is caused by a shift in the valence band position of the gate. For  $p^+$  gate devices the  $J_{q}$ - $E_{ox}$  characteristics depend on gate material and gate bias polarity. The onset of conduction at  $-\mathbf{V}_g$  occurs at a significantly higher oxide field than for  $+V_g$  condition. A new model based on Minority Carrier Tunneling(MCT) from the gate is proposed for the  $J_q$ - $E_{ox}$  characteristics of  $p^+$  gate devices under gate injection conditions ( $-V_q$ ). Furthermore, high frequency (10 kHz) C- $V_q$  curves of p<sup>+</sup> poly-Si gate devices on 4.8 nm oxide thickness show no sharp onset of gate inversion in the p<sup>+</sup> poly-Si gate at  $-V_q$ . This is most likely caused by carrier tunneling out of the gate which occurs at a higher rate than that of carrier generation under MCT injection conditions. For very thin oxides  $(t_{ox} < 4 \text{ nm})$ another contribution to the I-V characteristics at  $-V_g$  is observed. Carrier separation measurements indicate that a hole current is flowing from the source/drain to the gate in the low voltage regime. This current is presumably due to holes which can tunnel (via traps) from the hole inversion layer in the substrate to the gate. Furthermore, this hole current increases strongly with decreasing oxide thickness and can be important for the degradation and reliability of ultra-thin oxides.

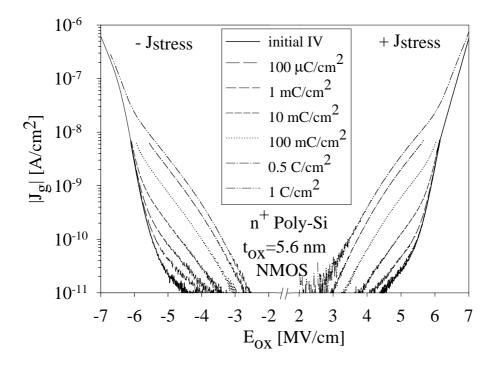

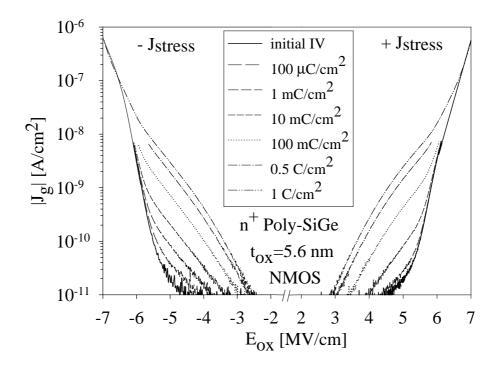

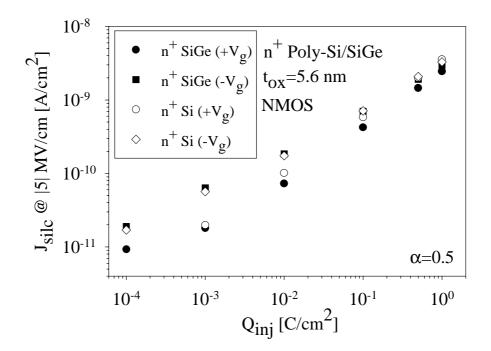

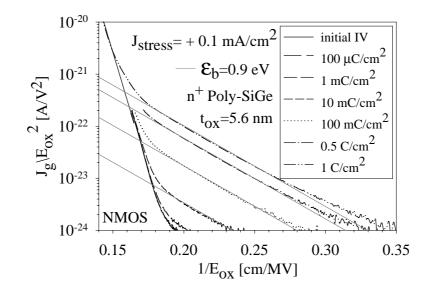

#### Chapter 3

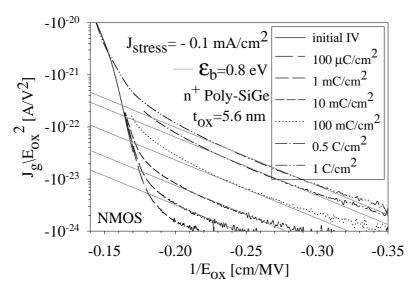

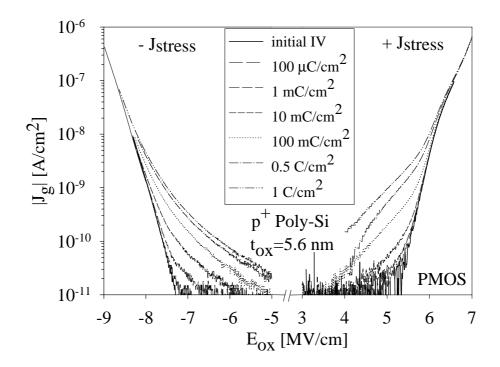

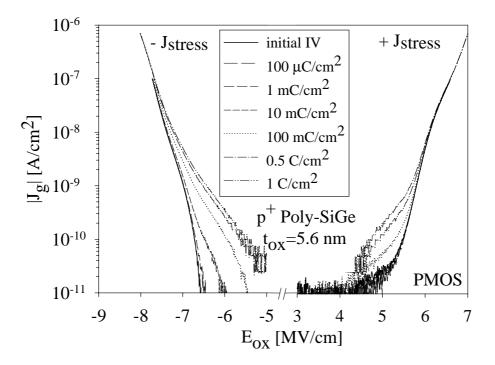

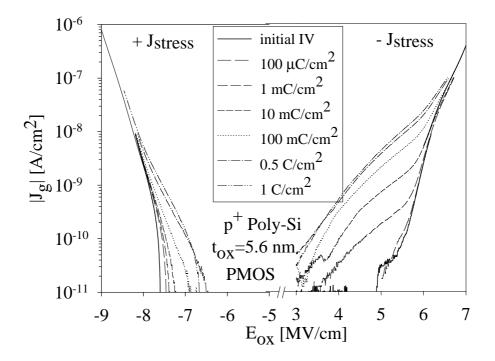

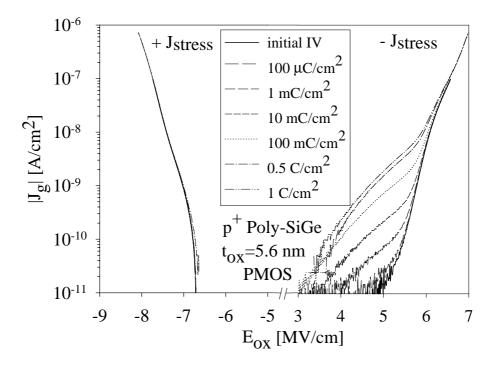

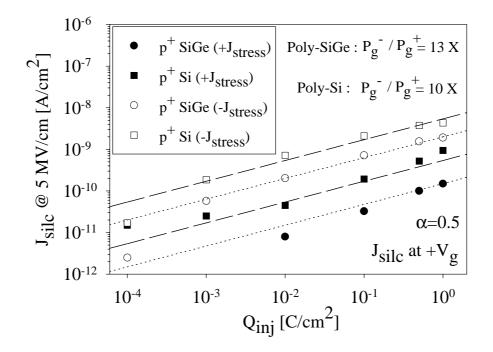

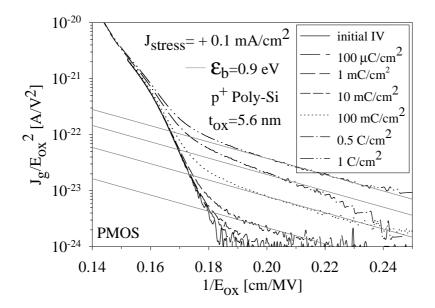

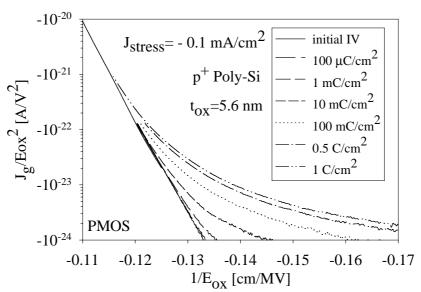

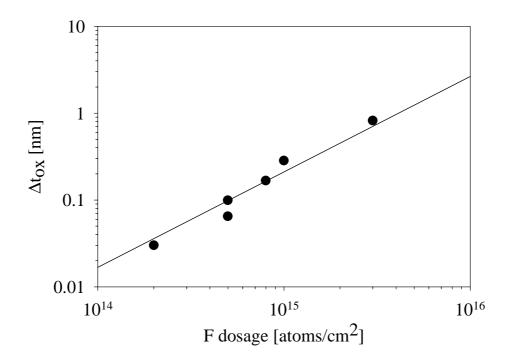

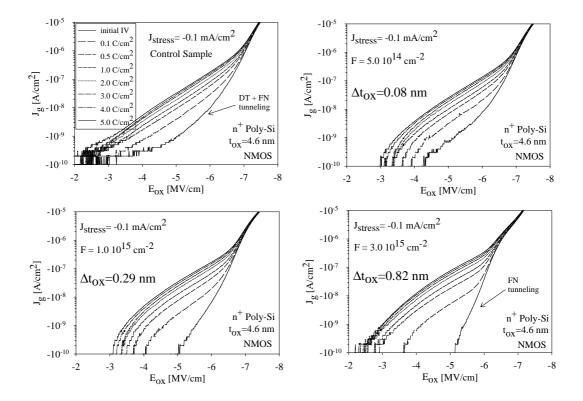

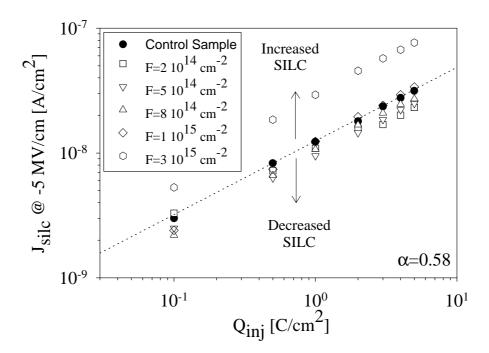

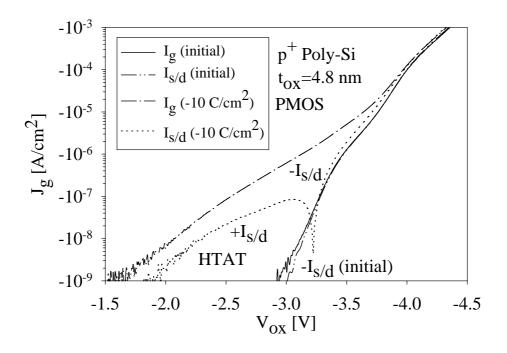

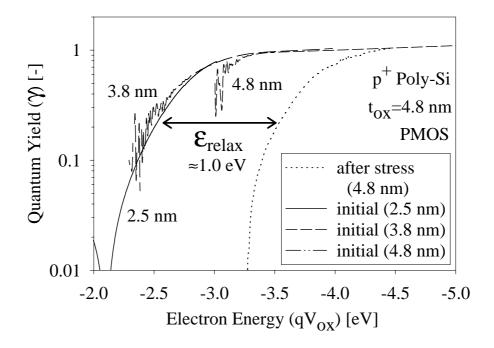

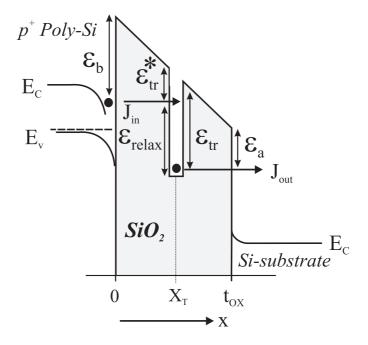

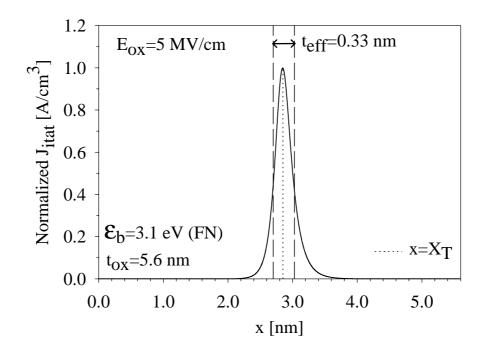

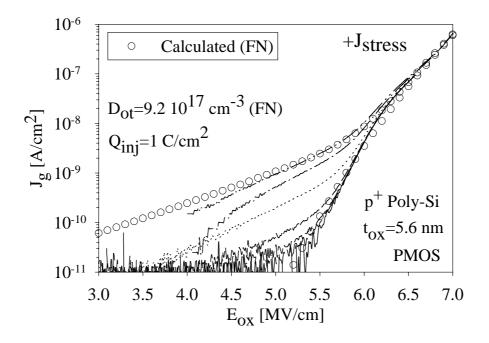

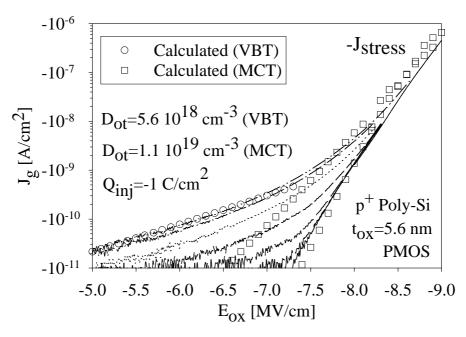

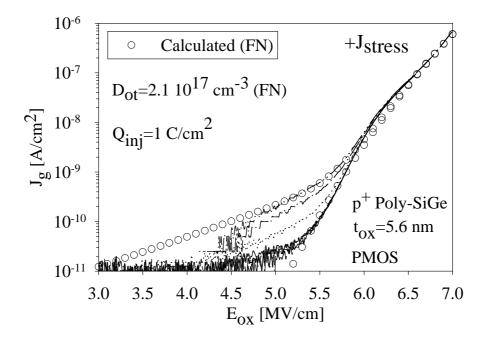

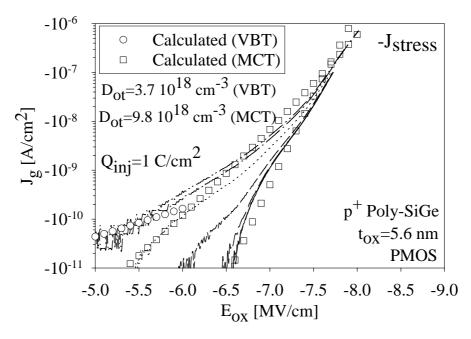

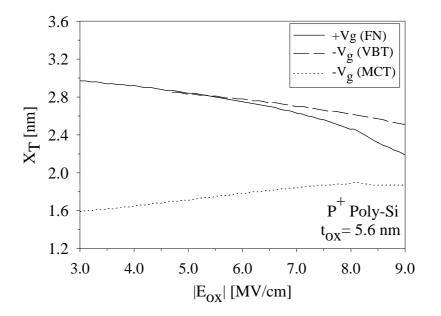

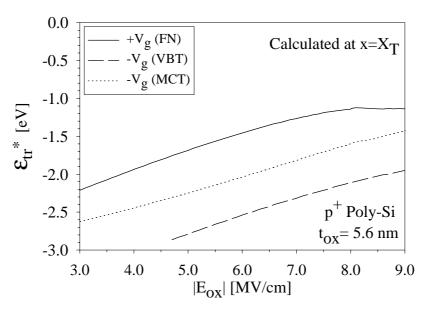

In this chapter the Stress-Induced Leakage Current(SILC) characteristics of NMOS and PMOS capacitors are studied.  $P^+$  and  $n^+$ -gates with poly silicon(poly-Si) and poly Silicon-Germanium(poly-Si<sub>0.7</sub>Ge<sub>0.3</sub>) were used to study the influence of gate workfunction on the SILC current. For  $n^+$  gate devices, symmetric SILC with gate bias polarity is observed. No significant difference in SILC characteristics between the  $n^+$  poly-SiGe and poly-Si reference devices is observed. For  $p^+$ -poly gate devices, asymmetric SILC (gate bias polarity) and reduced SILC for p<sup>+</sup> poly-Si<sub>0.7</sub>Ge<sub>0.3</sub> is observed. The stress injection bias polarity dependence of p<sup>+</sup> gate devices is also studied. It is found that the amount of traps generated per unit of injected charge is approximately 10 times higher for injection of stress from the gate compared to substrate injection of stress. For very thin oxides ( $t_{ox} < 4$  nm) the SILC current at  $-V_g$  and at low voltages is dominated by hole tunneling from the substrate to the gate. This current is interpreted as trap assisted hole tunneling (HTAT). The effect of fluorine(F) on the SILC characteristics of n<sup>+</sup> poly-Si gate devices has also been studied. A small amount of F suppresses the generation of new oxide traps under high field electron injection, which leads to reduced SILC. At excessive F doses an increase of SILC is observed. Finally, a two-step tunneling model was developed to evaluate the SILC current under FN, MCT and VBT injection conditions. It is shown that this model successfully describes the experimental I-V characteristics for both n<sup>+</sup> and p<sup>+</sup> poly gate devices under substrate as well as gate injection conditions.

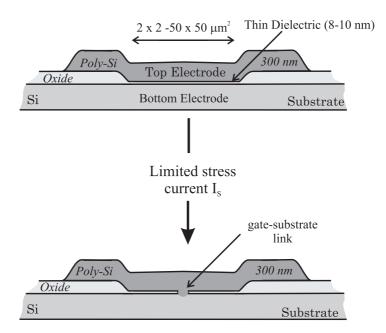

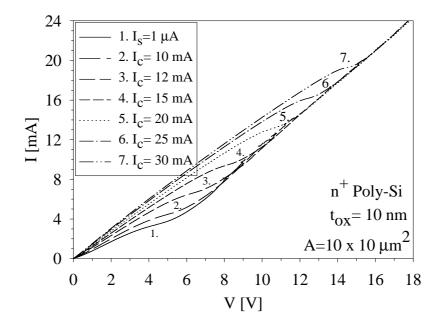

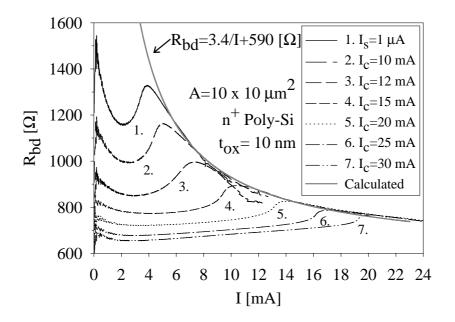

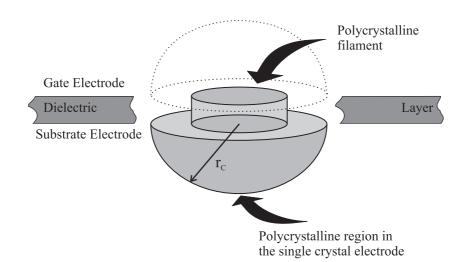

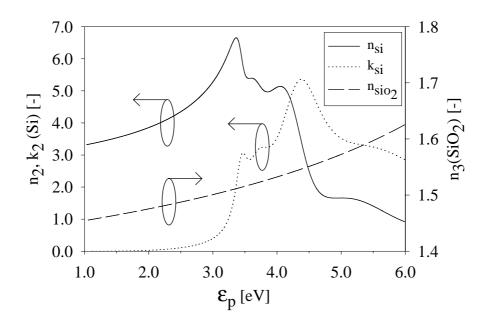

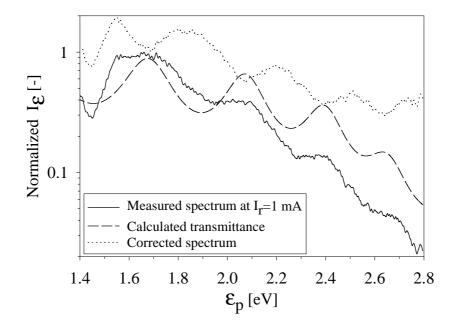

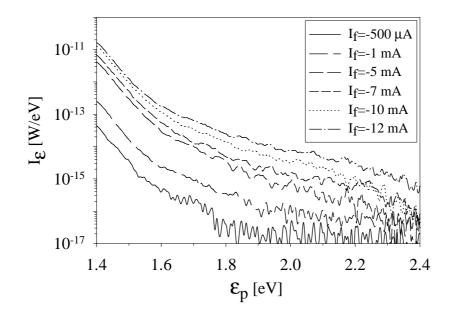

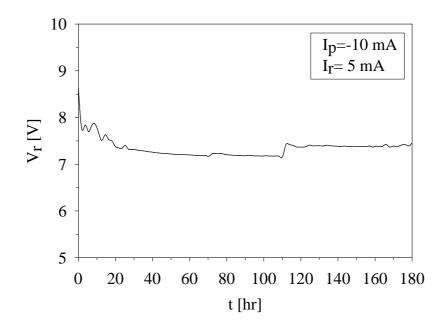

#### Chapter 4