## MOBILE MULTIMEDIA SYSTEMS

Paul J.M. Havinga

ISBN 90-365-1406-1 Copyright © 2000 by P.J.M. Havinga All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without prior written permission of the author.

## **MOBILE MULTIMEDIA SYSTEMS**

#### **PROEFSCHRIFT**

ter verkrijging van

de graad van doctor aan de Universiteit Twente,

op gezag van de rector magnificus,

prof.dr. F.A. van Vught,

volgens besluit van het College voor Promoties

in het openbaar te verdedigen

op vrijdag 11 februari 2000 te 16.45 uur.

door

**Paul Johannes Mattheus Havinga**

geboren op 1 januari 1962 te Groningen Dit proefschrift is goedgekeurd door

prof. dr. S.J. Mullender, promotor, en dr. ir. G.J.M. Smit, assistent-promotor.

#### **Preface**

This Ph.D. thesis is the result of research in the field of mobile multimedia computing. The research was conducted as part of the MOBY DICK project carried out at the faculty of Computer Science of the University of Twente in the Netherlands. As a project-assistant working for the group Systems Programming and Computer Architecture (later renamed to Embedded Systems) I have considered it a great privilege to have the chance to obtain my Ph.D. degree.

Although mine is the only name printed on the cover of this thesis, this work would not have been possible without my colleague and assistant-advisor Gerard Smit. Many ideas presented in this thesis have resulted from joint discussions. Working towards a Ph.D. was very pleasant and seemed very natural due to his valuable coaching and collaboration throughout all the years I worked with him at the University.

I would also thank the other members of the committee for their valuable comments and suggestions on the thesis, and especially my advisor Sape Mullender for his advice and support. Furthermore, I thank Luigi Rizzo from the University of Pisa for giving me the opportunity to work in a very pleasant environment on the topic of error control. I would like to thank all my helpful colleagues, especially Ties Bos for the many inspiring discussions on various topics and Pierre Jansen for keeping me away from practical-work obligations during the last year.

I would like to thank my sons for keeping me busy with all things but my thesis, and showing me that you can do more with a computer, like watching Teletubbies. Finally, but most important, I would like to thank Josephine for supporting and encouraging me through the years, and letting me know that life is more than work alone.

Paul Havinga Hengelo, January 2000

### **Table of contents**

| ABSTRACT                                                                                                                                       | xiii                  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| SAMENVATTING                                                                                                                                   | xv                    |

| CHAPTER 1 INTRODUCTION                                                                                                                         |                       |

| 1.1 PERSONAL MOBILE COMPUTING                                                                                                                  | 1 – 1                 |

| 1.2 PROBLEM STATEMENT                                                                                                                          | 1 – 2                 |

| <ul> <li>1.2.1 System architecture</li> <li>1.2.2 Wireless communication</li> <li>1.2.3 Energy efficiency</li> <li>1.2.4 Hypothesis</li> </ul> | 1-2 $1-4$ $1-5$ $1-6$ |

| 1.3 APPROACH                                                                                                                                   | 1 – 6                 |

| <ul><li>1.3.1 System architecture</li><li>1.3.2 Wireless communication</li></ul>                                                               | 1 - 7 $1 - 9$         |

| 1.4 RELATED WORK                                                                                                                               | 1 – 10                |

| 1.5 THESIS OVERVIEW                                                                                                                            | 1 – 12                |

| REFERENCES                                                                                                                                     | 1 – 14                |

# CHAPTER 2 DESIGN TECHNIQUES FOR ENERGY-EFFICIENT AND LOW-POWER SYSTEMS

| 2.1   | Introduction                                        | 2 - 1  |

|-------|-----------------------------------------------------|--------|

| 2.1.1 | The advance of technology                           | 2 - 2  |

| 2.1.2 | Outline                                             | 2 - 5  |

| 2.2   | FUNDAMENTALS OF LOW-POWER DESIGN                    | 2 - 6  |

| 2.2.1 | Design flow                                         | 2 - 7  |

| 2.2.2 | CMOS component model                                | 2 - 8  |

| 2.2.3 |                                                     | 2 - 9  |

| 2.2.4 | How much is a picojoule?                            | 2 - 9  |

| 2.3   | LOW-POWER TECHNOLOGICAL-LEVEL DESIGN                | 2 – 10 |

| 2.3.1 | Minimise capacitance                                | 2 - 11 |

| 2.3.2 | Reduce voltage and frequency                        | 2 - 13 |

| 2.3.3 | Avoid unnecessary activity                          | 2 - 14 |

| 2.3.4 | Technological and circuit-level conclusions         | 2 - 16 |

| 2.4   | LOW-POWER LOGIC-LEVEL DESIGN                        | 2 – 17 |

| 2.4.1 | Cell library                                        | 2 - 17 |

| 2.4.2 | Clock gating                                        | 2 - 18 |

| 2.4.3 | State-machine modifications                         | 2 - 19 |

| 2.4.4 | Logic encoding                                      | 2 - 20 |

| 2.4.5 | Data guarding                                       | 2 - 21 |

| 2.4.6 | Conclusion                                          | 2 - 21 |

| 2.5   | LOW-POWER SYSTEM-LEVEL DESIGN                       | 2 - 21 |

| 2.5.1 | Optimise communication channels                     | 2 - 22 |

| 2.5.2 | Low-power memory organisation                       | 2 - 23 |

| 2.5.3 | Programmability                                     | 2 - 27 |

| 2.5.4 | Operating system                                    | 2 - 30 |

| 2.5.5 | Applications, compilation techniques and algorithms | 2 - 37 |

| 2.5.6 | Energy reduction in communication                   | 2 - 39 |

| 2.6   | Conclusions                                         | 2 – 45 |

| REFE  | RENCES                                              | 2 – 47 |

# CHAPTER 3 THE DESIGN OF A SYSTEM ARCHITECTURE FOR MOBILE MULTIMEDIA COMPUTERS

| 3.1   | Introduction                                          | 3 - 1  |

|-------|-------------------------------------------------------|--------|

| 3.1.1 | Mobile systems today                                  | 3 - 2  |

| 3.1.2 | The future: Mobile Digital Companion                  | 3 - 3  |

| 3.1.3 | Approach                                              | 3 - 5  |

| 3.1.4 | Outline                                               | 3 - 5  |

| 3.2   | DESIGN ISSUES OF MOBILE SYSTEMS                       | 3 – 5  |

| 3.2.1 | Mobility                                              | 3 - 6  |

| 3.2.2 | Multimedia                                            | 3 - 7  |

| 3.2.3 | Limitation of energy resources                        | 3 - 9  |

| 3.2.4 | 1                                                     | 3 - 9  |

| 3.2.5 | System level integration                              | 3 - 10 |

| 3.2.6 |                                                       | 3 – 11 |

| 3.2.7 | Discussion                                            | 3 - 11 |

| 3.3   | THE SYSTEM ARCHITECTURE OF A MOBILE DIGITAL COMPANION | 3 – 12 |

| 3.3.1 | Approach                                              | 3 – 13 |

| 3.3.2 | Philosophy                                            | 3 - 15 |

| 3.3.3 | Memory-centric versus connection-centric              | 3 - 17 |

| 3.3.4 | Application domain specific modules                   | 3 - 22 |

| 3.3.5 | The interconnection network                           | 3 - 25 |

| 3.3.6 | Energy analysis                                       | 3 - 27 |

| 3.3.7 | $\epsilon$                                            | 3 - 31 |

| 3.3.8 | Quality of Service framework                          | 3 - 32 |

| 3.4   | RELATED WORK                                          | 3 - 34 |

| 3.4.1 | Multimedia architectures                              | 3 - 34 |

| 3.4.2 | Heterogeneous parallel architectures                  | 3 - 35 |

| 3.4.3 | Network attached devices                              | 3 - 37 |

| 3.4.4 | Energy management                                     | 3 - 38 |

| 3.5   | SUMMARY AND CONCLUSIONS                               | 3 – 39 |

| REEL  | RENCES                                                | 3_41   |

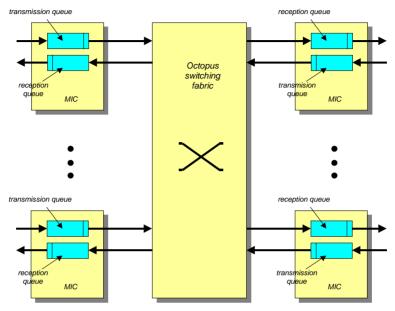

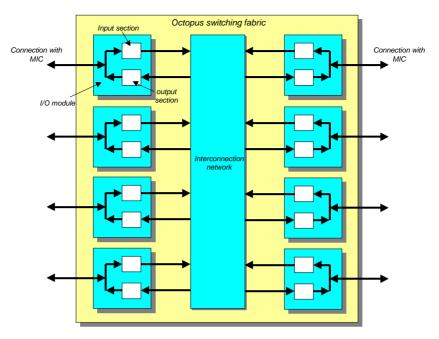

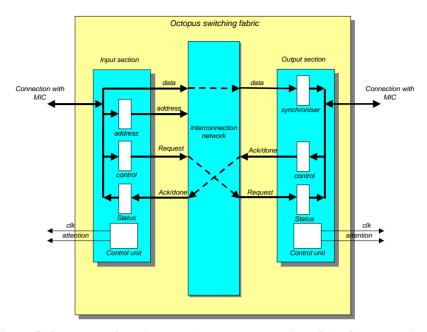

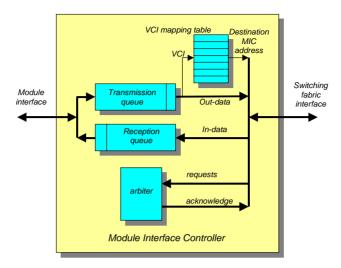

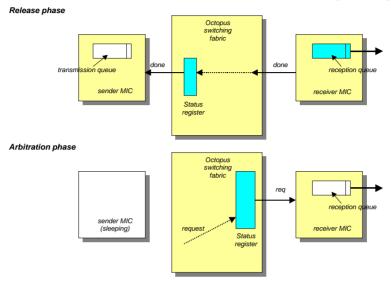

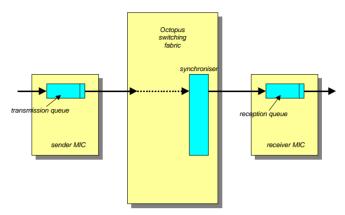

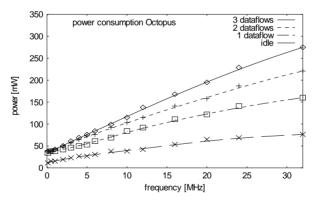

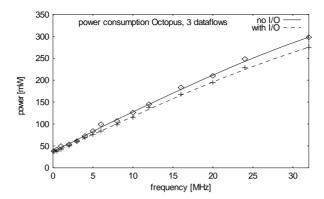

## CHAPTER 4 THE OCTOPUS SWITCH

| 4.1   | INTRODUCTION                                   | 4 – 1  |

|-------|------------------------------------------------|--------|

| 4.2   | ARCHITECTURE OF THE OCTOPUS SWITCH             | 4-3    |

| 4.2.1 | Octopus architecture                           | 4 - 3  |

| 4.2.2 |                                                | 4 - 5  |

| 4.2.3 | Buffer organisation                            | 4 - 7  |

| 4.2.4 | Octopus switching fabric architecture          | 4 - 9  |

| 4.2.5 |                                                | 4 - 12 |

| 4.2.6 |                                                | 4 - 13 |

| 4.2.7 | $\mathcal{E}$                                  | 4 - 15 |

| 4.2.8 | $\mathcal{E}$                                  | 4 - 18 |

| 4.2.9 | Clock Gating                                   | 4 - 21 |

| 4.3   | IMPLEMENTATION OF THE OCTOPUS SWITCH           | 4 – 23 |

| 4.3.1 |                                                | 4 - 23 |

| 4.3.2 | Implementation                                 | 4 - 24 |

| 4.3.3 |                                                | 4 - 27 |

| 4.3.4 | Conclusion                                     | 4 - 31 |

| 4.4   | SUMMARY AND CONCLUSIONS                        | 4 – 32 |

| REFI  | ERENCES                                        | 4 – 34 |

|       | APTER 5 RGY EFFICIENT WIRELESS COMMUNICATION   |        |

| 5.1   | INTRODUCTION                                   | 5 – 1  |

| 5.2   | WIRELESS DATA LINK LAYER NETWORK DESIGN ISSUES | 5 – 4  |

| 5.2.1 | The ISO/OSI network design model               | 5 - 5  |

| 5.2.2 | Wireless link restrictions                     | 5 - 6  |

| 5.2.3 | Basic wireless networking functions            | 5 - 7  |

| 5.2.4 | QoS renegotiation                              | 5 – 9  |

| 5.3   | ENERGY-EFFICIENT WIRELESS MAC DESIGN           | 5 – 10 |

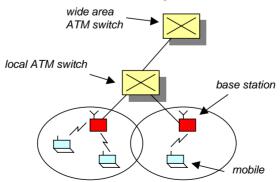

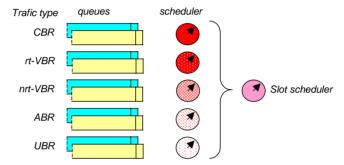

| 5.4   | ATM                                            | 5 – 14 |

| 5.4.1 | ATM service classes                            | 5 – 14 |

| 5.4.2 |                                                | 5 – 15 |

| 5.4.3 | 1 &                                            | 5 – 16 |

| 5.5                 | ENERGY-EFFICIENT ERROR CONTROL                         | 5 – 17           |

|---------------------|--------------------------------------------------------|------------------|

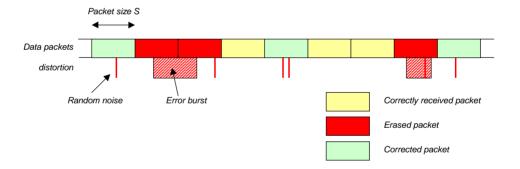

| 5.5.1               | The error model                                        | 5 – 18           |

| 5.5.2               |                                                        | 5 – 19           |

| 5.5.3               |                                                        | 5 - 21           |

| 5.5.4<br><b>5.6</b> | Related work  ENERGY-EFFICIENT WIRELESS NETWORK DESIGN | 5 - 23<br>5 - 24 |

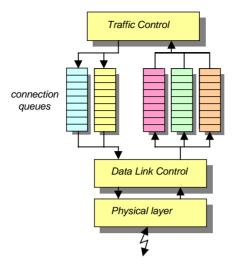

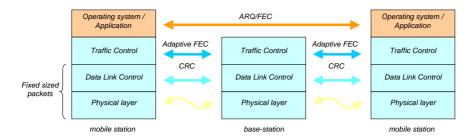

| 5.6.1               |                                                        | 5-25             |

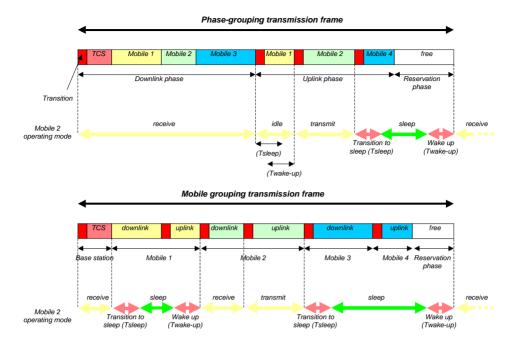

| 5.6.2               | System overview E <sup>2</sup> MaC protocol            | 5 - 23<br>5 - 27 |

| 5.6.3               | 1                                                      | 5 - 29           |

| 5.6.4               |                                                        | 5 - 32           |

| 5.6.5               | Buffer status coding and flow control                  | 5 - 36           |

| 5.6.6               |                                                        | 5 - 37           |

| 5.6.7               | 1                                                      | 5 – 39           |

| 5.6.8               | 11                                                     | 5 - 42           |

| 5.6.9<br>5.6.1      | •                                                      | 5 - 43<br>5 - 45 |

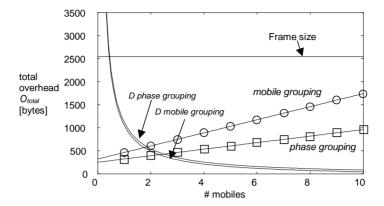

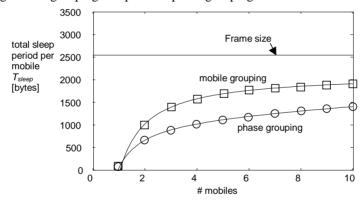

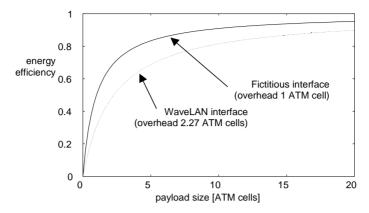

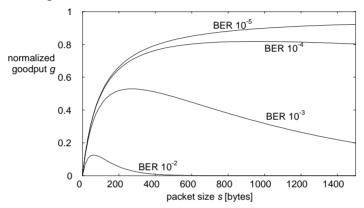

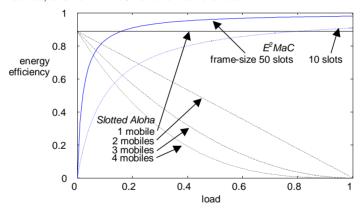

| 5.7                 | EVALUATION OF THE E <sup>2</sup> MAC PROTOCOL          | 5 – 46           |

| 5.7.1               | Synchronise the mobile and the base-station            | 5 – 47           |

| 5.7.2               | Minimise the number of transitions                     | 5 - 48           |

| 5.7.3               | Avoid unsuccessful actions                             | 5 - 57           |

| 5.8                 | RELATED WORK                                           | 5 – 61           |

| 5.9                 | Conclusions                                            | 5 – 63           |

| Refi                | ERENCES                                                | 5 – 65           |

| _                   | PTER 6 CLUDING REMARKS                                 |                  |

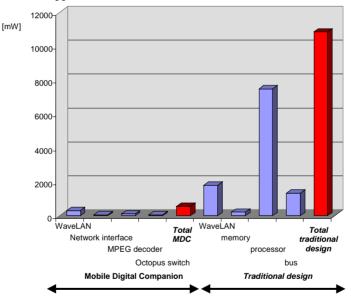

| 6.1                 | EVALUATION OF POWER DISSIPATION                        | 6 – 1            |

| 6.1.1               | Setup traditional architecture                         | 6 - 2            |

| 6.1.2               |                                                        | 6 – 4            |

| 6.1.3               | Power dissipation MP3 application                      | 6 - 5            |

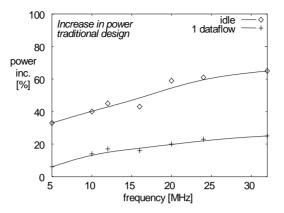

| 6.1.4               | Power dissipation when idling                          | 6 – 7            |

| 6.2                 | FUTURE RESEARCH                                        | 6 – 9            |

| 6.2.1               | Operating system architecture                          | 6 – 10           |

| 6.2.2               |                                                        | 6 – 11           |

| 6.2.3               | Modelling energy management                            | 6 - 12           |

| 6.3 CONCLUSION                                                              | 6 – 13 |

|-----------------------------------------------------------------------------|--------|

| REFERENCES                                                                  | 6 – 16 |

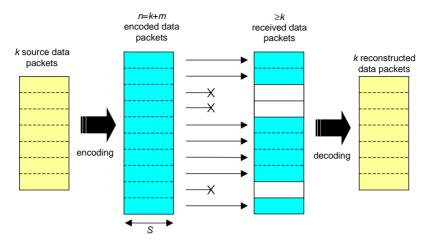

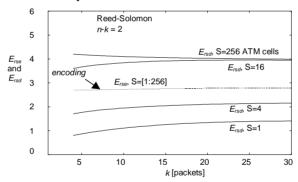

| APPENDIX A ENERGY EFFICIENCY OF ERROR CORRECTION FOR WIRELESS COMMUNICATION |        |

| A.1 Introduction                                                            | A – 1  |

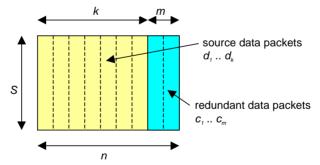

| A.1.1 The encoding packet model                                             | A-2    |

| A.1.2 Reed-Solomon coding                                                   | A-4    |

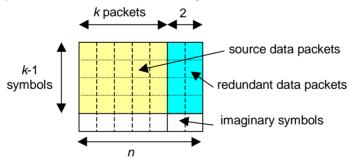

| A.1.3 EVENODD coding                                                        | A-5    |

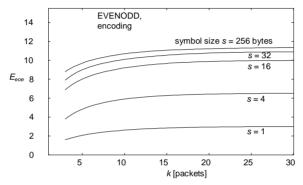

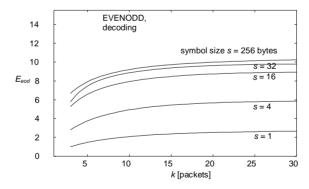

| A.2 IMPLEMENTATION AND RESULTS                                              | A-7    |

| A.2.1 Software implementation                                               | A-7    |

| A.2.2 EVENODD coding implementation                                         | A-8    |

| A.2.3 Reed-Solomon coding implementation                                    | A-9    |

| A.2.4 Comparison                                                            | A - 10 |

| A.2.5 A minimal communication system                                        | A - 11 |

| A.3 CONCLUSION                                                              | A – 12 |

| REFERENCES                                                                  | A – 13 |

|                                                                             |        |

|                                                                             |        |

|                                                                             |        |

|                                                                             |        |

#### **BIOGRAPHY**

**PUBLICATIONS**

#### **Abstract**

#### **Abstract**

Recent advances in wireless networking technology and the exponential development of semiconductor technology have engendered a new paradigm of computing, called personal mobile computing. In this paradigm, the basic personal computing and communication device will be an integrated, battery-operated device, small enough to carry with you all the time. This device will be used as a replacement of many items the modern human-being carries around. However, the technological challenges to establishing this paradigm are non-trivial. In particular, these devices have limited battery resources, will handle diverse data types, and will operate in environments that are insecure, time varying, and unplanned. As the mobiles must remain usable in a wide variety of environments, they must be flexible enough to accommodate a variety of multimedia services and communication capabilities and adapt to various operating conditions in an (energy) efficient way.

The opportunities given by the continuous miniaturisation of micro-electronics are employed in the architecture of the *Mobile Digital Companion* to solve some of the problems that mobile multimedia computers encounter. We have shown that it is not sufficient to simply continue advancing our chip architectures and technologies as just more of the same: building microprocessors and devices that are simply more complicated versions of the kind built today.

The characteristics and requirements of such future handheld computers, influences many levels of the design process. Key issue in this are *energy efficiency* and *Quality of Service* (QoS). There is a vital relationship between hardware architecture, operating system architecture and applications, where each benefits from the others. Achieving high energy efficiency requires first of all the elimination of the waste that typically dominates the energy consumption in general-purpose processors. The second main principle used is to have a high locality of reference. The philosophy is that all

operations that are required on the data should be done at the place where it the most efficient, thereby also minimising the transport of data through the system.

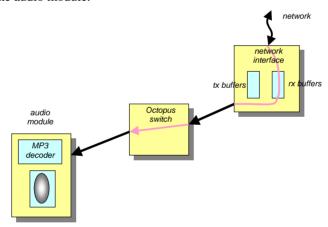

The approach made to achieve such a system is to use autonomous, adaptable components, interconnected by a switch rather than by a bus, and to offload as much work as possible from the CPU to programmable modules that are placed in the data streams. Thus, data is delivered exactly to where it is needed, work is carried out where the data passes through – bypassing the 'main' memory –, modules are autonomously entering an energy-conservation mode and adapt themselves to the current state of the resources and the requirements of the user.

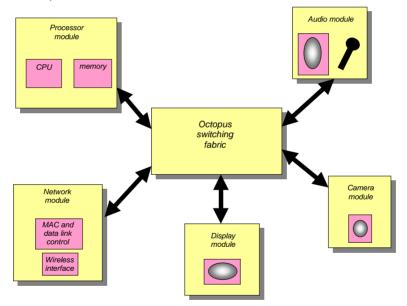

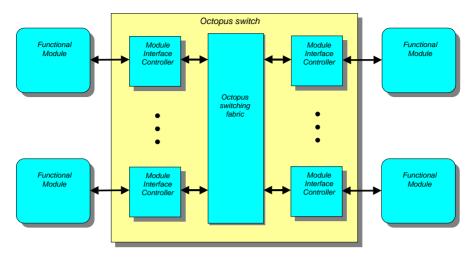

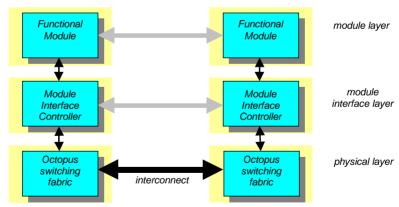

Of particular importance to the system architecture is the communication network that connects the modules. The system architecture of the *Mobile Digital Companion* is connection centric, which means that the media type of the traffic drives the data flow in the system using connections. The interconnect of the architecture is based on a switch, called *Octopus*, which interconnects a general-purpose processor, programmable (multimedia) devices (modules), and a wireless network interface. The switch is built analogous to some of the concepts that have been used in the field of ATM switching fabrics. All connections are identified with a connection identifier which is used to identify the type of data, and to determine the module destination address. This identifier provides the mechanism to support lightweight protocols that provide data-specific transport services that are associated with a certain QoS. This approach gives the system the possibility to control the QoS of a task down to the communication infrastructure.

The wireless network is another important aspect of a mobile multimedia system. We argue that energy-awareness must be applied in almost all layers of the network protocol stack. To achieve maximal performance and energy efficiency, *adaptability* is important, as wireless networks are dynamic in nature. We present an architecture of a highly adaptive network interface and a novel MAC protocol (E<sup>2</sup>MaC) that provides support for diverse traffic types and QoS while achieving a good energy efficiency of the wireless interface of the mobile.

#### **Samenvatting**

Recente vooruitgang in technologie voor draadloze netwerken en de exponentiële ontwikkeling van semi-conductor technologie hebben een nieuw toepassingsgebied voortgebracht, gebaseerd op persoonlijke mobiele systemen. In dit toepassingsgebied zal de persoonlijke computer en het communicatieapparaat een geïntegreerde, batterij gevoed, apparaat zijn, dat klein genoeg is om altijd bij je te dragen. Het apparaat zal gebruikt worden ter vervanging van vele dingen die moderne mensen bij zich dragen. Echter, de technologische uitdagingen om dit toepassingsgebied te verwezenlijken zijn niet triviaal. In het bijzonder zullen deze apparaten een beperkte hoeveelheid batterijenergie hebben, diverse typen data behandelen, en werken in omgevingen die niet veilig zijn, variëren in tijd, en niet van tevoren voorspelbaar zijn. Omdat de apparaten bruikbaar moeten blijven in velerlei omgevingen, dienen ze flexibel genoeg te zijn om geschikt te zijn voor een groot aantal multimedia diensten en communicatiemogelijkheden, en zich op een (energie) efficiënte manier kunnen aanpassen aan de verschillende omstandigheden.

De kansen die geboden worden door de continue miniaturisering van de microelektronica worden in de architectuur van de *Mobile Digital Companion* benut om een aantal problemen op te lossen waar mobiele multimedia computers op stuiten. We hebben aangetoond dat het niet afdoende is om simpelweg op dezelfde weg door te gaan met het verbeteren van de chip architecturen en technologieën als slechts meer van hetzelfde: het bouwen van microprocessoren en apparaten die slechts gecompliceerde versies zijn van het soort dat al bestaat.

De karakteristieken en eisen van toekomstige kleine ('handheld') computers, beïnvloedt diverse lagen in het ontwerpproces. Sleutelthema's hierin zijn *energie-efficiëntie* en *kwaliteit van geboden diensten*. Er bestaat een vitale relatie tussen hardware-architectuur, besturingssysteem en toepassingen, waarin elk component voordeel kan hebben van de anderen. Het bereiken van een hoge energie-efficiëntie vereist om te beginnen het vermijden van alle verspilling die in het algemeen domineert bij algemeen toepasbare processoren. Het tweede belangrijke principe is om een hoge mate van lokaliteit te bewerkstelligen. De gedachte hierachter is, dat de bewerkingen die nodig zijn op de data, plaats moeten vinden waar dat het meest efficiënt kan, waarbij tevens het datatransport door het systeem dient te worden geminimaliseerd.

De aanpak die gemaakt is om zo'n systeem te bereiken, is om autonome, aanpasbare componenten te gebruiken, die verbonden zijn door een dynamische schakelaar in plaats van een gemeenschappelijke verbinding (bus), en om zoveel mogelijk werk over te dragen van de algemene processor naar programmeerbare modulen die in de datastroom zijn geplaatst. Dus, data wordt afgeleverd precies daar waar het nodig is, werk wordt gedaan daar waar de data langs komt – zonder gebruik te maken van het hoofdgeheugen –, modulen komen autonoom in een energiezuinige modus en passen zichzelf aan de huidige toestand van de beschikbare middelen en de wensen van de gebruiker aan.

Een belangrijk aspect voor de systeemarchitectuur is het communicatienetwerk dat de modulen verbindt. De systeemarchitectuur van de *Mobile Digital Companion* is verbindings-georiënteerd, wat inhoudt dat het mediatype van het verkeer de datastroom in het systeem bepaalt, gebruik makende van verbindingen. De verbindingsstructuur is gebaseerd op een schakelaar, genaamd *Octopus*, die de verbindingen legt tussen de algemene processor, programmeerbare (multimedia) modulen, en het draadloze netwerk. De schakelaar is gebouwd naar analogie van sommige concepten die gebruikt worden in het veld van ATM-netwerk schakelsystemen. Alle verbindingen worden geïdentificeerd met een verbindings-identificatie die het type van de verbinding en de bestemmingsmodule bepaalt. Met deze identificatie kunnen lichtgewicht protocollen gemaakt worden die dataspecifieke transportdiensten leveren, en geassocieerd zijn met een bepaalde kwaliteit. Door deze aanpak heeft het systeem de mogelijkheid om de kwaliteit van een taak te besturen tot op het communicatiemedium.

Het draadloze netwerk is een ander belangrijk aspect in een mobiel multimedia systeem. We beargumenteren dat bijna alle lagen van het netwerk communicatieprotocol energiebewust moeten zijn. Om het maximale uit een systeem te halen en om energie-efficiënt te zijn, is aanpasbaarheid van belang, met name omdat draadloze netwerken van nature erg dynamisch zijn. We presenteren een architectuur van een sterk aanpasbaar netwerk interface, en een nieuw MAC protocol (E<sup>2</sup>MaC) dat diverse verkeerstypen en kwaliteiten ondersteunt, terwijl het een goede energie-efficiëntie geeft voor de draadloze interface van het mobiele systeem.

#### Introduction

Recent advances in wireless networking technology and the exponential development of semiconductor technology have engendered a new paradigm of computing, called personal mobile computing or ubiquitous computing. Users carrying portable devices will have access to a shared infrastructure independent of their physical location. The technological challenges to establishing this paradigm of computing are non-trivial, however. The research in this thesis is about designing such a mobile multimedia system. Personal mobile computing offers a vision of the future with a much richer and more exciting set of architecture research challenges than extrapolations of the current desktop architectures. In particular, these devices will have limited battery resources, will handle diverse data types, and will operate in environments that are insecure, dynamic and which vary significantly in time and location.

#### 1.1 Personal mobile computing

In recent years, technology drivers changed significantly. High-end systems used to direct the evolution of computer architectures and systems. Now low-end systems drive technology, due to their large volume and attainable profits. Advances in technology enable portable computers to be equipped with wireless interfaces, allowing networked communication even while mobile. Whereas today's notebook computers and personal digital assistants (PDAs) are self contained, tomorrow's networked mobile computers are part of a greater computing infrastructure.

Two trends – multimedia applications and mobile computing – will lead to a new application domain and market in the near future. *Personal mobile computing* (often also referred to as ubiquitous *computing* [27]) will play a significant role in driving technology in the next decade. In this paradigm, the basic personal computing and communication device will be an integrated, battery-operated device, small enough to carry along all the time. This device will be used as a replacement of many items the modern human-being carries around. It will incorporate various functions like a pager,

1 – 2 Introduction

cellular phone, laptop computer, diary, digital camera, video game, calculator and remote control. An important issue will be the user interface: the interaction with its owner. The device will support multimedia tasks like speech recognition, video and audio.

Wireless networking greatly enhances the utility of a personal computing device. It provides mobile users with versatile communication, and permits continuous access to services and resources of the land-based network. A wireless infrastructure capable of supporting packet data and multimedia services in addition to voice will bootstrap on the success of the Internet, and in turn drive novel networked applications and services.

However, the technological challenges to establishing this paradigm of personal mobile computing are non-trivial. In particular, these devices have limited battery resources, will handle diverse data types, and will operate in environments that are insecure, unplanned, and show different characteristics in time.

In the next section we will describe the problems to be solved when designing an architecture for such a *mobile multimedia system*. In Section 1.3 we describe our approach to solve these problems, followed by a brief introduction to current systems and research on mobile multimedia devices in Section 1.4. We conclude in Section 1.5 with an overview of the thesis.

#### 1.2 Problem statement

This dissertation is concerned about how mobile multimedia systems should be designed. The main focus is on those issues pertinent to the system design level, i.e. the area of the hardware system-designer and systems programming-designer. We will not delve into the lower level details of the VLSI realisation of the mobile system itself, nor into the higher levels of the operating system and applications.

In this section we survey the principal challenges faced in the system design of an architecture for a mobile multimedia computing device. The issues described herein divide cleanly into three items, each stemming from an essential property of mobile computing. Section 1.2.1 discusses the consequences of the required functionality on the *system architecture*, such as adaptability, multimedia functionality, wireless networking, and energy efficiency. Section 1.2.2 considers the implications of using *wireless communication* for multimedia traffic, for example susceptibility to errors and disconnections, (low) bandwidth availability, and variable network conditions. Section 1.2.3 investigates the pressure that the *energy efficiency* places on the design of a mobile system.

#### 1.2.1 System architecture

Today, the choice of wireless devices is largely limited to simple wireless phones on the one hand, to complex and bulky laptops with wireless communication capability on the other. While these devices serve their purposes, they are neither the most integrated nor

Problem statement 1-3

the most general: their functionality is often limited, they can operate for just a short time, and they are incapable of fully exploiting the emerging integrated wireless networks.

Even while current devices have the ability to communicate and process data, they are and by large primarily either data processing devices *or* communication devices. Simply shrinking the processing devices and communication devices, and packaging them together does not alleviate the architectural bottlenecks of integrated mobile multimedia devices [19]. The real challenge is to design a device where data processing and communication share equal importance.

Future wireless devices must meet five major requirements: high performance for multimedia functions, energy efficiency, small size, low design complexity, and a very intuitive and small user interface.

Multimedia functionality is a driving force for many research challenges. For example, due to the size constraints on a portable computer, the user interface must be small. This is a main reason that pens have become the standard input devices for PDAs. The shortage of area on a mobile device can cause us to trade buttons in favour of recognising the user's intention from analog input devices such as handwriting, gesture [4] and voice. Speech generation and recognition seem an ideal user interface since they require no surface area and allow hands-free and eye-free operation. However, general-purpose speech input and output places substantial storage and processing demands on a mobile device. Other research investigates the use of head-mounted virtual reality displays [26]. Main problems to be solved are the required processing power or communication bandwidth and the required weight and size (i.e. a small and light headgear).

A key challenge of mobile computing is that many attributes of the environment vary dynamically. Mobile devices face many different types of variability in their environment. Therefore, they need to be able to operate in environments that can change drastically in short term as well as long term in available resources and available services. Some short-term variations can be handled by adaptive communication protocols that vary their parameters according to the current condition. Other, more long-term variations generally require a much larger degree of adaptation. Merely algorithmic adaptations are not sufficient, but rather an entirely new set of protocols and/or algorithms may be required. For example, mobile users may encounter a complete different wireless communication infrastructure when walking from their office to the street. They might require another air interface, other network protocols, and so forth. A possible solution is to have a mobile device with a reconfigurable architecture so that it can adapt its operation to the current environment and operating condition.

Reconfigurability also has another more economic motivation: it will be important to have a fast track from sparkling ideas to the final design. If the design process takes too long, the return on investment will be less. It would further be desirable for a wireless terminal to have architectural reconfigurability whereby its capabilities may be modified by downloading new functions from network servers. Such reconfigurability would also

1 – 4 Introduction

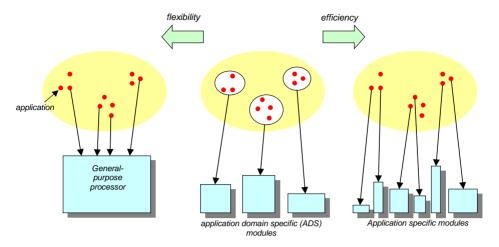

help in field upgrading as new communication protocols or standards are deployed, and in implementing bug fixes [19]. This also asks for a flexible architecture with a reasonable amount of programmability [20]. One of the key issues in the design of portable multimedia systems is to find a good balance between flexibility and high-processing power on one side, and area and energy-efficiency of the implementation on the other side.

#### 1.2.2 Wireless communication

Mobile computers require wireless network access, although sometimes they may physically attach to the network for a better or cheaper connection. Wireless communication is much more difficult to achieve than wired communication because the surrounding environment interacts with the signal, blocking signal paths and introducing noise and echoes. As a result wireless connections have a lower quality than wired connections: lower bandwidth, less connection stability, higher error rates, and, moreover, with a highly varying quality. These factors can in turn increase communication latency due to retransmissions, can give largely varying throughput, and incur a high energy consumption. Three key problems in networked wireless multimedia systems are 1) the need to maintain quality of service (throughput, delay, bit error rate, etc) over time-varying channels, 2) to operate with limited energy resources, and 3) to operate in a heterogeneous environment.

Quality of Service – Considerations of energy efficiency are fundamentally influenced by the trade-off between energy consumption and achievable Quality of Service (QoS). To deal with the dynamic variations in networking and computing resources gracefully, both the mobile computing environment and the applications that operate in such an environment need to adapt their behaviour depending on the available resources including the batteries.

*Energy-efficiency* – The wireless network interface of a mobile computer consumes a significant fraction of the total energy of a mobile computer. More extensive and continuous use of network services will aggravate this problem. Energy efficiency can be improved at various layers of the communication protocol stack. Adaptability of the protocols is a key issue is achieving this.

Heterogeneity – In contrast to most stationary computers, mobile computers encounter more heterogeneous network connections. As they leave the range of one network transceiver they switch to another. In different places they may experience different network qualities. There may be places where they can access multiple transceivers, or even may concurrently use wired access. The interface may also need to change access protocols for different networks, for example when switching from wireless LAN coverage in an office to cellular coverage in a city. This heterogeneity makes mobile computing more complex than traditional networking.

In this thesis we concentrate on the problems related to Quality of Service and energy-efficiency.

Problem statement 1 – 5

#### 1.2.3 Energy efficiency

Although the subject of low-power consumption of integrated circuits (ICs) is drawing considerable attention ("cool chips are hot"), this interest is only of recent date. There are several motivations for energy-efficient design. Perhaps the most visible driving source is the success and growth of the portable consumer electronic market. Today's desktop computers are not intended to be carried, so their design is liberal in their use of space, weight, energy consumption, noise, cabling, and heat dissipation. In contrast, the designer of a hand-held mobile computer should strive for the properties of a wristwatch: light, small, durable and long battery life.

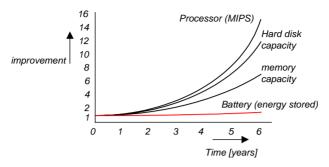

Batteries are the largest single source of weight in a portable computer. Minimising energy consumption can improve portability by reducing battery weight and lengthening the life of a charge. Moreover, the functionality of the mobile computer is limited by the required energy consumption for communication and computation. Unfortunately, the rate at which battery performance improves (in terms of available energy per unit size or weight) is fairly slow, despite the great interest generated by the booming wireless business. Aside from major breakthroughs it is doubtful that significant reduction of battery size and weight can be expected in the near future [21]. It has been generally expected that the battery technology alone will not solve the low-power problem. It therefore makes sense to look for alternative strategies for energy savings and energy management. The emerge of various applications and the need to support them in a wireless setting may open new possibilities for energy-saving strategies.

Remarkably, high performance computing systems also drives the low power needs. The power dissipation of high performance microprocessors is now already several dozen Watts, comparable to that of a hand-held soldering iron [25]. The *cost* associated with packaging and cooling such devices is becoming prohibitive.

In addition to cost, there is the issue of *reliability*. High power systems tend to increase the silicon temperature, and high temperature tends to exacerbate several silicon failure mechanisms. Every 10°C increase in operating temperature roughly doubles a component's failure rate [17].

Another major demand for low-power systems comes from *environmental concerns*. Computers are the fastest-growing electricity loads in the commercial sector [25]. Since electricity generation is a major source of pollution, inefficient energy usage in computing equipment indirectly contributes to environmental pollution.

Finally, a fraction of the consumed energy is radiated into space, possibly affecting other electronic equipment (Electro-Magnetic Compatibility, or EMC) [2].

The way out is *energy efficiency:* doing more work with the same amount of energy. Traditionally, energy efficiency has been focussed on low-power techniques for VLSI design. However, the key to energy efficiency in future mobile multimedia devices will be at the higher levels: energy-efficient system architectures, energy-efficient communication protocols, energy-cognisant operating system and applications, and a well designed partitioning of functions between wireless device and services on the network.

1-6 Introduction

A major challenge in achieving this will be that many attributes of the system environment can vary drastically by several orders of magnitude over the short and long term. Key to these issues will be *adaptability*. Research has shown that continually adapting the system and protocols can significantly improve the energy efficiency while maintaining a satisfactory level of performance [21]. Adapting to the variability is the shared responsibility of many layers in the system design of the mobile device, including the applications.

#### 1.2.4 Hypothesis

Energy efficiency and Quality of Service will be very important for mobile multimedia systems. In this dissertation the following two hypothesises are made:

- 1. The key to energy efficiency will be achieved in the design of the higher layers of the system, its system architecture, its functionality, its operating system, and the entire network. Of special importance in this are the communication channels.

- Quality of Service is an important mechanism for mobile multimedia systems not only to give users an adequate level of service, but also as a tool to achieve an energy efficient system.

#### 1.3 Approach

The research presented in this thesis addresses the design of an architecture for a mobile multimedia handheld computer that can cope with the requirements and difficulties mentioned above. The main focus is on the specification of a system architecture supporting the required functions for future handheld devices.

The approach made in our research was to study *practical* solutions to the inherent problems of handheld multimedia terminals. In this field too often, system architectures, protocols, and applications are developed with a theoretical background only and with a limited scope covering one horizontal layer in a system. In contrast, this research is characterised by a strategy that traverses *vertically* through various layers of the system architecture of a multimedia hand-held system and is driven by energy-efficient design considerations.

While low-level circuit and logic techniques have been well established for improving energy efficiency, they do not hold promise for much additional gain. As the issue of energy efficiency becomes even more pervasive, the battle to use the bare minimum of energy will be fought on multiple fronts: semiconductor technology, circuit design, design automation tools, system architecture, operating system, and application design. The key to energy efficiency in future mobile systems will be designing higher layers of the mobile system, its system architecture, its functionality, its operating system, and indeed the entire network, with energy efficiency in mind.

Approach 1–7

In its most abstract form, a networked computer system has two sources of energy drain required for operation:

- *Communication*, due to energy spent by the wireless interface and due to the internal traffic between various parts of the system, and

- *Computation*, due to processing for applications, the operating system, and tasks required during communication.

Broadly speaking, minimising energy consumption is a task that will require minimising the contributions of communication and computation, making the appropriate trade-offs between the two. For example, reducing the amount of transmitted data may be beneficial. On the other hand, the computation cost (e.g. to compress the data being sent) might be high, and in the extreme it might be such that it would be better to just send the raw data.

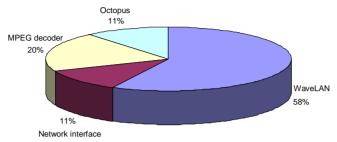

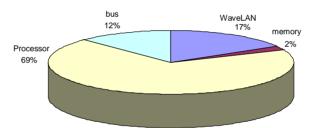

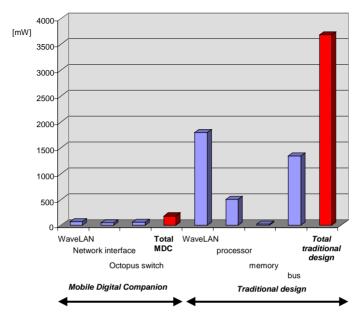

In this thesis we will concentrate on the *communication channels* rather than the computational elements. The communication channels contribute a significant amount of the total energy consumption of a typical mobile system. This property also holds for multimedia applications, even though these applications typically require a significant computational effort as well. This is for a significant part due to the limitations of most current hardware and operating systems that are unable to differentiate between various traffic streams. A general theme in this thesis is to reduce the amount of communication and avoid 'useless' and inefficient computation, which consequently reduces energy dissipation and increases performance of the system.

Specific contributions of the research described in this thesis are the design of an energy-efficient architecture for mobile multimedia systems and a reconfigurable connection switch, as well as the design of crucial wireless network functions (i.e. MAC protocol, adaptable network interface, and a model for adaptable error-correction) that are energy efficient and can support multimedia traffic.

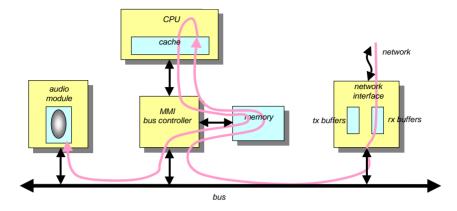

#### 1.3.1 System architecture

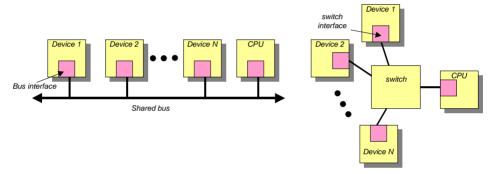

The traditional architecture of a mobile is centered around a general-purpose processor with local memory and a shared-bus that connects peripherals to the CPU. However, in such an architecture several problem areas can be identified. Main problem areas are energy consumption, performance, and Quality of Service guarantees.

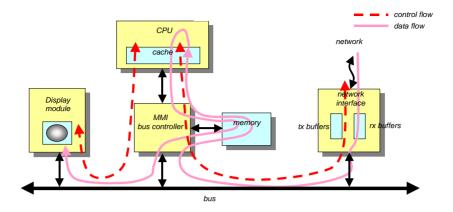

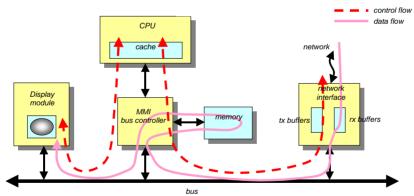

A large fraction of system time and power budget in a shared bus architecture is devoted to bus transactions. Busses are significant sources of power dissipation due to high switching activities and large capacitance. This architecture requires frequent traversal of multimedia streams over the bus and through the layers of the operating system software, and possibly also through to a network protocol stack which is composed of transport, network, link and medium access (MAC), and physical layer protocols. Typical functions in the network protocol stack include routing, congestion control, error control, resource reservation, scheduling, etc. Instead of arithmetic functions like additions and multiplications, the primary importance in the system is processing of the protocols.

1 – 8 Introduction

Current systems based on a shared bus architecture are able to deliver the required performance for various multimedia applications not only by using the rapid advance in technology, but also by careful design and use of the interface modules. The process to achieve this requires a huge amount of effort of both the hardware designer of the I/O interfaces and the system designer. There are many subtle device issues that can influence the overall I/O performance of a system. Minor changes in the hardware or software configuration can have severe consequences for the performance of the system. The reason for these problems are often caused by the interconnect and the interconnection protocols. Since a shared bus cannot give QoS guarantees, a single device or application can reduce the throughput that is available for all devices.

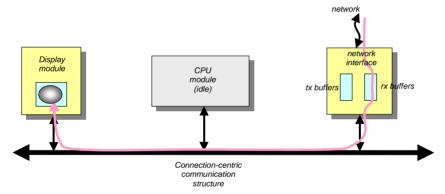

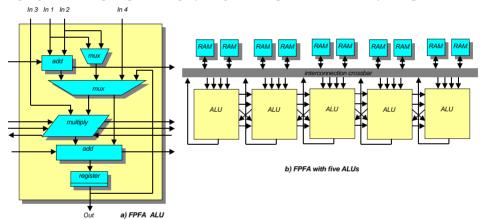

By designing a *connection-centric* architecture that moves processing power closer to the data stream, it is possible to solve these problems. The whole system is based on connections between modules. Each connection is associated with a certain QoS. This approach is especially well suited for continuous media data (e.g. audio, video, etc.), where the processing is actually of a very specialised nature (e.g. signal processing, compression, encryption, etc.) and needs to be carried out in real-time. In contrast to memory-centric (or CPU-centric) systems, a connection-centric system is decomposed out of application-specific modules. In such a system the data traffic is reduced, mainly because unnecessary data copies are removed. For example, in a system where a stream of video data is to be displayed on a screen, the data can be copied directly to the screen memory, without going through the main processor. The CPU is thus moved out of the data flow datapath, although it still participates in the control flow. The role of the CPU is reduced to a controller that initialises the system and handles complex protocol processing that are most easily implemented in software.

The approach used in our research to achieve a system as described above is to have autonomous, reconfigurable modules such as network, video and audio devices, interconnected by a switch rather than by a bus, and to offload as much as work as possible from the CPU to modules placed in the data streams. Thus, communication between components is not broadcast over a bus but delivered exactly where it is needed, work is carried out where the data passes through, bypassing the memory. To limit the communication overhead and the required buffering, the granularity of the tasks on the devices is rather coarse, and the application is partitioned in large blocks. The programmability of each module is more fine-grained and is controlled by the individual autonomous module.

The interconnect of the architecture is based on a reconfigurable communication network switch, called *Octopus*, which interconnects a general-purpose processor, (multimedia) devices, and a wireless network interface. Conceptually, the architecture is analogous to a self-routing packet switch. The connection-oriented approach using fixed sized cells and the asynchronous multiplexing are key factors. This not only eliminates the need to transfer a large number of address bits per access, it also gives the system the possibility to control the QoS of a task down to the communication infrastructure. All connections are identified with a connection identifier, which is used to identify the type of data, and the module destination address. This identifier provides the mechanism to support lightweight protocols that provide data-specific transport services that are

Approach 1 – 9

associated with a certain QoS. This is an important requirement since in a QoS architecture all system components, hardware as well as software, have to be covered end-to-end along the way from the source to the destination.

#### 1.3.2 Wireless communication

Another important aspect in mobile multimedia systems is wireless communication protocols that provide multimedia services to mobile users. Multimedia applications are characterised by their various media streams. Each stream can have different quality of service requirements. Depending on the service class and QoS of a connection a different policy can be applied by the communication protocol in order to minimise energy consumption. For example, by avoiding error-control overhead for connections that do not need it and by never transmitting stale data, efficiency is improved. This combination of limited bandwidth, high error rates, and delay-sensitive data requires tight integration of all subsystems in the device, including aggressive optimisation of the protocols that suits the intended application. The protocols must be robust in the presence of errors and they must be able to differentiate between classes of data, giving each class the exact service it requires.

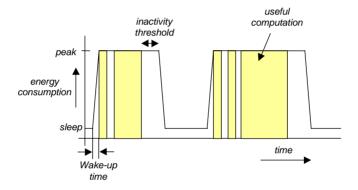

The access to the wireless channel is controlled by data link protocols. Many protocols for wireless networks are basically adaptations of protocols used in wired networks, and ignore energy issues. A first step in improving the energy efficiency of the wireless network protocols is to *eliminate useless activity* of the wireless interface. There are various reasons for this useless activity. It has been shown that for typical applications like a web-browser or e-mail, the energy consumed while the interface is 'on' and idle is more than the cost of actually receiving packets. That is because most applications have little demanding traffic needs, and hence the transceiver is idling most of the time. Furthermore, in a typical wireless broadcast environment, the receiver has to be powered 'on' at all times to be able to receive messages from the base station, resulting in significant energy consumption. The receiver subsystem typically receives all packets and forwards only the packets destined for this mobile. Another cause is due to the inactivity threshold, which is the time before a transceiver will go in the 'off' or 'standby' state after a period of inactivity, which causes the receiver to be in an energy consuming mode needlessly for a significant time. Significant time and energy is further spent by the mobile in switching from transmit to receive modes, and vice-versa.

The next step is to *reduce the amount of data*, which must be pushed through the channel. This goal can be reached in a number of ways. One is to reduce the *overhead of a protocol* which influences the energy requirements due to the amount of 'useless' control data and the required computation for protocol handling. Another step is to avoid *collisions* that typically may occur in broadcast networks. This causes the data to become useless and the energy needed to transport that data to be lost. The high *error rate* that is typical for wireless links is another source of energy consumption for several reasons. First, when the data is not correctly received the energy that was needed to transport and process that data is spoiled. Second, energy is used for error control mechanisms. This includes energy spent in the physical radio transmission process, as well as energy spent in computation, such as signal processing and error control at the

1 – 10 Introduction

transmitter and the receiver. Finally, because in wireless communication the error rate varies dynamically over time and space, a fixed-point error control mechanism that is designed to be able to correct errors that hardly occur, spoils energy and bandwidth. If the application is error-resilient, trying to withstand all possible errors spoils even more energy for needless error control. Reducing the amount of data is also an application-layer issue. For example, the application might change the compression rate or possibly reduce the data resolution. Instead of sending an entire large full-colour image, one can send black-and-white half-size images with lossy compression.

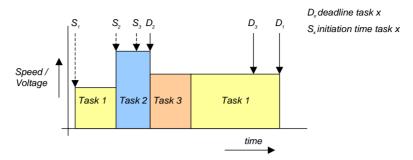

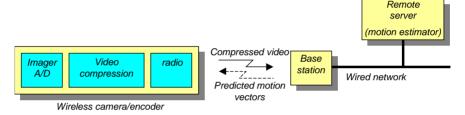

The goals of low energy consumption and the required support for multiple traffic types lead to the communication system described in this thesis that is based on reservation and scheduling strategies. For each connection a different set of parameters concerning scheduling, flow control and error control is applied. The wireless network is composed of several base-stations that each handle a single radio cell possibly covering several mobile stations. The base-station controls access on the wireless channel based on communication requests for connections of the mobiles by dividing bandwidth into transmission slots. The key to providing QoS for these connections and the energy efficiency of the mobiles will be the scheduling algorithm that assigns the bandwidth. The premise is that the base-station has virtually no processing and energy limitations, and will perform actions in courtesy of the mobile. The main principles are: avoid unsuccessful actions by avoiding collisions and by providing provisions for adaptive error control, minimise the number of transitions by scheduling traffic in larger packets, synchronise the mobile and the base-station which allows the mobile to power-on precisely when needed, and migrate as much as possible work to the base-station.

#### 1.4 Related work

The growing popularity of mobile systems has spawned much interest and research by industry and universities in both computer science and electrical engineering. Most of the current research, however, often tackles just one horizontal layer of the design. Although this research is valuable, and must be applied whenever suitable, we will provide here merely a brief overview of those systems and current research that look into the problem of designing a mobile multimedia device in an integrated fashion. We do not include the wireless devices that are on the market today, because, as discussed above, they are somewhere in the spectrum between portable computers with a wireless interface and a wireless phone. They fail to address the specific requirements and fail to exploit the possibilities offered by multimedia communication. The related research of the specific issues of the mobile computer system architecture (like interconnection structures, medium access and data link protocols) is reviewed in the corresponding chapters in this thesis.

Currently, there is a broad consensus that the existing mobile devices are by far not capable of supporting the required multimedia functionality. Some reasons are: processing power, energy consumption, communication bandwidth requirements, etc.

Related work 1-11

About the solution to solve this problem there is much less consensus, however. Within the notion of mobile computing, there is considerable latitude regarding the role of the portable device. Is it a terminal or an independent, stand-alone computer? How many purposes shall the device serve? Many different architectural choices are possible, each with a different partitioning of functions between the wireless device and remote servers. These design choices greatly affect the issues mentioned in this chapter.

Several architectures have been proposed that address mobile multimedia computing. Only few systems address energy reduction. Systems like the *InfoPad* [24] and *ParcTab* [6] are designed to take advantage of high-speed wireless networking to reduce the amount of computation required on the portable. These systems are portable terminals and take advantage of the processing power of remote compute servers. No local computation, except for appropriate coding/decoding of the I/O data, is done at the pad. Such devices are known as *thin clients*, since the client itself does little work. This approach simplifies the design and reduces power consumption for the processing components, but significantly increases the network usage and thus potentially increases energy consumption because the network interface is energy expensive. These systems also rely on the availability of a high bandwidth network connectivity and cannot be used when not connected.

In the Ubiquitous Communications project (*Ubicom*) [26] at the Delft University of Technology the clients also depend heavily on the wireless communication network. This project aims at developing a campus-wide system for wireless communication that is capable of supporting multimedia applications. The target is a visual geographic information system that uses augmented reality techniques to display information on a mobile user's headset; information is super-imposed on the user's view using a retinal scanning display. To minimise energy consumption in the mobile unit, the main processing power is located in the backbone network.

The *Merlin* project of the University of California at Los Angeles (UCLA) [21][18] is developing mobile computing and wireless communication technologies with the focus on creating a wireless I/O-network subsystem that can be used to create many different types of wireless connected multimedia nodes: handheld computes, wireless cameras, wireless IP phones, etc. The subsystem is composed of a wireless network processor, codecs, and radio to provide all the necessary wireless networking and multimedia processing capabilities. In the architecture of *WAND*, a low-power embeddable module built at UCLA for creating multimedia wireless terminals, the general-purpose processor is moved out of the packet flow data path, and the data streams flow directly between the radio and the speech and image codecs. A full-fledged PC or PDA may be adjunct to WAND, but its presence is optional and, in many wireless terminals unnecessary.

Other research is mainly concentrated on specific topics, and is not covering the system architecture of a mobile computer as a whole. There is much research on multimedia processors, hardware accelerators, and heterogeneous multiprocessor architectures mainly targeted for DSP algorithms (e.g. [1][18][20]). In recent years much research has been done in providing QoS over a wireless link. Access protocols for these systems typically only address network performance metrics such as throughput, efficiency, and packet delay. However, thus far, little attention is given to energy conserving protocols,

1 – 12 Introduction

and researchers mainly focuses their effort on energy reduction by circuit design. Very recently there is a growing interest in energy-efficient design, although mainly concentrating on medium access and link-layer energy reduction techniques. Chapters 5 and 6 give more details on this research.

#### 1.5 Thesis overview

This thesis is divided into 6 chapters. This chapter has presented a survey of the principal challenges faced when designing a mobile multimedia handheld computer. It presented a motivation for and introduction to the low-power methodologies and systems that will be presented in subsequent chapters. The following chapters are largely based on papers presented at conferences and published in journals. The structure of the thesis is guided along these papers.

Chapter 2 will describe low-power design techniques at all levels ranging from process technology to applications, and will motivate the need for a vertical system-wide energy-efficient design approach. The chapter does not aim to be a complete presentation in the field, but is instead focussed on issues of relevance to the discussion in other chapters of the dissertation.

The chapter is based on papers [6], [7] and [9]:

- "Design techniques for low power systems", Havinga P.J.M., Smit G.J.M., *Journal of Systems Architecture*, Vol. 46, Issue 1, 2000.

- "Minimizing energy consumption for wireless computers in Moby Dick", Havinga, P.J.M., Smit, G.J.M., *Proceedings IEEE International Conference on Personal Wireless Communication (ICPWC'97)*, pp. 306-310, December 1997.

- "Minimizing energy consumption for handheld computers in Moby Dick", Havinga P.J.M., Smit G.J.M., *Proceedings of the 23<sup>rd</sup> Euromicro Conference 97*, pp. 196-201, September 1997.

Chapter 3 addresses fundamental issues in the architecture, design and implementation of low-power multimedia hand-held computers, with particular emphasis on energy conservation. This chapter introduces the system architecture of the portable computer that is topic of our research, called *Mobile Digital Companion*, which provides support for handling multimedia applications efficiently. The Mobile Digital Companion saves energy by using system decomposition at different levels of the architecture and exploits locality of reference with dedicated, optimised modules. The approach is based on dedicated functionality and the extensive use of energy reduction techniques at all levels of system design. The system has an architecture with a general-purpose processor accompanied by a set of heterogeneous autonomous programmable modules, each providing an energy efficient implementation of dedicated tasks.

Thesis overview 1-13

Chapter 3 is based on papers [8] and [22]:

• "The Pocket Companion's architecture", Havinga P.J.M., Smit G.J.M., *I*<sup>st</sup> Euromicro summer school on mobile computing '98, pp. 25-34, Oulu, August 1998.

• "An overview of the Moby Dick project", Smit G.J.M., Havinga P.J.M., et al., 1<sup>st</sup> Euromicro summer school on mobile computing '98, pp. 159-168, Oulu, August 1998.

Chapter 4 presents the reconfigurable internal communication network switch, called *Octopus*. The switch is implemented as a simplified ATM switch and provides Quality of Service guarantees and enough bandwidth for multimedia applications found in a handheld computer. We have built a testbed of the architecture, of which we will present performance and energy consumption characteristics.

Chapter 4 is based on papers [11] and [14]:

- "Octopus: embracing the energy efficiency of handheld multimedia computers", Havinga P.J.M., Smit G.J.M., *Proceedings fifth annual ACM/IEEE international conference on mobile computing and networking (Mobicom'99)*, pp. 77-87, August 1999.

- "Octopus an energy-efficient architecture for wireless multimedia systems", Havinga P.J.M., Smit G.J.M., *Proceedings ProRISC workshop on Circuits, Systems and Signal Processing (ProRISC'99)*, pp. 185-192, November 1999.

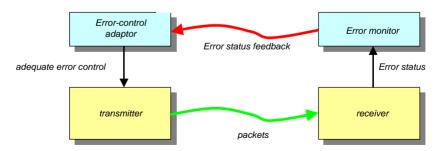

In Chapter 5 we delve into the problems related to wireless communication. We present an energy-efficient highly adaptive architecture of a network interface and novel data link layer protocol for wireless networks that provides Quality of Service (QoS) support for diverse traffic types. In our approach we apply adaptability through all layers of the protocol stack, and provide feedback to the applications. In this way the applications can adapt the data streams, and the network protocols can adapt the communication parameters. Since high error rates are inevitable to the wireless environment, *energy-efficient error control* is an important issue for mobile computing systems. We therefore investigate the energy efficiency of error-control mechanisms that can be used to build adaptive error-control schemes.

Chapter 5 is based on papers [10], [12] and [13]:

- "Energy efficient wireless ATM design", Havinga P.J.M., Smit G.J.M., Bos M., to appear in ACM/Baltzer Journal on Mobile Networks and Applications (MONET), Special issue on Wireless Mobile ATM technologies, Vol. 5, No 2., 2000.

- "Energy efficiency of error correction on wireless systems", Havinga P.J.M., Proceedings IEEE Wireless Communications and Networking Conference (WCNC'99), September 1999.

- "Energy efficient wireless ATM design", Havinga P.J.M., Smit G.J.M., Bos M., *Proceedings second IEEE international workshop on wireless mobile ATM implementations (wmATM'99)*, pp. 11-22, June 1999.

To conclude, Chapter 6 gives a brief evaluation, provides directions for future research, and gives some general conclusions.

1 – 14 Introduction

#### References

[1] Abnous A., Seno K., Ichikawa Y., Wan M., Rabaey J.: "Evaluation of a low-power reconfigurable DSP architecture", proceedings 5<sup>th</sup> Reconfigurable Architectures workshop (RAW'98), March 30, 1998, Orlando, USA. (URL: <a href="http://xputers.informatik.uni-kl.de/RAW/RAW98/adv\_prg\_RAW98.html">http://xputers.informatik.uni-kl.de/RAW/RAW98/adv\_prg\_RAW98.html</a>)

- [2] Berkel K. van, Rem M.: "VLSI programming of asynchronous circuits for low power", Nat. Lab. Technical Note Nr. UR 005/94, Philips Research Laboratories, Eindhoven, the Netherlands, 1994.

- [3] Black A., Inouye J.: "System support for mobility", proceedings 1996 SIGOPS European Workshop, pp.129-132, 1996.

- [4] "Rock 'n' Scroll Button-free Tilt and Gesture Input for Itsy", http://www.research.digital.com/wrl/projects/RocknScroll/RocknScrollOverview.htm.

- [5] Forman G.H.: "The challenges of mobile computing", UW CSE Tech report # 93-11-03, ftp.cs.washington.edu.

- [6] Havinga, P.J.M., Smit, G.J.M.: "Minimizing energy consumption for wireless computers in Moby Dick", proceedings IEEE International Conference on Personal Wireless Communication ICPWC'97, pp. 306-310, December 1997.

- [7] Havinga P.J.M., Smit G.J.M.: "Minimizing energy consumption for handheld computers in Moby Dick", *Proceedings of the 23<sup>rd</sup> Euromicro Conference 97*, pp. 196-201, September 1997.

- [8] Havinga P.J.M., Smit G.J.M.: "The Pocket Companion's architecture", *Euromicro summer school on mobile computing* '98, Oulu, pp. 25-34, August 1998

- [9] Havinga P.J.M., Smit G.J.M.: "Design techniques for low power systems" *Journal of Systems Architecture*, Vol. 46, Iss. 1, 2000, a previous version appeared as CTIT Technical report, No. 97-32, Enschede, the Netherlands, ISSN 1381-3625

- [10] Havinga P.J.M., Smit G.J.M., Bos M.: "Energy efficient wireless ATM design", proceedings second IEEE international workshop on wireless mobile ATM implementations (wmATM'99), pp. 11-22, June 1999.

- [11] Havinga P.J.M., Smit G.J.M.: "Octopus: embracing the energy efficiency of handheld multimedia computers", proceedings fifth annual ACM/IEEE international conference on mobile computing and networking (Mobicom'99), pp.77-87, August 1999.

- [12] Havinga P.J.M.: "Energy efficiency of error correction on wireless systems", proceedings IEEE Wireless Communications and Networking Conference (WCNC'99), September 1999.

- [13] Havinga P.J.M., Smit G.J.M., Bos M.: "Energy efficient wireless ATM design", to appear in ACM/Baltzer Journal on Mobile Networks and Applications (MONET), Special issue on Wireless Mobile ATM technologies, Vol. 5, No 2., 2000.

- [14] Havinga P.J.M., Smit G.J.M.: "Octopus an energy-efficient architecture for wireless multimedia systems", *Proceedings Program for Research on Integrated Systems and Circuits (ProRISC'99)*, pp. 185-192, November 1999.

References 1 – 15

[15] Kantarjiev C. et al.: "Experiences with X in a wireless environment", Mobile and locationindependent computing symposium, Cambridge MA, August 1993.

- [16] Kozyrakis C.E., Patterson D.A.: "A new direction for computer architecture research", Computer, Nov. 1998, pp. 24-32.

- [17] Landman P.E.: "Low-power architectural design methodologies", Ph.D. thesis, *University of California at Berkeley*, 1994.

- [18] Leijten J.A.J.: "Real-time constrained reconfigurable communication between embedded processors", *Ph.D. thesis, Eindhoven University of Technology*, November 1998.

- [19] Lettieri P., Srivastava M.B.: "Advances in wireless terminals", *IEEE Personal Communications*, pp. 6-19, February 1999.

- [20] Nieuwland A.K., Lippens P.E.R.: "A heterogeneous HW-SW architecture for hand-held multi-media terminals", proceedings IEEE workshop on Signal Processing Systems, SiPS'98, pp. 113-122, 1998.

- [21] Sheng S., Chandrakasan A., Brodersen R.W.: "A Portable Multimedia Terminal", *IEEE Communications Magazine*, pp. 64-75, vol. 30, no. 12, Dec., 1992.

- [22] Smit G.J.M., Havinga P.J.M., et al.: "An overview of the Moby Dick project", *Ist Euromicro summer school on mobile computing*, pp. 159-168, Oulu, August 1998.

- [23] Srivastava M.: "Design and optimization of networked wireless information systems", IEEE VLSI workshop, April 1998.

- [24] Truman T.E., Pering T., Doering R., Brodersen R.W.: The InfoPad multimedia terminal: a portable device for wireless information access", *IEEE transactions on computers*, Vol. 47, No. 10, pp. 1073-1087, October 1998.

- [25] Yeap G.K.: "Practical low power digital VLSI design", Kluwer Academic Publishers, ISBN 0-7923-80.

- [26] Toetenel H.: "The ubiquitous communication program", Euromicro summer school on mobile computing '98, Oulu, pp. 181-189, August 1998, http://ubicom.twi.tudelft.nl.

- [27] Weiser M.: "Some computer science issues in ubiquitous computing", *Communications of the ACM*, 36(7):75-84, July 1993.

1 – 16 Introduction

# Design techniques for energy efficient and low-power systems

Portable systems are being used increasingly. Because these systems are battery powered, reducing energy consumption is vital. In this chapter we give an overview of low-power design and provide a review of techniques to exploit them in the architecture of the system. We focus on: minimising capacitance, avoiding unnecessary and wasteful activity, and reducing voltage and frequency. We review energy reduction techniques with applications in the architecture and design of a hand-held computer including its wireless communication system.

#### 2.1 Introduction

The portability requirement of hand-held computers and other portable devices places severe restrictions on size and power consumption. Even though battery technology is improving continuously and processors and displays are rapidly improving in terms of power consumption, battery life and battery weight are issues that will have a marked influence on how hand-held computers can be used. These devices often require real-time processing capabilities, and thus demand high throughput. Power consumption is becoming the limiting factor in the amount of functionality that can be placed in these devices. More extensive and continuous use of network services will only aggravate this problem since communication consumes relatively much energy. Research is needed to provide policies for careful management of the energy consumption while still providing the appearance of continuous connections to system services and applications. In this chapter<sup>1</sup> we will explore sources of energy consumption and provide a variety of energy reduction techniques at various levels in the design flow of a computer system. We will

<sup>&</sup>lt;sup>1</sup> Major parts of this chapter will be published in the *Journal of Systems Architecture*, 2000 [25] and were presented at the *IEEE International Conference on Personal Wireless Communications* (ICPWC'97), 1997 [24].

try to point out the main driving forces in current research. This provides the foundation of the techniques we have applied in the design of the *Mobile Digital Companion* that is topic of the research presented in this thesis.

#### 2.1.1 The advance of technology

The semiconductor technology has continuously improved and has lead to ever smaller dimensions of transistors, higher packaging density, faster circuits, and lower power dissipation. Over a three year period from 1998 to 2001 there will be a factor 100 increase in 3D graphics performance and nearly a factor 10 increase in hard disk capacity - far outstripping Moore's law [81]. The bandwidth of wireless networks has doubled every six months. Significant new features are being added. Video capturing, for example, is becoming a mainstream feature with MPEG-2 video encoding and decoding available on low-cost video adapters. These dramatic improvements are occurring even as the cost of computing for the average user is quickly dropping. This has been possible due to the use of parallel hardware, on-chip memory (RAM), new algorithms, and the increased level of integration of IC technology. Over the past five years, feature sizes have dropped from about 0.8µm to about 0.35µm. Semiconductor Industry Associates (SIA) have developed a road map for the next few years [62]. It is expected that a feature size of 0.1µm will be reached in 2007 within the context of our current CMOS technology. Such advances provide an effective area increase of about an order of magnitude. To avoid the effect of high-electric fields, which is present in very small devices, and to avoid the overheating of the devices, power supply must be scaled down. The power supply voltage is expected to be as low as 0.9 V in 2007.

The rapid advance in technology can be used for several purposes. It can be used to increase performance, to add functionality, but also to reduce energy consumption. One way to use this opportunity would be to continue advancing our chip architectures and technologies as just more of the same: building microprocessors that are simply more complicated versions of the kind built today. For more than thirty years, performance optimisation has been extensively studied at all abstraction levels. The current trend in industry is to focus on high-performance processors, as this is the area in which a semiconductor vendor can enhance status [10]. Therefore, the architecture of a general-purpose processor is most widely studied, and optimisations for processor performance is the main goal. Technology innovation has lead to a number of processor improvements like superscalar technology, multi-level pipelines, large on-chip caches, etc.

Another environment that will become more important in the near future is that of application specific or embedded processors. The goal of these processors is to optimise the overall cost-performance of the system, and not performance alone. The modern application-specific processors can use the novel technology to increase functionality such as compression and decompression, network access, and security functions.

Introduction 2-3

#### Energy consumption

Power consumption has become a major concern because of the ever-increasing density of solid-state electronic devices, coupled with an increasing use of mobile computers and portable communication devices. The technology has thus far helped to build low-power systems. The speed-power efficiency has indeed gone up since 1990 by 10 times each 2.5 years for general-purpose processors and digital signal processors (DSPs). Table 1 shows the performance and power consumption of some recent processors [71]. However, this help will slow down, because physical limits seem to be reached soon.

| Processor           | MHz | Year | SPECint-95 | Watts | Watts/SPECint |

|---------------------|-----|------|------------|-------|---------------|

| P54VRT (Mobile)     | 150 | 1996 | 4.6        | 3.8   | 0.83          |

| P55VRT (Mobile MMX) | 233 | 1997 | 7.1        | 3.9   | 0.55          |

| PowerPC 603e        | 300 | 1997 | 7.4        | 3.5   | 0.47          |

| PowerPC 740 (G3)    | 300 | 1998 | 12.2       | 3.4   | 0.28          |

| Mobile Celeron      | 333 | 1999 | 13.1       | 8.6   | 0.65          |

Table 1: Speed and power characteristics of some recent processors.