# Identifying Failure Mechanisms in LDMOS Transistors by Analytical Stability Analysis

A. Ferrara, P.G. Steeneken, B.K. Boksteen, A. Heringa, A.J. Scholten, J. Schmitz, and R.J.E. Hueting

Abstract—In this work, analytical stability equations are derived and combined with a physics-based model of an LDMOS transistor in order to identify the primary cause of failure in different operating and bias conditions. It is found that there is a gradual boundary between an electrical failure region at high drain voltage and a thermal failure region at high junction temperature. The theoretical results are mapped onto a 3D space comprising gate-width normalized drain current, drain voltage and junction temperature, allowing an immediate visualization of the different failure mechanisms. The validity of the proposed analysis is supported by measurements of the safe operating limits of silicon-on-insulator (SOI) LDMOS transistors.

Index Terms—Power MOSFET, Silicon-on-insulator (SOI), electro-thermal coupling, electrical runaway, thermal runaway, parasitic bipolar, impact ionization, self-heating, Safe Operating Area (SOA), Safe Operating Volume (SOV), stability factor, failure function.

#### I. Introduction

In power transistors, failure is often associated to instability, which causes one or more device parameters (current, voltage and/or temperature) to diverge (runaway) [1]. Stability can be experimentally investigated by measuring the device characteristics close to the failure limit [2]–[6]. This allows calculation of a stability factor that is a measure of the device sensitivity to runaway. However, such a procedure has two drawbacks: 1) it can degrade device reliability; 2) it detects the occurrence of instability but not its physical origin (electrical or thermal). In order to overcome the first drawback, physics-based models [2], [3], [5], [7], [8] or TCAD simulations [9] have been used to predict and quantify instability. However, modeling and simulating runaway effects causes the output parameters to diverge and makes it difficult to identify the physical origin of the numerical instability.

In this work, it is shown how an analytical stability analysis can be used to identify the boundary between electrical and thermal failure mechanisms (Fig. 1). Electrical and thermal stability factors (and corresponding failure functions) are defined (Figs. 2-3) assuming that self-heating does not play a role in electrical runaway, while avalanche breakdown and parasitic bipolar do not affect thermal stability.

Device failure can be related to an electro-thermal stability

Manuscript changed June 30, 2014

This work is a part of the Dutch Point-One program and is supported financially by Agentschap NL, an agency of the Dutch Ministry of Economic Affairs. A. Ferrara, B.K. Boksteen, J. Schmitz and R.J.E. Hueting are with the MESA+ Institute for Nanotechnology, University of Twente, Enschede, The Netherlands (e-mail: a.ferrara@utwente.nl).

P.G. Steeneken is with NXP Semiconductors, The Netherlands and Delft University of Technology, Delft, the Netherlands. A. Heringa and A.J. Scholten are with NXP Semiconductors, The Netherlands.

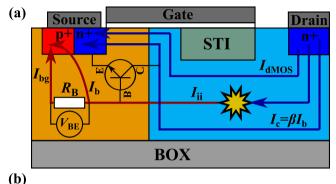

Fig. 1: a) Parasitic bipolar and avalanche multiplication in the operation of an LDMOS transistor. b) Schematic of the Safe Operating Area (SOA), showing the failure and operating functions which are analytically investigated in this work.

factor (failure function) including both the electrical and thermal failure mechanisms. The individual analysis of runaway mechanisms allows determination of the relative contributions of electrical and thermal phenomena to failure, thus identifying the primary cause of runaway. This knowledge allows one to determine, depending on the operating conditions, whether the electrical or thermal device properties (or both) need to be improved to increase the Safe Operating Area (SOA).

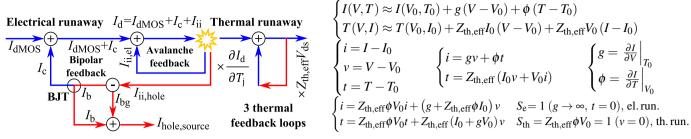

The stability equations (Figs. 2-3) need to be combined with models of the different current contributions in an LDMOS (MOS current  $I_{\rm dMOS}$ , bipolar base and collector currents  $I_{\rm b}$  and  $I_{\rm c}$ , and impact ionization current  $I_{\rm ii}$ ) and their temperature dependencies. For this purpose analytical models for LDMOS transistors, TCAD simulations, experimental data or combinations can be used [2], [3], [5], [7]–[10]. In this work, physics-based analytical expressions [11], [12] with experimental [6] fitting parameters have been used (Appendix).

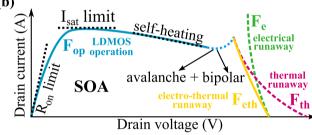

Fig. 2: Left. Schematic representation of the origin of electrical and thermal runaway. Right. Procedure for deriving the analytical stability equations by linearization around a bias point  $(V_0, I_0, T_0)$ . Applying these equations to  $I_{\text{dMOS}}$ ,  $I_{\text{c}}$  and  $I_{\text{ii}}$  and combining the results leads to the actual expressions for the stability factors and failure functions in Fig. 3.

#### II. ORIGIN OF ELECTRO-THERMAL RUNAWAY

# A. Feedback mechanisms

A general overview of the positive electrical and thermal feedback mechanisms leading to instability and runaway is provided in Fig. 1. At high drain voltages  $V_{ds}$ , the MOS electron current  $I_{\rm dMOS}$  generates electron-hole pairs contributing to an impact ionization current  $I_{ii}$  with an electron and a hole component. The electrons flow towards the highly doped  $n^+$ drain contact, the holes move towards the  $p^+$  body contact inducing a voltage drop  $V_{\rm BE}$  over the base resistance  $R_{\rm B}$ . This switches on the internal parasitic bipolar with a base current  $I_{\rm b}$  and a corresponding collector current  $I_{\rm c} \approx \beta I_{\rm b}$ , where  $\beta$ is the current gain. This current  $I_c$  is in turn multiplied by avalanche when flowing in the drift extension, resulting in a positive feedback behavior. Self-heating [5], [8], [13] is included in the model by introducing an effective thermal impedance  $Z_{\text{th,eff}} \approx (T_{\text{i}} - T_{\text{amb}})/P_{\text{d}}$  [6], where it is assumed for simplicity that the dissipated power  $P_d$  is independent of pulse time  $t_{\text{pulse}}$ .

# B. Electrical, thermal and electro-thermal failure

Electrical failure occurs because of the interaction of the parasitic bipolar with the current  $I_{ii}$ . Part of this current flows through the base of the bipolar and contributes to  $I_c \approx \beta I_b$ , which is avalanche multiplied and fed back into the base. Thermal failure can occur because of thermal runaway in each of the current components  $I_{dMOS}$ ,  $I_c$  or  $I_{ii}$ . The temperature coefficient of  $I_{\rm dMOS}$  depends on  $V_{\rm gs}$  [14],  $I_{\rm ii}$  has a slightlynegative temperature coefficient [15] (not included in the model), and  $I_c$  has a positive temperature coefficient [16]. In most cases, the increase in  $I_c$  (also including thermal leakage) induced by self-heating determines thermal instability [2], [3], [5], [8]. However, for  $V_{\rm gs}$  below the zero-temperature coefficient point,  $I_{\rm dMOS}$  also contributes to instability [5], [8], [14]. Although electrical and thermal failure mechanisms often both play a role in transistor failure, their relative contributions can be identified by introducing the analytical failure functions  $F_{\rm e}$  and  $F_{\rm th}$  (Fig. 1b)).

#### III. ANALYTICAL STABILITY ANALYSIS

# A. Stability factors and failure functions

In order to quantify the relative contributions of electrical [17] and thermal [5], [8] runaway to coupled electro-thermal [2], [9], [18] failure mechanisms, analytical stability equations are derived following the linearization procedure in Fig. 2. The electrical, thermal and electro-thermal stability factors

$$\begin{cases} I_{\text{li}} = (M-1) \left( I_{\text{dMOS}} + I_{\text{c}} \right) & \textbf{(1a)} \\ I_{\text{bg}} = \frac{V_{BE}}{R_{\text{B}}} & \textbf{(1b)} \\ I_{\text{li}} = I_{\text{bg}} + I_{\text{b}} \Rightarrow V_{\text{BE}} = c_1 + c_2 \cdot \exp\left(\frac{V_{\text{BE}}}{V_{\text{T}}}\right) & \textbf{(1c)} \\ c_1 = R_{\text{B}} (M-1) \cdot \left( I_{\text{dMOS}} + I_{R} \right) & \textbf{(1d)} \\ c_2 = R_{\text{B}} \left[ \beta (M-1) - 1 \right] \frac{I_{\text{S}}}{\beta} & \textbf{(1e)} \\ I_{\text{dn}} = M \cdot \frac{\left( I_{\text{dMOS}} + I_{c} \right)}{W_{\text{gate}}} = f_{\text{e}} \left( V_{\text{gs}}, V_{\text{ds}}, V_{\text{BE}}, T_{\text{j}} \right) & \textbf{(2a)} \\ T_{\text{j}} = T_{\text{amb}} + Z_{\text{th,eff}} \left( t_{\text{pulse}}, A \right) W_{\text{gate}} V_{\text{ds}} I_{\text{dn}} & \textbf{(2b)} \\ \left\{ \phi_{\text{dMOS}} = \frac{\partial I_{\text{dMOS}}}{\partial T_{\text{j}}} \right|_{V_{\text{gs}}, V_{\text{ds}}} & \textbf{(3a)} \\ \phi_{\text{c}} = \frac{\partial I_{\text{c}}}{\partial T_{\text{j}}} \right|_{V_{\text{BE}}} & \textbf{(3b)} \\ S_{\text{e}} = \beta (M-1) - \frac{r_{\text{b}}}{R_{\text{B}}}, r_{\text{b}} = \frac{\partial V_{\text{BE}}}{\partial I_{\text{b}}} \right|_{T_{\text{j}}} & \textbf{(3c)} \\ S_{\text{th}} = Z_{\text{th,eff}} V_{\text{ds}} \cdot \left( \phi_{\text{dMOS}} + \phi_{\text{c}} |_{V_{\text{BE}}} = 0 \right) & \textbf{(3d)} \\ S_{\text{eth}} = Z_{\text{th,eff}} V_{\text{ds}} \cdot \left( \phi_{\text{dMOS}} + \phi_{\text{c}} |_{V_{\text{BE}}} \right) & \textbf{(3d)} \\ S_{\text{eth}} = Z_{\text{th,eff}} V_{\text{ds}} \cdot \left[ M \cdot \frac{1 + \frac{r_{\text{b}}}{R_{\text{B}}} \left( 1 + \frac{\phi_{\text{c}}}{\phi_{\text{dMOS}}} \right)}{1 - S_{\text{c}}} \right] \phi_{\text{dMOS}} & \textbf{(3e)} \\ F_{\text{X}} = S_{\text{X}} - 1 & \text{(x = e, th, eth)} & \textbf{(4a)} \\ F_{\text{op}} = \left\{ \left( I_{\text{dn}}, V_{\text{ds}}, T_{\text{j}} \right) \in \mathbb{R}^3 : \left[ I_{\text{dn}} - f_{\text{e}} \left( V_{\text{gsa}}^{\text{max}}, V_{\text{BE}} = 0 \right) = 0 \right] \right\} & \textbf{(4b)} \\ V_{\text{X}} = \left\{ \left( I_{\text{dn}}, V_{\text{ds}}, T_{\text{j}} \right) \in \mathbb{R}^3 : F_{\text{X}} \left( I_{\text{dn}}, V_{\text{ds}}, T_{\text{j}} \right) < 0 \right\} & \textbf{(4c)} \\ V_{\text{SOV}} = V_{\text{eth}} \cap V_{\text{op}} & \textbf{(4d)} \end{cases}$$

(1a)

Fig. 3: Physics-based model and analytical stability equations. The equations used for modeling the avalanche coefficient M, the MOS current  $I_{\rm dMOS}$  and bipolar currents  $I_c$  and  $I_b$  are provided in the Appendix.

$S_{e}$ ,  $S_{th}$  and  $S_{eth}$  are evaluated in Fig.3 together with the corresponding failure functions  $F_{\rm e},\,F_{\rm th}$  and  $F_{\rm eth}$  defined such that  $F_{\rm x}(I_{\rm dn},V_{\rm ds},T_{\rm i})=S_{\rm x}-1$ . For safe operation, all failure functions need to obey  $F_x < 0$ , and failure occurs when  $F_{\text{eth}} = 0$ in practice. In order to determine  $F_{\text{eth}}$ , the gate-width  $(W_{\text{gate}})$ normalized drain current  $I_{dn}$  and the junction temperature  $T_i$  are found in each bias condition by solving the system (2a)-(2b) in Fig. 3. The base-emitter voltage  $V_{\rm BE}$  has to be determined numerically from Eq. (1c) [7] in order to calculate  $I_c$ . The expressions used in this work for M,  $I_{dMOS}$ ,  $I_c$ ,  $I_b$  and their temperature dependencies are provided in the Appendix.

# B. Determining the root of instability

Electrical failure is described by S<sub>e</sub> in Eq. (3c) (Fig. 3), derived as in Fig. 2 assuming that self-heating does not occur (small-signal analysis with temperature variation t = 0). Avalanche and bipolar contributions (but not leakage) are excluded from thermal failure by assuming M = 1 and  $V_{BE} = 0$ in the stability analysis. A small-signal voltage variation v = 0in Fig. 2 leads to  $S_{th}$  in Eq. (3d). A complete stability analysis including all runaway mechanisms ( $t \neq 0$  and  $v \neq 0$ ) yields  $S_{\text{eth}}$  in Eq. (3e). In this expression it can be seen how electrical instability can trigger thermal runaway, since S<sub>e</sub> appears as a feedback term in S<sub>eth</sub> (electrically-induced thermal instability [2]).

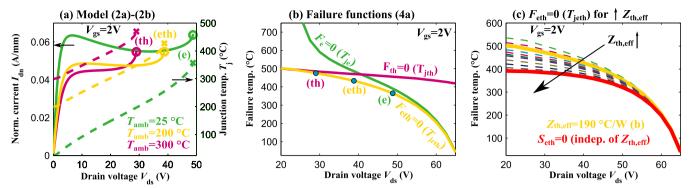

**Fig. 4:** a) Modeled  $I_{dn}$ - $V_{ds}$  and  $T_j$ - $V_{ds}$  curves for  $V_{gs} = 2V$  and three different ambient temperatures  $T_{amb}$  until the edge of the SOA. b) Failure temperature  $(T_{j,fail})$  vs.  $V_{ds}$  for  $V_{gs} = 2V$  showing the gradual boundary between thermal and electrical failure as  $V_{ds}$  increases and  $T_{j,fail}$  reduces. c) Same as b) for different values of the effective thermal impedance  $Z_{th,eff}$ . The red line corresponds to a safer operating condition obtained for  $S_{th} = 0$  rather than  $S_{th} = 1$ .

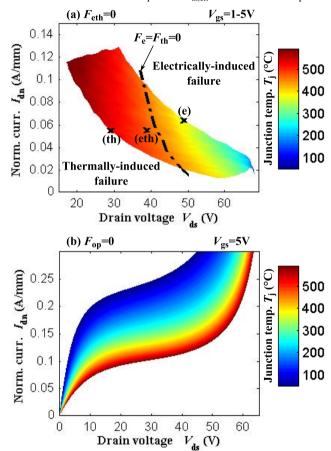

**Fig. 5: a)** Color plot of the surface  $F_{\rm eth}=0$  for different  $V_{\rm gs}$  values. The black line corresponds to the bias points where  $F_{\rm e}=F_{\rm th}=0$  and allows separation of the regions of electrically and thermally induced failure. **b)** The MOS operating function  $F_{\rm op}=0$  for various junction temperatures defined for  $V_{\rm gs,max}=5\,{\rm V}$  and  $V_{\rm BE}=0\,{\rm V}$ .

#### IV. THE SAFE OPERATING VOLUME (SOV)

## A. Building the failure function $F_{\text{eth}}$

Figure 4a) shows the modeled  $I_{\rm dn}$ - $V_{\rm ds}$  and  $T_{\rm j}$ - $V_{\rm ds}$  curves for  $V_{\rm gs}=2{\rm V}$  at three different ambient temperatures  $T_{\rm amb}$  (Eq. (2a)-(2b) in Fig. 3). The failure points at the edge of the SOA ( $F_{\rm eth}=0$ ) where the model stops converging are investigated by analyzing the temperature ( $T_{\rm j}$ ) behavior of failure functions (Eq. (4a) in Fig. 3), as indicated by the circles in Fig. 4b). This analysis allows determination of the failure

junction temperatures  $(T_{\rm j,fail})$  corresponding to electrical  $(T_{\rm je})$ , electro-thermal  $(T_{\rm jeth})$  and thermal failure  $(T_{\rm jth})$ . In all cases failure is limited by  $F_{\rm eth}=0$   $(T_{\rm j,fail}=T_{\rm jeth})$ , but there is a gradual boundary between thermal to electrical runaway as  $V_{\rm ds}$  (and therefore the multiplication factor M) increases and  $T_{\rm i}$  reduces.

# B. Influence of the device area and operating conditions

In Fig. 4c), the dependence of  $F_{\rm eth} = S_{\rm eth} - 1$  upon the effective thermal impedance  $Z_{\rm th,eff}$  is investigated. The failure temperature is affected by  $Z_{\rm th,eff}$  mainly for low  $V_{\rm ds}$ , where failure is thermally induced, while tends to become independent of  $Z_{\rm th,eff}$  for large  $V_{\rm ds}$ , where failure is electrically induced. However, if a safer operating failure criterion is used ( $S_{\rm eth} = 0$  rather than  $S_{\rm eth} = 1$ , red line in Fig. 4c)), the failure temperature becomes independent of  $Z_{\rm th,eff}$  and therefore of ambient temperature, pulse time and device area. This is a significant result of this work, as discussed in Section V.

# C. Mapping electro-thermal failure

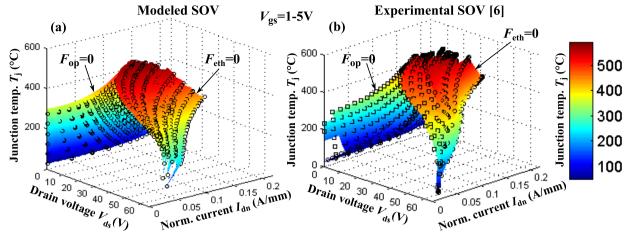

In Fig. 5a), it is shown how electrical and thermal failure mechanisms are mapped on the failure function  $F_{\text{eth}}$ . The black dash-dotted line ( $F_e = F_{th} = 0$ ) indicates the boundary between electrical and thermal failure regions, and the three crosses correspond to the failure points in Fig. 4a). In addition, the operating range is limited by the on-resistance and saturation current that are included using the operating function  $F_{op}$  in Eq. (4b) (Fig. 3). This is defined from Eq. (2a) for  $V_{gs} = V_{gs,max}$ ,  $V_{\rm BE}=0$  at different temperatures in absence of self-heating. In Fig. 5, the operating and failure functions  $F_{op}$  and  $F_{eth}$  are mapped onto a 3D space comprising gate-width normalized drain-current  $I_{dn}$ , drain voltage  $V_{ds}$  and junction temperature  $T_i$ . Intersecting the corresponding volumes  $V_{\rm op}$  and  $V_{\rm eth}$  (Eq. (4d) in Fig. 3) yields a new volume describing the operating limits of LDMOS transistors, which was defined as Safe Operating Volume (SOV) in earlier work [6]. For comparison with measurement results, the total SOV has been constructed using the model equations (2a)-(2b) (Fig. 3) and compared with the experimental data from [6] in Fig. 6.

Fig. 6: Comparison between a) modeled and b) experimental [6] SOV, showing qualitative agreement across a wide range of bias conditions.

# V. DISCUSSION

The presented analysis is useful for the following reasons.

- 1) It allows identification of the main failure mechanism (electrical, thermal, electro-thermal) of LDMOS transistors on a theoretical basis, which is important for device optimization.

- 2) It shows that there is a gradual boundary between an electrical failure region at high drain voltage  $V_{ds}$  and a thermal failure region at high junction temperature  $T_i$ .

- 3) It explains why the SOV can be used as a general measure for the operating range of transistors, which is to a large extent independent of the size and operating conditions.

- 4) It suggests that the failure functions can be combined with the model results in Fig. 6a) to reduce the number of measurements needed to construct the experimental SOV in Fig. 6b).

While in theory the electro-thermal runaway condition is given by  $S_{\rm eth}=1$  [1] ( $F_{\rm eth}=0$ ), experiments [6] show that the range  $0 < S_{\text{eth}} < 1$  is often unsafe due to the high value of  $\frac{dS_{\text{eth}}}{dV_{\text{ds}}}$ . Therefore, a safer operating condition can be introduced that is given by  $S_{\text{eth}} = 0$ , which leads to a reduction of the estimated safe operating limits (mainly in the thermal runaway regime) but makes the SOV independent of  $Z_{th,eff}$  (Fig. 4c)). In practice, the condition  $S_{\rm eth} = 0$  cannot be achieved for  $V_{\rm gs}$ values below the zero temperature coefficient point [14] since the temperature coefficient of the MOS current is positive in this range. For this reason, a practical value of  $S_{\rm eth} = 0.2$  was used in [6] for the different operating conditions, yielding a good trade-off between transistor safety and experimental accuracy.

# VI. CONCLUSIONS

In this work, an analytical procedure for identifying electrical, thermal and electro-thermal failure in LDMOS transistors has been presented. The results allow the operating limits to be mapped on the Safe Operating Volume (SOV), which is defined as an extension of the Safe Operating Area (SOA). Suitable modifications of the stability analysis and SOV representation can extend their applicability to other kinds of transistors (see, e.g. [16]).

#### REFERENCES

- [1] P. L. Hower and P. K. Govil in Trans. El. Dev., vol. 21, p. 617, 1974.

- P. Hower et al., Proc. ISPSD'01, p. 153, 2001.

- P. L. Hower in Proc. ISPSD'02, p. 1, 2002.

- V. Khemka et al., Electron. Device Lett., vol. 25, p. 705, 2004.

- [5] D. Dibra et al., Trans. Electron. Dev., vol. 58, p. 3477, 2011.

- [6] A. Ferrara et al., IEDM'13, p. 6.7.1, 2013.

- U. Radhakrishna et al., Trans. Electron. Dev., vol. 58, p. 4035, 2011.

- M. Pfost et al., Trans. Electron. Dev., vol. 60, p. 699, 2013.

- Y. S. Chung and B. Baird in Microel. Reliab., vol. 42, p. 211, 2002.

- [10] S. J. Sque et al., Proc. IEDM'13, p. 12.7.1, 2013.

- [11] D. B. M. Klaassen in Solid-State Electron., vol. 35, p. 953, 1992.

- N. Arora, Mosfet Modeling for VLSI Simulation: Theory And Practice. World Scientific, 2007.

- A. Ferrara et al., Proc. ICMTS'13, p. 115, 2013.

- G. Breglio et al., Proc. ISPSD'99, p. 233, 1999.

- [15] S. Reggiani et al., Trans. Electron. Dev., vol. 52, p. 2290, 2005.

- T. Vanhoucke and G. A. M. Hurkx in Proc. BCTM'05, p. 37, 2005.

- S. Reggiani et al., Trans. Electron. Dev., vol. 56, p. 2811, 2009. [17]

- [18] P. Moens and G. Van den Bosch in Trans. Device Mat. Rel., vol. 6, p. 349, 2006.

## APPENDIX

Avalanche, MOS and bipolar model equations used in this

$$\begin{cases} M = \frac{1}{1 - \left(\frac{V_{\rm ds}}{BV}\right)^m} \qquad (\mathbf{A1}) \end{cases}$$

$$K(T_{\rm j}) = K(T_{\rm ref}) \left(\frac{T_{\rm j}}{T_{\rm ref}}\right)^{-m_{\rm ch}}$$

(M1)

$$V_{th}(T_{j}) = V_{th}(T_{ref}) - k_{th}(T_{j} - T_{ref})$$

$$R_{\rm on}(T_{\rm j}) = R_{\rm on}(T_{\rm ref}) \cdot \left(\frac{T_{\rm j}}{T_{\rm ref}}\right)^{m_{\rm drift}}$$

(M3)

$$I_{\mathrm{dsat}}(T_{\mathrm{j}}) = I_{\mathrm{dsat}}(T_{\mathrm{ref}}) \cdot \exp\left(-\frac{T_{\mathrm{j}} - T_{\mathrm{ref}}}{\theta}\right)$$

(M4)

$$\begin{cases} V_{\text{dsat}}(T_{j}) = R_{\text{on}}(T_{j}) \cdot I_{\text{dsat}}(T_{j}) \end{cases}$$

(M5)

$$V_{\text{dsat}}(T_j) = R_{\text{on}}(T_j) \cdot I_{\text{dsat}}(T_j) \qquad (M5)$$

$$I_{\text{ch}} = \frac{K \cdot (V_{\text{gs}} - V_{\text{th}})^{\alpha_{\text{ch}}}}{1 + \theta_{V_{\text{gs}}}(V_{\text{gs}} - V_{\text{th}})} \cdot \frac{1}{\left[1 + \left(\frac{V_{\text{ch}}}{V_{\text{gs}} - V_{\text{th}}}\right)^{\eta_{\text{ch}}}\right]^{1/\eta_{\text{ch}}}} \qquad (M6)$$

$$I_{\text{drift}} = I_{\text{dsat}} \cdot \frac{(V_{\text{ds}} - V_{\text{ch}})}{V_{\text{dsat}}} \cdot \frac{\left[1 + \frac{V_{\text{ds}} - V_{\text{ch}}}{V_{\text{ch}}}\right]^{1 + Q_{\text{drift}}}}{\left[1 + \left(\frac{V_{\text{ds}} - V_{\text{ch}}}{V_{\text{ch}}}\right)^{\eta_{\text{drift}}}\right]^{1/\eta_{\text{drift}}}} \quad (\mathbf{M7})$$

$$I_{\text{dMOS}}(V_{\text{ds}}) = I_{\text{ch}}(V_{\text{ch}}) = I_{\text{drift}}(V_{\text{ds}} - V_{\text{ch}})$$

(M8)

$$I_{s}(T_{j}) = I_{s}(T_{ref}) \cdot \exp\left[-\frac{qE_{g}}{k_{B}}\left(\frac{1}{T_{j}} - \frac{1}{T_{ref}}\right)\right]$$

(B1)

$$I_{R}(T_{j}) = I_{R}(T_{ref}) \cdot \exp\left[-\frac{qE_{g}}{2k_{B}}\left(\frac{1}{T_{j}} - \frac{1}{T_{ref}}\right)\right] \quad (\mathbf{B2})$$

$$I_{R}(T_{j}) = I_{R}(T_{ref}) \cdot \exp \left[ -\frac{qE_{g}}{2k_{B}} \left( \frac{1}{T_{j}} - \frac{1}{T_{ref}} \right) \right]$$

(B2)

$$R_{B}(T_{j}) = R_{B}(T_{ref}) \cdot \left( \frac{T_{j}}{T_{ref}} \right)^{m_{npn}}$$

(B3)

$$\beta(T_{j}) = \beta(T_{ref}) \left( \frac{T_{j}}{T_{ref}} \right)^{m_{\beta}}$$

(B4)

$$\beta(T_{\rm j}) = \beta(T_{\rm ref}) \left(\frac{T_{\rm j}}{T_{\rm ref}}\right)^{m_{\beta}} \tag{B4}$$

$$I_{b}(V_{\text{BE}}, T_{j}) = \frac{I_{S}}{\beta}(T_{j}) \cdot \exp\left(\frac{V_{\text{BE}}}{V_{T}}\right)$$

$$I_{c}(V_{\text{BE}}, T_{j}) = I_{S}(T_{j}) \cdot \exp\left(\frac{V_{\text{BE}}}{V_{T}}\right) + I_{R}(T_{j})$$

(B6)

$$I_{c}(V_{BE}, T_{j}) = I_{S}(T_{j}) \cdot \exp\left(\frac{V_{BE}}{V_{T}}\right) + I_{R}(T_{j})$$

(B6)