Roadmap for European research on Smartcard rElated Technologies

## Project Deliverable Ref.: D5

## Deliverable Title: "Final Roadmap"

## Date of Preparation: 15 May 2003

## Version: 5.0

## **Status: Final**

## **Dissemination Level: Public**

# **Table of Contents**

| 1 | EXE                                           |                                                                   | /E SUMM                                                                                      | ARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---|-----------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | INTI                                          | RODU                                                              | CTION .                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | CURF<br>MAIN<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>CURF | RENT MA<br>APPLICA<br>Telecom<br>Financial<br>Identifica<br>Multimec<br>Transpor<br>RENT FRA | <b>CONTEXT 9</b> RKET CONTEXT       9         ATION FIELDS       11         1       11         1       11         1       11         1       11         1       11         1       11         1       11         1       11         1       11         1       11         1       12         1       12         1       12         1       12         1       12         1       12         1       12         1       12         1       12         1       12         1       12         1       13         1       13         1       13         1       13 |

| 4 | TEC                                           | COMI<br>4.1.1<br>4.1.2                                            | <b>OGY CH</b><br>MUNICAT<br>Technolo<br>Scientific                                           | ALLENGES       15         TION AND NETWORKS PROTOCOLS       15         ogies trends and market requirements       15         and technical challenges       16         n orientations       17         Short / Medium term       17                                                                                                                                                                                                                                                                                                                            |

|   | 4.2                                           | 4.2.1                                                             | Technolo<br>4.2.1.1<br>4.2.1.2<br>4.2.1.3                                                    | Long term18D SOFTWARE19ogy trends and market requirements19Operating systems and high-level languages19Development tools19System integration19and technical challenges20Operating systems and high-level languages20Development tools20Development tools20Operating systems and high-level languages20Development tools20Development tools20                                                                                                                                                                                                                   |

|   | 4.3                                           | SMAF                                                              | 4.2.2.3<br>Researc<br>4.2.3.1<br>4.2.3.2<br>RT CARD                                          | Development tools       20         System integration       20         n Orientations       21         Short / Medium term       21         Long term       24         ACCEPTING DEVICES, INTERFACES AND BIOMETRY       25         ogy trends and market requirements       26         Evaluation in specific areas       26         Market requirements       27                                                                                                                                                                                              |

|   |     | 5.1.1 | Business                                                                             | opportunities and market requirements                                                                                                                                 | 60                         |

|---|-----|-------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 5 |     |       |                                                                                      | <b>IRONMENT FOR BUSINESS AND TECHNOLOGY DEVELOPMENT</b> IORS                                                                                                          |                            |

|   | 4.7 | SYNT  | HETIC O                                                                              | VERVIEW                                                                                                                                                               | 59                         |

|   |     |       | 4.6.3.1<br>4.6.3.2                                                                   | Short/Medium term                                                                                                                                                     | 58                         |

|   |     | 4.6.3 |                                                                                      | n orientations for improvement                                                                                                                                        |                            |

|   |     |       | 4.6.2.1<br>4.6.2.2                                                                   | On a short/medium term On a medium/long term                                                                                                                          | 57                         |

|   |     | 4.6.2 | Scientific                                                                           | and technical challenges                                                                                                                                              |                            |

|   |     |       | 4.6.1.1<br>4.6.1.2                                                                   | Technology trends                                                                                                                                                     |                            |

|   |     | 4.6.1 | Semicon                                                                              | ductor technology trends and market requirements                                                                                                                      | 52                         |

|   | 4.6 | MICR  | O-ELECT                                                                              |                                                                                                                                                                       |                            |

|   |     |       | 4.5.3.1<br>4.5.3.2                                                                   | Short / medium term                                                                                                                                                   |                            |

|   |     | 4.5.3 | Researc                                                                              |                                                                                                                                                                       |                            |

|   |     |       | 4.5.2.1<br>4.5.2.2                                                                   | Cryptographic functionalities and protocols                                                                                                                           |                            |

|   |     | 4.5.2 | Scientific                                                                           | and technical challenges                                                                                                                                              | 45                         |

|   |     | 4.5.1 | Evaluatio                                                                            | on of technology trends and market requirements                                                                                                                       | 43                         |

|   | 4.5 | HIGH  | -END CR                                                                              | YPTOGRAPHY, TAMPER-PROOF AND SECURITY TECHNOLOGIES .                                                                                                                  | 43                         |

|   |     |       | 4.4.3.1<br>4.4.3.2<br>4.4.3.3<br>4.4.3.4<br>4.4.3.5<br>4.4.3.6<br>4.4.3.7<br>4.4.3.8 | Card Hardware Architecture                                                                                                                                            | 41<br>42<br>42<br>43<br>43 |

|   |     |       |                                                                                      | n orientations                                                                                                                                                        | 40                         |

|   |     |       |                                                                                      | and technical challenges                                                                                                                                              |                            |

|   |     |       |                                                                                      | bgy trends and market requirements                                                                                                                                    |                            |

|   | 4.4 | EMBE  | 4.3.3.1<br>4.3.3.2<br>4.3.3.3<br>EDDED P                                             | Physical Properties and Types of card accepting devices<br>Data Transmission / Communication<br>Transactions and Security<br>ERIPHERALS, SUBSYSTEMS AND MICRO-SYSTEMS | 31<br>32                   |

|   |     | 4.3.3 | Researc                                                                              | n orientations                                                                                                                                                        | 30                         |

|   |     |       | 4.3.2.1<br>4.3.2.2                                                                   | Generic aspects of smart card systems evolution                                                                                                                       |                            |

|   |     | 4.3.2 | Scientific                                                                           | and technical challenges                                                                                                                                              | 28                         |

|   |     | 5.1.2 | Security:          | "Arms race" between attacks and counter-measures                                              | 1 |

|---|-----|-------|--------------------|-----------------------------------------------------------------------------------------------|---|

|   |     | 5.1.3 | Increase           | d consideration for consumer requirements                                                     | 2 |

|   |     | 5.1.4 | Product            | cost and international competition 6                                                          | 2 |

|   | 5.2 | BOTT  | LENECK             | S                                                                                             | 3 |

|   |     | 5.2.1 | Heteroge           | eneous chip architectures and operating systems                                               | 3 |

|   |     | 5.2.2 | Weak co            | nnectivity to IT and consumer worlds 6                                                        | 3 |

|   |     | 5.2.3 | Lack of c          | card accepting infrastructures 6                                                              | 4 |

|   |     | 5.2.4 | Limitatio          | n of available components, materials and card assembly technologies $\ldots$ 6                | 4 |

|   |     | 5.2.5 | Limitatio          | ns of available development, test, integration and certification tools $\ldots$ 6             | 5 |

|   | 5.3 | CHAL  | LENGES             | 66                                                                                            | 6 |

|   |     | 5.3.1 | Commur             | nication and networks protocols 6                                                             | 6 |

|   |     | 5.3.2 | Systems            | and S/W 6                                                                                     | 7 |

|   |     |       | 5.3.2.1            | Operating Systems and High Level Languages 6                                                  |   |

|   |     |       | 5.3.2.2<br>5.3.2.3 | Development Tools       6         Systems Integration and Card Application Management       6 |   |

|   |     | 533   |                    | ard accepting devices, interfaces and biometry                                                |   |

|   |     |       |                    | bedded peripherals, subsystems and microsystems                                               |   |

|   |     | 0.0.4 | 5.3.4.1            | Standard Card Hardware Architecture                                                           |   |

|   |     |       | 5.3.4.2            | Power Supplies                                                                                |   |

|   |     |       | 5.3.4.3            | Packaging technologies                                                                        |   |

|   |     |       | 5.3.4.4<br>5.3.4.5 | Interconnections technologies                                                                 |   |

|   |     |       | 5.3.4.6            | Material and material transformation                                                          |   |

|   |     | 5.3.5 | Cryptogr           | aphy, tamper-proof and security technologies                                                  | 1 |

|   |     |       | 5.3.5.1            | Design of secure smart card chips 7                                                           |   |

|   |     |       | 5.3.5.2            | Investigation and prevention of attacks                                                       |   |

|   |     |       | 5.3.5.3<br>5.3.5.4 | Development and implementation of high-end cryptology                                         |   |

|   |     | 5.3.6 |                    | ectronics                                                                                     |   |

|   |     |       | 5.3.6.1            | Javacard standard evolution (V2.2, V3.0)                                                      | 2 |

|   |     |       | 5.3.6.2            | Improved security levels 7                                                                    | 3 |

|   |     |       | 5.3.6.3<br>5.3.6.4 | Card interface with networks & systems                                                        |   |

|   |     |       | 5.3.6.5            | Global technology improvement                                                                 |   |

|   |     |       |                    |                                                                                               |   |

| 6 |     |       |                    | OR COLLABORATIVE RESEARCH                                                                     |   |

|   | 6.1 |       |                    | IES FOR COLLABORATION - OTHER RTD PROGRAMMES IN EUROPE 7                                      |   |

|   |     | 6.1.1 | The ME             | DEA+ programme                                                                                |   |

|   |     |       | 6.1.1.1            | MEDEA + Projects                                                                              |   |

|   |     | 610   | 6.1.1.2            | MEDEA + Roadmap - EDA (Electronic Design Automation)                                          |   |

|   | 6.0 |       |                    | research programmes                                                                           |   |

|   | 0.2 | KE9E  |                    |                                                                                               | Э |

| 7 | CONCLUSIONS: SMART CARD RELATED RTD PRIORITIES                                                                                                                                                                                                                                                                                               |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8 | SCENARIOS FOR AN RTD IMPLEMENTATION828.1IMPLEMENTATION WITH TECHNOLOGY FOCUSED RTD PROJECTS828.1.1Technologies for security and trust828.1.2Technologies for networking and new communication models838.1.3Technologies for SW platforms and OS838.1.4Technologies for HW chip platforms83                                                   |

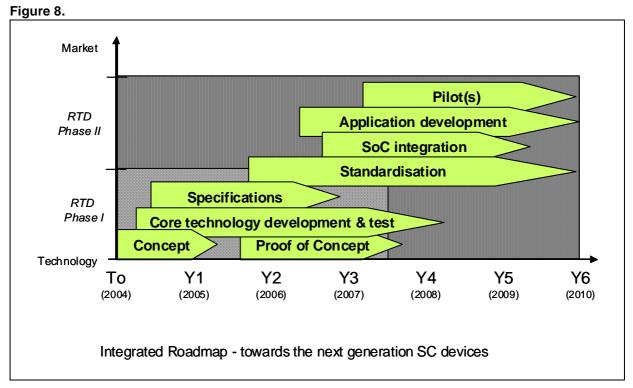

|   | 8.2       IMPLEMENTATION IN AN INTEGRATED APPROACH: DEVELOPMENT<br>OF THE NEXT GENERATION SMART CARD DEVICE       84         8.2.1       Phase I: Next generation SC device technology development       85         8.2.2       Phase II: Development and demonstration of next generation<br>SC device components and applications       85 |

| 9 | ANNEX       87         9.1 LIST OF ACTIVE CONTRIBUTORS       87         9.2 GLOSSARY OF SPECIFIC TERMS AND ACRONYMS       90                                                                                                                                                                                                                 |

## **1 EXECUTIVE SUMMARY**

The objective of RESET (Roadmap for European research on Smartcard related Technologies) is to investigate the RTD needs corresponding to current and expected future technology gaps, identified by the industry and resulting from market and product trends foreseen by smart card industrial players. The goal of this initiative is to describe current and future RTD challenges and deliver roadmaps for RTD on secure devices and platforms, relevant for European RTD programmes beyond FP5 and for national and international RTD programmes.

Smart cards are key components addressing security needs in a number of well established consumer applications. Although the smart card industry is currently experiencing a decreased development rate - mainly resulting from the global slow down of ICT markets and in particular mobile phone markets - experts are convinced that there is still an enormous potential for smart card deployment in traditional, and new application areas.

Traditional high-volume applications include banking, telecom, pay-TV, etc. (see also section 3). There is still a strong need for innovation to address the requirements of those applications to overcome existing limitations and anticipated evolving environments. But an even higher potential for smart card technology applications is expected from upcoming ubiquitous computing and ambient intelligence environments. These environments create a need for "handy" personal keys that can provide the required level of trust and confidence to users in networked applications. Current smart card technology has an advance over other solutions to address these needs - however some of the existing technology limitations should be overcome to enable the integration of smart card technology-based personal devices as integral components of networked applications.

In order to establish a suitable roadmap, the RESET project had to take into account a specificity of smart card systems, which is to integrate a wide range of technologies. The investigation to be carried out has therefore been divided in 6 main technology areas, each of them covered by one expert working group:

WG1: Communication and networking

WG2: Systems and S/W

WG3: Smart card accepting devices, interfaces and biometry

WG4: Card embedded peripherals, subsystems and micro-systems

WG5: High-end cryptography, tamper-proof and security technologies

#### WG6: Micro-electronics

The investigation of the working groups was carried out following a common framework which included the following topics:

- State of the art: existing and emerging technologies, their limitations, competing technologies

- On-going research: inside and outside the smart card world

- Evaluation of technology and marketing requirements: evolution of the smart card technologies in information / communication / transaction systems, scientific and technical challenges, market requirements, etc.

- Research orientations for improvement: short / medium and long term

Furthermore, each of the WGs was invited to come up with a research roadmap for its specific domain as contribution to the global roadmap. Finally, following the process of gathering and consolidating R&D needs in each domain, the participants to the WGs were invited to think of scenarios for collaborative RTD project that could answer these needs with a perspective to reach a real impact in smart card technology within a timeframe of 5-6 years from now.

The results of this investigation and consultation process are presented in this report. It starts from a short description of the socio-economic context that influences the development and deployment of smart card applications. Then a summary of the main outcomes of the 6 working groups is introduced. As the complete material prepared by the WGs is too large to be integrated in this report, result of their investigations and discussion is available in the form of material resulting from dedicated workshops or self-standing consolidated reports that can be read for a more in-depth understanding of each of the 6 mentioned technology domains.

Section 5 of the roadmap summarises the main driving and blocking factors that condition the evolution of smart cards and then identifies the technical challenges that need to be mastered to enable the European smart card technology suppliers to deal with these factors, address anticipated requirements and exploit new market opportunities.

Section 6 contains a summary list of the resulting main R&D targets and RTD programmes and resources that have a capacity to carry out smart card technology related research.

Section 7 contains a table which consolidates the identified main RTD topics in an integrated collaborative research programme that would have the potential to federate a sufficient number of European R&D resources to address these R&D targets.

## **2 INTRODUCTION**

RESET is the first ever made attempt of the European smart card industry and academic stakeholders to assess and introduce technology and marketing priorities, with the view to provide global R&D orientations.

This initiative is reflecting a situation shortly described hereunder, where:

- Smart card industry is facing a new economic environment, where global players of the information society aim at providing technology and systems building blocks upon an integrated way, in order to deliver solutions which fit global market requirements, especially in terms of security and trust

- Global growth rate of traditional smart card markets, especially in the telecom area, is no more at the level of the 90s. This means that companies have to carefully select R&D priorities fitting their business development strategy, in order to optimize use of human and financial resources

- Smart card has yet to improve its performances and features for being fully acknowledged as an

element of the new generation networked environments, especially in the IT and consumer domains

- 6th Framework Programme, with new instruments and improved R&D integration, provides a valuable opportunity for helping the smart card industry to better structure its effort towards common technology excellence achievements by a coordinated joint RTD effort

Smart card industry has therefore to identify and address major challenges of the global information and communication society, such as:

- Improved interconnection with IT infrastructures, specifically in the context of the new generation Internet, for enhanced access to trusted e-services

- Evolution towards extended open HW and SW platforms, addressing requirements for secure, interactive and personal devices

- Overtaking of current technology bottlenecks, through provisioning of technical features required by rapidly evolving systems and networks environments. Main expected improvements are faster data communication, extended and manageable memory capacity, secure co-design of elements integrated in the value-chain (µcontrollers, crypto algorithms, multi-tasking OS,...), embedding of new components for security (sensors), energy (power supply), user convenience (display), etc.

- Implementation of standard architectures, supporting open OS, multi-application schemes management, interface bus, etc.

- Extended cooperation in test suites implementation and security certification procedures

- In this context, RESET roadmap deliverable is aiming at:

- Accurately identifying the common priorities of the smart card industry, in terms of technology improvement and marketing requirements

- Being of a highly manageable instrument, acknowledged as such by any current or potential player of smart card related activities

- Providing a sound basis for efficient co-operation in R&D programmes, with regards to FP6.

## **3 SOCIO-ECONOMIC CONTEXT**

#### **3.1 CURRENT MARKET CONTEXT**

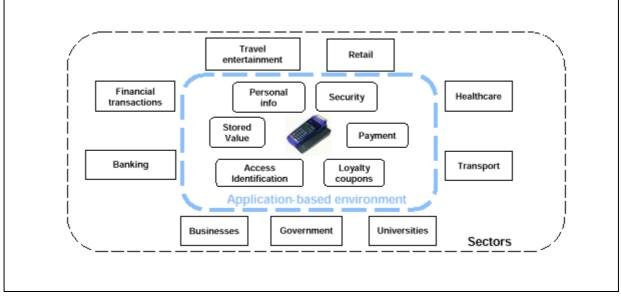

Smart cards offer several basic security services that, in fact, underlie other smart card applications (ecommerce, medical identification, etc.). They allow secure logging to systems and webs, secure signature of electronic documents, encryption and decryption of digital information, etc.

Accessing a network or some information using a smart card provides the parties (users, networks, devices and information) with mutual authentication and trust. On the other hand, in an increasingly on-line environment, where information transactions are performed over an insecure network such as Internet, security is a key issue. In general, the market requires high security products that can be implemented at a low incremental cost.

Smart cards are used in a variety of different applications. Due to the increasing computing power of processors embedded in cards, more and more security-related actions are performed by means of the smart card itself. Use of high-end-cryptography (assuring high security) can result in relatively high execution times of encryption and decryption processes. The market needs high performance of the smart card applications including short calculation times for the cryptographic procedures.

The implementation of new and enhanced security technologies should not increase the price of the smart card products. Elegant ways for developing and implementing new security technologies in a cost-efficient manner are sought.

Europe is still the main marketplace for smart cards, from supply and demand standpoint. However, global growth rate for µprocessor cards is faster in Asia, with special notice to inland China, and in South America for memory cards, with special notice to Mexico.

Smart card industry is currently experiencing significant evolution as regards business. The telecom sector, which remains the first revenue generator for smart card-based solutions, is facing since 2001 a heavy reduction in rate of increase, due to market saturation.

Meanwhile, the financial sector is meeting a steady though regular 15 to 20% yearly growth rate, mainly due to the EMV roll-out.

Finally, the so-called emerging markets, which have been termed as such for many years, are now offering real business opportunities, through government ID and public transports projects.

#### Table 1. Smart card market. Millions of units shipped per year per sector, world-wide

(Source: Eurosmart, November 2002)

|               | Year 1998 | Year 1999 | Year 2000 | Year 2001 | Year 2005<br>(forecast) |

|---------------|-----------|-----------|-----------|-----------|-------------------------|

| Telecom       | 930       | 1 113     | 1 390     | 1 440     | 2 750                   |

| Pay TV        | 25        | 30        | 20        | 25        | 80                      |

| Banking       | 73        | 108       | 120       | 142       | 150                     |

| Loyalty       | -         | -         | -         | 48        | 40                      |

| Transport     | 16        | 44        | 13        | 35        | 210                     |

| Healthcare ID | 35        | 58        | 27        | 32        | 160                     |

| Internet ID   | -         | -         | 5         | 5         | 150                     |

| ID            | -         | -         | -         | -         | 200                     |

| Others        | 75        | 77        | 28        | 24        | 70                      |

| TOTAL         | 1154      | 1429      | 1603      | 1751      | 3810                    |

#### Table 2. Memory and microprocessor smart cards market in 2002

in millions of units, world-wide (Source: Eurosmart, April 2003)

| Sector                                | Card (Mu) |                |  |

|---------------------------------------|-----------|----------------|--|

| Sector                                | Memory    | Microprocessor |  |

| Telecom                               | 950       | 430            |  |

| Financial Services / Retail - Loyalty | 23        | 175            |  |

| Government / Healthcare               | 30        | 32             |  |

| Transport                             | 60        | 15             |  |

| Pay TV                                | 0         | 35             |  |

| IT / Security                         | 9         | 7              |  |

| Others                                | 13        | 7              |  |

| TOTAL                                 | 1085      | 701            |  |

| TOTAL 2002                            | 17        | 786            |  |

Table 3. Smart card market by geographical areas. Millions of units (memory & µprocessor cards) shipped per year per region (Source: Eurosmart)

|             | Year 1999 | Year 2000 | Year 2001 |

|-------------|-----------|-----------|-----------|

| Europe & ME | 903 (63%) | 888 (55%) | 786 (45%) |

| Asia & Pac  | 262 (18%) | 424 (26%) | 447 (25%) |

| America     | 264 (18%) | 291 (18%) | 518 (29%) |

| TOTAL       | 1429      | 1603      | 1751      |

#### **3.2 MAIN APPLICATION FIELDS**

#### 3.2.1 TELECOM

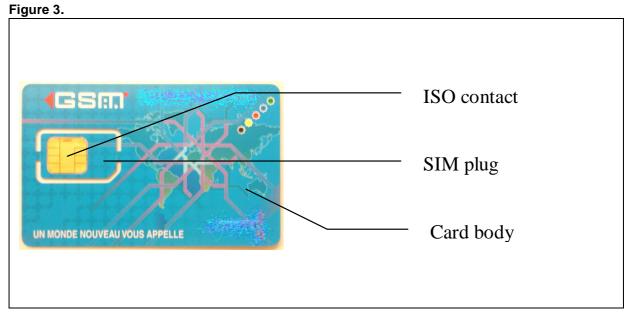

SIM cards for mobile telephony and prepaid public telephone cards are the main outlets for smart cards in telecommunication services.

About 1500 million units of mobile phone and prepaid telephony cards were sold in 2001 (this quantity has steadily increased from the 930 millions of units shipped in 1998). According to Eurosmart's forecast, sales of about 2700 millions of smart cards are expected in 2005 in the telecommunications sector (see Table 1 & 2), with µprocessor SIM cards greatly overtaking memory cards at that time.

In telephone systems, the growth of prepaid telephone cards is expected to drop as mobile phones increase their share of the market. A new market cycle is expected in the telecom area, supported by two major drivers: extended delivery of added-value services and implementation of the next generation wireless networks (GPRS and UMTS).

Telecom operators (telcos) have been very active in provisioning new services to subscribers, and smart card suppliers have compensated to a certain extent price drop by improved-technology products, such as extended EEPROM capacity (from 2 to 64 Kilobytes in 8 years) or open OS platforms for improved added-value services management.

Due to a lack of standards and a fragmented set of technical solutions, m-Commerce has not yet fully reached its target. However, it remains a strong priority for telcos, provisioning services such as Information on Demand (IOD), games and multi-media message services (MMS) supported by new colour-screen handsets, with the view to improving ARPU (average revenue per user).

The churn rate (volatility of subscribers) is still high and could become worse with telephone number portability (same phone number for subscriber, irrespective of the network operator). However, compared with handset, SIM card remains for telcos a valuable tool for optimizing security management (personalisation) and keeping a direct and loyal link to their subscribers.

The 3G revolution, expected in Europe for 2004, should provide the smart card industry with a new cycle of dynamic business, thanks to securely managed (and packaged) third party services to customers.

#### 3.2.2 FINANCIAL SERVICES

The market growth in banking sector is mainly resulting of the conversion of magstripe debit & credit cards to smart cards, for improving trust and security and providing enhanced marketing payment schemes. The major part of worldwide markets has adopted precise deadlines for migration towards international EMV standards for chip-based payment. The value behind deadlines is a shift in liability, for any type of card fraud to whichever party - card issuer or merchant acquirer - which would not accept EMV cards.

Europe is on the front line for this liability transfer application, targeted for January 1st, 2005. However, the pace for migration is very much depending on the situation regarding fraud.

Banks are also exploring the use of high end card products, running either multi-application schemes, or enhanced functions as e-signature. In Central Europe and Turkey for instance, banks are experiencing real differentiation schemes thanks to privileged agreements with a large range of service providers (re-tail, petrol, airline...), thus offering their customers the possibility to really access services on a frequent and regular basis.

However higher "product mix" is still at a preliminary phase in the banking sector, mainly due to the high level of investment required by the EMV migration (cards, terminals, back-office,...). Real differentiation schemes, as compared with the wireless telecom sector, are still at an investigation stage. The main real

multi-application scheme is still the provision of an electronic purse application twinned with a debit/credit function.

#### 3.2.3 IDENTIFICATION

As government, public and private organizations move towards electronic methods of service provision, the need of secure electronic personal identification (ID) becomes more critical. According to this, shipment of about 200 millions of smart cards for personal identification purposes is expected in 2005. At the moment of this writing, a few millions of smart cards are sold yearly for Internet identification purposes. An important market niche is related to health services, for identification and storage of personal insurance and health records.

Every organization (university, company, library, etc.) is a potential consumer of smart cards for identification purposes. Issuing smart cards to employees, students, etc. is becoming widespread as the card is a valid device for multi-application schemes in these closed environments.

Smart cards are a clear identity product. Managing identity information is one of the smart cards' roles in most of the areas which they are used in. Smart card-enabled PKI (public key infrastructure) technology is expected to play a growing role in the implementation of smart card-based network access for enterprise IT systems and the roll-out of national ID card programs. Thus, identification might be considered the next killer application in smart cards industry. Biometrics is likely to be a key issue in smart card based ID applications.

The memory requirements are about from 2KB to 8Kbytes, but larger amounts will be needed in order to accommodate new applications based on identification card usages.

#### 3.2.4 MULTIMEDIA AND PAY-TV

The sales volume related to pay-TV amounts to about 30 millions of units per year. Substantial increase of this figure is expected in the next years, because of the new interactive and Internet television market. For payment TV, microprocessor cards do need to increase memory, in order to store larger keys and be able to participate in interactive TV applications. In pay-TV only microprocessor cards are used.

Digital Asset Protection (DAP) is a type of software developed to enable secure distribution - and perhaps more importantly, to disable illegal distribution - of paid content over the Web. DAP technologies are being developed as a means for fair use of commercially marketed material, in particular in the context of the widespread use of peer-to-peer file exchange programs. Smart cards will play an important role in DAP, in order to meet the requirements needed to protect the interest of copyright holders of multimedia contents, software or large amounts of data.

#### 3.2.5 TRANSPORTATION

There are several uses of smart cards in the transportation sector. For instance: 1) contact smart cards can be used for highway toll payment or parking control; 2) for public transportation, contactless smart cards are being deployed at several cities (the user does not need to physically plug her/his card at the metro station barriers). Replacing magnetic stripe or paper cards by chip cards in a new generation of ticketing systems is a major trend in transportation. The volume of sales related to new ticketing systems is expected to reach 150 millions of units in 2005, to be added to the 20 or 30 millions of smart cards annually sold for other transportation purposes.

In Europe, two programmes are in the spotlight in 2003, Paris and London. Paris mass transit operators (RATP and SNCF) have already issued more than 500 K contactless chip cards and equipped 800 subway stations.

In London, the "prestige" project (Transport for London) should provide access to network for commuters from spring 2003, and within 18 months, 2 to 3 million people are expected to use smart cards.

Rome and Berlin should be the next two European capitals to issue card-based automatic fare collection for their public transport networks.

System integrators of card-based solutions often provide operators with licenses which permit the combination of low-cost systems for short term ticketing schemes, and long-term agreements for implementation of adding added-value services.

#### 3.3 CURRENT FRAMEWORK FOR ACTIVITIES IN THE SMART CARD INDUSTRY

Smart card industry is still under the control of Europe-based companies, which have installed settlements all over the world for product trade and manufacturing, often via joint ventures with local companies. However, due to serious economic factors, such as reduced market growth in mobile telephony which is the first revenue generator for smart card industry, or the slow emergence of new market opportunities such as ID or e-ticketing, the global activity is currently facing, as other fields of electronic industry, high pressure on product cost and profit margin.

This has an impact on financial results of many market players and, in parallel, on the motivation of the investors' community to support its development.

In this context, smart card industry is considering *innovation as a key factor* for preventing evolution towards provisioning of pure "commodity" card products, which are doomed to be manufactured in low labour cost countries.

Re-adjustments are seen in the value-chain, with increased overlaps between components suppliers (IC, card and CAD manufacturers, application/service providers, system integrators), which have begun to extend their business position beyond their current limits. For example, card manufacturers could have their own IC design and architecture development team, and IC manufacturers could go right ahead with IC packaging and micro-module assembly, through existing or new device form factors, memory configurations or protocol implementations (USB, MMC, ...).

System-On-Chip design is now providing great deals of embedded SW, thus decreasing cost of ownership for issuers and users and reducing product time to market through enhanced solution interoperability. This could speed industry restructuring through merge & acquisition operations, generating major changes in the smart card supplying chain in the years to come.

#### 3.4 IMPACT OF LEGAL ISSUES AND REGULATIONS, ETC.

With regard to information society requirements, smart card industry has to deliver products and solutions which comply with the legal and regulation framework. Smart card is a key instrument for secure access to network and online services, and for trusted management of user consent in transactions. Therefore, two major regulation domains have to be seriously considered:

- electronic signature

- protection of personal data and privacy management

As far as e-signature is concerned, an enormous amount of new legislation governing the way that companies and consumers do business in electronic environments has been issued worldwide. In this process, the electronic signature has made much progress towards gaining the same legal recognition as its hand-written, paper-based counterpart. Electronic signatures - whatever type - have been accepted as a means to identify e-commerce participants and thus constitute a common approach to identification and authentication in e-commerce.

The European Union has issued a European Electronic Signature Directive, in order to provide a legal framework to guarantee EU-wide recognition of electronic signatures - a prerequisite for ensuring the security of data that is transmitted electronically (Directive 1999/93/EC of the European Parliament and of the Council of 13 December 1999 on a Community Framework for Electronic Signatures).

The purpose of the Directive is to facilitate the use of electronic signatures and to contribute to their legal recognition. It establishes a common framework for electronic signatures and certain certification services, in order to harmonise this type of activity in the internal market.

Detailed **technical specification** of the requirements for qualified certificates, certification service providers and secure signature creation devices that are generally provided for in the Annexes will have to be officially endorsed by the **Article 9 Committee** which has been tasked by the Directive to follow the technical developments. Suggestions related to these specifications have been discussed and agreed upon within the scope of the **European Electronic Signature Standardization Initiative (EESSI)**. Proposals for Secure Signature Creation Devices (SSCD), for a general format for Advanced Electronic Signatures, for Qualified Certificate Profiles, for Policies for Certification Providers issuing Qualified Certificates, for Time Stamping Profiles and for Procedures for Electronic Signature Verification have already been published and circulated for comment.

The smart card as a SSCD is more specifically addressing requirements for "advanced" or "qualified" signature, and targeting a great deal of business opportunities in e-Government applications, which most often require the setting of Public Key Infrastructures, for providing trust and confidence over open networks. Compatibility of national legislations and acknowledgement of wireless networks as infrastructures offering the required security mechanisms for such services and applications will be key issues for supporting the position of smart card as a SSCD in the years to come.

Privacy and personal data protection issues have as well a major impact on smart card technology and marketing requirements, as the card is most often holding -and protecting- the identity of users.

Most consumers are extremely reluctant to give out personal information, such as credit card number and expiry date, for fear that it will be intercepted by a third party and fraudulently used.

Again, the European Union has the most advanced regulatory framework as regards data protection. Two European Directives have to be mentioned, as directly relating to the T2R infrastructure:

- Directive 95/46/EC of the European Parliament and the Council of 24th October 1995 on the Protection of Personal Data 95/46/EG adopted 24th October 1995

- Directive 97/66/EC of the European Parliament and of the Council of 15 December 1997 concerning the processing of personal data and the protection of privacy in the telecommunications sector.

These two directives have been up-dated in 2002.

In most European countries, personal data protection is a constitutional principle and the right to privacy is enshrined in the European Convention on Human Rights (Article 8). However, until now, differences between national data protection laws have resulted in obstacles to transfers of personal data between Member States. Both Directives therefore lay down common rules, to be observed by those who collect, hold or transmit personal data as part of their economic or administrative activities or in the course of the activities of their association.

However whereas the Directive 97/66/EC relates only to data processing by telecommunication service providers, the Directive 95/46/EC holds the general principles for processing of personal data and regulates the transfer of personal data to third countries outside the European Union.

## 4 TECHNOLOGY CHALLENGES

Smart card related technology challenges are presented hereafter for the 6 main technology areas identified by RESET:

- Communication and networking

- Systems and S/W

- Smart card accepting devices, interfaces and biometry

- Card embedded peripherals, subsystems and micro-systems

- High-end cryptography, tamper-proof and security technologies

- Micro-electronics

#### 4.1 COMMUNICATION AND NETWORKS PROTOCOLS

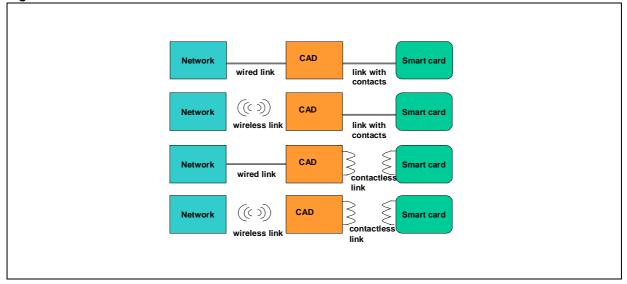

This chapter addresses the evolution of smart card communication protocols and the integration of smart card in new networks such as wireless home or corporate mobile networks.

Communications relate to physical and logical means that are needed and used by smart card to exchange information with at least a CAD. Usually communication operates with electrical and logical protocols.

Networking means that smart card is able to exchange data with other applicative entities, located somewhere on the network. It belongs to a distributed computing architecture and includes peers identification, as well as how to involve them. Networking uses communication services to work with external application in a peer to peer mode.

Hereinafter three areas for research and improvement of smart card in the domain of "Communication & Networking" are considered:

- Physical link

- Communication protocol

- Integration of smart card in networks.

#### 4.1.1 TECHNOLOGIES TRENDS AND MARKET REQUIREMENTS

Evolution of the smart cards technologies have to be assessed in relation with the evolution of information systems and network infrastructure.

#### SMART CARDS

From the beginning smart cards were developed on proprietary platforms and mostly used for one single application. One major change, driven by a lack of interoperability between smart card vendors, has been the move to open platform and more precisely Java. Aside from cutting costs and development time, Java is supposed to increase personalization of the service after the smart cards has been issued. This requires an evolution of the communication model for keeping its promise. Unfortunately, smart cards are still using ISO 7816 protocols which are not well suited for solving these new challenges.

#### **INFORMATION SYSTEMS**

As far as communication and networking are concerned, the major changes in the IT industry are:

- Internet protocols: TCP/IP everywhere, broadband Internet access, new application models (Web, peer-to-peer)

- High speed peripherals: USB, IEEE1394

#### **TELECOMMUNICATIONS**

Another major evolution concerns the telecom sector, where mobile phones are progressively replacing fixed network connections.

New requirements in communication and networking correspond to an interest for cooperation with IT industry, with the view to use the same communication standards in order to ease the convergence in the networks infrastructure managed by the different operators.

#### WIRELESS LOCAL AREA NETWORKS (W-LAN)

Wireless LAN is a new networking technology providing high speed data rate, which has rapidly gained much popularity. Different technologies exist which support different needs. The main players are:

- 802.11, for connection within a range of around 300 m

- Bluetooth, for personal environment (a few meters)

The improved convenience of wireless access to networks has increased the range of situations where people can perform computing, thus increasing security concerns.

#### CONCLUSION

In recent years, smart card has evolved from a specific device to a more open platform, offering multiple applications and enhanced security. At the same time, network connectivity has become an integral part of computing environments.

However, neither the smart card application model nor its communication protocols have evolved accordingly with regards to the evolving external computing world.

#### 4.1.2 SCIENTIFIC AND TECHNICAL CHALLENGES

Smart cards should carry on being used as trusted personal devices, with a better integration within their environment and high speed interfaces. Experts believe that the greatest challenge will be to integrate networking features inside the devices, with the view to make them a part of the interconnected IT world. For the time being, networking features are supported by the card accepting device. For the future, the trusted personal device should be able to virtually connect to an arbitrary Web page for getting up-dated information, as well as authenticating a transaction via a high-speed and secure direct link to a server.

#### PERFORMANCE IMPROVEMENT

In the context of the emergence of new protocols, it becomes urgent for the smart card to enhance its communication capabilities, according to the state of the art in the world to which it is connected.

It is necessary to improve the interface in both the wired and wireless modes. As an example, following targets should be considered:

- from Kbit/s to 100Mbits/s for data exchange speed rate

- low power consumption for enhanced portability

- full-duplex for multi-protocol

#### CONNECTIVITY ENHANCEMENT

From the communication and networking point of view, evolution towards open platform will become possible when smart card is in the position of being smoothly integrated in the interconnected IT world.

Following targets should be considered:

- TCP/IPv6 for Internet protocols

- Security of connection link

- Wireless communication protocols

The use of protocols such as IPv6 could compromise the privacy management required by a wide scope of applications. Therefore, the possibilities provided by IETF regarding privacy and security (such as IPSec or RFC3041) should be investigated.

#### SUPPORT NEW COMMUNICATION MODEL

Real multi-application smart card requires that different applications could have simultaneous access to available resources (communication stack, NVM memory, etc.). This will undoubtedly impact the underlying Operating System and the following aspects will have to be considered:

- Multi-tasking OS

- faster access to NVM

- improved RAM capacity

Further to interoperability and adaptability, new applications, such as secure peer-to-peer applications, will require smart cards being considered as real network nodes.

#### 4.1.3 RESEARCH ORIENTATIONS

Three areas for research and improvement are considered hereafter, as elements addressing smart card communication and networking: physical link, communication protocols, integration in networks.

#### 4.1.3.1 Short / Medium term

#### PHYSICAL LINK

Enhanced standard link between terminal and smart card

High speed protocol

#### **COMMUNICATION PROTOCOLS**

Non-exotic / non proprietary communication protocols easy to implement (in program) and available every where (e.g. IPv6)

#### INTEGRATION IN NETWORKS

Integration in wired and wireless Internet access specifications

## 4.1.3.2 Long term

## PHYSICAL LINK, COMMUNICATION PROTOCOL AND INTEGRATION IN NETWORKS:

Migration path to Smart Objects

Wireless Objects Protocols

Depending on the type of approach (smart card as a specific ISO device or as a "platform"), improvements could be assessed upon items introduced here under:

|                        | Device Current SC                                               | "Platform" extended SC                        |

|------------------------|-----------------------------------------------------------------|-----------------------------------------------|

|                        | Full duplex                                                     |                                               |

|                        | High speed                                                      |                                               |

| Physical link          | Clock recovery                                                  | Multi-interface (USB, Bluetooth,)             |

|                        | Pin(s) number                                                   |                                               |

|                        | Wireless                                                        |                                               |

|                        | Card to something (1 to 1 and 1 to any)                         | Peer to peer                                  |

|                        | Multi-protocol<br>Protocols used in IT and consumer (like lpv6) | Multi-protocol                                |

| Communication protocol |                                                                 | Protocols used in IT and consumer (like Ipv6) |

|                        | Wireless protocols                                              | Wireless protocols                            |

| Integration in network | Internet                                                        | Internet                                      |

| Integration in network | Security                                                        | Security                                      |

## ASSESSMENT OF PRIORITY TECHNOLOGIES

#### Operating system:

Multitasking operating system (cf Ch 4.2)

#### Hardware requirements:

Embedded RF

**Embedded Battery**

Faster non volatile memory access

Larger RAM

### Network requirements:

Connectivity with IT

Implementation of mobiles nodes connected through wireless links

Improvement of W-LAN technologies for large and dense networks

## Security requirements:

Maintenance of privacy and security level

### TENTATIVE TIME SCHEDULE

IPv6 integration: Short term (2 years from now)

High speed protocol: Short term (2 years from now)

Multi-tasking: Medium to long term (2 to 5 years from now)

Wireless solution: Medium to long term (2 to 5 years from now)

#### 4.2 SYSTEMS AND SOFTWARE

To cope with the broad range of topics involved with the technology domain "Systems and Software", three different sub domains were created:

- Operating Systems (OS) and High Level Languages

- Development Tools

- Systems Integration and Card Application Management

#### 4.2.1 TECHNOLOGY TRENDS AND MARKET REQUIREMENTS

Several general and sub-domain specific requirements can be identified. First of all, smart card systems should be dependable and trustworthy, which should be proven by high levels of certification. In contradiction to this, the development costs for new products have to be affordable and a short time to market is required for new products and applications. To meet both requirements, sophisticated development tools are needed.

From the IT systems side, smart cards must be easy to integrate into large networked systems, by appropriate middleware concepts.

The general future view is that with a single smart card, a given user should be able to connect anywhere, anytime, to all the value-added services he or she has subscribed to. It should also be easy for the user to add/remove any new type of service to/from the lot of subscriptions. In addition, this requires a sophisticated management of smart cards and their content.

#### 4.2.1.1 Operating systems and high-level languages

Future operating systems will have to support new upcoming hardware features. Mainly new communication and network protocols must be integrated. In addition multi-application capacity will be of importance. This does not only mean to store several applications on the card and to select between them, which is current state-of-the-art, but also to integrate the concurrent execution of applications on the card. Future programming languages must better support the special requirements of smart cards, either as high-level multi-purpose languages or as portable and efficient low-level languages (possibly with dedicated features).

#### 4.2.1.2 Development tools

In general research results from the software engineering field have to be adapted to the field of smart cards. Therefore, smart card specific requirements like the restricted resources and special security needs have to be considered. These tools have to support all aspects of certification and clearly defined validation techniques will be needed. An integrated design of on-card and off-card applications has to be considered.

#### 4.2.1.3 System integration

There is a strong need for improved system integration, which is currently on a very low level (proprietary APDU definitions).

Three main fields can be identified. First, smart card middleware will enable an easier integration. The card of the future will adapt itself to the end-user terminal or network to which it is connected, while still maintaining a high level of security for the applications. Second, smart cards that become smart objects need an improved management of the cards themselves, the applications, and the content stored on them. Third, project management tools will support the prediction of (human) resource requirements, distributed development, and the interaction between development and validation.

#### 4.2.2 SCIENTIFIC AND TECHNICAL CHALLENGES

#### 4.2.2.1 Operating systems and high-level languages

The main barrier that could be identified is the variety of smart card hardware that might hinder the development of more sophisticated operating systems and programming languages, due to the enormous porting costs.

The second barrier are the limited resources available on the smart card, since state of the art IT operating system techniques like multi-tasking and multi-threading cannot be easily adapted to the smart card hard-ware.

#### 4.2.2.2 Development tools

Concerning the development tools the main challenge will be to improve security and the certification process. Formal methods must be defined on different levels. Formal modelling with description languages should support concurrent and mobile computations. Formal verification should be as automatic as possible through the use of static analysis, model checking and automated theorem proving. Last, program verification that complements security issues has to address challenging issues like applet life time, persistence, atomicity and reset, specific runtime environments and libraries, etc. All of the before mentioned methods have to be supported by appropriate development tools. In addition, on-card analysers that verify applets have to support strong security models.

### 4.2.2.3 System integration

Although middleware and integration tools have already been investigated in Software Engineering to a certain extend, these concepts have to be adapted to the special characteristics of smart cards (e.g. restricted resources, I/O capabilities,...). A second challenge of importance is the management of smart cards and their content, which lacks a fundamental approach for defining the model(s) sustaining the card management system, thus conducting to difficult integration of card management systems in information systems.

#### **4.2.3 RESEARCH ORIENTATIONS**

#### 4.2.3.1 Short / Medium term

#### **OPERATING SYSTEMS**

The key themes for Operating Systems are: Open source OS., Multi tasking/multi-threading OS, File System management/Memory Management Models, Modularity (Multi layered OS), Real Time OS, I/ O speed enhancement, High-speed communication protocols.

#### **OPERATING SYSTEMS**

|                                            | Dynamic and symbolic on-card linking: this is a great way to reduce the burden on<br>both the application developers and the card issuers, because it reduces the man-<br>agement cost of the card. For example, loading class files complicates a bit the de-<br>sign of the OS, but reduces a lot the learning curve, which is today a big problem,<br>encountered by developers when they try to figure out what they can do with the<br>card. |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enhanced execution environment             | Multi-threaded OS: it is very useful to support true multi-application models. It is also mandatory to deploy applications developed independently, without à priori knowledge, which is not the case with current cards.                                                                                                                                                                                                                         |

|                                            | High-level memory management: it is necessary for the developer to reduce the work that has to do with memory, and it can help a lot on performance issues tra-<br>ditionally encountered with today's cards. Discussing persistent and transient memory managements and abstractions is a major issue.                                                                                                                                           |

|                                            | Enhanced transactions (with regards to multithreading)                                                                                                                                                                                                                                                                                                                                                                                            |

| Support for non-functional proper-<br>ties | QoS for e.g. streaming applications, but also for the management of generic laten-<br>cies.                                                                                                                                                                                                                                                                                                                                                       |

|                                            | Deadlock prevention/detection                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Resource control                           | Improved use of the card resources shared by multiple applications                                                                                                                                                                                                                                                                                                                                                                                |

|                                            | Lease model for resources: static/dynamic guarantees                                                                                                                                                                                                                                                                                                                                                                                              |

|                                            | Static scalability of the system with regards to hardware capabilities and applica-<br>tions requirements.Post-issuance update of the system components e.g. for real<br>and safe OS patches rather than proprietary card filters!                                                                                                                                                                                                                |

| System adaptability and flexibility        | Dynamic reconfiguration e.g. on the fly communication buffer resizing for optimi-<br>zation.                                                                                                                                                                                                                                                                                                                                                      |

|                                            | Dynamic extension e.g. for adding on-the-fly an application protocol (ftp) required by a newly installed applications                                                                                                                                                                                                                                                                                                                             |

| Declára                                    | For example, the SIM application has deadline constraints that are managed in the application code without any support/guarantee by an operating system. Facing real-time issues will be more and more critical in future applications.                                                                                                                                                                                                           |

| Real-time                                  | <ul> <li>Mastering the execution time of the OS primitives.</li> <li>Predicting execution time of application codes.</li> <li>Scheduling real-time tasks in accordance to their respective deadlines.</li> </ul>                                                                                                                                                                                                                                  |

#### HIGH LEVEL LANGUAGES

#### Better general-purpose programming languages

A first direction for improvement is to enhance the expressiveness of the programming languages used for smart card programming, while keeping them general-purpose: for instance, to replace the Java Card subset of Java by full Java, including garbage collection and threads. This requires a significant engineering effort, both on the system software side (implement garbage collection in the virtual machine) and on the hardware side (to revisit the RAM/Flash trade-off).

Alternative high-level languages should also be considered. An obvious alternative to Java is C#. However, C# shares much the same traits and limitations as Java; the choice between C# and Java is yet more

political than technical. Other languages of interest include Eiffel and Modula-3: both include native support for features that could help writing reliable and secure smart card applications. Eiffel supports logical assertions and programming by contract, while Modula-3 offers strong type abstraction and genericity mechanisms.

Rather than switching languages entirely, a "mix and match" approach is possible, whereas new language features of interest are added to a, say, Java base. For instance, Generic Java adds genericity to Java, and the JML modelling language (see below) adds logical assertions.

#### **Domain-specific and scripting languages**

Domain-specific languages (DSL) are a complementary alternative to general-purpose languages. By design, a DSL tries to reflect the characteristics and idioms of the intended application domain directly as language concepts, constructs, and notations. For instance, a DSL for financial analysis could have primitive notions of contracts, financial products, indicators, etc, with special syntax to express them -- just like integers or arrays are primitive notions with special syntax in general-purpose programming languages. DSLs do not emphasize generality -- many are not able to express arbitrary computations -- but aim at supporting a particular application domain with maximal clarity, safety and conciseness, and in such a way domain experts that are not professional programmers can write that programs.

The so-called scripting languages often start as domain-specific languages specialized in e.g. command scripting (command shells), Web programming (PHP), or text processing (AWK). Some scripting languages later evolve into full-fledged general-purpose languages via feature accretion (e.g. Perl, Python).

Besides allowing shorter, clearer programs, DSLs offer two advantages stemming from their limited expressiveness. First, they can often be compiled down to table-driven automata, or byte-code for specially designed virtual machine, leading to small compiled code that can be executed very efficiently. Second, DSLs often have a strong declarative flavour, thus facilitating the application of formal methods (proofs, model checking, test generation).

There have been relatively few attempts to apply the DSL / scripting approach to the smart card world. The only example we are aware of is the SIMspeak scripting language to describe succinctly customer interaction on GSM phones. Some examples of smart card programming situations where adequate DSLs could improve software quality and compactness:

- Implementation of APDU-based communication protocols, perhaps via ASN1-style notations for bitand byte-level manipulations, and automatic generation of robust encoders and decoders.

- Expressing concurrent computations in the synchronous reactive style (as in Esterel or SCADE), from which state machines interfaced with an asynchronous I/O API can be generated.

Other opportunities for using DSLs might emerge in the near future, once careful domain analyses are conducted.

#### DEVELOPMENT TOOLS

#### Connections with modelling and specification languages

Applying formal methods to a program requires that both the actual program and the specification it is intended to fulfil are expressed in a common framework that can be processed by machine. Sometimes, the program is obtained as a by-product of the specification, via incremental refinements of the specification up to a fully executable specification (as in the B method).

At the other end of the spectrum, the specification can be embedded as annotations inside the program: pre- and post-conditions on functions and methods, invariants for loops, etc. For the latter approach, the programming language must be extended with the ability to express these conditions and invariants in a suitable logic, and attach them to program points. The Java Modelling Language (JML) is an example of such an extension for the Java language. Significant work remains to be done to

- Design modelling languages that are sound and expressive, yet remain usable in practice, and

- Develop adequate interfaces between these modelling languages and existing theorem provers and model checkers.

In the longer term, efforts on modelling and specification languages can have significant fallbacks on the design of the programming languages themselves. Rather than considering formal methods as an after-thought, it could be worthwhile to take into account provability and testability early in the design of future programming languages. For instance, emphasis on program proofs favours declarative language constructs over imperative ones; and emphasis on model checking and formal testing favours programming via finite-state machines.

#### SYSTEM INTEGRATION

#### Integrated tools

Integrated set of tools for the development of applications in a global framework, permitting to test all types of elements, such as card applets, midlets, and all other sort of software components that fits in the framework. These tools should fit in very different usage scenarios: 3G Mobile networks, digital Pay-TV networks, TCP/IP based networks, etc.

#### Enabling technologies

#### RMI and others

Regarding Java Card, RMI seems the middleware of choice to use. From Java Card 2.2, the elements needed to bring RMI to the smart card begin to appear on scene. But the RMI, as it has been proposed in the specification aforementioned, is far from being optimal. In one hand, only unidirectional remote calls are foreseen, from the outside world to the applet inside the card. On the other hand, even this part is still lacking some services that should make use of remote objects inside the card completely transparent for the developer.

This gap should be filled in a first phase, so as that calls from client applications outside the card, to the applets inside the card, appear to be exactly the same as standard RMI. Then, RMI in the other direction (from inside to outside) should also be considered, since this would simplify the development of applets in some cases, or create new types of uses for these applets in other cases.

Other types of middleware technologies also could be considered to be ported to the card: Corba, SOAP based RPC, .NET Remoting, etc.

MIDP and others

Mobile Information Device Profile (MIDP) has been defined by Sun and other participants of the corresponding Java Community Process (JCP) expert group (MIDPEG). As it reads in one of their docs: "The

goal of this specification is to define the architecture and the associated APIs required to enable an open, third party, application development environment for mobile information devices, or MIDs". The idea is that this kind of specification will greatly simplify development of applications (midlets) for mobile devices that use the Java 2 Platform, Micro Edition (J2ME).