University of Twente Faculty of Electrical Engineering, Mathematics and Computer Science Telecommunication Engineering Group

# Context, Design and Implementation of a Control System for Ring Resonator-based Optical Beam Forming Networks

by

Jan-Willem van 't Klooster

Master thesis Executed from May 7, 2007 to October 10, 2008.

Supervisor: Dr. Ir. C.G.H. Roeloffzen Dr. Ir. A. Meijerink Dr. Ir. B.J.F. van Beijnum

## Summary

This Thesis reports on a Master assignment conducted at the Telecommunication Engineering (TE) Group at the University of Twente. The task is to develop and implement a control system for ring resonator-based Optical Beam Forming Networks (OBFNs).

Beam shaping and beam steering, together called beamforming, is needed when processing radio-frequency signals from phased array antennas. This can be achieved in the optical domain, by tuning an OBFN. The tuning of such a network is the task of a control system. That system is the topic of research in this assignment. It enables thermo-optical tuning of ring resonator based OBFNs.

In this thesis, the context, design and implementation of the control system are studied. Measurements are described to show the correct working of the implemented prototype.

The control system may be used in the future in an airborne application. It may form part of a system that provides services such as radio, television, and internet access to en route aircraft. It is a challenge to make this possible.

The control system consists of a controller and an interface to operate it. The controller has hardware and software aspects. The hardware is a modular set of components that can easily be extended when necessary. The software in the controller operates the hardware and provides the means for tuning OBFNs. A graphical interface is provided on a PC to operate the controller. This can easily be adapted to future needs.

Two prototypes for the control system have been delivered in this assignment. The first prototype met the most important requirements but was not very easy to operate. The second implemented also met the more advanced requirements, enabled tuning of larger OBFNs, and was provided with an easy-to-use Java interface.

The system has been used extensively in the TE lab and also at the Dutch Aerospace Laboratory (NLR). In the future, the system can be extended to provide angle and

azimuth steering (to steer the beam to a certain point) and tracking and tracing functionalities (to find and keep focussed on a source).

# Samenvatting

Dit afstudeerverslag doet verslag van een afstudeeropdracht bij de Telecommunication Engineering (TE) Group van de Universiteit Twente. Het doel van deze opdracht is om een aansturingssysteem te ontwerpen en te realiseren.

*Beam shaping* en *beam steering*, samen ook wel bundelvorming genoemd, is noodzakelijk vor het verwerken van signalen van meerdere antennes, zoals antenne-arrays. Deze functionaliteit kan worden gerealiseerd in het optische domein, door middel van het tunen van een optisch bundelvorm-netwerk (OBFN). Een aanstuursysteem zorgt voor het correct afregelen van zo'n netwerk. Dit systeem is het onderwerp van onderzoek in deze opdracht.

In dit verslag worden de context, het ontwerp en de implementatie van dit controlesysteem bestudeerd. Om de correcte werking van het geimplementeerde prototype aan te tonen, worden tevens metingen beschreven.

In de toekomst kan het aanstuursysteem worden gebruikt in de luchtvaart. Het zou onderdeel uit kunnen maken van een systeem dat zorgt voor diensten zoals televisie en internet op vliegtuigen die onderweg zijn.

Het ontwerp van het aanstuursysteem bestaat uit een aansturend gedeelte en een interface om het aansturende gedeelte te bedienen. Het aansturende gedeelte heeft zowel hardware- als software aspecten. De hardware is een modulaire set componenten, die gemakkelijk kan worden uitgebreid, indien noodzakelijk. De software in de controller bedient de hardware en zorgt ervoor dat OBFN's kunnen worden getuned. Op een PC is een interface aanwezig waarmee de controller kan worden bediend. Deze kan eenvoudig worden aangepast aan toekomstige eisen.

Tijdens deze opdracht zijn twee versies van het aanstuursysteem opgeleverd. Het eerste prototype voldeed aan de belangrijkste eisen, maar was niet erg gebruiksvriendelijk. De tweede implementatie voldeed ook aan de meer geavanceerde eisen, en maakte het mogelijk om grotere OBFN's af te kunnen regelen. De bediening van deze versie is een stuk gemakkelijker omdat voorzien was in een gebruiksvriendelijke, grafische Javainterface.

Het systeem is veel gebruikt in het laboratorium van TE en tevens in het Nederlands Lucht- en Ruimtevaartlaboratorium (NLR). In de toekomst kan het systeem worden uitgebreid met functionaliteiten zoals hoek- en azimutsturing en het traceren en volgen van een bepaalde zender.

## Foreword

Welcome. In front of you is my Master thesis, written to accomplish my Master of Science study in Telematics. Writing a thesis has parallels with the story of Theseus, the ancient Greek hero, who faced and overcame a multifaceted problem and a labyrinth, with some aid of good people.

The work on which this thesis reports is conducted within the Telecommunication Engineering Group at the University of Twente. The assignment was to make a controller for optical beamforming networks. You can read all about this in this thesis.

Now I am almost finished writing, I want to thank some people. First of all my daily advisor dr. ir. Chris Roeloffzen, whose aid and ideas have really been useful. Chris has the wonderful ability to really motivate tens or maybe even hundreds of people and stil give them all personal attention. Moreover, he is one of the best down-to-earth teachers explaining difficult topics in very clear language.

I want to thank prof. dr. ir. Wim van Etten for giving me the opportunity to graduate at Telecommunication Engineering, and I also want to thank my advisors dr. ir. Arjan Meijerink and dr. ir. Bert-Jan van Beijnum, for their useful ideas and the good discussions. I would like to thank Jaco, Pieter, Adriaan and Harm from NLR for their support.

Without the support of my family and girlfriend this result would never have been possible, therefore a very big thank you to Anita and Kees and to Tabea, who are always there for me. I also want to thank my father for his professional support and ideas, and for motivating me to publish.

Leimeng, Eduard and Theo I want to thank for their assistance, mainly in the TE lab and I want to thank my fellow (ex-)students Audrey, Roland, Dick, Liang, Sjoerd, Nicolas, Martin, Roelof, Jack and Thomas for the good time at the group, as well as all employees, PhD students and the secretary Lilian for their support. TE is a really inspiring working environment to go to!

Another very good place to work is Menzing in Haaksbergen, I want to thank Erik to being so flexible regarding my tasks there.

Last but not least I would like to thank my good friends Patrick, Wouter, Olivier, Ivo, Evert, Vera, Gert, Martijn, Wilco, Emad and Rob for the good times.

Of course there are people I have forgotten. So do not worry if you are not listed, I also want to thank you. You know why.

Jan-Willem van 't Klooster, October 4<sup>th</sup>, 2008.

# **Abbreviations**

| AE      | Antenna Element                                           |

|---------|-----------------------------------------------------------|

| СВВ     | Connexion By Boeing                                       |

| CDMA    | Code Division Multiple Access                             |

| сотѕ    | commercial of the shelf                                   |

| CS      | Chip Select                                               |

| DAC     | Digital to Analog Converter                               |

| DFD     | Data Flow Diagram                                         |

| DSSS    | Direct Sequence Spread Spectrum                           |

| DVB-RCS | Digital Video Broadcasting - Return Channel via Satellite |

| DVB-S   | Digital Video Broadcasting - Satellite                    |

| DVB-S2  | Digital Video Broadcasting - Satellite 2                  |

| EDFA    | Erbium Doped Fiber Amplifier                              |

| EMI     | Electromagnetic Interference                              |

| EPG     | Electronic Programming Guide                              |

| FDC     | Frequency down conversion                                 |

| FDMA    | Frequency Division Multiple Access                        |

| FHSS    | Frequency Hopping Spread Spectrum                         |

| FRAM    | Ferroelectric Random Access Memory                        |

| FSR     | Free Spectral Range                                       |

| FTDI    | Future Technology Devices International                   |

| GES   | Ground Earth Station                                           |

|-------|----------------------------------------------------------------|

| GPRS  | General Packet Radio Service                                   |

| GUI   | Graphical User Interface                                       |

| IBM   | International Business Machines                                |

| IDE   | Integrated Drive Electronics                                   |

| IETF  | Internet Engineering Task Force                                |

| ISDN  | Integrated Services Digital Network                            |

| IP    | Internet Protocol                                              |

| LAN   | Local Area Network                                             |

| LCD   | Liquid Crystal Display                                         |

| LED   | Light Emitting Diode                                           |

| LEE   | Lammerink Electrical Engineering                               |

| LLC   | Logical Link Control                                           |

| LNA   | Low Noise Amplifier                                            |

| MAC   | Medium Access Control                                          |

| MiSo  | Master In Slave Out                                            |

| MES   | Mobile Earth Station                                           |

| MoSi  | Master Out Slave In                                            |

| MVC   | Model View Control                                             |

| MZI   | Mach-Zehnder Interferometer                                    |

| NIVR  | Nederlands Instituut voor Vliegtuigontwikkeling en Ruimtevaart |

| NLR   | National Aerospace Laboratory                                  |

| OBFN  | Optical Beam Forming Network                                   |

| opamp | operational amplifier                                          |

**ORR** Optical Ring Resonator

| OSBF   | Optical Sideband Filter                         |

|--------|-------------------------------------------------|

| ΡΑΑ    | Phased Array Antenna                            |

| РСВ    | Printed Circuit Board                           |

| RISC   | Reduced Instruction Set Computer                |

| SACK   | Selective Acknowledgement                       |

| SD     | Secure Digital                                  |

| SPI    | Serial Perhiperal Interface                     |

| SSB-SC | Single Sideband Suppressed Carrier              |

| ТСР    | Transport Control Protocol                      |

| TDMA   | Time Division Multiple Access                   |

| ТЕ     | Telecommunication Engineering                   |

| TEC    | Temperature Controller                          |

| UART   | Universal Asynchronous Receiver and Transmitter |

| UDP    | User Datagram Protocol                          |

| UML    | Unified Modelling Language                      |

| UMTS   | Universal Mobile Telecommunications System      |

# Contents

| Sι | ımma  | ary     |                                                             | iii |

|----|-------|---------|-------------------------------------------------------------|-----|

| Sa | men   | vatting |                                                             | v   |

| Fo | orewo | rd      |                                                             | vii |

| AI | bbrev | iations |                                                             | xi  |

| 1  | Intr  | oductio | on                                                          | 1   |

|    | 1.1   | Motiva  | ation                                                       | 1   |

|    | 1.2   | Backg   | round                                                       | 2   |

|    |       | 1.2.1   | System overview                                             | 2   |

|    |       | 1.2.2   | Related work                                                | 6   |

|    | 1.3   | Resear  | rch organization                                            | 7   |

|    |       | 1.3.1   | Research goals                                              | 7   |

|    |       | 1.3.2   | Methodology                                                 | 7   |

|    |       | 1.3.3   | Research questions                                          | 8   |

|    | 1.4   | Thesis  | g organization                                              | 8   |

| 2  | Con   | text    |                                                             | 9   |

|    | 2.1   | OSI R   | Leference model                                             | 9   |

|    | 2.2   | Motiva  | ation                                                       | 11  |

|    | 2.3   | Desigr  | ns                                                          | 11  |

|    |       | 2.3.1   | A design employing a unidirectional satellite link $\ldots$ | 11  |

|    |       | 2.3.2   | A design employing a bidirectional satellite link $\ldots$  | 12  |

|    | 2.4   | Infrast | tructure                                                    | 13  |

|    | 2.5   | Conse   | quences                                                     | 15  |

|    |       | 2.5.1   | Operational issues                                          | 15  |

|    |       | 2.5.2   | Hardware issues                                             | 15  |

|    |       | 2.5.3   | Software issues                                             | 16  |

|    |       | 2.5.4   | Network issues                                              | 17  |

|    | 2.6   | Discus  | ssion                                                       | 17  |

|   | 2.7 | Summary 1                                                                                                                                 | 18 |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3 | Des | ign of the Control System 1                                                                                                               | 9  |

|   | 3.1 | Requirements analysis                                                                                                                     | 19 |

|   |     | 3.1.1 Hardware requirements                                                                                                               | 19 |

|   |     | 3.1.2 Software requirements                                                                                                               | 20 |

|   |     | 3.1.3 Performance requirements                                                                                                            | 20 |

|   | 3.2 | Use cases                                                                                                                                 | 21 |

|   | 3.3 | Design                                                                                                                                    | 22 |

|   |     | 3.3.1 Hardware design                                                                                                                     | 22 |

|   |     | 3.3.2 Software design $\ldots \ldots 2$ | 23 |

|   | 3.4 | Summary                                                                                                                                   | 25 |

| 4 | Imp | lementation of the Control System 2                                                                                                       | 27 |

|   | 4.1 | Implementation approach                                                                                                                   | 27 |

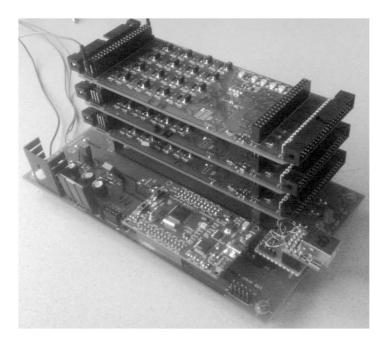

|   |     | 4.1.1 Hardware                                                                                                                            | 28 |

|   |     | 4.1.2 Software                                                                                                                            | 28 |

|   | 4.2 | Implementation of the Yeti controller                                                                                                     | 29 |

|   |     | $4.2.1$ Motherboard $\ldots$ $2$                                                                                                          | 29 |

|   |     | 4.2.2 Other components                                                                                                                    | 29 |

|   |     | 4.2.3 Communication between PC and controller                                                                                             | 29 |

|   | 4.3 | Implementation of the FlySmart controller                                                                                                 | 30 |

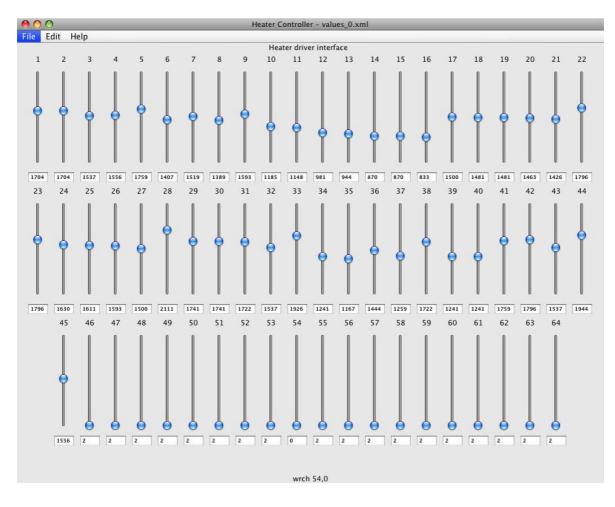

|   |     | 4.3.1 User interaction $\ldots \ldots 3$                                   | 30 |

|   |     | 4.3.2 Speed improvement                                                                                                                   | 30 |

|   |     | 4.3.3 Addressing more channels                                                                                                            | 31 |

|   | 4.4 | Setting calculation                                                                                                                       | 32 |

|   | 4.5 | Controlling the channels                                                                                                                  | 34 |

|   | 4.6 | A reconsideration of the interface                                                                                                        | 35 |

|   | 4.7 | Extending the number of DAC PCBs 3                                                                                                        | 36 |

|   | 4.8 | Summary and conclusions                                                                                                                   | 37 |

| 5 | Mea | asurements 3                                                                                                                              | 9  |

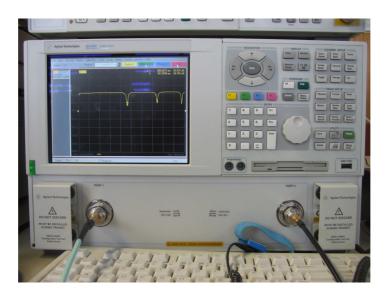

|   | 5.1 | Controller measurements                                                                                                                   | 39 |

|   |     | 5.1.1 FRAM measurements                                                                                                                   | 39 |

|   |     | 5.1.2 DAC measurements                                                                                                                    | 10 |

|   |     | 5.1.3 Discussion $\ldots \ldots 4$                           | 11 |

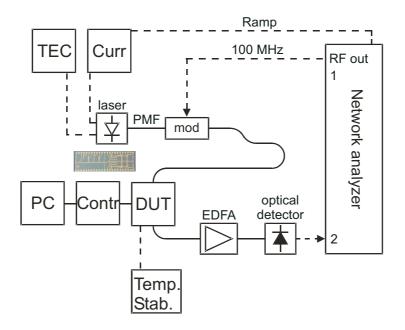

|   | 5.2 |                                                                                                                                           | 11 |

|   | 5.3 |                                                                                                                                           | 14 |

|   |     | -                                                                                                                                         | 14 |

|   |     |                                                                                                                                           | 14 |

|        | 5.4                                                                                                                | $FlySmart chip \dots \dots$                                                                                                                                                                                                                                                                                                                                                 | 16                                                       |

|--------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|        |                                                                                                                    | 5.4.1 Delay measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                                                       |

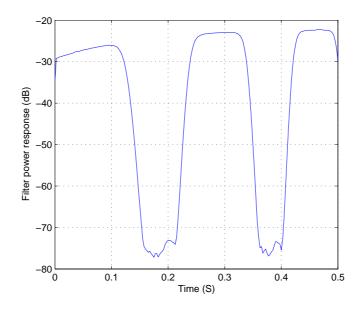

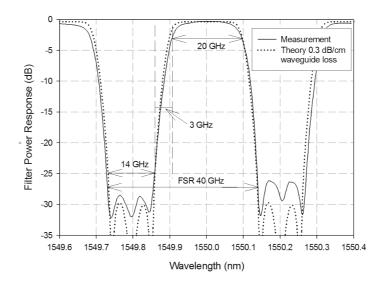

|        |                                                                                                                    | $5.4.2$ Filter measurements $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 4$                                                                                                                                                                                                                                                                                                                                                                             | 17                                                       |

|        |                                                                                                                    | 6.4.3 Ring behavior measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                       |

|        |                                                                                                                    | 5.4.4 EMI measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53                                                       |

|        | 5.5                                                                                                                | Discussion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $5$                                                                                                                                                                                                                                                                                                                                                                                                     | 53                                                       |

|        | 5.6                                                                                                                | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54                                                       |

| 6      | Con                                                                                                                | usions and directions for further research 5                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                                                        |

|        | 6.1                                                                                                                | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57                                                       |

|        | 6.2                                                                                                                | Directions for further research                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 59                                                       |

| Re     | ferer                                                                                                              | es 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                        |

| Ар     | penc                                                                                                               | ces 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3                                                        |

|        | <b>C</b>                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F                                                        |

| Α      | Con                                                                                                                | oller Commands 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ))                                                       |

| A<br>B |                                                                                                                    | oller Commands 6<br>Protocol 6                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

|        |                                                                                                                    | Protocol 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

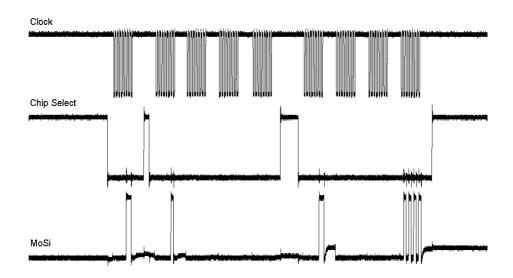

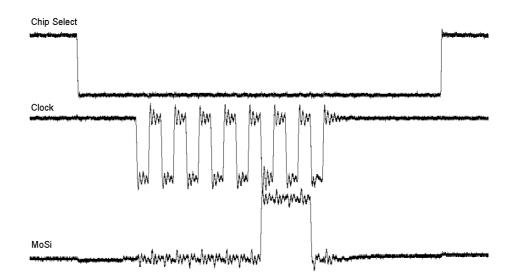

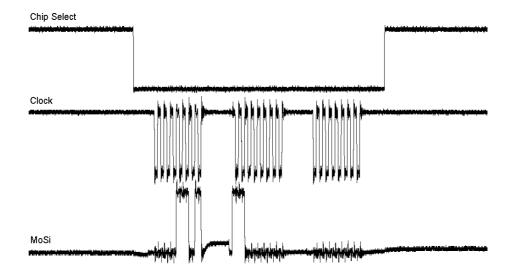

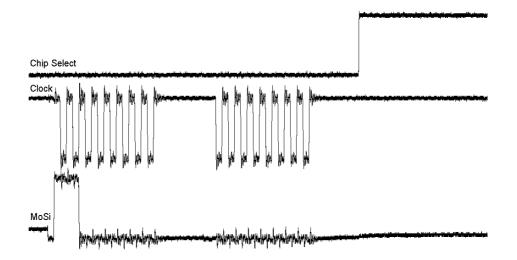

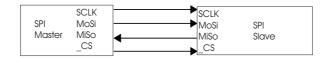

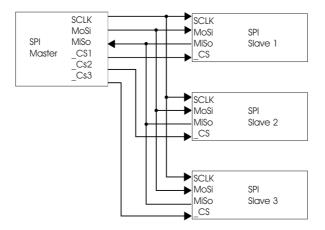

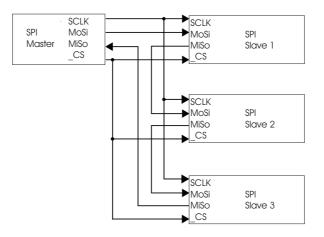

|        | SPI                                                                                                                | Protocol 6<br>SPI overview                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                        |

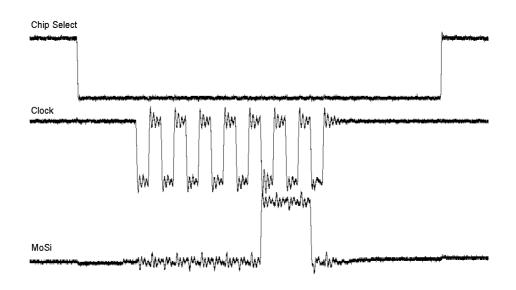

|        | SPI                                                                                                                | Protocol       6         SPI overview       6         3.1.1       Transmission: chip select       6                                                                                                                                                                                                                                                                                                                                                                               | 5 <b>7</b><br>57                                         |

|        | <b>SPI</b><br>B.1                                                                                                  | Protocol       6         SPI overview       6         3.1.1       Transmission: chip select       6         Modes       6                                                                                                                                                                                                                                                                                                                                                         | 5 <b>7</b><br>57                                         |

|        | <b>SPI</b><br>B.1                                                                                                  | Protocol       6         SPI overview       6         3.1.1       Transmission: chip select       6         Modes       6         3.2.1       Different modes on the controller       6                                                                                                                                                                                                                                                                                           | 5 <b>7</b><br>58<br>58                                   |

|        | <b>SPI</b><br>B.1<br>B.2                                                                                           | Protocol       6         SPI overview       6         3.1.1       Transmission: chip select       6         Modes       6         3.2.1       Different modes on the controller       6         Different chip select lines or daisy chain       6                                                                                                                                                                                                                                | 5 <b>7</b><br>57<br>58<br>58<br>59                       |

|        | <b>SPI</b><br>B.1<br>B.2<br>B.3                                                                                    | Protocol6SPI overview63.1.1Transmission: chip select6Modes63.2.1Different modes on the controller6Different chip select lines or daisy chain63.3.1SPI adjustments for three DAC PCBs7                                                                                                                                                                                                                                                                                             | 5 <b>7</b><br>58<br>58<br>58                             |

| В      | <b>SPI</b><br>B.1<br>B.2<br>B.3<br>B.4                                                                             | Protocol       6         SPI overview       6         3.1.1       Transmission: chip select       6         Modes       6         3.2.1       Different modes on the controller       6         Different chip select lines or daisy chain       6         3.3.1       SPI adjustments for three DAC PCBs       7                                                                                                                                                                 | 5 <b>7</b><br>57<br>58<br>58<br>59<br>59<br>70<br>73     |

| В      | <b>SPI</b><br>B.1<br>B.2<br>B.3<br>B.4                                                                             | Protocol6SPI overview63.1.1Transmission: chip select6Modes63.2.1Different modes on the controller6Different chip select lines or daisy chain63.3.1SPI adjustments for three DAC PCBs7Suggestion with regard to SPI7Package7                                                                                                                                                                                                                                                       | 57<br>57<br>58<br>58<br>59<br>59<br>70<br>73             |

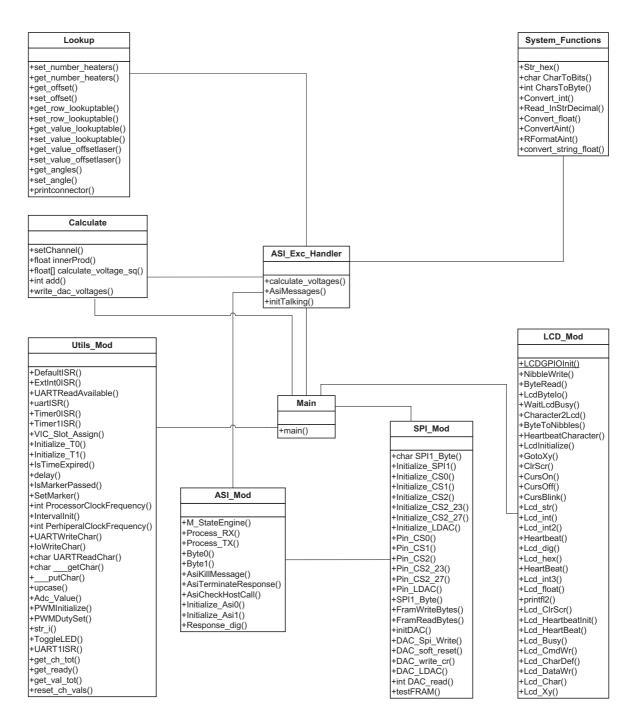

| В      | <ul> <li>SPI</li> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>Cod</li> </ul>                           | Protocol       6         SPI overview       6         3.1.1       Transmission: chip select       6         Modes       6         3.2.1       Different modes on the controller       6         3.2.1       Different modes on the controller       6         Different chip select lines or daisy chain       6         3.3.1       SPI adjustments for three DAC PCBs       7         Suggestion with regard to SPI       7         Package       7         JML diagram       7 | 57<br>57<br>58<br>58<br>59<br>59<br>70<br>73             |

| В      | <ul> <li>SPI</li> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>Cod</li> <li>C.1</li> <li>C.2</li> </ul> | Protocol       6         SPI overview       6         3.1.1       Transmission: chip select       6         Modes       6         3.2.1       Different modes on the controller       6         3.2.1       Different modes on the controller       6         Different chip select lines or daisy chain       6         3.3.1       SPI adjustments for three DAC PCBs       7         Suggestion with regard to SPI       7         Package       7         JML diagram       7 | 57<br>57<br>58<br>58<br>59<br>59<br>70<br>73<br>75<br>75 |

## Chapter 1

## Introduction

A Phased Array Antenna (PAA) is an interesting alternative to a conventional dish antenna because of its appealing properties such as flatness, electronical steering and multi-beam capabilities.

Beam shaping and beam steering, together called *beamforming*, is needed when processing radiofrequency signals from PAAs. This can be achieved by tuning an Optical Beam Forming Network (OBFN). The tuning of such a network is the task of a control system. That system is the subject of this Master assignment.

The purpose of this Thesis is to present the context, design and implementation of a control system for ring resonator-based OBFNs. That control system was developed at the chair of Telecommunication Engineering (TE), within in the context of the SMART project: **Sm**art **A**ntennas for **R**adio **T**ransceivers [1].

The chapter continues as follows. The motivation for this assignment is given in Section 1.1. In Section 1.2, the background of this research is presented. The system description is given and related work is discussed. Section 1.3 gives the research organization. The methodology that is used is presented, and the research goals and question are formulated. This chapter ends with the structure of the Thesis in Section 1.4.

### 1.1 Motivation

There are two main reasons<sup>1</sup> for conducting this Master assignment.

- 1. The development of the controller is a challenging engineering activity that is not finished yet. Important parts of the controller still have to be designed, and the complete control system has to be integrated and implemented as a part of this assignment, in order to tune OBFNs.

- 2. The TE group is interested in the higher layer aspects of the beamforming system. For example, what applications could be made available with such a

<sup>&</sup>lt;sup>1</sup>Another main reason (outside this particular scope) is obtaining an MSc degree.

system, and are there any consequences for the infrastructures and protocols on which these applications rely? The project results require higher level developments to reach production readiness eventually.

## 1.2 Background

The task is to make a controller for the beamformer used in the SMART project. Beamforming is necessary when combining signals from multiple antennas, such as PAAs.

When receiving, the beamformer is tuned, such that it combines the signals of the antenna elements with the right delay. In that way, constructive interference and a stronger signal is achieved.

When transmitting, the signal is split and delayed in the beamformer to a certain extent, before radiated by the antenna elements in the desired direction. This work focusses mostly on receive scenarios however.

Beamforming can be achieved in various ways, including digital beamforming, microwave beamforming, local beamforming, aerial beamforming and optical beamforming [2].

We focus on optical beamforming. This technology provides compactness, large bandwidth, frequency independence, Electromagnetic Interference (EMI) immunity, low loss, potentially low costs, and no beam squinting, which is often a problem with electronic beamforming. Hence it is possible to communicate in a tunable direction, in a cost effective manner. It is possible to enable a large instantaneous bandwidth. So the amount of information that can potentially be processed instantaneously, is large when optical beamforming is employed. For applications such as broadband internet access or mobile satellite television reception, this is a very useful feature.

#### 1.2.1 System overview

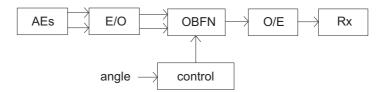

The proposed SMART system is a system employing optical beamforming. It is shown in Figure 1.1. For a receive scenario, it consist of the shown parts. The Antenna Elements (AEs) receive satellite signals. These RF signals are intensity modulated onto an optical carrier (E/O block) and fed into the OBFN, where they are delayed and combined. This results in one strong optical signal, which is then converted back to the electrical domain using a photodiode detector (O/E block). Afterwards, it can be detected using for example a set top box.

The tuning of the OBFN is managed by a control system. Its input is information belonging to the steering angle of the antenna array. Using this information, the OBFN is tuned such that there is *constructive interference* for RF signals coming from the

# Figure 1.1: System overview of the optical beamforming system for phased array receive antennas.

desired direction.

At the heart of this system is the OBFN, produced on an optical chip. The next part of this introduction discusses the OBFN.

#### **Optical beamforming network**

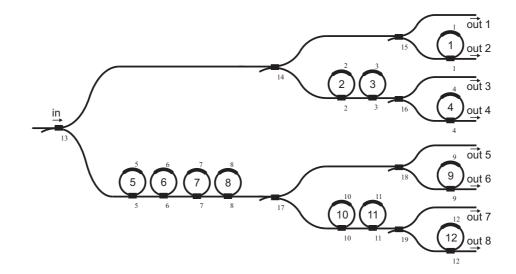

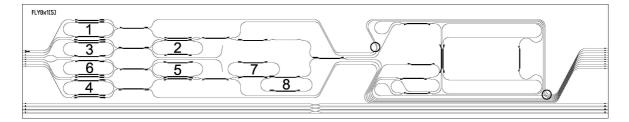

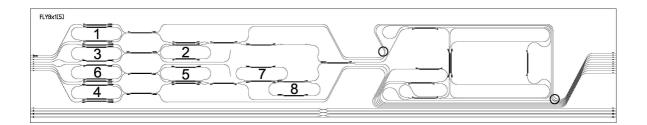

The optical chip in this system is manufactured using planar optical waveguide technology by Lionix B.V. [3]. It consists of the following building blocks: waveguides, Mach-Zehnder Interferometers (MZIs), couplers and Optical Ring Resonators (ORRs). ORRs are chosen because they provide true time delay when cascaded, so beam squinting will not occur. The building blocks are combined to form an OBFN. A  $1\times8$  OBFN for a transmitter phased array is shown in Figure 1.2.

**Figure 1.2:** A 1×8 binary tree OBFN for a transmitter phased array antenna with 1 input, 8 outputs and 12 optical ring resonators.

It employs a binary tree topology, which has an efficient layout with respect to the required number of ORRs. This puts restrictions on tuning freedom compared to a parallel topology, but reduces tuning complexity. An ORR consists of a straight waveguide and a circular waveguide coupled to it. It has a periodic group delay response, representing the effective time delay to the modulated RF signal. The group delay is expressed by [4]

$$\tau_{\rm g}(f) = \frac{(\kappa T)}{2 - \kappa - 2\sqrt{1 - \kappa}\cos(2\pi f T + \phi)} \tag{1.1}$$

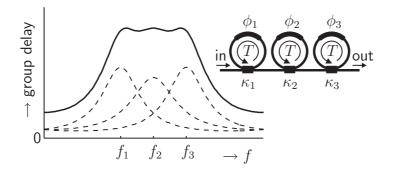

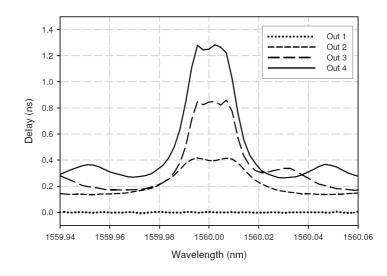

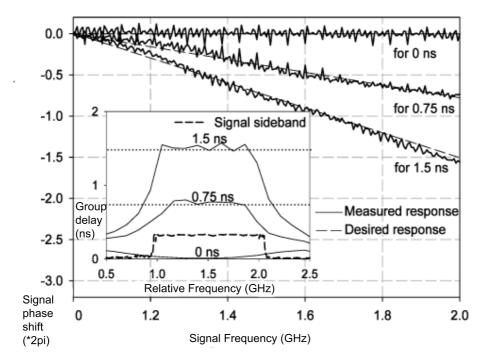

It depends on the round trip time T, the power coupling coefficient  $\kappa$  and additional round-trip phase shift of the ring  $\phi$ . It is possible to control both the phase shift  $\phi$  and power coupling coefficient  $\kappa$ , thereby tuning the ORR peak value delay and resonance frequency. There is a trade-off between peak delay and bandwidth. Therefore it is required to cascade ORRs, creating broadband delay elements. This yields a group delay response that is simply the sum of the individual ORR responses. Figure 1.3 clarifies this: the group delay response of three cascaded rings (shown in the inset) is the sum of the three individual responses, marked with the three dashed lines. As the resonance frequencies of the ORRs gets closer, the ripple becomes smaller. The group delay then becomes more flat, but at the cost of a smaller bandwidth.

Figure 1.3: Theoretical group delay response of three cascaded ORRs. The three dashed lines in the graph show the group delay responses for the three individually tuned ORRs. The solid line is the total group delay. The inset shows the configuration and tunable elements of three cascaded ORRs. (picture taken from [5]).

In our system, the OBFN is used to realign the individual AE signals, in order to combine them with maximal constructive interference. The output of a single laser is split, after which each AE signal is modulated using filter-based Single Sideband Suppressed Carrier (SSB-SC) modulation, as discussed below.

The optical chip is tuned thermo-optically by electrically heating chromium resistors on it. As a consequence, the optical waveguide heats up and its refractive index changes. This allows for tuning of the resonance frequencies and power coupling ratios. The tuning is performed by the control system, as discussed later in this Section. Thermooptical tuning itself is very well explained in Section 3.4 of [6].

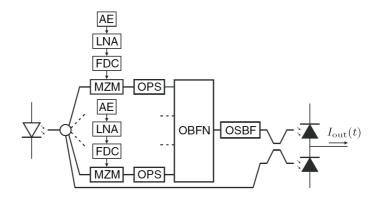

#### Modulation and demodulation

A more architectural view of the system is presented in Figure 1.4. After amplification in the Low Noise Amplifier (LNA) and Frequency down conversion (FDC), E/O conversion is done using a Mach-Zehnder Modulator (MZM). The Antenna Element (AE) signals are then processed in the OBFN and enter an Optical Sideband Filter (OSBF). This is used to reduce the optical bandwidth as it filters out one sideband and the carrier of the optical signal, resulting in SSB-SC modulation. Because of this type of modulation, balanced detection is used. A  $2\times 2$  directional coupler (combining an unmodulated version of the optical signal and the OSBF output) and two photo diodes as shown in the right part of the Figure serve as the balanced detector.

**Figure 1.4:** The system architecture (taken from [7]).

#### **Control** system

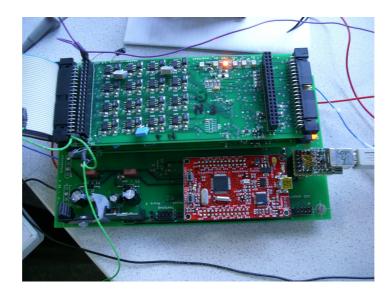

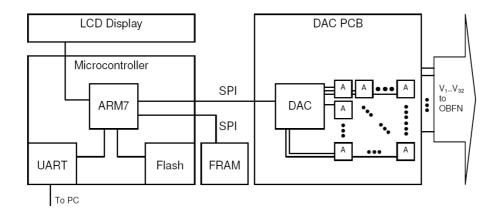

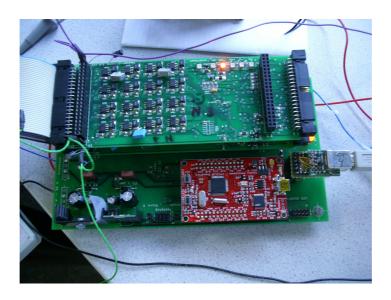

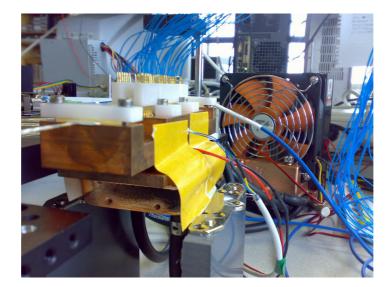

This part currently consists of an amplifier array Printed Circuit Board (PCB) and a microcontroller. The microcontroller is a Rowley CrossFire LPC2138 equipped with an LPC2138 Reduced Instruction Set Computer (RISC) microprocessor. It can be programmed via an universal USB. It controls the amplifier PCB that actually heats the chromium heaters on the OBFNs. This is done by sending commands to it via the RS232 port of a PC. Part of the task is to integrate the chosen and existing hardware onto a mother board, to provide the microcontroller with software such that it can tune OBFNs, and to make an interface for it on a PC.

#### Case study

Throughout the assignment, usage of the SMART system on a passenger aircraft serves as a case study. It is among the goals of the SMART project to provide the airplane industry with antenna systems suited for broadband data communication in-flight. This draws the need for weather-proof steerable antennas and high data throughputs. When connected to orbiting satellites, data communication thus can be provided to offer single unidirectional communication services such as live television, or bidirectional services such as internet. This is a reason why special attention to these services is given in Chapter 2.

#### 1.2.2 Related work

This section covers achievements and other projects that are related to this work because of similarities.

#### **Connexion By Boeing**

Broadband full duplex connectivity was provided to airplanes via geostationary satellites in the Connexion By Boeing (CBB) service. The antenna subsystem used PAAs and conventional dish antennas for transmission and reception via commercial Ku-band links. In this way it was possible to provide high speed internet connections to en route aircraft passengers [8], [9].

There are quite demanding technical requirements for *avionics* (aviation electronics). Airborne equipment should conform to RTCA/DO-160E [10]. This is usually driving up the costs of installation. This was also one of the reasons Boeing shut the initiative down: it was too expensive as a non-core business. Moreover, third parties were not willing to invest in it. Boeing did not want to continue the service as the market had not developed as was expected. CBB also carried out experiments using piconet GSM and CDMA2000 cells, providing mobile telephony access in-flight in cooperation with Qualcomm. By closing down the CBB initiave, also this extension stopped however.

#### Lufthansa

Lufthansa, interested in providing onboard internet access, used the CBB system until 2006 and called it *SkyAccess*. When CBB stopped, Lufthansa provided access to customers via satcom provider Thrane & Thrane. Their solution includes a mobile access router that is also capable of routing traffic via General Packet Radio Service (GPRS), Wireless Local Area Network (LAN), and Integrated Services Digital Network (ISDN) depending on the place of the aircraft. The WLAN interface is called GateLink, a 802.11g based connection to link aircraft to ground crew.

#### Starling MIJET

An Israelic company called Starling Advanced Communications offers an broadband bidirectional Ku-band satellite link via its service called MIJET. Using this link it is possible to have full duplex internet access [11]. Ku-band is chosen for several reasons, including the capability to deliver broadband access, and the use of mature existing technology. Satellites are widely available and the ground infrastructure already exists. It uses a integrated, mechanically steered 75 cm diameter, 15 cm heigh antenna that supports bitrates up to 1.25 Mbps (uplink from the aircraft) and 10-15 Mbps (downlink towards the aircraft). Peak test rates were even up to 5 Mbps (uplink) and 20 Mbps (downlink).

## 1.3 Research organization

This section briefly states the research goals, the methodology used to conduct the research, and the research questions that have to be answered when this assignment is finished. Research goals define the 'what' of an assignment, and the methodology states the 'how', how an assignment is conducted. As an aid for focus and guideline to what should be answered in the conclusions, the research questions are formulated.

#### 1.3.1 Research goals

The goals of this research are listed below in chronological order.

- 1. The software, hardware and performance *requirements* for the control system should be made clear.

- 2. Based on the requirements, a *modular design* for the controller will be developed. This design should be documented in this report.

- 3. Afterwards, it is a goal to develop a working *prototype* based on this design, and based on current developments of the complete system.

- 4. It should be reported how the system could be used, what *services* should be available, and how they could be made available.

#### 1.3.2 Methodology

A methodology is used to identify distinct actions taken in the process of this assignment. [12]. The following steps are taken in a more or less sequential order.

- Literature study. Related papers, theses and books are studied to get acquinted with the subject.

- **Definition of research questions.** In this Thesis, several research questions will be answered. These questions are given further on in this section.

- **Requirements analysis.** In order to present a proper design and implementation of a controlling system, the requirements have to be studied and get clear.

- Architecture design. The design of the controlling system is presented based on which a prototype can build.

- **Prototype implementation.** A prototype implementation is developed to test and verify the design, and to provide input for further research.

- **Results and conclusions.** The results are evaluated. Research questions will be answered and conclusions will be formulated.

- Suggestions for further research. Indications in which further research could be directed are pointed out.

This thesis documents the above mentioned steps.

#### 1.3.3 Research questions

In this section, the research questions and subquestions for this project are presented. The following questions and subquestions are identified in this research:

- 1. What would a *design* for a control system for OBFNs consist of?

- 2. To what extent is it possible to implement and evaluate a *prototype* for such a controlling system, and how could this system be used in an airplane?

Separate Chapters address the main research questions as will be pointed out in Section 1.4. The following subquestions are also addressed. Related to the first research question, the following subquestions are defined:

- 1. Which software, hardware and performance requirements are important?

- 2. How can the control system be made in such a way that it is easily adaptable to future needs, and such that it will be a flexible system?

Related to the second research question, the following subquestions are defined:

- 1. How to develop a prototype for the controller?

- 2. To what extent is it possible to evaluate the design using this prototype?

- 3. How could the system be used in an airplane once installed?

### 1.4 Thesis organization

This chapter provided an introduction to the project, its technology, related work, and the organisation of this research. The rest of this thesis is presented as follows. In Chapter 2, the context of the antenna controller is discussed. In Chapter 3, the design of the control system is presented. In Chapter 4, the implementation of this design is discussed. In Chapter 5, measurement results are presented. Finally, in Chapter 6, conclusions and answers to the research questions are given. Also suggestions for further research are mentioned.

## Chapter 2

## Context

What if there is a working, fully operational PAA receive system available in an airplane, as described in the previous Chapter? What could one do with the composition of the antenna front-end, modulation, beamformer, detection and controller subsystems?

This Chapter is about the context for which this system is developed, or -said differently- its possible applications. These main applications are the services of live television, in case of only unidirectional communication (reception on the airplane only), and internet access, in case of bidirectional communication. Of course the latter one relies on a more complicated system - but we will see this later on. It is not the purpose of this Chapter to be complete - the implementation of these services is worth a study and some full time employees by itself. However this Chapter tries to provide a little more insight in the details of these services and their dependabilities.

The Chapter starts with explaining the OSI model in Section 2.1, and giving a relation between the SMART project and this reference model to show what steps still need to be taken. In Section 2.2, a motivation for the television and internet services is given. Then, Section 2.3 discusses two possibilities for a system design employing a PAA with beamforming. Both designs (again, one for a unidirectional scenario and one for a bidirectional scenario) are elaborated. Section 2.4 describes what infrastructure is needed. Consequently, operational, hardware, network and software consequences are mentioned in Section 2.5. The Chapter ends with a discussion and a conclusion in Section 2.6 and 2.7, respectively.

## 2.1 OSI Reference model

The OSI Reference Model (Open System Interconnection Basic Reference Model) is a standard reference model defined by the International Standards Organization ISO. It is very useful when making decompositions of network infrastructures. It consist of seven layers, shown in Table 2.1.

| OSI Model    |

|--------------|

| Application  |

| Presentation |

| Session      |

| Transport    |

| Network      |

| Data Link    |

| Physical     |

Table 2.1: The OSI Reference Model

Discussing these layers is useful in this context, because the context of the control system is the subject here. The network is part of that context. Therefore each layer is described below:

- Application layer. This layer provides the interface to front-end application processes. Example: the HTTP protocol for internet browsing applications.

- *Presentation layer.* Provides the representation and eventually encryption of the data. Example: a service that makes a XML representation of application data.

- Session layer. Manages and administers a session between peers. Example: secure sockets.

- *Transport layer.* Provides the transport of messages between peers. Example: The Transport Control Protocol (TCP) protocol.

- *Network layer.* Provides the routing of datagrams. Example: The Internet Protocol (IP) protocol.

- Data link layer. This layer provides both the Logical Link Control (LLC) and the Medium Access Control (MAC), together providing data transfer in a network, using an interface such as LAN, Wireless LAN or Bluetooth.

- *Physical layer*. This layer defines the means of transmitting raw bits onto the hardware transmission medium, such as a cable or a radio frequency.

Though current network initiatives are not always bound to just one of these layers, it is very interesting to show this model here. We use it to point out developments that still have to be done to provide a fully operational system in an airplane (as meant in the introduction of this Chapter).

At this moment, work has been done to provide a part of the physical layer interface by means of an antenna array with optical beamforming. The physical layer has partly been provided by means of modulating signals onto this interface, and demodulation after the optical components. However, there is no MAC and LLC at this moment. This Chapter points out that the development of that will not be a trivial task. Next to this, also higher layer developments should be conducted in order to provide for example internet applications onto this system. For television this is a lot easier, since there is no bidirectional communication, and a medium access function is not needed.

### 2.2 Motivation

Until now, live television or internet access on airplanes is only very sparsely available. Market research however shows that customers are attracted to these forms of time spending when flying [13]. Especially on long (for example transatlantic) flights this is of interest to a large audience. Also when still docked, people appreciate this kind of services. Next to this, crew and cabin personnel, but especially maintenance personnel, rely on access to distant information for which bidirectional internet access would be very useful. The airline could communicate flight data, electronic techlogs, aircraft documentation, navigational data and more in this way. So both the customer (either as consumer or as businessman) and the provider of the transport service would benefit from live television and internet access.

### 2.3 Designs

In this Section two possible system designs are presented: a downlink-only design, with unidirectional communication towards an airplane, and a bidirectional link, with bidirectional communication between an airplane and a ground station.

#### 2.3.1 A design employing a unidirectional satellite link

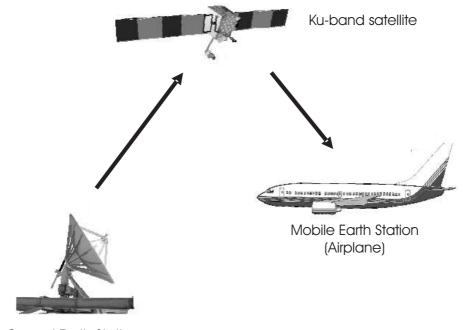

In the context of the FlySmart project a unidirectional communication link from a geostationary satellite to a Mobile Earth Station (MES) is addressed, the MES being an airplane. One of the intended and appealing applications is the live provisioning of television via satellite using Digital Video Broadcasting - Satellite (DVB-S). The architecture of this system is shown in Figure 2.1. A Ground Earth Station (GES) center transmits the DVB-S signal to the satellite, where it is received, amplified and transmitted to decoders such as set-top boxes. The MES is one of these receivers. Its set-top boxes decode the signal and provide the passengers with the channel of their choice, as well as auxiliary information such as an Electronic Programming Guide (EPG). This can be displayed on the in-flight entertainment systems that most long-haul aircraft nowadays have. Partly, it will also replace the back-end components such as file servers of the entertainment systems, because the data can now be streamed to the airplane instead of (costly) storing it in the plane.

Ground Earth Station

Figure 2.1: Unidirectional communication architecture.

#### 2.3.2 A design employing a bidirectional satellite link

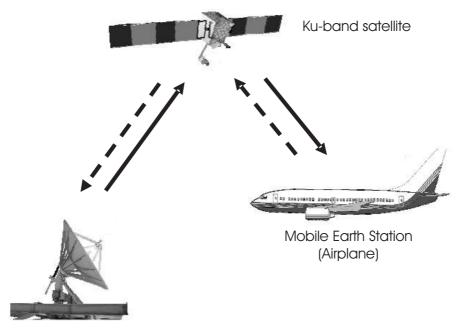

When a bi-directional link is employed, the above sketched service of live television is still possible, but also duplex communication is now available. Hence internet, phone calls, crew services and interactive television may be provided. In this idea two separate system designs can be identified: a synchronous connection using the same frequency band for uplink and downlink, and a asynchronous connection, using different frequency bands via possibly different satellites. These two designs are presented in Figure 2.2 and Figure 2.3.

In Figure 2.2, the scenario is sketched in which the transmission of data (from MES to GES) is achieved via the same link as the reverse link, using the geostationary satellite's Ku-band. However internet traffic is typically asynchronous (the downlink is used more than the uplink). Also the complexity of sharing a single transponder amongst many MESs needs to be regarded. A multiplexing technique must be offered when multiple MESs get data via the same transponder on the satellite. This channel accessing can be achieved using time multiplexing using Time Division Multiple Access (TDMA), code multiplexing as in CBB using Code Division Multiple Access (CDMA) or frequency multiplexing using Frequency Division Multiple Access (FDMA), eventually combined with frequency spreading techniques such as Frequency Hopping Spread Spectrum (FHSS) or Direct Sequence Spread Spectrum (DSSS). However when also the link from the MES to GES is built using a transponder on the same satellite, an increased coordination is needed to address portions of that link to the different MESs.

Ground Earth Station

**Figure 2.2:** Bidirectional communication architecture with broadband uplink via Ku-band satellite.

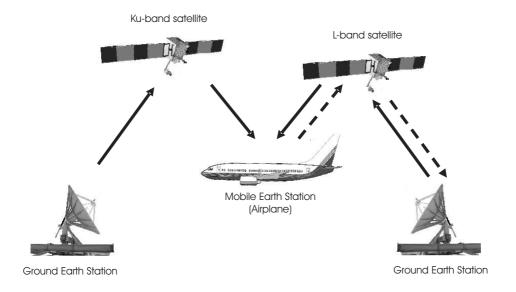

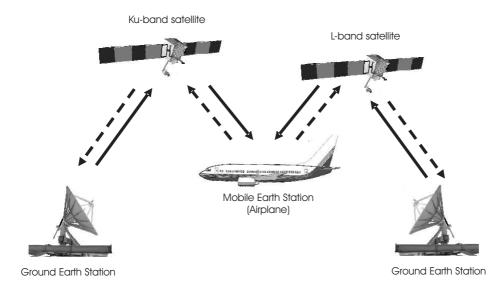

Therefore a system is proposed in which the MES-GES link is a smaller-bandwidth, individual link from each MES to a GES, without sharing. This link is established using an L-band connection for which a number of antennas is already available, as well as ongoing research related to the integration of Ku- and L-band antennas [14]. The proposed system is shown in Figure 2.3. Another advantage of this system is that transceive functionality for L-band is already common and available for airplanes, whereas for Ku-band it is not. So not to end up with double bidirectional connections as shown in Figure 2.4, for both Ku-band and L-band, the system as described in Figure 2.3 is in favor.

### 2.4 Infrastructure

This section discusses the in-plane and supporting infrastructure needed for both system designs. First of all, the RF signals should be received by the MES, preferable using a conformal PAA mounted on the fuselage skin on the aircraft. Its signals are downconverted, amplified and processed as discussed in Subsection 1.2.2. The received signal is then sent to a series of set-top boxes for reception of DVB-S or Digital Video Broadcasting - Satellite 2 (DVB-S2) [15, 16]. It may also be processed by a router in case of just internet (IP) data. The DVB-S2 protocol stack can be used as it is capable of both television and IP data. The return channel for internet and interac-

Figure 2.3: Bidirectional communication architecture with uplink via L-band only.

Figure 2.4: Bidirectional communication architecture with uplink via Ku-band and L-band.

tive television can be provided using Digital Video Broadcasting - Return Channel via Satellite (DVB-RCS). However an adaption needs to be made with regard to the standard solution, in case a different satellite transponder is used for the communication from the airplane to the ground. This is not a problem in the sense that DVB-RCS is designed to be frequency and frequency band independent [17]. Also, crew services and maintenance data should be separated from eventual communication with the television operator, which is generally the only practice with DVB-S2 and DVB-RCS. Therefore, the Satellite Operator as discussed in the next Section, should be a trustable party taking care of the separation of these streams. The advantage however of integration of television and IP services into DVB-S2, is that it makes the complete system (which is already quite complex) a little less complex, and already more equipment is available which is capable of the necessary functions.

## 2.5 Consequences

Some of the consequences of bringing such kinds of infrastructures to airplanes, are worth mentioning. Firstly we look at some practical aspects, then at hardware aspects, then at some software aspects.

#### 2.5.1 Operational issues

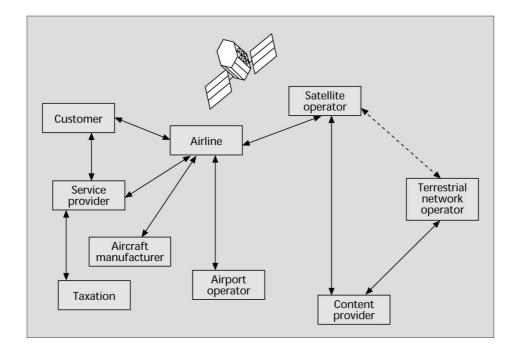

Considering the practical issues, it is sure that the systems sketched above involve multiple parties and multiple desires, rules, targets and working procedures. This will make installing and maintaining such systems quite a complex task. To give an overview of the participants, Figure 2.5 lists all the stakeholders and their relations. The customers, paying to both the Airline (tickets) and the Service provider making the wireless services possible are the main participants. The latter one may be a subsidiary of the airline. It has ties with Taxation entities for billing and administration purposes. The Airport operator is mentioned since it also is in this business, albeit at the airport. Together with the Airline it may provide combined services. The Aircraft manufacturer may include and advertise for wireless services in its planes, and operate them (such as in the CBB subsidiary). The Satellite operator operates the link between the MES and the ground, where it is connected to one or more Content providers to supply content to show in the plane, and to gateways of various Terrestrial networks.

Next to this, airline maintenance processes can now be improved, because maintenance data can now be gathered and communicated via the internet link of the aircraft, and maintenance personnel can update their findings using this connection, reducing administration, paperwork and grounding time of aircraft for maintenance.

#### 2.5.2 Hardware issues

Installing electronical equipment in aircraft is bound to strict regulations, in Europe issued by EASA. Because of this, and because of practical issues, it is recommended to conduct the installment of the hardware in cooperation with, or outsourced to, suppliers of in-flight entertainment systems.

Regarding the test procedures that have to be fulfilled before the equipment can be certified, RTCA/DO-160E provides a set of regulations with respect to requirements on the products and precise procedures for testing these requirements [10]. The hardware for such systems shall be tested before it can be said certifiable, the complete certification is conducted on an aircraft as-a-whole. When properly designed, the complete system would not have very big issues in such kind of tests, however some problems

Figure 2.5: Stakeholders in a possible value chain for provisioning of wireless in-plane services (taken from [13]).

that arose in the design of the controller, such as EMI, show that still the requirements for these tests need to be considered along the development process.

Another issue regarding the antennas is the following. Typically, transatlantic flights for which the abovementioned services are interesting, are carried out at a high latitude. The geostationary satellite to point at for television service, is above the equator, so very south. Hence in order to have a large effective aperture, the PAA needs to be very large, (from the left side from the airplane all the way to the right side seen from the fuselage) or two antennas must be placed. Another quite unlikely mechanical rotation mechanism could also be placed (but this is not recommended due to is small mean time between failures). The most feasible option is placing two antennas, but still this increases the complexity of the system and the costs.

#### 2.5.3 Software issues

As for hardware, also for software in aircraft there are regulations. RTCA DO 178 states classifications and requirements with different levels of severeness based on the importance of the software, and danger once shut down. Also here, it would not be an impossible goal to have the software running on the controller (and the tracking mechanism needed for tracking the right satellite) certified, but there need to be taken more steps to reach this level. For example, the software itself must be checked on completeness, code coverage, thread safety and correctness. But also the compiler and eventually other tools used when developing the code must be certified. In order for the

compete system, still functions for tracking satellite, angle calculation and amplitude tapering functions have to be added to the control system before a certification must be started.

#### 2.5.4 Network issues

When communicating via satellites, one mentions longer delays than using landlines, because of the extra distance travelled by the data. For satellite television this is not too much of a problem, but for internet access this is certainly the case. The performance is affected by large and changing delays, occasionally varying error rates, band and path asymmetries and large round trip times. This affects both the Transport Control Protocol (TCP) and User Datagram Protocol (UDP). These problems are well described in [17] (Section 2.5.3). They are a reason for various enhancements proposed by the Internet Engineering Task Force (IETF) working group TCP over Satellite. Amongst them is the implementation of larger TCP windows (needed for more underway data), acknowledgement of only correctly received TCP packets (Selective Acknowledgement (SACK)) instead of cumulative acknowledgements, and proxying of data.

### 2.6 Discussion

A big issue when discussing such kind of systems is the feasibility of the systems discussed here. Already the CBB service was discontinued because at that time the market did not develop as expected. Not only were there very large development costs involved, also the number of paying customers did not cover enough costs. This makes it questionable whether or not such services will be viable. This will mainly have to do with installing costs, maintenance and contracts with satellite operators. A difference in this regard compared to roughly 10 to 5 years ago, is that more and more people are willing to pay to have mobile internet access, as can be seen for example with mobile data subscriptions using Universal Mobile Telecommunications System (UMTS) technology. A drawback is that such kind of systems are rather complex and it will take some more development exercises to make the system robust.

Starting in 2008, airlines were beginning to include piconets in their aircraft, to provides cellular connectivity aboard. Such services can in future be integrated with internet connectivity and crew communication services aboard.

## 2.7 Summary

The motivation for airborne connectivity was given and different designs for communication between an airborne MES and a GES were presented. The discussion was based on the OSI Reference Model, which was introduced in Section 2.1. Both unidirectional designs and bidirectional designs for different purposes were introduced in Section 2.3. Their advantages and disadvantages were discussed. Some of the consequences of these infrastructures were given in Section 2.4. Issues regarding the stakeholders and their relations, the hardware, the software and the network were given in Section 2.5. Finally, the feasibility was discussed in Section 2.6.

# Chapter 3

# **Design of the Control System**

The OBFN should be controlled thermo-optically, by means of a control system. This chapter presents the design of the control system, consisting of a controller and an interface for the controller, which is running on a PC. Firstly, the requirements have to be clear; they are presented in Section 3.1. As illustrative examples for the desired functionalities, some use cases are elaborated afterwards in Section 3.2. In Section 3.3 the design itself is given, consisting of a hardware and a software design. In Section 3.4 a summary is presented.

# 3.1 Requirements analysis

In this section the requirements for the OBFN control subsystem are presented. Software, hardware, and performance requirements are identified. For each of them, the requirements are mentioned and explained.

### 3.1.1 Hardware requirements

- 1. The hardware used should have low costs, using commercial of the shelf (COTS) components where possible, and should be fast enough to execute tasks, such as the calculation of voltages for the tuning of the optical chip, with delays in the maximal order of milliseconds.

- 2. The hardware should be able to provide the operator of the system with information, by means of a screen and status Light Emitting Diodes (LEDs).

- 3. The hardware should be easily connectible using standard plugs and cables.

- 4. The hardware should be designed in a modular way, so that it is easy to add parts as other parts of the total system grow, for example if the OBFN expands with more tunable elements.

- 5. A storage place is needed to store information about the optical chip such as offsets, number of heaters, and voltages corresponding to different tuning settings.

This storage should be fast, random accessible, rewritable and large enough for current OBFNs, and also for OBFNs of near future.

- 6. The hardware should be accessible using a PC but also able to operate independently.

- 7. In a final stadium, the hardware should conform to avionics requirements listed in DO 160/E and other relevant requirements for aviation systems.

- 8. In a final stadium, the complete system should be compact, packaged in a small sized box.

### 3.1.2 Software requirements

Next to being able to handle the use cases presented in the next Section, the control system should be able of the following software requirements:

- 1. The software running on the control system should make it possible to tune the OBFN, given a set of  $\kappa s$  and  $\phi s$ , (for the tunable elements described in Subsection 1.2.1) or voltages corresponding to these  $\kappa s$  and  $\phi s$ .

- 2. The software should be able to communicate fast enough with the hardware parts involved in tuning, according to the performance requirements stated below.

- 3. The software should be able to present operational information on what it is doing to the user.

- 4. The software should be easily upgradeable.

- 5. Debugging and logging data produced by the software, must be stored if needed.

- 6. The software should include drivers necessary to communicate with the storage device or devices it communicates with.

- 7. In a final stadium, the software should conform to avionics software requirement listed in RTCA DO 178B.

### 3.1.3 Performance requirements

Below, the most important performance requirements are addressed.

- 1. The system should be able to perform tuning within 1 ms, as this is the maximum speed of the heaters.

- 2. The system should boot reasonably fast, within 60 seconds.

- 3. The accuracy of tuning should be within 1 mV to be able to tune precisely enough. Voltages applied on the optical chip should match inputted values on the microcontroller.

- 4. The applied voltages should be stable and not oscillate.

# 3.2 Use cases

The system may be used as follows, although usage is not limited to the use cases presented below. They are presented as illustrative examples. The use cases below are given as from a user perspective. Note that the user may either be, initially, a human being, but in a later stadium, the user should be a software process.

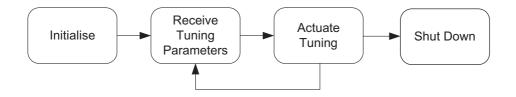

#### Use case 1. Initialization, tuning and shutting down

- 1. Initialization. After turning the system on, the user may verify that the system starts. He may also see the number of tunable channels.

- 2. Setting values. After initialisation, the user may set values for the individual heaters.

- 3. Recall values. After initialisation, the user may set values for the heaters stored from memory.

- 4. Shutting down. After initialization, the user may shut down the system. The user may verify that the system exits properly.

### Use case 2. Calculation

- 1. Initialization. See use case 1.

- 2. Setting phase values. After initialisation, the user may set desired phases for a given number of rings. The system then calculates the corresponding voltages and the user may verify that the system tunes the OBFN accordingly.

- 3. Shutting down. See use case 1.

### Use case 3. Calibration

- 1. Initialization. See use case 1.

- 2. In order to make use case 2 possible, crosstalk parameters should be put in the system. The user may store these parameters in the controller.

- 3. Shutting down. See use case 1.

#### Use case 4. Loading and saving

- 1. Initialization. See use case 1.

- 2. Loading. The user may recall a set of values that form a setting for tuning of the OBFN.

- 3. Saving. The user may save a similar set of values. The last settings are automatically saved.

- 4. Shutting down. See use case 1.

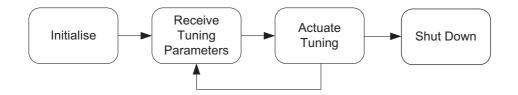

# 3.3 Design