## Western University Scholarship@Western

**Digitized Theses**

**Digitized Special Collections**

2008

## A Software Architecture for Adaptive Modular Sensing Systems

Andrew C. Lyle Western University

Follow this and additional works at: https://ir.lib.uwo.ca/digitizedtheses

#### **Recommended Citation**

Lyle, Andrew C., "A Software Architecture for Adaptive Modular Sensing Systems" (2008). *Digitized Theses*. 4087. https://ir.lib.uwo.ca/digitizedtheses/4087

This Thesis is brought to you for free and open access by the Digitized Special Collections at Scholarship@Western. It has been accepted for inclusion in Digitized Theses by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

## A SOFTWARE ARCHITECTURE FOR ADAPTIVE MODULAR SENSING SYSTEMS

(Thesis format: Monograph)

by

#### Andrew C. Lyle

#### Graduate Program in Engineering Science Department of Mechanical and Materials Engineering

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Engineering Science

The School of Graduate and Postdoctoral Studies The University of Western Ontario London, Ontario, Canada

© Andrew C. Lyle 2008

## Abstract

In this thesis, a novel software architecture and knowledge representation scheme is described that facilitates the combination and reconfiguration of modular sensor and actuator components, termed *transducer interface modules* (TIMs), to produce flexible modular sensor systems. Each TIM provides a core sensing or actuation functionality. A composite sensor is able to automatically determine its overall geometry and assume an appropriate collective identity, and if reconfigured, may then assume a different identity to match its new geometry. In current practice, a fixed combination of sensors and actuators is typically utilized, and is tailored to a specific application. Such systems cannot be cheaply or quickly reconfigured to handle a change in process requirements. Domains that may benefit from easily reconfigurable modular sensing systems include flexible inspection, mobile robotics, surveillance, and even space exploration.

The software architecture is distributed, and is comprised of six layers where the implementation of each layer is encapsulated from the layer above, to which it provides service. The use of a distributed and layered architecture promotes scalability, mitigates against a single point of failure, and enables each layer to be easily implemented, modified, and debugged independently of the others. The modularization of the software architecture is further facilitated through the utilization of a pre-emptive real-time operating system, which enables the concurrent execution of the various software components specific to the architecture that implement the services provided within most of its layers. Among the layers comprising the software architecture is a virtual machine layer, which implements a lightweight, architecture-specific version of Sun Microsystems' Java Virtual Machine that runs on top of the real-time operating system. The integration of a virtual machine enables the platform-independent *template algorithms* utilized at the *composition layer* to be written once and executed on any TIM irrespective of its underlying hardware architecture. These template algorithms are unique to this software architecture and provide intelligence to a set of heterogeneous TIMs, enabling them to collaborate and behave as a single entity termed a *logical module*.

The evaluation of the software architecture consists of performing multiple runs of two tests in which select sensors and actuators are associated with TIMs that are then allowed to interact in order to form a logical entity. The first test evaluates the behaviour of a logical module in which the constituent TIMs interact entirely through wireless communication. The second test evaluates the behaviour of a logical module in which the constituent TIMs are physically connected in various orientations, and interact through both wireless communication as well as through their physically connected faces.

In both tests, correct behaviour was exhibited. However, the performance and scalability of the architecture was somewhat restricted by the limited processing and memory resources present in the current implementation of the TIMs. The design of the software architecture facilitates easy portability between embedded platforms and scales with increasing hardware capability. Therefore, utilization of future TIM hardware variations possessing increased processing and memory resources will reduce the latencies introduced throughout the architecture and lead to tangible improvements in its performance.

**Keywords:** distributed software architecture, adaptive sensing system, modular sensing system, sensor module, actuator module, transducer module, logical module, position and orientation determination, virtual machine.

## Acknowledgements

Many individuals have played a guiding and supporting role in the completion of this thesis, whom I would like to thank. Firstly, I would like to thank my supervisor, Dr. Michael D. Naish, for his expert guidance and patience, and for providing me with the opportunity to pursue graduate studies at The University of Western Ontario. This research programme has been an immense learning experience for me, and from him I have learned a great deal about the engineering process that I will be able to apply in my future endeavours.

I would like to thank my fellow Sensing and Mechatronics Systems (SaMS) Laboratory researchers Anita Jain, who coordinated with me on this project, for all her hard work and Christopher Ward for his insightful input. I am also grateful to the engineers in the Electrical and Computer Engineering Electronics Shop for their assistance in sourcing components, as well as their useful technical advice.

I am very grateful to Marie Wyatt, who played a key role in ensuring that my stay in London was a comfortable one. I am also grateful to my friends and family who maintained an active interest in my progress, especially to my parents for their steadfast support and financial assistance, and for always encouraging me to pursue my ambitions. I am also thankful to God for blessing me throughout my programme.

The financial support of the Natural Sciences and Engineering Research Council of Canada (NSERC) is also gratefully acknowledged.

# Contents

| $\mathbf{C}$ | ertifi         | cate of | Examination                           | ii           |  |  |

|--------------|----------------|---------|---------------------------------------|--------------|--|--|

| A            | bstra          | ct      |                                       | iii          |  |  |

| A            | cknov          | wledge  | ements                                | $\mathbf{v}$ |  |  |

| Ta           | able (         | of Con  | tents                                 | vi           |  |  |

| Li           | st of          | Figur   | es                                    | xii          |  |  |

| Li           | List of Tables |         |                                       |              |  |  |

| Li           | st of          | Algor   | ithms                                 | xv           |  |  |

| 1            | Intr           | oduct   | ion                                   | 1            |  |  |

|              | 1.1            | Sensor  | rs and Actuators in Industry          | 1            |  |  |

|              | 1.2            | The N   | leed to Combine Sensors and Actuators | 2            |  |  |

|              | 1.3            | Surve   | y of Related Work                     | 3            |  |  |

|              |                | 1.3.1   | Logical Sensor Architectures          | 3            |  |  |

|              |                | 1.3.2   | The IEEE 1451 Standards               | 6            |  |  |

|              |                | 1.3.3   | Existing Modular Sensing Systems      | 9            |  |  |

|              | 1.4            | Resea   | rch Objective                         | 14           |  |  |

|          | 1.5                    | Thesis Outline                           | 15 |  |  |  |  |  |  |

|----------|------------------------|------------------------------------------|----|--|--|--|--|--|--|

| <b>2</b> | Arc                    | Architecture Description 18              |    |  |  |  |  |  |  |

|          | 2.1                    | Introduction                             |    |  |  |  |  |  |  |

|          | 2.2                    | 2 Module Hardware Overview               |    |  |  |  |  |  |  |

|          |                        | 2.2.1 Transducer Interface Modules       |    |  |  |  |  |  |  |

|          |                        | 2.2.2 Other Module Types                 | 19 |  |  |  |  |  |  |

|          | 2.3                    | Software Architecture Stack              |    |  |  |  |  |  |  |

|          | 2.4                    | Real-Time Operating System               |    |  |  |  |  |  |  |

|          |                        | 2.4.1 Scheduling Policies                |    |  |  |  |  |  |  |

|          |                        | 2.4.2 Choice of RTOS                     |    |  |  |  |  |  |  |

|          |                        | 2.4.3 Task Types                         |    |  |  |  |  |  |  |

|          | 2.5                    | File System                              |    |  |  |  |  |  |  |

|          |                        | 2.5.1 Choice of FAT32 File System Driver |    |  |  |  |  |  |  |

|          |                        | 2.5.2 Standard File Structure            |    |  |  |  |  |  |  |

|          | 2.6                    | TEDS Specification Format                | 31 |  |  |  |  |  |  |

|          | 2.7                    | Core Data Types                          |    |  |  |  |  |  |  |

|          |                        | 2.7.1 Vector Implementation              | 33 |  |  |  |  |  |  |

|          |                        | 2.7.2 Task Data Types                    |    |  |  |  |  |  |  |

|          |                        | 2.7.3 Module Data Types                  |    |  |  |  |  |  |  |

|          | 2.8                    | Summary                                  |    |  |  |  |  |  |  |

| 3        | Communication Layer 40 |                                          |    |  |  |  |  |  |  |

|          | 3.1                    | Introduction                             | 40 |  |  |  |  |  |  |

|          | 3.2                    | Communication Layer Services             | 41 |  |  |  |  |  |  |

|          |                        | 3.2.1 Logical Link Control               | 41 |  |  |  |  |  |  |

|          |                        | 3.2.2 Medium Access Control              |    |  |  |  |  |  |  |

|   |     | 3.2.3   | Time Synchronization              | 46 |

|---|-----|---------|-----------------------------------|----|

|   |     | 3.2.4   | Wireless Security                 | 47 |

|   | 3.3 | Packet  | t Format                          | 51 |

|   | 3.4 | Chann   | els and Packet Types              | 53 |

|   |     | 3.4.1   | Control Channel Packet Types      | 54 |

|   |     | 3.4.2   | Data Channel Packet Types         | 55 |

|   | 3.5 | Initial | ization                           | 55 |

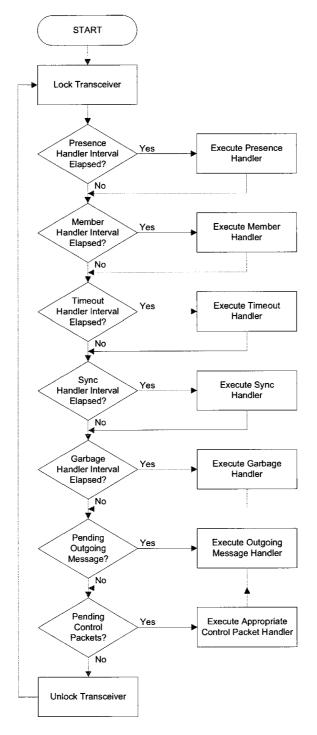

|   | 3.6 | Netwo   | rk Communication Task             | 56 |

|   |     | 3.6.1   | Standard Handlers                 | 57 |

|   |     | 3.6.2   | Control Packet Handlers           | 62 |

|   | 3.7 | Face C  | Connectivity                      | 65 |

|   |     | 3.7.1   | Face Structure                    | 65 |

|   |     | 3.7.2   | Face Identification Packet Format | 67 |

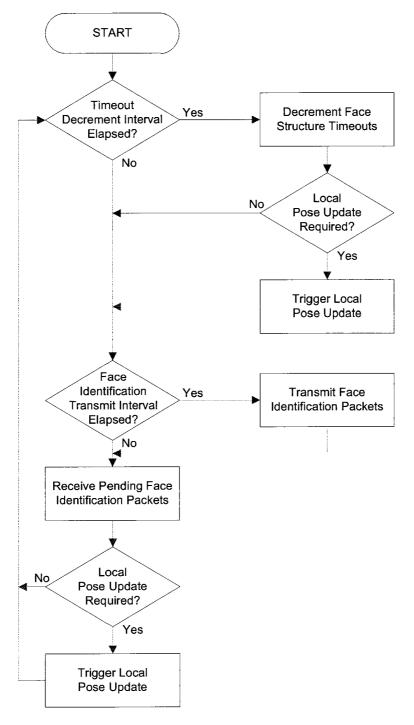

|   |     | 3.7.3   | Face Communication Task           | 69 |

|   | 3.8 | Summ    | ary                               | 73 |

| 4 | Mid | ldlewa  | re Layer                          | 74 |

|   | 4.1 | Introd  | uction                            | 74 |

|   | 4.2 | Middle  | eware Types                       | 74 |

|   | 4.3 | Messa   | ge Format                         | 77 |

|   | 4.4 | Servic  | e Functions and Service Calls     | 80 |

|   |     | 4.4.1   | Service Function Types            | 82 |

|   | 4.5 | Modul   | le Message Handler Task           | 84 |

|   |     | 4.5.1   | Message Acquisition               | 87 |

|   |     | 4.5.2   | Standard Status Checks            | 90 |

|   | 4.6 | Summ    | ary                               | 91 |

| 5   | Vir | tual Machine                                    | 93  |

|-----|-----|-------------------------------------------------|-----|

|     | 5.1 | Introduction                                    | 93  |

|     |     | 5.1.1 Choice of Dynamic Reprogramming Mechanism | 93  |

|     | 5.2 | Class Loading                                   | 98  |

|     | 5.3 | Class Execution                                 | 99  |

|     | 5.4 | Standard Class Library                          | 103 |

|     |     | 5.4.1 The java.lang Package                     | 103 |

|     |     | 5.4.2 The amss.system Package                   | 104 |

|     | 5.5 | Summary                                         | 106 |

| . 6 | Cor | nposition Layer                                 | 108 |

|     | 6.1 | Introduction                                    | 108 |

|     | 6.2 | Template Data Types                             | 109 |

|     |     | 6.2.1 Template Structure                        | 109 |

|     |     | 6.2.2 Role Structure                            | 110 |

|     |     | 6.2.3 Local and Remote Join Structures          | 112 |

|     |     | 6.2.4 Pose Update Structure                     | 113 |

|     | 6.3 | Template and Role Matching                      | 115 |

|     |     | 6.3.1 Matching Existing Logical Modules         | 115 |

|     |     | 6.3.2 Creating New Logical Modules              | 118 |

|     | 6.4 | Transducer Composition                          | 122 |

|     |     | 6.4.1 Logical Module General Operation          | 122 |

|     |     | 6.4.2 Logical Module Primary Handler Operation  | 122 |

|     | 6.5 | Pose Composition                                | 125 |

|     |     | 6.5.1 Pose Representation and Theory            | 125 |

|     |     | 6.5.2 Pose Composition Process                  | 128 |

|     | 6.6 | Summary                                         | 132 |

|     |     |                                                 |     |

## ix

| 7  | Arc           | hitectu | re Evaluation                                                                                              | 134         |  |  |  |  |  |

|----|---------------|---------|------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|

|    | 7.1           | Introd  | uction                                                                                                     | 134         |  |  |  |  |  |

|    | 7.2           | Wirele  | ess Collaboration Behaviour $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 135         |  |  |  |  |  |

|    |               | 7.2.1   | Evaluation Setup                                                                                           | 135         |  |  |  |  |  |

|    |               | 7.2.2   | Evaluation Procedure                                                                                       | 137         |  |  |  |  |  |

|    |               | 7.2.3   | Results and Analysis                                                                                       | 138         |  |  |  |  |  |

|    | 7.3           | Physic  | eal Collaboration Behaviour                                                                                | 142         |  |  |  |  |  |

|    |               | 7.3.1   | Evaluation Setup                                                                                           | 142         |  |  |  |  |  |

|    |               | 7.3.2   | Evaluation Procedure                                                                                       | 143         |  |  |  |  |  |

|    |               | 7.3.3   | Results and Analysis                                                                                       | 145         |  |  |  |  |  |

|    | 7.4           | Collab  | poration Performance Analysis                                                                              | 152         |  |  |  |  |  |

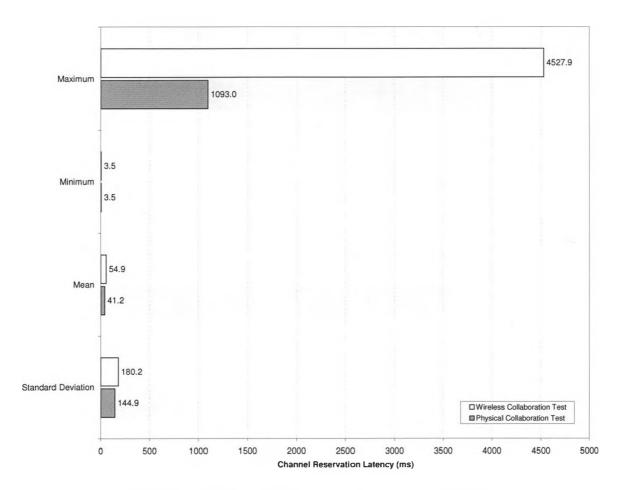

|    |               | 7.4.1   | Channel Reservation Latencies                                                                              | 153         |  |  |  |  |  |

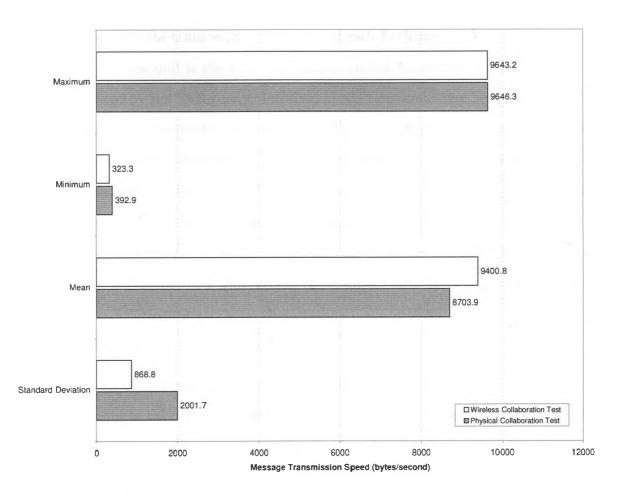

|    |               | 7.4.2   | Message Transmission Speeds                                                                                | 153         |  |  |  |  |  |

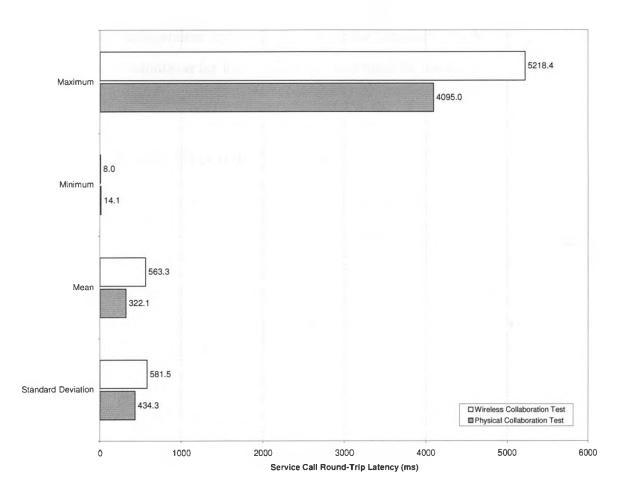

|    |               | 7.4.3   | Service Call Round-Trip Latencies                                                                          | 156         |  |  |  |  |  |

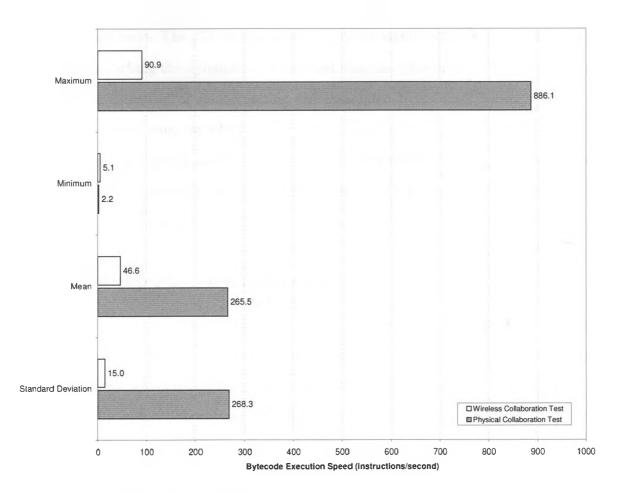

|    |               | 7.4.4   | Bytecode Execution Speeds                                                                                  | 158         |  |  |  |  |  |

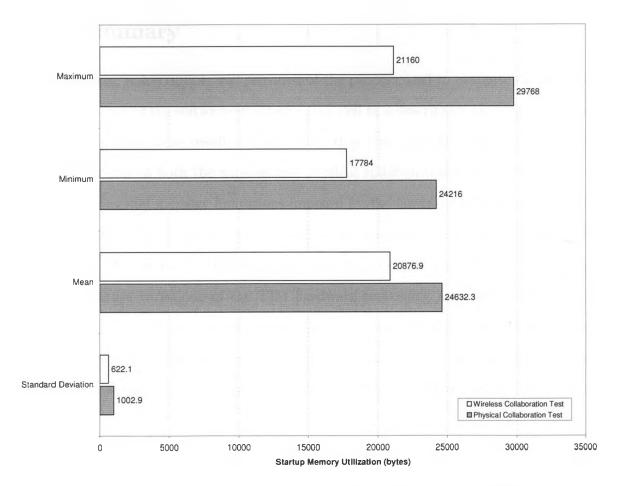

|    |               | 7.4.5   | Startup Memory Utilization                                                                                 | 160         |  |  |  |  |  |

|    | 7.5           | Summ    | ary                                                                                                        | 162         |  |  |  |  |  |

| 8  | Conclusions 1 |         |                                                                                                            |             |  |  |  |  |  |

|    | 8.1           | Conclu  | uding Remarks                                                                                              | 163         |  |  |  |  |  |

|    | 8.2           | Thesis  | Summary                                                                                                    | 165         |  |  |  |  |  |

|    | 8.3           | Recon   | nmendations                                                                                                | 167         |  |  |  |  |  |

| Re | efere         | nces    |                                                                                                            | <b>17</b> 1 |  |  |  |  |  |

| Aj | ppen          | dices   |                                                                                                            | 178         |  |  |  |  |  |

| Α | Star       | ndard                                     | Class Library                                                                       | 178                             |

|---|------------|-------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------|

|   | A.1        | Introd                                    | luction                                                                             | 178                             |

|   | A.2        | Packa                                     | ge java.lang                                                                        | 178                             |

|   |            | A.2.1                                     | java.lang.Math                                                                      | 178                             |

|   |            | A.2.2                                     | java.lang.String                                                                    | 180                             |

|   | A.3        | Packa                                     | ge amss.system                                                                      | 181                             |

|   |            | A.3.1                                     | amss.system.AMSS                                                                    | 181                             |

|   |            | A.3.2                                     | amss.system.Message                                                                 | 182                             |

|   |            | A.3.3                                     | amss.system.Module                                                                  | 185                             |

|   |            | A.3.4                                     | amss.system.Pose                                                                    | 186                             |

|   |            | A.3.5                                     | amss.system.Vector3D                                                                | 187                             |

| в | Arc        | hitecti                                   | ure Evaluation Data                                                                 | 189                             |

| Ľ |            |                                           | luction                                                                             | 189                             |

|   | B.1        |                                           |                                                                                     |                                 |

|   | B.2        | Modu                                      | le TEDS                                                                             | 189                             |

|   |            | B.2.1                                     | accel.mod                                                                           | 189                             |

|   |            | B.2.2                                     | $lcd.mod  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 190                             |

|   |            | _                                         |                                                                                     |                                 |

|   |            | B.2.3                                     | ldr.mod                                                                             | 191                             |

|   |            | B.2.3<br>B.2.4                            | ldr.mod                                                                             | 191<br>192                      |

|   | B.3        | B.2.4                                     |                                                                                     |                                 |

|   | B.3        | B.2.4                                     | servo.mod                                                                           | 192                             |

|   | B.3        | B.2.4<br>Templ                            | servo.mod                                                                           | 192<br>193                      |

|   | B.3<br>B.4 | B.2.4<br>Templ<br>B.3.1<br>B.3.2          | servo.mod                                                                           | 192<br>193<br>193               |

|   |            | B.2.4<br>Templ<br>B.3.1<br>B.3.2          | servo.mod                                                                           | 192<br>193<br>193<br>194        |

|   |            | B.2.4<br>Templ<br>B.3.1<br>B.3.2<br>Templ | servo.mod                                                                           | 192<br>193<br>193<br>194<br>196 |

### Curriculum Vitae

-

$\mathbf{204}$

# List of Figures

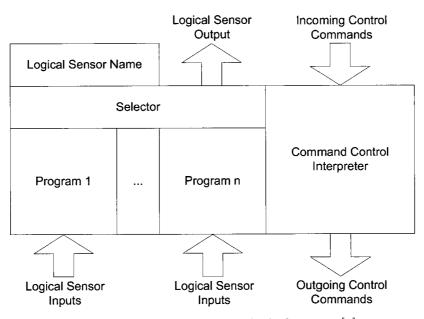

| 1.1  | Logical sensor block diagram.                             | 5  |

|------|-----------------------------------------------------------|----|

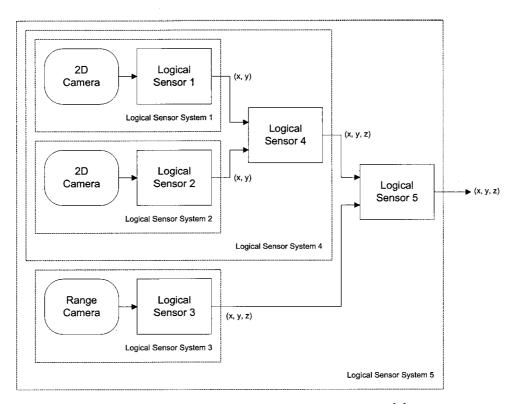

| 1.2  | Sample logical sensor hierarchy.                          | 6  |

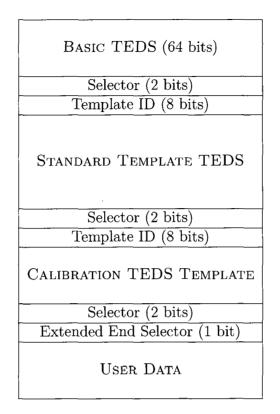

| 1.3  | Sample TEDS layout                                        | 8  |

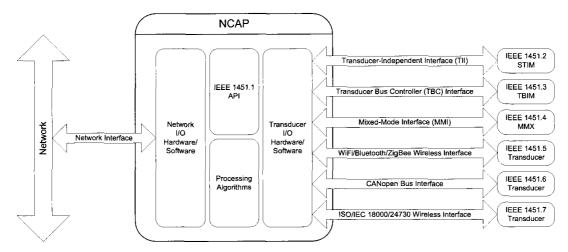

| 1.4  | Application of the IEEE 1451 standards                    | 9  |

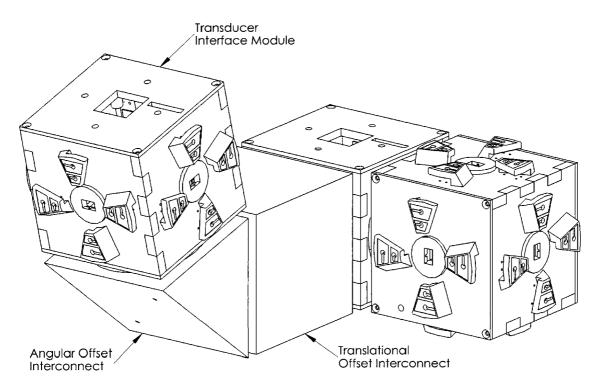

| 2.1  | Transducer Interface Modules and interconnects            | 20 |

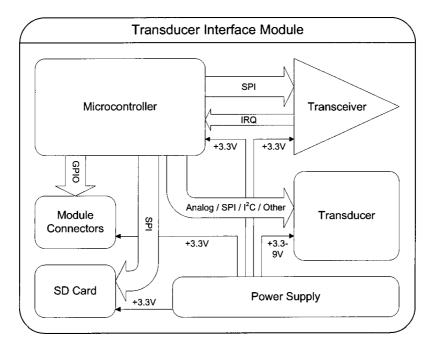

| 2.2  | Transducer Interface Module block diagram.                | 20 |

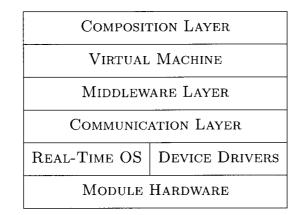

| 2.3  | Software architecture stack.                              | 22 |

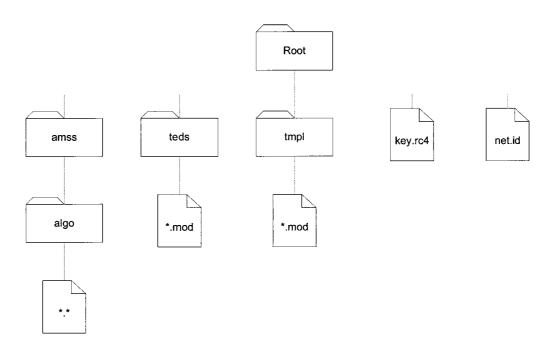

| 2.4  | File system block diagram                                 | 29 |

| 3.1  | Transmission of two packets using an unreliable medium.   | 42 |

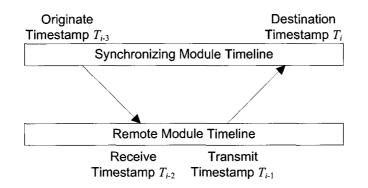

| 3.2  | Time synchronization packet exchange                      | 48 |

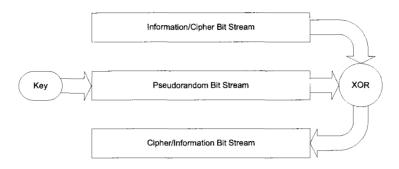

| 3.3  | Stream cipher operation block diagram                     | 49 |

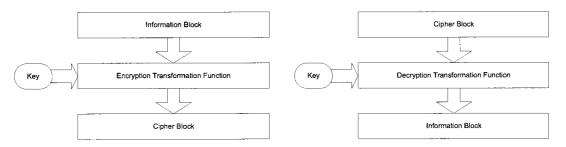

| 3.4  | Block cipher operation block diagram.                     | 50 |

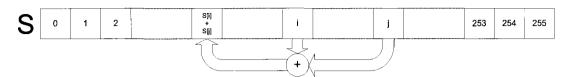

| 3.5  | ARC4 pseudorandom keystream generator operation           | 51 |

| 3.6  | Communication layer packet format (field sizes in bits)   | 52 |

| 3.7  | Multi-channel operation.                                  | 54 |

| 3.8  | Network communication task operation.                     | 58 |

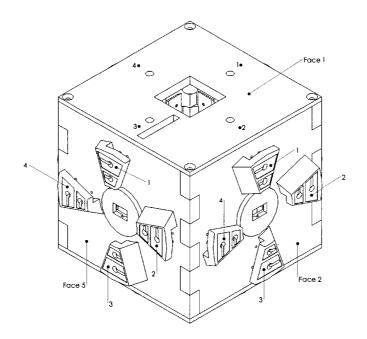

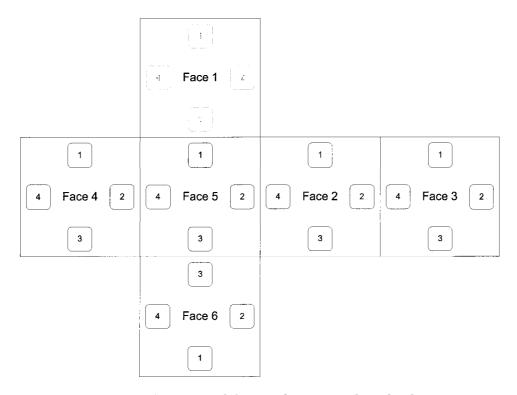

| 3.9  | Three-dimensional face and contact identifier layout view | 66 |

| 3.10 | Two-dimensional face and contact identifier layout view.  | 66 |

| Face identification packet format (field sizes in bytes) | 69                                 |

|----------------------------------------------------------|------------------------------------|

| Face communication task operation.                       | 70                                 |

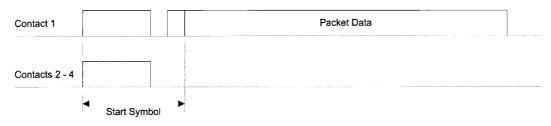

| Face contact transmission signals.                       | 72                                 |

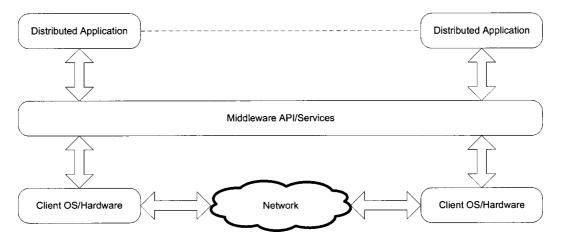

| Middleware operation block diagram.                      | 75                                 |

| Middleware layer message format (field sizes in bytes)   | 78                                 |

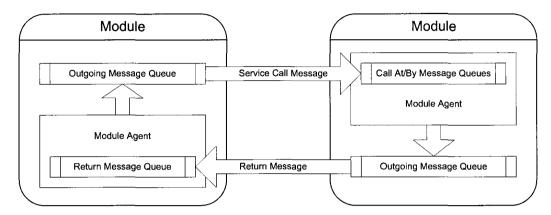

| Service call operation.                                  | 81                                 |

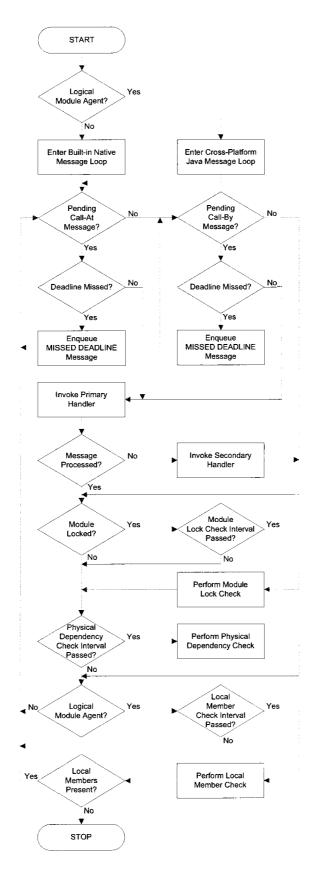

| Module message handler task operation.                   | 86                                 |

| Module pose vectors.                                     | 106                                |

| Logical module operation block diagram.                  | 123                                |

| Standard TIM object coordinate space                     | 127                                |

| Servo TIM positions for given accelerometer TIM angles   | 139                                |

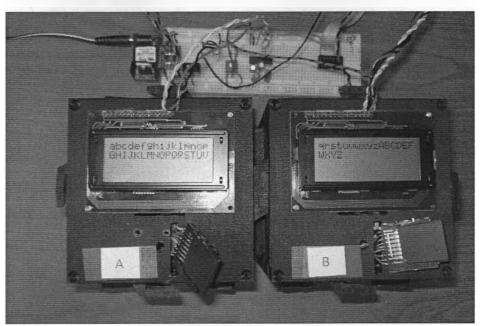

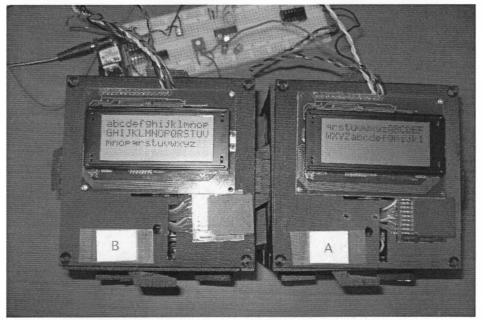

| $32 \times 4$ character composite LCD TIM configurations | 146                                |

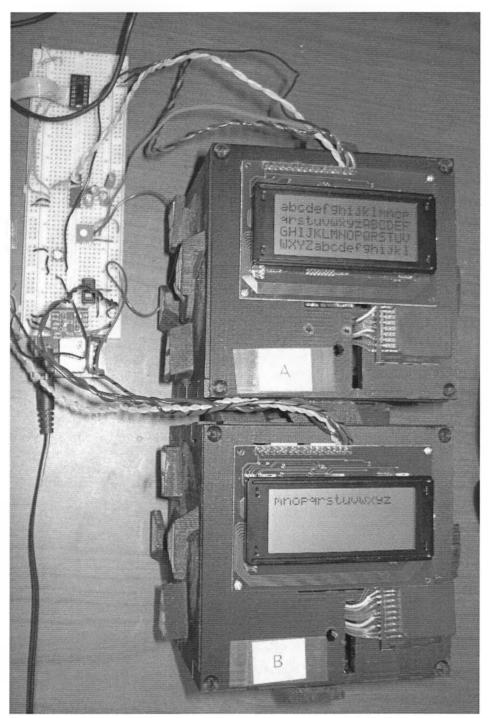

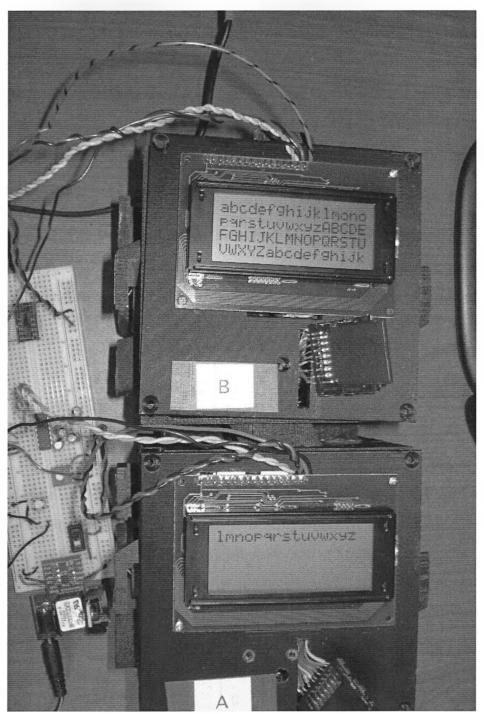

| 16 $\times$ 8 character composite LCD TIM configurations | 147                                |

| MAC protocol channel reservation latencies.              | 154                                |

| PAR protocol message transmission speeds.                | 155                                |

| Service call round-trip latencies.                       | 157                                |

| Virtual machine bytecode execution speeds.               | 159                                |

| Startup memory utilization after logical module creation | 161                                |

|                                                          | Face communication task operation. |

# List of Tables

| 3.1 | Face contact connection patterns and corresponding angular offsets             | 72  |

|-----|--------------------------------------------------------------------------------|-----|

| 4.1 | Service function status constants.                                             | 82  |

| 6.1 | Rotations required to bring $x$ -axis perpendicular to locally connected face. | 130 |

| 6.2 | Rotations about $x$ -axis required to achieve correct relative angular offset. | 131 |

| 6.3 | Rotations required to move locally connected face adjacent to correct re-      |     |

|     | mote face                                                                      | 131 |

# List of Algorithms

| 4.1 | Primary handler execution process.                                  | 88  |

|-----|---------------------------------------------------------------------|-----|

| 4.2 | Secondary handler execution process.                                | 88  |

| 5.1 | Method execution process.                                           | 101 |

| 6.1 | Existing logical module matching process.                           | 116 |

| 6.2 | New logical module matching process                                 | 119 |

| 6.3 | New logical module creation process.                                | 120 |

| 6.4 | Get processing in primary handler for logical module with two roles | 124 |

## Chapter 1

## Introduction

### **1.1** Sensors and Actuators in Industry

Sensors and actuators have seen widespread utilization in many of today's industrial processes. These devices respectively convert physical phenomena to and from electrical signals for the purpose of measurement, tracking, and/or control by way of digital devices such as microcontrollers, programmable logic controllers (PLCs), and mainstream computers. In current practice, fixed combinations of sensors and actuators are typically employed, with each combination often deployed in a static orientation and tailored to fulfil a specific application.

In order to enhance accuracy and reliability in many such applications, multiple sensors are often directly or indirectly combined into composite entities. For example, a single camera is only capable of reporting a grid of values representing the intensity of incident light on its array of sensing elements. However, two or more cameras operating in tandem could, through sensor fusion, effectively form a sensor capable of depth perception. Sensors that detect different, but related, types of physical phenomena may also be combined to produce a new device that produces measurements that are more

#### **1** INTRODUCTION

accurate than either of its constituent sensors are capable of providing. An example of this would be the combination of a thermocouple and an infrared camera for the purpose of increasing the accuracy of sensed temperature.

The sizes of the transistors used in the implementation of microprocessors and other integrated circuits through very large-scale integration (VLSI) are becoming ever smaller, consistent with *Moore's Law* [1], due to advancements in semiconductor fabrication techniques. The sizes of sensors and actuators are also being reduced at an equally rapid rate due to advancements in *microelectromechanical systems* (MEMS) and *nanoelectromechanical systems* (NEMS) fabrication techniques. As a result of these technological advancements, it has become quite practical to combine sensing, actuation, processing logic, as well as transceivers that provide wired and wireless networking capability into a single monolithic device termed a *smart transducer*. With the ability to transmit information and locally execute algorithms independently, without depending upon a larger, static, and more powerful mainstream computer system, the potential for smart transducers to collaborate amongst themselves without any external influence in order to achieve a specific goal becomes worthy of consideration.

### **1.2** The Need to Combine Sensors and Actuators

Sensing systems designed to be operated in a static orientation and under controlled operating conditions cannot be cheaply or quickly reconfigured to handle a change in process requirements, such as in assembly lines where the product being assembled changes completely or is now required to be processed in previously unconsidered orientations. Instead of merely considering each existing sensor as a strictly self-contained device that is to be utilized in an exclusive scenario, or in tandem with others sensors, each sensor may be enhanced through physical combination with one or more actuators in addition to other sensors, resulting in an *active* sensing device.

Combining a sensor with an actuator greatly enhances the ability of the sensor, which is now augmented with mobility and gains the ability to adapt to changing process requirements, such as monitoring non-stationary objects of interest. For example, a camera could be mounted on a rotational stage to form a panoramic camera with a field of view of 360 degrees, enabling it to track objects that move anywhere within a particular plane. The relocation of processing logic directly onto the hardware comprising a smart transducer allows such a composite sensing device to be completely self-contained, and scalable to even larger combinations of modules. The ability to combine diverse modular sensor and actuator components to produce flexible modular sensor systems facilitates rapid reconfiguration to suit any requirement, and is a technique that will prove useful in many modern applications. Examples of applicable domains include flexible inspection, mobile robotics, surveillance, and even space exploration.

## **1.3** Survey of Related Work

#### **1.3.1** Logical Sensor Architectures

Modular sensing systems are often composed of a number of sensors and possibly actuators of diverse types. Enabling intercommunication and collaboration among these transducers, especially in a manner such that the sensing system is easily reconfigurable, is often problematic due to the various interfaces through which communication with inherently different types transducers must take place. For example, the interface through which readings are obtained from an analog transducer is often quite different from that through which readings are obtained from a digital transducer. Therefore, facilitating interoperability between the devices often requires solutions that are specific to the interfaces through which they communicate. Reconfiguring such solutions in large systems in which numerous sensors and actuators are present can become unwieldy to the system user when transducers with newer interfaces are to be introduced and utilized within the systems.

One approach that aims to simplify the specification and assembly of multi-sensor systems, aspects of which are utilized in the design of the software architecture described in thesis, is the *Logical Sensor Specification* (LSS) [2, 3]. The LSS introduces the useful abstraction of a *logical sensor*, shown in Figure 1.1. The specification of a logical sensor facilitates the abstraction of the data produced by many different types of sensors into a uniform representation that is adhered to by all the sensors, and thus the internal hardware implementation of a sensor and the details of its data acquisition interface are completely hidden from the system user. As a result, dynamically reconfigurable modular sensing systems may be easily assembled through the composition of the logical sensor representations of its comprising sensors.

Since a logical sensor exposes a standardized interface, another strength of the logical sensor abstraction is that a logical sensor need not necessarily be associated with a physical entity. A logical sensor may be a software program that satisfies this abstraction interface, or may be a physical sensor that is augmented with processing algorithms implemented in software. Hierarchies of logical sensors may even be assembled in which multiple logical sensors are combined to form a composite logical sensor that appears to the system user as a single entity. Logical sensors higher in the hierarchy communicate with encompassed logical sensors lower in the hierarchy through the transmission of commands that are interpreted by a *control command interpreter*, and acquire data from the logical sensors through any of a set of programs each designed to obtain data in a unique fashion from a set of inputs. The ability of a logical module to selectively utilize different methods of acquiring data, through the use of its *selector*, is useful in the event of failure in the lower levels of the hierarchy. An example of a logical sensor hierarchy in

Figure 1.1: Logical sensor block diagram [2].

which two two-dimensional cameras and a stereo processing algorithm, or alternatively an active range camera, are used to implement a three-dimensional measurement system is shown in Figure 1.2.

Another existing architecture that provides similar benefits to that of a logical sensor hierarchy is that of *logical neighbourhoods* [4, 5]. In this architecture, sensor and actuator nodes are abstracted into uniform *virtual nodes* that may in turn be further abstracted into a composite collection termed a *logical neighbourhood*. Logical neighbourhoods appear as a single virtual node entity that may be further composed into larger neighbourhoods. Virtual nodes higher in the hierarchy transmit commands and data to nodes lower in the hierarchy through a wireless interface. The definition of virtual nodes and logical neighbourhoods is facilitated through template definitions written in the *SPIDEY* declarative language [4, 5].

#### **1** INTRODUCTION

Figure 1.2: Sample logical sensor hierarchy [3].

#### 1.3.2 The IEEE 1451 Standards

The knowledge representation scheme utilized with the software architecture to represent the functionality and capabilities of modular sensing and actuation components utilizes aspects of the NIST *IEEE 1451* [6, 7] family of standards for smart transducers. These standards describe a set of network-independent communication interfaces that simplify the connection of sensors or actuators to microprocessors, instrumentation systems, and networks, enabling them to be utilized in a "plug-and-play" manner. The core feature of these standards is the *Transducer Electronic Data Sheets* (TEDS) defined for each transducer type, which is a region of memory that stores information about the functionality and capabilities of the transducers, such as calibration information and measurement range, in an easily accessible and network-independent form. Where embedded mem-

#### **1** INTRODUCTION

ory is not available to facilitate local storage of the TEDS, a remote *virtual TEDS* may instead be used. A standard TEDS layout is shown in Figure 1.3.

The first member of the IEEE 1451 family of standards is *IEEE 1451.0*. This standard defines a common set of commands and TEDS on which the other members of the IEEE 1451 family are built. Through the use of these commands, sensors and actuators may be accessed in a standard fashion independent of the communications medium to which they are connected. This also simplifies the addition of further IEEE 1451 standards to the family as the need arises. The second standard, *IEEE 1451.1*, defines a standard object-oriented, extensible class hierarchy that describes the behaviour of, and provides a software interface to, networked smart transducers. This network-based software interface to the transducers is facilitated by a processing node present within each smart transducer known as the *Network Capable Application Processor* (NCAP). The NCAP contains the logic and hardware necessary to enable the smart transducer module to be interfaced with the communications medium. A customized software framework may be easily implemented through the utilization and composition of the classes present within the IEEE 1451.1 hierarchy.

Each of the remaining members of the IEEE 1451 family define a unique TEDS specification and an interface that provides a link between the NCAP and a particular class of transducers, enabling those transducers to be accessed through any communications medium to which the NCAP may be interfaced. These standards are depicted in Figure 1.4 and are outlined below:

• IEEE 1451.2 — The *IEEE 1451.2* standard defines a point-to-point digital interface, termed the *Transducer-Independent Interface* (TII), between the NCAP and a *Smart Transducer Interface Module* (STIM). A STIM contains and provides a standard digital interface to the various analog and digital transducers present within a particular networked smart transducer module.

Figure 1.3: Sample TEDS layout [8].

- IEEE 1451.3 The *IEEE 1451.3* standard defines a distributed multi-drop digital interface, facilitated through a *Transducer Bus Controller* (TBC), between the NCAP and any number of *Transducer Bus Interface Modules* (TBIMs). Each TBIM provides a standard digital interface to one or more of the transducers present within the multi-drop network.

- IEEE 1451.4 The *IEEE 1451.4* standard defines a digital mixed-mode interface (MMI) between the NCAP and any number of mixed-mode transducers (MMX). Mixed-mode transducers are able to transfer data in both analog and digital forms.

- IEEE 1451.5 The *IEEE 1451.5* standard defines a digital wireless interface between the NCAP and any number of transducer modules utilizing various standard wireless transmission protocols. Supported protocols include *WiFi* (IEEE 802.11),

Figure 1.4: Application of the IEEE 1451 standards.

Bluetooth (IEEE 802.15.1), and ZigBee (IEEE 802.15.4).

- IEEE 1451.6 The *IEEE 1451.6* standard defines a digital interface between the NCAP and any number of transducer modules utilizing the *CANopen* controller area network bus protocol. Both intrinsically safe and non-intrinsically safe operating modes are supported.

- IEEE 1451.7 The *IEEE 1451.7* [9] standard defines a digital interface between the NCAP and any number of transducer modules that support communication with ISO/IEC 24753-compliant *radio-frequency identification* (RFID) tags. RFID tags are normally applied to objects of interest for tracking and identification purposes.

### 1.3.3 Existing Modular Sensing Systems

A number of implementations of reconfigurable modular sensing systems exist in which smart sensor and actuator components may be combined or otherwise collaborate, and are described in the following subsections. Further relevant literature pertinent to the individual components of the software architecture described in this thesis may be found in subsequent chapters.

#### Mica

A popular implementation of a reconfigurable modular sensing system is the UC Berkeley *Mica* platform [10]. Each Mica node, known as a *mote*, measures  $1.25 \times 2.25$  inches and runs the TinyOS real-time operating system [11] using a 4 MHz ATmega103L or ATmega128 microcontroller. Wireless communication capability of up to 115 kbps (kilobits per second) is facilitated through the use of an RF Monolithics TR1000 transceiver. Although the motes are capable of collaboration through the use of a peer-to-peer multi-hop wireless networking protocol, no actuation capabilities are supported, and therefore the motes are limited to operating in non-active sensing applications.

#### Smart-Its

A similar system to the Mica project is the *Smart-Its* [12] project. Smart-Its are selfcontained nodes, as small as  $17 \times 25 \times 15$  mm, designed to be stuck onto everyday objects. The objects are thus enhanced with sensing and computational capabilities. Each Smart-Its node is aware of its attached sensors and is capable of relaying this information to other nodes in its environment on demand through the use of a query-based *Perception Application Programming Interface* (PAPI). Using the PAPI, each node can gather readings from other nodes in its environment in addition to its own sensor reading through a wireless interface. These values may then be processed locally and transmitted to higher-end devices such as personal computers and personal digital assistants (PDAs). However, like the Mica motes, the active operation and automatic reprogramming capability of Smart-Its nodes is limited.

#### eBlocks

More closely related to the system described in this thesis are the *eBlocks* [13, 14] embedded system building blocks. An eBlock is an electronic module, incorporating a Microchip PIC microcontroller to provide local intelligence, that allows a small-scale sensor-based system to be created by connecting various eBlocks together. Unlike general purpose sensor-network nodes such as the Mica motes, and like the system described in this thesis, each eBlock performs a specific, well-defined function. Simple sensor networks may be constructed even by users who are not technically adept.

There are four classes of eBlock: *sensor blocks*, which include sensors such as light and motion detectors and output either a digital "yes" or "no"; *logic/state blocks*, which combine the yes and no outputs from the sensor blocks and generate further outputs using combinational or sequential logic; *communicate blocks*, which transform a wired interface into a wireless link; and *output blocks*, which include an actuator such as an LED, buzzer, or relay, and also possess a general-purpose interface that may be used to control other electronic devices or communicate with a more powerful processing device such as a personal computer. Although reconfigurable, connected blocks are unable to determine their overall geometry or quickly and automatically assume a collective identity to suit new configuration requirements. The possible applications of the system are also limited due to the usage of simple combinational and sequential logic functions to produce composite readings and actions.

#### I-BLOCKS

Another relevant project focusing on the development of modular sensing systems is the *I-BLOCKS* project [15], in which LEGO DUPLO bricks are populated with a PIC16F876 microcontroller as well as select sensors and actuators. These building blocks, like the eBlocks, allow the creation of a modular sensing system without the need to learn and

use a traditional programming language. When physically connected, the blocks are able to communicate with each other through a half-duplex connection, and may also employ wireless communication if desired. The blocks have also been demonstrated to be capable of achieving a degree of positional awareness through the use of infrared positioning techniques based on sensor fusion of the readings produced by multiple infrared sensors. However, like the eBlocks, connected blocks are unable to determine their overall geometry or automatically assume a collective identity based on their orientations. The blocks are also not designed to be easily reprogrammed to suit changing application requirements.

#### MASS

*MASS* (Modular Architecture for Sensing Systems) [16] is a modular sensing system architecture that is optimized for low power consumption and is based on modular intelligent nodes. Each node itself consists of physically separable and hot-pluggable modules, each containing a processing controller that facilitates access to resources specific to the module. Node modules communicate through a shared 80-pin bus that also provides structural integrity.

There are four types of MASS modules that may be combined as necessary to produce a node to suit a specific application: *General Purpose Processor* modules (GPPs), which contain a powerful microprocessor or digital signal processor (DSP) used for heavy local data processing or sensor fusion; *sensor* modules, which contain a specific type of sensor and a low power controller that performs rudimentary local sensor data analysis; *Wireless Network Connector* (WNC) modules, which provide wireless connectivity that facilitates inter-node communication; and *power* modules, which provide power to an entire node. Upon connection, modules within a particular node detect each other's resources and the node assumes an appropriate behaviour profile based on the resources discovered.

Similar to the software architecture described in this thesis, the MASS software ar-

chitecture is a layered architecture based on the *Open Systems Interconnection* (OSI) reference model [17], and contains a message-based API (Application Programming Interface) for inter-node communication. Exchange of IEEE 1451-compliant datasheets as described in Section 1.3.2 is also supported. However, MASS provides no capability for active nodes nor the assumption of behaviour profiles based on node positions and orientations.

#### BUG

BUG [18] is a powerful modular sensing system platform consisting of a collection of electronic modules that are designed to be snapped together to produce a variety of composite components. Available BUG modules include: *BUGbase*, which is a fully programmable embedded computer based on the ARM1136JF-S microprocessor possessing 128 MB (megabytes) of on-board memory, several high-speed communication interfaces including Ethernet, and four slots to which other BUG modules are attached; BUGview, which contains a 2.46 inch touch-screen LCD with a resolution of  $320 \times 240$  pixels; BUG*motion*, which consists of an infrared motion detector with a range of 2 meters and an accelerometer with a software-selectable 2.5 g to 10 g sensitivity; BUGlocate, which contains a (GPS) receiver based on a SiRF chipset; and BUGcam2MP, which contains a 2-megapixel camera capable of capturing video. Although extremely flexible, the BUG platform does not currently provide functionality to facilitate active sensing. In addition, the orientations in which BUG modules may be attached to the BUGbase are still somewhat limited, and cannot be determined, thus restricting the ability of a composite BUG system to form a new collective identity based on the orientation of its constituent components.

#### Posey

*Posey* [19] is a hub-and-strut construction kit enhanced with computational ability. Within a Posey assembly, hubs and struts are optocoupled into flexible ball-and-socket joints with three degrees of freedom, where each ball possesses an array of 11 infrared LEDs and each socket possesses an array of four phototransistors. Each hub and strut contains an embedded ATmega168 microcontroller that captures data from the optocoupled connections, which is used to determine the geometric configuration of any particular joint without requiring explicit alignment of the joint. The microcontroller then relays this information through an XBee ZigBee (IEEE 802.15.4) wireless transceiver to a remote personal computer for further processing. Although Posey supports the acquisition of position and orientation information from the local processing unit located within each ball-and-socket joint, the units themselves do not locally collaborate to form a composite entity. Rather, the system depends upon a more powerful mainstream computer system to provide the necessary intelligence to compose the data provided from the joints.

## 1.4 Research Objective

The aim of this work is to develop a software architecture and knowledge representation scheme that facilitates the flexible, scalable, and reliable combination of modular sensing and actuation components for the purpose of forming composite sensing devices with motion capability. Each modular component provides a core sensing or actuation functionality (such as temperature or pressure measurement) and contains embedded knowledge of its capabilities (such as its operating range and response time), which is communicated to other modules within its environment. The design of the architectural framework should fulfil the following criteria:

• Heterogeneity — Support the connection of sensor and actuator modules possess-

ing diverse functionality and capabilities.

- Autonomy Support the autonomous discovery of the capabilities of networked modules, and the autonomous configuration of these modules based on their discovered capabilities.

- **Pose/Geometry Determination** Support the determination of the absolute or relative *pose* (position and orientation) of individual modules, and by extension the overall geometry of a set of connected modules.

- Assumption of a Collective Identity Facilitate the assumption of a collective identity by successfully connected modules, based on their capabilities and relative positions and orientations.

- **Process Distribution** Support the splitting and distribution of a complex task among a group of networked modules.

- Resource Management Manage the hardware resources on each module in an efficient, intuitive, and simple manner.

- Scalability Maintain reliable operation with an increasing number of connected sensor and actuator modules.

- **Robustness** Adapt automatically to the addition, removal, or failure of modules in real-time.

## 1.5 Thesis Outline

This thesis is divided into eight chapters that progressively describe the design and operation of the software architecture from its lowest level interactions with the module hardware to its highest level software components. A brief synopsis of the contents of each chapter is provided as follows:

- Chapter 1 Introduction: This introductory chapter. Outlines the motivation behind the development of the software architecture as well as its design criteria, and provides a survey of existing modular sensing system architectures as well as standards facilitating sensor interoperability.

- Chapter 2 Architecture Description: Outlines the software architecture itself and the hardware on which it executes. Topics covered include the utilized real-time operating system and file system, as well as an overview of the various layers present within the architecture.

- Chapter 3 Communication Layer: Describes the communication layer of the software architecture, which provides a reliable, connection-oriented service for wired and wireless communication to the layers above it, and also facilitates time synchronization between modules.

- Chapter 4 Middleware Layer: Outlines the middleware layer of the software architecture, which defines a standard application programming interface (API) that facilitates interoperability between the modules on which the architecture executes and enables them to request services from each other.

- Chapter 5 Virtual Machine: Describes the virtual machine utilized within the software architecture, based on Sun Microsystems' Java Virtual Machine, that promotes the straightforward portability of collaborative intelligence algorithms between diverse module hardware platforms.

- Chapter 6 Composition Layer: Outlines the composition layer of the software architecture, where intelligence is implemented and utilized in the form of platform-

independent algorithms that enable a group of modules to collaborate and form composite entities.

- Chapter 7 Architecture Evaluation: Provides results and analysis of the behaviour and performance of the software architecture once deployed on actual module hardware.

- Chapter 8 Conclusions: Provides a final overview of the software architecture and also provides recommendations for further improvement.

## Chapter 2

## Architecture Description

## 2.1 Introduction

This chapter provides a description of the module hardware on which the software architecture executes, as well as the layered model on which the architecture is based. The real-time operating system utilized for the purpose of concurrent task management is then described, followed by information on the file system driver and the organization of the standard file structure. A description of the core data types utilized throughout the software architecture is then provided.

### 2.2 Module Hardware Overview

### 2.2.1 Transducer Interface Modules

The basic module used to construct modular sensing systems is the *transducer interface* module (TIM). Each is capable of a single sensing or actuation function, and is uniquely identified by a 64-bit address. This address possesses a most significant bit of zero, since addresses with a most significant bit of one are reserved for assignment to composite

module entities termed *logical modules* that are comprised of a set collaborating TIMs. The zero address and the address of all ones are also reserved, and may not be assigned to single nor composite modules. The address of all ones is utilized for broadcasts to all the modules comprising a modular sensing system. With this addressing scheme, up to approximately  $9.2 \times 10^{18}$  physical transducer modules may be uniquely addressed, a value which is likely to exceed the number of modules created throughout the lifetime of the technology. As specified in the IEEE 1451 standard for smart transducers [6], each module possesses one or more *Transducer Electronic Data Sheet* (TEDS) specifications in non-volatile memory, from which a description of the characteristics of its associated sensors or actuators may be obtained.

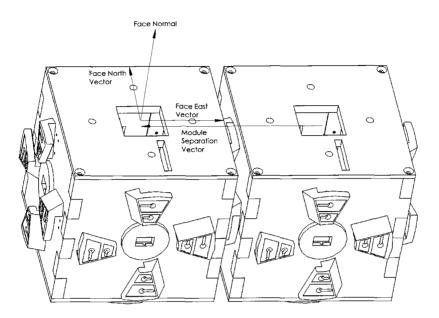

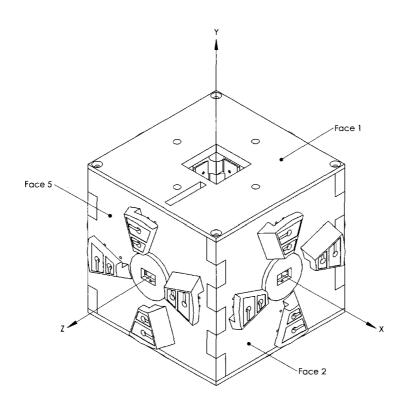

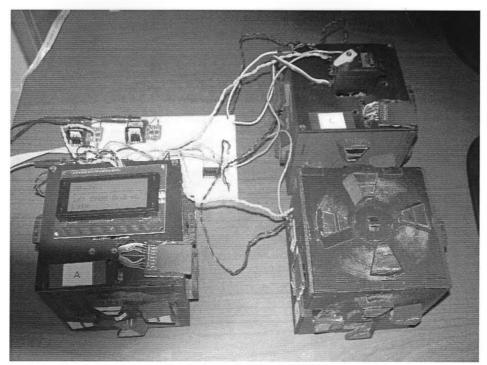

TIMs are cubical in shape, and thus each possesses six faces to which up to five other modules may be connected, as shown in Figure 2.1. One face is reserved for use by the transducer associated with the module. The hardware which comprises a TIM, shown in Figure 2.2, includes the associated transducer; a high-speed NXP Semiconductors LPC2148 ARM-based microcontroller [20]; a Nordic Semiconductor nRF24L01 [21] wireless transceiver supporting high-speed data transmission, multi-channel operation and carrier detection; a Secure Digital<sup>TM</sup> (SD) flash memory card providing high-capacity, non-volatile storage for data and algorithms; a power supply capable of providing a voltage of 3.3 volts to 9 volts; and five *module connectors*, which are proprietary interfaces used to physically connect additional modules. The interfaces are designed such that the relative orientation between any two connected modules may be determined. Further details on the electrical and mechanical design aspects of the TIMs may be found in [22].

#### 2.2.2 Other Module Types

A modular sensing system may consist of two other types of modules significant to the software architecture. These modules perform tasks unrelated to sensing and actuation;

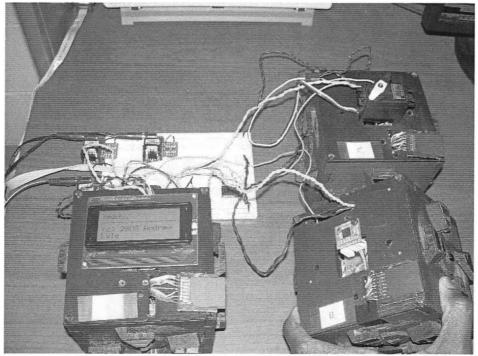

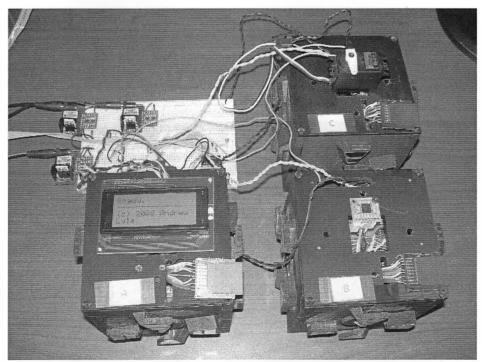

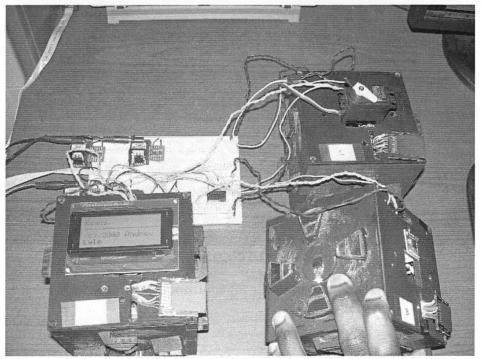

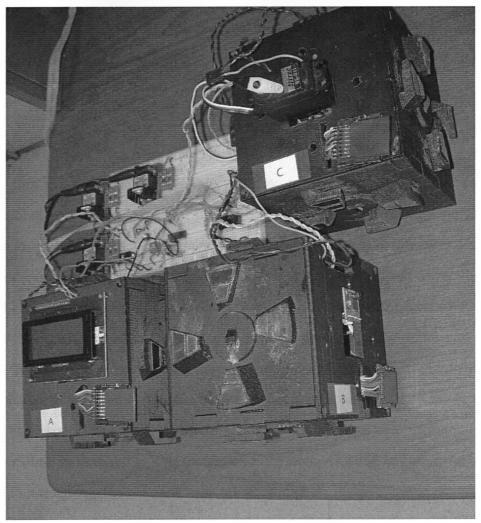

Figure 2.1: Transducer Interface Modules and interconnects.

Figure 2.2: Transducer Interface Module block diagram.

instead, they support the inter-operation of a group of TIMs.

#### Administration Module

An *administration module* is used by the system user to detect and manage TIMs within its vicinity. It possesses only a power supply, a microcontroller, and a transceiver. It may be integrated into a complete computer system, or be a small, self-contained console with a user interface. Administration modules may also act as a sink for transducer readings and as a gateway for communication with a larger network, such as the Internet. All TIMs, however, may run an optional shell task which provides the system user with administrative functionality.

#### Interconnect Module

Interconnect modules are each built to assume one of a variety of non-standard shapes, and are used to provide angular and translational offsets between connected TIMs which would otherwise not be possible due to the cubical shape of the TIMs. An example of an interconnect module which provides an angular offset is shown in Figure 2.1. They possess only a microcontroller and module connectors, and draw power from the TIMs to which they are connected. The nature of the offset provided by a particular interconnect module is stored in its TEDS, and may be accessed through its module connectors.

### 2.3 Software Architecture Stack

The software architecture described in this thesis is a distributed architecture based on the *Open Systems Interconnection* (OSI) reference model [17], and consists of six layers (one of which is divided into two sub-layers) as shown in Figure 2.3. The use of a *distributed* architecture ensures that no single point of failure exists within a modular

Figure 2.3: Software architecture stack.

sensing system and also facilitates architecture scalability, unlike *centralized* architectures, in which a single point of failure is often introduced that can also limit scalability in large systems where communication between nodes mostly occurs through this point. The use of a layered architecture model allows the implementation of any layer to change independently of the others, since the implementation of each layer is encapsulated from the layer above, to which it provides service. This information-hiding technique also facilitates a more robust software architecture, and makes each of the architecture layers easier to implement, modify, and debug. The function of each layer is defined as follows:

- Module Hardware Contains the physical components of a module needed for execution of the operating system, sensing and actuation functionality, as well as wired and wireless communication.

- Real-Time Operating System/Device Drivers Provides resource management functionality and an environment for concurrent task execution, as well as the low-level software routines needed to manipulate and manage the hardware resources present in the module.

- Communication Layer Provides an interface to the wireless transceiver driver

that automatically accounts for transmission problems such as packet loss and synchronization. This layer also provides an interface through which modules may communicate using their face connectors.

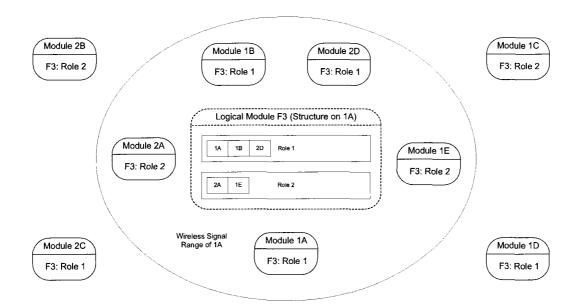

- Middleware Layer Provides the commands and services through which the member TIMs comprising a *logical module* may interact and communicate with each other in order to achieve a specific goal. A logical module is an abstraction of one or more collaborating TIMs, a representation of which is present locally on each of the TIMs comprising the logical entity. More than one logical module representation may be present on a single TIM.

- Virtual Machine Provides a platform-independent execution environment for the algorithms utilized in the composition layer. This enables the behaviour of a group of collaborating TIMs to be specified in a manner that is completely decoupled from their underlying hardware architecture. Platform independence is facilitated through the use of a compact implementation of Sun Microsystems' Java Virtual Machine [23].

- Composition Layer Encompasses one or more *logical module template algorithms* that process the transducer state and module pose messages transferred among a group of collaborating TIMs and enables them behave as a logical entity. Each template algorithm, in the form of a Java class, is accompanied by a *logical module template TEDS* that describes the basic characteristics of a logical module entity derived from on it.

# 2.4 Real-Time Operating System

The software architecture utilizes a *real-time operating system* (RTOS), which enables it to be implemented in a modular fashion through the concurrent execution of various *tasks*. As a result, the management of the hardware resources of a module, as well as the development and debugging of the software architecture, is vastly simplified. Tasks are implemented as independent functions, each with its own stack and register set, that appear to be running simultaneously, but are actually sharing the execution time of the microcontroller through the use of *scheduling* mechanisms implemented within the operating system.

### 2.4.1 Scheduling Policies

In an RTOS, concurrently executing tasks may be scheduled using either a *pre-emptive* scheduling policy or a *cooperative* scheduling policy. In pre-emptive scheduling, CPU time is automatically shared between tasks based on their assigned priority, while in cooperative scheduling each task maintains control of the CPU until it explicitly yields control. Pre-emptive scheduling is advantageous since it prevents long-running, low-priority *back-ground* tasks from blocking shorter, higher-priority *foreground* tasks from executing, thus improving system response speed to external events. In the popular *TinyOS* [11] RTOS, which utilizes a cooperative scheduler, all tasks must run to completion. Long-running background tasks are therefore prohibited, and care must be taken to ensure that each task completes in a reasonable amount of time.

## 2.4.2 Choice of RTOS

Two real-time operating systems, *FreeRTOS* [24] and *TNKernel* [25], were considered for use in the software architecture. Due to the limited 40 kilobytes of internal RAM (random-

access memory) present on the LPC2148 microcontroller, more complex operating systems such as eCos and RTLinux could not be assessed. Both FreeRTOS and TNKernel are free, open source, compact, and well documented; they also possess a large user base and code that has been heavily tested on a variety of embedded architectures, including the ARM architecture. In addition, FreeRTOS and TNKernel both contain a priority-based pre-emptive task scheduler, and make provisions for message passing and synchronization between concurrently executing tasks.

The real-time operating system chosen for use in the software architecture presented herein is TNKernel. This RTOS was chosen over FreeRTOS due to its more compact and easily modifiable code base. In addition to not relying on the standard C library, TNKernel does not utilize any form of dynamic memory allocation internally, thereby allowing the implementation of a simplified dynamic memory allocator to be used exclusively by the upper layers of the software architecture where necessary.

## 2.4.3 Task Types

Three standard background tasks, and at least one message handling task, are created and executed upon startup and initialization of a module. Multiple message handling tasks may also be created and executed by the software architecture at any point during its execution, depending on the type of modules that are within close proximity. These various task types are briefly described below.

• Network Communication Task — Performs various duties related to communication on the various wireless data channels. These duties include broadcasting control packets which indicate the presence of the module in the network; transmitting, receiving, and processing data packets; and maintaining synchronization with other modules in the environment. This task is described in further detail in Section 3.6.

- Face Communication Task Manages the communication of the module with others physically connected to its faces. This task detects the physical connection and disconnection of other modules to any of the five connectible module faces, handles the transfer of data through the connectors on the faces, and calculates the relative *pose* (position and orientation) between the module and those to which it is physically connected. This task is described in further detail in Section 3.7.3.

- Administrative Interface Task Allows the system user to monitor and administrate any module, or logical group of modules, within the modular sensing system. Some of the functionality available to the system user includes listing the modules in the environment, manually forming a logical module entity, reading and writing to module sensors and actuators, modifying the local clock of the module, and various debugging features such as suspending and resuming tasks and monitoring wireless channel activity.

- Module Message Handler Task Handles middleware layer messages placed within the incoming message queues of a TIM or a logical module entity of which it is a member. This task is also responsible for performing various status checks on its associated module before each received message is processed, such as determining if a queued write message was received from a source with the appropriate write permissions. At least one message handler task is created by default for a TIM upon initialization, to process and transmit messages related to its local hardware. Other instances may be created as the TIM becomes a member of one or more logical module entities. For physical TIMs, the message handler task is fully implemented natively, while for logical modules it is mostly implemented using platform-independent Java classes.

# 2.5 File System

A *file system* is a set of data structures that facilitates the storage, organization, and retrieval of files from a data storage device. A file system is employed within the software architecture to provide an efficient, high-level interface to information and algorithms stored on SD flash cards that determine the identity and behaviour of a particular module in a network. Utilizing a lightweight and widely adopted file system enables the system user to easily access and modify these files using standard computers and operating systems.

SD flash cards to be utilized by the software architecture are formatted with the FAT32 (32-bit File Allocation Table) [26] file system and initialized with a standard file structure that is described in Section 2.5.2. The FAT32 file system was chosen due to its wide support on numerous mainstream operating systems for personal computers, particularly Microsoft Windows, GNU/Linux, and Mac OS X. FAT32 is also lightweight as compared to other popular file systems such as *ext3* (Third Extended Filesystem) [27] and *NTFS* (New Technology File System) [28] that utilize additional data structures and memory in order to reduce file fragmentation and to provide features such as *journaling* that aid recovery from file corruption, neither of which is crucial to the operation of TIMs. Finally, the FAT32 file system is also well understood, resulting in the availability of a number of stable and mature FAT32 file system drivers for embedded devices.

### 2.5.1 Choice of FAT32 File System Driver

Two popular FAT32 file system drivers, the *FAT File System Module* [29] and the *Embedded Filesystems Library* (EFSL) [30], were considered for use in the software architecture. Both are open source, compact, and easy to use and modify. The FAT File System Module was chosen for use in the software architecture due to the availability of the extremely compact *Tiny-FatFs* version of its standard *FatFs* driver. It consumes much less flash memory space and utilizes much less RAM as compared to FatFs and EFSL, and is also easily adaptable to any type of input/output (I/O) device assuming a block I/O driver is provided. Unlike FatFs and EFSL, Tiny-FatFs does not support I/O transfers to more than one storage device at a time; however, the SD card is the only storage device present in a TIM.

### 2.5.2 Standard File Structure

As previously mentioned, an SD card formatted for use with a TIM is initialized with a standard file structure for organizational purposes. A standard file structure is utilized to ensure that the software architecture is consistently able to locate and access the files necessary for its operation from predictable locations irrespective of the underlying hardware on which it executes or the storage medium on which these files are located. Access to these files by the users of the system is also made more convenient. The file structure designed for the purposes of the software architecture is depicted in Figure 2.4, and consists of four directories as well as up to four different types of files. These directories and files are described below.

• Template Class Directory — The template class directory amss/algo is the directory in which the Java classes, termed the logical module template classes, are placed. These classes provide the platform-independent intelligence that enables connected TIMs to collaborate with each other. The template class directory path amss/algo adheres to the Java naming convention for package paths, and corresponds to the package amss.algo that all template classes are declared a member of. Unlike standard Java classes, template classes possess no .class extension since the Tiny-FatFs driver requires strict adherence to the 8.3 file naming convention [31]. In this convention files may only possess a name consisting of up to eight characters

Figure 2.4: File system block diagram.

optionally followed by a period and an extension of three characters. This limitation was imposed by the original FAT file system used in older Microsoft operating systems, and is only non-obligatory in the more complex implementations of FAT32 utilized in mainstream operating systems.

- Module TEDS Directory The module TEDS (Transducer Electronic Data Sheet) directory teds consists of one or more text files termed module TEDS, each possessing the extension .mod, that identify and describe the characteristics of the transducers associated with a particular physical TIM in the form of a list of property-value pairs. The format of these text-based specifications is further described in Section 2.6.

- Template TEDS Directory The *template TEDS directory* tmpl consists of zero or more text files termed *template TEDS* that identify and describe the characteristics of a combination of collaborating TIMs known as a *logical module*. Tem-

plate TEDS are specified using the same format as module TEDS and possess the same .mod extension. Each template TEDS specification is associated with one template class in the template class directory. In addition to the standard characteristics of the logical module, a template TEDS specification also describes the various *roles* (further outlined in Section 6.2.2), also in the form of property-value pairs, that may be fulfilled by a particular TIM within the logical entity. The usage of template TEDS files within the software architecture is further outlined in Chapter 6.

- ARC4 Key File The ARC4 key file key.rc4 stores the variable-length key required by the Alleged Rivest Cipher 4 (ARC4) cryptographic stream cipher [32] utilized by the software architecture for the secure transmission of packets. If this file is not found, a default key is used. All packets transmitted by TIMs on the wireless communication medium are encrypted and decrypted in software using the ARC4 algorithm, and modules are only able to communicate with others that are utilizing the same key. Packets received from modules utilizing different keys will be indecipherable upon reception and are dropped. More details on the ARC4 algorithm and key file may be found in Sections 3.2.4 and 3.5 respectively.

- Network Identifier File The *network identifier file* net.id stores the 5-byte *network identifier* used to indicate that a particular TIM is a member of the network of TIMs possessing the network identifier specified. If this file is not found, a default identifier is used. Packet transmissions from modules with different network identifiers are completely ignored, thus reducing packet processing overhead within the software architecture. More details on the network identifier may be found in Sections 3.3 and 3.5.

# 2.6 TEDS Specification Format

As described in Section 2.5.2, TEDS (Transducer Electronic Data Sheet) specifications are text files that are defined to identify and describe the characteristics of the transducers associated with a particular physical TIM, or to identify and describe the general characteristics of a combination of collaborating TIMs known as a logical module. A TEDS specification always possesses the extension .mod, and consists of a list of property-value pairs, each on a separate line, with whitespace used to separate each property name from its value. Comments are supported within the file format; all characters on a line after and including the # character are ignored. The usage of a text format enables the TEDS to be specified in an easily human-understandable form, unlike the binary TEDS format normally utilized within the IEEE 1451 standards for smart transducers [8], which is typically incomprehensible to human readers. The *Extensible Markup Language* (XML) [33], a popular format for representing data through the use of text, is not utilized for the purpose of module TEDS specification since it introduces redundant, verbose syntax that often makes information of interest difficult to locate by human readers. XML is also non-trivial to parse, especially on resource-constrained embedded devices.

Sample module TEDS specifications may be seen in Section B.2, and sample template TEDS specifications may be seen in Section B.3. A standard TEDS specification consists of three sections. The first section is the AMSS (Adaptive Modular Sensing System) TEDS, which is specific to the software architecture and describes the essential attributes of a module necessary for the software architecture to utilize it. The other two sections, the Basic TEDS and the Standard Template TEDS, facilitate the definition of manufacturer-specific information and transducer properties as defined within the IEEE 1451 standards, and are outlined in [8]. An additional Roles section, also specific to the software architecture, is present only within template TEDS specifications. As described in Section 2.5.2, the Roles section defines the roles within a logical entity derived from the template TEDS that may be fulfilled by its member modules, and is further outlined in Section 6.2.2. The fields contained within an AMSS TEDS specification are defined as follows:

- Module Address The 64-bit address assigned to a module to uniquely identify it. This field is not present within template TEDS specifications, since the addresses of the logical modules derived from these templates are automatically assigned by the software architecture at runtime.

- Module Type A constant indicating the type of the module, which may be a *sensor* module, an *actuator* module, an *interconnect* module, or an *administrator* module.

- Module Class A constant indicating the *class* of the module. A *class* refers to a family of sensors or actuators that may be used to sense a particular physical quantity or facilitate a specific type of motion respectively. Currently, the supported module classes are *acceleration* modules, *positional* modules, *rotational* modules, *status* modules, *text display* modules, and *voltage* modules.

- Module Data Type A constant indicating the data type of the array of values returned by the module. The return type may be an 8-bit, 16-bit, 32-bit, or 64-bit signed or unsigned *integer*, a 32-bit or 64-bit *floating point* value, a *status string*, an encompassed middleware layer *message* (see Section 4.3), or a generic *object* consisting of raw bytes.

- Module Data Type Width Specifies the number of columns in the array of values returned by the module.

- Module Data Type Height Specifies the number of rows in the array of values returned by the modules.