# Western University Scholarship@Western

**Electronic Thesis and Dissertation Repository**

4-26-2023 1:30 PM

# A Novel Two-Stage AC-DC Power Converter with Partial Power Processing

Mina Fakhri,

Supervisor: Dr. Gerry Moschopoulos, *The University of Western Ontario* A thesis submitted in partial fulfillment of the requirements for the Master of Science degree in Electrical and Computer Engineering © Mina Fakhri 2023

Follow this and additional works at: https://ir.lib.uwo.ca/etd

Part of the Power and Energy Commons

#### **Recommended Citation**

Fakhri, Mina, "A Novel Two-Stage AC-DC Power Converter with Partial Power Processing" (2023). *Electronic Thesis and Dissertation Repository*. 9237. https://ir.lib.uwo.ca/etd/9237

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

# Abstract

A two-stage power converter with an AC-DC boost converter and a soft-switched DC-DC fullbridge converter is proposed in this thesis. The first stage has two interleaved modules that perform power factor correction; the second stage converts the output of the first stage to the desired output. An auxiliary circuit with a switch, a small transformer, and passive components is used to turn off the AC-DC converter switches with soft-switching; the auxiliary switch can also be turned on and off softly. The secondary of the auxiliary transformer is connected to the output of the overall converter so that some power can be transferred from the front-end converter to the output. This power is processed only once, thus reducing conversion losses. The thesis explains the operation of the converter and presents steady-state analysis and a design procedure. Results obtained from an experimental prototype are presented to confirm the converter's feasibility.

## Keywords

Two stage AC-DC converter, Interleaved boost converter, soft switching, PWM – ZVS full bridge converter, power processing

# Summary for Lay Audience

AC-DC power converters are used in many commercial and industrial applications to convert AC voltage into DC voltage to feed loads. This power conversion is typically done with two converter stages, an AC-DC stage followed by a DC-DC stage. The AC-DC stage shapes the input current so that it is sinusoidal and in phase with the input voltage to maximize power factor. The DC-DC stage takes the output of the AC-DC converter and converts to the required output voltage.

Power fed from the input to the load is processed by two converter stages with this type of converter. Each stage generates power losses when converting power, which decreases converter efficiency. This thesis proposes a novel two-stage converter that processes some of the power fed to the load using only one converter stage. This direct power transfer reduces losses that would have been generated by the second-stage converter. In this thesis, the operation of the proposed converter is explained, its steady-state operation is analyzed, and a procedure for the design of key components and parameters is developed and demonstrated with an example. The feasibility of the converter is confirmed with results obtained from an experimental prototype.

# Acknowledgments

I am honored to express my sincere appreciation to my advisor, Dr. Gerry Moschopoulos, for his invaluable patience, expertise, and guidance throughout my Master's research. His unwavering support has been instrumental in shaping this work, and I am proud to have had the opportunity to learn from him.

Furthermore, I would like to express my deep gratitude to Dr. Adel Abosnina, my fellow researcher at the Power Engineering Lab, for his invaluable guidance and support. His expertise in power electronics has been crucial to my academic pursuits, and I am grateful for the opportunity to have worked alongside him. I would like to thank Asad Hameed for his help with some of the experimental work as well.

Last but not least, my deepest gratitude goes to my lovely husband, Saeed, for his endless love and support. I would also like to express my profound appreciation to my parents, who have been the driving force behind my success. Their unwavering support and encouragement have been the greatest gift anyone could ask for, and I am forever indebted to them for allowing me to pursue my dreams and achieve my full potential.

| Abstractii                                                     |

|----------------------------------------------------------------|

| Summary for Lay Audienceiii                                    |

| Acknowledgmentsiv                                              |

| List of Tables                                                 |

| List of Figuresix                                              |

| Acronyms xii                                                   |

| Abbreviations                                                  |

| Chapter 1 1                                                    |

| 1 Introduction                                                 |

| 1.1 Introduction to power electronics                          |

| 1.2 Power electronic devices                                   |

| 1.2.1 Diodes                                                   |

| 1.2.2 The metal-oxide-silicon field-effect transistor (MOSFET) |

| 1.2.3 Insulated-gate bipolar transistor (IGBT)                 |

| 1.3 Switching losses                                           |

| 1.4 Soft switching                                             |

| 1.5 AC-DC converters                                           |

| 1.6 Interleaved AC-DC boost converters                         |

| 1.7 DC-DC full bridge converter                                |

| 1.8 Partial power processing                                   |

| 1.9 Literature review                                          |

| 1.10Thesis objectives                                          |

| 1.11Thesis outline                                             |

| Chapter 2                                                      |

# Table of Contents

| 2                                                                         | A novel two-stage AC-DC power converter with partial single-stage power processing |                    |                                                                         |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------|

|                                                                           | 2.1                                                                                | Introdu            | action                                                                  |

|                                                                           | 2.2                                                                                | AC-DO              | C interleaved ZCS-PWM boost converter                                   |

|                                                                           | 2.3                                                                                | PWM 1              | full-bridge converter                                                   |

|                                                                           | 2.4                                                                                | Modes              | of operation                                                            |

|                                                                           | 2.5                                                                                | Conver             | rter features                                                           |

|                                                                           | 2.6                                                                                | Conclu             | sion                                                                    |

| Cl                                                                        | napte                                                                              | er 3               |                                                                         |

| 3                                                                         | Cor                                                                                | verter c           | ircuit analysis                                                         |

|                                                                           | 3.1                                                                                | Introdu            | action                                                                  |

|                                                                           | 3.2                                                                                | AC-DO              | C interleaved boost converter                                           |

|                                                                           | 3.3                                                                                |                    | Voltage Switching (ZVS) Pulse-Width Modulated (PWM) Full-Bridge<br>rter |

|                                                                           |                                                                                    | 3.3.1              | ZVS for lagging leg                                                     |

|                                                                           |                                                                                    | 3.3.2              | ZVS for leading leg                                                     |

|                                                                           |                                                                                    | 3.3.3              | Secondary duty cycle loss:                                              |

|                                                                           | 3.4                                                                                | Conclu             | sion                                                                    |

| Cl                                                                        | Chapter 4                                                                          |                    |                                                                         |

| <ul><li>4 Design procedure and example</li><li>4.1 Introduction</li></ul> |                                                                                    | cedure and example |                                                                         |

|                                                                           |                                                                                    | action             |                                                                         |

|                                                                           | 4.2                                                                                | Design             | procedure for the AC-DC interleaved boost converter                     |

|                                                                           |                                                                                    | 4.2.1              | Input inductors L <sub>1</sub> and L <sub>2</sub>                       |

|                                                                           |                                                                                    | 4.2.2              | DC link capacitor                                                       |

|                                                                           |                                                                                    | 4.2.3              | Main switches S <sub>1</sub> and S <sub>2</sub>                         |

|                                                                           |                                                                                    | 4.2.4              | Design procedure for the auxiliary power circuit                        |

|                                                                           | 4.3                                                                                | Design             | procedure for the ZVS – PWM full bridge converter                       |

|                        |       | 4.3.1  | Turns ratio of the high-frequency transformer        | 62 |

|------------------------|-------|--------|------------------------------------------------------|----|

|                        |       | 4.3.2  | Resonant inductor                                    | 64 |

|                        |       | 4.3.3  | Output filter inductor and capacitor                 | 65 |

|                        |       | 4.3.4  | Output rectifier diodes                              | 66 |

|                        | 4.4   | Conclu | usion                                                | 67 |

| Cl                     | hapte | er 5   |                                                      | 68 |

| 5 Experimental results |       |        |                                                      | 68 |

|                        | 5.1   | Introd | uction                                               | 68 |

|                        | 5.2   | Experi | mental setup                                         | 68 |

|                        | 5.3   | Experi | mental waveforms                                     | 68 |

|                        |       | 5.3.1  | AC-DC boost converter waveforms (first stage)        | 68 |

|                        |       | 5.3.2  | DC-DC full-bridge converter waveforms (second stage) | 74 |

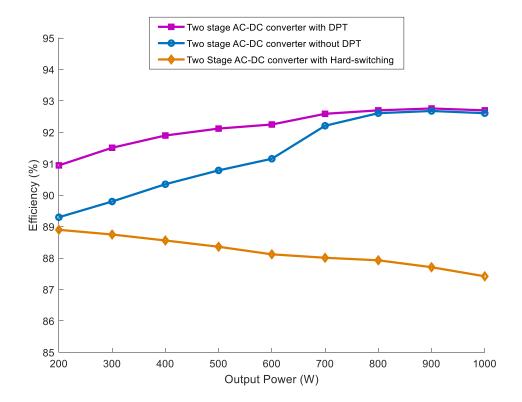

|                        | 5.4   | Conve  | rter efficiency                                      | 77 |

| Cl                     | hapte | er 6   |                                                      | 79 |

| 6 Conclusion           |       |        | 79                                                   |    |

|                        | 6.1   | Summ   | ary                                                  | 79 |

|                        | 6.2   | Conclu | usions                                               | 81 |

|                        | 6.3   | Contri | butions                                              | 82 |

|                        | 6.4   | Future | Work                                                 | 83 |

| R                      | efere | nces   |                                                      | 84 |

| C                      | urric | ulum V | itae                                                 | 90 |

|                        |       |        |                                                      |    |

# List of Tables

| Table. 5.1. Specification of the converter | components |

|--------------------------------------------|------------|

|--------------------------------------------|------------|

# List of Figures

| Fig. 1.1. Block diagram of a power electronic system 1                                 | 1 |

|----------------------------------------------------------------------------------------|---|

| Fig. 1.2. (a) idealized i-v characteristic (b) actual i-v characteristic               | 2 |

| Fig. 1.3. Reverse recovery current of a diode                                          | 3 |

| Fig. 1.4. Classification of MOSFET                                                     | 4 |

| Fig. 1.5. Circuit symbol of an N-Channel power MOSFET                                  | 4 |

| Fig. 1.6. Circuit symbol of an IGBT with an anti-parallel diode                        | 5 |

| Fig. 1.7. Typical actual switch voltage and current waveforms                          | 5 |

| Fig. 1.8. ZVS implementation for MOSFETs                                               | 7 |

| Fig. 1.9. ZCS implementation for IGBTs                                                 | 8 |

| Fig. 1.10. Block diagram of standard two-stage PFC AC-DC converters                    | 9 |

| Fig. 1.11. AC-DC boost converter                                                       | ) |

| Fig. 1.12. Topology of a basic AC-DC interleaved boost converter                       | 1 |

| Fig. 1.13. Inductor current waveforms according to the switching pattern in the DCM 12 | 2 |

| Fig. 1.14. DC-DC full bridge Converter                                                 | 3 |

| Fig. 1.15. Concept of power flow in a partial power converter                          | 4 |

| Fig. 1.16. Two-phase interleaved boost converter with soft switching                   | 5 |

| Fig. 1.17. Breadboarded interleaved ZCT boost converter                                | 5 |

| Fig. 1.18. Interleaved ZCS boost converter                                             | 5 |

| Fig. 1.19. ZCS interleaved bidirectional DC-DC Converter                               | 7 |

| Fig. 1.20. Front-end interleaved AC-DC -ZCS-PWM boost converter                                                                                               | 18 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

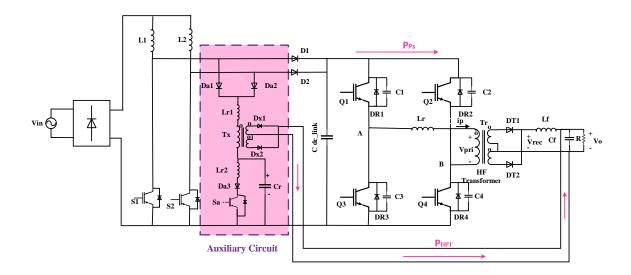

| Fig. 2.1. Proposed two-stage AC-DC power converter with Direct Power Transfer (DPT)2                                                                          | 21 |

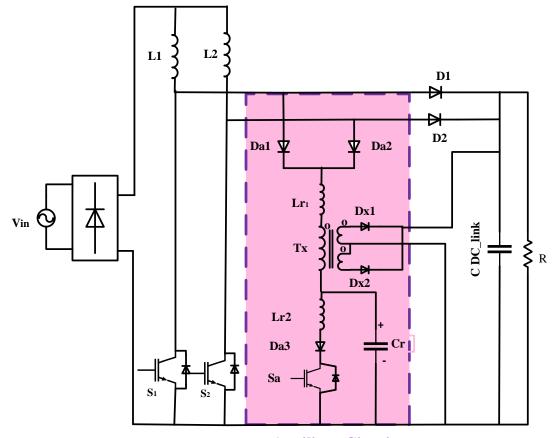

| Fig. 2.2. Front-end interleaved AC-DC ZCS-PWM boost converter                                                                                                 | 22 |

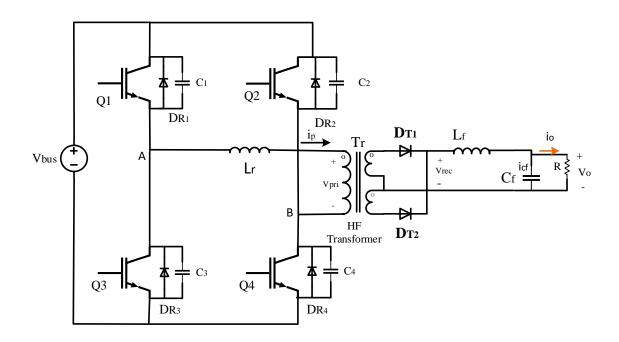

| Fig. 2.3. DC-DC full bridge Converter                                                                                                                         | 23 |

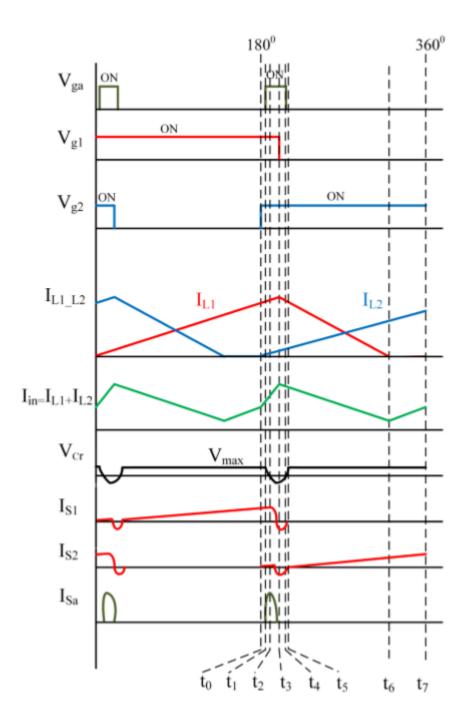

| Fig. 2.4. Typical waveforms of the converter shown in Fig. 2.2 [26]                                                                                           | 28 |

| Fig. 2.5. Key waveforms of the full-bridge DC-DC converter                                                                                                    | 29 |

| Fig. 2.6. Mode 1                                                                                                                                              | 30 |

| Fig. 2.7. Mode 2                                                                                                                                              | 30 |

| Fig. 2.8. Mode 3                                                                                                                                              | 31 |

| Fig. 2.9. Mode 4                                                                                                                                              | 31 |

| Fig. 2.10. Mode 5                                                                                                                                             | 32 |

| Fig. 2.11. Mode 6                                                                                                                                             | 32 |

| Fig. 2.12. Mode 7                                                                                                                                             | 33 |

| Fig. 3.1. Flow chart of the program to determine if the converter is operating under steady-<br>state conditions and obtaining the value of the $i_{Lr1}=i_x$ | 45 |

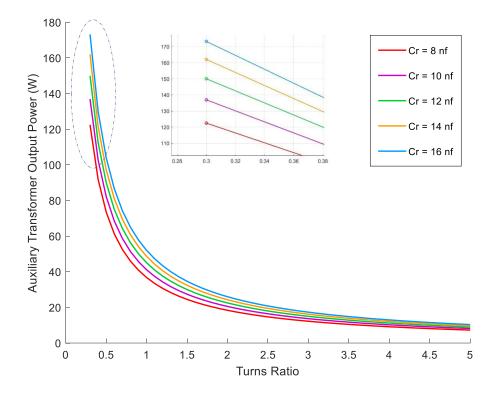

| Fig. 4.1. Effect of increasing the C <sub>r</sub> on the power transferred to the output by auxiliary transformer                                             | 57 |

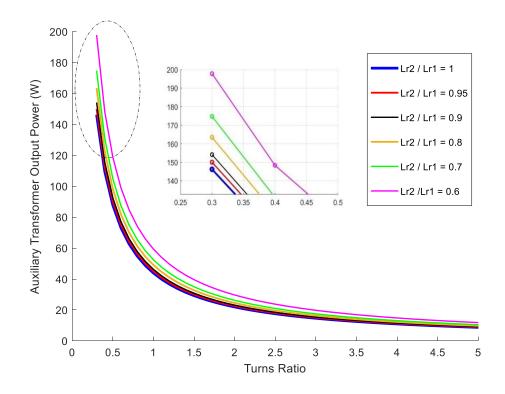

| Fig. 4.2. Effect of increasing the increasing of the $L_{r1}/L_{r2}$ on the transmitted power to the output through auxiliary transformer                     | 59 |

| Fig. 4.3. Effect of increasing the $L_{r2}$ on the ZCS conditions for auxiliary switch                                                                        | 59 |

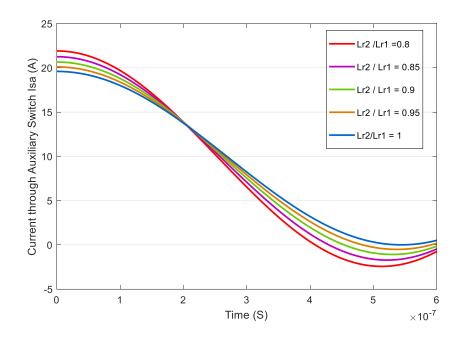

| Fig. 4.4. Auxiliary transformer output power vs turns ratio                                                                                                   | 61 |

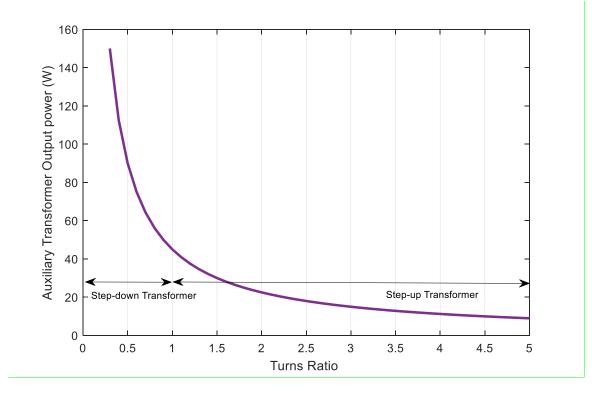

| Fig. 5.1. Input current and input voltage (V <sub>in</sub> : 75V/div, I <sub>in</sub> : 15A/div, $t = 5m/div$ )                                               | 70 |

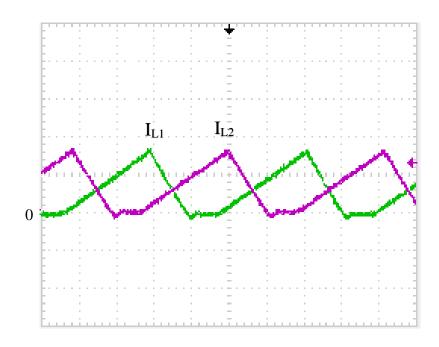

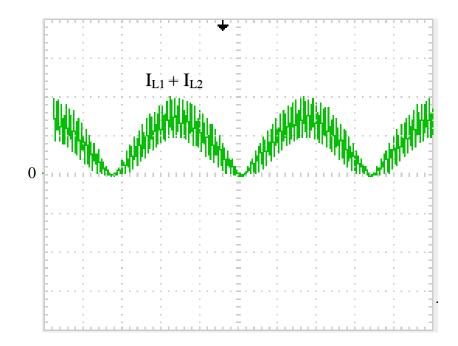

| Fig. 5.2. Input inductors currents (I <sub>L</sub> : 5 A/div, $t= 5 \mu s/div$ )                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 5.3. Interleaved current of $I_{L1}$ and $I_{L2}$ ( $I_L$ : 5 A/div, t= 5 ms/div)                                                                    |

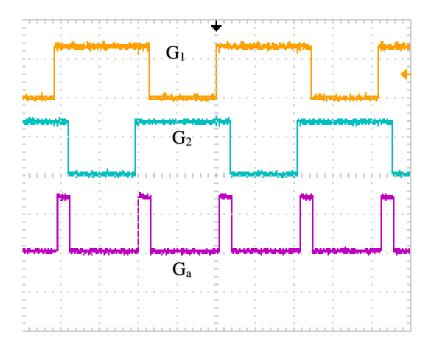

| Fig. 5.4. Gating signals of the main and auxiliary switches (V: 20 V/div, t = 5 $\mu$ s/div) 72                                                           |

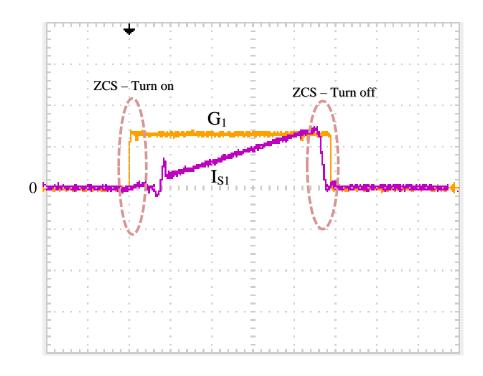

| Fig. 5.5. Main switch S1 gating signal and current waveforms $G_1$ , $I_{S1}$ ( $I_{S1}$ : 5 A/div, t= 2.5 $\mu$ s/div)                                   |

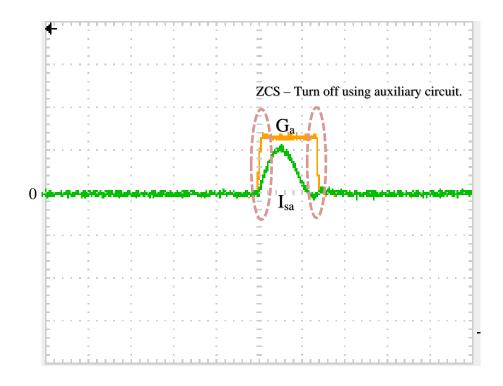

| Fig. 5.6. Auxiliary switch gating signal and current waveforms $G_a$ , Isa (I <sub>Sa</sub> : 10 A/div, t= 1 $\mu$ s/div)                                 |

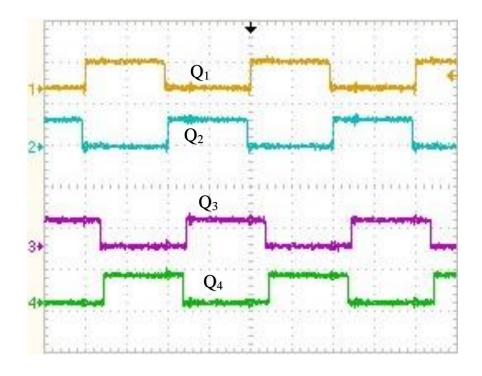

| Fig. 5.7. Gate signals for switches $Q_1$ , $Q_2$ , $Q_3$ , and $Q_4$ ( $V_{bus}$ : 20V/div, $t = 5 \mu s/div$ )                                          |

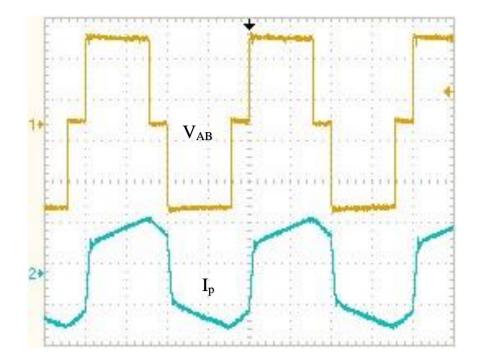

| Fig. 5.8. Transformer primary current and voltage waveforms of the DC-DC full-bridge converter ( $V_{AB}$ : 200V/div, $I_p$ : 2 A/div, t = 5 $\mu$ s/div) |

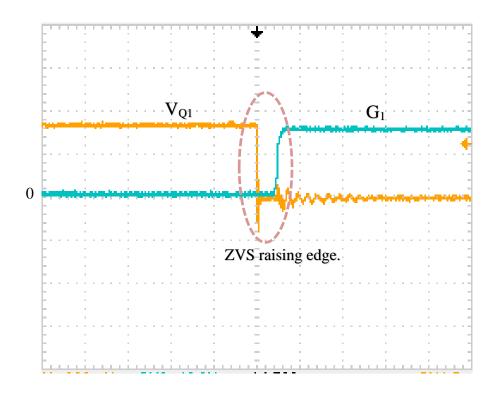

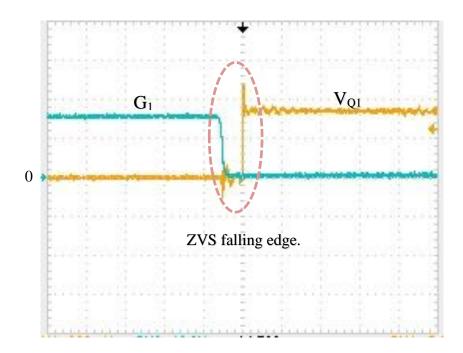

| Fig. 5.9. voltage and the gating signal of the switch $Q_1$ at rising edge (V <sub>bus</sub> : 20V/div, t = 5 $\mu$ s/div)                                |

| Fig. 5.10. voltage and the gating signal of the switch $Q_1$ at falling edge. (V <sub>bus</sub> : 20V/div, t = 5 $\mu$ s/div)                             |

| Fig. 5.11. Efficiency of the proposed converter vs load power                                                                                             |

# Acronyms

| AC     | Alternative Current                               |

|--------|---------------------------------------------------|

| DC     | Direct Current                                    |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| IGBT   | Insulated Gate Bipolar Transistor                 |

| BJT    | Bipolar Junction Transistor                       |

| ZCS    | Zero Current Switching                            |

| ZVS    | Zero Voltage Switching                            |

| ССМ    | Continuous Current Mode                           |

| DCM    | Discontinuous Current Mode                        |

| PFC    | Power Factor Correction                           |

| RMS    | Root Mean Square                                  |

| PWM    | Pulse Width Modulation                            |

| KCL    | Kirchhoff's Current Law                           |

| KVL    | Kirchhoff's Voltage Law                           |

| DPT    | Direct Power Transfer                             |

| HF     | High Frequency                                    |

# Abbreviations

| C <sub>f</sub>   | Output Capacitor                             |

|------------------|----------------------------------------------|

| Cr               | Resonant Capacitor                           |

| $C_{dc\_link}$   | Dc Link Capacitor                            |

| C1               | Intrinsic Capacitor of the Switch Q1         |

| C <sub>2</sub>   | Intrinsic Capacitor of the Switch Q2         |

| C <sub>3</sub>   | Intrinsic Capacitor of the Switch Q3         |

| C <sub>4</sub>   | Intrinsic Capacitor of the Switch Q4         |

| $C_{\text{lag}}$ | Parallel-connected capacitor for lagging leg |

| Clead            | Parallel-connected capacitor for leading leg |

| D <sub>T1</sub>  | Rectifier diode 1 of the HF transformer      |

| D <sub>T2</sub>  | Rectifier diode 2 of the HF transformer      |

| D <sub>R1</sub>  | Antiparallel Diode of the Switch Q1          |

| D <sub>R2</sub>  | Antiparallel Diode of the Switch Q2          |

| D <sub>R3</sub>  | Antiparallel Diode of the Switch Q3          |

| D <sub>R4</sub>  | Antiparallel Diode of the Switch Q4          |

| D <sub>x1</sub>  | Auxiliary Transformer Diode 1                |

| D <sub>x2</sub>  | Auxiliary Transformer Diode 2                |

| D <sub>a3</sub>  | Auxiliary Diode 3                            |

| Dal              | Auxiliary Diode 1                            |

| D <sub>a2</sub> | Auxiliary Diode 2                                |

|-----------------|--------------------------------------------------|

| D <sub>1</sub>  | Main Diode 1                                     |

| $D_2$           | Main Diode 2                                     |

| $L_1$           | Main Inductor 1                                  |

| L <sub>2</sub>  | Main Inductor 2                                  |

| L <sub>r1</sub> | Resonant Inductor 1                              |

| L <sub>r2</sub> | Resonant Inductor 2                              |

| L <sub>r</sub>  | Resonant Inductor in the Full Bridge Converter   |

| $L_{\rm f}$     | Output Inductor                                  |

| $L_{fp}$        | Output Filter Inductance Referred to the Primary |

| Tr              | High Frequency Transformer                       |

| T <sub>x</sub>  | Auxiliary Transformer                            |

| $S_1$           | IGBT Main Switch 1                               |

| $S_2$           | IGBT Main Switch 2                               |

| Sa              | IGBT Auxiliary Switch                            |

| Q1              | MOSFET Switch 1                                  |

| Q2              | MOSFET Switch 2                                  |

| Q3              | MOSFET Switch 3                                  |

| Q4              | MOSFET Switch 4                                  |

| V <sub>in</sub> | Input Voltage                                    |

| Vo                    | Output Voltage                           |

|-----------------------|------------------------------------------|

| V <sub>rec</sub>      | Rectified Voltage                        |

| V <sub>pri</sub>      | Primary Voltage of the HF Transformer    |

| V <sub>bus</sub>      | Bus Voltage                              |

| V <sub>bus_min</sub>  | Minimum Bus Voltage                      |

| $V_{\mathrm{f}}$      | Diode Rectifier Forward Voltage          |

| V <sub>in</sub>       | Input Voltage                            |

| Ν                     | High Frequency Transformer Turns Ratio   |

| N <sub>x</sub>        | Auxiliary Transformer Turns Ratio        |

| N <sub>pri</sub>      | Primary Turns Ratio of the Transformer   |

| N <sub>sec</sub>      | Secondary Turns Ratio of the Transformer |

| i <sub>p</sub>        | Primary Current of the HF Transformer    |

| I <sub>critical</sub> | Critical Current                         |

| I <sub>in</sub>       | Input Current                            |

| I <sub>s1</sub>       | Current through the Main Switch S1       |

| I <sub>s2</sub>       | Current through the Main Switch S2       |

| I <sub>sa</sub>       | Current through the Auxiliary Switch Sa  |

| Io                    | Output Current                           |

| D                     | Duty Cycle of the Main Switches          |

| Po                    | Output Power                             |

| Deff           | Effective Secondary Duty Cycle                 |

|----------------|------------------------------------------------|

| R              | Output Resistive Load                          |

| R'             | Output Resistive Load Reflected to the Primary |

| T <sub>h</sub> | Hold-up Time                                   |

# Chapter 1

# 1 Introduction

## 1.1 Introduction to power electronics

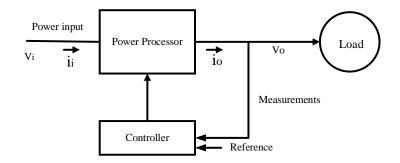

Power electronics involves the study of electronic circuits that convert power from an input source to meet the requirements of an output load, using power semiconductor devices along with passive elements such as capacitors, inductors, transformers. A feedback controller is used to compare the power output unit with a reference value, and the controller minimizes the error between the two, as shown in the block diagram in Fig. 1.1 [1]. The focus of this thesis is on a two-stage AC-DC converter topology. This proposed converter is comprised of two main converters, the first stage is an AC-DC interleaved boost converter, and the second stage is a DC-DC full bridge converter.

In this chapter, basic power electronic concepts which describe the technical background of this thesis will be discussed, and a literature review of previous works is performed, then the objectives of the thesis are explained.

Fig. 1.1. Block diagram of a power electronic system

#### 1.2 Power electronic devices

There are several types of power semiconductor devices that can be used in power converters. In this section, three types are briefly reviewed: diodes, metal-oxide-silicon field-effect transistors (MOSFETs) and insulated-gate bipolar transistors (IGBTs).

#### 1.2.1 Diodes

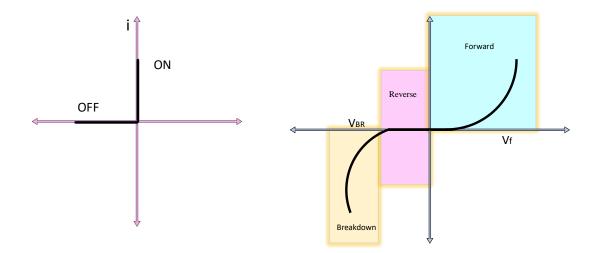

The behavior of the semiconductor diode in a circuit is given by its linear and non-linear current-voltage characteristics as shown in Fig. 1.2(a), and Fig 1.2(b), respectively. As it can be seen from the ideal characteristic in Fig. 1.2(a), an ideal diode conducts only positive current, and no negative current can flow through it.

A non-ideal diode has a non-linear characteristic that can be divided into three regions: the forward-biased region, the reverse-biased region, and the breakdown region. Current flows through the device between anode and cathode when it is forward-biased, when the voltage between its anode and cathode tries to exceed its forward voltage drop, which is typically about 0.7 V.

When a positive current flows through a non-ideal diode, there is a voltage drop of about 0.7 V between anode and cathode. The amount of forward voltage drops changes slightly the current through the device is increased. When voltage is applied between the diode's cathode and anode, no current flows through the device except for a very small amount of leakage current. The device enters the breakdown region if the voltage placed across the cathode and the anode exceeds the voltage rating of the device [2].

Fig. 1.2. Diode characteristics: (a) idealized i-v characteristic: (b) actual i-v characteristic

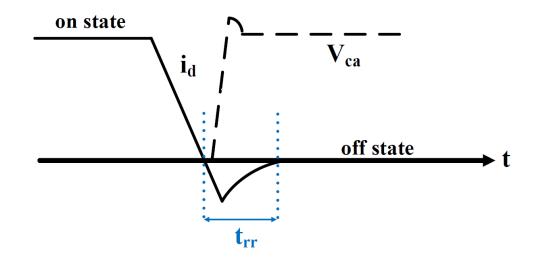

It is possible for current to flow in the reverse direction, from cathode to anode, in a nonideal diode, as can be seen in Fig. 1.3. This can happen when the diode is in the process of turning off. In a non-ideal diode, the current flowing through it falls to zero, then becomes negative, temporarily, as it is trying to turn off. Eventually, the device does turn off and the current becomes zero. This negative current is defined as reverse recovery current and has a duration of  $t_{rr}$  [2]. This current increases switching losses and it increases peak current stresses in other converter components as well.

Fig. 1.3. Reverse recovery current of a diode [1]

#### 1.2.2 The metal-oxide-silicon field-effect transistor (MOSFET)

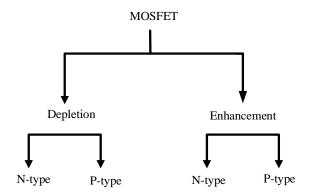

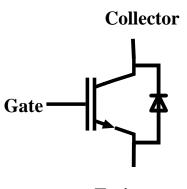

The MOSFET is a voltage-controllable device with fast switching response and minimal drive requirements due to its insulated gate. It has four terminals: gate (G), body (B), source (S), and drain (D), with the body connected to the source to reduce the number of terminals to three. Its operation can be controlled by the voltage between its gate and source. There are four types of MOSFETs as shown in Fig. 1.4. MOSFETs can be enhancement type with positive gate-source voltages or depletion type with negative gate-source voltages, n-type or p-type, as with bipolar junction transistors (BJTs). Fig. 1.5 shows a circuit symbol of a n-type enhancement MOSFET, which is by far the most commonly used MOSFET used in power electronics [3].

Fig. 1.4. Classification of MOSFET

Fig. 1.5. Circuit symbol of an N-Channel power MOSFET

MOSFETs have three regions of operation: the cut-off region, the linear/triode region, and the saturation region. When operating in the cut-off region, a MOSFET is like an open circuit with no current flowing through it, it is off. When operating in the linear/triode region, a MOSFET acts like a voltage-controlled resistor and current flows through it, from drain to source. When operating in the saturation region, a MOSFETs acts like a closed switch with a small drain-source resistance between its drain and its source. When a MOSFET is operating in the saturation region, its equivalent circuit can be considered to be a small drain-source resistance. When it is off, its equivalent circuit can be considered to be a small, drain-source capacitance. MOSFETs are always operated in the saturation region when used in power converters. It should be noted that real-life MOSFETs have an anti-parallel diode connected between their source and drain. This diode is very useful in many power electronics applications.

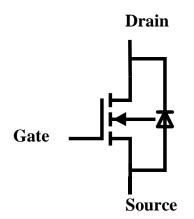

#### 1.2.3 Insulated-gate bipolar transistor (IGBT)

Fig. 1.6 shows a circuit symbol of an IGBT. The device has three terminals: collector (C), emitter (E), and gate (G). An IGBT is essentially a combination of a MOSFET and a BJT as it has the gate of a MOSFET, but the body of a BJT. An IGBT requires minimal gate current as its gate is insulated, like a MOSFET, and it has a fixed voltage drop, called the saturation voltage, between its collector and emitter, like a BJT. IGBTs do not have the switching speeds of MOSFETs but have a lower collector-emitter drop when higher currents flow through them. In general, MOSFETs are used in lower power converters and IGBTs are used in higher power converters.

The following should be noted about IGBTs:

- They have a current-tail when they are turned off. In other words, the current in an IGBT does not fall to zero quickly when it is turned off but falls gradually. This current tail limits the speed of IGBTs and creates switching losses as well, as will be explained later in this chapter.

- IGBTs typically have anti-parallel body diodes like MOSFETs. For some applications, however, this body-diode needs to be blocked, thus IGBTs with series diodes that block the anti-parallel diode are commercially available for high power applications.

Emitter

Fig. 1.6. Circuit symbol of an IGBT with an anti-parallel diode

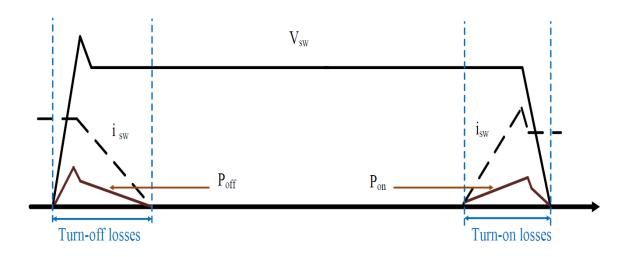

## 1.3 Switching losses

Non-ideal power semiconductor devices such as MOSFETs and IGBTs have conduction losses and switching losses. As discussed above, MOSFETs have an equivalent drain-source resistance when they are on and IGBTs have a fixed voltage drop when they are on. Conduction losses are generated when these devices conduct current. Switching losses are generated when these devices are turned on and off as there is overlap between voltage and current during switching transitions, as shown in Fig. 1.7. Given that power is related to the product of voltage and current, this overlap of voltage and current creates power losses in MOSFETs and IGBTs.

Fig. 1.7. Typical switch voltage and current waveforms

## 1.4 Soft switching

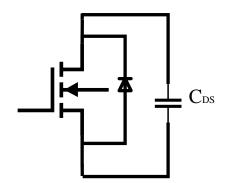

Power converters operating with high switching frequencies will have considerable switching losses unless something is done to reduce their switching losses. Switching losses can be reduced if either the voltage or current of a switching device is made zero at the time that a switching transition takes place. This can be done with either zero-voltage switching (ZVS) where the voltage across the switching device is zero during switching transitions [4] - [7] or zero-current switching (ZCS) methods when it is the current that is zero [8] - [11]. Both methods are classified as being soft-switching methods as the switching transition is gradual and considered to be "soft", as opposed to conventional hard-switching where no such methods are used, and the switching transitions are sudden.

Due to the nature of the devices, ZVS is preferred for MOSFETs and ZCS is preferred for IGBTs. MOSFETs have larger drain-source capacitances than IGBTs, which makes ZVS preferable for MOSFETs while IGBTs have a current-tail when they turn off, which makes ZCS preferable.

A typical implementation of ZVS for MOSFETs is shown in Fig. 1.8. A ZVS turn-on is achieved by injecting current through the body-diode of the device before it is turned on. This clamps the voltage across the device to zero (one forward voltage drops, typically about 0.7 V) so that when the device is turned on, it is done with zero voltage across it. A ZVS turn-off is achieved by having a capacitor connected across the device, as shown in Fig. 1.8 This capacitor slows down the rate of voltage rise across the device when it is turned off so that the overlap between voltage and current is reduced during this switching transition. This reduction of overlap between the voltage and current results in lower power dissipation and thus fewer losses. The amount of capacitance that is used depends on the applications, additional capacitance must be added externally across the device.

Fig. 1.8. ZVS implementation for MOSFETs

A typical application of ZCS for IGBTs is shown in Fig. 1.9. A ZCS turn-on is achieved by placing an inductor in series with the switching device. This inductor slows down the rate of rise of current in the device when it is turned on, this reducing the overlap between voltage and current during turn-on switching transitions. A ZCS turn-off is achieved by the gradual removal of current from the device before it is turned off. This can be done by the natural operation of the rest of the power converter, by providing an alternative path for current to flow through, a path with lower voltage potential, or by reversing the polarity of voltage across the switch-inductor combination. ZCS operation helps eliminate the turn-off current tail in IGBTs during turn-off switching transitions, which reduces the losses that the current tail would cause otherwise [12].

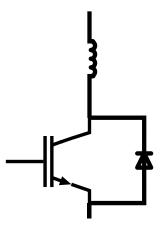

Fig. 1.9. ZCS implementation for IGBTs

# 1.5 AC-DC converters

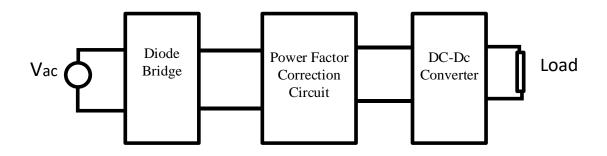

AC-DC converters convert an AC input voltage into a DC voltage. The input may be obtained from the utility grid or an AC generator. The term "AC-DC converter" can refer to a single AC-DC converter module [13] or to a two-stage converter [14] that has an AC-DC front-end converter followed by a second converter, a DC-DC converter that converts the output of the front-end converter into a DC output voltage, as shown in Fig. 1.10. A two-stage approach is used when the output voltage must be low (e.g., 5-48 V) or isolation is needed between the input and output voltages [15].

Fig. 1.10. Block diagram of a standard two-stage AC-DC converter

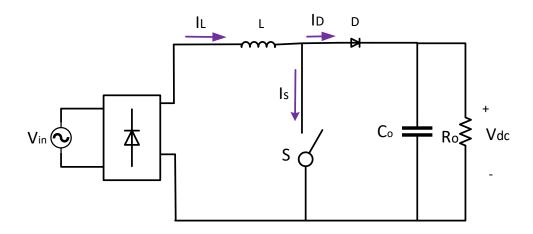

The most popular AC-DC option is some sort of boost converter that performs power factor correction (PFC) to meet the regulatory agency requirements on harmonic content [16]-[18], such as the one shown in Fig. 1.11. PFC is performed by shaping the input current that is drawn from the input AC source so that it is sinusoidal and in phase with the input voltage. The power factor of unity represents the most efficient use of power from the source.

The basic operation of a boost converter can be described as follows: When the switch is turned on, energy is placed in the input inductor and the current flowing through the inductor rises. When the switch is turned off, the energy that was stored in the inductor is transferred to the output and its current falls. The output of the converter depends on the width of the gating signal pulse or the width of the on-time of the switch so that boost converters are operated with pulse-width modulation (PWM) control.

Boost converters can operate in either continuous current mode (CCM) [19] or discontinuous current mode (DCM) [20]. When a boost converter is operated in CCM, a controller varies the converter's duty cycle (D), defined as the ratio of switch on-time  $T_{on}$  to switching cycle period  $T_s$  as follows:

$$D = \frac{T_{on}}{T_s}$$

(1-2)

The input current can be shaped to be a sine wave with some ripple current and is never zero except when its polarity changes from positive to negative. When a boost converter is operated with DCM, the converter's duty cycle is fixed throughout the input line cycle. The current starts from zero when the switch is turned on then falls back to zero after the

switch is turned off, some time before the start of the next switching cycle. The input current is a series of triangular pulses whose peak follows a sine wave. This current can be filtered to produce a sinusoidal input current with a converter power factor of unity.

Fig. 1.11. AC-DC boost converter

# 1.6 Interleaved AC-DC boost converters

The input inductor of an AC-DC boost converter filters the high-frequency AC ripple current to make the input current as purely sinusoidal as possible. If the input inductor is large, then the input current ripple can be reduced, but such an inductor adds size and weight to the converter. If the input inductor is small, as is the case when the boost converter is operating in DCM, then the ripple current is large and power factor is reduced.

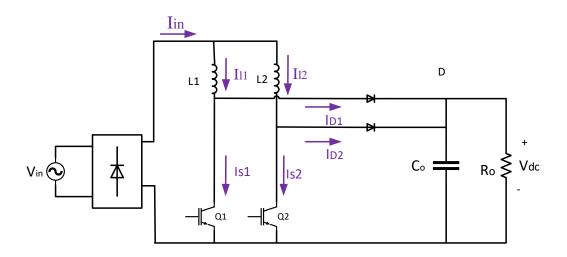

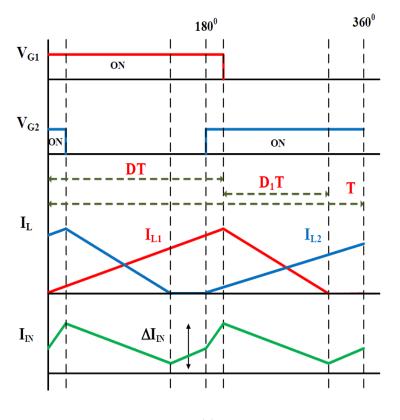

A common way to reduce input current AC ripple is to implement the boost converter with interleaving, as shown in Fig. 1.12. Interleaving in AC-DC boost involves the use of two or more individual boost converter modules connected in parallel. The switch in each boost converter module has the same duty cycle as those of the other switches, but its gating signal is phase-shifted relative to those of the other switches [21]-[24]. In the case of the interleaved converter shown in Fig. 1.12, the two switches have the same gating signals, but they are 180 degrees out of phase. Typical waveforms are shown in Fig 1.13 for the case when the switches are operating with D > 0.5 and D < 0.5.

Fig. 1.12. Topology of a basic AC-DC interleaved boost converter

Although interleaved boost converters are implemented with multiple sets of boost converter switches and diodes, which makes them more expensive than a single boost converter module, they have several advantages [25]:

- They produce less input ripple.

- The net size and weight of their input inductance is lower than the input inductor of a single boost converter module.

- Power is processed by multiple modules instead of one, which reduces the stress of the converter components. This allows the converter to operate at higher power levels or cheaper components with lower current ratings can be used to offset somewhat the cost of additional components.

- Since the converter modules operate in discontinuous current mode, their switches can be turned on with ZCS as the current flowing in a module is zero at the start of a switching cycle.

Fig. 1.13. Inductor current waveforms according to the switching pattern in DCM [26] (a) D > 0.5 (b) D < 0.5

# 1.7 DC-DC full bridge converter

The DC-DC converter in a two-stage AC-DC converter is typically a flyback or forward converter for low power applications or a full-bridge converter for higher power applications (> 500 W). Since a DC-DC full-bridge converter will be used in the converter proposed in this thesis, its basic structure and operation are discussed in this section. Its topology is shown in Fig. 1.14.

A full bridge DC-DC converter [27]-[32] consists of four switches  $S_{1-4}$  that can be either MOSFETs or IGBTs. These switches are turned on using an appropriate sequence so that an AC square voltage is generated across the primary of the transformer. A high-frequency (HF) transformer is used to step down the primary to the required voltage of the output; it also provides isolation between input and output. The AC square voltage from the transformer is processed by a diode bridge rectifier, which rectifies it, and the result is fed to an output low pass filter to mitigate AC harmonics so that a DC output voltage is produced. Details of how a full-bridge converter is operated are explained in later chapters of this thesis.

Fig. 1.14. DC-DC full bridge converter

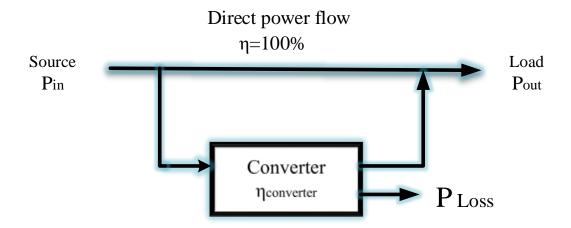

# 1.8 Partial power processing

One issue that two-stage AC-DC converters have is that any input power that is transferred to the output must be processed twice, once by each converter. Since neither the AC-DC front-end converter nor the DC-DC back-end converter are ideal, this means that either converter produces losses as it performs power converter. Overall converter efficiency can be improved if, somehow, some of the input power can be processed by only one converter then fed directly to the load, thus bypassing the second converter. This type of operation is referred to as partial power processing in literature.

Partial power processing methods have been developed for various types of converters. The general principles of partial power processing can be seen in the block diagram shown in Fig. 1.15. The basic idea is that instead of a converter processing the full power that is fed to it, the converter processes a portion of this power with the remaining power fed directly to the output [33]. Partial power processing methods have been shown to be effective in increasing overall converter efficiency, but they are not often used because of limits in converter topology structures. Only some topologies can be implemented with partial power processing [34]-[38].

Fig. 1.15. Concept of power flow in a partial power converter

# 1.9 Literature review

The converter that is proposed in this thesis is a two-stage AC-DC converter. Since the second-stage converter is a conventional DC-DC full-bridge converter, the focus of the literature review presented in this section is on the AC-DC front-end converter. The front-end converter can be implemented with MOSFETs and ZVS or with IGBTs and ZCS. Given that the current flowing in the converter is not insignificant and that an interleaved approach with DCM operation that ensures that the converter switches are turned on with ZCS will be used, interleaved ZCS-PWM boost converters are emphasized in this literature review.

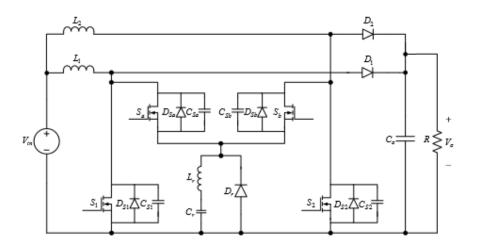

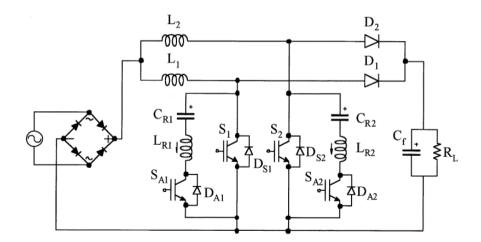

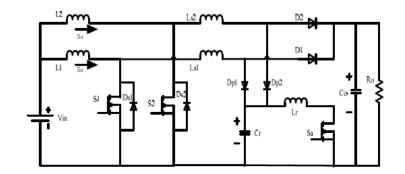

Several ZCS-PWM interleaved boost converters are shown in Fig. 1.16-1.20 [39] - [42], [26]. These converters have at least one of the following drawbacks:

- They use an auxiliary circuit to help the main switch of an AC-DC boost converter module operate with ZCS. This means that an interleaved boost converter made up of two converter modules needs two auxiliary circuits with two auxiliary switches, which increases the cost of the converter.

- The auxiliary circuit is a resonant circuit. Whenever it is activated, time is needed for the circuit to go through a resonant cycle before it is deactivated. The greater the amount of time that the circuit needs to be active, the greater its RMS current stress becomes, thus increasing the stresses and the losses of the converter.

- The auxiliary circuit components are in the main power path of the circuit instead of being in an auxiliary circuit that is parallel to the main power circuit. This increases auxiliary circuit component stresses and losses.

- There is no path for energy in the auxiliary circuit to be transferred to the output. As a result, this energy is trapped in the auxiliary circuit and dissipated, which creates power losses and limits the amount of power that the converter can process.

- The auxiliary circuit injects current into the main power switches. This is the case when the auxiliary circuit is some sort of resonant circuit. This additional current increases the peak current stress of the main switches so that they must be implemented with higher current-rated, more expensive components.

Fig. 1.16. Two-phase interleaved boost converter with soft switching [39]

Fig. 1.17. Breadboarded interleaved ZCT boost converter [40]

Fig. 1.18. Interleaved ZCS boost converter [41]

Fig. 1.19 ZCS interleaved bidirectional DC-DC Converter [42]

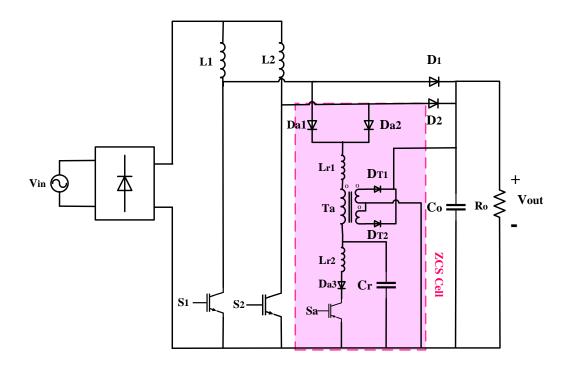

An interleaved AC-DC ZCS-PWM boost converter that does not have these drawbacks was proposed in [26]; the converter is shown in Fig. 1.20. A key feature of this converter is that it has a transformer in its auxiliary circuit. The secondary of this transformer is connected to the output of the converter. The main idea of this thesis is to use this converter as the front-end converter and connect the secondary of the auxiliary circuit transformer to the output of the whole two-stage converter instead of the output of the AC-DC converter, which is connected to the intermediate DC link. This connection allows some of the input power to be processed only by one converter instead of two converters, thus, presumably, reduce the overall losses of the converter.

# 1.10 Thesis objectives

The main objectives of this thesis are as follows:

- To propose a new two-stage AC-DC converter with the interleaved ZCS-PWM converter proposed in [26] as the first-stage converter and a conventional DC-DC full-bridge converter as the second-stage converter and investigate the effect to using the auxiliary circuit transformer for the first-stage converter to allow some of the input power to be processed by only one converter.

- To determine the steady-state characteristics of this converter by performing a mathematical analysis of the converter's modes of operation.

- To develop a procedure that can be used to design the converter. This procedure can be used to determine key converter component values and parameters that can be used in the implementation of a prototype of the converter.

- To confirm the feasibility of the converter and the effectiveness of its partial power processing ability with results obtained from an experimental prototype of the converter.

# 1.11 Thesis outline

The outline of this thesis is organized as follows:

In Chapter 2, a novel two-stage AC-DC power converter consisting of an interleaved AC-DC boost converter module that can perform power factor correction and a DC-DC full bridge converter that steps down the output voltage and provides isolation using a high frequency is proposed. The first-stage converter has an auxiliary circuit with a small-size transformer that allows all its switches to operate with ZCS and that can be used to improve the total efficiency. In this chapter, the operation of the proposed converter is explained, and its features will be described.

In Chapter 3, a steady-state analysis of the operation of the proposed converter is performed. Mathematical equations for each mode of steady-state operation are derived. These equations are the basis of the design procedure that is developed in the next chapter.

In Chapter 4, graphs of steady-state characteristic curves that can be used for design purposes are generated using MATLAB software, according to the steady-state equations derived in the previous chapter. Using these graphs and the steady-state equations, a procedure for the design of key converter components and parameters is developed and the procedure is demonstrated with an example. The results of the design example were used to implement an experiment prototype of the proposed converter.

In Chapter 5, experimental results that demonstrate the feasibility of the proposed converter are presented. The efficiency of the proposed two-stage converter is compared to that of a two-stage converter without direct power transfer.

In Chapter 6, the content of this thesis is summarized, and the conclusions and contributions of this thesis are presented, along with suggestions for future work.

# Chapter 2

# 2 A novel two-stage AC-DC power converter with partial single-stage power processing

# 2.1 Introduction

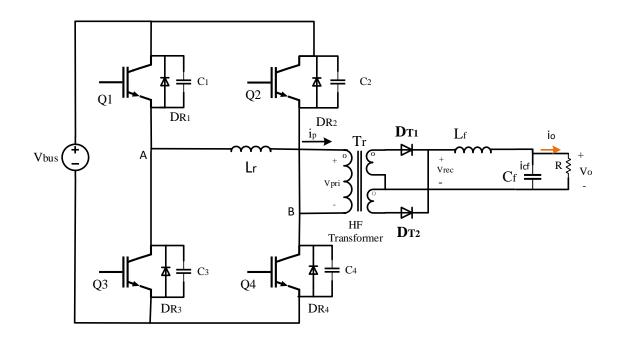

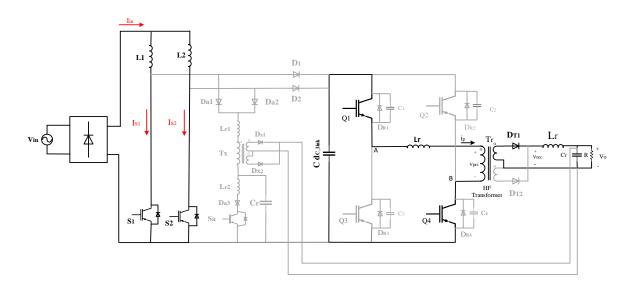

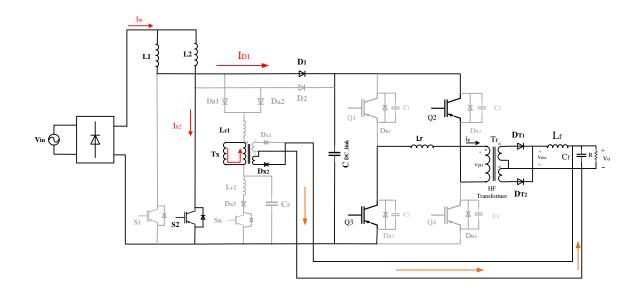

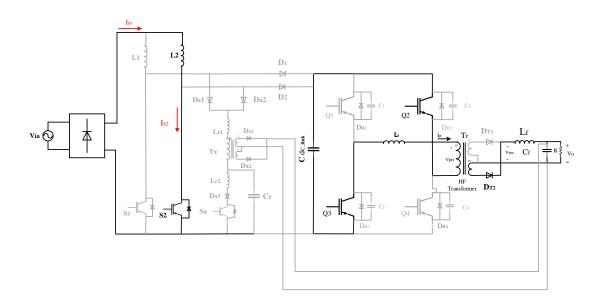

The two-stage AC-DC converter proposed in this thesis is shown in Fig. 2.1. The proposed converter consists of an interleaved ZCS-PWM AC-DC boost converter with an auxiliary circuit in the first stage that operates with power factor correction and soft-switching and a ZVS-PWM full-bridge DC-DC converter that steps down the DC link voltage to the desired output voltage and provides isolation using a high-frequency transformer. Power is processed first by the AC-DC converter, then by the DC-DC converter. The soft-switching techniques used in the converters are different as their operating conditions are different. IGBTs are used in the first stage because of the high currents that flow through its converter switches, which can generate conduction losses. Since IGBTs are used, the soft-switching method that is used is ZCS, as explained in the previous chapter. MOSFETs are used in the second stage because the current that flows through their switches is relatively low. Since MOSFETs are used in this converter, the soft-switching method that is used for the full-bridge converter is ZVS, as explained in the previous chapter.

All input power that is transferred to the output in a two-stage AC-DC converter is generally processed by both converter stages. Given that each converter stage is non-ideal, each stage processes power with less than 100% efficiency. The basic premise of this thesis is that converter efficiency can be improved if some of the input power is transferred directly from the first converter to the output, thus being processed only once. In the proposed converter, some input power is transferred to the output through the auxiliary circuit of the first-stage converter.

In this chapter, the AC-DC first-stage converter and the DC-DC second-stage converter are described, and their general operating principles are explained. The modes of operation of the overall two-stage converter are then presented and the features of the converter are stated.

Fig. 2.1. Proposed two-stage AC-DC power converter with Direct Power Transfer (DPT)

## 2.2 AC-DC interleaved ZCS-PWM boost converter

The first-stage of the proposed AC-DC converter, shown in Fig. 2.1, consists of two boost converter modules: one with  $L_1$ ,  $S_1$  and  $D_1$ , the other with  $L_2$ ,  $S_2$  and  $D_2$ . The gating signals of the two main switches,  $S_1$  and  $S_2$  are identical, but shifted 180° with respect to each other. The currents in  $L_1$  and  $L_2$  are discontinuous and identical, but also shifted 180° with respect to each other.

The two boost modules are connected to the same auxiliary circuit, which consists of: connection diodes  $D_{a1}$  and  $D_{a2}$ , reverse blocking diode  $D_{a3}$ , inductors  $L_{r1}$  and  $L_{r2}$ , capacitor  $C_r$ , and center tap feed forward transformer  $T_x$  which has two diodes  $D_{x1}$  and  $D_{x2}$ . The auxiliary circuit is activated whenever a main switch is about to be turned off and its switch can be turned on and off with ZCS as well. The auxiliary circuit allows the converter to operate without an increase in the peak current or the voltage stresses of the main switches as it does not add current to the main switch and does not affect the peak voltage of these devices. The auxiliary switch in the converter is active for a much shorter time than in most other ZCS-PWM converters. This allows the converter to operate at higher power levels than other previously proposed interleaved ZCS-PWM converters with a single auxiliary switch as it is active for only a fraction of the switching cycle. AC-DC converters that operate with input power factor correction (PFC) and consist of two or more interleaved boost converter modules are popular in industry. PFC is required in modern AC-DC converters as their input current must meet harmonic standards set by regulatory agencies. With interleaving, the input current of each module can be made to be discontinuous, and the size of their input inductors reduced. Interleaving can reduce the high ripple in each module and produce a net input current with a ripple that is comparable to that achieved by a single boost converter module with a large input inductor. Moreover, there is less current stress on the converter components because they each handle a fraction of the overall current and the control is easier as the more sophisticated control methods required for continuous current mode (CCM) operation are avoided. The AC-DC interleaved boost converter that is used in this thesis is shown in Fig. 2.2.

**Auxiliary Circuit**

Fig. 2.2. Front-end interleaved AC-DC ZCS-PWM boost converter.

## 2.3 PWM full-bridge converter

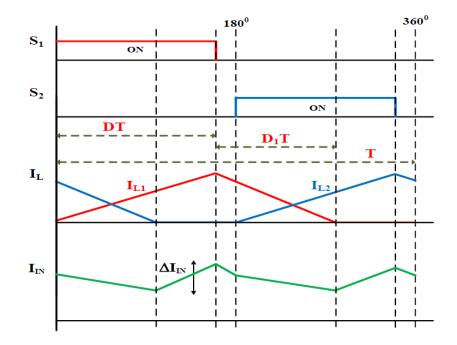

The DC-DC full-bridge converter, shown in Fig. 2.3, is the converter that is most often used for applications when DC-DC power converter greater than 500 W is needed. This converter takes the voltage from the first AC-DC converter stage, typically about 400 V and converts to a lower DC voltage, typically 5-48 V DC [43]- [45]. The converter has four switches,  $Q_1$ ,  $Q_2$ ,  $Q_3$  and  $Q_4$  in two legs, with two switches each, a high frequency power transformer T, diode rectifier  $D_{T1}$ ,  $D_{T2}$  and an output filter that consists of an inductor  $L_f$  and a capacitor  $C_f$ . The four switches transform a DC input voltage to a square wave voltage that is stepped down by the transformer, then rectified by the output diode rectifier at the secondary side.

Fig. 2.3. DC-DC full bridge converter

There are generally two types of PWM methods by which the DC-DC converter can operate. In the first method, basic PWM as shown in Fig. 2.3, diagonally opposed switches  $Q_1$  and  $Q_4$  or  $Q_2$  and  $Q_3$  are turned on and off simultaneously. When diagonally opposed switches are on, the input DC voltage is impressed across the transformer primary with the voltage polarity depending on the switch pair that is on. The transformer primary voltage becomes zero when all the switches are off. The transformer voltage is rectified by the

secondary diodes, then filtered to produce the output DC voltage. This output voltage is dependent on the width of the square pulses of the transformer primary voltage waveform – as the output voltage increases as the square voltage pulses are made larger, or the zero voltage states are made smaller. Maximum output voltage can be achieved when the transformer primary voltage is a square wave with no zero voltage states. The output voltage is zero when the primary voltage is always zero.

At the secondary side, when switches  $Q_1$  and  $Q_4$  are conducting, the voltage across the transformer primary is stepped up or down (generally down) and secondary rectifier diodes  $D_{T1}$  conducts. The secondary rectified voltage  $V_{rec}$  is equal to  $V_{bus}/N$ , where N is the transformer primary-to-secondary-winding-turns ratio. This voltage, minus the output voltage, is applied across the output filter inductor  $L_f$ , causing the inductor current  $I_{Lf}$  to increase linearly. The primary current  $i_p$  is equal to the output filter inductor current reflected to the primary side, and correspondingly it increases linearly.

When switches  $Q_2$  and  $Q_3$  are conducting, the converter operates in the exact same manner as it does when switch  $Q_1$  and  $Q_4$  are on except that secondary diode  $D_{T2}$  conducts instead of  $D_{T1}$ . When all the power switches are off, the primary current  $i_p$  is zero and the output filter inductor current freewheels through the two rectifier diodes as the transformer secondary voltage is zero.

The second PWM method used to operate the DC-DC full-bridge converter is phase-shift PWM. With this method, the width of all the gating signals is fixed to be about 50% of the switching cycle. The gating signals of the switches in each converter leg,  $Q_1$  and  $Q_3$  or  $Q_2$  and  $Q_4$ , are complementary to each other with both switches in a leg never being on at the same time. A small dead time when neither switch in a leg is on is implemented to give time for one switch in a leg to be fully off before its complementary switch is turned on, to avoid the possibility of a short-circuit.

The output voltage is adjusted by shifting the gating signals of one leg relative to those of the other. Voltage is impressed across the transformer whenever a pair of diagonally opposed switches is on. No voltage is impressed across the transformer and a zero-voltage state occurs whenever two top switches,  $Q_1$  and  $Q_2$  or two bottom switches,  $Q_3$  and  $Q_4$  are

on. The converter is said to be in a freewheeling mode of operation when two top switches or two bottom switches are on as current in the transformer circulates in the primary. The leg with the switches that put the converter in a freewheeling mode of operation when they are turned on is generally referred to as the leading leg, while the leg with the switches that put the converter out of a freewheeling mode of operation is referred to as the lagging leg. It should be noted that regardless of whether the full-bridge converter is operated with basic PWM or with phase-shift PWM, the operation of the converter at the secondary side is identical.

## 2.4 Modes of operation

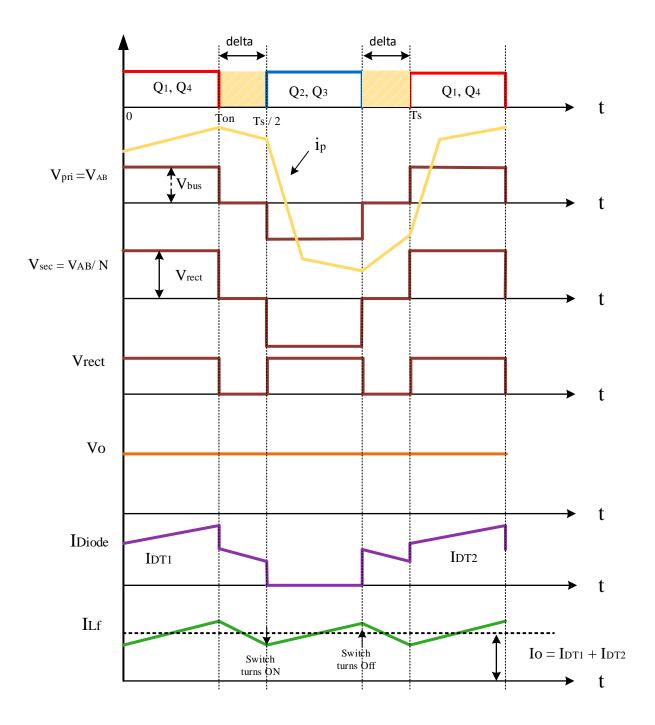

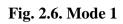

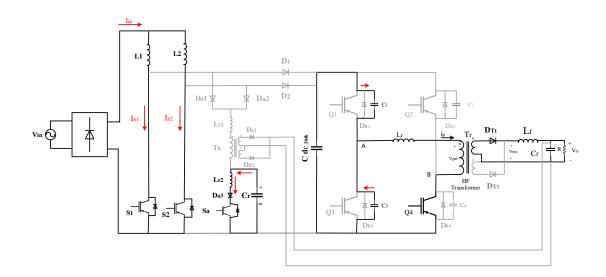

The proposed converter has the following modes of operation for a half switching cycle when duty cycle is  $D \ge 0.5$  and when  $S_2$  is turned on and  $S_1$  is turned off. Typical waveforms and circuit diagrams for these modes are shown in Fig. 2.4, Fig. 2.5 and Figs. 2.6 – 2.12 respectively.  $T_s$  in Fig. 2.5 is the period of the switching cycle.

The modes of operation for the other half-cycle when  $S_1$  is turned on and  $S_2$  is turned off are identical. The modes of operation are derived based on the following assumptions:

- Since the AC input voltage can be considered to be a DC input source in a very short amount of time, the steady-state analysis is done with DC input voltage.

- The proposed circuit has two boost modules that are designed to be operated in DCM, so the input inductor current of each one will become discontinuous. However, the input current of the converter, which is the sum of the inductor currents, should be continuous.

- The output filter capacitor (C<sub>f</sub>) is large enough to be considered as a voltage source (V<sub>o</sub>).

- All semiconductor switches are ideal with no switching or conduction losses.

- All inductors and capacitors are ideal; therefore, they have negligible resistances.

- All diodes are ideal and the reverse recovery time of each one of them is zero.

The converter's modes of operation are as follows:

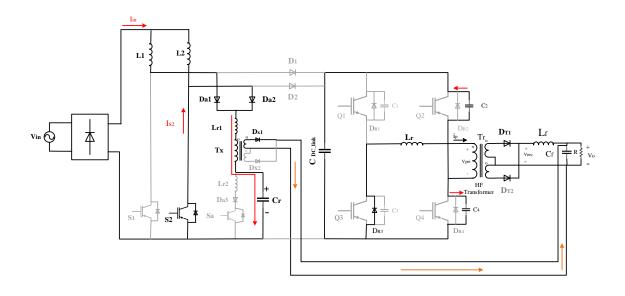

<u>Mode 1 (T<sub>0</sub> < t < T<sub>1</sub>)</u>: This mode begins when switch S<sub>2</sub> is turned on. The rectified voltage is applied to L<sub>2</sub> and the current through L<sub>2</sub> linearly increases, as does the input current in the input inductor (I<sub>in</sub>). The slope of the current is  $\frac{v_{in}}{l_2}$ . Since I<sub>in</sub> is the summation of I<sub>L1</sub> and I<sub>L2</sub>, it will increase with greater slope. Meanwhile, switches Q<sub>1</sub> and Q<sub>4</sub> of the DC-DC full-bridge converter are on, and the DC link voltage is impressed across the primary. This voltage is stepped down by the transformer, then rectified through diode D<sub>T1</sub> and fed to the output filter and the load.

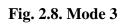

<u>Mode 2 ( $T_1 < t < T_2$ )</u>: This mode begins when the auxiliary switch ( $S_a$ ) is turned on in preparation to turn off main switch  $S_1$  with ZCS.  $S_a$  turns on with ZCS because  $L_{r2}$  limits the rise of the switch current. After  $S_a$  is turned on,  $C_r$  starts to resonate with  $L_{r2}$  so that the current in  $L_{r2}$  rises while the voltage across  $C_r$  decreases. Meanwhile, at the full-bridge converter, switch  $Q_1$  begins turned off and the process of charging the switch capacitance of  $Q_1$  and discharging that of  $Q_3$  starts.

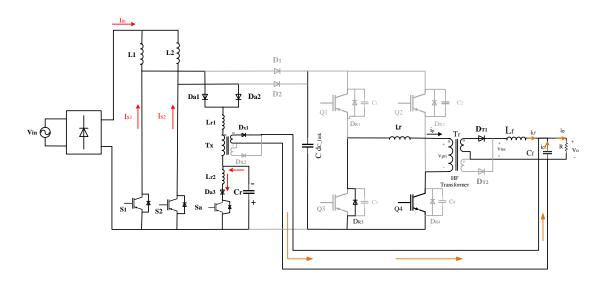

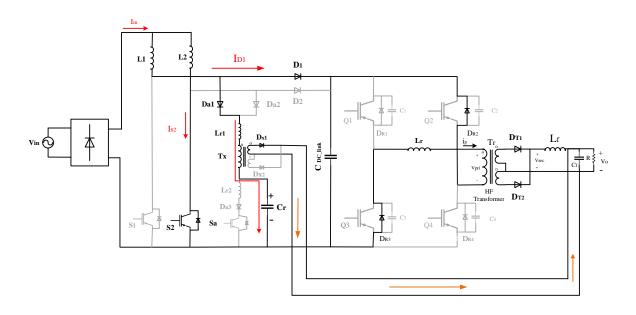

**Mode 3** ( $T_2 < t < T_3$ ): This mode begins when the voltage across  $C_r$  ( $V_{Cr}$ ) is zero. During this mode,  $V_{Cr}$  is charged to a negative voltage and  $D_{a1}$  and  $D_{a2}$  start to conduct.  $D_{x1}$  starts to conduct so that the circulating energy from the auxiliary circuit is transferred to the output during this time. The current through  $L_{r1}$  and  $L_{r2}$  decreases and goes to zero. The currents through  $S_1$  and  $S_2$  then become negative and flow through their body diodes. When this happens,  $S_1$  can be turned off with ZCS. During this mode, the current in  $L_{r2}$  reaches zero because of its resonance with  $C_r$ . Afterwards, the energy in  $L_{r1}$  is transferred to  $C_r$ , thus increasing its voltage so that  $V_{Cr}$  becomes less negative and eventually becomes positive. As the secondary side of the auxiliary circuit transformer  $T_x$  is connected to the output capacitor,  $C_f$ , a portion of power is transferred directly to the output from the auxiliary circuit.

At the full-bridge converter, the switch capacitance of  $Q_3$  has been fully discharged and current is flowing through the body-diode of the switch.  $Q_3$  can be turned on with ZVS as long as current is flowing through its body-diode.

**Mode 4 (T<sub>3</sub> < t < T<sub>4</sub>):** This mode begins when  $S_a$  is turned off with ZCS.  $V_{Cr}$  keeps increasing, so the current through  $S_2$  starts to become less negative. The negative current through body diode of  $S_2$  rises to zero, thus the auxiliary diode  $D_{a2}$  stops conducting at the end of this mode. At the full-bridge converter, the converter is in a freewheeling mode of operation and current just circulates in the primary side of the converter. At the secondary side, both output diodes conduct current as the voltage across the transformer secondary is zero. During this mode,  $Q_4$  is turned off and the output capacitance of  $Q_2$  begins to discharge while that of  $Q_4$  begins to charge. It should be noted that Fig. 2.9 shows that current flows through the output capacitance sometime in the mode after  $Q_4$  is turned off.

<u>Mode 5 ( $T_4 < t < T_5$ )</u>: This mode begins when the net voltage across the C<sub>r</sub> and L<sub>r1</sub> becomes positive, causing D<sub>1</sub> to start conducting. This mode ends when the current through L<sub>r1</sub> reaches zero. At the end of this mode, the maximum voltage across the auxiliary capacitor (V<sub>cm</sub>) can be derived. Meanwhile, current flows through the body-diode of Q<sub>2</sub> during this mode. Q<sub>2</sub> can be turned on with ZVS at the end of this mode.

<u>Mode 6 (T<sub>5</sub> < t < T<sub>6</sub>)</u>: This mode begins when I<sub>Lr1</sub> reaches zero, thus D<sub>a1</sub> and D<sub>x1</sub> stop conducting. During this mode, the current in the magnetizing inductance of the feed forward transformer is discharged to the output by D<sub>T2</sub>. The voltage across L<sub>1</sub> becomes  $V_{in,rec}$ - $V_o$  and the current through L<sub>1</sub> starts to decrease linearly. Meanwhile, at the DC-DC full-bridge, the current flowing in the converter primary reverses direction and flows through Q<sub>2</sub> and Q<sub>3</sub> instead of their body-diodes. Current continues to flow through both secondary diodes, but the distribution of current is uneven as the current flowing through D<sub>T2</sub> is increasing while that flowing through D<sub>T1</sub> is decreasing.

<u>Mode 7 ( $T_6 < t < T_7$ )</u>: This mode begins when the current in L<sub>1</sub> reaches zero. This is the last mode of the half-cycle. The next half-cycle begins when S<sub>1</sub> is turned on under ZCS. During this mode, the full-bridge converter is able to transfer power to the output as voltage is impressed across the transformer primary.

Fig. 2.4. Typical waveforms of the converter shown in Fig. 2.2 [26]

Fig. 2.5. Key waveforms of the full-bridge DC-DC converter

Fig. 2.7. Mode 2

Fig. 2.9. Mode 4

Fig. 2.10. Mode 5

Fig. 2.11. Mode 6

Fig. 2.12. Mode 7

## 2.5 Converter features

The proposed converter has the following features:

- All the converter switches turn on and off with ZCS.

- There is only one active auxiliary circuit for both main switches instead of each main switch needing its own active auxiliary circuit to help it turn off with ZCS.

- The main switch does not have increased peak and RMS current stresses, as is the case with resonant type ZCS auxiliary circuits, because no current from the auxiliary circuit flows into the main circuit.

- None of the auxiliary circuit components are in the main power path, therefore they only handle a fraction of the current that the main circuit components handle.

- The maximum voltage stress of the auxiliary switch is close to the output voltage because of the transformer. Also, the current in the auxiliary circuit can be transferred to the output to increase efficiency.

- The main boost diodes do not have reverse recovery current because the input inductor currents are discontinuous.

- The auxiliary circuit does not interfere with the interleaving operation of the converter; thus, all the advantages of interleaving are maintained.

- The auxiliary circuit can be deactivated when the converter is operating under lightload conditions, unlike most ZCS methods, where the auxiliary circuit must always be in operation, regardless of the load. This leads to an improvement in the lightload efficiency because it removes the auxiliary circuit losses under operating conditions where the current in the converter is low and ZCS is unnecessary. This can be done because there are no auxiliary circuit components in the main power circuit.

- The auxiliary circuit needs to be operational for a very short amount of time, typically around 0.7  $\mu$ s. Since the auxiliary transformer is not in series with the auxiliary switch, the maximum voltage of the resonant capacitor increases which leads to faster soft switching for S<sub>1</sub>. Also, because L<sub>r1</sub> is in series with the resonant circuit, the auxiliary switch can go to zero current faster. In addition, since the converter operates in DCM, there is no reverse recovery current for the main diodes, therefore L<sub>r1</sub> does not need to be chosen high enough to eliminate it. As a result, small L<sub>r2</sub> can be chosen which decreases the operating time of the auxiliary switch.

## 2.6 Conclusion

The operation of the proposed two-stage AC-DC converter was discussed in this chapter. First, the operation of the PWM interleaved AC-DC boost front-end converter was explained. This converter uses only a single active auxiliary circuit to help all the main converter switches operate with ZCS and operates with ZCS itself. The auxiliary switch works for only a very small fraction of the switching cycle so that the converter generally operates as a conventional PWM interleaved boost converter. Next, the modes of operation of a conventional full-bridge ZVS-PWM DC-DC converter were explained. This converter steps down the output voltage produced by the first AC-DC stage and provides isolation using a high-frequency transformer. The modes of operation that the converter goes through during a half switching cycle were presented and explained. Finally, the features of the proposed converter were stated. The distinguishing feature of the converter is that it has a transformer in the auxiliary circuit of its front-end converter that not only ensures the soft-switching of its switches, but also provides a path for power to be transferred directly to the output, which helps reduce converter losses, as will be shown later in this thesis.

# Chapter 3

# 3 Converter circuit analysis

# 3.1 Introduction

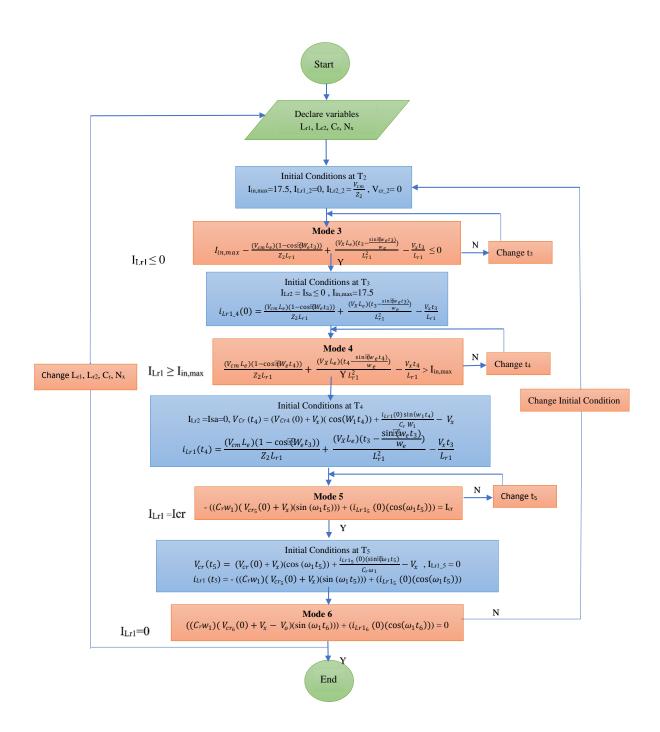

In this chapter, the steady-state analysis of the proposed two-stage AC-DC power converter is performed. The purpose of this analysis is to determine equations and formulas that can be used to develop a design procedure for key converter components in the next chapter. Since the operation of the two converter stages can be considered to be independent of each other, in general, the analysis of each converter will be considered separately.

# 3.2 AC-DC interleaved boost converter

The circuit analysis that is presented in this chapter will focus mainly on two things:

- The soft-switching operation of the converter switches.

- The amount of power that can be directly transferred from the first-stage to the output, bypassing the DC-DC full-bridge converter.

The analysis will be done by solving key equations that characterize the modes of operation that were presented in the previous section, then using these equations to develop a MATLAB program that can be used to develop graphs of steady-state characteristic curves that can be used to develop a design procedure for the converter. The following assumptions are made to simply the analysis of the circuit:

- The converter operates under steady-state conditions.

- Since the AC input voltage can be considered to be a DC input source for a very short portion of the AC line cycle, the steady-state analysis is done with DC input voltage when short switching cycles are considered.

- All components, including semiconductor switches, inductors, capacitors, and diodes of the converter are considered to be ideal.

- Transformer T<sub>x</sub>, the main power transformer in the DC-DC full-bridge stage, is considered as an ideal transformer in series with a primary leakage inductance L<sub>r</sub>.

- When current is flowing through the auxiliary circuit, the maximum primary voltage of the transformer  $T_x$ , is clamped to  $V_x=V_o / N_x$ , where  $N_x=N_2 / N_1$ . The polarity of the primary voltage of the auxiliary transformer is dependent on the polarity of the current and on whether it is secondary diode  $D_{x1}$  or  $D_{x2}$  that is conducting.

- The proposed circuit has two boost modules that are designed to be operated in DCM, so that the input inductor current of each one is discontinuous, but the actual input current of the converter, which is the sum of these inductor currents is continuous.

- When the auxiliary circuit is operating, the input current, I<sub>in</sub>, and the output voltage, Vo, are considered to be fixed, with no ripple.

- As the second half-cycle of a switching cycle is equal to that of first half-cycle, circuit analysis is performed for the first half-cycle of the operation when the switch S<sub>2</sub> begins to turn on and switch S<sub>1</sub> begins to turn off.

The analysis can proceed as follows:

**Mode 1** ( $t_0 < t < t_1$ ): This interval begins when switch  $S_2$  is turned on and current through  $L_2$  starts to rise. The auxiliary circuit is not active during this mode and power  $P_{ps}$  is processed by two converter stages. During this mode, the resonant capacitor is charged to  $V_{cr0}$ .

**Mode 2** ( $t_1 < t < t_2$ ): This interval begins when the auxiliary switch,  $S_a$ , is turned on under ZCS condition. Since  $S_a$  is in series with resonant inductor  $L_{r2}$ , the rate of the auxiliary switch current is limited and thus the switch can be turned on with ZCS. During this mode, auxiliary circuit current rises, and the value of  $V_{Cr}$  reduces until reaches zero at the end of this mode. The current through resonant inductor  $L_{r1}$  is zero so the primary current passing through the auxiliary transformer is zero; therefore, there is no power to the output through the auxiliary transformer in this mode.

By applying KCL, the following equation can be obtained:

$$i_{Lr2}(t_2) = i_{cr}(t_2) = -\frac{d}{dt}q_{cr}(t_2) = -C_r \frac{d}{dt}V_{cr}(t_2)$$

(3-1)

By applying KVL and considering  $V_{cr}(0) = V_{cm}$  as the initial condition for the capacitor voltage, where  $V_{cm}$  is the maximum voltage across the capacitor and  $i_{Lr2}(0) = 0$  as the initial condition for the auxiliary inductor current, the following expression can be written

$$V_{cr}(t_2) = -V_{cm} \cos \omega_2 t_2 \qquad T_1 < t < T_2$$

(3-2)

where  $\omega_2 = \frac{1}{\sqrt{L_{r2} C_r}}$ .

The maximum current through the auxiliary circuit at the end of this mode can be expressed as

$$i_{Lr2}(t_2) = i_{smax} = \frac{V_{Cm}}{Z_2}$$

$t = T_2$  (3-3)

**Mode 3** ( $t_2 < t < t_3$ ): This interval begins when the voltage across C<sub>r</sub>, reaches zero and the current flowing through the auxiliary current reaches its maximum value. During this interval, current is diverted from S<sub>1</sub> and S<sub>2</sub> to auxiliary switch so that the current through the main switches becomes negative and their body diodes start to conduct. This allows S<sub>1</sub> to be turned off with ZCS condition at the end of this mode t<sub>3</sub>. When the auxiliary circuit is operating, D<sub>a1</sub> and D<sub>a2</sub> begin to conduct, and a portion of the power in the auxiliary circuit is transferred to the output of the converter. The voltage across the primary of the transformer T<sub>x</sub>, is no longer zero volts but is clamped to V<sub>x</sub> =  $\frac{V_0}{N_x}$ , where N<sub>x</sub> is the turn ratio of the auxiliary transformer, N<sub>x</sub> =  $\frac{N_2}{N_1}$ .

In this mode of operation, input power can be transferred to the output through two different paths. Most of the power transferred to the output is through the DC-link capacitor and then the DC-DC full bridge converter. A portion of the energy in the auxiliary circuit is transferred through the auxiliary transformer to the output, P<sub>DPT</sub>. The total power that is delivered to the output can be expressed as:

$$P_{o}(t) = P_{DPT}(t) + P_{ps}(t)$$

(3-4)