#### UNIVERSITY OF OKLAHOMA

#### GRADUATE COLLEGE

# DEVELOPMENT AND TESTING OF AN FPGA-CONTROLLED SWITCHED-INTEGRATOR CURRENT AMPLIFIER FOR USE IN SCANNING TUNNELLING MICROSCOPY

# A THESIS SUBMITTED TO THE GRADUATE FACULTY in partial fulfillment of the requirements for the

Degree of

MASTER OF SCIENCE

By

VINCENT PALMER Norman, Oklahoma 2023

# DEVELOPMENT AND TESTING OF AN FPGA-CONTROLLED SWITCHED-INTEGRATOR CURRENT AMPLIFIER FOR USE IN SCANNING TUNNELLING MICROSCOPY

# A THESIS APPROVED FOR THE DEPARTMENT OF ENGINEERING PHYSICS

#### BY THE COMMITTEE CONSISTING OF

Dr. Lloyd A. Bumm, Chair

Dr. Michael B. Santos

Dr. Clifford W. Fitzmorris

#### Acknowledgements

First and foremost, I would like to thank my advisor, Dr. Lloyd Bumm. You were the first person I spoke to or met at the University of Oklahoma, and without your guidance and advice I would not have been able to take the leap to leave the military, return to college, and pursue a graduate degree. The fact that I ended up in your research group seems almost predestined as a result, and this thesis would not have been possible without the guidance, education, and support you provided. To my committee members Dr. Santos and Dr. Fitzmorris, thank you for giving me a solid foundation in electronics and engineering, advice, and technical insight along the way, and finally for helping me complete this thesis. To Steven, thank you for the hours of conversation, for listening to me rage, and for being the least lame vegetarian/runner combo I've ever met. And last, but certainly not least, I would like to thank my beautiful wife Becca. Your support these years after I left a promising career to pursue my dreams has never wavered. I could not have asked for a better partner in crime, and I plan on spending the rest of my life paying you back for everything.

#### **Abstract**

The scanning tunnelling microscope (STM) is a very powerful analytic tool capable of achieving atomic resolution. Unfortunately, the STM is restricted to samples that are sufficiently conductive to allow adequate tunneling current for feedback control. The amplifier used to measure the tunneling current is the critical limiting component. If the amplifier could be made more sensitive, the STM could be operated at lower tunneling currents allowing lower conductivity samples to be studied. Most amplifiers used in STM employ a resistor feedback design, which become unstable at high gain necessitating a tradeoff between gain and bandwidth. One way to circumvent that stability problem is to use a capacitor feedback design (switched integrator), which does not exhibit the same stability problem. This comes at the expense of added complexity because the output is the integral of the current and needs to be periodically reset. In this project, a switched-integrator current amplifier is constructed and explored. It consisted of an analog switched integrator controlled by a field-programmable-gate-array (FPGA) with a 16-bit analog-to-digital converter and an 18-bit digital-to-analog converter. A viable prototype was created which allowed for the exploration of the gain, phase, and time delay of such systems. This exploration helped further characterize the important design considerations and trade-offs necessary for such a system. A design sequence is proposed that allows for optimal planning based on the desired tunneling current and system bandwidth.

### Table of Contents

| ACKN   | OWLEDGEMENTS                               | IV   |

|--------|--------------------------------------------|------|

| ABSTE  | RACT                                       | V    |

| TABLI  | E OF CONTENTS                              | VI   |

| LIST C | OF FIGURES                                 | VIII |

| LIST C | OF TABLES                                  | X    |

| СНАР   | TER 1: INTRODUCTION                        | 1    |

| 1.1    | OVERVIEW OF SCANNING TUNNELLING MICROSCOPY | 1    |

| 1.2    | Motivation                                 |      |

| 1.3    | OVERVIEW OF THE PROJECT                    |      |

| 1.4    | SCOPE OF THE THESIS                        | 5    |

| 1.5    | References                                 | 6    |

| CHAP   | TER 2: STM CURRENT AMPLIFIERS              | 7    |

| 2.1    | Noise Sources in Transimpedance Amplifiers | 7    |

|        | 1.1 Shot Noise                             |      |

|        | 1.2 Thermal Noise                          |      |

|        | 1.3 kTC Noise                              | _    |

| 2.2    | AMPLIFIER TYPES                            | 9    |

| 2.     | 2.1 Resistor Feedback                      |      |

| 2.     | 2.2 Capacitor Feedback                     | 12   |

| 2.3    | STABILITY                                  |      |

| 2.4    | References                                 | 14   |

| CHAP   | TER 3: SYSTEM DESIGN                       | 15   |

| 3.1    | SIGNAL INTEGRATION                         | 16   |

| 3.2    | SIGNAL DIFFERENTIATION                     |      |

| 3.3    | References                                 |      |

| CHAP   | TER 4: LOW-PASS DIFFERENTIATION            | 21   |

| 4.1    | STANDARD FIR FILTERS                       | 21   |

| 4.2    | LOW-PASS DIFFERENTIATING FIR FILTER        | 22   |

| 4.3    | SOFTWARE DESIGN                            | 23   |

| 4.4    | CAPACITOR RESET                            | 25   |

| 4.5    | DESIGN OF FILTER FOR TESTING               | 27   |

| 4.6    | References                                 | 30   |

| CHAP   | TER 5: PCB SWITCHED INTEGRATOR             | 31   |

| 5.1    | SWITCHED INTEGRATOR TEST CIRCUIT DESIGN    | 31   |

| 5.2    | System Performance Analysis                | 33   |

| 5.2.1   | Demonstration of System Performance             | 34 |

|---------|-------------------------------------------------|----|

| 5.2.2   | Magnitude vs Frequency Response                 | 35 |

| 5.2.3   | Phase Response and Time Delay                   | 37 |

| 5.2.4   | Low-Frequency, Low-Amplitude Analysis           |    |

| 5.3 I   | References                                      | 43 |

| CHAPTER | R 6: CONCLUSION                                 | 44 |

| 6.1     | SUMMARY OF RESULTS                              | 44 |

| 6.2 I   | LIMITATIONS AND POSSIBLE IMPROVEMENTS           | 45 |

| 6.2.1   | VHDL-2008 Constraints                           | 45 |

| 6.2.2   | Clocking Constraints and Resolution Limitations | 46 |

| 6.2.3   | Reset Considerations                            | 46 |

| 6.2.4   | Parallel Filter Design                          | 48 |

| 6.2.5   | Noise                                           | 48 |

| APPENDI | X                                               | 49 |

| A.1 FIF | R FILTER                                        | 49 |

| A.2 FP  | GA CODE (VHDL-2008)                             | 50 |

| A.3 AD  | DITIONAL ELECTRONICS SCHEMATICS                 | 67 |

## List of Figures

| Figure 1.1: STM example image                                                                 | 2  |

|-----------------------------------------------------------------------------------------------|----|

| Figure 1.2: Diagram of a scanning tunnelling microscope                                       | 3  |

| Figure 1.3: Conceptual diagram of the capacitor feedback operational amplifier                | 4  |

| Figure 2.1: Simplified diagram of a resistor feedback operational amplifier                   | 9  |

| Figure 2.2: Elements contributing to stability and bandwidth in transimpedance amplifiers     | 10 |

| Figure 2.3: Schematic of a switched integrator operational amplifier                          | 12 |

| Figure 3.1: Block diagram of components of signal integrator and signal differentiator        | 15 |

| Figure 3.2: Block diagram of input integration components                                     | 16 |

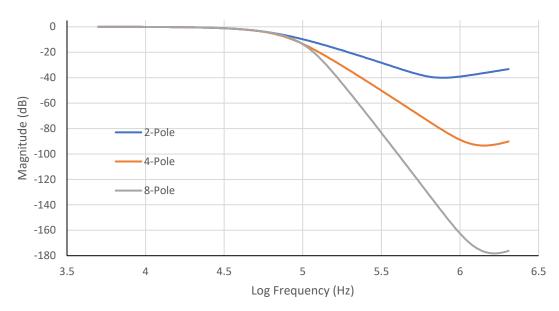

| Figure 3.3: Magnitude response of the Sallen-Key anti-aliasing filters                        | 16 |

| Figure 3.4: Group delay of the Sallen-Key anti-aliasing filters                               | 17 |

| Figure 3.5: Schematic of the ADC, FPGA, and DAC                                               | 18 |

| Figure 3.6: Functional block diagram of the AD4001 Analog-to-Digital Converter                | 19 |

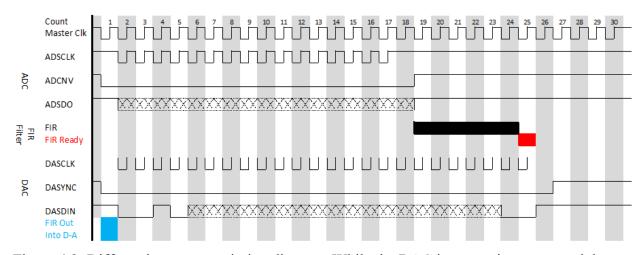

| Figure 3.7: Functional block diagram of the AD5781 Digital-to-Analog Converter                | 19 |

| Figure 3.8: Picture of the CMOD-A7 35T                                                        | 20 |

| Figure 4.1: Block diagram of VHDL-2008 code                                                   | 23 |

| Figure 4.2: Differentiator master timing diagram                                              | 24 |

| Figure 4.3: Graphical description of the correction made to the FIR register upon resetting   | 26 |

| Figure 4.4: Impulse response of 81 <sup>st</sup> order direct-form differentiating FIR filter | 29 |

| Figure 4.5: Magnitude response of 81st order direct-form differentiating FIR filter           | 30 |

| Figure 5.1: Circuit diagram of PCB layout                                                     | 32 |

| Figure 5.2: Demonstration of integration and differentiation of input signal                  | 34 |

| Figure 5.3: Measured gain of the integrator                                                   | 36 |

| Figure 5.4: Measured gain of the differentiator                                               | 36 |

| Figure 5.5: Integrator phase                                                                  | 37 |

| Figure 5.6: Differentiator phase                                    | 38 |

|---------------------------------------------------------------------|----|

| Figure 5.7: Phase of entire system                                  | 49 |

| Figure 5.8: Determination of time delay                             | 40 |

| Figure 5.9: Performance of system at low amplitudes and frequencies | 40 |

| Figure 5.10: Relationship between sampling time and ADC resolution  | 41 |

| Figure 5.11: Performance of system at 13.3 k samples per second     | 42 |

| Figure 6.1: Design sequence for future iterations                   | 45 |

| Figure A.1: Schematic of anti-aliaisng filter                       | 67 |

| Figure A.2: Schematic of differential amplifier                     | 68 |

### List of Tables

| Table A.1: | : List of | coefficients | in 81st ord | der direct- | -form d | lifferentiati | ng FIR f | ilter for l | PCB |    |

|------------|-----------|--------------|-------------|-------------|---------|---------------|----------|-------------|-----|----|

| integrator | testing   |              |             |             |         |               |          |             | 4   | 19 |

#### Chapter 1: Introduction

#### 1.1 Overview of Scanning Tunnelling Microscopy

The scanning tunnelling microscope (STM) can image surfaces with atomic resolution and has proven to be an extremely powerful tool in modern physics. The technique was developed by Gerd Binnig and Heinrich Rohrer while working at IBM and demonstrated for the first time in 1983 (along with Gerber and Weibel), earning them the 1986 Nobel Prize in Physics. Physics.

In STM, an atomically sharp probe tip, typically made of tungsten or a platinum-iridium alloy, is positioned less than a nanometer above the surface of the material by a piezoelectric actuator. Once the probe tip is close enough, the electron wavefunctions of the probe tip and the sample will overlap, and quantum tunneling between the two will become possible. By applying a bias voltage between the probe tip and the sample, a net quantum tunnelling current will result. Because the tunnelling current is strongly dependent on the probe tip-sample separation, the tunneling current can be used to maintain the separation which avoids physical contact between the probe tip and the sample. One common STM operational mode achieves this by operating at a constant tunneling current. Negative feedback by the piezoelectric actuator is used to maintain the tunneling current at an operator-selected set point, and thus a nominally constant probe tipsample separation. The difference between setpoint current and the measured current is the error signal which drives the piezoelectric actuator. For example, if the tunneling current is above the set point, the separation is too small, and the probe tip is moved away from the surface. If the current is below the set point, the separation is too large, and the probe tip is moved closer to the surface. This balance is maintained throughout the time when the STM is operating. This feedback minimizes the error signal and holds the tunneling current constant. To image the sample surface, the tip is scanned across the material in a raster pattern, and the tip height at constant tunneling current is recorded for each point in the pattern, generating an electronic topographic map of the sample. The corresponding z-coordinate can then be mapped as a function of the x- and y- coordinate to create an image of the sample surface.<sup>4</sup> An example of an STM image is given in Figure 1.1. The amplifier that measures the tunneling current is a critical component of the STM and is the focus of this project.

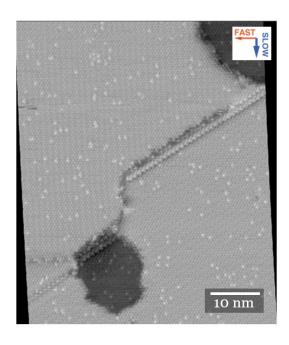

Figure 1.1:STM example image. DHCT-corrected STM image of alkanethiol-on-Au(111) self-assembled monolayers. The dark regions are topographically lower than the lighter regions and represent regions of gold vacancy islands. The monolayer is composed of a decanethiol host (10 carbon backbone) containing a small fraction of longer undecanethiol guest molecules (11 carbon backbone). The bright spots represent the longer chains on a sea of smaller chains.<sup>5</sup>

While it was initially believed that the technique mapped solely the topography of the surface of a material, in 1996 Diebold showed that the STM map was in fact a map of the electronic structure of the material. Thus, an STM image represents the convolution of the physical and electronic properties of the surface. By changing the imaging conditions (e.g., sample bias or the set-point current), it is possible to probe different electronic states or atoms within a sample. This ability to provide atomic resolution of materials surfaces has proven extremely valuable and has even recently allowed for the study of quantum superposition of electrons in monolayer graphene. The study of quantum superposition of electrons in monolayer graphene.

#### 1.2 Motivation

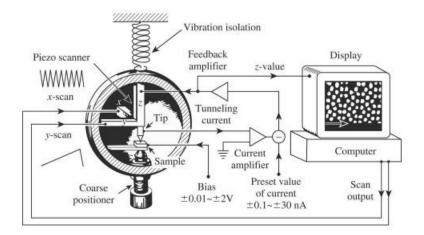

Controlling an STM requires a sophisticated set of electronics and a computer to process the measurements into a gray-scale image like in Figure 1.1, and a simplified diagram of these components is show in Figure 1.2. The tunnelling current must be measured and conditioned, most commonly by a current-to-voltage amplifier, to a voltage level that can interface with the

Figure 1.2: Diagram of a scanning tunnelling microscope. The tunnelling current is amplified to interface with the STM control electronics which raises or lowers the tip, and the tip height in relation to the x and y position on the sample is stored to generate the contour map from Figure 1.1.<sup>1</sup>

STM control electronics. The performance of this current amplifier is a key design consideration for the STM.

Standard STM set-ups use transimpedance amplifiers, which use resistors as the feedback mechanism. The advantages of this set-up follow.

- 1. Simple to use: The gain, and therefore the voltage generated by the tunnelling current, can be easily manipulated by changing the resistance of the feedback resistor in accordance with Ohm's law.

- 2. Ease of processing: Since the output voltage is directly proportional to the input current, extracting the tunnelling current requires little processing.

- 3. History of success: Transimpedance amplifiers have historically worked very well for samples with relatively high conductance. They have been employed for imaging with tunnelling currents as low as 0.1 pA.

However, two issues exist that severely limit resistor-feedback systems. The first is that the parasitic capacitance in the feedback resistor results in a pole of the transfer function that limits the bandwidth of the amplifier. The second is that the input capacitance creates a zero in the transfer function which can lead to oscillation. This forces a compromise between bandwidth and gain. One way around this is to use a capacitor as the feedback element instead of a resistor, which has been used successfully in the design of patch clamp amplifier. These systems are

more stable than their resistor feedback counterparts but are more complicated to implement. This type of feedback may allow for the detection of smaller tunnelling currents without sacrificing bandwidth, which would allow for application of STM to samples that are intractable by current systems due to low surface conductance. Section 2.2 discusses the theoretical implementation of these current amplifiers, and their actual usage is discussed in the following chapters.

#### 1.3 Overview of the Project

The intent of this project was to explore the feasibility of using an integrating (capacitor-feedback) amplifier for use as an STM current amplifier. The ultimate objective is to achieve STM operation with tunneling currents below 1 pA with a bandwidth of 2 kHz or greater with a current signal to noise ratio (SNR) greater than 10. To interface with existing STM control electronics, the output voltage must be proportional to the current. Because the current amplifier is part of the STM feedback loop, the phase margin of the system will need to be >45° to assure stable operation, which places limits on the group delay to below 200 µs.

Figure 1.3: Conceptual diagram of the capacitor feedback operational amplifier.

There are two required components for this design, the integrator, and the differentiator. In this project, the integrator was implemented on a printed circuit board with additional support components to provide the necessary input current and output voltage conditioning.

Differentiation was accomplished by digitizing the signal with an analog-to-digital converter (ADC), differentiating it with a field-programmable gate array (FPGA), and outputting the processed signal with a digital-to-analog converter (DAC). Additionally, the FPGA controlled

the ADC, DAC, and the reset switch across the capacitor in the integrator. A simplified diagram of the general set-up is shown in Figure 1.3.

#### 1.4 Scope of the Thesis

This thesis will cover the theory, general design, prototyping, and implementation of a switched integrator capacitor feedback operational amplifier system that could be used for STM. Chapter 1 introduced the theory of STM, the motivation for studying capacitor-feedback operational amplifiers, and the general overview of the project. The information in Chapter 2 lays the theoretical groundwork for understanding the limitations of traditional STM current amplifiers, and how capacitor-feedback can work around these limitations. Chapter 3 breaks down the hardware and components used in the system to a greater extent and discusses what each piece of the system does. Chapters 4 and 5 break down into detail the two major components. Chapter 4 describes the differentiator, specifically the theory behind the low-pass differentiating filter used as well as the software that controls the ADC, DAC, reset switch, and implementation of the filter. Chapter 5 covers the detailed PCB board implementation of a precise switched integrator. This chapter shows that the system works as intended and highlights the important design criteria revealed by these tests for future implementation. Chapter 6 summarizes the results from Chapters 5, discusses a possible design sequence based on the necessary design criteria, and recommends possible improvements for future similar systems.

#### 1.5 References

- 1. Binnig, G.; Rohrer, H., Scanning tunneling microscopy from birth to adolescence. *Reviews of Modern Physics.* **1987**, *49*, 615-625.

- 2. Binnig, G.; Rohrer, H.; Gerber. C.; Weibel, E., Surface studies by scanning tunnelling microscopy. *Phys. Rev. Lett.* **1982**, *49*, 57-61.

- 3. The Nobel Prize in Physics 1986. NobelPrize.org. Nobel Prize Outreach AB 2023. Fri. 7 Apr 2023. https://www.nobelprize.org/prizes/physics/1986/summary/.

- 4. Chen, J., *Introduction to Scanning Tunnelling Microscopy*. Second Edition, Oxford University Press, 2008.

- 5. Yothers, M., High-precision measurements of alkanethiol self-assembled monolayer structure with scanning tunneling microscopy. Univ Oklahoma. PhD Dissertation. 2020. https://shareok.org/handle/11244/325434.

- 6. Diebold, U.; Anderson, J.; Ng, K.; Vanderbilt, D., Evidence for the Tunneling Site on Transition-Metal Oxides: TiO2. *Phys. Rev. Lett.* **1996**, **77**, 1322-1325.

- 7. Hembacher, S.; Giessibl, F. J.; Mannhart, J.; Quate, C. F., Revealing the hidden atom in graphite by low-temperature atomic force microscopy. *Proc. Natl. Acad. Sci.* **2003**, *100* (22), 12539-12542.

- 8. Feenstra, R. M., Scanning tunneling microscopy and spectroscopy of gold on the GaAs(110) surface. *J. Vac. Sci. Technol. B* **1989,** 7 (4), 925-930.

- 9. Bumm, L. A.; Arnold, J. J.; Dunbar, T. D.; Allara, D. L.; Weiss, P. S., Electron transfer through organic molecules. *J. Phys. Chem. B* **1999**, *103* (38), 8122-8127.

- 10. Liu, X.; Farahi, G.; Chiu, C.; Papic, Z.; Watanabe, K.; Kenji, T.; Takashi, Z.; Zaletel, M.; Yazdani, A., Visualizing broken symmetry and topological defects in a quantum Hall ferromagnet. *Science.* **2021**, *375*, 6578, 321-326.

- 11. Finkel, A. S., Progress in instrumentation technology for recording from single channels and small cells. In *Cellular and Molecular Neurobiology: A Practical Approach*, Chad, J.; Wheal, H., Eds. Oxford UniversityPress: 1991.

- 12. Sigworth, F. J., Electronic Design of the Patch Clamp. In *Single-Channel Recording*, Sakmann, B.; Neher, E., Eds. Springer US: Boston, MA, 1995; pp 95-127.

#### Chapter 2: STM Current Amplifiers

The current amplifier is a key component of the STM that imposes limits on the gain and bandwidth of the tunnelling current, which is fundamental in measuring the tunnelling current in STM. Bandwidth determines the response time of the STM, and sufficient bandwidth is required required for the STM to be able to accurately follow the contours of the sample and react to variations in the surface without crashing. The gain limits the tunnelling current (and therefore the conductance of materials) that can be studied. These amplifiers that convert current to voltage are called transimpedance amplifiers. Converting current into voltage is useful because most electronic systems encode information as voltages, making it easier to interface with other components.

The main factor that needs to be controlled to ensure a successful operational amplifier set-up is the signal-to-noise ratio. If the noise on a signal is too high, it may be difficult, if not impossible, to recover the desired signal in a timely manner. Increasing the gain of a system will also increase the amplitude of contributing noise sources. Different amplifier configurations will have different noise sources and responses to them. This chapter discusses the noise sources in transimpedance amplifiers, how different amplifier configurations work, and the resulting noise analysis that goes along with those amplifier configurations.

#### 2.1 Noise Sources in Transimpedance Amplifiers

The three major noise sources relevant to STM amplifiers are shot noise, thermal noise, and kTC noise. Understanding what causes them and the effect they have on the measurement allows for systems to be designed that manage noise sources to improve the signal-to-noise ratio.

#### 2.1.1 Shot Noise

Shot noise results from the discrete nature of electric charge. Current results from the movement of electrons. When current is high, the movement of the electrons follows the law of high numbers, the relative number of statistical fluctuations will be statistically small. However, at lower currents, the relative number of statistical fluctuations will increase, causing noise in the current. The equation for RMS shot noise is

$$N_S = \sqrt{2eIB}$$

,

where e is the electron charge, I is the average dc current, and B is the frequency bandwidth. The resulting SNR is

$$SNR_S = \sqrt{\frac{I}{2eB}}.$$

Shot noise is an inherent property of the current being measured. The SNR at 1 nA, 1pA, and 1 fA in 2 kHz bandwidth gives SNRs of 1200, 40, and 1.2, respectively. At high current, the effect of shot noise is generally less relevant, and if other noise sources dominate can be neglected. Shot noise can begin to dominate as other noise sources are reduced or when measuring a very small current.

Because the shot noise is fundamental to the tunneling current, considering the shot noise alone estimates the expected current noise from a noiseless current amplifier. Using the target parameters from Section. 1.3 (SNR of 10 in a 2 kHz bandwidth), the smallest practical current the STM can operate at is 64 fA. In practice the STM loop bandwidth is effectively lower than this target because the STM feedback is primarily an integrator, and the loop can be slowed below the 2 kHz bandwidth to reduce the noise.

#### 2.1.2 Thermal Noise

Thermal noise, also known as Johnson-Nyquist noise, is a phenomenon that arises from the thermal motion of electrons. The fluctuation of electrons within the resistor gives at any instant a voltage across the resistor. The RMS voltage noise that results in a resistor with resistance R is

$$N_I^V = \sqrt{4k_BTBR},$$

and the resulting RMS current noise is

$$N_J^I = \sqrt{\frac{4k_BTB}{R}}.$$

#### 2.1.3 kTC Noise

Ideal capacitors are lossless devices. However, Johnson-Nyquist noise on the rest of the circuit will impress a voltage fluctuation on the capacitor. This results in thermal noise on the capacitor known as kTC noise.<sup>2</sup> The RMS voltage noise is

$$N_K^V = \sqrt{k_B T/C}$$

,

and the charge noise is

$$N_K^Q = \sqrt{k_B T C}.$$

An interesting consequence of this is the presence of reset noise left on a capacitor when a switch is opened. The random thermal motion of the charges is then frozen onto the plates of the capacitor, resulting in the presence of noise while the capacitor is discharging, which can be the limiting source of noise for capacitive sensors.<sup>3</sup>

#### 2.2 Amplifier Types

Response to the above noise sources is an important consideration when developing an STM. While there are numerous possible amplifier configurations that could be used in an STM, the focus of this thesis will be limited to those based on operational amplifiers. While many STMs use resistor feedback for their operational amplifiers, capacitive feedback has many characteristics that may be useful in low tunneling current applications. This next section differences between these two types of feedback.

#### 2.2.1 Resistor Feedback

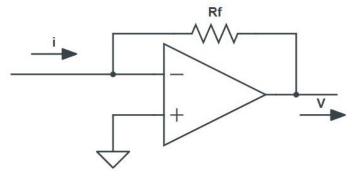

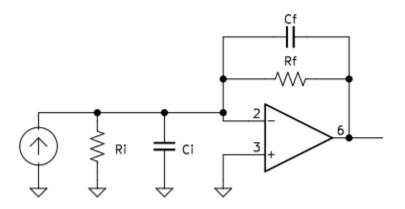

Figure 2.1: Simplified diagram of a resistor feedback operational amplifier. Most STM's use current amplifiers with resistor feedback.

In the resistor feedback operational amplifier shown in Figure 2.1, the relationship between the current into the inverting terminal and voltage across the feedback resistor can be easily found from Ohm's law and the op amp golden rules<sup>4</sup>

$$V = -IR$$

.

These types of operational amplifiers are sufficient for samples with relatively high conductance. The gain in a resistor-feedback amplifier is proportional to R, and the Johnson-Nyquist voltage noise is proportional to  $\sqrt{R}$ . Increasing the feedback resistor increases the gain faster than the noise, thus increasing the signal-to-noise ratio. However, the choice amplifier of gain must consider the entire circuit.

Figure 2.2: Elements contributing to stability and bandwidth in transimpedance amplifiers.

The schematic in Figure 2.2 shows a resister feedback amplifier, along with the feedback resistors parasitic capacitance, input capacitance, and input resistance. Resistors and the circuit wiring contribute parasitic stray capacitance, and the input capacitance and resistance are important elements in the response and stability of the amplifier. The stray capacitance and the feedback resistor contribute a pole at

$$f_P = \frac{1}{2\pi R_f C_f},$$

which results in a 3dB frequency reduction of the bandwidth at  $f_P$ . When the denominator of the pole is large, the bandwidth becomes small. Thus, at a fixed  $C_f$ , there must be a trade-off between the gain and the bandwidth, since increasing R to increase the gain will decrease the bandwidth. Additionally, the parallel sum of the capacitances and the resistances contributes a zero at

$$f_Z = \frac{R_f + R_i}{2\pi R_f R_i (C_f + C_i)},$$

which can affect stability and, in the worst case, cause the system to oscillate. Operational amplifier stability is discussed in section 2.3. A typical value for stray capacitance that has been reported in STM amplifiers is 0.5 pF.<sup>1</sup>

Since the voltage gain of the resistor feedback operational amplifier is also dependent on the resistance of the feedback resistor, this also inherently limits the conductance of materials that can be studied; if the conductance is too low, the gain-limited current-to-voltage amplifier will not be able to generate a large enough current to drive the feedback mechanism of the STM. There have been numerous methods developed to maintain an acceptable bandwidth while sampling low-conductance materials in STM. A few are discussed below.

- 1. Atomic Force Microscopy (AFM): AFM is another type of scanning probe microscopy that can measure forces as small as 10<sup>-18</sup> N.<sup>6</sup> It has proved very successful in sampling many different materials but has roughly 10-100x less resolution.<sup>7</sup>

- 2. Cascading Amplifiers: Running the current through multiple stages of amplifiers, rather than one stage, can increase the frequency response of the amplifier, but results in an increase in noise because the internal noise of each amplifier is amplified by the subsequent stages.<sup>89</sup> For example, a two-stage amplifier can be used, where the first stage will typically have high gain and low bandwidth for stability and the second stage recovers the lost bandwidth from the first stage.

- 3. Another option is the use of composite amplifiers, where the last stage completes a feedback loop to the first stage. These designs can take the best elements of each amplifier while reducing their negative effects.<sup>10</sup>

- 4. Feedback Loop Compensation: A team in 2020 was able to achieve 28 kHz bandwidth with 10 times lower Johnson-Nyquist noise than traditional transimpedance amplifiers. They did this by applying a compensating capacitor and resistor to the feedback mechanism. Another team devised a circuit with an operational amplifier that resulted in an additional "negative capacitance" seen across the feedback element of a transimpedance amplifier. 12

#### 2.2.2 Capacitor Feedback

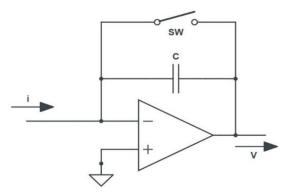

Figure 2.3: Schematic of a switched integrator operational amplifier. The switch is used in parallel with the feedback capacitor to allow the capacitor to discharge when nearing saturation.

Figure 2.2 shows the layout of a switched capacitor feedback operational amplifier. Unlike the resistor feedback system, when a capacitor with capacitance C is used as the feedback mechanism for these current-to-voltage amplifiers, the relationship between the input current I and the output voltage V is given by<sup>4</sup>

$$V_{out} = -\frac{1}{C} \int I_{in} \, dt.$$

Thus, the voltage depends on the sum total of the charge built up on the capacitor. So, whereas in a resistor feedback system a constant current into the amplifier would result in a constant voltage output, a constant current into a capacitor feedback system would result in a linearly increasing voltage output. The output would continue to increase until the amplifier saturates. Saturation needs to be avoided by the periodic discharge of the capacitor. This is accomplished with the in parallel with the capacitor, which keeps the capacitor in the range necessary to accurately measure the current being amplified. For defining the gain of the integrator, we consider the output quantity to be  $\frac{dV_{out}}{dt}$  because it is instantaneously related to the input quantity  $I_{in}$ . The gain of the amplifier can be seen as the inverse of the capacitance of the feedback capacitor by taking the time derivative of the above equation, yielding the relation

$$\frac{\left(\frac{dV_{out}}{dt}\right)}{I_{in}} = -\frac{1}{C} = A_I,$$

where  $A_I$  is the gain of the integrator.

The STM feedback that drives the raising and lowering of the tip depends on the tunnelling current through the sample, not its integral. Therefore, the voltage signal needs to be differentiated to interface with the STM control electronics. While differentiating the signal adds another component, these amplifiers have improved noise performance compared to resistor feedback systems, particularly at the high frequencies and gains necessary to analyze samples with low conductance. 13141516

Capacitor feedback systems are popular in the biological sciences through patch clamp amplifiers, <sup>17</sup> but these instruments require modifications and are usually too bulky to be mounted close to the scanning tip which increases the system noise. <sup>18</sup> However, other capacitive feedback systems have been developed and shown to be viable for different situations. <sup>19</sup>

#### 2.3 Stability

Time delays in the system can cause stability issues with the STM. As the tip moves over the surface of the sample, the piezo needs to be able to respond to these changes. As the voltage from the changing tunnelling current varies, the amplifier will try to respond. Time delays cause the op amp to fail to detect that it has reached the correct output voltage, which causes it to overshoot. The op amp then must try to correct back to the desired output voltage. If the delay is small enough compared to the frequency of the input signal, this will result in damped successive feedback oscillations that eventually settles on the correct output. If the time delay is results in a phase approaching 180° and a gain greater than 1, then positive feedback can result, causing the system to continuously oscillate and never settle to the correct value.

#### 2.4 References

- 1. Chen, J., *Introduction to Scanning Tunnelling Microscopy*. Second Edition, Oxford University Press, 2008.

- 2. Sarpeshkar. R; Delbruck, T.; Mead C., White noise in MOS transistors and resistors. *IEEE Circuits and Devices Magazine* **1993,** *9*, 6.

- 3. Fowler, B.; Godfrey, M.; Mims, S., Reset Noise Reduction in Capacitive Sensors. *IEEE Transactions On Circuits And Systems*, **2006**, *53*, 8.

- 4. Horowitz, P.; Hill, W., *The Art of Electronics*. Third Edition, Cambridge University Press, 2015.

- 5. Graeme, J., *Photodiode Amplifiers Op Amp Solutions*. McGraw-Hill, 1995.

- 6. Binnig, G.; Quate, C.; Gerber, C. Atomic Force Microscope. *Phys. Rev. Lett.* **1986,** *56*, 930.

- 7. Umbach, C. C.; Blakely, J. M., Development of a sub-picoampere scanning tunneling microscope for oxide surfaces. *Appl. Surf. Sci.* **2001**, *175-176*, 746-752.

- 8. Steer, M., *Fundamentals of Microwave and RF Design*. North Carolina State University Libraries, 2019.

- 9. Petersen, J. P.; Kandel, S. A., Circuit design considerations for current preamplifiers for scanning tunneling microscopy. *Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena* **2017**, *35* (3), 033201.

- 10. Gift, S.; Maundy, B., Versatile composite amplifier configuration *International Journal of Electronics*, **2015**, *102*, 6, 993–1006.

- 11. Štubian, M.; Bobek, J.; Setvin, M.; Diebold, U.; Schmid, M., Fast low-noise transimpedance amplifier for scanning tunneling microscopy and beyond. *Rev. Sci. Instrum.* **2020,** *91* (7), 074701.

- 12. Xie, K.; Liu, Y.; Li, X.; Guo, L.; Zhang, H. Expanding the bandwidth of the ultra-low current amplifier using an artificial negative capacitor. *Review of Scientific Instruments*. **2004**, 75, 2.

- 13. Burr-Brown, Noise Analysis of FET Transimpedance Amplifiers. *Burr-Brown Application Bulletin* **1994**, *SBOA060*.

- 14. Baker, B. C., Improved Noise Performance of the ACF2101 Switched Integrator. Ibid. **1993**, *SBOA032*.

- 15. Baker, B. C., Comparison of Noise Performance between a FET Transimpedence Amplifier and a Switched Integrator. *Burr-Brown Application Bulletin* **1994**, *SBOA034*.

- 16. Raczkowski, K.; Piasecki, T.; Rudek, M.; Gotszalk, T., Design and evaluation of precise current integrator for scanning probe microscopy. *Meas. Sci. Technol.* **2017**, *28* (3), 034013.

- 17. Sigworth, F. J., Electronic Design of the Patch Clamp. In *Single-Channel Recording*, Sakmann, B.; Neher, E., Eds. Springer US: Boston, MA, 1995; pp 95-127.

- 18. Carlà, M.; Lanzi, L.; Pallecchi, E.; Aloisi, G., Development of an ultralow current amplifier for scanning tunneling microscopy. *Rev. Sci. Instrum.* **2004**, *75* (2), 497-501.

- 19. Umbach, C. C.; Blakely, J. M., Development of a sub-picoampere scanning tunneling microscope for oxide surfaces. *Appl. Surf. Sci.* **2001**, *175-176*, 746-752.

#### Chapter 3: System Design

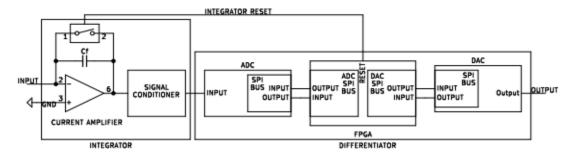

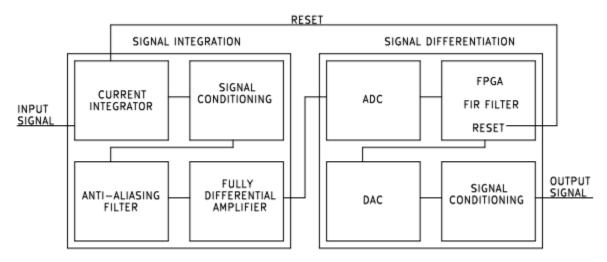

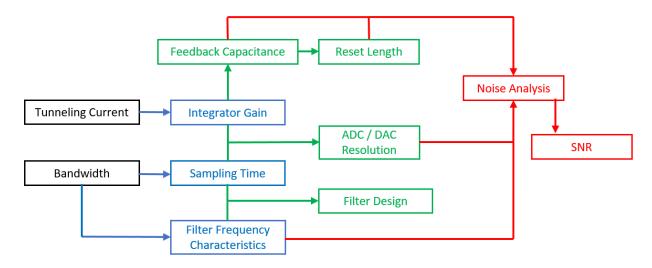

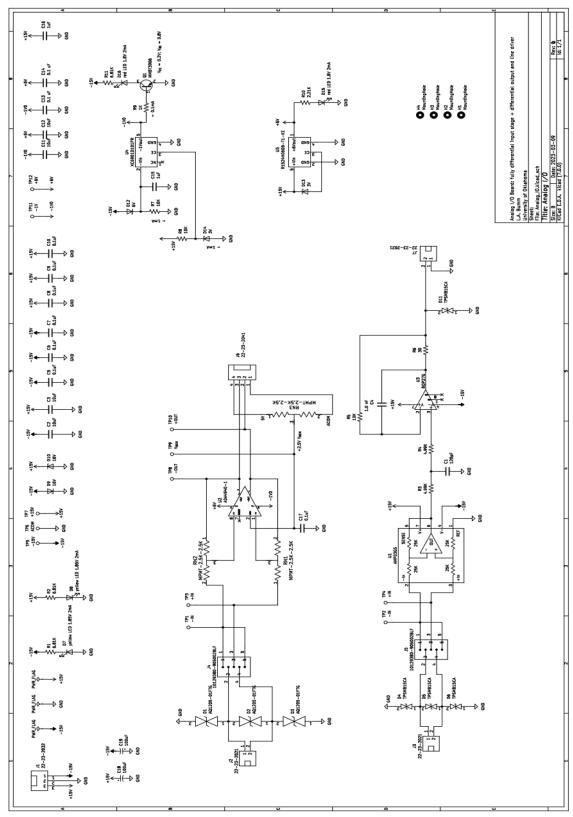

Before diving into the specific construction of the system, it is important to understand generally how each component works together as well as the general design philosophy of the system as a whole. Since the voltage across a switched integrator is proportional to the integral of the current into the input, the signal needs to be differentiated to extract the tunnelling current. This was accomplished by first integrating the input signal with the switched integrator. The output of the integrator is conditioned first by an anti-aliasing filter with a differential input. The former removes frequencies above the Nyquist frequency of the digital sampling. The latter suppresses common mode noise. It is then converted to a fully differential signal and input to the 16-bit analog-to-digital converter (ADC). Digital signal processing and differentiating is accomplished in the FPGA using a differentiating finite impulse response (FIR) filter and outputting the differentiated signal with a digital-to-analog converter (DAC). The output voltage can then be compared with the error voltage in the feedback electronics to determine the necessary adjustments to the tip height. A block diagram showing the general relationship of each component is shown in Figure 3.1. Each component is described in more detail in the following sections of this chapter.

Figure 3.1: Block diagram of components of signal integrator and signal differentiator.

#### 3.1 Signal Integration

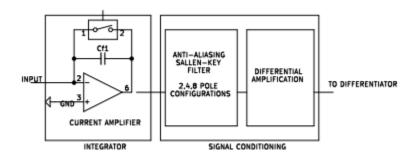

Figure 3.2: Block diagram of input integration components

Figure 3.2 shows the three major elements responsible for integrating and conditioning the input from the STM. The first, and most important component of this system is the switched integrator. It contains the capacitor feedback amplifier, the switch to discharge the capacitor, and all the additional electronics to process and amplify the signal. The tested switched integrator systems are covered in Chapters 5 and 6.

Figure 3.3: Magnitude response of the Sallen-Key anti-aliasing filters. While all three filters have the same pass-band and stop-band, the attenuation provided by the 8-pole filter is significantly stronger than the other two.

Next the signal is processed through an anti-aliasing filter. Aliasing occurs when a signal over the Nyquist frequency (discussed in Chapter 4) is sampled, causing false frequencies to

appear in a signal. High frequency noise signals can cause the appearance of features in the data that are not actually there. The anti-aliasing filter is a low-pass filter, preventing signals with frequencies above the Nyquist frequency from entering the ADC. The system is jumper selectable for 2, 4, and 8-pole Sallen-Key active low-pass filter as well as an 8-pole clock-tunable Bessel filter. The schematics are included in Appendix A.3, and plots of the Sallen-Key filters performance are shown in Figure 3.3 and Figure 3.4. The 8-pole filter has the strongest attenuation, reaching –87 dB at the Nyquist frequency of 333 kHz while introducing a 10 μs group delay. This time delay can combine with other time delays in the system to produce a frequency dependent phase shift which can cause oscillations of the STM control loop at frequencies where the phase reaches 180°, as discussed in Section 2.2.1.

Figure 3.4: Group delay of the Sallen-Key anti-aliasing filters. The consequence of the increased attenuation provided by the 8-pole filter is the increase in the group delay.

The signal is then amplified by a fully differential amplifier as required by the ADC, which also provides immunity to common mode noise such as ground loops. The fully differential amplifier used was the ADA4940-1ARZ differential amplifier<sup>2</sup>, which converts the single-ended signal out of the integrator into a fully-differential signal to be processed by the ADC. This board also contains components that condition the output signal, which will be

discussed in the next section. The schematics for the set-up used are included in Appendix A.4.2. From here, the signal is then transmitted to the differentiator.

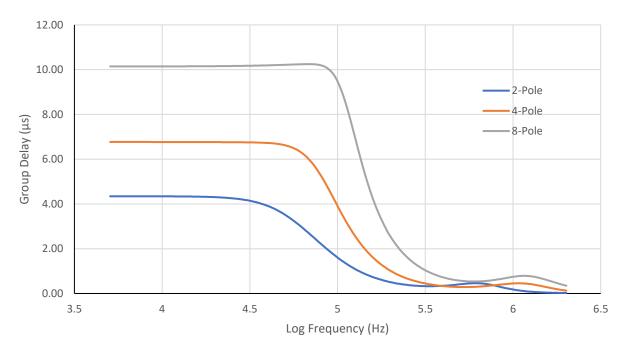

#### 3.2 Signal Differentiation

Figure 3.5 shows a circuit diagram of the set-up of the ADC, DAC, and FPGA. Communication between these components used a serial peripheral interface (SPI) bus, which is designed for short distances. To communicate between the PCB boards, ribbon cables with alternating signal and ground wires connections were implemented to reduce crosstalk and control the impedance as well as added  $100~\Omega$  source resistors to attenuate the signal reflections. After the processed signal is output by the DAC, it is first conditioned by a AMP03GS precision, unity gain differential amplifier<sup>3</sup> and is then buffered by a unity gain line driver OP27G lownoise precision amplifier.<sup>4</sup> An external power source providing  $\pm 15$ V was also built to power the entire set up.

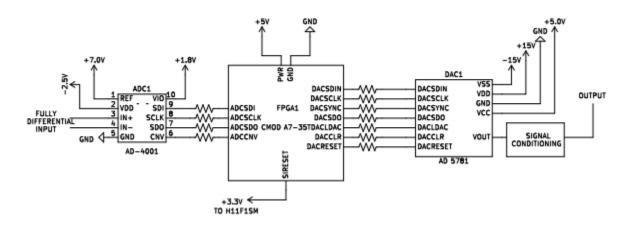

Figure 3.5: Schematic of the ADC, FPGA, and DAC.

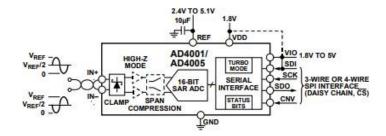

The ADC used was an Analog Devices AD4001. The AD4001 is a low power, high accuracy analog to digital converter. It outputs a 16-bit integer which has a range of -5V to +5V, yielding a resolution of 152.6  $\mu V$ . It can convert and output a maximum of 2 MSPS and communicates via a modified SPI protocol. Figure 3.6 shows the functional block diagram of the AD4001.

Figure 3.6: Functional block diagram of the AD4001 Analog-to-Digital Converter. <sup>5</sup>

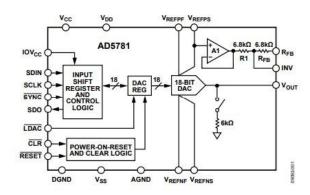

The DAC used was an Analog Devices AD5781. The AD5781 is a low power, high accuracy digital-to-analog converter. It takes in a 24-bit instruction, consisting of a 4-bit register access command, an 18-bit integer corresponding to the desired output voltage in the range of -10~V to +10~V, and two additional bits that are not used. This yields a resolution of 76.3  $\mu$ V. It can accept a maximum clock frequency of 35 MHz and communicates via SPI. Figure 3.7 shows the functional block diagram of the AD5781.

Figure 3.7: Functional block diagram of the AD5781 Digital-to-Analog Converter.<sup>6</sup>

The AD4001 and the AD5781 were controlled via a CMOD-A7 35T which is built around a Xilinx Artix-7 FPGA. The VHDL-2008 code used to control both components works in parallel to minimize downtime between reading data in from the ADC and outputting it to the DAC. Additionally, the low-pass differentiating FIR filter discussed later in Chapter 4, as well as the integrator reset controller, was programmed into the FPGA. The code controlling these three processes is included in the Appendix. The CMOD-A7 was modified from its standard 12 MHz clock to an 80 MHz clock, which theoretically would allow up to 1.33 M samples per second. Through experimentation, it was determined that the maximum reliable throughput of this set-up

of 667 k samples per second was achieved by slowing the clock down to 20 MHz. We believe the limitation was SPI inter-board connection. Figure 3.8 shows a picture of the CMOD-A7 35-T.

Figure 3.8: Picture of the CMOD-A7 35T.<sup>7</sup>

#### 3.3 References

- 1. Finlay, D. J.; Dodwell, P.C.; Caelli, T.M.; The wagon-wheel effect. *Perception*. **1984**, *105* (13), 237–248.

- 2. Analog Devices, ADA4940-1/ADA4940-2 Datasheet Rev E., Norwood MA **2018**. https://www.analog.com/media/en/technical-documentation/data-sheets/ADA4940-1\_4940-2.pdf.

- 3. Analog Devices, AMP03 Datasheet Rev E., Norwood MA, **2003**. https://www.mouser.com/datasheet/2/609/AMP03-1503769.pdf.

- 4. Analog Devices, OP27 Datasheet Rev H., Norwood MA, **2015**. https://www.analog.com/media/en/technical-documentation/data-sheets/OP27.pdf.

- 5. Analog Devices, AD4001/AD4005 Datasheet Rev C., Norwood MA, **2021**. https://www.analog.com/media/en/technical-documentation/data-sheets/ad4001-4005.pdf.

- 6. Analog Devices, AD5781 Datasheet Rev E., Norwood MA, **2018**. https://www.analog.com/media/en/technical-documentation/data-sheets/AD5781.pdf.

- 7. Digilent, CMOD A7 Reference Manual, Pullman, WA, Date Unknown, https://digilent.com/reference/programmable-logic/cmod-a7/reference-manual.

#### Chapter 4: Low-Pass Differentiation

#### 4.1 Standard FIR Filters

The output of the capacitor feedback operational amplifier is an example of a continuous time signal. Thus, this system takes an input system I(t), and outputs a transformation of that data O(t).

$$O(t) = T\{I(t)\}.$$

This transformation can be accomplished through the implementation of a carefully constructed filter. Finite impulse response filters are filters that have no feedback into the filter and whose impulse response only accounts for data within a specific duration. The general formula used for a FIR filter is

$$O(n) = \sum_{i=0}^{N} c_i I(n-i),$$

where N is the number of taps/samples used to filter the data, and c is the ith coefficient, or impulse response. Outside of these values, c is zero, which means that for a sampling time of  $t_s$ , the total impulse response duration is  $t_s$  (N-I). At the next sampling instance, I(0) is added to this register as i=0. The other values in the register are shifted down by one; i=0 becomes i=1, i=1 becomes i=2... until the last value at i=N-I, which is shifted out of the register.

In a standard direct-form FIR filter, when viewed in the time domain, the values of  $c_i$  create a moving "window" through which certain values are used to process the signal, and outside of the window the values are discarded. This mathematically is represented by a convolution

$$O(t) = I(t) * W(t),$$

where I(t) is the input signal and W(t) is the window function. Different window functions can be convolved with the input signal depending on the desired frequency response of the filter<sup>2</sup>.

The values of the coefficients in a FIR filter can be designed such that it can perform as a variety of filters, e.g., high pass, low pass, or in this application, a low-pass differentiator. Proper design of the filter coefficients can allow certain frequency bands through while attenuating others. For a switched integrator STM, a low pass differentiating filter is desirable to help eliminate high frequency noise while still effectively extracting the tunnelling current.

Additionally, the characteristics of the FIR filter can be tuned such that it acts as a linear phase

filter in the desired frequency region, which ensures that the group delay for the system will be constant, preventing signals with different frequencies from shifting relative to one another.

Increasing the number of taps in a FIR filter will generally improve the desired characteristics, to include the sharpness of the transition from pass band to stop band and the amount of attenuation in the cut-off band. However, this will introduce a time delay equal to roughly half of the total impulse response duration. This time delay needs to be considered along with other time delays in the system, such as the anti-aliasing filter delay from Section 3.1.1. If the total time delay results in a phase shift of 90° or greater, this can lead to instability and oscillation of the STM control loop as discussed in Section 2.2.1.

The Nyquist frequency is another critical component to ensure proper design and functioning of a FIR filter. The Nyquist frequency of a filter is the maximum input signal frequency that filter can sample without aliasing; sampling signals above this frequency can result in the appearance of false signals. The Nyquist frequency is half of the sampling frequency, meaning if a filter samples a signal at 2 MHz, the Nyquist frequency of that filter would be 1 MHz.<sup>3</sup> Thus, increasing the sampling rate (which corresponds to decreasing the time between samples, or the sampling time, of a filter) will increase the bandwidth of the filter.

#### 4.2 Low-Pass Differentiating FIR Filter

An interesting algebraic property of convolutions which can easily be seen from the definition of a convolution is that the derivative operator is communicative, i.e.

$$\frac{d}{dt}I(t)*W(t) = I(t)*\frac{d}{dt}W(t).$$

Thus, the derivative of an input signal I(t) can be extracted by running it through a filter with the derivative of the desired window function.<sup>4</sup> This property is useful, since as discussed in Section 2.1.1, the output of a capacitor feedback operational amplifier is related to the integral of the current into it. The differentiating FIR filter thus also allows for the recovery of the input tunnelling current. A consequence of this is that one of the key features of a differentiating FIR filter is the coefficients are anti-symmetric.

The gain of a differentiator in the time domain is proportional to the RC time constant

$$V_{out}(t) = RC\left(\frac{dV_{in}}{dt}\right).$$

Unit analysis of this gain shows that the gain has units of seconds. The gain of a non-inverting differentiator can be expressed in the frequency domain as

$$\frac{V_{out}(\omega)}{V_{in}} = j\omega RC,$$

which shows that gain is proportional to frequency and has an output phase shift of +90°. In the linear response region, this means that high frequencies will be amplified more than low frequencies. The required dynamic range of gain can create challenges in the required accuracy of the coefficients and the dynamic range of the DAC.

For a practical differentiator, the frequency range of differentiation must be limited. The FIR filter gain also needs to fall below the least significant bit of the DAC at or below the Nyquist sampling frequency to prevent aliasing noise from being amplified by the differentiator. Steep fall-off to and strong attenuation in the stop band generally requires many coefficients but this requirement can be relaxed due to the additional attenuation provided by the pre-ADC low-pass anti-alias filter.

#### 4.3 Software Design

Figure 4.1: VHDL-2008 code block diagram.

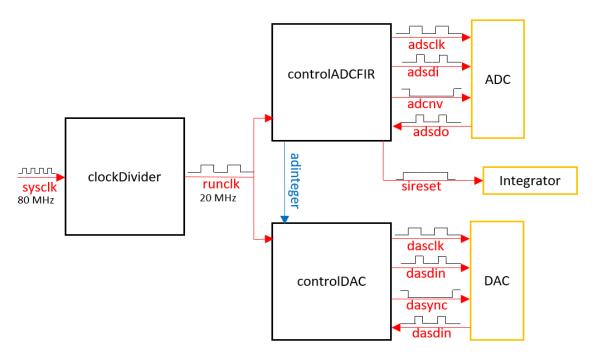

The VHDL-2008 code is included in Appendix A.2. It features three major processes; one to generate the 20 MHz clock, one to control the ADC and the FIR filter, and one to control the DAC. Figure 4.1 shows the block diagram of the relationship between these three processes. Figure 4.2 shows the global timing diagram showing the coordination between the ADC, the DAC, and the FIR filter. The DAC is the rate limiting step, requiring 30 clock cycles to output one transmission. This process runs in parallel to first the combined ADC and FIR filter.

<u>Process clockDivider:</u> This process takes the 80 MHz and divides it down to 20 MHz, which is used to run the rest of the operations. Additionally, it generates a 2 MHz clock to control the anti-aliasing Bessel filter if it is in use.

Process controlADCFIR: The ADCNV pin is taken low on the first clock cycle, signaling the ADC to begin outputting its 16-bit signal. The ADC takes 20 clock cycles to output its 16-bit binary signal to the FPGA on the ADSDO pin, which stores it as the corresponding decimal integer. Upon completion of the ADC output, the ADCNV pin is taken high, which switches the ADC from outputting data to converting the input voltage into a new integer. This integer is then input into the FIR filter register, which takes five clock cycles to process the data. On clock cycle 26, the FPGA completes the transformed signal. Additionally, when the ADC outputs a value corresponding to a specified min or max limit, this is means capacitor is saturated beyond the limits that the ADC can measure and needs to be reset, which results this process sending a signal to the switch to initiate a reset. A buffer of ±4.8 V was used as the limits to keep the data

Figure 4.2: Differentiator master timing diagram. While the DAC is outputting processed data, the ADC is receiving new data to run through the FIR filter or converting data for the next transmission.

well within the operational limits of the ADC. The process for this is discussed in detail in Section 4.4.

Process controlDAC: On the first clock cycle of the subsequent iteration of the algorithm, the output of the FIR filter is shifted into the process controlling the DAC. On the second clock cycle, the DASYNC pin of the DAC is taken low to signal an incoming signal transmission. Over the next 24 clock cycles, the output of the FIR filter is converted into an 18-bit binary signal and output on the DASDI pin, along with the appropriate register access code. On clock cycle 28, the DASYNC pin is taken high to signal completion of a signal transmission and is held high long enough for the DAC to process and output the corresponding voltage before the whole cycle repeats again. Thus, on iteration *n* of the algorithm, the DAC is outputting the result of the *n-1* FIR processed ADC conversion.

The ADC can be used without configuration based on its standard settings, but the DAC requires that the configuration register be accessed to appropriately configure it before it begins converting transmitted values. At start-up, controlDAC outputs 1000 configuration transmissions to ensure DAC has received configuration data, and then begins outputting values to DAC for it to convert. This was initially done while designing the code for troubleshooting simplicity purposes; during power-on, the DAC and FPGA receive power at the same time. Identifying exactly when either component is ready was not attempted. Instead, hard-coding numerous configuration transmissions ensured the DAC receives at least one configuration message before controlDAC starts attempting to transmit data. It was not removed from the code because it was not found to negatively affect the performance of the system and because the total time for 1000 transmissions with a 20 MHz clock is only 1.5 ms.

#### 4.4 Capacitor Reset

Since the ADC is limited to ±5 V, the capacitor will need to be reset before the ADC receives voltages at these limits. For the ADC, this corresponds to the integers 32767 (+5 V) and 32768 (-5 V) since it uses two's complement to express negative numbers. If controlADCFIR, detects that the ADC output is between 31400 (+4.8 V, rounded down) and 34100 (-4.8 V, rounded up), it will begin outputting a +3.3 V signal to the switch for 2 ms, during which time capacitor switch will close allowing the capacitor to reset. The 0.2 V buffer around the two listed values accounts for any offset errors in the input voltage and prevents the ADC from being stuck

at the rails without being able to reset. During the reset time, the clock signals to the ADC and DAC will not be output, effectively freezing the input and output. Once 2 ms have passed, the entire process will restart. 2 ms was chosen as a safe value during testing that will was short enough that it did not significantly distort data in the expected operating ranges, but long enough that the capacitor had more than enough time to discharge fully. It is possible that as the system is eventually revised, this time could be reduced significantly.

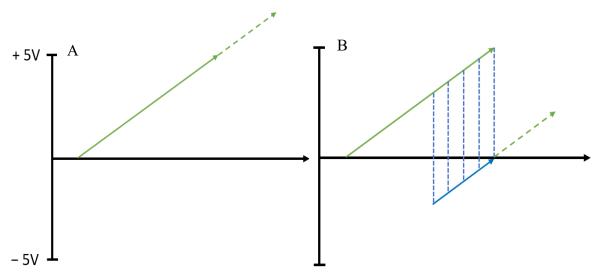

Figure 4.3: Graphical description of the correction made to the FIR register upon resetting. (A) A constant tunnelling current into the integrator will generate a linear voltage ramp (solid green line) that can exceed the limits of the ADC (dashed green line). (B). Resetting the integrator will introduce a false discontinuity in the output of the integrator, which will degrade the signal when differentiated. Subtracting the most recent value stored in the FIR register from every value in the register (dashed blue lines) will translate the signal so that the slope is preserved, but the discontinuity is removed (solid blue line).

After the reset, the fully discharged capacitor will start back at 0 V and resume integrating the signal. This will introduce a discontinuity in the output of the integrator that is not representative of the current input. If the old values in the FIR filter are used, this large discontinuity will propagate through the differentiator, resulting in a spike in the output of the differentiator until it has propagated through the FIR filter. If the values in the FIR filter are reset entirely to zero, there will be a delay as the filter refills. Because this is a differentiator, a continuous slope is expected in the data values in the filter and can be accomplished by patching the discontinuity. This patch is implemented on each reset by subtracting the most recent value in the FIR filter from all the data values. This adjusts the values in the register so that the most

recent value is 0 V which will stitch with the next value after reset (close to zero) and continue the same slope as the signal before reset. A graphical representation of the process is found in Figure 4.3.

#### 4.5 Design of Filter for Testing

Identifying the conditions under which a filter will be used is important for understanding how to optimize the filter for desired performance. The ideal differentiator would have a linear response up to the Nyquist frequency, and then a step-response drop off to extremely high attenuation. However, this is not possible, and trade-offs must be made to maximize performance.

- Sharp cut-off: In order to achieve a very sharp cut-off, the number of coefficients in

the filter must be very high. The trade-off to this is that the time delay of the filter

increases linearly with the order of the filter, and since the STM requires real-time

feedback, the time delay cannot be allowed to grow too large without resulting in

control loop instability.

- 2. Large pass-band region: In order to have a pass-band that accommodates a large range of frequencies, the coefficients will have a range in magnitude. Coefficients with very high magnitude can cause the intermediate values within the FIR register to overflow due to integer limitations, and very small coefficients can reduce the intermediate values to below the resolution of the ADC or DAC and cause loss of information. An additional complication is the fact that VHDL-2008 is incompatible with floating-point numbers, so the floating-point coefficients had to be converted by multiplying the coefficients by a large enough power of 10 to achieve at most 6 integer digits per coefficient, and then dividing the sum by the same power of 10 at the end. If the disparity of the coefficient values is large enough, some of the smallest coefficients will express to zero, affecting the order of the filter and resulting in significant loss in information.

- 3. High attenuation: In order to achieve high attenuation in the stop-band, the order of the filter must be high, which circles back to the issues discussed above.

Considering the STM operation conditions, it is desirable to have high gain in the low frequency region to ensure that the ADC and DAC will be able to resolve the data. Extremely

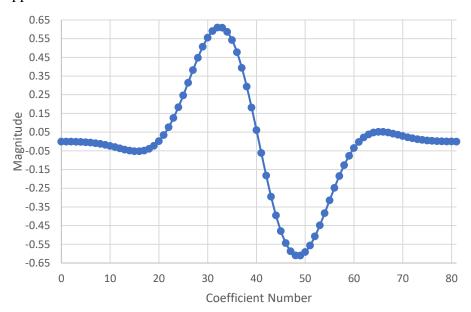

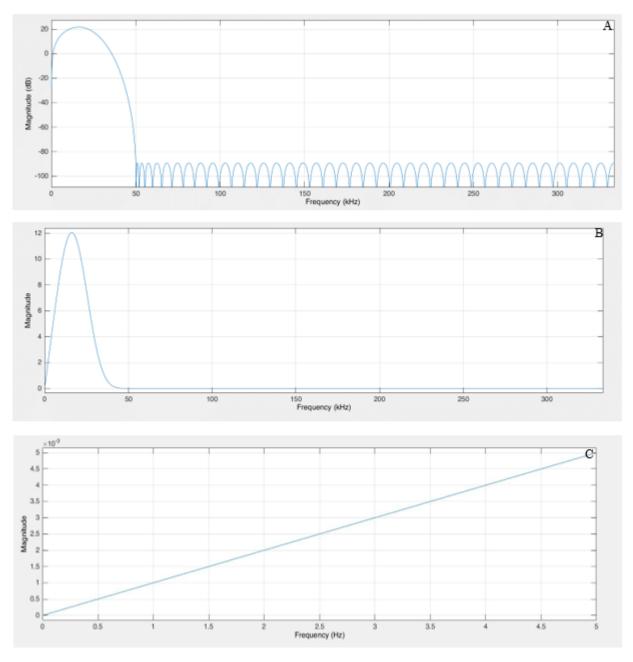

high attenuation was not prioritized because additional attenuation was achieved with the antialiasing filter. Numerous filters were used and tested throughout this project, and the filter described below was chosen for the tests in Chapter 5 because of the considerations discussed above. It was generated with the Filter Designer tool available in MATLAB<sup>5</sup> with the goal of achieving –90 dB attenuation below the Nyquist frequency, and with a linear response region up to 30 kHz to give ample bandwidth in which to test. Figure 4.4 shows the impulse response of this filter, and Figure 4.5 shows the magnitude response, both generated by MATLAB. Note that the coefficients are anti-symmetric as expected of a differentiator. The table of coefficients is included in Appendix A.1.

Figure 4.4: Impulse response of 81<sup>st</sup> order low-pass differentiating direct form FIR filter.

Figure 4.5: Magnitude response of 81<sup>st</sup> order direct-form differentiating FIR filter. (A) Magnitude (dB) vs frequency up to Nyquist frequency. (B) Magnitude (linear) vs frequency up to Nyquist frequency. (C) Magnitude (linear) vs frequency up to 5 Hz. This filter was determined through trial and error, and achieved the necessary compromises discussed in Section 4.5 to optimize performance for the tests in Chapter 5.

#### 4.6 References

- 1. McClellan, J.; Schafer, R.; Yoder, M., Signal Processing First. Pearson Education Inc. 2003.

- 2. Prabhu, K., Window Functions and Their Applications in Signal Processing. CRC Press. 2014.

- 3. Shannon, C., Communication in the Presence of Noise. *Proceedings of the IEEE*, **1998**, *86*, 2.

- 4. Read, R., The convolution theorem and its applications. *Structural Medicine-Protein Crystallography Course*, University of Cambridge, 2009 https://www-structmed.cimr.cam.ac.uk/Course/Convolution/convolution.html.

- 5. MathWorks, Using Filter Designer, 2023 https://www.mathworks.com/help/dsp/ug/using-filter-designer.html.

### Chapter 5: PCB Switched Integrator

There are trade-offs to be considered when designing a switched-integrator system. There is a trade-off between gain and system reset frequency dependent on the feedback capacitor. A smaller feedback capacitor yields higher integrator gain but will require frequent resets. Each reset introduces a deadtime that blinds the amplifier to changes of input current during the reset interval. To minimize disruption of STM operation, the resets must be carefully orchestrated into the STM control loop operation. See Section 2.2.2.

There is also a trade-off between time delay and noise attenuation related to the number of coefficients in the FIR filter. While attenuating the high frequency noise is important to prevent aliasing from interfering with the current signal, the FIR filter does not have to provide all the attenuation. This can allow fewer coefficients to be used, which can significantly decrease the time delay of the system. Additionally, the linear relation between gain and frequency requires that the system be carefully tuned to the expected sampling conditions.

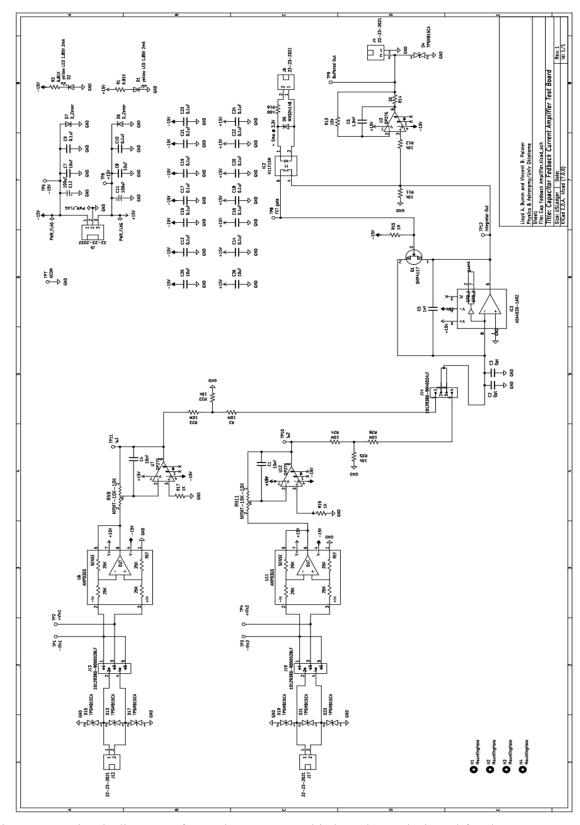

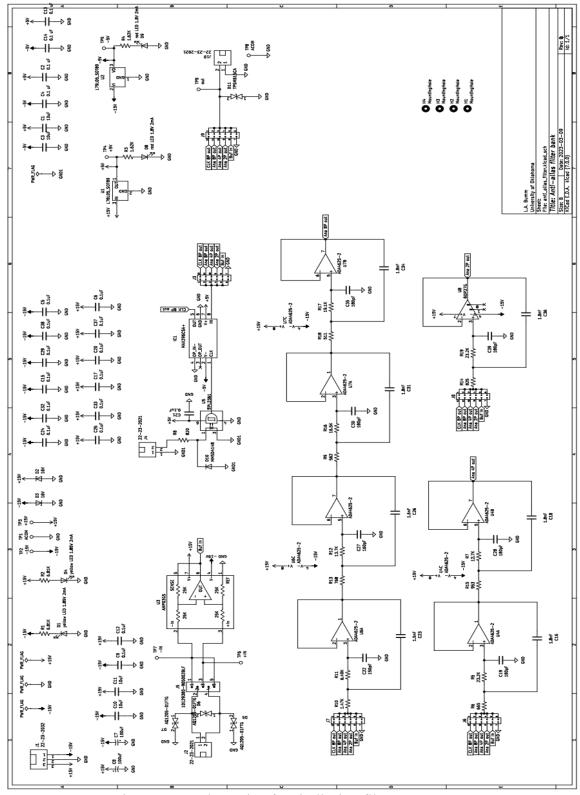

The effect of these design considerations will be discussed and shown in relation to the PCB design discussed in this chapter. The circuit diagram is found in Figure 5.1.

#### 5.1 Switched Integrator Test Circuit Design

The board is powered by  $\pm 15 \text{V}$ , and is protected with a system of zener diodes and capacitors to prevent damaging the board if power is improperly connected. Two current sources were included in order to allow for the possibility of more complex inputs for future testing. Each signal input is protected by TVS diodes. The J13 and J19 jumpers allow for selecting the input signal polarity. For these tests, the J13 jumper was configured to invert the polarity of the input signal to negate the inversion of the current amplifier. The signals are then conditioned by an AMP03G differential amplifier. The current source uses a 10 M resistor followed by a 1000x current divider. An input of 1 V provides 100 pA to the integrator. The integrator output is buffered and conditioned by an OP27G line driver. These OP27G amplifiers have a 10 k $\Omega$  resistor and 10 nF capacitor that contribute a pole at 1.6 kHz that contribute to the measured magnitude and phase of the integrator component.

Figure 5.1: Circuit diagram of PCB layout. Note this board was designed for the ADA4530 but was modified to accept the ADA4622 due to survivability issues experienced during testing.

The PCB was designed to use the ADA4530-1ARZ femtoampere input bias current electrometer amplifier as the integrator, because of its very small input current offset and voltage noise. However, during initial testing we were not able to get the ADA4530 to work. Instead, the ADA4622, a precision JFET transistor op amp with a high bandwidth (-3dB = 15.5 MHz) and slew rate ( $\sim 20 \text{ V/}\mu\text{s}$ ) was substituted instead The feedback capacitor C5 was initially planned to be a 1 nF capacitor, but during testing it was found that the gain was too small, and and after testing that will be discussed in the next sections, was replaced with a 5 pF capacitor. This means that the expected gain of the amplifier is

$$A_I = \frac{1}{5 \times 10^{-12} \,\mathrm{F}} = 200 \times 10^9 \mathrm{F}^{-1}.$$

The SMP4117<sup>4</sup> acted as the switch, and was opened and closed by the H11F1SM<sup>5</sup>, which receives the +3.3 V signal from the FPGA prior to the ADC reaching its limits and closes the switch of the SMP4117, allowing the capcitor to discharge. The PCB was designed with a provision for loading the input with capacitance for testing, C2 and C3. For these tests C1 and C2 were populated by MMBD301-TP schottky diodes to protect the inverting input from exceeding ±0.35 V. The output of the switched integrator is buffered by an OP27G and output to the anti-aliasing filter.

### 5.2 System Performance Analysis

All tests were performed with a Stanford Research Systems DS345 30 MHz synthesized function generator.<sup>6</sup> The signals out of the function generator, integrator, and differentiator were analyzed with a Keysight DSOX1204G oscilloscope.<sup>7</sup> Also note that a small DC offset in the range of -0.12 V was applied to the function generator output waveforms to compensate for an apparent input offset current in the integrator. This offset was manually adjusted for each measurement to cancel the DC drift of the integrator output.

#### 5.2.1 Demonstration of System Performance

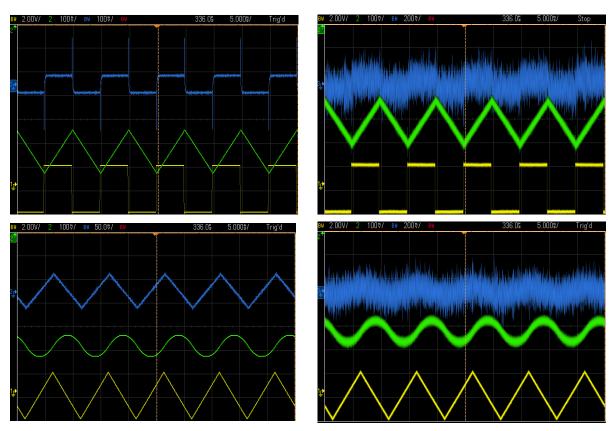

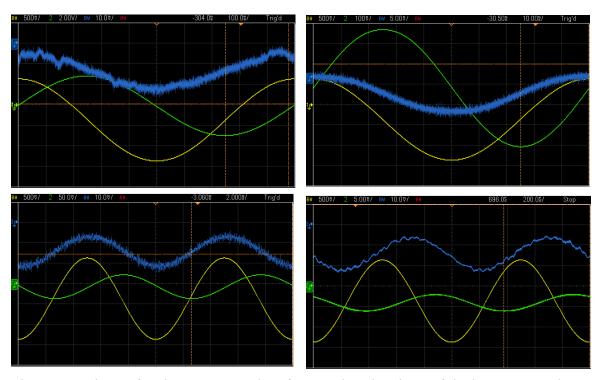

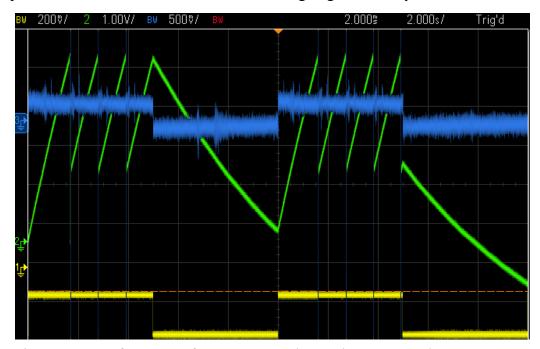

Figure 5.2 demonstrates the ability of this system to effectively process various signal waveforms. Triangle and square waves at 100 Hz were input to the system with max amplitude of  $\pm 2$  V for the function generator. The output from the integrator were parabolas and triangle waves respectively, matching the expected shape and sign of the integral of triangle and square waves.

Next, the relative accuracy of the gain of both the integrator and differentiator can be checked by comparing the rough magnitudes of the signals resulting from the input square wave. For the 4 V peak-to-peak square wave, the integrator output slope has a magnitude of 40 V/s, and the differentiator output has a magnitude of 80 mV peak-to-peak. The resulting gains are  $2\times10^{11}$  F<sup>-1</sup> for the integrator,  $1\times10^{-3}$  s for the differentiator, in line with the expected values and yields

Figure 5.2: Demonstration of integration and differentiation of input signal. Yellow is the input signal, green is the output of the integrator, and blue is the output of the differentiator. Bottom two images show a 100 Hz triangle wave with ~2V amplitude, top two images show a 100 Hz square wave with same amplitude. Images on the left are after averaging over 65536 samples. Images on the right are without averaging.

an overall transimpedance gain of  $2\times10^8$  V/A. The frequency response of the above component gains is checked in the next section.

When the output of the differentiator is averaged over a large number of samples, the original input waveform is recovered. Without averaging however there appears to be a significant amount of noise on both the differentiator and the integrator. Additionally, averaging the signal over so many samples is not ideal for STM application, as the STM requires real-time feedback. Comparing the averaged and raw data out of the integrator shows a slight fuzziness which indicates noise on the integrator. Since differentiators are highly susceptible to noise, it is possible that the noise on the integrator is being amplified by the gain of the differentiator and will need to be mitigated to produce cleaner signals.

#### 5.2.2 Magnitude vs Frequency Response

Next, the gain of both the integrator and the differentiator were measured individually across a wider range of frequencies and compared to the theory. For these tests, the gain was computed in the time domain with an input sine wave represented by the formula

$$V_{in} = V_I \sin 2\pi f t$$

.

Given that the 1000x current divider outputs 100 pA of current for every 1 V of input signal, and defining the resulting transadmittance gain as

$$A_g = 1 \times 10^{-10} \left(\frac{A}{V}\right),$$

the equation for the current coming into the amplifier is

$$I_{in} = V_I A_g \sin 2\pi f t.$$

The voltage output of the integrator is another sinusoid, and since it is related to the integral of the input current, it takes the form,

$$V_{out} = V_O \cos 2\pi f t,$$

Plugging these equations into the equation shown in Section 2.2.2 for the gain on an integrator in the time domain yields

$$\frac{\left(\frac{dV_{out}}{dt}\right)}{I_{in}} = \frac{2\pi f V_O}{V_I A_O} = A_I.$$

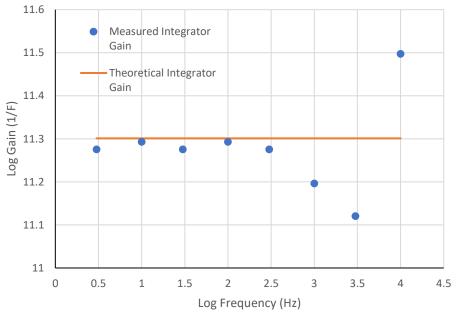

The voltage out of the integrator was measured at every half decade of frequency from 1 Hz to 3000 Hz and is plotted in Figure 5.3 to determine the gain. Below 3000 Hz, the gain matches

very closely with the expected value of  $2 \times 10^{11}$  F<sup>-1</sup> but begins to deviate above 3000 Hz due to the roll off of the gain of due to U12 and U7 that begins around 1.6 kHz. This shows that the integrator is behaving as expected.

Figure 5.3: Measured gain of the integrator. Below 3000 Hz, the amplifier gain was within 10% of the theoretical value based off the feedback capacitance and can be seen to decrease as frequency increases as expected. Above 3000 Hz, the poles from U7 and U12 cause the gain to deviate.

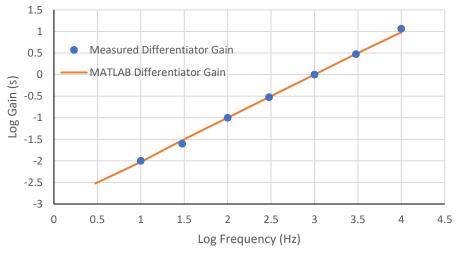

Figure 5.4: Measured gain of the differentiator. The slope of the linear differential gain was measured to follow the same relationship as predicted from the MATLAB filter designer tool.

The gains of the differentiator were measured via the same means and compared to the predicted values generated by the MATLAB Filter Designer tool. The measured gain vs frequency relationship for the differentiator is found in Figure 5.4. The values were found to nearly match the MATLAB values, indicating that the differentiator is behaving as expected and that the Filter Designer tool can be used to produce filters with desired gains in specific frequency bands with this implementation. The discrepancy at low frequencies is most likely due to precision limitations of the oscilloscope.

### 5.2.3 Phase Response and Time Delay

Next, the phase of both the integrator and the differentiator were measured compared and compared to the theory. In the frequency domain, the gain of a non-inverting integrator is

$$\frac{V_{out}}{V_{in}} = \frac{1}{j\omega RC}.$$

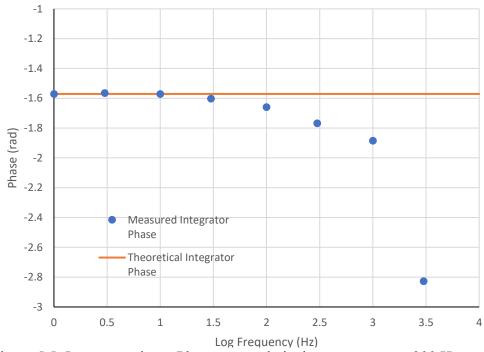

This shows that the expected phase response of this integrator is  $-90^{\circ}$ . To measure the phase response of the integrator, the time delay between an input sine wave and the output of the integrator were compared to the period of the input sine wave. As shown in Figure 5.5, the phase

Figure 5.5: Integrator phase. Phase stays relatively constant up to 300 Hz at  $-90^{\circ}$  as expected. Beyond that, the effect of the additional poles contributed by U12 and U7 affect the shape of the graph.

is relatively constant up to 300 Hz at roughly  $-90^{\circ}$ . The effect of the pole at 1.6 kHz on U7 and U12 can be seen above 1 kHz.

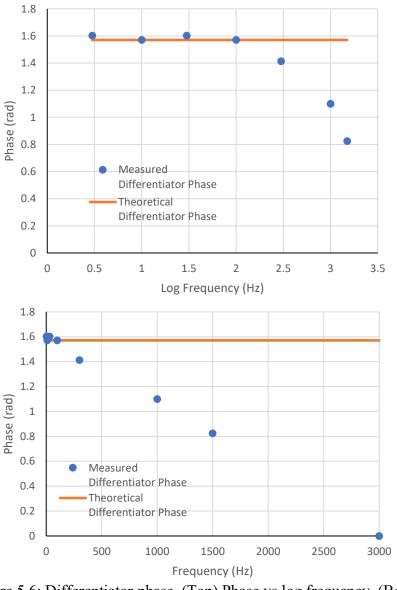

Figure 5.6 shows the differentiator phase as a function of frequency compared to the standard value for a differentiator. As expected, the values start near  $+90^{\circ}$ , but decrease as frequency increases, which can be explained by the group delay of the FIR filter compared to the input frequency. The group delay of the differentiator can be extracted from the slope of linear plot, yielding a group delay of 83  $\mu$ s.

Figure 5.6: Differentiator phase. (Top) Phase vs log frequency. (Bottom) Phase vs linear frequency. Phase stays relatively constant up to 300 Hz at 90° as expected. Beyond that, the phase begins to decrease because of the time delay of the FIR filter.

Figure 5.7 shows the relationship between the input, integrator, and differentiator waveforms with an increase in frequency. At low frequencies, the differentiator appears to be in phase with the input waveform, with the integrator 90° out of phase. This is because of the opposing phase response of the differentiator and integrator, which cancel each other out. As frequency increases however, the group delay causes the differentiator to not fully correct back in phase with the input signal. This is due to the FIR filter and the anti-aliasing filter contributing time delays in the system that are not noticeable at low frequencies but become more apparent at high frequencies.

Figure 5.7: Phase of entire system. At low frequencies, the phase of the integrator and differentiator cancel out, leaving the differentiated signal in phase with the input. As frequency increases, the time delay of the FIR filter causes the differentiator signal to fall out of phase with the input. (Top left) 1 Hz. (Top right) 10 Hz. (Bottom left) 100 Hz. (Bottom right) 1000 Hz.

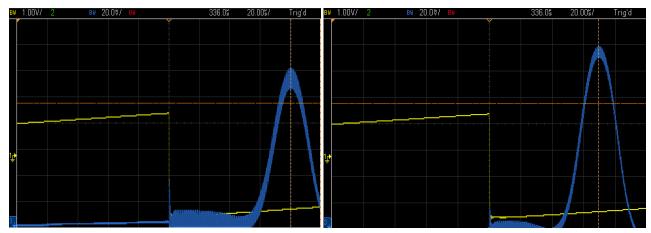

To measure and verify the total system group delay, a sawtooth wave was used as the input because the discontinuity is easy to correlate to the output of the differentiator. Measuring the time delay shown in Figure 5.8 gives a total time delay from input of 80  $\mu$ s. This is very close to the measured time delay from Figure 5.6 of 83  $\mu$ s, again showing the system is working as expected.

Figure 5.8: Determination of group delay. With the Sallen-Key filter (left) and without (right). The time delay is increased by 10 µs compared to the rest of the system, in line with Figure 3.4. It also matches closely with the measured group delay of 83 µs from Figure 5.6.

#### 5.2.4 Low-Frequency, Low-Amplitude Analysis

Figure 5.9: Performance of system at low amplitudes and frequencies. Input was a 0.1 V square wave at 0.1 Hz. Signals were processed with boxcar averaging.

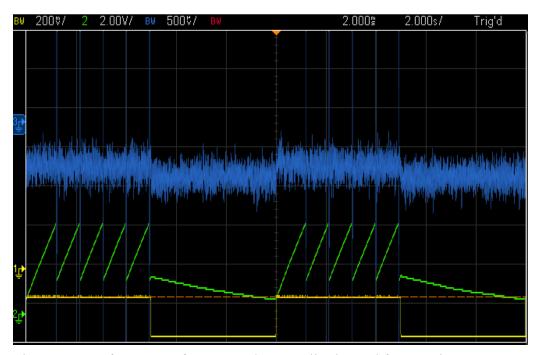

As the tunneling currents expected in these STM operations are very small, the expected performance of the system is better tested at low-frequency and low amplitude. Figure 5.9 shows the performance of the filter under a 0.1 V, 0.1 Hz square wave. At this frequency, the resets are

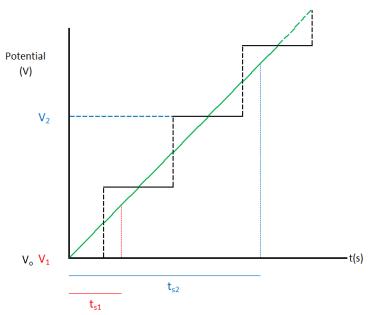

apparent in the capacitor, occurring several times per cycle. The difference in slopes highlight the drift inherent in the system, and shows that even with the offset discussed earlier applied, the drift could not be fully cancelled out. While the signal on the integrator is very sharp, there is still a high amount of noise on the differentiator. This was unexpected, as reducing the amount of noise out of the integrator should reduce the noise on the differentiator. A possible explanation for this was the effect of small slopes combined with the resolution of the ADC. If the input from the integrator results in a high slope, then there will be significant changes in the voltage between samples. However, if the voltage does not increase beyond the resolution of the ADC between samples, then the ADC will output the same voltage in between samples, resulting in the slope being transformed into a straight line. This could cause the ADC output to bounce between zero and very small numbers due to random fluctuations, which when compared to the small voltages it is trying to output would result in an increase in the signal-to-noise ratio. Figure 5.10 demonstrates this graphically and shows that the combination of the sampling time and the input voltage will determine if the ADC is able to resolve input voltages reliably.

Figure 5.10: Relationship between sampling time and ADC resolution. The green line represents the actual voltage being input to the system. The black line represents the digitized voltage the ADC will interpret in a certain range.  $V_0$  is the voltage sampled prior to the current sampling. The slope of the voltage being sampled does not change between the two sampling times, but long sampling times ( $t_{s2}$ ), allow for the voltage to change enough that the second voltage ( $V_2$ ) is substantially different from  $V_0$ , and thus a slope can be measured. Short sampling times ( $t_{s1}$ ) can result in the next sampling resulting in the ADC outputting a voltage ( $V_1$ ) with the same value as  $V_0$ . Thus, the FIR filter would interpret this as a straight line.