## Toward Cascading Failure Mitigation in High Voltage Power System Capacitors

A thesis presented in fulfilment of the requirement for the degree of

## Doctor of Philosophy

to the

Institute of Energy and Environment

Department of Electronic and Electrical Engineering

University of Strathclyde

Calum J. Mackinnon 28<sup>th</sup> of February, 2022 **This thesis** is the result of the author's original research. It has been composed by the author and has not been previously submitted for examination which has led to the award of a degree.

**The copyright of this thesis** belongs to the author under the terms of the United Kingdom Copyright Acts as qualified by University of Strathclyde Regulation 3.50. Due acknowledgement must always be made of the use of any material contained in, or derived from, this thesis.

## Acknowledgements

An ancient truism states 'it takes a village to raise a child': a PhD is no exception to this sentiment, albeit as an incomparably fleeting task and even if a participant benefits from life experience beyond its object; as an individual effort this work might not strictly be collaborative, but I am lucky to have been able to undertake it amid a community of direct and indirect contributors at the University of Strathclyde and further afield, who I hope know who they are. I thank Professor Brian Stewart for his enthusiasm, guidance, support, tact, and patience throughout the course of this research project. Secondly, thanks go to you the reader for any investment you make of your time into this work, as its value would otherwise be significantly limited. University and industry colleagues including: Andrew Carlin; Alan Davenport; Dr. Martin Given; Prof. Scott McMeekin; Kevin Butter; Alastair Ferguson; David Monkhouse; and Dr. Antonios Tzimas contributed practical support, technical insights, and facilitated site visits. Dr. Vic Catterson, Dr. Michael Gilroy, Dr. Phil Bagley, Dr. Sotirios Terzis, Dr. Andrew Roscoe, Prof. Stephen McArthur, Dr. James Irvine, Prof. Graeme Burt, and many others have been inspirational to me. Their example, enthusiasm, and openness have been instrumental in encouraging my interest in a PhD. I thank my family and friends for their patience, support, and understanding. If a dissertation can be dedicated then this is to my family, and in memory of Jim McShane: his inquisitive nature inspired my interest in technology at an early age. This work builds on a wealth of academic and industrial effort, in recognition that literature is only a subset of the understanding, know-how, and appreciation for a subject matter on the whole.

# Contents

| $\mathbf{A}$                                  | Abstract vii        |        |                                                                       |  |  |   |      |

|-----------------------------------------------|---------------------|--------|-----------------------------------------------------------------------|--|--|---|------|

| Li                                            | st of               | Publi  | cations                                                               |  |  | , | viii |

| 1                                             | Intr                | oducti | ion                                                                   |  |  |   | 1    |

|                                               | 1.1                 | Premi  | se                                                                    |  |  |   | 1    |

|                                               |                     | 1.1.1  | Hypothesis and Aim                                                    |  |  |   | 1    |

|                                               |                     | 1.1.2  | Approaches                                                            |  |  |   | 2    |

|                                               | 1.2                 | Conte  | xt                                                                    |  |  |   | 5    |

|                                               |                     | 1.2.1  | Energy Trilemma                                                       |  |  |   | 5    |

|                                               | 1.3 Interconnection |        |                                                                       |  |  |   | 6    |

|                                               |                     | 1.3.1  | High-Voltage Direct Current                                           |  |  |   | 7    |

|                                               |                     | 1.3.2  | Converter Topologies                                                  |  |  |   | 7    |

|                                               |                     | 1.3.3  | Early Experience of HVDC: the Nelson River Transformers $\ . \ . \ .$ |  |  |   | 11   |

|                                               |                     | 1.3.4  | Criticality, Reliability, and Availability                            |  |  |   | 12   |

|                                               |                     | 1.3.5  | Design Informed by Reliability Centred Maintenance                    |  |  |   | 13   |

|                                               | 1.4                 | Comm   | nercial Considerations                                                |  |  |   | 14   |

|                                               |                     | 1.4.1  | Scottish Power Energy Networks' Converter Station                     |  |  |   | 14   |

|                                               |                     | 1.4.2  | A Changing Network                                                    |  |  | • | 22   |

| <ul> <li>1.3.2 Converter Topologies</li></ul> |                     |        |                                                                       |  |  |   | 23   |

|                                               | 2.1                 | Resear | rch Avenues                                                           |  |  |   | 23   |

|                                               |                     | 2.1.1  | Capacitors                                                            |  |  |   | 23   |

|                                               |                     | 2.1.2  | Motivations for Fault Mitigation                                      |  |  |   | 25   |

|                                               |                     | 2.1.3  | Health Assessment                                                     |  |  |   | 26   |

|                                               |                     | 2.1.4  | Condition Monitoring                                                  |  |  |   | 27   |

|                                               |                     | 2.1.5  | General Electric (Alstom Power)                                       |  |  |   | 27   |

|                                               |                     | 2.1.6  | Approaches in Data Analytics                                          |  |  |   | 28   |

|                                               | 2.2                 | Techn  | ical Background                                                       |  |  |   | 30   |

|                                               |                     | 2.2.1  | Capacitors in Power Systems                                           |  |  |   | 30   |

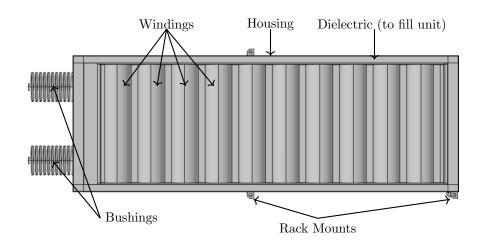

|                                               |                     | 2.2.2  | Unit Design                                                           |  |  |   | 30   |

|                                               |                     | 2.2.3  | Capacitor Banks                                                       |  |  |   | 36   |

|                                               |                     | 2.2.4  | Cascading Failure                                                     |  |  |   | 37   |

|                                               |                     | 2.2.5  | Approaches to Failure Detection                                       |  |  |   | 38   |

| 3 | Mo                 | lelling                                                 | 40              |

|---|--------------------|---------------------------------------------------------|-----------------|

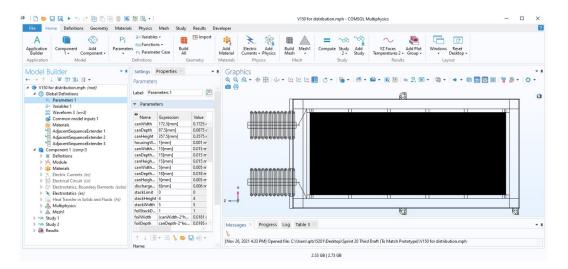

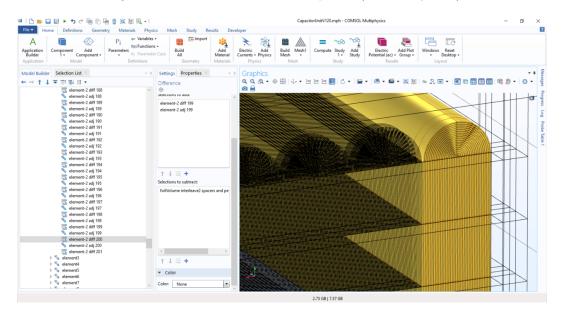

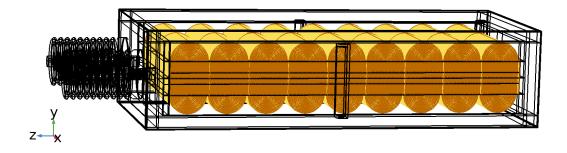

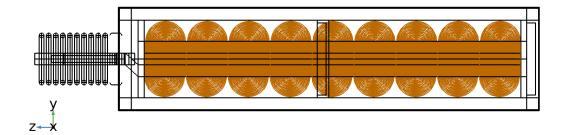

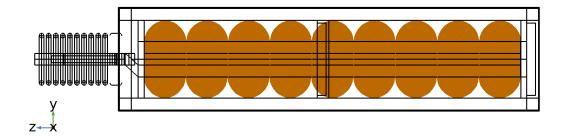

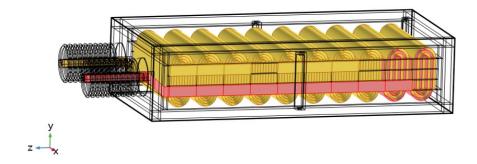

|   | 3.1                | Modelling in COMSOL Multiphysics ${}^{\textcircled{R}}$ | 40              |

|   |                    | 3.1.1 Model File                                        | 41              |

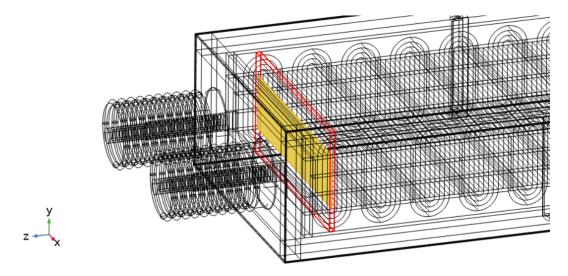

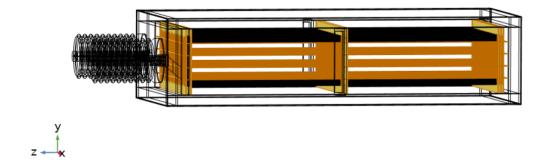

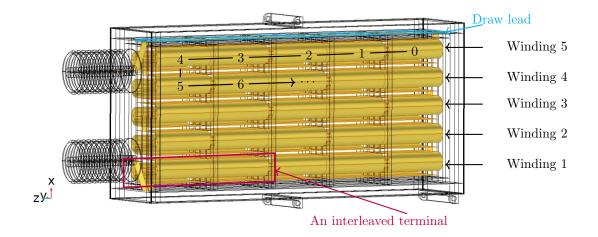

|   |                    | 3.1.2 Geometry                                          | 42              |

|   |                    | 3.1.3 Mesh Sequences                                    | 44              |

|   |                    | 3.1.4 Materials                                         | 46              |

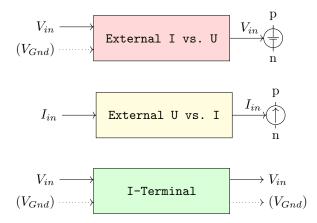

|   |                    | 3.1.5 Physics Interfaces                                | 47              |

|   |                    | 3.1.6 Means of Coupling                                 | 49              |

|   |                    | 3.1.7 Study Configurations                              | 50              |

|   |                    | 3.1.8 Post-processing                                   | 50              |

|   | 3.2                | Discussion and Modelling Trade-offs                     | 51              |

|   |                    | 3.2.1 Parameterisation                                  | 51              |

|   |                    | 3.2.2 Definitions                                       | 51              |

|   |                    | 3.2.3 Model Methods                                     | 58              |

|   |                    | 3.2.4 Indicative Configurations                         | 59              |

| 4 | Flor               | trical Effects                                          | 61              |

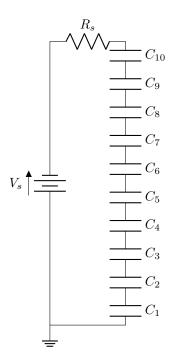

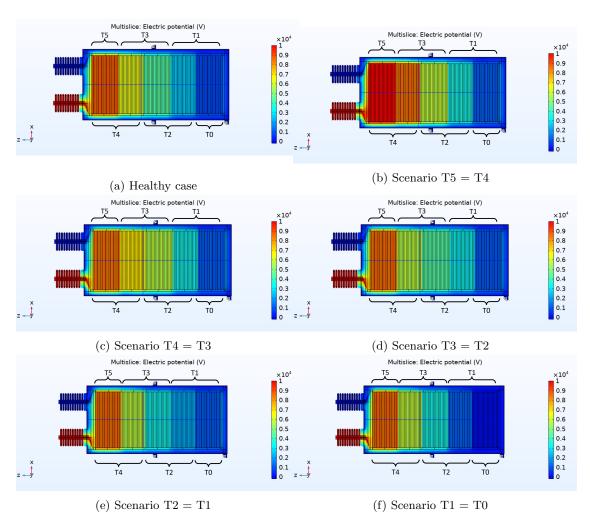

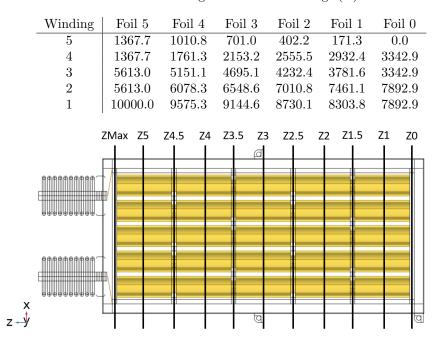

| 4 | 4.1                | Effects of Failure on Voltage Distribution              |                 |

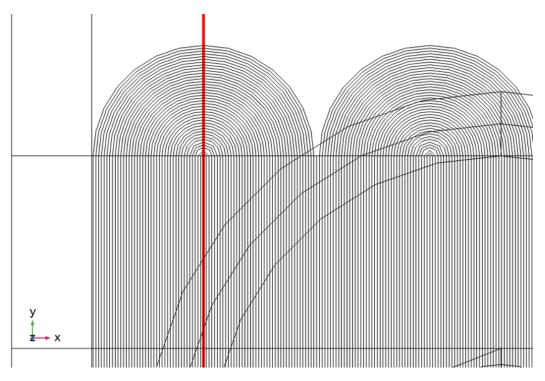

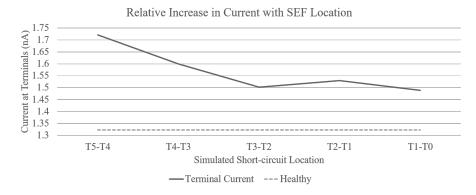

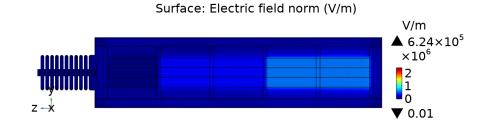

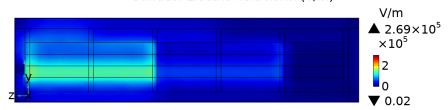

|   | 1.1                | 4.1.1 Simulation Studies and Results                    |                 |

|   |                    | 4.1.2 Discussion and Implications                       |                 |

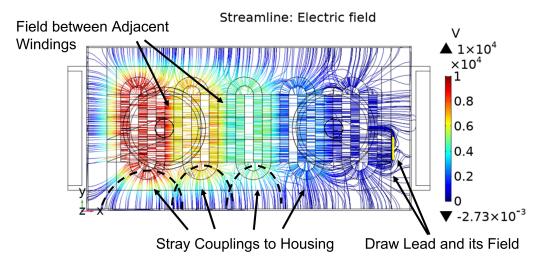

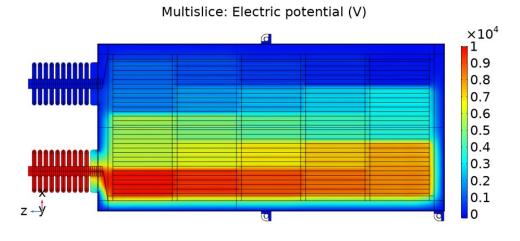

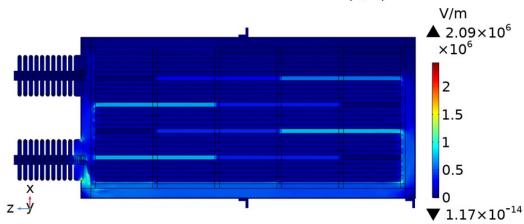

|   |                    | 4.1.3 Parasitic and Stray Capacitances                  |                 |

|   |                    | 4.1.4 Changed Terminal Characteristics                  |                 |

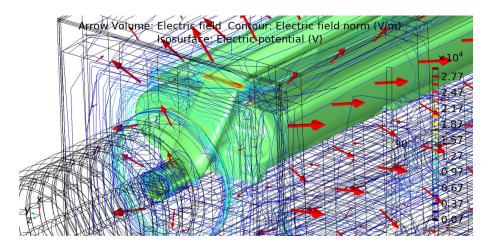

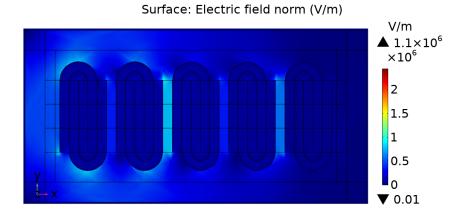

|   | 4.2                | Electric Field Effects in a Capacitor Unit              |                 |

|   |                    | 4.2.1 Setup                                             |                 |

|   |                    | 4.2.2 Simulation Studies                                |                 |

|   |                    | 4.2.3 Results                                           | 75              |

|   |                    | 4.2.4 Discussion                                        | 77              |

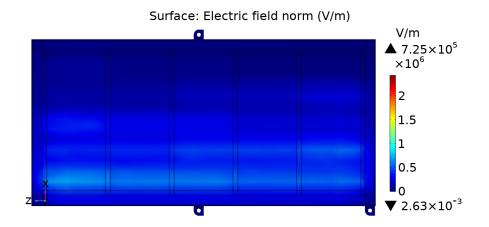

|   | 4.3                | Modelling Multiple Units                                | 81              |

|   |                    | 4.3.1 Simulation and Results                            | 81              |

|   |                    | 4.3.2 Discussion: First Study                           | 82              |

|   |                    | 4.3.3 Discussion: Second Study                          |                 |

|   | 4.4                | Conclusions                                             | 86              |

|   |                    | 4.4.1 Series Element Failure and Voltage Distribution   | 86              |

|   |                    | 4.4.2 Electrical Stress                                 | 86              |

|   |                    | 4.4.3 Multiple Units                                    | 87              |

|   |                    | 4.4.4 Further Work                                      | 88              |

| - | <b>701</b>         | rmal Effects                                            | 60              |

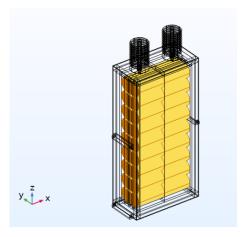

| 5 | <b>1 ne</b><br>5.1 | Introduction                                            | <b>89</b><br>89 |

|   | $5.1 \\ 5.2$       | Simulation Studies                                      |                 |

|   | 0.2                |                                                         | 90<br>01        |

|   |                    | 5.2.1 Studied Design Aspects                            | 91<br>01        |

|   | 59                 |                                                         | 91<br>02        |

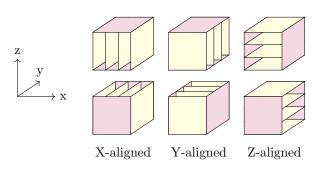

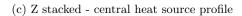

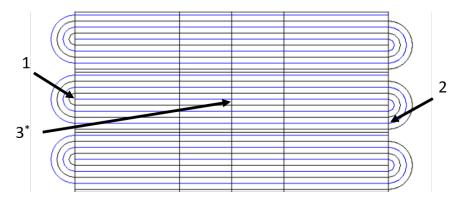

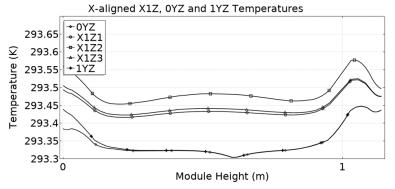

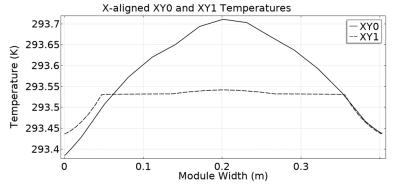

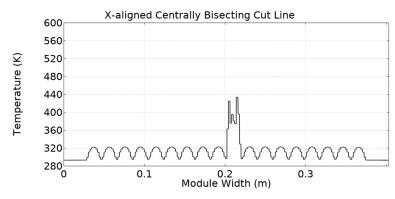

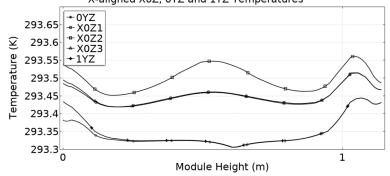

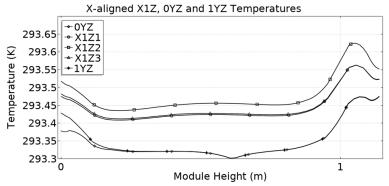

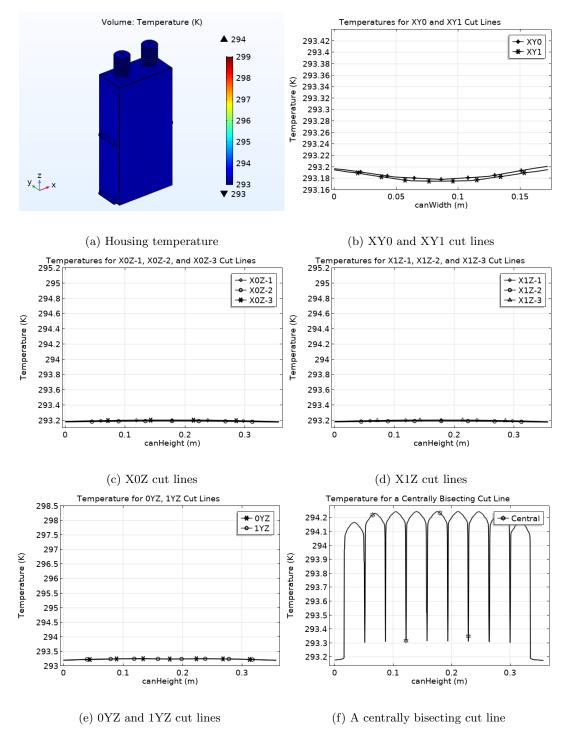

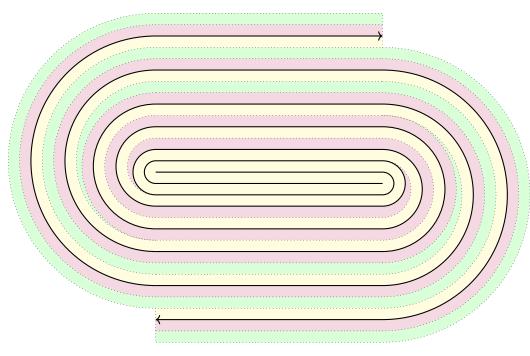

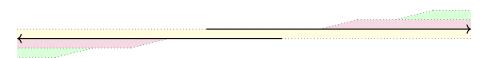

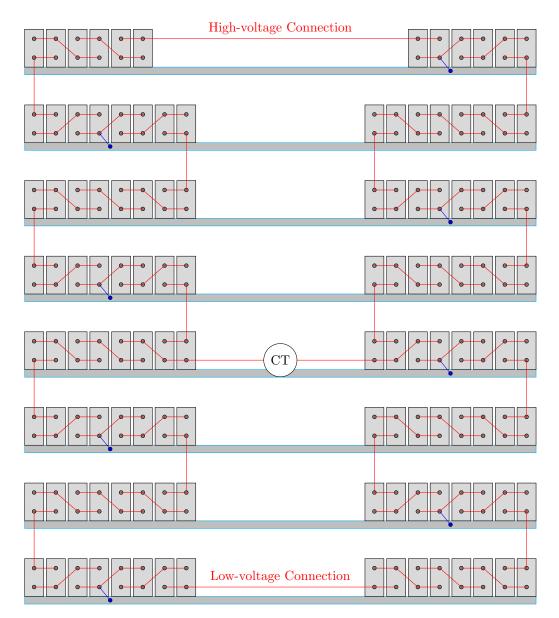

|   | 5.3                | The Influence of Winding Alignment                      | 92<br>02        |

|   |                    | 5.3.1 Diagrams                                          |                 |

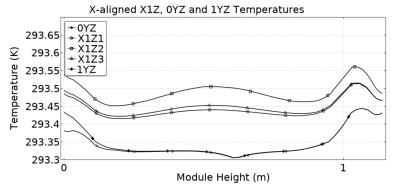

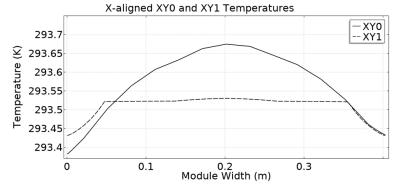

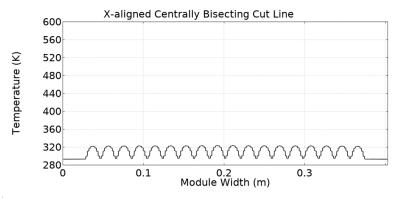

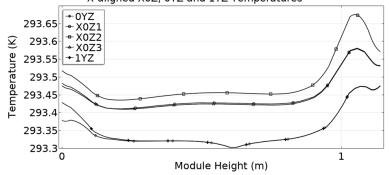

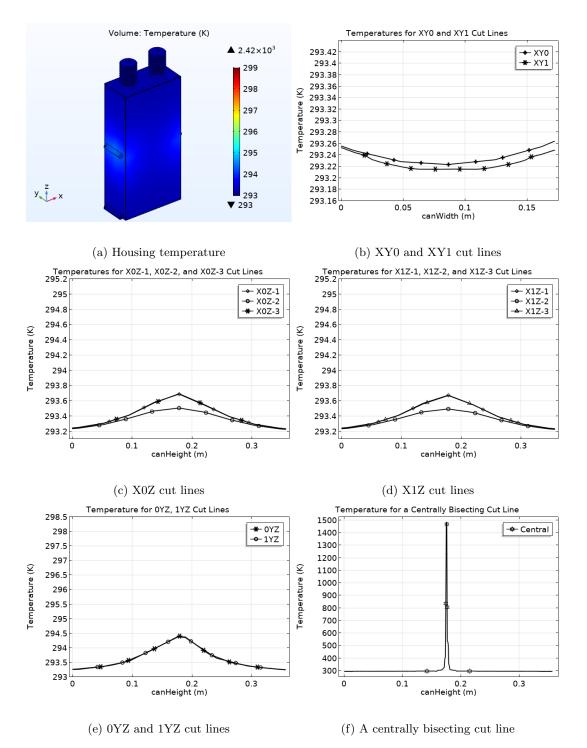

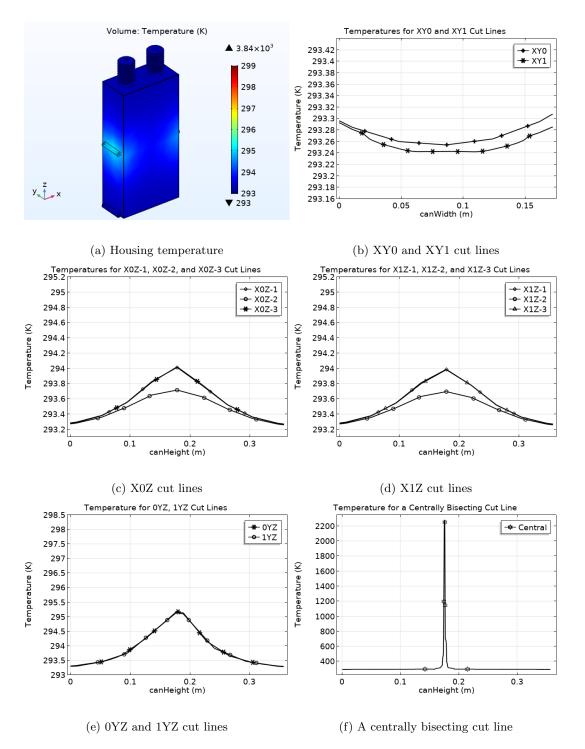

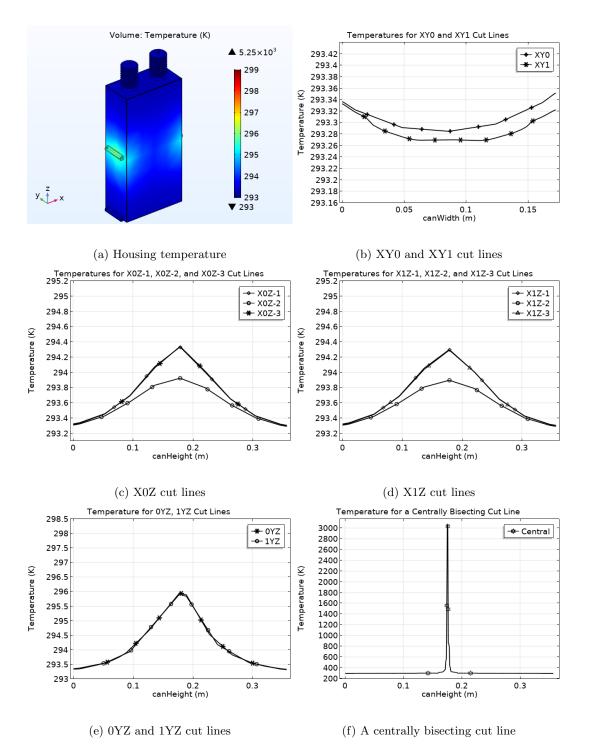

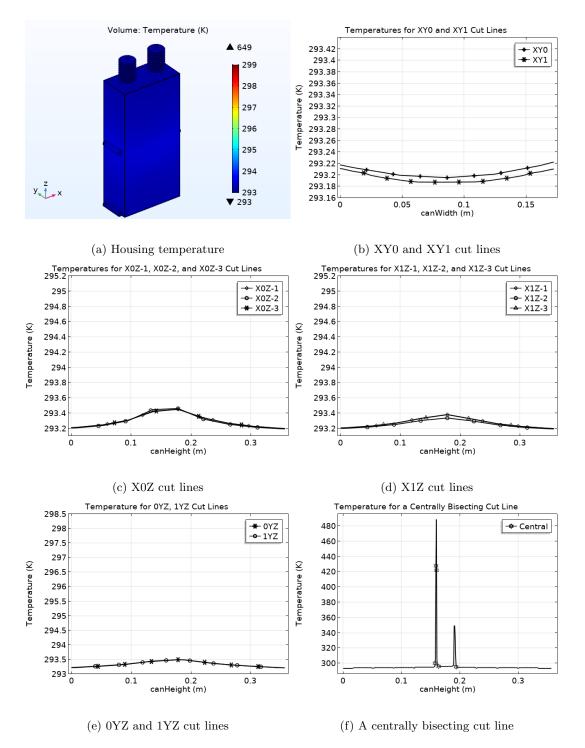

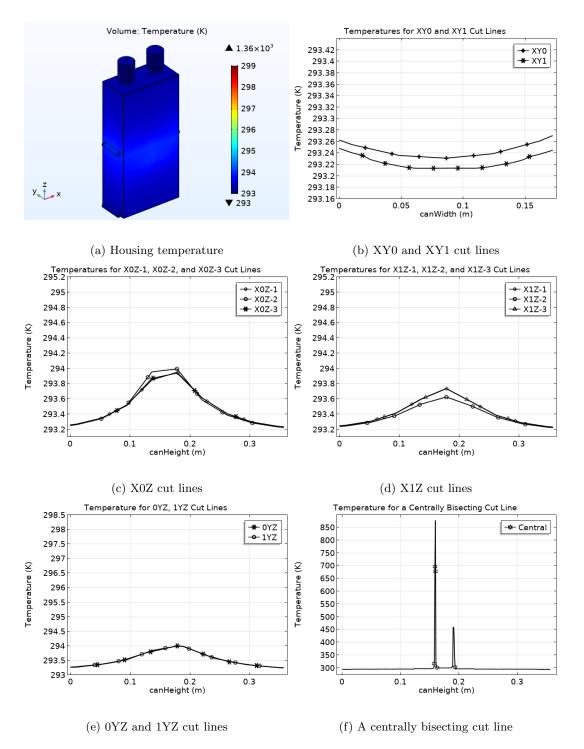

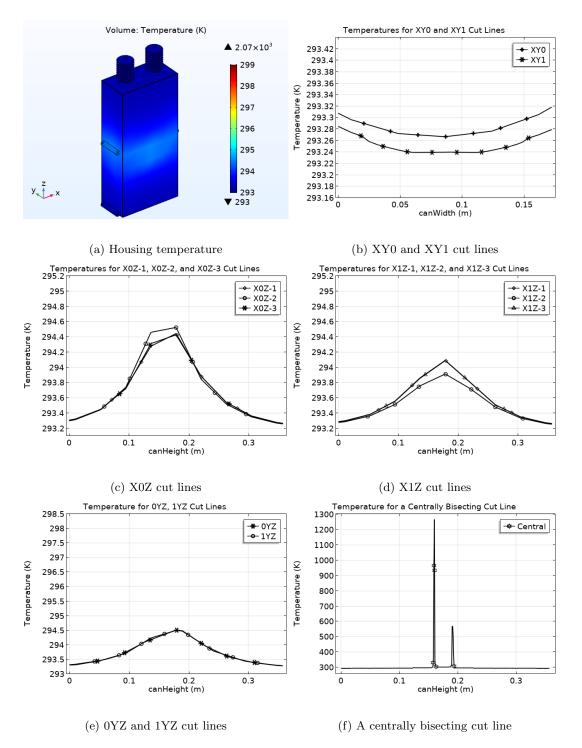

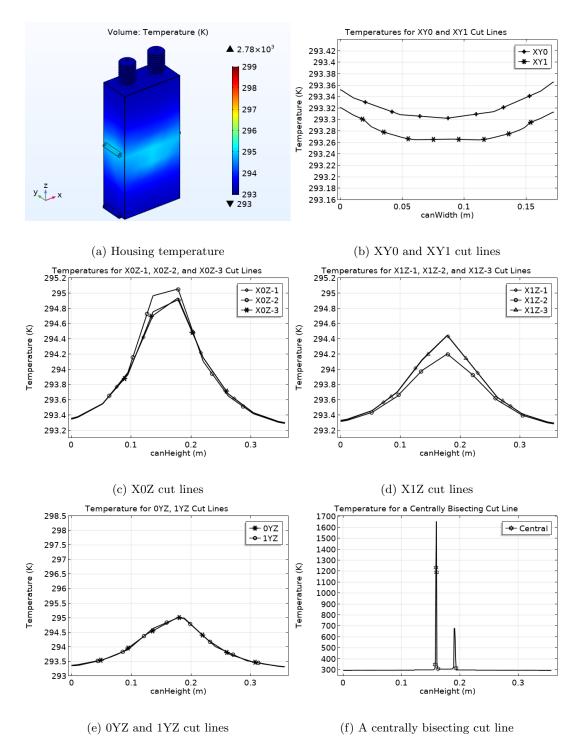

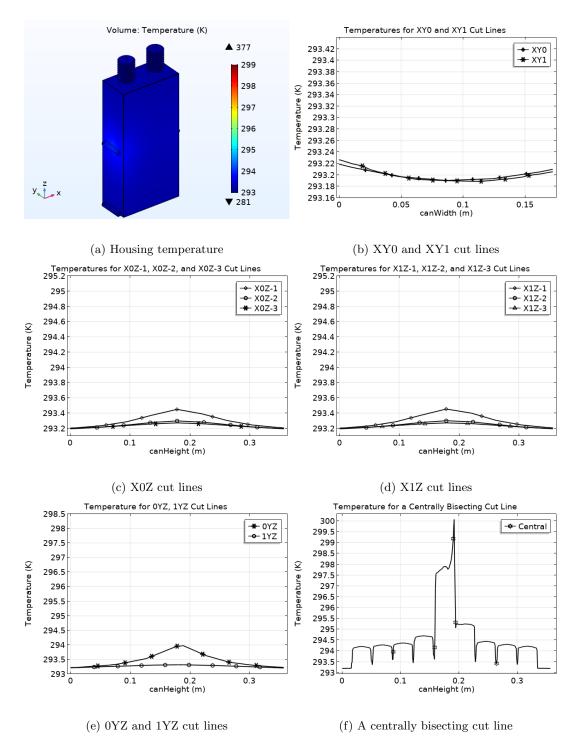

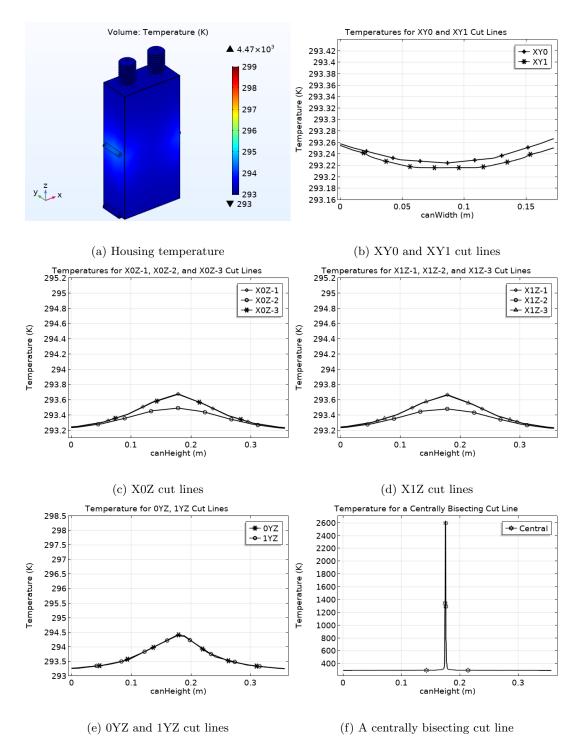

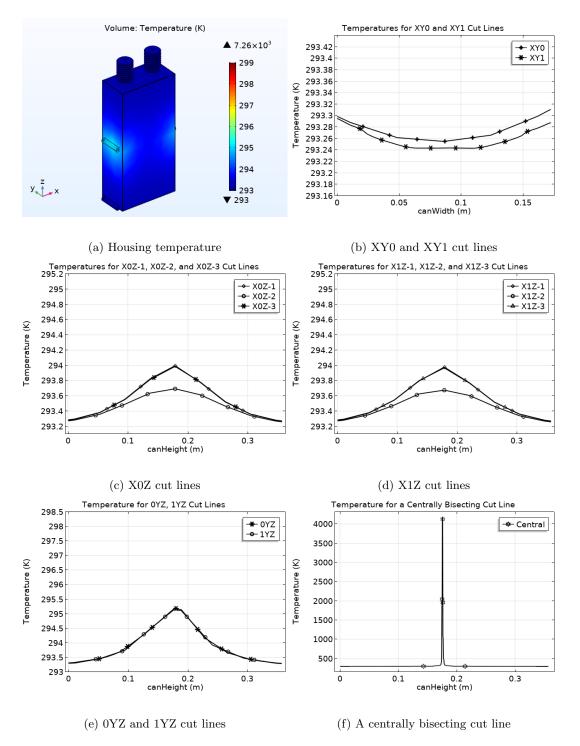

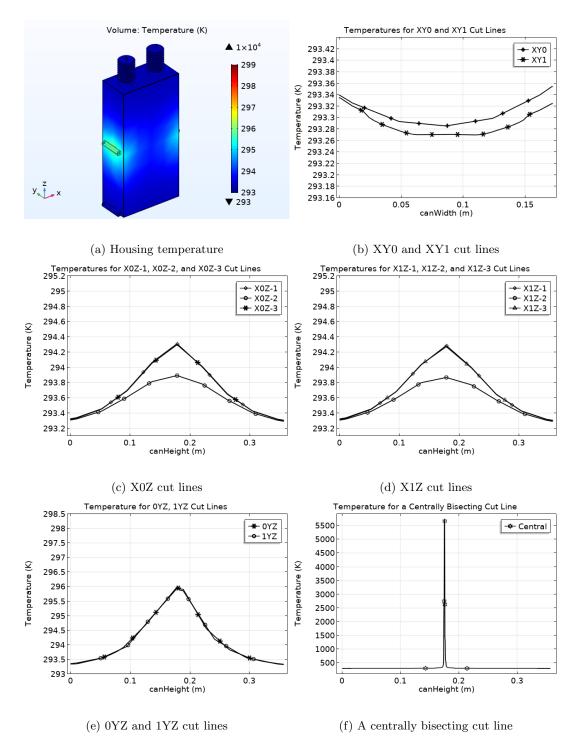

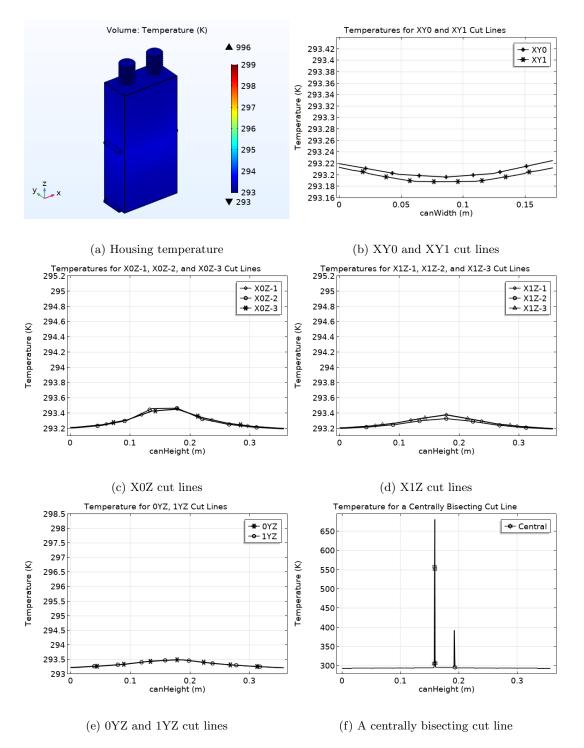

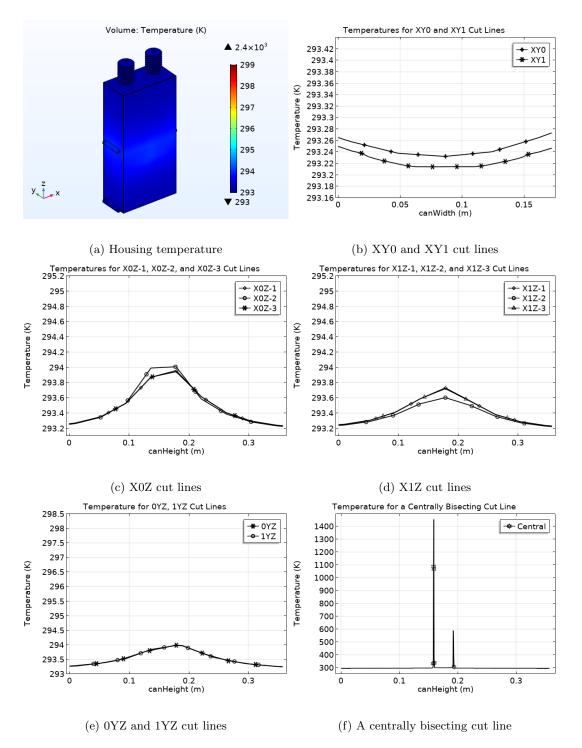

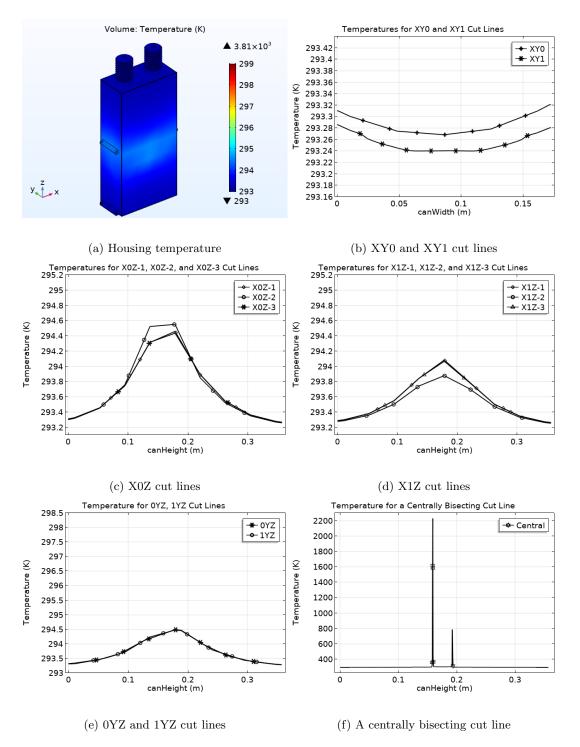

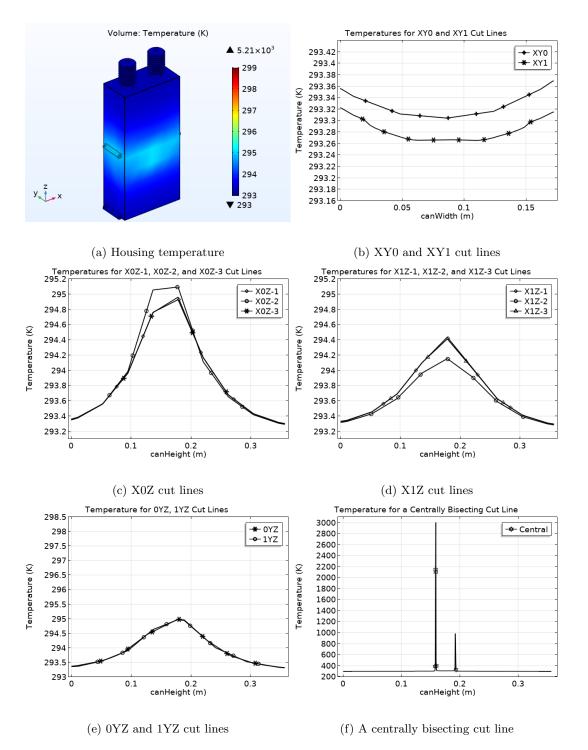

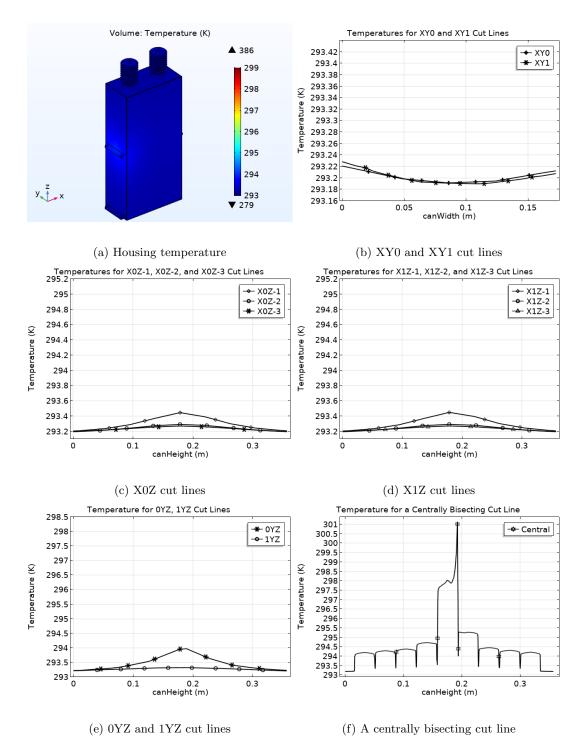

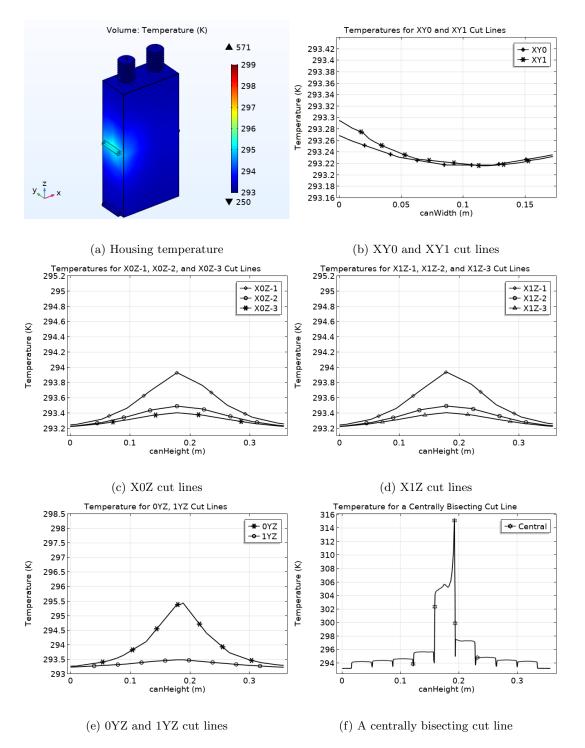

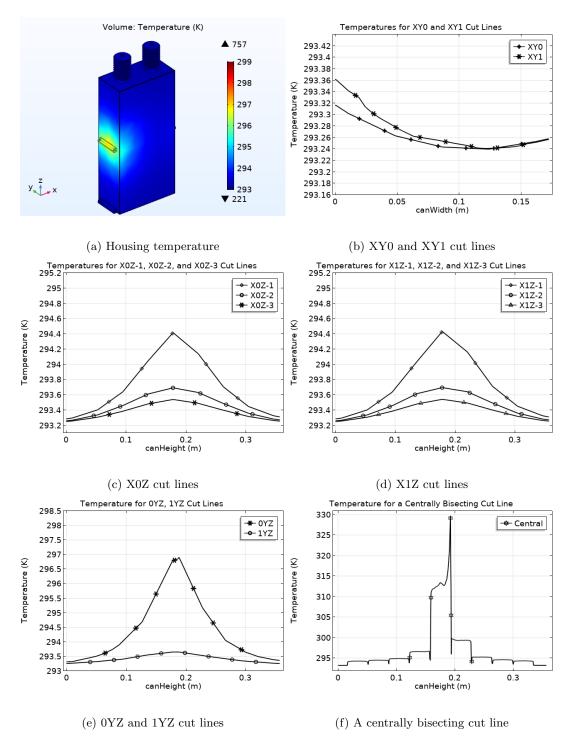

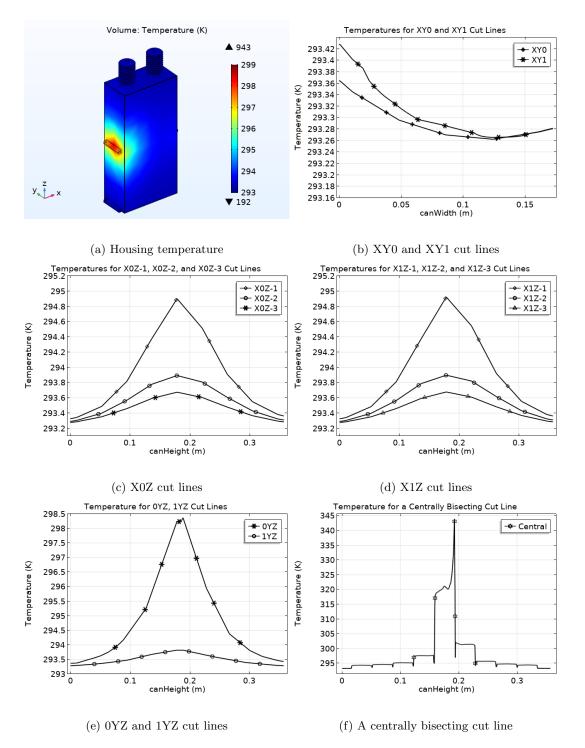

|   |                    | 5.3.2 Results                                           | 92              |

|   | 5.4 | The Int  | fluence of Fault Location                                                           | <br> | <br> | <br> | . 95  |

|---|-----|----------|-------------------------------------------------------------------------------------|------|------|------|-------|

|   |     | 5.4.1    | Heat Source Positions                                                               | <br> | <br> | <br> | . 95  |

|   |     | 5.4.2    | Discussion                                                                          | <br> | <br> | <br> | . 95  |

|   | 5.5 | Identify | ying Limits                                                                         | <br> | <br> | <br> | . 100 |

|   |     | 5.5.1    | Results                                                                             | <br> | <br> | <br> | . 100 |

|   |     | 5.5.2    | Discussion                                                                          | <br> | <br> | <br> | . 101 |

|   | 5.6 | Further  | Work                                                                                | <br> | <br> | <br> | . 102 |

|   |     | 5.6.1    | Simulation                                                                          | <br> | <br> | <br> | . 104 |

|   | 5.7 | Discuss  | $sion \ldots \ldots$ | <br> | <br> | <br> | . 105 |

|   | 5.8 | Conclu   | sions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                         | <br> | <br> | <br> | . 106 |

| 6 | Pro | totype   |                                                                                     |      |      |      | 108   |

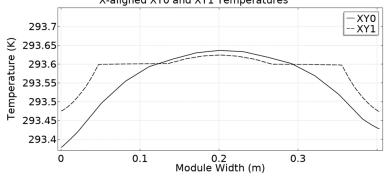

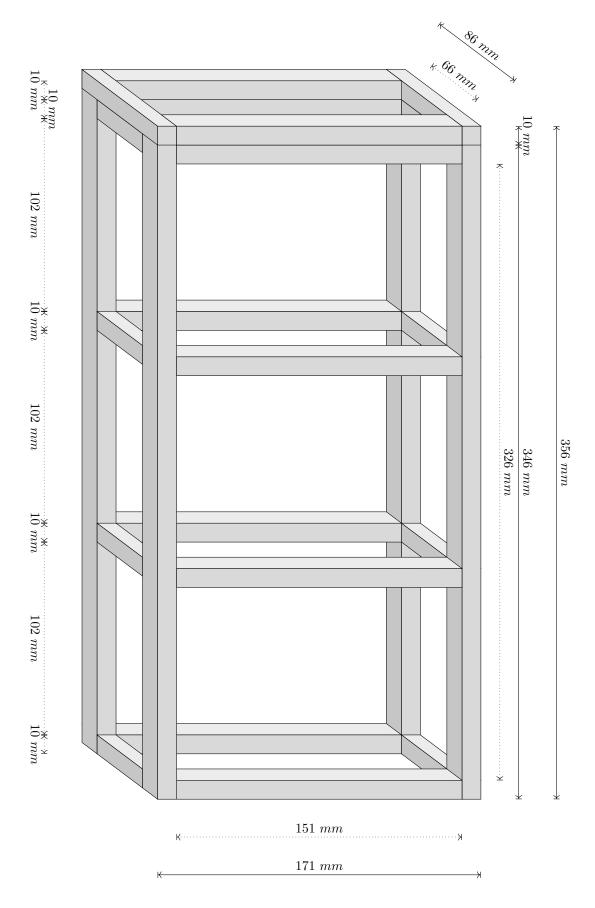

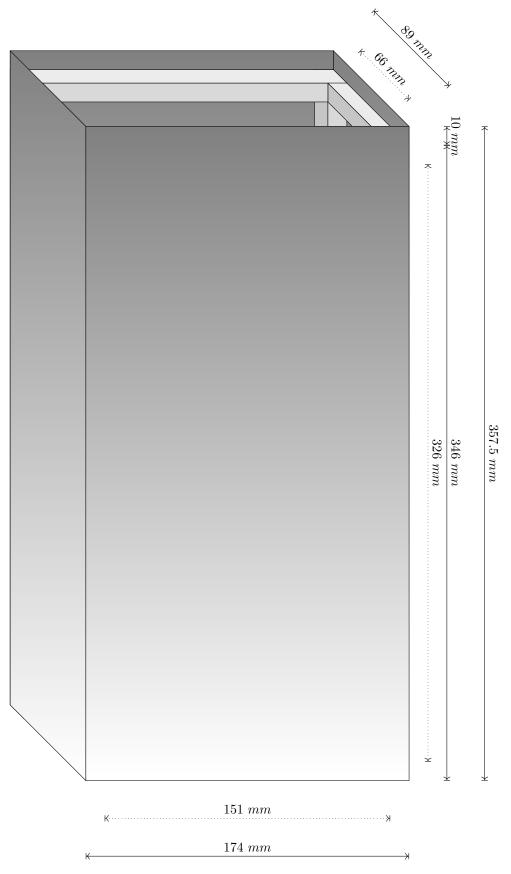

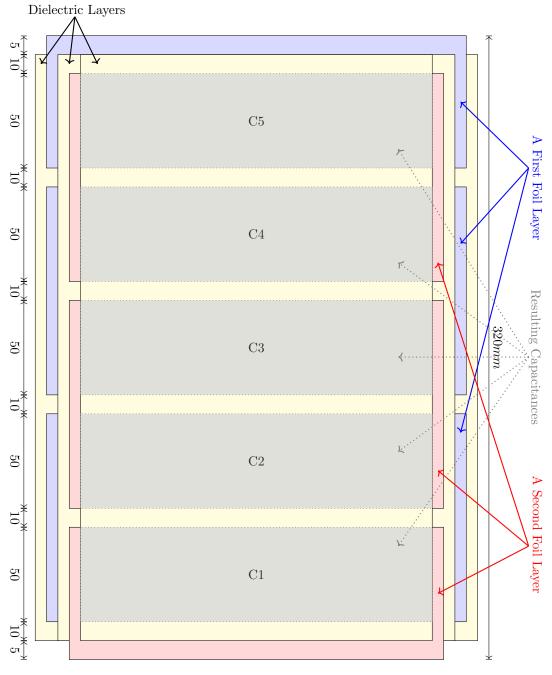

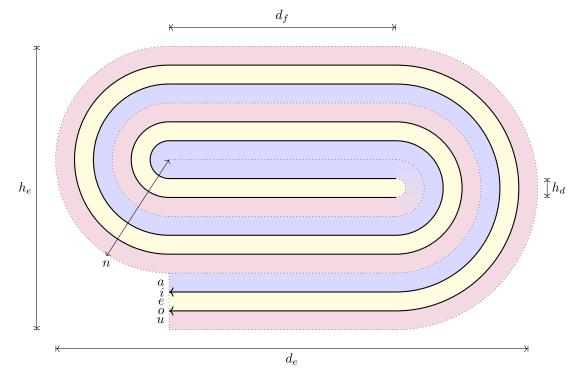

| 0 | 6.1 | • -      | Iodel Design                                                                        |      |      |      |       |

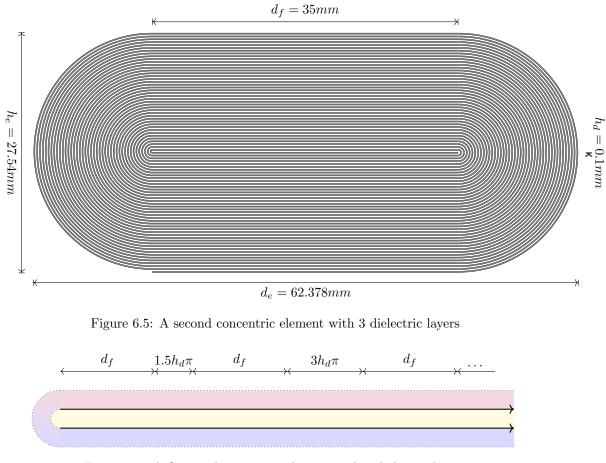

|   | 0.1 |          | Dimensions                                                                          |      |      |      |       |

|   |     |          | Housing Design                                                                      |      |      |      |       |

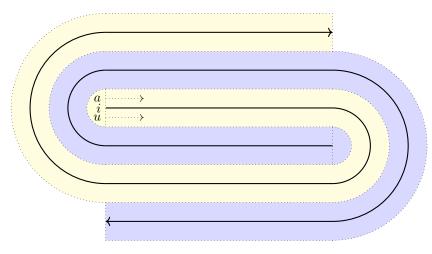

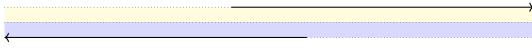

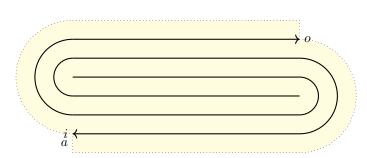

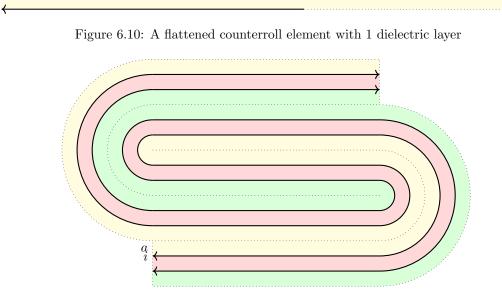

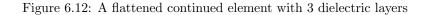

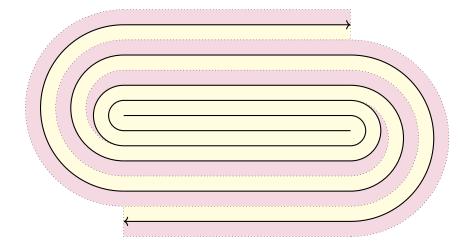

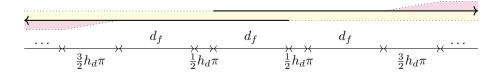

|   |     |          | Winding Design Options                                                              |      |      |      |       |

|   |     |          | Winding Specification                                                               |      |      |      |       |

|   | 6.2 |          | vpe Construction                                                                    |      |      |      |       |

|   | 0.2 |          | Paper Roll Cutting                                                                  |      |      |      |       |

|   |     |          | Foil Cutting                                                                        |      |      |      |       |

|   |     |          | Winding Rolling                                                                     |      |      |      |       |

|   |     | 6.2.4    | Corrective Measures                                                                 |      |      |      |       |

|   |     |          | Practical Correction                                                                |      |      |      |       |

|   |     |          | Final Windings                                                                      |      |      |      |       |

|   |     |          | Internal Connections                                                                |      |      |      |       |

|   | 6.3 |          | rement                                                                              |      |      |      |       |

|   |     |          | Corresponding Simulation                                                            |      |      |      |       |

|   |     |          | Discussion                                                                          |      |      |      |       |

|   | 6.4 |          | uation                                                                              |      |      |      |       |

|   | 6.5 |          | sions                                                                               |      |      |      |       |

|   |     |          |                                                                                     | <br> | <br> | <br> |       |

| 7 |     | clusion  |                                                                                     |      |      |      | 135   |

|   | 7.1 |          | sion                                                                                |      |      |      |       |

|   | 7.2 |          | d Conclusions                                                                       |      |      |      |       |

|   | 7.3 |          | Modelling Options                                                                   |      |      |      |       |

|   |     |          | Modelling Practise                                                                  |      |      |      |       |

|   |     |          | COMSOL Support Feedback                                                             |      |      |      |       |

|   |     |          | Options for Further Model Develop                                                   |      |      |      |       |

|   |     |          | Improvements Requested from COM                                                     |      |      |      |       |

|   | 7.4 |          | Research Options                                                                    |      |      |      |       |

|   |     |          | Further Exploration of Dielectrics                                                  |      |      |      |       |

|   |     |          | Nonlinear Voltage Distribution                                                      |      |      |      |       |

|   |     |          | Unit Allocation                                                                     |      |      |      |       |

|   | _   |          | Capacitor Asset Salutogenesis                                                       |      |      |      |       |

|   | 7.5 | Contrib  | outions                                                                             | <br> | <br> | <br> | . 148 |

| 7.5.1                            | Novelty               | . 149 |  |  |  |  |

|----------------------------------|-----------------------|-------|--|--|--|--|

| 7.5.2                            | Industrial Engagement | . 150 |  |  |  |  |

| 7.5.3                            | Summary               | . 150 |  |  |  |  |

| A Detectable Thermal Behaviour 1 |                       |       |  |  |  |  |

| Index                            |                       | 182   |  |  |  |  |

## Abstract

As electrical power networks adapt to new challenges, advances in high voltage direct current interconnection offer one means to reinforce alternating current networks with flexibility and control, accordingly improving diversity to become a present-day, viable alternative to network flexibility and energy storage measures. High voltage capacitors support these links and offer simple means of voltage support, harmonic filtering, and are inherent to established and emerging converter designs. Where research literature predominantly explores use of modern dielectrics in efforts toward improved capacitor technologies, but reveals little about: existing capacitor designs; associated failure modes or statistics; or avenues in monitoring or maintenance, simulation modelling equips engineers with an approach to pre-emptively anticipate probable incipient fault locations toward improving designs for systems yet to be commissioned. This Dissertation presents a high-voltage capacitor simulation model, before exploring two questions about these hermetically sealed, highly modular assets: where are incipient faults most likely to arise; and how can internal faults be externally located? Nonlinear voltage distributions are found within each and among connected units, induced through parasitic effects with housings supported at rack potential. Consequent implications are considered on: stresses within unit dielectrics, susceptibility to cascading failure, and an ability to locate internal faults. Corroboration of fault detection and location is additionally found possible using unit housing temperatures. A model is presented, developed to be scalable, configurable, and extensible, and made available for posterity. Opportunities in asset design, modelling, manufacture, and monitoring are proffered toward improvements not only in operational longevity, but in understanding and early awareness of incipient faults as they develop.

## List of Publications

- C. J. Mackinnon, B. G. Stewart, "Simulation of High Voltage Direct Current Filters", 53<sup>rd</sup> International Universities' Power Engineering Conference, September 2018.

- C. J. Mackinnon, B. G. Stewart, "A High Voltage Capacitor Element Model", 37<sup>th</sup> IEEE Electrical Insulation Conference, June 2019.

- C. J. Mackinnon, B. G. Stewart, "Thermal Profiles of High-voltage Capacitor Units", Annual Conference on Electrical Insulation and Dielectric Phenomena, October 2019.

- C. J. Mackinnon, B. G. Stewart, "Regions of Electrical Stress in High Voltage Capacitor Units", COMSOL Conference Europe, September 2019.

- C. J. Mackinnon, B. G. Stewart, "A Capacitor Bank Simulation Model", 38<sup>th</sup> IEEE Electrical Insulation Conference, June 2020.

# List of Conferences

The conferences attended during the course of this research programme are listed in Table 1, which uses the symbol \* to denote those at which presentations and publications were given.

| Conference                | Year | Month                    | Dates   | Location        |

|---------------------------|------|--------------------------|---------|-----------------|

| LCNI                      | 2016 | October                  | 11 - 13 | Manchester, UK  |

| UHVNet                    | 2017 | January                  | 18 - 19 | Glasgow, UK     |

| AllEnergy                 | 2017 | May                      | 10 - 11 | Glasgow, UK     |

| CIRED                     | 2017 | June                     | 12 - 15 | Glasgow, UK     |

| $\mathrm{UHVNet}^*$       | 2018 | January                  | 15 - 16 | Winchester, UK  |

| Futurewind                | 2018 | March                    | 22      | Glasgow, UK     |

| AllEnergy                 | 2018 | May                      | 2 - 3   | Glasgow, UK     |

| UPEC*                     | 2018 | September                | 4 - 7   | Glasgow, UK     |

| $SmartFuturES^*$          | 2018 | September                | 19      | Glasgow, UK     |

| $\mathrm{UHVNet}^*$       | 2019 | January                  | 15 - 16 | Manchester, UK  |

| $\mathrm{EIC}^*$          | 2019 | June                     | 16 - 20 | Calgary, Canada |

| $\operatorname{COMSOL}^*$ | 2019 | ) September 24 - 26 Camb |         | Cambridge, UK   |

| CEIDP*                    | 2019 | October                  | 20 - 23 | Washington, USA |

| $\mathrm{UHVNet}^*$       | 2020 | January                  | 15 - 16 | Glasgow, UK     |

| $\mathrm{EIC}^*$          | 2020 | June                     | 7 - 11  | Online          |

Table 1: Conferences

## Chapter 1

## Introduction

This Chapter introduces the premise, aims, approaches<sup>1</sup>, and structure of this work in Section 1.1, before in more detail introducing its wider subject domain in Section 1.2 for context.

## 1.1 Premise

In accordance with one of Shigeo Shingo's principles (for value to be drawn according to a basis of need), an open-minded approach to identifying a domain and direction for this research project has been adopted. High voltage direct current (HVDC) is an area of interest articulated by industrial partners of the centre for doctoral training by which this project has been funded.

While some electrical transmission assets (such as transformers) are sufficiently well established and numerous as to have monitoring techniques and statistics collated on reliability, HVDC remains a relatively recent set of technologies in terms of diagnostics and prognostics. Thus, while a prospective contributor might begin a research project by exploring literature to identify a research niche, it can be daunting to instead stumble upon a metaphorical crevasse.

Principles of reliability centred maintenance invite manufacturers to include measurement points and design countermeasures in anticipation of eventual faults within each assets' design. Where vulnerabilities are understood, this knowledge informs iterative design refinements to aid detectability, mitigate consequences, and reduce the likelihood of failure modes toward improved reliability and longevity from a 'whole lifecycle' perspective. As increasing numbers of HVDC systems are set to be planned and deployed to help decarbonise the global economy, information on failure modes of assets critical to these links could prove timely. Rather than await failure or reliability data, this research adopts existing design information as a basis to anticipate failure modes by returning to the fundamentals of component physics and operation.

### 1.1.1 Hypothesis and Aim

This project hypothesises that:

as yet unidentified signals betray failure modes in HVDC converter stations.

This project consequently aims to identify those *signals which arise due to faults* in HVDC converter stations, and appropriate associated measurands. It therefore explores both electrical and thermal effects associated with one particular asset critical to HVDC function: capacitors.

<sup>&</sup>lt;sup>1</sup>Material given in this introduction will, naturally, be treated more comprehensively in subsequent Chapters.

#### 1.1.2 Approaches

#### Motivation

An increasing use of power electronics means capacitors are becoming more common as power systems evolve to meet modern challenges; unit designs also vary as new topologies – such as modular multilevel converter (MMC) – and (composite and dry dielectric) materials emerge.

High-voltage capacitors are a suitable subject of study given the large numbers deployed at converter stations for conventional HVDC. Although some online monitoring solutions exist, capacitor banks' structure makes them opportune assets for unit-specific condition monitoring, facilitated by ubiquitous information technology, in addition to the benefits of informed design. This is particularly given units' vulnerability to signal artefacts when connected at high-voltage in converter stations and their increasing criticality in alternating current (AC) power systems.

#### **Research Landscape**

Internally fused and fuseless unit designs offer no visual indication of internal dielectric breakdown, and any existing element failures can lead to further susceptibility (faults 'cascade'). It is accordingly imperative to detect and protect against capacitor unit faults, which is typically achieved using counters and imbalance protection; recent advances can identify the string of units on which each fault occurs for efficient maintenance by narrowing the search space for faulted units. Such techniques use existing sensors, but remain limited by them. In future, distributable measurements could: 1. detect *incipient* faults; 2. significantly reduce the search for detected faults; and 3. take account of operational temperatures which are critical to capacitor longevity (every 8 to 10 °C increase in core temperature approximately halves expected life [1]). Improved understanding alone can identify vulnerabilities to inform maintenance and design.

#### A Model-based Approach

Modelling discussed in this Dissertation focusses on electrical and thermal effects, as capacitors are electrical assets with dielectrics primary to their function, and where operating temperatures are known to significantly influence unit health and longevity. Simulation modelling allows:

- 1. estimations to be made on (a) *dynamic* behaviour of assets which can only be safely measured offline, and (b) the *internal* physics of hermetically sealed units;

- 2. models to be (a) adapted and developed in tandem with understanding of internal designs, or conversely to be (b) configurable so as to accommodate design uncertainty and emulate a variety of unit types, and to be (c) agnostic of any one supplier;

- 3. data to be generated with (a) a minimum of physical waste, (b) fewer safety concerns relative to lab experiments (with (c) resilience to limits on practical work); and allows

- 4. support for repeatability and further work through reference to a digital model file.

Disadvantages of modelling include: 1. the time taken to build (familiarity with an environment and) a model of sufficient detail; and 2. an inevitable simplicity inherent to any model, which typically omits noise, manufacturing defects, and ambient conditions (physical assets will always be more nuanced in reality). Nonetheless, by emulating the effects of an applied electrical signal, associated electric field stresses, dielectric heating, and heat from incipient faults, modelling allows insights into asset behaviour, vulnerabilities, and failure modes to be obtained.

#### **Dissertation Structure**

This Dissertation is structured with seven Chapters, each contributing as follows.

- 1. The remainder of this **Chapter 1 introduces the subject area**, including drivers for change in electrical power systems, to identify technologies for which monitoring could be opportune. HVDC is a large subject, but as these systems advance so too does a gulf between expectations for reliable operation and means of assessing the failure modes which will inevitably, eventually arise in forms potentially unique to emerging technologies.

- 2. Chapter 2 explores suitable research directions and returns to the fundamentals of capacitor unit design before offering an insight into approaches used for fault detection and location in high-voltage power system capacitors, as discussed in current literature.

Figure 1.1: Chapter dependencies

- 3. Chapter 3 presents a configurable high voltage capacitor unit model to aid further study in this area. This is made available online for the study of different capacitor designs, and has been designed to be configurable to that end. Good practise techniques are discussed and improvements which could be made to the simulation environment to support these techniques have been highlighted to COMSOL<sup>®</sup> directly.

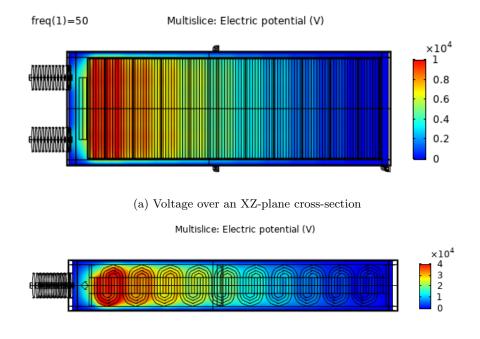

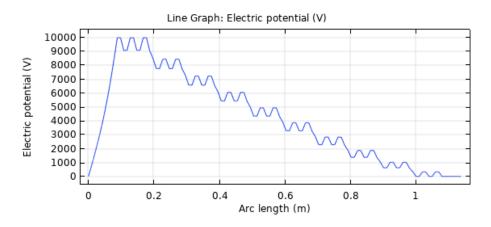

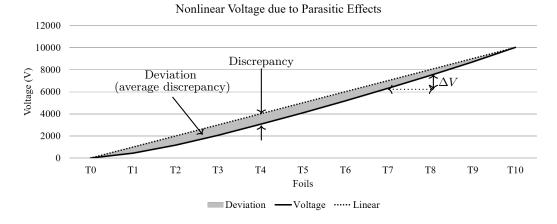

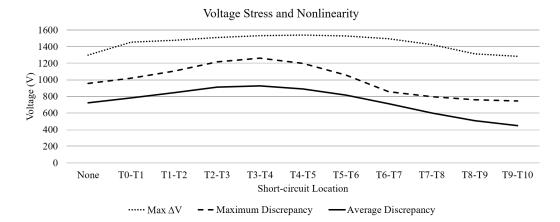

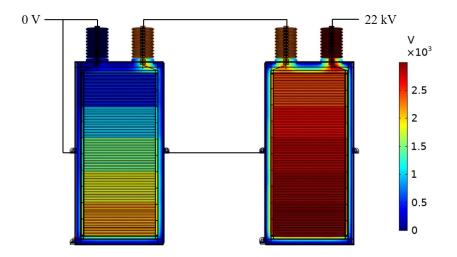

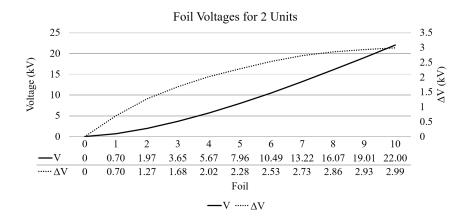

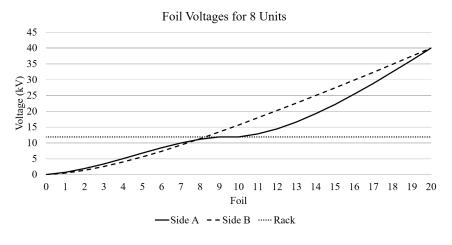

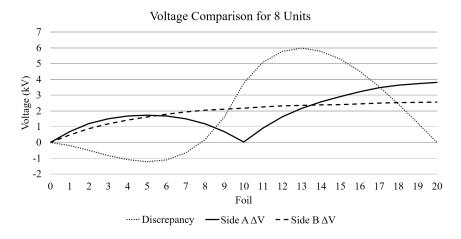

- 4. Chapter 4 explores electrical effects in pursuit of probable fault locations and possible diagnostics. Unit housing is shown to provoke parasitic electric field effects, which invoke a nonlinear electrical distribution within each unit. Solvability of a corresponding electrical circuit and the influence of internal faults on terminal characteristics are discussed, and regions of high electrical field stress associated with aspects of a capacitor unit design are considered. This is found to extend throughout multiple units on a rack.

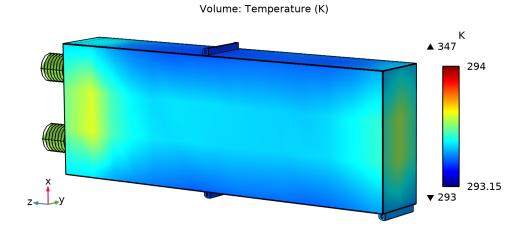

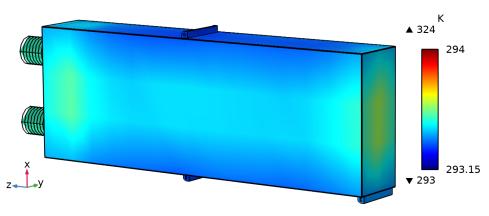

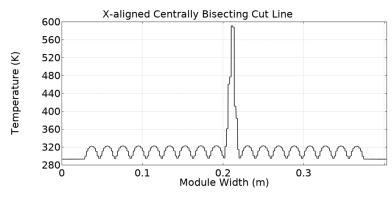

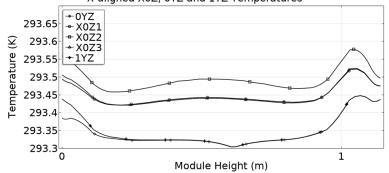

- 5. Chapter 5 considers thermal behaviour and how this is heavily influenced by element winding alignment within each unit, since foils both contain and direct thermal energy. This can be used to corroborate electrical diagnostics, which is an area of significant importance to capacitor asset longevity but with limited consideration thus far.

- 6. Chapter 6 covers preparation of a physical prototype capacitor. It outlines the design, build, and measurement of this scale replica unit in a laboratory setting, and finds practical measurements to accord with the principles of operation found by simulation.

- 7. Chapter 7 collates conclusions of the dissertation from discussion within prior Chapters. It considers learning outcomes, and possible avenues and opportunities for further research to support future work.

The author hopes that by offering background understanding, suggestions for further investigation, and a baseline for modelling, future exploration can be encouraged in this area at an intersection of energy systems, asset management, information technology, and sustainability. Chapter dependencies are represented graphically in Figure 1.1 to support selective reading.

#### Conventions

References to this Dissertation, the Chapters, Sections, Figures, and Tables it contains are capitalised. COMSOL requests the <sup>®</sup> symbol accompanies references to the software environment. References to components of the modelling environment use verbatim typesetting (and in the index are capitalised) to delineate their use as a reference to terminology specific to COMSOL<sup>®</sup> rather than more general use of the term: all capacitors have geometry, but a computer model has a **Geometry** (as a node within the model tree). An algebraic convention to encapsulate newly substituted terms in brackets is followed to reduce ambiguity in algebraic working.

## 1.2 Context

Electrical networks underpin modern lifestyles and serve a critical (if often unnoticed) role in advanced economies; they are a cornerstone of advances in sustainable development goal 7 [2], and the nature of these networks is changing in three notable ways.

- 1. Power systems are becoming increasingly sustainable. Traditionally, power systems have operated by conveying power from synchronous generators, which are controllable, few in number, and centrally located on a network, but which tend to be carbon-intensive, presently nearing the end of their useful life, or are simply challenged by economic competition with modern alternatives. In efforts to reduce greenhouse gas emissions, such forms of centrally-owned historical generation are increasingly becoming superfluous to geographically disparate, more numerous, and less controllable *renewable sources*, which are necessarily far from centres of demand, connected at all voltage levels, and connected by converter interfaces which do not offer equivalent inertia to support network stability.

- 2. Networks should be cost-effective. These systems are expected to (a) operate at *minimal* cost to consumers [3], (b) ensure a competitive market for trading energy and its associated services, in part to (c) offer competition to other available forms of domestic energy, and to (d) further a form of social justice to permit everyone access to the energy we need.

- 3. Energy must be dependable. High availability ('uptime') is desired for electrical supplies to be relied upon as a technology. Not only are renewable sources less reliable, but the manner in which a network must operate to connect large proportions of converter-based renewable generation can leave it vulnerable to frequency and voltage deviations in response to sudden changes, whether faults or unanticipated variation in intermittent generation output. Thus, transitioning to a modern generation portfolio poses a risk to *security* (the expectation for energy to be *available* when needed).

## 1.2.1 Energy Trilemma

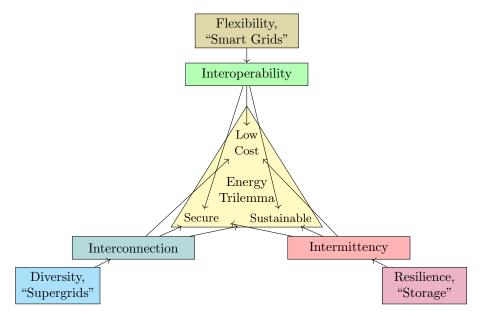

These three aspects of a changing energy landscape are captured by the 'energy trilemma' index [4], which attempts to outline the scale of desired change. As illustrated in Figure 1.2, research endeavour in this field revolves around these aims, and broadly conforms to three approaches to their resolution: intermittency (using bulk or distributed storage mechanisms, or shifting intermittent loads, to better match instantaneous supply and demand), interoperability (pursuit of the 'smart grid' paradigm and network flexibility), and interconnection (increasing natural supply and demand diversity through physical integration of established systems).

'Smart grid' paradigms and similar solutions designed to achieve flexibility (such as active network management and dynamic thermal ratings) unlock these capabilities with information and communication technology (ICT) stacks. Alongside ICT, power electronics offers a means of introducing controllability by decomposing and reconstituting alternating current (AC) waveforms, to thus be used together with ICT to provide the interoperability, intermittency, and interconnection needed to address the changing nature of modern networks.

Another aspect of this transition is ownership: large, established market participants which own and control conventional generation are giving way to a broader array of owners concordant with the distributable nature of renewables, with both economic and operational implications.

Figure 1.2: A representation of the power systems research landscape

#### **Consumer Engagement**

Over recent years, consumer engagement has been suggested as a fourth aim for electrical networks [5]. While proponents of this argument suggest the use of smart metering, awareness of carbon footprint, and the importance of cultivating responsible energy use such as through home insulation, choice of tariff, and even choice of car, these arguments are often made by those with an established interest in electrical technology or in the industry. These efforts are well intentioned, but overlook a principle of ubiquitous technology first outlined in 1991 [6]:

"the most profound technologies are those that dissappear. They weave themselves into the fabric of everyday life until they are indistinguishable from it."

When viewed as a ubiquitous technology, the electrical power system *should* be sufficiently pervasive, dependable, cheap, and conscionable as to be ignorable. Thus, while energy trilemma aims accord with one another, they better lend themselves toward the aims of a *ubiquitous* technology rather than toward consumer engagement per se. However, the array of advances the energy trilemma index demands for power systems globally might nevertheless draw technical interest and could increase engagement of consumers as a by-product of these core ambitions.

## **1.3** Interconnection

While any one of these three approaches (storage, 'supergrids', or 'smart grids') taken in extreme could suffice to address the challenges posed by the energy trilemma, in practise a combination is necessary. Energy storage is viewed as a hallmark need for electrical energy systems given its ability to offset (and hence match) instantaneous demand and supply. However, reinforcing and connecting existing networks can create the diversity between generation and load necessary to improve the scale at which any balancing must occur. Similarly, while 'smart grids' can make use of distributable ICT to co-ordinate supply and demand around constraints, interconnection offers a comparatively mature way of alleviating constraints to begin with, through diversity.

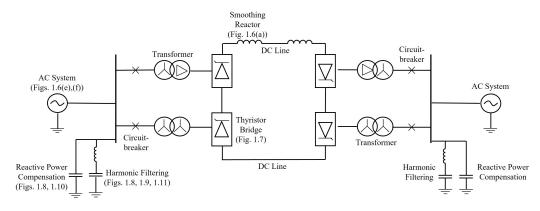

Figure 1.3: Line diagram of an LCC HVDC link [8]

In short, interconnection and preparations toward a 'pan-European' network [7] is a modern approach to conventional reinforcement: a natural next step to the historic development of network infrastructure through increasing voltage levels. It solves key aims of the energy trilemma predominantly by improving the diversity of supply and demand on a network it strengthens:

- 1. costs are shared (and therefore reduced) over a wider area between newly connected networks to unlock economics of scale;

- 2. network security is improved as a result of controllability, and since a better connected network can be made more resilient to faults; and interconnection

- 3. permits higher proportions of renewables by connecting different geographies, allowing each area to make the most of its natural resources.

Accordingly, the European network of transmission system operators for electricity (ENTSO-E) calls for 50 GW of European cross-border capacity by 2030, beyond projects already planned [7].

### 1.3.1 High-Voltage Direct Current

As an abstract concept, interconnection can be realised in practise through established AC technology, but to achieve greater capacities (where networks are already mature as is broadly true in developed economies) it is becoming increasingly appropriate to use high voltage direct current (HVDC) systems. HVDC links use power electronic converters, which although prone to losses allow efficiency gains to be made overall. As such, power electronic conversion provides a modern means of conventional power system reinforcement. A line diagram of an line commutated converter (LCC) HVDC system is shown in Figure 1.3.

### 1.3.2 Converter Topologies

Developments in semiconductor technology have enabled new forms of power electronics, which in turn have allowed high-voltage applications. In the 1980s mercury arc valves were used for the first HVDC link to Gotland, Sweden. Since then the underlying semiconductor technology has advanced further to respectively use thyristors and insulated gate bipolar transistors (IG-BTs) for conventional line commutated converter (LCC) and voltage source converter (VSC) topologies. The main constraint with advances in these core semiconductors is heat extraction,

#### CHAPTER 1. INTRODUCTION

where modern switching elements are typically cooled using deionised water [9]. An ability to control the firing angle of switching elements (e.g. thyristors) offers converters a significant advantage over conventional AC networks, as these links are *controllable*.

#### Advantages of LCC HVDC

Specific advantages of LCC HVDC over conventional AC connections are listed here (numbers 1 to 6), before VSC technology is discussed as a way to expand these advantages with (7 to 8).

- 1. Primarily, advantages are in the *capacity* and *distance* that HVDC solutions cost-effectively offer. Although conversions between AC and direct current (DC) power are lossy, DC electrical transmission sees savings in the need for fewer conductors with more efficient use of each cross-sectional area, and by operating at higher voltages, is liberated from some losses for the length of the line (associated with capacitive components of its transfer function). Thus, for a given cost, DC links are capable of greater distances and capacities.

- 2. In connecting renewables, the principle for using converter-based power electronic interfaces is that generation (turbine) speeds are decoupled from that of the grid. This same principle of *decoupling frequency* in connections allows integration of systems which might otherwise remain independent: asynchronous networks can be connected via an intermediate DC stage to form 'supergrids' on continental scales.

- 3. The *compact footprint* of converter stations relative to the electrical power capacities they convey is another strong advantage, in that it allows reduced converter station footprints which is an important factor in connecting: offshore installations; where land is expensive; and to form high-capacity connections to urban areas [8].

- 4. Reduced asset footprints are also true of the associated transmission assets, due to HVDC links' need for *fewer conductors*, leading to further cost savings over long distance connections. Additionally, this capability allows existing AC circuits to be converted to higher-capacity DC connections, should converter stations be positioned at either end of existing conductors.

- 5. HVDC allows connections to be made *subsea* which would otherwise be limited by the capacitive nature of a saltwater environment. This is important for the viability of offshore wind at distances far from the coast, and is crucial to providing an option to circumnavigate the need for overhead lines and associated wayleaves for connections by land.

- 6. HVDC can even be used as a form of network *resilience* to weather: in Canada, in response to ice loading on overhead lines, a bipole link can be isolated, connected together at one end, and used to pass direct current for de-icing, before being reinstated to the network.

#### Advantages of VSC HVDC

As semiconductor technologies have advanced, newer HVDC topologies have been developed: VSC options allow for a different set of strengths and weaknesses but in general are more technically capable at greater cost. In addition to firing angle ( $\alpha$ ), IGBTs are self-commutating and allow VSC converters to control commutation angle ( $\mu$ ) (p123, [8]). Combined with IGBTs' high-frequency switching capabilities, controllable commutation angles represent a significant

#### CHAPTER 1. INTRODUCTION

advantage by permitting use of pulse width modulation: a converter can be switched to mimic an AC waveform which extends control over active power ( $\alpha$ ) with independent control of reactive power ( $\mu$ ). Thus, it is possible with VSC to connect to low-voltage and completely passive networks, meaning this technology can support a greater variety of network locations, renewable generation<sup>2</sup>, multiterminal HVDC, and blackstart.

- 7. VSC technologies offer improved connectivity through the possibility of *multiterminal* HVDC systems (MTDC), which can allow a resource (such as large offshore wind arrays proposed for the North Sea [8]) to be shared by networks in multiple countries.

- 8. A main advantage is *controllability* of power flows. Back-to-back HVDC links can be used to mitigate risk of frequency events spreading and thus can provide 'firewalls' within a network. Converters can be set to transfer only the power required, and thereby: stabilise networks in terms of active and reactive power; to dampen subsynchronous modes; and can be used to mitigate the short-circuit current contribution of connected generators.

#### Drawbacks

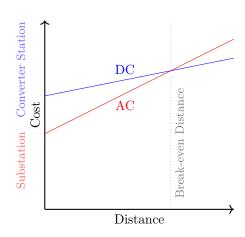

Figure 1.4: Cost-distance relationship for AC and DC connections (p320, [10])

The drawbacks of HVDC systems are their higher costs (when considered independently of capacity and distance – Figure  $1.4^3$ ) relative to conventional AC connections, and possibly limitations with supply chains faced with global demand. Although conversion to DC facilitates subsea connections, such routes are necessarily inaccessible with significant associated costs for installation (and maintenance should a fault arise).

Increasing proportions of converter-connected generation presents challenges for network operation, particularly in terms of inertia. This is also true where demand is reduced on networks designed to be loaded: parts of the network risk becoming loosely controlled.

LCC topologies are vulnerable to disturbances and signal artefacts on the AC network, so require electrically strong network locations to connect to, in the

interests of preventing commutation failure. VSC technologies, on the other hand, can connect to entirely passive networks and are able to cope with AC signal artefacts, but are instead vulnerable to DC line faults by virtue of large DC capacitors shunt connected at each station.

Moreover, given their nature as a relatively recent technological development, HVDC systems present a challenge to operators for their operation and maintenance. That new designs and emerging topologies are used for new developments, there is also a risk that the technology could carry associated risks to asset health over the course of its lifetime. For instance, the Nelson River project experienced a series of coincidental transformer alarms indicative of challenges associated with an early system design.

<sup>&</sup>lt;sup>2</sup>This simple progression from (firing angle controlled) thyristors to (firing and commutation angle controlled) IGBTs is the means by which opportunities in renewables and offshore technologies are unlocked.

$<sup>{}^{3}</sup>$ Break-even distances are stated as around 800 km for overhead line and 50 km for subsea connections [8], [10].

#### Voltage-source Converters

VSC systems are a more modern and capable form of HVDC first introduced in 1997. Their main advantage over thyristor-based LCC topologies is *greater controllability* by using IGBTs, which allow control of both firing and blocking. Combined with higher switching frequencies, this allows more sophisticated behaviour by permitting techniques such as pulse width modulation and third harmonic injection to reduce characteristic harmonics and "synthesise a fully controlled AC voltage, which enables precise control of active and reactive powers" [8].

One of the most important strengths of VSC technology is that these systems are liberated from a need to connect only to strong networks. Instead, they have an ability to connect weak systems and even to network locations which are entirely passive (thus making such links suitable for blackstart capability and in connecting generation).

This high level of controllability means that characteristic harmonics associated with the conversion between AC and DC can be deliberately mitigated. And as each VSC converter can control active and reactive power *independently* of one another, each converter station can act as a static compensator (STATCOM) to support the local AC network.

A reduction in characteristic harmonics of VSC systems as well as removing a need for voltage support at the point of connection means that VSC systems require *less filtering*, which leads to the possibility of further reductions in the required footprint of VSC converter stations. Such filtering arrangements are also simpler, as they can be permanently connected to the converter and need not be switched in and out according to load profiles (page 136, [8]), thereby further removing concern for longevity of switchgear designated in LCC arrangements for this task in meeting daily load profile variation.

In LCC systems, STATCOMs bridge any difference between the reactive power required and that supplied by the filter banks connected at a given point in time. As VSC topologies can instead control this reactive power, the need for a separate supporting STATCOM diminishes.

VSC converters permit *smooth reversal* of power flow, such that they can participate more fluidly within modern networks. However, appropriate choice of dielectric must be made for cables in order for this capability to be realised in practise. This is an important ability since VSC links can transfer just the power required at any given point of time, and the ability to reverse the direction of power flow allows such systems to play a role in accommodating daily and seasonal variation in network use, and even should network power flows change over time as new connections are made.

VSC systems can be *multi-terminal*, which means they could be used to connect a common resource to multiple possible beneficiaries, such as in the case of proposals for islands of offshore wind connected to a number of surrounding countries.

#### Modular Multilevel Converters

Modular multilevel converter (MMC) topologies [11] are designed around half-bridge 'submodule' switching elements [12] which lead to more complex and less technologically mature designs, but offer much greater controllability. This in turn allows harmonic output to be minimised, significantly reducing the need for filtering and reactive power support and thus facilitating even further reduced station footprints.

#### 1.3.3 Early Experience of HVDC: the Nelson River Transformers

One of the first HVDC systems brought online experienced seemingly coincidental failures [13], which suggests something intrinsic to this early link had not been fully understood at the time. An HVDC system was commissioned to connect Winnipeg in Manitoba, Canada to a hydro power station on the Nelson River, and was brought online in 1979. This link was commissioned with mercury arc valves (it would later be upgraded with Alstom's H300 thyristors in 1990 [9] and then with further thyristors in 1993 [13]), was expanded in its capacity in 1983 and 1984, and had new generation connected between 1990 and 1992. It has one  $\lambda$  and one  $\Delta$  transformer for a 12-pulse valve group on each of its two bipoles, which, when duplicated at both rectifier and inverter, sums to a total of 8 converter transformers first put into service in 1978 [14].

During these transformers' operation, a series of failures plagued the project (in particular where ethylene gassing occurred within the oil) as listed in Table 1.1  $[14]^4$ . Two transformers were returned to their manufacturer in 1978, and others later had remedial modifications.

Table 1.1: Nelson River HVDC converter transformer (Tx.) failures [14]

| Month       | Tx. Location            | Protection                              | Fault Location |

|-------------|-------------------------|-----------------------------------------|----------------|

| Feb 1994    | Inverter $(\downarrow)$ | Gas Alarm $\rightarrow$ Manual Block    | Valve winding  |

| May 1998    | Rectifier $(\bot)$      | Ground Differential Relay               | Line winding   |

| Aug 1998    | Rectifier $(\Delta)$    | Pressure Relief                         | Valve winding  |

| Nov 1999    | Inverter $(\Delta)$     | Pressure Relief                         | Valve winding  |

| Feb 2000    | Inverter $(\downarrow)$ | Sudden Pressure Alarm                   | Valve winding  |

| Sept $2000$ | Rectifier $(\Delta)$    | Gas Alarm $\rightarrow$ Pressure Relief | Valve winding  |

These provoke two noteworthy considerations. Firstly, the similar timescales of these failures is interesting in the context of their approximately twenty-year service at time of their respective failures. Second is the similar nature of the failures in predominantly being associated with the first few winding turns, particularly on valve windings [13], [14]. Importantly, on inspection, there is strong evidence of breakdown *between adjacent winding turns* on the first handful of valve winding turns where paper has in some cases been seen to be "virtually incinerated" [14].

Secondly, while alarms associated with these failures were sudden and unanticipated (even where online gas monitoring had been installed), all transformers analysed had signs of prior aging or of having suffered gradual deterioration over a sustained duration. With the exclusion of the September 2000 failure these were respectively: • returned to factory in 1979 with concern around metal particulates; • similarly returned in 1979 due to ethylene gassing; • returned in 1991 due to ethylene gassing; • evidence on post-mortem of reduced insulation resistance on winding turns; and • with paper wrapping and enamel destroyed on the first turns on all legs.

Possible causes of this breakdown mechanism are harmonics (characteristic or otherwise) introduced by conversion between AC and DC, and the potential for voltage impulses [15]. Since the reactance of an inductive winding  $X_L = j\omega L$ , where  $\omega = 2\pi f$ , is proportional to the signal frequency f, transients at high frequencies see each transformer winding as a "large reactance" [15], such that high frequency signals reach only the first few turns. Accordingly, this leads to voltage discrepancies between adjacent turns and puts stress on intermediate dielectrics.

Conventional converter station topologies feature transformers as the *first* assets seen on the AC side of converter valves, *next to which is filtering equipment* designed to attenuate harmonic signals before an interface to an AC system [9].

<sup>&</sup>lt;sup>4</sup>The author offers his condolences to those privileged to have known the late first author of these papers.

Nowadays, converter transformers are designed to be more robust to such transients, by increasing the strength of insulation for at least the first winding turns seen by such transient signal artefacts (harmonics and commutation impulses) where "the thickness of the paper tape layer varies with the local stress" (p. 589 [16]). However, it is not yet apparent from the literature that similar precautions are adopted for *other* assets in the vicinity of a converter station valve hall beyond high-criticality converter transformers. As filter banks are the target destination for a converter station's characteristic harmonics, their assets are those electrically next subjected to high-frequency signal components from transformers. Should such evidently stressful signal artefacts be dissipated by local impedances and dielectrics, this highlights these assets' suitability for further investigation with a view to unlocking potential improvements in their design, possibly analogous to those now adopted as a common practise for transformers.

### 1.3.4 Criticality, Reliability, and Availability

Possible options for converter switching controllability can additionally enhance network capacity not only by interconnection, but through power factor correction, series compensation, and connection of renewable sources dispersed across a network in terms of both connection voltage and location. Thus, the introduction of HVDC links to a network has potential to unlock benefits and offer *combined capabilities* greater than the sum of their parts.

Since these technologies are responsible for greater capacities, they become more critical to network operation and as a component of power electronic interfaces and standalone power factor correction, shunt capacitor banks correspondingly become "increasingly important" for reliable power systems [17], across voltage levels. Since interconnection projects are typically for large capacities, their availability is increasingly critical [18] for: • network diversity; • providing access to bulk storage; and • allowing placement and connection of geographically disparate renewable resources. As this trend toward greater penetrations of renewable generation continues, and as network inertia wanes, power systems will become increasingly reliant on converter-connected systems. Hence, to maximise benefits to networks and encourage development of similar projects [19], availability is paramount for converter-based systems.

#### Risks

Despite an increasing prevalence in electrical power infrastructure due to a growth of HVDC and other power electronic applications (such as reactive power compensation, for instance), and despite accordingly becoming more critical to network reliability, at present fault location and monitoring for high voltage capacitors has received "very little" attention in the literature [20].

Conventional LCC converter topologies offer high capacities, but introduce characteristic and non-characteristic harmonics, and where these systems are deployed, there is a consequent risk posed to existing and potentially aged assets. Moreover, since many of these systems are recent, bespoke developments and employ technologies which continue to be refined, reliability information can be limited, commercially sensitive, and in any case is not readily available.

Rather than await statistical information on asset reliability, it is preferable to anticipate degradation and failure of certain assets. Representative models can simulate stresses and breakdown processes to aid understanding of how assets degrade over time. Simulation can also be used to investigate the influence of assets' operational environment and dynamic characteristics, which could each deviate from measurements acquired offline under static conditions.

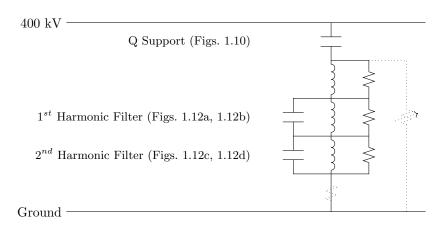

Figure 1.5: A filter bay line diagram (p108, [9])

#### Harmonic Filtering and Voltage Support

Characteristic harmonics result from conversion between AC and DC power, by nature of the converter (valve) topology: for example, on a 12 pulse topology the AC side would have a filter for the  $11^{th}$  and  $13^{th}$  harmonics with the possibility of a  $12^{th}$  harmonic filter on the DC side. Figure  $1.5^5$  shows filters which attempt to keep harmonics within limits and protect other transmission assets from these high frequencies. To accommodate multiple harmonics, and to offer a degree of redundancy, there are ordinarily multiple such filter bays connected in parallel.

Voltage support at a point of connection is similarly important. LCC systems require a strong network location to mitigate risk of commutation failure, so are often sited electrically near synchronous generation (Figure 1.6e) and reactive power ('Q') support is critical.

Filtering assets are therefore central to safeguarding the electrical conditions necessary for converter technologies to contribute to a power network without degrading established (and, depending on where a connection is made, potentially critical) electrical infrastructure.

High voltage capacitor banks are one such asset, which perform a dual function within LCC converter stations: 1. as part of tuned filtering arrangements; and 2. in providing reactive power to support an interface between a converter station and the AC network it connects to.

### 1.3.5 Design Informed by Reliability Centred Maintenance

Although modern converter topologies are increasingly sought, conventional alternatives remain commercially viable for high-capacity connections to strong networks. Hence, it is possible that any design refinements could be considered for systems yet to be commissioned [19]. Moreover, HVDC and other converter interfaces have a large role to play in providing an element of controllability to existing networks under emerging use conditions.

Being able to build sensors into equipment during manufacture offers the ability to apply unit testing to equipment, for use throughout its development during the integration stages, acceptance testing, and then throughout its operational life. Being able to predict the remaining useful life of assets allows for longer lead times on replacement assets, in turn meaning that assets can be manufactured from further afield, aiding globalisation and economics of scale.

<sup>&</sup>lt;sup>5</sup>Different grounding arrangements are reported in the literature, where some filter bays are grounded via a resistance and others use variable resistances as in [9].

## **1.4** Commercial Considerations

The Western Link HVDC link is a 420 km long, 2.2 GW 600 kV<sup>6</sup> bipole LCC connection between Hunterston in Ayrshire, Scotland, and Deeside, North Wales [21]. This link was motivated by a need to improve network capacity so as to accommodate a growth in renewable energy in Scotland requiring transmission to demand centres in England and Wales.

While HVDC projects such as the Western Link [22] can be controlled to actively attenuate subsynchronous modes<sup>7</sup> and hence improve capacity of existing network assets, control algorithms are not typically shared, meaning operators are unable to consider converter control as an option. Instead, operators prefer to isolate a link should oscillations pose problems [23].

Scottish Power Energy Networks (SPEN) even suggested that HVDC links can exacerbate the presence of subsynchronous modes. Such links introduce large capacitances to the network, so there is potential to significantly alter its resonant frequency and thereby increase the likelihood that an existing subsynchronous resonance could cause problems and damage assets already connected and in safe operation for years. There is scope for improved understanding among industry participants, which in this case could mean greater openness about how technologies work such that, not only could problems in the introduction of new technologies be mitigated, but benefits to the long-term operation of the network could be unlocked.

#### 1.4.1 Scottish Power Energy Networks' Converter Station

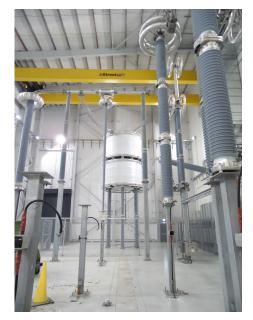

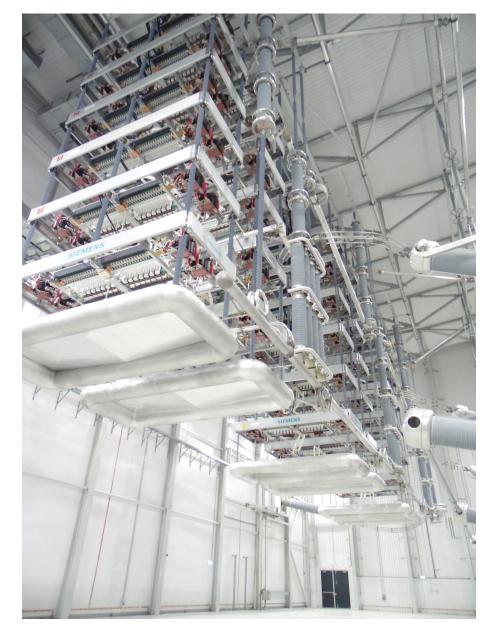

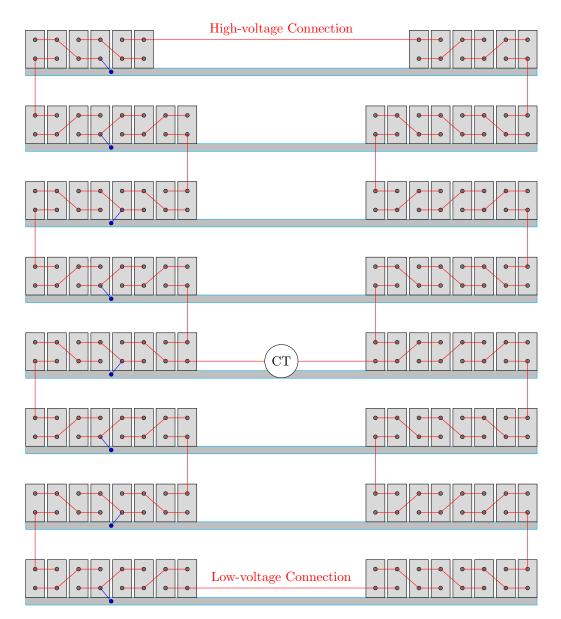

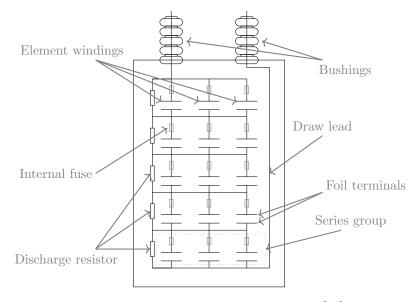

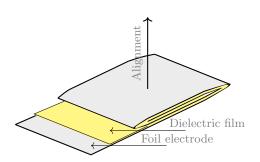

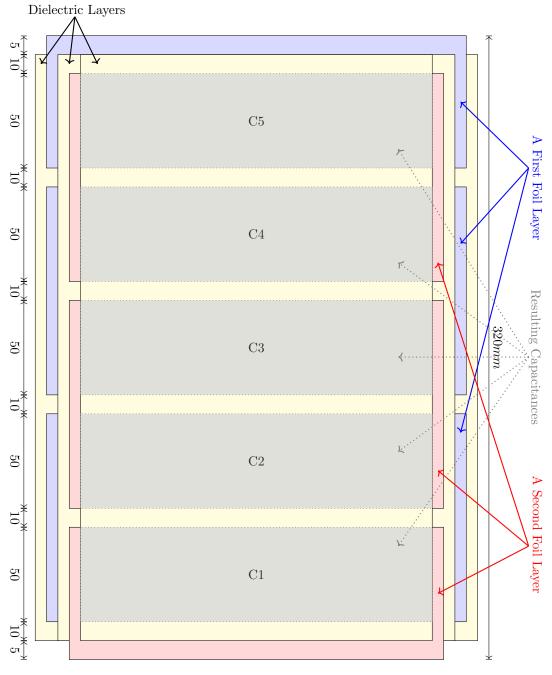

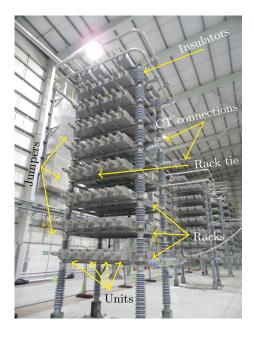

Figures 1.6, 1.7, 1.8, 1.9, 1.10, and 1.12 show a selection of photographs<sup>8</sup> from a visit to Hunterston converter station, kindly facilitated by industry colleagues as this research project began. Although these photographs relate to one specific converter station, they are shown in this section to provide a graphical introduction to the type of equipment typical for conventional converter stations generally. From the capacitor bank arrangements in Figure 1.10, and the system voltage, typical voltages across a individual unit can be inferred to approximately 10 kV.

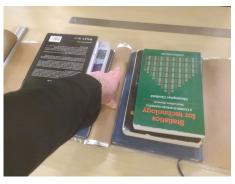

To illustrate, Figure 1.10b highlights jumper connections between series-connected units in yellow, and Figure 1.11 outlines in more detail the connections evident in Figures 1.10c and 1.10d for a large capacitor bank, including connections to a current transformer (CT), which divides this two-sided bank into an 'H-bridge' arrangement consisting of four series 'strings' of units.

#### Points of Discussion

SPEN share ownership of the Western Link with National Grid, but the contractor (Siemens) is responsible for commissioning and operation of the link for the first five years of service. An early stage of this project involved meeting with Alastair Ferguson and Kevin Butter from SPEN in an effort to gauge areas of concern SPEN might have in anticipation of assuming responsibility for operation of this LCC connection and its converter station. Some of the discussion points raised are listed as follows.

<sup>&</sup>lt;sup>6</sup>This project was the first subsea connection at this voltage [21].

<sup>&</sup>lt;sup>7</sup>Subsynchronous resonances (p198, [10]) are oscillations below nominal network frequency as a consequence of series capacitive and inductive effects on long AC network connections, and can effectively limit the maximum capacities practical for critical network links: the 'B6' boundary between Scotland and England in Great Britain is an example. As such oscillations can pose a risk to the mechanical integrity of network-critical synchronous generators, they must be evaluated and network operations accordingly limited to protect valuable generation.

<sup>&</sup>lt;sup>8</sup>Access and photograph permissions were obtained courtesy of SPEN but copyright remains with the author.

(a) DC reactor

(c) Heat extraction

(e) Hunterston B nuclear facility

(b) Converter valves

(d) Spare converter transformer

(f) AC network connection

Figure 1.6: Main components of Hunterston HVDC converter station

Figure 1.7: Valve hall

Figure 1.8: Filter hall

(a) Filter bay (looking south)

(c) CT for 400 kV bank

(b) View along filter bays (looking westward)

(d) Other RL assets in the filter bay

Figure 1.9: Hunterston HVDC converter station filter bay assets

(a) Eastern elevation of a capacitor bank

(c) Large capacitor bank (eastern elevation)

(b) Western elevation (with jumpers in yellow)

(d) Large capacitor bank (western elevation)

Figure 1.10: Varied unit orientations at Hunterston HVDC converter station

Figure 1.11: Jumper (red), rack tie (blue), and CT connections for both sides of a large bank

(a) Elevation of a second capacitor bank

(c) Small capacitor bank (southern elevation)

(b) Opposite elevation of a second bank

(d) Small capacitor bank (northern elevation)

Figure 1.12: Capacitor banks at Hunterston HVDC converter station

- Monitoring for the STATCOM. This is a single point of failure for both poles of the converter station and it is not possible to enter the room while it is online, and hard to see in the door, such that a means of online monitoring for this particular asset would be valuable to SPEN as a future operator of this site.

- Monitoring for the cable. The cable is the single largest investment in the link, covers a large distance, and is not easily accessible. It is measured to be around only 4  $\Omega$  which is remarkable given that it spans a distance in excess of 400 km.

- Temperature. More than 500 MW of heat need to be extracted from the converter station under full load, meaning there is a significant challenge to extract heat from the facility and there are also concerns for the health of electrical assets and considerations for personnel safety given the unsuitability of the valve and filter halls as a working environment under conditions where these buildings could reach 40 °C. This is partly due to the need to build the station indoors to protect it from coastal air.

- For operational reasons, filter hall doors must be opened once monthly, possibly only to maintain them. Given implications for a need to isolate nearby filter bays to do this, a form of monitoring could save effort needed to repeat this monthly task.

- To comply with safety rules, significant access restrictions are in place for when the system is operational which likely prevent use of thermal imaging as a monitoring technique.

- HVDC converter station switchgear has a heavy duty cycle. Ordinarily switchgear (circuitbreakers) are used for rare switching events for network reconfiguration or in the event of faults (also, ideally, rare). On HVDC converter stations these must make and break current to connect capacitor banks according to load profiles which vary on a daily basis. Manufacturers' expected lifetimes are based on typical switching duties, rather than those associated with an HVDC link. There is a question about duty cycle but also concerns raised about the unusual currents these assets might have to break or make onto.

- Similarly, transformer tap changers are required for voltage control (and therefore operability of this LCC link) so could be put under additional switching duty. This unusual switching duty could invalidate expectations of asset longevity, which is of particular interest for critical assets such as switchgear and transformers.

- As a regulated asset, no ground return path is permitted for this bipole Western Link. If either pole is out of service there is no return path and as such this link does not have the redundancy often associated with bipole arrangements.

- Thyristors could be prone to failures which could be hard to detect. Each individual cell should be reliable, but there are 28 thyristors per module, 3 modules per valve, and 1 redundant thyristor (which gives per phase 84 overall) where failures can be tolerated on up to 3 thyristors on any valve but at most 1 per module.

- Discharge resistors are designed to dissipate static charge before earthing can be applied, but do not have monitoring. It is thus not presently possible to verify a discharge, and is considered best practise simply to wait for the appropriate time before applying an earth.

- DC-side surge arrestors and DC reactors are considered critical assets, but not as critical as the cable which is comparatively inaccessible and a significant expenditure.

#### **Filtering Capacitors**

Following this dialogue, filtering capacitors were noted as assets facing operational challenges by the: 1. heightened temperatures they will experience over operational lifetimes; 2. electrical proximity to repetitive switching operations; 3. large number on site; 4. need for filter banks to switch in line with daily changes in loading on the link; and 5. filter hall access restrictions.

#### Temperature

LCC HVDC links require strong points of connection on existing networks in order to facilitate commutation. Frequency pertubations on the AC side of a converter station can provoke commutation failure. The Western Link was therefore sited between Hunterston, at the site of a nuclear facility, and Deeside, at a strong node on the transmission network: both are proximal to the coast and are vulnerable to salt concentrations in coastal air.

The Hunterston converter station has electrical assets housed indoors: vast filter and valve halls were constructed for the purposes of protecting electrical assets from the coastal environment and providing a homogenous, controllable operating environment. Assets exposed to sunlight, for instance, can be susceptible to imbalanced lifetimes (and operational performance) when one side is exposed more than another. The trade-off is not only capital cost, but also operational conditions over the long term since infrastructure cannot as readily dissipate heat when it operates indoors. Significant cooling apparatus is necessary on site to extract heat generated by the converter station and regulate the internal environment.

## 1.4.2 A Changing Network

The Western Link was proposed prior to the closure of Longannet coal power station. Hunterston and Deeside were chosen as connection points for being electrically strong points on the transmission network and close to the coast for a cable route to be predominantly subsea.

In time, however, the nature of demand and generation connecting to the network has changed. Coal plants such as Longannet were removed from service, making Scotland one of the first European countries to have completely coal-free generation. As an LCC system, the Western Link takes time to accommodate power reversal, but as synchronous plant in Scotland is being disconnected, this link could prove useful in occasionally transferring power northward beyond its primary envisaged role in supporting export of renewable power to demand centres.

Moreover, one of the risks associated with HVDC converter stations is the nature of characteristic harmonics they can propagate onto electrical networks. One question could concern the effects of increased harmonic output on assets connected electrically nearby, such as transformers associated with the nuclear facility at Hunterston, as seen from the converter station building by the view in Figure 1.6e. At time of writing it now seems certain that Hunterston B will soon be disconnected and eventually decomissioned [24]. While this implies that: (a) the LCC Western Link could stand to benefit from additional voltage support to strengthen this network location; and that (b) this might relieve the aging but critical assets which connect this 1970's nuclear station from characteristic and non-characteristic harmonics induced by a new converter station within close electrical proximity (as highlighted in Section 1.3.3); it remains the case that (c) LCC systems generally connected at 'strong' network locations can nonetheless threaten critical, and potentially aged assets already in situ, such as generation transformers.

## Chapter 2

## Background

Literature associated with capacitor assets mimics that of HVDC more generally, as introduced in Chapter 1, in that a significant portion of research endeavour understandably focusses on improvements in future designs, and comparatively little considers failure mechanisms of existing technology. Human factors possibly contribute to a dynamic in which self-motivated research best lends itself toward 'building' new technologies (which stand to be more readily seen and appreciated [25]) rather than protection of existing ones, possibly if "no one wants to dwell on the inevitable demise" of important infrastructure [26]. This Chapter introduces the research direction pursued, offers an overview of capacitor unit designs, bank topologies, and briefly discusses failure modes: research directions and motivations are outlined in Section 2.1; and Section 2.2 details the contents of a literature review into capacitor unit designs.

## 2.1 Research Avenues

More recent HVDC projects are based on modern converter topologies. While such designs are interesting in their own right, this project primarily focusses on routes toward a means of condition monitoring, and as such the most recent project designs are not necessarily of greatest interest. Rather, those topologies which are potentially the most liable to faults and to which operators have already made substantial long-term commitments stand to benefit most from any means of monitoring or mitigation which could result from present-day research. Moreover, learning from existing systems is a potentially fruitful source of improvements for enhancements which can be incorporated in emerging system designs. This project therefore has a predominant focus on more conventional, line commutated converter (LCC) HVDC systems.

### 2.1.1 Capacitors

Capacitors are deployed as primary or auxiliary assets in support of a variety of applications within power systems, most notably in power factor correction, harmonic filtering, signal smoothing, and voltage support for modern electrical power systems. Capacitors connected in series are effective in mitigating voltage drop (such as on long spans of network used to reach distant demand or generation), and are additionally especially effective in correcting power factors where there is inherent line reactance [10]. Series capacitors can also smoothen transitions which occur where demand or generation fluctuate, as is characteristic of renewable resources.

#### CHAPTER 2. BACKGROUND

Shunt capacitors are introduced where line current is limited by thermal considerations.

Capacitors are critical for conventional, modern, and emerging HVDC system topologies. In the context of power electronic converters, capacitors fulfil three important roles:

- 1. *harmonic filtering* by accommodating and smoothly dissipating the heightened energies in high-frequency signal components within tuned filters;

- 2. *voltage support*, which for conventional (LCC) arrangements crucially enables smooth converter operation by mitigating against network disturbances and commutation failure;

- 3. facilitating power conversion directly as controllable components in modern topologies.

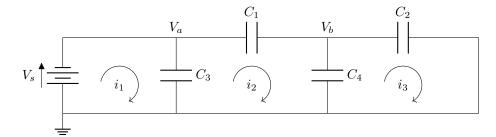

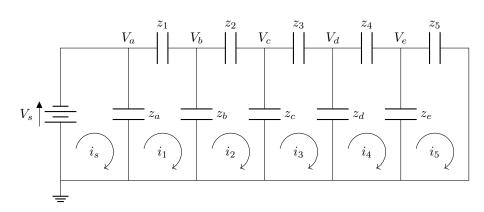

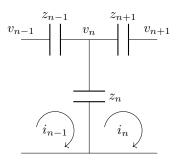

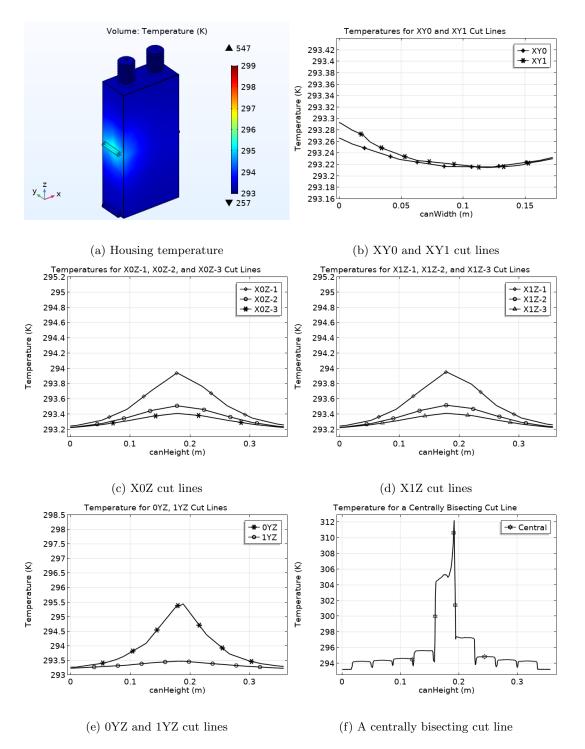

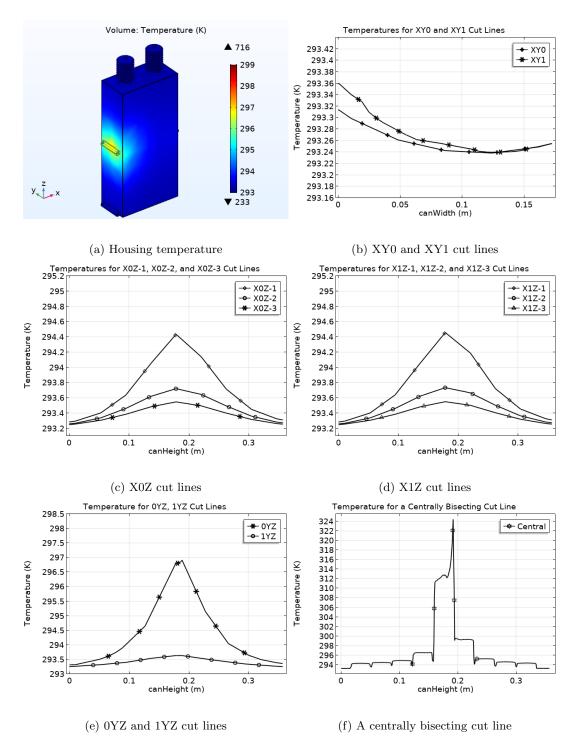

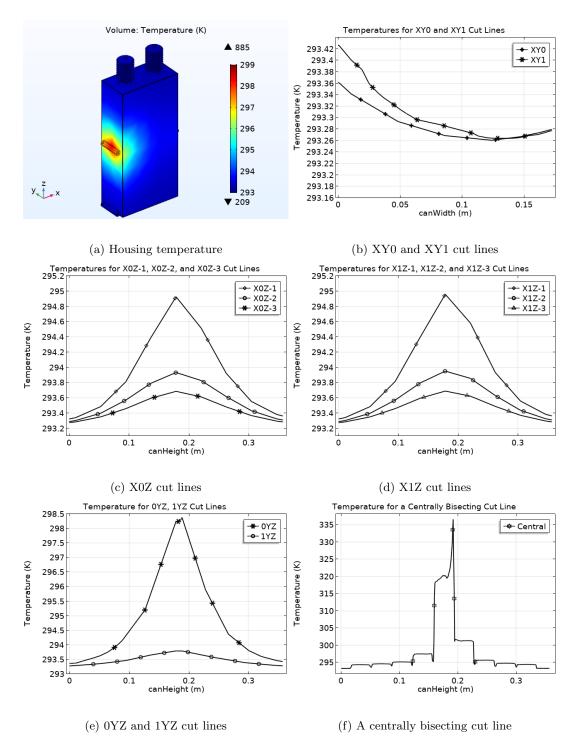

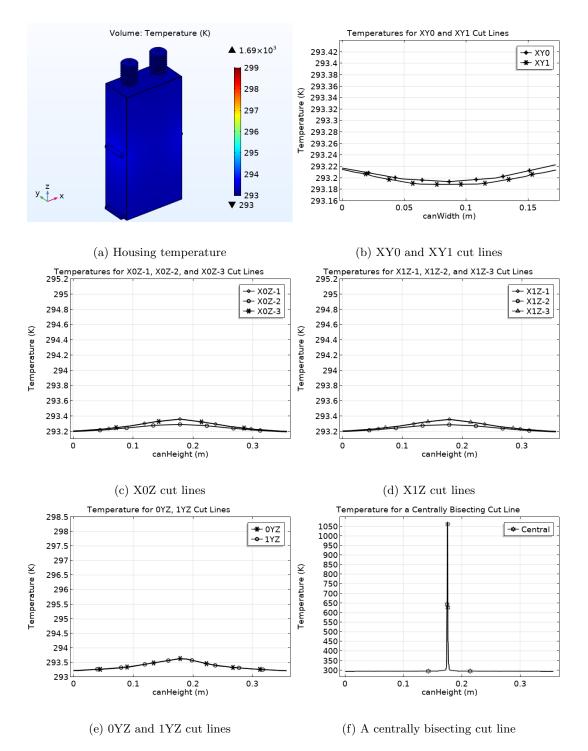

In filtering arrangements (Figure 1.8) specifically, capacitor banks attenuate characteristic harmonics generated by the conversion process: switching elements introduce discontinuities as they fire (or, in VSC, block) a sinusoidal waveform at any point other than its zeros.