## Towards Development of Flexible Sensor Systems Based on Organic Thinfilm Transistors

By

#### AMAYIKAI AJIBAUKA ISHAKU

Submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

Department of Electronic and Electrical Engineering

University of Strathclyde

2021

**Declaration of Authenticity and**

**Author's Rights**

This thesis is the result of the author's original research. It

has been composed by the author and has not been previously

submitted for examination which has led to the award of a

degree.

The copyright of this thesis belongs to the author under

the terms of the United Kingdom Copyright Acts as qualified

by University of Strathclyde Regulation 3.50. Due

acknowledgement must always be made of the use of any

material contained in, or derived from, this thesis.

Amayikai Ajibauka Ishaku

Date: November 2021

ii

# This thesis is dedicated to my loving family, caring friends, and supportive supervisors

#### **Author's Declaration**

I declare that the work presented in this thesis has been carried out by me, unless otherwise acknowledged.

Amayikai Ajibauka Ishaku

Date: November 2021

#### Acknowledgement

First and foremost, I would like to thank the almighty God for his blessings seeing me through my studies.

To my supervisors, Dr Helena Gleskova and Prof. Ivan Glesk, I would like to show my greatest gratitude for this opportunity and your patience throughout. I have grown and gain valuable knowledge, skills, and confidence through your wisdom.

To my dad, Rev. Ishaku Bitrus Ajibauka, and Ruth, I would like to thank you for your prayers, support, and your words of encouragement; "If they can do it, you can too", "You can achieve anything you set your mind to". Without your abundance of support and guidance none of this would be possible.

To my mom, Blessing, thank you for your support and for keeping me on track in my academic and personal life, your prayers for my success and support have been with me throughout.

To my sister Grace for always asking "so how long do you have left", it's finally finished! Thank you for always being there for me, your endless support, encouragement, prayers, and cooking skills are unmatched!

To my sister Hebron, thank you for always keeping me company. Your dedication for your work has kept me inspired and motivated. Last but not least, to my inquisitive baby brother Eben, thank you for the noise and chaos while I was studying at home, now I can cope with stress and work well under pressure:).

#### **Abstract**

To date, significant progress has been made to advance the performance of organic thin-film transistors (OTFTs). These included new materials and structures and innovative fabrication methods to yield properties such as light-weight, mechanical flexibility, and low-temperature fabrication. Yet, many OTFTs still suffer from low on-state drain current and electrical instability seen as a hysteresis or a shift in the transistor transfer characteristics, thus hindering wider OTFT applications. This thesis aims to tackle these issues by presenting low-voltage OTFTs based on air-stable dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) and hydrophobic bi-layer dielectric made of aluminium oxide and octadecyl phosphonic acid (AlO<sub>x</sub>/C<sub>18</sub>PA) on PEN substrates. The fabricated transistors are approximately hysteresis-free and exhibit on-state drain current approaching 100 µA at gate-source and drain-source voltages of -2 V. This is a notable advancement compared to the performance of similar devices reported in the literature and indicative of a robust design and fabrication. High on-state drain current was enabled by ultra-thin gate dielectric and interdigitated source/drain contacts leading to high channel width-to-length ratio and small transistor area.

The electrical stability was studied in the above transistors, both fresh and aged. AC square pulses with constant bias time of 1 second and varying pulse period were simultaneously applied to gate and drain of the transistor to simulate the recurrent turn-on/turn-off transistor operation. OTFT performance marginally degraded under AC pulses, with the exception of field-effect mobility that improved. Degradation

proceeded faster in aged OTFTs stored in dark ambient environment but the on-state drain current stabilised after ~500 pulses. The stabilisation resulted from the rising field-effect mobility compensating the threshold voltage increase. Finally, the inclusion of the above OTFT as a voltage amplifier in a temperature sensor system raised the temperature sensitivity by a factor of ~5, thus laying foundation for future flexible sensors and circuit applications.

#### **Table of contents**

| Abs  | tract  |                                                                                | vi    |

|------|--------|--------------------------------------------------------------------------------|-------|

| List | of fig | gures                                                                          | xi    |

| List | of ta  | bles                                                                           | xviii |

| List | of sy  | mbols and acronyms                                                             | xix   |

| List | of pu  | ıblications                                                                    | xxv   |

| Cha  | pter   | 1: Introduction                                                                | 1     |

| 1.1  | Or     | ganic electronics                                                              | 1     |

| 1.2  | Th     | esis motivation                                                                | 3     |

| 1.3  | Th     | esis objectives                                                                | 5     |

| 1.4  | Th     | esis outline                                                                   | 6     |

| 1.5  | Th     | esis contributions                                                             | 7     |

| Refe | erence | es                                                                             | 8     |

| Cha  | pter : | 2: Research background                                                         | 11    |

| 2.1  | Or     | ganic thin-film transistors (OTFT)                                             | 12    |

| 2.   | 1.1    | Metal-insulator-metal structure                                                | 13    |

| 2.   | 1.2    | OTFT structures and materials                                                  | 15    |

| 2.2  | ГО     | FT Operation                                                                   | 17    |

| 2.   | 2.1    | Linear regime $ V_{DS} <  V_{GS}  -  V_{TH} $ and $ V_{GS}  >  V_{TH} $        | 20    |

| 2.   | 2.2    | Saturation regime $ V_{DS}  \ge  V_{GS}  -  V_{TH} $ and $ V_{GS}  >  V_{TH} $ | 22    |

| 2.   | 2.3    | Subthreshold regime $ V_{GS}  <  V_{TH} $                                      | 22    |

| 2.3  | ГО     | FT Parameters                                                                  | 23    |

| 2.4  | To     | wards integration in analogue circuits                                         | 25    |

| 2.   | 4.1    | OTFT performance improvement                                                   | 26    |

| 2.   | 4.2    | Analogue circuit applications                                                  | 31    |

| 2.5  | Su     | mmary                                                                          | 33    |

| Refe | erence | es                                                                             | 33    |

| Cha  | pter : | 3: Methodology                                                                 | 42    |

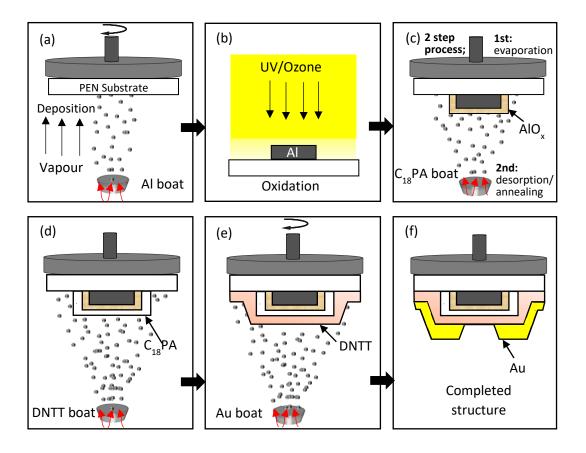

| 3.1  | Fal    | orication on PEN: MIM and OTFT structures                                      | 43    |

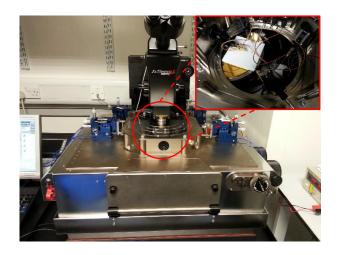

| 3.2  | Мє     | easurement: MIM structures                                                     | 47    |

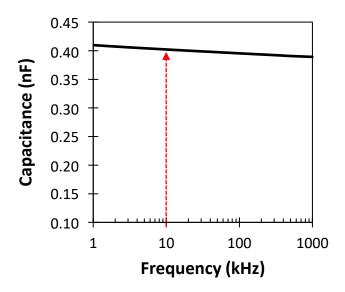

| 3.   | 2.1    | Capacitance of MIM structures                                                  | 48    |

| 3.   | 2.2    | Gate dielectric capacitance per unit area                                      | 49    |

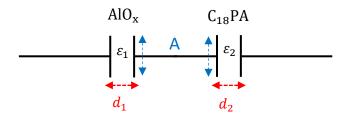

| 3.2  | 2.3         | AlO <sub>x</sub> and C <sub>18</sub> PA thicknesses                                                                              | 50      |

|------|-------------|----------------------------------------------------------------------------------------------------------------------------------|---------|

| 3.3  | Me          | easurement: OTFT                                                                                                                 | 51      |

| 3    | 3.1         | Transfer characteristics                                                                                                         | 51      |

| 3    | 3.2         | Output characteristics                                                                                                           | 55      |

| 3    | 3.3         | OTFT hysteresis                                                                                                                  | 56      |

| 3    | 3.4         | OTFT with high transconductance on PEN                                                                                           | 57      |

| 3    | 3.5         | Transistor channel dimension                                                                                                     | 58      |

| 3.4  | Me          | easurement: OTFT response to pulsed bias stress                                                                                  | 59      |

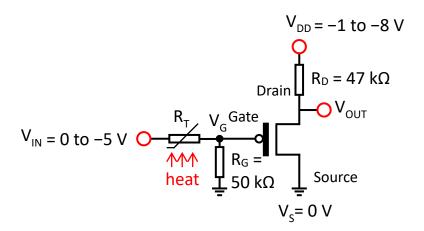

| 3.5  | Co          | nstruction: OTFT-based temperature sensor system                                                                                 | 61      |

| 3.6  | Me          | easurement: OTFT-based temperature sensor system                                                                                 | 63      |

| 3.0  | 6.1         | Temperature vs. thermistor response                                                                                              | 65      |

| 3.0  | 6.2         | Effect of resistor R <sub>G</sub> on gate voltage                                                                                | 65      |

|      | 6.3<br>nsor | Effect of temperature and supply voltage on OTFT based temperature for temperature and supply voltage on OTFT based temperature. | erature |

| 3.7  | Su          | mmary                                                                                                                            | 67      |

| Refe | rence       | ·S                                                                                                                               | 67      |

|      | _           | 4: High transconductance OTFTs with interdigitated source                                                                        |         |

|      |             | n PEN foils                                                                                                                      |         |

| 4.1  |             | roduction                                                                                                                        |         |

| 4.2  |             | perimental details                                                                                                               |         |

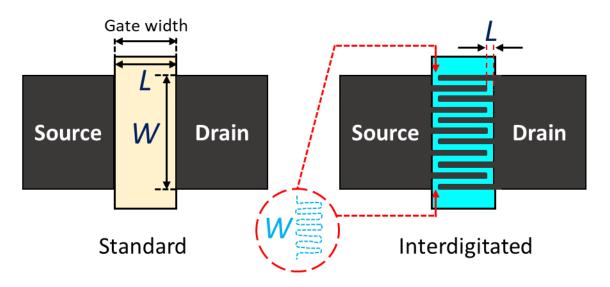

|      | 2.1         | Interdigitated source/drain contacts                                                                                             |         |

|      | 2.2         | Drain current and AC transconductance                                                                                            |         |

| 4.3  |             | erdigitated source/drain contact in narrow-gate OTFTs                                                                            |         |

|      | 3.1         | Transfer and output characteristics                                                                                              |         |

|      | 3.2         | Field-effect mobility and threshold voltage                                                                                      |         |

|      | 3.3         | On-state and off-state drain currents                                                                                            |         |

|      | 3.4         | Sub-threshold slope                                                                                                              |         |

|      | 3.5         | Gate leakage current                                                                                                             |         |

| 4.4  |             | erdigitated source/drain contact in wide-gate OTFTs                                                                              |         |

|      | 4.1         | Field-effect mobility and threshold voltage                                                                                      |         |

|      | 4.2         | On-state and off-state drain currents                                                                                            |         |

|      | 4.3         | Sub-threshold slope                                                                                                              |         |

|      | 4.4         | Gate leakage current                                                                                                             |         |

| 4 7  | Α(          | transconductance in narrow- and wide-gate OTFTs                                                                                  | 89      |

| 4.:  | 5.1    | Drain current                                               | 89  |

|------|--------|-------------------------------------------------------------|-----|

| 4.:  | 5.2    | AC transconductance                                         | 90  |

| 4.6  | Di     | scussion                                                    | 91  |

| 4.7  | Su     | mmary                                                       | 95  |

| Refe | erence | es                                                          | 96  |

| Cha  | pter   | 5: Bias stress effect in DNTT organic thin-film transistors | 99  |

| 5.1  | Int    | roduction to bias stress effects                            | 100 |

| 5.2  | Ex     | perimental details                                          | 103 |

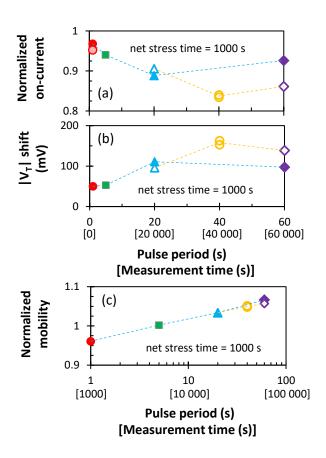

| 5.3  | Bia    | as stress effect in fresh and aged transistors              | 105 |

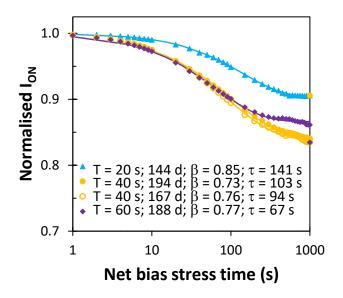

| 5    | 3.1    | On-state drain current                                      | 105 |

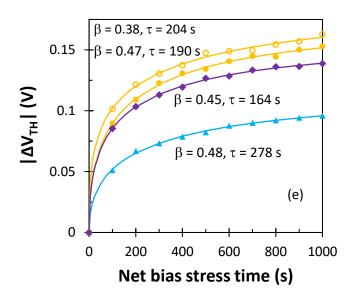

| 5    | 3.2    | Threshold voltage                                           | 106 |

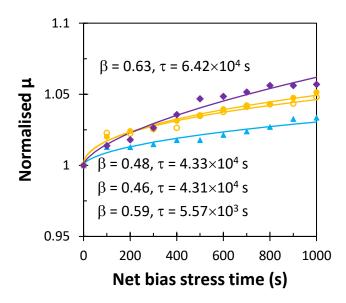

| 5    | 3.3    | Field-effect mobility                                       | 107 |

| 5    | 3.4    | Normalised on-state drain current $I_{ON}(t)/I_{ON}(0)$     | 107 |

| 5    | 3.5    | Threshold voltage shift $ \Delta V_{\mathrm{TH}} $          | 109 |

| 5    | 3.6    | Normalised field-effect mobility $\mu(t)/\mu(0)$            | 110 |

| 5    | 3.7    | Effect of environmental aging                               | 111 |

| 5.4  | Di     | scussion                                                    | 113 |

| 5.5  | Su     | mmary                                                       | 117 |

| Refe | erence | es                                                          | 118 |

| Cha  | pter   | 6 Temperature sensor based on OTFT                          | 121 |

| 6.1  | Int    | roduction                                                   | 122 |

| 6.2  | Ex     | perimental details                                          | 124 |

| 6.2  | 2.1    | Transistor fabrication                                      | 124 |

| 6.2  | 2.2    | Sensor circuit design and experimental setup                | 125 |

| 6.3  | Re     | sults                                                       | 127 |

| 6    | 3.1    | Temperature sensor                                          | 127 |

| 6    | 3.2    | Temperature sensor model                                    | 135 |

| 6.4  | Di     | scussion                                                    | 137 |

| 6.5  | Su     | mmary                                                       | 140 |

| Refe | erence | es                                                          | 141 |

| Cha  | pter   | 7 Conclusions and future work                               | 146 |

| 7.1  | Co     | nclusions                                                   | 146 |

| 7.2  | Fu     | ture work                                                   | 149 |

### List of figures

| Figure 1.1: | OLED ultra-thin panel for lighting [1.13] (a), large area printed organic                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------|

|             | photovoltaic [1.14] (b), and flexible display [1.15] (c)                                                                |

| Figure 2.1: | Schematic diagram of MIM structure                                                                                      |

| Figure 2.2: | OTFT structures: TGBC (a) and BGTC (b)16                                                                                |

| Figure 2.3: | OTFT channel formation. Linear regime ( $ V_{\rm DS}  <  V_{\rm GS}  -  V_{\rm TH} $ ) (a),                             |

|             | pinch-off ( $ V_{\rm DS}  =  V_{\rm GS}  -  V_{\rm TH} $ ) (b), and saturation regime ( $ V_{\rm DS}  >  V_{\rm GS} $ – |

|             | $ V_{\rm TH} )$ (c)                                                                                                     |

| Figure 3.1: | OTFT and MIM structure cross-sectional view                                                                             |

| Figure 3.2: | Flow diagram of MIM structure and OTFT fabrication stages. Note,                                                        |

|             | DNTT (stage d) is omitted during MIM structure fabrication45                                                            |

| Figure 3.3: | Agilent B1500A and probe station for device characterisation49                                                          |

| Figure 3.4: | MIM capacitance as a function of AC frequency49                                                                         |

| Figure 3.5: | Gate dielectric bi-layer, where $A$ is the contact area (identical for $AlO_x$                                          |

|             | and $C_{18}PA$ ), $\epsilon_1$ , $\epsilon_2$ and $d_1$ , $d_2$ are the permittivity and thicknesses of                 |

|             | AlO <sub>x</sub> and C <sub>18</sub> PA respectively                                                                    |

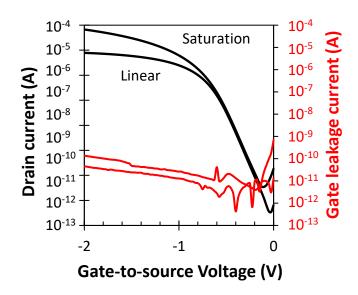

| Figure 3.6: | Transfer characteristics in linear ( $V_{DS} = -0.1 \text{ V}$ ) and saturation regime                                  |

|             | $(V_{\rm DS} = -2 \text{ V})$ for $V_{\rm GS}$ sweep from 0 to $-2 \text{ V}$                                           |

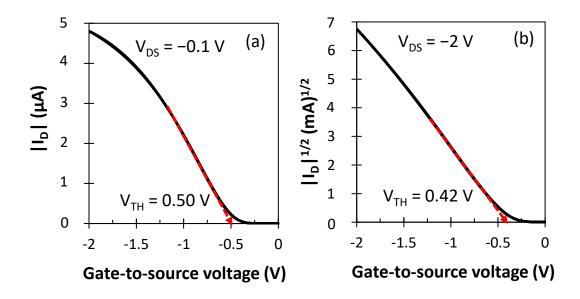

| Figure 3.7: | Threshold voltage extraction from slopes of $I_D$ and $I_D$ as functions of $V_{GS}$                                    |

|             | in linear ( $V_{\rm DS} = -0.1~{\rm V}$ ) (a) and saturation ( $V_{\rm DS} = -2~{\rm V}$ ) (b) regimes 53               |

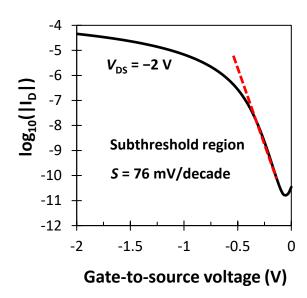

| Figure 3.8: | Subthreshold slope extraction from the subthreshold region                                                              |

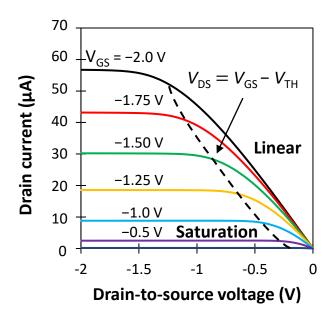

| Figure 3.9: Output characteristics, plot of drain current as a function of drain-to-    |

|-----------------------------------------------------------------------------------------|

| source voltage from 0 to $-2\ V$ and gate-to-source voltage at $-0.25\ V$               |

| increments. Dashed line divides the linear and saturation regimes 56                    |

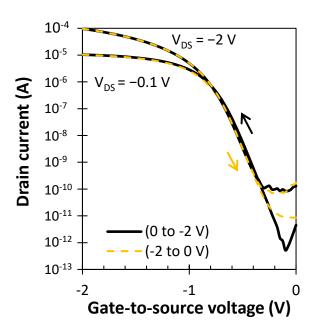

| Figure 3.10: OTFT hysteresis measurement, forward ( $V_{GS} = 0$ to $-2$ V) and reverse |

| $(V_{\rm GS}$ –2 to 0 V) sweep (arrows show the direction of sweep) in linear           |

| $(V_{\rm DS} = -0.1 \text{ V})$ and saturation $(V_{\rm DS} = -2 \text{ V})$ regimes    |

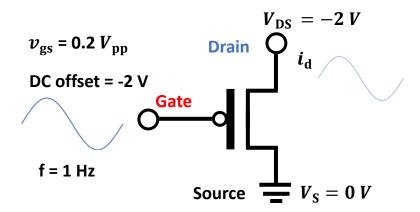

| Figure 3.11: AC transconductance measurement setup                                      |

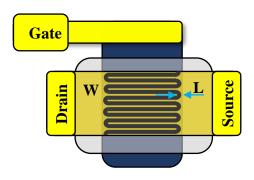

| Figure 3.12: Top view of an organic thin-film transistor with interdigitated            |

| source/drain contacts59                                                                 |

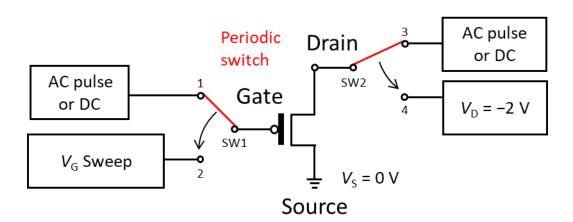

| Figure 3.13: Bias stress setup. The same AC pulse or DC bias were applied to gate       |

| and drain (switch positions 1 and 3 respectively). Transfer characteristics             |

| were measurement by sweeping $V_{GS}$ from 0 to -2 V and $V_{DS} = -2$ V                |

| (saturation) and $V_S = 0$ V (synchronised switch to positions 2 and 4                  |

| respectively) 61                                                                        |

| Figure 3.14: OTFT-based temperature sensor schematic                                    |

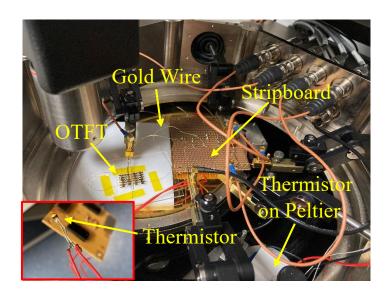

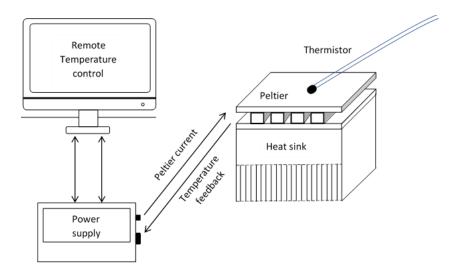

| Figure 3.15: Temperature sensor measurement setup                                       |

| Figure 3.16: Thermistor temperature control system setup                                |

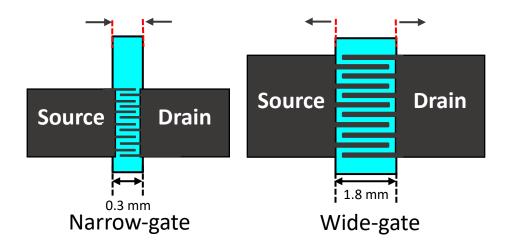

| Figure 4.1: Standard rectangular and interdigitated source/drain contacts71             |

| Figure 4.2: Schematic of narrow gate and wide-gate OTFTs                                |

| Figure 4.3: Top-view of narrow-gate width OTFT with $L = 17 \mu m$ and $W = 4.03 mm$ .  |

| 74                                                                                      |

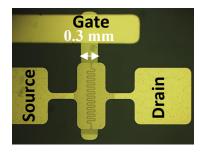

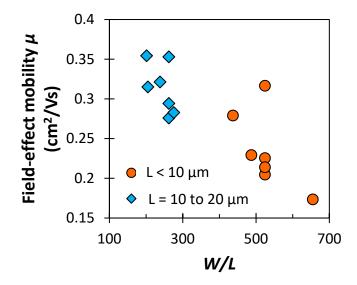

| Figure 4.4: Transfer (a, b) and output (c, d) characteristics for wide-gate (a, c) and  |

| narrow-gate (b, d) OTFTs on PEN. Each curve shows hysteresis                            |

| measurement from 0 to -2 V (solid line) and back (dash lines) 75                        |

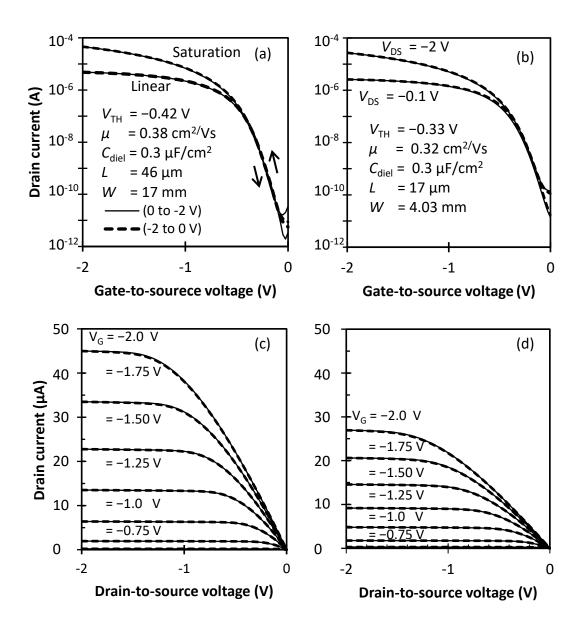

| Figure 4.5: Field-effect mobility as a function of <i>W/L</i> for narrow-gate OTFTs with    |

|---------------------------------------------------------------------------------------------|

| interdigitated source/drain contacts and $L < 10 \mu m$ (circles) or $L = 10$ to            |

| 20 μm (diamonds)                                                                            |

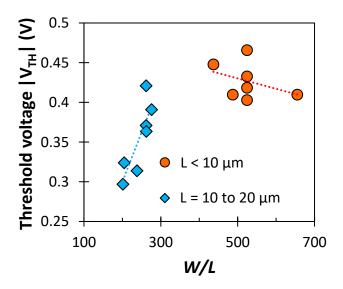

| Figure 4.6: Threshold voltage as a function of <i>W/L</i> for narrow-gate OTFTs with        |

| interdigitated source/drain contacts and $L < 10 \mu m$ (circles) or $L = 10$ to            |

| 20 μm (diamonds)                                                                            |

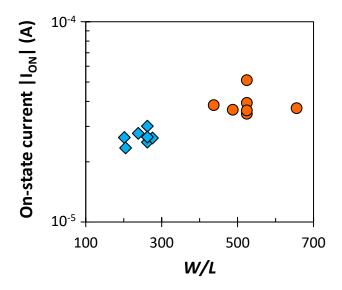

| Figure 4.7: On-state drain current as a function of <i>W/L</i> for narrow-gate OTFTs with   |

| interdigitated source/drain contacts and $L < 10 \mu m$ (circles) or $L = 10$ to            |

| 20 μm (diamonds) <b>79</b>                                                                  |

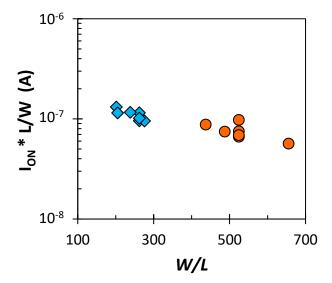

| Figure 4 8: Normalised on-state drain current as a function of <i>W/L</i> for narrow-gate   |

| OTFTs with interdigitated source/drain contacts and $L < 10 \mu m$ (circles)                |

| and $L = 10$ to 20 µm (diamonds)                                                            |

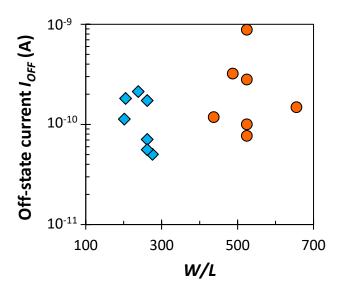

| Figure 4.9: Off-state drain current as a function of <i>W/L</i> for narrow-gate OTFTs with  |

| interdigitated source/drain contacts and $L < 10 \mu m$ (circles) or $L = 10$ to            |

| 20 μm (diamonds) <b>80</b>                                                                  |

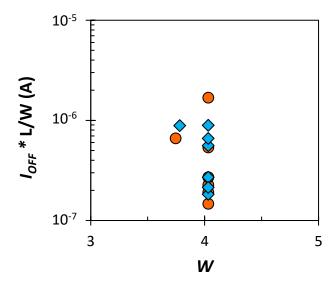

| Figure 4.10: Normalised off-state drain current as a function of W for narrow-gate          |

| OTFTs with interdigitated source/drain contacts and $L < 10 \mu m$ (circles)                |

| or $L = 10$ to 20 $\mu$ m (diamonds)                                                        |

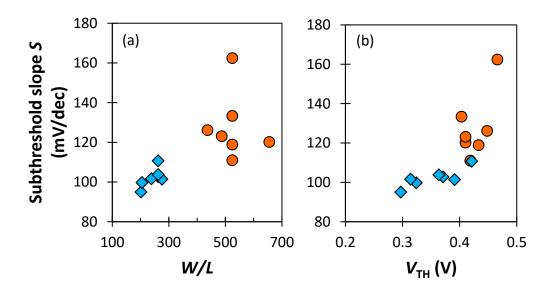

| Figure 4.11: Subthreshold slope as a function of $W/L$ (a) and $V_{TH}$ (b) for narrow-gate |

| OTFTs with interdigitated source/drain contacts and $L < 10 \mu m$ (circles)                |

| or $L = 10$ to 20 µm (diamonds)                                                             |

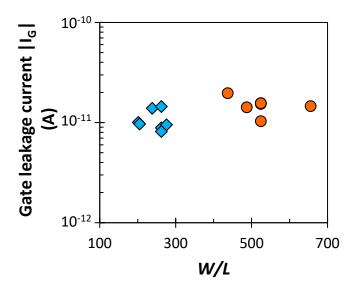

| Figure 4.12: Gate leakage current as a function of <i>W/L</i> for narrow-gate OTFTs with             |

|------------------------------------------------------------------------------------------------------|

| interdigitated source/drain contacts and $L < 10 \ \mu m$ (circles) or $L = 10 \ to$                 |

| 20 μm (diamonds) <b>82</b>                                                                           |

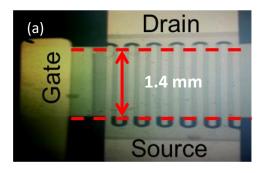

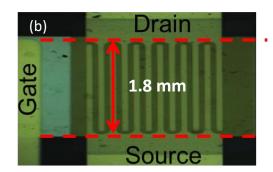

| Figure 4.13: Gate width manipulation in wide-gate OTFTs resulting in reduced gate                    |

| width of 1.4 mm and $W = 15.40$ mm (a) and full gate width of 1.8 mm                                 |

| and $W = 18.23$ mm (b). Dashed horizontal lines show the gate width                                  |

| boundaries                                                                                           |

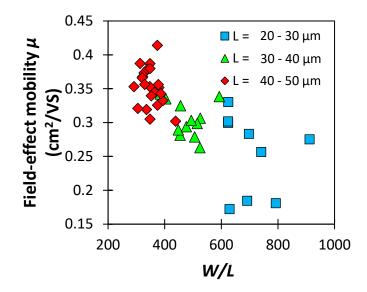

| Figure 4.14: Field-effect mobility as a function of <i>W/L</i> for wide-gate OTFTs with              |

| interdigitated source/drain contacts and $L=20$ to 30 $\mu m$ (square), $L=30$                       |

| to 40 $\mu$ m (triangles), or $L=40$ to 50 $\mu$ m (diamonds)                                        |

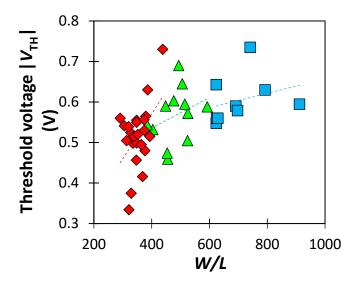

| Figure 4.15: Threshold voltage as a function of <i>W/L</i> for wide-gate OTFTs with                  |

| interdigitated source/drain contacts and $L=20$ to 30 $\mu m$ (square), $L=30$                       |

| to 40 $\mu$ m (triangles), or $L=40$ to 50 $\mu$ m (diamonds)                                        |

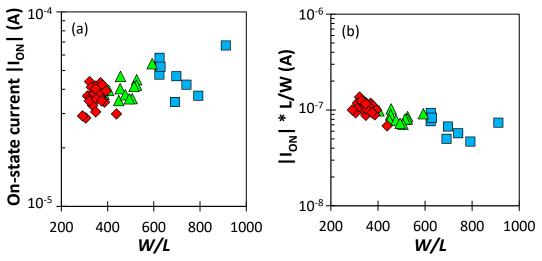

| Figure 4.16: On-state drain current (a) and normalised on-state drain current (b) as                 |

| functions of $W/L$ and channel lengths $L = 20$ to 30 $\mu$ m (squares), 30 to 40                    |

| μm (triangles) and 40 to 50 μm (diamonds) <b>86</b>                                                  |

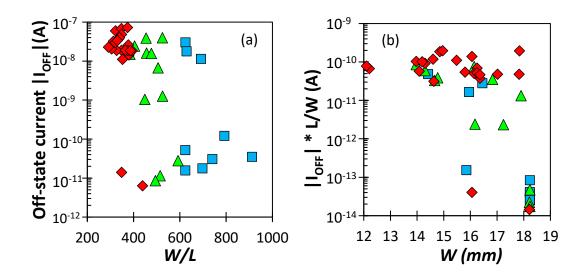

| Figure 4.17: Off-state drain current (a) and normalised off-state drain current (b) as               |

| functions of $W/L$ and width $W$ respectively, for channel length $L=20$ to                          |

| $30~\mu m$ (squares), $30$ to $40~\mu m$ (triangles) and $40$ to $50~\mu m$ (diamonds).<br><b>86</b> |

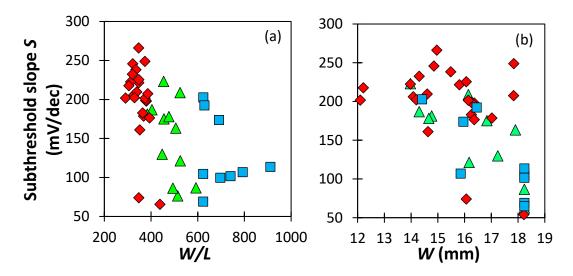

| Figure 4.18: Subthreshold slope as a function of $W/L$ (a) and $W$ (b) for wide-gate                 |

| OTFTs with interdigitated source/drain contacts and $L = 20$ to 30 $\mu m$                           |

| (square), $L = 30$ to 40 µm (triangles), or $L = 40$ to 50 µm (diamonds), 87                         |

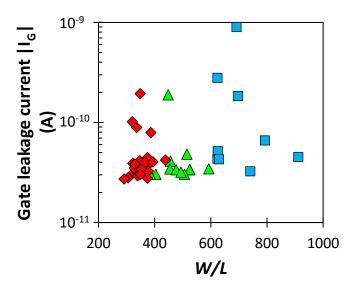

| Figure 4.19: | Gate leakage current as a function of <i>W/L</i> for wide-gate OTFTs with                |

|--------------|------------------------------------------------------------------------------------------|

|              | interdigitated source/drain contacts and $L = 20$ to 30 $\mu$ m (square), $L = 30$       |

|              | to 40 $\mu$ m (triangles), or $L = 40$ to 50 $\mu$ m (diamonds)                          |

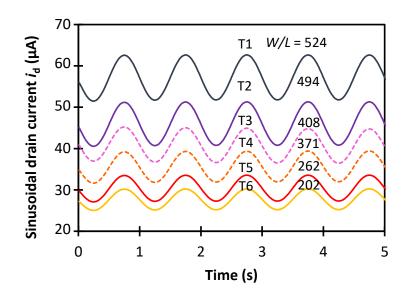

| Figure 4.20: | Sinusoidal drain current as a function of time (for $v_{gs}$ of $-0.2V_{pp}$ , and       |

|              | $V_{\rm DS}$ and $V_{\rm S}$ of $-2$ V and 0 V respectively. The solid and dashed lines  |

|              | correspond to narrow- and wide-gate transistors, respectively90                          |

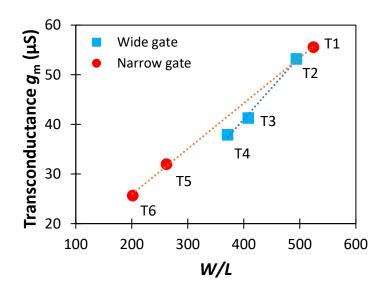

| Figure 4.21: | AC transconductance $g_m$ as a function of $W/L$ for narrow-gate (circles)               |

|              | and wide-gate (squares) OTFTs91                                                          |

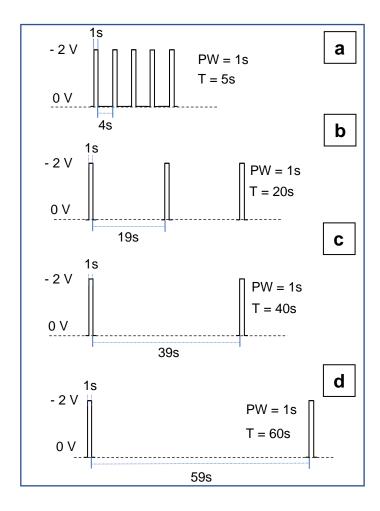

| Figure 5.1:  | AC pulse signals with 1-s-pulse width (PW), on-state and off-state                       |

|              | voltages of -2 V and 0 V, and period (T) of 5s (a), 20s (b), 40s (c) and                 |

|              | 60s (d). During the bias stress the same pulse was applied to the gate and               |

|              | drain of the transistor                                                                  |

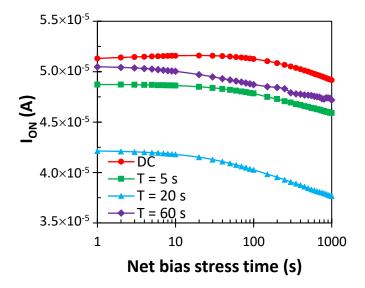

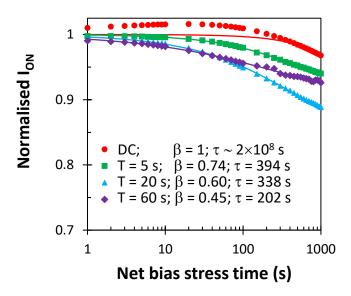

| Figure 5.2:  | On-state drain current $I_{\rm ON}$ as a function of net bias stress time for DC         |

|              | (circles), and AC pulse periods with 1 s on-time and periods; $T = 5$ s                  |

|              | (square), 20 s (triangles) and 60 s (diamonds)                                           |

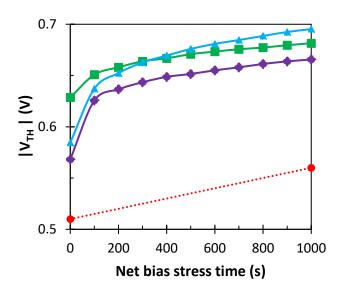

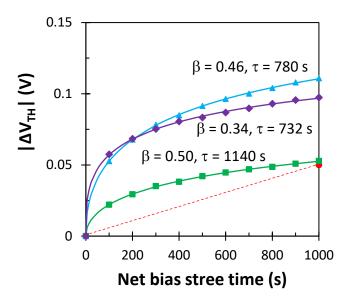

| Figure 5.3:  | Threshold voltage $V_{\mathrm{TH}}$ as a function of net bias stress time. The legend of |

|              | Figure 5.2 applies                                                                       |

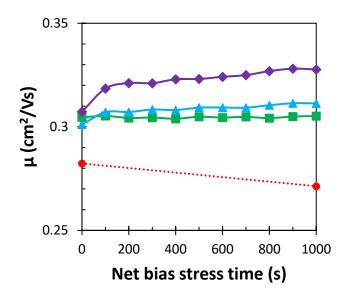

| Figure 5.4:  | Field-effect mobility $\mu$ as a function of net bias stress time. The legend of         |

|              | Fig. 5.2 applies                                                                         |

| Figure 5.5:  | Normalised on-state drain current of freshly fabricated OTFTs as a                       |

|              | function of net bias stress time. Points (symbols) represent measured data               |

| ,            | and lines are the stretched exponential fits with fitting parameters of $\beta$          |

|              | and τ                                                                                    |

| Figure 5.6: | Threshold voltage shift of freshly fabricated OTFTs as a function of net                              |

|-------------|-------------------------------------------------------------------------------------------------------|

|             | bias stress time. The legend of Fig. 5.5 applies110                                                   |

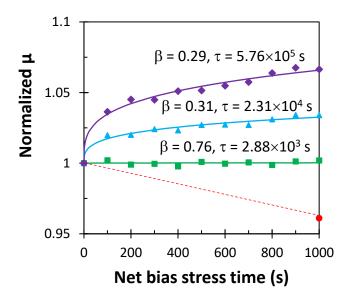

| Figure 5.7: | Normalised filed-effect mobility of freshly fabricated OTFTs as a                                     |

|             | function of net bias stress time. The legend of Fig. 5.5 applies 111                                  |

| Figure 5.8: | Normalised on-state drain current of 5-6 months aged OTFTs as a                                       |

|             | function of net bias stress time                                                                      |

| Figure 5.9: | Threshold voltage shift of 5-6 months aged OTFTs as a function of net                                 |

|             | bias stress time. The legend of Fig. 5.8 applies113                                                   |

| Figure 5.10 | ): Normalised field-effect mobility of 5-6 months aged OTFTs as a                                     |

|             | function of net bias stress time. The legend of Fig. 5.8 applies 113                                  |

| Figure 5.11 | : Normalized on-state drain current (a), threshold voltage shift (b) and                              |

|             | normalized field-effect mobility (c) versus the pulse period T or                                     |

|             | measurement/lapsed time, for net bias stress of 1000 s. DC bias stress is                             |

|             | represented as $T = 1$ s. Full and empty symbols correspond to the fresh                              |

|             | and aged transistors. The light and dark blue dashed lines connect the                                |

|             | measurements from fresh and aged transistors respectively. The pink                                   |

|             | symbol in (a) shows the change in drain current from its maximum value                                |

|             | for DC bias stress                                                                                    |

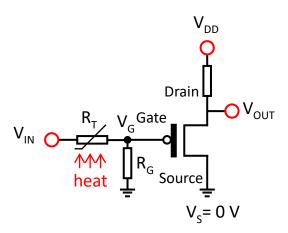

| Figure 6.1: | OTFT based temperature sensor. $V_{\rm IN} = 0$ to $-5$ V, $V_{\rm DD} = -1$ to $-8$ V, $V_{\rm S} =$ |

|             | 0 V. $R_T$ has nominal resistance of 100 k $\Omega$ at 25° C and $R_D$ = 47 k $\Omega$ 126            |

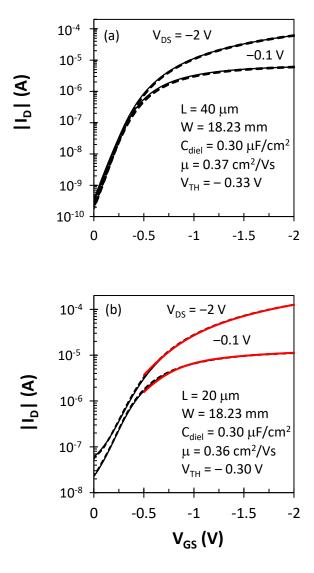

| Figure 6.2: | Transfer characteristics of OTFTs used in the temperature sensor and                                  |

|             | verification model. Solid black lines and dotted lines represent hysteresis                           |

|             | for $V_{\rm GS}$ ramped in forward direction (0 to $-2$ V) and reverse ( $-2$ to 0 V)                 |

|             | respectively. Solid red lines represents the transistor model                                         |

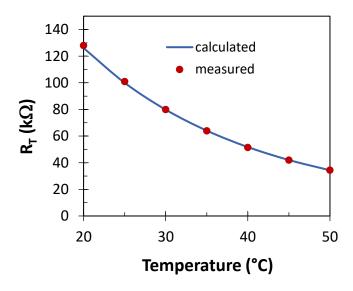

| Figure 6.3: | Temperature response of a thermistor having a nominal resistance of 100                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|

|             | $k\Omega$ at 25°C                                                                                                              |

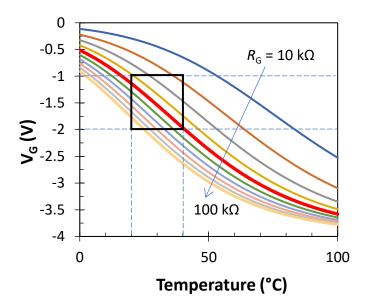

| Figure 6. 4 | : Effects of resistor $R_G$ (10 k to 100 kΩ) on $V_G$ as a function of                                                         |

|             | temperature. The desirable temperature and voltage range for $V_{\rm G}$ are                                                   |

|             | indicated by the black rectangle. The red thick curve corresponds to $R_{\rm G}$ =                                             |

|             | 50 kΩ. The results correspond to $V_{\rm IN}$ = -4 V130                                                                        |

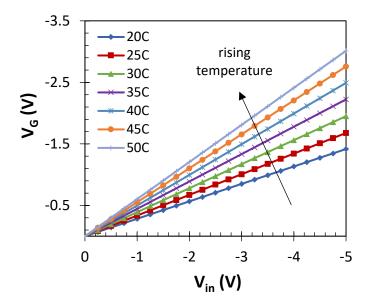

| Figure 6.5: | $V_{\rm G}$ as a function of $V_{\rm IN}$ for temperatures ranging from 20 to 50°C and $R_{\rm G}$                             |

|             | $= 50 \text{ k}\Omega.$                                                                                                        |

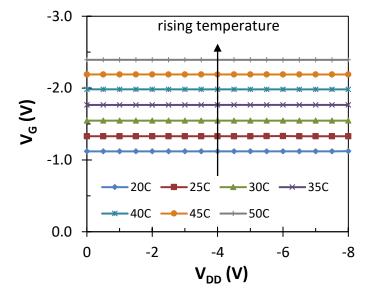

| Figure 6.6: | $V_{\rm G}$ as a function of $V_{\rm DD}$ for temperatures between 20 and 50°C, $R_{\rm G}=50$                                 |

|             | $k\Omega$ , $R_D = 47 \ k\Omega$ and $V_{IN} = -4 \ V$ . $V_G$ is referenced to ground                                         |

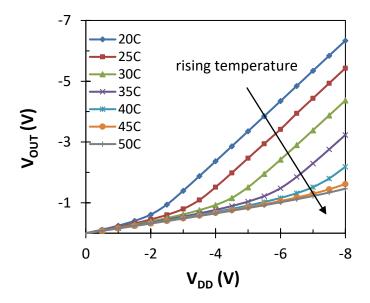

| Figure 6.7: | $V_{\rm OUT}$ as a function of $V_{\rm DD}$ for temperatures between 20 and 50°C, $R_{\rm G}=50$                               |

|             | $k\Omega$ , $R_D = 47 k\Omega$ and $V_{IN} = -4V$                                                                              |

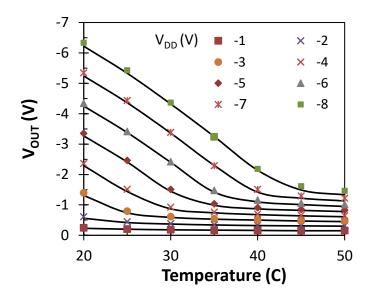

| Figure 6.8: | $V_{ m OUT}$ of temperature sensor as a function of temperature between 20 and                                                 |

|             | 50°C for $R_G$ = 50 kΩ, $R_D$ = 47 kΩ, and $V_{\rm IN}$ = -4 V. The solid black lines                                          |

|             | in (c) correspond to the sensor model                                                                                          |

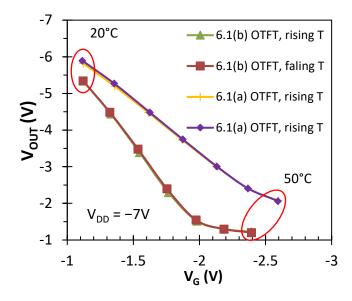

| Figure 6.9: | Repeated measurements of $V_{\text{OUT}}$ as a function of $V_{\text{G}}$ for $V_{\text{IN}} = -4 \text{ V}$ , $V_{\text{DD}}$ |

|             | = $-7$ V, $R_D = 47$ k $\Omega$ , $R_G = 50$ k $\Omega$ and OTFTs of Figure 6.2(a) and (b).                                    |

|             | Rising and falling T represent ramping temperature from 20 to 50°C and                                                         |

|             | from 50 to 20°C respectively                                                                                                   |

#### List of tables

| Table 1. Gate dielectrics for high OTFT capacitance [2.42, 2.43]28                     |

|----------------------------------------------------------------------------------------|

| Table 2. Comparison of MIM structure and OTFT fabrication properties48                 |

| Table 3. Dependence of AC drain current and transconductance on W/L ratio89            |

| Table 4. Gate voltage of the transistor                                                |

| Table 5. Electrical characteristics of OTFTs with interdigitated electrodes in narrow- |

| and wide-gate configurations                                                           |

#### List of symbols and acronyms

#### Acronyms

AC Alternating current

a-IGZO Amorphous indium gallium zinc oxide

BGTC Bottom gate top contact

C-f Capacitance vs frequency

C-V Capacitance vs voltage

D Drain

DC Direct current

DI Deionized

DNTT Dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene

FET Field-effect transistor

G Gate

HOMO Highest occupied molecular orbital

I-V Current vs voltage

LUMO Lowest unoccupied molecular orbital

MIM Metal insulator metal

NTC Negative temperature coefficient

OLED Organic light-emitting diode

OTFT Organic thin-film transistor

PMMA Polymethyl methacrylate

PDQT Diketopyrrole—thiophene

PEN Polyethylene naphthalate

PI Polyimide

ppm Particle per million

PS Polystyrene

PUT Putrescine

PVA Polyvinyl alcohol

PVC Polyvinyl chloride

PVP Polyvinyl phenol

PW Pulse width

RFID Radio frequency identification

RTD Resistance temperature detector

S Source

SAM Self-assembled monolayer

SGOTFT Suspended gate organic thin-film transistor

SPGU Semiconductor pulse generator unit

TC Transfer characteristic

TCR Temperature coefficient of resistance

TGBC Top gate bottom contact

UV Ultraviolet

UVOCS Ultraviolet ozone cleaning system

WF Work function

#### Symbols

$\Delta L/L$  Channel length modulation

$\Delta V_{\text{TH}}$  Threshold voltage shift (V)

$\mu$  Field-effect mobility (cm<sup>2</sup>/Vs)

$\mu_0$  Low-field mobility (cm<sup>2</sup>/Vs)

A Cross-sectional area (cm<sup>2</sup>)

Al Aluminium

Al<sub>2</sub>O<sub>3</sub> Aluminium oxide

AlO<sub>x</sub> Aluminium oxide

Au Gold

BaZrTiO<sub>3</sub> Barium zirconium titanate

C Capacitance (F)

C<sub>18</sub>PA Octadecyl phosphonic acid

$C_{Alox}$  Capacitance of aluminium oxide (F/cm<sup>2</sup>)

$C_{\text{C18PA}}$  Capacitance of octadecyl phosphonic acid (F/cm<sup>2</sup>)

$C_{\text{diel}}$  Gate dielectric capacitance per unit area (F/cm<sup>2</sup>)

CeO<sub>2</sub> Ceric oxide

Cr Chromium

d Thickness of the dielectric layer (mm)

$d_1$  Thickness of the AlO<sub>x</sub> layer (mm)

$d_2$  Thickness of the C<sub>18</sub>PA layer (mm)

E(x) Electric field (V/m)

f Frequency (Hz)

g<sub>m</sub> Transconductance (S)

H<sub>2</sub>O Water

HfO<sub>2</sub> Hafnium oxide

$I_{\rm D}$  Drain current (A)

*i*<sub>d</sub> Drain-to-source current (peak-peak) (A<sub>PP</sub>)

$I_{\rm G}$  Gate leakage current (A)

*I*<sub>OFF</sub> Off-state drain current (A)

*I*<sub>OFF</sub>\**L/W* Normalised off-state drain current (A)

*I*<sub>ON</sub> On-state drain current (A)

*I*<sub>ON</sub>\**L/W* Normalised on-state drain current (A)

$I_{\rm ON}/I_{\rm OFF}$  On/off current ratio

J Current density (A/cm<sup>2</sup>)

k Dielectric constant or relative permittivity

*L* Channel length (μm)

$L_{\rm p}$  MIM structure electrode length ( $\mu$ m)

*n* Number of MIM structures

N<sub>2</sub> Nitrogen

O<sub>2</sub> Oxygen

P(VDF-TrFE) Poly(vinylidene fluoride-trifluoroethylene)

P(VDF-TrFE-CFE) Poly(vinylidene fluoride-trifluoroethylene-chlorofluroethylene)

Q Accumulated charge (C)

q Charge of an electron (C)

Q(x) Charge density at point x in the channel (C/m)

$R_{\rm C}$  Contact resistance ( $\Omega/{\rm cm}^2$ )

$R_{\rm CH}$  Channel resistance ( $\Omega/{\rm cm}^2$ )

$R_{\rm D}$  Drain resistance ( $\Omega$ )

$R_{\rm G}$  Gate resistance  $(\Omega)$

$R_{\rm T}$  Thermistor resistance  $(\Omega)$

S Subthreshold slope (mV/decade)

t Time (s)

T Pulse period (s)

Ta<sub>2</sub>O<sub>5</sub> Tantalum pentoxide

te Channel thickness (nm)

TiO<sub>2</sub> Titanium oxide

TiO<sub>x</sub> Titanium oxide

V External voltage (V)

V(0) Voltage at the source side of the channel (V)

V(L) Voltage at the drain side of the channel (V)

V(x) Voltage at point x in the channel (V)

$V_{\rm D}$  Drain voltage (V)

$V_{\rm DD}$  Supply voltage (V)

VD<sub>EODR</sub> Effective overdrive drain voltage (V)

$V_{\rm DS}$  Drain-to-source voltage (V)

$V_{\rm G}$  Gate voltage (V)

$V_{GS}$  Gate-to-source voltage (V)

$v_{\rm gs}$  Gate-to-source voltage (peak-peak) ( $V_{\rm PP}$ )

$V_{\rm IN}$  Input voltage (V)

$V_{\text{OUT}}$  Output voltage (V)

$V_{PP}$  Peak- to-peak voltage (V)

$V_{\rm S}$  Source voltage (V)

VS<sub>EODR</sub> Effective overdrive source voltage (V)

$V_{SS}$  Subthreshold slope voltage (V)

$V_{\text{TH}}$  Threshold voltage (V)

W Channel width (mm)

$W_{\rm p}$  MIM structure electrode width (mm)

x Point located along the channel length between drain and source

ZrO<sub>2</sub> Zirconium dioxide

$\alpha$  Steady state value at infinity

$\beta$  Stretching parameter

γ Mobility enhancement factor

$\delta_{VT}$  Threshold voltage bias sensitivity

ε Permittivity

$\epsilon_0$  Permittivity of vacuum (F/m)

$\epsilon_r$  Relative permittivity

λ Channel modulation factor

p Hole carrier density (/cm²)

$\sigma$  Electrical conductivity (S/m)

$\tau$  Time constant (s)

#### List of publications

#### Journal papers

- **1.** Amayikai A. Ishaku and Helena Gleskova. "Potential of low-voltage organic transistors with high on-state drain current for temperature sensor development." *Organic Electronics*, vol. 93, 2021, p. 106152.

- Afra Al Ruzaiqi, Amayikai A. Ishaku, and Helena Gleskova. "Organic thin film transistors with multi-finger contacts as voltage amplifiers." *IEEE Access*, vol. 6, 2018, p. 43770-43775.

#### **Conference papers**

- 1. Amayikai A. Ishaku, Afra Al Ruzaiqi, and Helena Gleskova. "Low-Voltage High-Transconductance Dinaphtho-[2, 3-b: 2', 3'-f] thieno [3, 2-b] thiophene (DNTT) Transistors on Polyethylene Naphthalate (PEN) Foils." *IEEE International Conference on Flexible and Printable Sensors and Systems* (FLEPS). IEEE, 7<sup>th</sup> 10<sup>th</sup> July 2019, Glasgow, UK.

- 2. Amayikai A. Ishaku, Aris Tranganidas, Slavomír Matúška, Róbert Hudec, Graeme McCutcheon, Lina Stankovic, Helena Gleskova. "Flexible force sensors embedded in office chair for monitoring of sitting postures." 2019 IEEE International Conference on Flexible and Printable Sensors and Systems (FLEPS). IEEE, 7<sup>th</sup> 10<sup>th</sup> July 2019, Glasgow, UK.

## Chapter 1

#### Introduction

#### 1.1 Organic semiconductors in electronics

The introduction of organic semiconductors and the subsequent development of various organic devices has transformed the field of flexible and wearable electronics. The term 'organic' refers to material compounds composed of primarily carbon and hydrogen, while 'semiconductor' refers to materials with electrical conductivity which lies between a conductor with high conductivity and insulator with low conductivity. Organic semiconductors for organic transistors are based on polymers or small molecules [1.1, 1.2]. Their molecular properties make them insulators until becoming semiconducting as a result of charge injection, optical excitation, or thermal activation [1.3]. Their electrical conductivity and formation of electric current depends on the charge carrier transport in the highest occupied

molecular orbital (HOMO) or lowest unoccupied molecular orbital (LUMO), also referred to as the valence and conduction bands in inorganic semiconductors, respectively [1.4]. Low-lying HOMO energy levels have been shown to promote air and thermal stability and high carrier mobility in small molecule organic semiconductors such as dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT), [1.1] making them favourable organic semiconductor material for transistor research.

The advantage of organic semiconductors lies in their chemistry. Organic semiconductors can be modified at the molecular level to provide wide variety of customisation to meet design requirements [1.5]. Therefore, organic semiconductors can have molecular properties allowing them to flex, stretch or print on flexible substrates [1.6], with minimal or reversible effect on performance or stability [1.7]. Additionally, self-healing properties have also been explored for electronic skin applications [1.8]. Such use of organic semiconductors in organic thin-film transistors has fuelled the rapid progress of flexible and wearable devices, thus altering the way technology is implemented and used. With potential for scalability, integration of electronics onto flexible substrates, and inexpensive large-area roll-to-roll manufacturing compatible with printing technology, it is no surprise that innovative applications including flexible organic light emitting diode (OLED) displays and lighting, and large-area printed organic solar cells [1.9-1.12] are becoming increasingly popular, see Figure 1.1.

**Figure 1.1:** OLED ultra-thin panel for lighting [1.13] (a), large area printed organic photovoltaic [1.14] (b), and flexible display [1.15] (c)

#### 1.2 Thesis motivation

The current state of flexible and wearable electronics demands inexpensive materials and simple low-temperature fabrication techniques married with devices that deliver high performance at low-voltages, while enabling mechanical flexibility. Organic thin-film transistors (OTFTs) are ideal candidates offering great potential through careful selection of materials, downscaling in size for increased integration density [1.16], and diverse range of flexible and stretchable substrate solutions. This is in contrast to traditionally rigid, bulky, and fragile inorganic devices. In addition, OTFT-based sensors could provide initial stage amplification and on-site transducing of physical stimulus into electrical signal in miniaturised sensors. Yet, OTFTs have some drawbacks. Current state-of-the-art solutions address their performance, low-

voltage operation, short-channel downscaling effects, hysteresis, and electrical or atmospheric instabilities. Some of the developed solutions are not adopted, typically because of cost, obtainability of material and/or equipment, complexity of procedures, or trade-off between enhancement of a target parameter and degradation in other parameters. For example, downscaling transistor size and channel length for increased integration density, enhanced operating speed and reduced cost is met with short channel and contact resistance effects.

This thesis discusses the fabrication, optimisation, analysis, and sensor demonstration of a low-voltage, hysteresis-free DNTT organic thin-film transistor that is optimised using simple approach to meet its integration in flexible analogue circuits and sensors. It aims to fabricate OTFTs on polyethylene naphthalate (PEN) plastic substrate to enable mechanical flexibility and to employ ultra-thin gate dielectric of medium-k material functionalised with a self-assembled monolayer (SAM) to achieve high capacitance ( $C_{\rm diel}$ ), low leakage current ( $I_{\rm G}$ ), and low-voltage transistor operation. Finally, enhancement of the on-state drain current ( $I_{\rm ON}$ ) and transconductance ( $g_{\rm m}$ ) for voltage gain amplification relies on modification of the transistor channel with interdigitated source/drain contacts based on the work previously conducted in [1.17].

OTFT stability is crucial throughout its lifetime of usage and storage. Therefore, understanding the effects of electrical and environmental factors on the OTFT performance and the origin of any transistor deterioration are essential for predicting the device behaviour over time, particularly after integration. Consequently, investigation of the bias stress effect and ambient storage is performed on fresh and aged transistors, then a stretch-exponential model is fitted to examine the degradation

in the performance parameters. Finally, integration of the OTFT in an analogue temperature sensor system is presented. Here, the transistor performs the task of transducing temperature stimuli into electrical signal and provides initial amplification.

#### 1.3 Thesis objectives

This thesis builds on the previous development and optimisation of low-voltage OTFTs on glass substrate based on DNTT organic semiconductor and bi-layer gate dielectric made of ozone-oxidised Al functionalised with octadecyl phosphonic acid at Strathclyde University [1.17]. The following objectives were set to advance the research towards flexible analogue circuit and sensors:

- OTFT fabrication on PEN Fabrication of DNTT OTFTs on PEN substrates.

This should involve employment of interdigitated source/drain contacts to maximise the channel width (W) to length (L) ratio and achieve increased drain current and transconductance. The transistors should maintain the low-voltage operation, low gate-leakage current, and hysteresis-free behaviour.

- OTFT stability Study of a bias stress effect under AC conditions. The AC bias stress should mimic the recurrent turn-on/turn-off of the transistors, as such approach may be implemented in sensors with infrequent data collection [1.18].

- OTFT-based sensor Design of a temperature sensor based on the OTFT transistor amplifier. The experimental sensor data should be accompanied by a model that reproduces and allows prediction of the sensor behaviour in future sensor designs.

#### 1.4 Thesis outline

This thesis is organised into 7 chapters and focuses on the fabrication, development, analysis, and sensor demonstration of low-voltage, high transconductance organic thin-film transistors based on DNTT and fabricated on PEN foils.

Chapter 2 looks at the background literature and discusses the transistor structures, materials, parameters, and regimes of operations. Furthermore, it reflects on state-of-the-art employed towards development of analogue circuits and applications. Chapter 3 describes all fabrication procedures, measurements, OTFT parameter extraction and evaluation of the metal-insulator-metal (MIM) structures. It also describes the experimental setup and measurement techniques used in the investigation of the OTFT bias stress instability, followed by the design, measurement, and analysis of OTFT-based temperature sensor system. Chapter 4 presents and discusses the effectiveness of interdigitated source/drain contact geometry and gatewidth variations employed in two different OTFT designs for increasing the channel width to length ratio (W/L) and enhancing transistor performance. Finally, it confirms the effect of W/L on AC drain current and transconductance. Chapter 5 provides a study of AC bias stress on low-voltage, high drain current OTFTs and highlights the impact of ageing and pulse period (T) on the stability of the transistors. Chapter 6 investigates the design, construction, and full system analysis of a temperature sensor system based on high-transconductance OTFT. A DC compact model of the transistor's transfer characteristic (TC) is included in the sensor model, and a comparison between the theory and experiment is given. Finally, chapter 7 presents the key conclusions and suggests potential future work.

#### 1.5 Thesis contributions

This thesis details the fabrication, evaluation, and integration of low-voltage, high-transconductance DNTT OTFTs on plastic substrate into analogue sensors. The principal contributions are summarised below.

The adoption of interdigitated source/drain contacts significantly increased the drain current and transconductance of the OTFTs on PEN substrate. While the DNTT-based OTFTs with similar cross-section and standard layout of the source/drain contacts previously achieved drain current of  $\sim 1~\mu A$  at  $V_{DS} = V_{GS} = -2~V$  [1.19], the OTFTs on PEN foils achieved drain current of up to  $\sim 120~\mu A$ .

Next, investigation of the transistor stability under AC conditions was performed. For the first time, square AC pulses with varied pulse period were simultaneously applied to the drain and gate electrodes, causing the transistor to turn on and off repeatedly. The turn-on and turn-off voltages were -2 and 0 V respectively and four different pulse periods were used: T of 5, 20, 40 and 60 s. For each T, 1000 pulses with turn-on time of 1 s and varying turn-off times were applied to the transistors, leading to the aggregate net stress time of 1000 s in all cases. The reduction in the on-state drain current did not exceed 17% and stabilization was observed after only 500 cycles in some cases. This stabilisation is believed to result from the simultaneous increase in field-effect mobility and threshold voltage. The maximum

degradation in the on-state drain current occurred for medium T, thus making T = 60 s a favourable condition for sensor systems.

Finally, the above transistors were investigated for sensor development. To demonstrate the voltage-amplifying ability of such transistors for raising the sensitivity of a sensor, the OTFT was used to increase the response to the temperature ordinarily achieved with a thermistor. Two transistors with on-state drain current of  $\sim$ 60 and  $\sim$ 120  $\mu$ A were tested, leading to voltage gain of  $\sim$ 2.8 and  $\sim$ 4.9 V/V, respectively, thus increasing the sensor sensitivity by a factor of up to 5.

#### **References**

- [1.1] Usta, Hakan, and Antonio Facchetti. "Polymeric and small-molecule semiconductors for organic field-effect transistors." *Large Area and Flexible Electronics*, 2015, p. 1-100.

- [1.2] Facchetti, Antonio. "Semiconductors for organic transistors." *materials today*, vol. 10, no. 3, 2007, p. 28-37.

- [1.3] Bässler, Heinz, and Anna Köhler. "Charge transport in organic semiconductors." *Unimolecular and supramolecular electronics I*, 2011, p. 1-65.

- [1.4] Brédas, Jean-Luc, et al. "Organic semiconductors: A theoretical characterization of the basic parameters governing charge transport." *Proceedings of the National Academy of Sciences*, vol. 99, no. 9, 2002, p. 5804-5809.

- [1.5] Ahmad, Shamim. "Organic semiconductors for device applications: current trends and future prospects." *Journal of Polymer Engineering*, vol. 34, no. 4 (2014), p. 279-338.

- [1.6] Søndergaard, Roar R., Markus Hösel, and Frederik C. Krebs. "Roll-to-Roll fabrication of large area functional organic materials." *Journal of Polymer Science Part B: Polymer Physics*, vol. 51, no. 1, 2013, p. 16-34.

- [1.7] Bensaid, B., et al. "Reliability of OTFTs on Flexible Substrate: Mechanical Stress Effect." *The European Physical Journal Applied Physics*, vol. 55, no. 2, 2011, p. 23907.

- [1.8] Oh, Jin Young, et al. "Stretchable self-healable semiconducting polymer film for active-matrix strain-sensing array." *Science advances*, vol. 5, no. 11, 2019.

- [1.9] Bonnassieux, Yvan, et al. "The 2021 flexible and printed electronics roadmap." *Flexible and Printed Electronics*, vol. 6, no. 2, 2021, p. 023001.

- [1.10] Zhou, Lisong, et al. "All-organic active matrix flexible display." *Applied Physics Letters*, vol. 88, no. 8, 2006, p. 083502.

- [1.11] Brunetti, Francesca, et al. "Printed solar cells and energy storage devices on paper substrates." Advanced Functional Materials, vol. 29, no. 21, 2019, p. 1806798.

- [1.12] Wang, Guodong, et al. "Large-area organic solar cells: material requirements, modular designs, and printing methods." *Advanced Materials*, vol. 31, no. 45, 2019, p. 1805089.

- [1.13] *LG OLED display Lamp*. 2017 [image] Available at: <a href="https://www.digitaltrends.com/home/lg-oled-lamp-news/">https://www.digitaltrends.com/home/lg-oled-lamp-news/</a>> [Accessed 15 July 2021].

- [1.14] Flexible solar cell. 2008 [image] Available at: <a href="https://www.flickr.com/photos/marufish/2720185982">https://www.flickr.com/photos/marufish/2720185982</a> [Accessed 15 July 2021].

- [1.15] *LG OLED TV*. 2017 [image] Available at: <a href="https://tarnaeluin.houseofbeor.net/ces-2017-reduction/">https://tarnaeluin.houseofbeor.net/ces-2017-reduction/</a> [Accessed 15 July 2021].

- [1.16] Guo, Xiaojun, et al. "Down-scaling of thin-film transistors: Opportunities and design challenges." *ECS Transactions*, vol. 22. no. 1, 2009, p.227.

- [1.17] Afra Salim Mohamed Al Ruzaiqi. Low-voltage organic transistors with high transconductance. PhD Dissertation. University of Strathclyde, 2020.

- [1.18] Fiske, Kate, and Lara Delmolino. "Use of discontinuous methods of data collection in behavioral intervention: Guidelines for practitioners." *Behavior Analysis in Practice*, vol. 5, no. 2, 2012, p. 77-81.

- [1.19] Hannah, Stuart, et al. "Interplay between vacuum-grown monolayers of alkylphosphonic acids and the performance of organic transistors based on dinaphtho [2, 3-b: 2', 3'-f] thieno [3, 2-b] thiophene." *ACS applied materials & interfaces*, vol. 8, no. 38, 2016, p. 25405-25414.

## Chapter 2

#### Research background

In this thesis the OTFT has been optimised to function as a voltage amplifier in a proposed analogue sensor. This development, aimed towards integration into flexible analogue circuits, prioritises advances in low-voltage OTFTs, i.e. it implements structure, materials, and channel geometry to effectively enhance the onstate drain current and transconductance.

This chapter looks at OTFT structures, materials, principles of operation and measured parameters and explores various techniques employed to enhance OTFT performance. It begins with a brief introduction of the organic thin-film transistors and transistor materials and structures in Section 2.1, followed by the background theory and OTFT operation in section 2.2. Section 2.3 discusses various transistor parameters used in the characterisation of transistor performance. Sections 2.4 reflects on state-

of-the-art development and OTFT applications towards organic analogue circuits. Section 2.5 summarises the chapter.

#### 2.1 Organic thin-film transistors (OTFT)

The history of the transistor can be traced back to the late 1940's when the first ever transistor was reported [2.1-2.3]. Described as a dual functioning device, the transistor was the first and only device to function both as a signal amplifier and an electronic signal control switch. Successful implementation of thin-films in transistors in the early 1960's saw the innovation of depositing thin-films of the active layers, dielectrics, metal contacts/electrodes in the first thin-film transistor [2.4]. Two decades later, in the mid 1980's, the implementation of organic semiconductor in the first organic field-effect transistor was reported [2.5].

Today, decades later, the breakthroughs in the organic materials have paved the way towards the commercialisation of organic thin-film transistors. The pursuit of OTFTs in recent years has stemmed from the unique properties offered by the organic materials when compared to their inorganic counterparts. Low-cost, large area fabrication processes replaced complex, expensive and sophisticated vacuum growth techniques combined with photolithography, as required by silicon technology [2.6]. The compatibility of organic materials with low temperature fabrication processes benefited from the introduction of a wide variety of conventional and unconventional substrate materials including glass [2.7], paper [2.8], plastic [2.9] and textile [2.10], making this technology well-suited for wearables and flexible electronics. Notable applications include flexible displays [2.11], bio-sensors [2.12, 2.13], pressure sensors

[2.14], radio frequency identification (RFID) tags [2.15], e-paper [2.16], and wearable cloth [2.17].

#### 2.1.1 Metal-insulator-metal structure

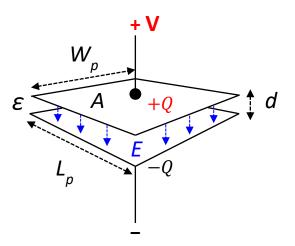

A metal-insulator-metal or MIM structure is a two-terminal system defined by two parallel metal layers separated by a dielectric (see Figure 2.1). Also called a parallel-plate capacitor, the MIM structure shares similarities with the field-effect transistor (FET); however, the FET contains an additional semiconductor layer. The MIM structure is particularly useful for determining the capacitance of the transistor gate dielectric and thus the accumulated charge (Q) in the channel of the FET.

Figure 2.1: Schematic diagram of MIM structure.

The dielectric within the MIM structure becomes polarised in the presence of an electric field (E). Polarisation occurs when a voltage-induced electric field forces the 'separation and alignment' of positive and negative charges, i.e. polarisation, within the dielectric. The degree of polarisation depends on the strength of the electric field and the relative permittivity or dielectric constant ( $\varepsilon_r$ ) of the given dielectric

material. The relative permittivity of all dielectric materials (other than vacuum) is  $\varepsilon_r$  > 1 and it is a characteristic material property.

As shown in Figure 2.1 and described by Equation 2.2, the MIM structure is fundamentally a parallel-plate capacitor characterised by the electrode area  $(A = W_p \times L_p)$ , where  $W_p$  and  $L_p$  are the length and width of one electrode. The charge Q is given by the product of the MIM structure capacitance (C) and the externally applied voltage (V), as described by Equation 2.1. The dielectric capacitance per unit area  $(C_{\text{diel}})$  is given by Equation 2.2.

$$Q = CV \tag{2.1}$$

$$C_{\text{diel}} = \frac{C}{A} = \frac{\varepsilon_0 \varepsilon_r}{d} \tag{2.2}$$

where C is the capacitance of the MIM structure, d is the thickness of the dielectric, and  $\varepsilon = \varepsilon_0 \varepsilon_r$  is the permittivity, where  $\varepsilon_0$  is  $8.854 \times 10^{-12} \, \text{F} \cdot \text{m}^{-1}$ .

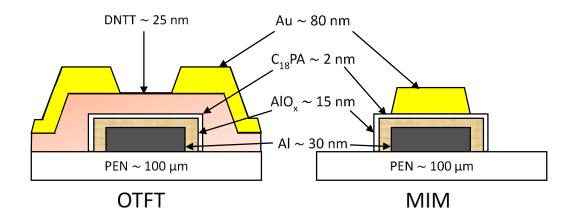

The dielectric capacitance  $C_{\rm diel}$  is an important parameter when designing and evaluating transistors. Higher capacitance leads to higher drain current and transconductance and low-voltage operation. While higher capacitance can be achieved by reducing the thickness of the gate dielectric, very thin inorganic dielectrics lead to increased leakage current. Consequently, MIM structure with bi-layer gate dielectric consisting of aluminium oxide (AlO<sub>x</sub>) and octadecyl phosphonic acid (C<sub>18</sub>PA), with an average area of  $2.45 \times 10^{-3}$  cm<sup>2</sup> and  $C_{\rm diel} = 0.3 \pm 0.029$  µF/cm<sup>2</sup> is used in this thesis.

#### 2.1.2 OTFT structures and materials

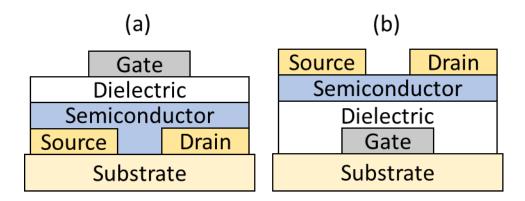

Transistors are multi-layered devices and the OTFT is no exception. Their various structural configurations depend on the arrangement of the transistor layers in relation to the position of the organic semiconductor. As such, OTFTs can take up various forms, two of which are described in this section.

In staggered OTFTs, also referred to as top-gate bottom-contact (TGBC) structure, the placement of the gate electrode sits higher than the organic semiconductor and the source and drain electrodes. The order of deposition from bottom to top is as follows: source/drain electrodes, organic semiconductor, gate dielectric and gate electrode (see Figure 2.2(a)). In inverted-staggered or bottom-gate top-contact (BGTC) configuration the gate electrode is positioned below the semiconductor layer with the source and drain electrodes placed above as shown in Figure 2.2(b). The order of deposition is as follows: gate electrode, gate dielectric, organic semiconductor and source/drain contacts.

It has been shown that the device performance can be greatly affected by the chosen structure/configuration of the OTFT [2.18-2.22]. This thesis adapts the wildly used inverted-staggered BGTC configuration for the following reasons: (a) larger saturation current [2.20] associated with staggered configurations, (b) increased mobility, and (c) reduced source/drain contact resistance [2.19-2.21].

Figure 2.2: OTFT structures: TGBC (a) and BGTC (b).

In addition to the selected OTFT structure, the choice of material for each layer plays a crucial role in OTFT performance. OTFTs have three main groups of materials – metals, insulators, and semiconductors. The most wildly used metals are pliable precious metals such as gold (Au), typically used for their high conductivity and work function that matches the energy levels of the organic semiconductor, although aluminium (Al) and chromium (Cr) are also desirable and cost effective. When choosing the insulating materials, high relative permittivity and extremely low DC conductivity are desirable. Aluminium oxide (AlO<sub>x</sub>) treated with octadecyl phosphonic acid ( $C_{18}PA$ ) has been shown to exhibit reduced gate leakage current and low surface energy [2.23, 2.24]. Other high-k materials such as hafnium oxide (HfO<sub>2</sub>) and titanium oxide (TiO<sub>x</sub>) are also popular choices.

Organic semiconducting materials based on thiophenes exhibit much better air stability when compared to the previously used pentacene [1.1]. Among them the commercially-available, small-molecule, dinaphtho-[2,3-b:2',3'-f]thieno[3,2-b] thiophene (DNTT) shows good reproducibility, low-voltage operation, and high field-

effect mobility and drain current. Consequently, thiophenes remain the popular choice of p-type semiconductor in organic transistors [2.25].

Organic transistors enable incorporation of a wide range of substrates which can provide added functionality in areas typically not suited for conventional inorganic electronics. This attribute has become the driving force behind flexibility, stretchability, and conformability centred around OTFTs. This thesis uses polyethylene naphthalate (PEN) (Optfine PQA1, DuPont Teijin) to achieve mechanically flexible OTFTs for flexible and wearable electronics. PEN is a lightweight, heat resistant polymer with low-permeability to oxygen and water and bending radius up to 1 mm [2.26].

### 2.2 OTFT Operation

The operation of an OTFT can be thought of as a voltage-driven current source [2.27], i.e. the application of a small voltage bias on the gate and drain terminals, with source typically grounded, creates a conduction channel allowing current to flow from drain to source, identified as drain current ( $I_D$ ). The current is proportional to the gate bias, i.e. an increase in gate bias causes an increase in the accumulated charge in the channel which results in increased drain current. However, the regime of operation varies with the drain bias. Specifically speaking, the gate controls the channel formation while the drain and source electrodes act as charge carrier injection and extraction terminals.

OTFTs operate on the principles of charge carrier accumulation at the semiconductor/dielectric interface. When a gate-to-source voltage ( $V_{\rm GS}$ ) greater than

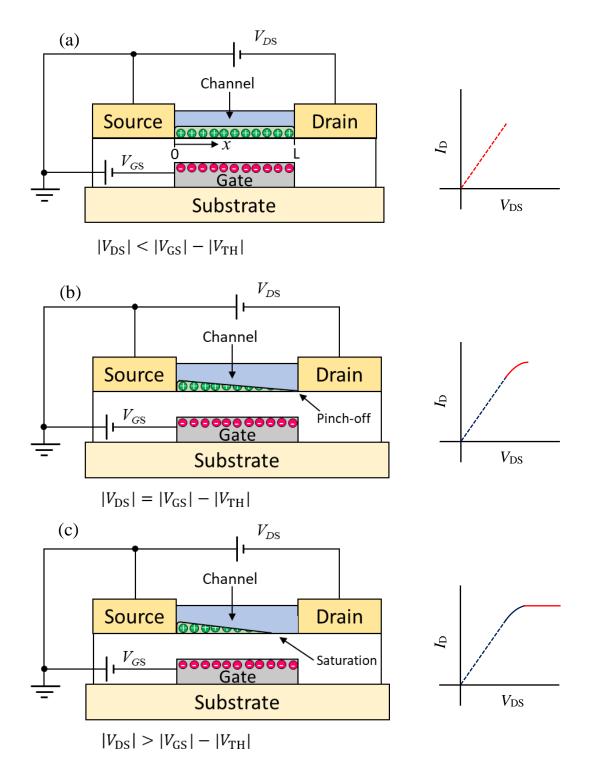

threshold voltage ( $V_{\rm TH}$ ) is applied, where  $V_{\rm TH}$  is the minimum  $V_{\rm GS}$  required to start the charge accumulation process, a conduction channel is formed. The accumulation of charge carriers results in high charge carrier density, thus significantly lowering the resistance between the source and drain and allowing the current to flow. In a p-channel (or n-channel) device a negative (positive)  $V_{\rm GS}$  triggers the accumulations of holes (electrons) and subsequent channel formation. Applying voltage between drain and source ( $V_{\rm DS}$ ) results in the movement of charge carriers and drain current  $I_{\rm D}$  appears. This implies that if  $V_{\rm GS}$  is sufficiently high to form the channel,  $V_{\rm DS}$  is still needed for  $I_{\rm D}$  to flow. Figure 2.3 illustrates the formation of the conduction channel in an OTFT for various voltages applied on the transistor terminals.

During the steady-state operation of the transistor, a small portion of the charges transported along the channel penetrates through the gate dielectric into the gate and leads to an unwanted gate leakage current  $I_G$ . This results from the  $V_{GS}$  voltage that leads to vertical electric field that is much larger than the horizontal electric field resulting from  $V_{DS}$ . Therefore, the gate dielectric has two main functions: (a) to provide a high capacitance per unit area  $C_{\text{diel}}$  and (b) to minimise the gate leakage current  $I_G$ . In an ideal transistor all carriers are transported along the channel, i.e.  $I_G$  is zero and  $I_D$  is maximum. However, in practice, charges become trapped into states in the semiconductor and/or gate dielectric/semiconductor interface resulting in reduction of the accumulated charge density. These trapped charges are accounted for by the threshold voltage  $V_{TH}$  [2.28]. The charge per unit area accumulated in the transistor channel Q is therefore given as

$$Q = C_{\text{diel}}(V_{\text{GS}} - V_{\text{TH}}) \tag{2.3}$$

**Figure 2.3:** OTFT channel formation. Linear regime ( $|V_{DS}| < |V_{GS}| - |V_{TH}|$ ) (a), pinch-off ( $|V_{DS}| = |V_{GS}| - |V_{TH}|$ ) (b), and saturation regime ( $|V_{DS}| > |V_{GS}| - |V_{TH}|$ ) (c).

# 2.2.1 Linear regime ( $|V_{DS}| < |V_{GS}| - |V_{TH}|$ ) and $|V_{GS}| > |V_{TH}|$

An OTFT is known to operate in one of three regimes (linear, saturation and subthreshold) based on the voltages applied on its terminals. The transistor operates in the linear regime, when  $|V_{DS}| < |V_{GS}| - |V_{TH}|$  and  $|V_{GS}| > |V_{TH}|$ . Derivation of the drain current in the linear regime follows.

Point x positioned in the given channel (Figure 2.3(a)) with length L so that  $0 \le x \le L$ , has the potential V(x). Therefore, the charge density Q(x) at point x is expressed as:

$$Q(x) = C_{\text{diel}} [V_{GS} - V_{TH} - V(x)]$$

(2.4)

Using Equation (2.5), the drain current ( $I_D$ ) is given as the product of current density (J) and cross-sectional area (A). At the same time, the current density J is proportional to the product of the electrical conductivity ( $\sigma$ ) and electric field (E(x)) given by Equations (2.5) – (2.7) respectively. Substituting Equations (2.6) and (2.7) into (2.5) leads to (2.8). Considering only the magnitude:

$$J = \sigma E = \frac{I_D}{A} \tag{2.5}$$

$$\sigma = qp\mu \tag{2.6}$$

$$E(x) = -\frac{dV(x)}{dx} \tag{2.7}$$

$$J = qp\mu \frac{dV(x)}{dx} \tag{2.8}$$

Here q is 1.602 x10<sup>-19</sup> C, p is the hole carrier density and  $\mu$  is the hole mobility.  $I_D = J \cdot A$ , where the cross-sectional area A is a product of channel width (W) and channel thickness  $(t_c)$ . Therefore substituting Equation (2.8) into (2.5) and taking  $A = W \cdot t_c$  and  $q \cdot p = Q/t_c$ , where Q is given by Equation (2.4), gives  $I_D$  as:

$$I_{D} = \mu W C_{\text{diel}} [V_{GS} - V_{TH} - V(x)] \frac{dV(x)}{dx}$$

(2.9)

Integrating  $I_D$  over the length of the channel in terms of voltages from source (x = 0 : V(0) = 0) to drain  $(x = L : V(L) = V_{DS})$  for a constant current gives:

$$\int_{0}^{L} I_{D} dx = \mu W C_{\text{diel}} \int_{0}^{V_{DS}} [V_{GS} - V_{TH} - V(x)] dV(x)$$

(2.10)

$$I_D = \mu C_{\text{diel}} \frac{W}{L} \left[ (V_{GS} - V_{TH}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.11)

Very small values of  $V_{\rm DS}$  in the linear regime, i.e.  $|V_{\rm DS}| < |V_{\rm GS}| - |V_{\rm TH}|$ , implies that (2.11) can be simplified to (2.12) since the last term  $\frac{V_{DS}^2}{2}$  is negligible:

$$I_D = \mu C_{\text{diel}} \frac{W}{I} (V_{GS} - V_{TH}) V_{DS}$$

(2.12)

Equation (2.12) shows a linear increase in  $I_D$  with  $V_{DS}$ .  $V_{GS} - V_{TH}$ , known as the overdrive voltage, also affects  $I_D$ .

# 2.2.2 Saturation regime $(|V_{DS}| \ge |V_{GS}| - |V_{TH}|)$ and $|V_{GS}| > |V_{TH}|$

The saturation operation of an OTFT is realised when  $|V_{\rm DS}| \ge |V_{\rm GS}| - |V_{\rm TH}|$  and  $|V_{\rm GS}| > |V_{\rm TH}|$ . Setting  $|V_{\rm DS}| = |V_{\rm GS}| - |V_{\rm TH}|$ , the voltage on the drain at point x = L gives  $V(L) = V_{\rm DS}$ . Thus, the effective potential on the drain channel side becomes  $V_{\rm GS} - V_{\rm TH} - V_{\rm DS}$ , and since  $|V_{\rm DS}| = |V_{\rm GS}| - |V_{\rm TH}|$  the potential is effectively zero on the drain side. Yet the potential at the source side remains  $V_{\rm GS} - V_{\rm TH}$ . Therefore, the estimated Q at the drain end of the channel is zero (see Figure 2.3(b)) and is commonly referred to as pinch-off and marks the start of the saturation regime [2.29]. Substituting  $|V_{\rm DS}| = |V_{\rm GS}| - |V_{\rm TH}|$  into Equation (2.11) gives  $I_{\rm D}$  in the saturation regime as (2.13) which simplifies to (2.14). Setting  $|V_{\rm DS}| > |V_{\rm GS}| - |V_{\rm TH}|$  results in a shift of the pinch-off point towards the source (x < L) with no further increase in  $I_{\rm D}$ .  $I_{\rm D}$  is said to be saturated and is independent of  $V_{\rm DS}$ , as shown in Figure 2.3(c).

$$I_D = \mu C_{\text{diel}} \frac{W}{L} \left[ (V_{GS} - V_{TH})(V_{GS} - V_{TH}) - \frac{(V_{GS} - V_{TH})^2}{2} \right]$$

(2.13)

$$I_D = \mu C_{\text{diel}} \frac{W}{2L} (V_{GS} - V_{TH})^2$$

(2.14)

# 2.2.3 Subthreshold regime $(|V_{GS}| < |V_{TH}|)$

The drain current in a transistor is known to exist even for  $|V_{GS}| < |V_{TH}|$ . This regime of operation below the threshold region is known as the subthreshold regime and is characterised by the so-called subthreshold slope (S). The current in this region of operation is orders of magnitude less than the maximum drain current when  $|V_{GS}| >$

$|V_{\text{TH}}|$  and increases exponentially with  $V_{\text{GS}}$ . Therefore, the subthreshold slope is particularly important in device characterisation where switching speed during transitions between on- and off-states are essential.

#### 2.3 OTFT Parameters

Organic thin-film transistors use various parameters to evaluate their performance. These parameters are highly sensitive to a number of factors including device fabrication procedures, transistor structure, selection of materials and layer thicknesses, and are determined from current-voltage (I-V) measurements, namely the transistor output and transfer characteristics.

The field-effect mobility  $(\mu)$  is considered one of the most significant OTFT parameters. The field-effect mobility is a measure of the average charge carrier drift velocity in the presence of applied electric field. In other words, it represents the movement efficiency of the accumulated charge carriers along the conduction channel. The field-effect mobility is a good method for evaluating the suitability of an OTFT for the required application.

The threshold voltage ( $V_{\rm TH}$ ) is described as the minimum  $V_{\rm GS}$  required to satisfy the condition for the accumulation of charge carriers and the forming of a conduction channel. To ensure proper transistor operation, the threshold voltage needs to be controlled. Low threshold voltages are typically preferred for reducing power consumption and are desirable in low-voltage applications. Under prolonged application of gate bias, this parameter is known to experience a shift in the direction of the applied gate bias, a phenomenon known as threshold voltage shift. The transistor

behaviour becomes altered under such conditions. Additionally, the channel length and thicknesses of the semiconductor and dielectric can influence the threshold voltage.

When biased with voltage higher than the minimum voltage required for accumulation ( $V_{\rm GS} > V_{\rm TH}$ ), an OTFT is said to operate in the on-state. The accumulation of mobile charge carriers leads to a drain current to flow from the drain to the source terminal. In this thesis, the maximum value of the drain current while the transistor operates in saturation is referred to as the on-state drain current ( $I_{\rm ON}$ ). Similarly, the minimum drain current while operating in the off-state ( $V_{\rm GS} < V_{\rm TH}$ ) is referred as the off-state drain current ( $I_{\rm OFF}$ ). The ratio between the on-state and off-state currents is expressed as  $I_{\rm ON}/I_{\rm OFF}$ . High current ratio  $I_{\rm ON}/I_{\rm OFF}$  represent transistors with lower losses in the form of gate leakage current.

The gate leakage current is the unwanted current flowing from the channel through the dielectric into the gate. Ideally, the gate leakage current should be zero; however, values up to 1 nA can be observed. The gate leakage current has been shown to be controlled by the thickness of the dielectric and dielectric constant, annealing, overlap between the gate-source and gate-drain electrodes and gate/drain bias [2.30-2.32].

Transconductance  $(g_m)$  is another important transistor parameter. The transconductance describes transistor's efficiency relating the output to the input. It is defined as the ratio of change in the output  $I_D$  due to a change in the input  $V_{GS}$ .

When metals and semiconductors are joined together, the interface connecting the two materials is subjected to a 'resistance' generally termed as the contact resistance ( $R_c$ ). The contact resistance is the result of the energy mismatch between the