University of Strathclyde

# Large Step Down Voltage Converters for Desalination

Department of Electronic and Electrical Engineering

Richard Charles Pollock August, 2019 This thesis is the result of author's original research. It has been composed by the author and has not been previously submitted for examination which has led to the award of a degree.

The copyright of the thesis belongs to the author under the terms of the United Kingdom Copyright Acts as qualified by the University of Strathclyde Regulation 3.50. Due acknowledgement must always be made of the use of any material contained in, or derived from, this thesis.

### Acknowledgement

I would like to thank Prof. Barry W. Williams and Dr. Neville McNeill for their continuous guidance, advice and knowledge sharing, without whom this work would not have been possible.

I also would like to thank Dr. Derrick Holliday for his support and advice throughout my PhD study.

Finally, a sincere thankfulness goes to my father, mother, sisters, brother and Abigail for their support, encouragement, and endurance through this period.

## **Table of Contents**

| Acknov    | wledgement                                               |    |

|-----------|----------------------------------------------------------|----|

| Table o   | of Contents                                              |    |

| Abstrac   | ct                                                       |    |

| List of S | Symbols                                                  | i  |

| List of A | Abbreviations                                            | ii |

| Chapte    | er 1 Introduction                                        | 1  |

| 1.1       | Water Desalination Background                            | 1  |

| 1.2       | Energy Economics of Desalination                         | 3  |

| 1.3       | Methods of Desalination                                  | 4  |

| 1.4       | Summary of Techniques                                    | 7  |

| 1.5       | Requirements of Electrochemical Methods of Desalination  | 7  |

| 1.6       | Summary                                                  | 11 |

| 1.7       | Converter Parameter Specification                        | 11 |

| 1.8       | Thesis Structure                                         | 12 |

| Chapte    | er 2 DC-DC Converters for Voltage Step-Down Applications | 14 |

| 2.1       | Circuit Design Scope                                     | 14 |

| 2.2       | DC-DC Converters                                         | 14 |

| 2.2       | 2.1 Comparison and Simulation of Converters              | 15 |

| 2.2       | 2.2 Buck Converter                                       | 15 |

| 2.2       | 2.3 Buck-Boost Converter                                 | 17 |

| 2.2       | 2.4 Flyback Converter                                    | 18 |

| 2.2       | 2.5 Cuk Converter                                        | 19 |

| 2.2       | 2.6 Dual Active Bridge Converter                         | 21 |

| 2.3       | Tapped Inductor Topologies                               | 21 |

| 2.3       | 3.1 Coupled-Inductor Buck Converter                      | 24 |

| 2.4       | The Need for Switch Protection                           | 26 |

| 2.4       | 4.1 Transformer Action                                   | 26 |

| 2.4       | 4.2 Leakage Inductance                                   | 29 |

| 2.4       | 4.3 Solutions                                            | 30 |

|         | arge Step-Down Voltage Ratio Coupled-Inductor Buck Topology Circuit – snubb<br>nd clamping circuits | oer<br>30   |

|---------|-----------------------------------------------------------------------------------------------------|-------------|

| 2.5.1   | Ultrahigh Step-Down Converter [50]                                                                  | 31          |

| 2.5.2   | High Voltage Tapped-inductor Buck Converter – shunt capacitors                                      | 34          |

| 2.5.3   | Tapped-Inductor Buck Converter for High-Step-Down Ratio dc-dc Convers                               | ion35       |

| 2.5.4   | DCDL Coupled-Inductor Buck                                                                          | 39          |

| 2.5.5   | RC Snubber                                                                                          | 41          |

| 2.5.6   | RCD Snubber                                                                                         | 43          |

| 2.5.7   | RCD Clamp (Pre-charged)                                                                             | 44          |

| 2.5.8   | ZRC Snubber                                                                                         | 47          |

| 2.6     | Summary                                                                                             | 51          |

| Chapter | 3 Flyback and Buck Circuit Alternatives for High Step-Down Voltage Ra                               | tios        |

|         |                                                                                                     | 53          |

| 3.1     | Comparison of Buck Circuits                                                                         | 53          |

| 3.2     | Equations of Buck Type Circuits                                                                     | 56          |

| 3.2.1   | Flyback Converter                                                                                   | 56          |

| 3.2.2   | Coupled-Inductor Buck Converter                                                                     | 57          |

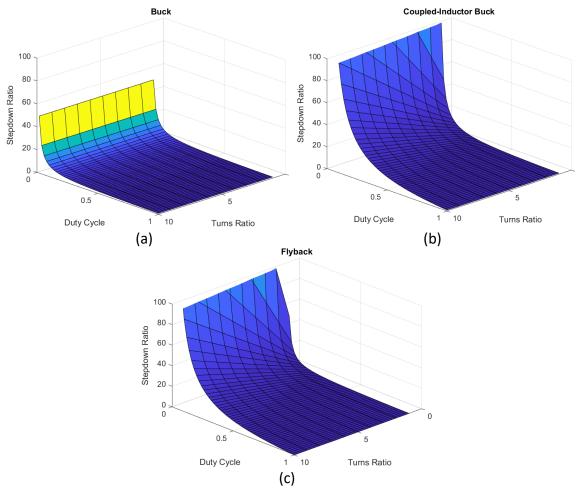

| 3.2.3   | Comparison of Voltage Transfer Ratios Against Main Switch Duty Cycle                                | 58          |

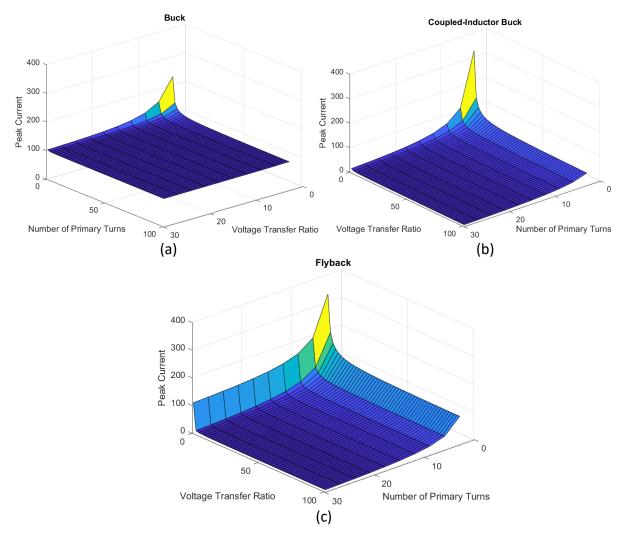

| 3.2.4   | Peak Current in the Buck Converter                                                                  | 60          |

| 3.2.5   | Peak Current in the Coupled-Inductor Buck Converter                                                 | 61          |

| 3.2.6   | Peak Current in the Flyback Converter                                                               | 62          |

| 3.3     | Benefit of Higher Duty Cycle Operation                                                              | 63          |

| 3.3.1   | Switch and Diode Voltage Ratings                                                                    | 65          |

| 3.4     | Magnetic Component Considerations                                                                   | 66          |

| 3.4.1   | Magnetic Core Comparison                                                                            | 66          |

| 3.4.2   | Leakage Inductance Considerations                                                                   | 67          |

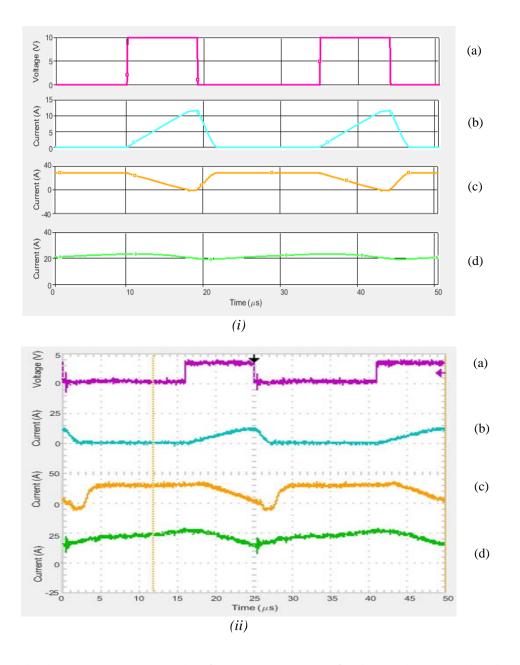

| 3.5     | Simulation supported Experimental Comparison of the Flyback and Coupled-Ind Buck Converters         | uctor<br>67 |

| 3.5.1   | Experimental and Simulated Waveforms                                                                | 70          |

| 3.5.2   | Comparison of Flyback and Coupled-Inductor Buck Converters                                          | 74          |

| 3.6     | Summary                                                                                             | 77          |

| Chapter | 4 Active Switch Protection Circuits for Large Step-Down Voltage<br>Coupled-Inductor Converters      | 79          |

| 4.1     | Novel Fly-forward Regenerative Snubber                                                              | 79          |

| 4.1.1   | Regenerative snubber Simulation                                                                     | 81          |

| 4 1     | 2     | Construction Coloritoria                                           |          |

|---------|-------|--------------------------------------------------------------------|----------|

| 4.1.2   |       | Coupled-Inductor Calculations                                      | 82<br>85 |

| 4.1.3   |       | Regenerative Snubber Experimentation                               |          |

|         |       | Snubber Testing                                                    | 86       |

| 4.1.    |       | Regenerative Snubber Summary                                       | 89       |

| 4.2     |       | k-boost Clamp Snubber                                              | 90       |

| 4.2.    |       | Investigating the Effect of the Clamping Voltage                   | 94       |

| 4.2.    | .2    | Practical Single-Ended Converter                                   | 95       |

| 4.2.    | .3    | Data Analysis                                                      | 98       |

| 4.3     | Sun   | nmary                                                              | 100      |

| Chapter | : 5   | Asymmetrical Half-Bridge Coupled-Inductor Buck Converter           | 102      |

| 5.1     | Asy   | mmetrical Half-Bridge Coupled-Inductor Converter                   | 102      |

| 5.1.    | .1    | Simulation of the Asymmetrical Half-Bridge                         | 103      |

| 5.1.    | .2    | Experimental Results                                               | 104      |

| 5.1.    | .3    | Asymmetrical Half-Bridge Testing                                   | 105      |

| 5.1.    | .4    | Results Comparison                                                 | 107      |

| 5.2     | Sun   | nmary                                                              | 109      |

| Chapter | : 6   | Experimental Results – Asymmetrical Half-bridge Flyback            | 110      |

| 6.1     | Asy   | mmetrical Half-bridge Flyback Circuit Topology                     | 110      |

| 6.2     | Imp   | lementation of Flyback Converter                                   | 112      |

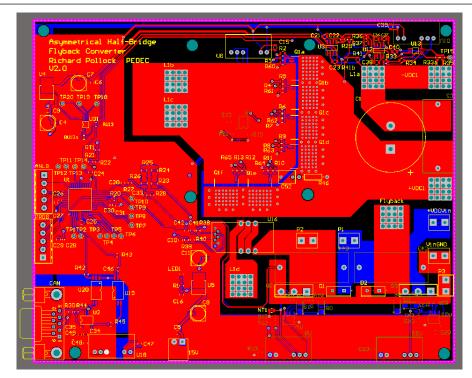

| 6.2.    | .1    | Hardware Design                                                    | 113      |

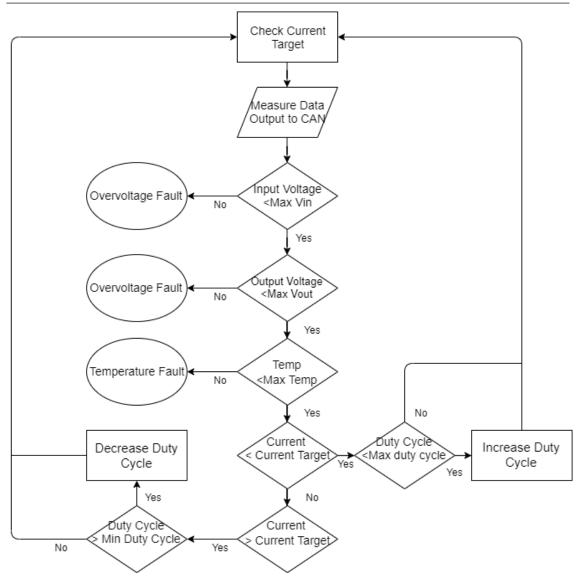

| 6.2.    | .2    | Software Design                                                    | 116      |

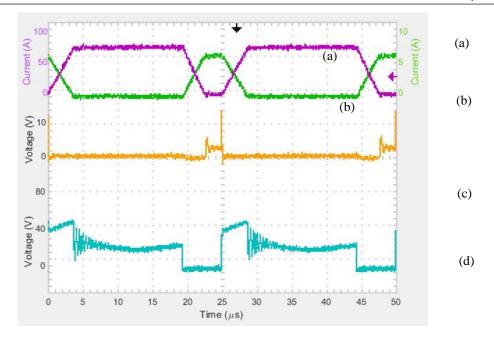

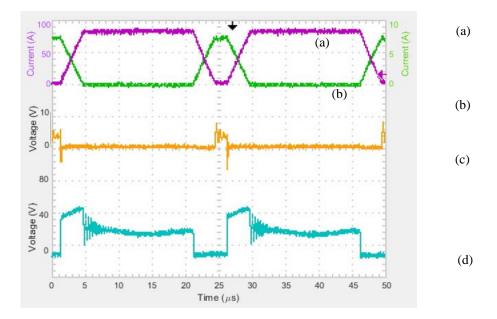

| 6.3     | Initi | al Testing                                                         | 117      |

| 6.3.    | 1     | Closed Loop Operation                                              | 119      |

| 6.3.    | .2    | Maximum Power Operation - Short Circuit Tests                      | 119      |

| 6.4     | Test  | tRigs                                                              | 123      |

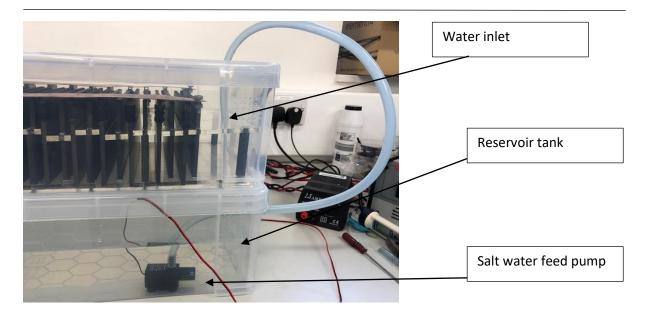

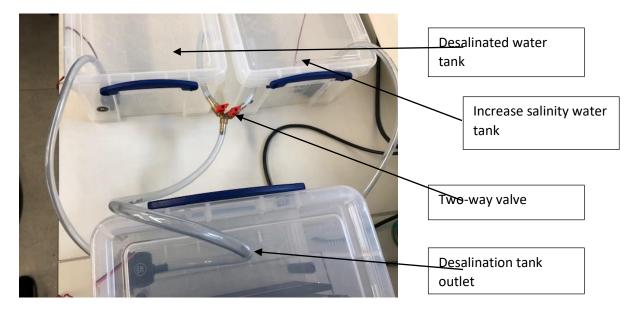

| 6.4.    | 1     | Desalination Test Rig                                              | 123      |

| 6.4.    | .2    | Super Capacitor Test Rig                                           | 123      |

| 6.4.    | .3    | Super Capacitor Charging with Asymmetrical Half-Bridge Flyback Con | verter   |

|         |       |                                                                    | 124      |

| 6.4.    | .4    | 340V Input Voltage                                                 | 129      |

| 6.5     | Sun   | nmary                                                              | 133      |

| Chapter | 7     | Conclusion                                                         | 134      |

| 7.1     | Sun   | nmary and General Conclusions                                      | 134      |

| 7.1.    | .1    | Existing literature                                                | 135      |

|         |       |                                                                    |          |

| 7.1.2 Experimental Assessment                   | 137 |

|-------------------------------------------------|-----|

| 7.2 Author's Contribution                       | 138 |

| 7.3 Future Research                             | 139 |

| References                                      | 140 |

| Appendix A PCB Control Software                 | 146 |

| Converter Initialisation                        | 146 |

| Current Control Loop                            | 147 |

| Voltage, Current and Temperature Fault Function | 148 |

| Appendix B Desalination Cell Design             | 149 |

| Appendix C List of Figures and Tables           | 152 |

| List of Figures                                 | 152 |

| Appendix Figures                                | 158 |

| List of Tables                                  | 159 |

| Appendix D List of Author's Publications        | 160 |

| Conference Papers                               | 160 |

|                                                 |     |

### Abstract

One percent of the world's drinking water is currently desalinated, and this will have to increase to 14% by 2025. Desalination is energy intensive, having significant commercial and ecological implications.

One of the most promising methods of desalination is capacitive deionisation which only uses 1kWh/m<sup>3</sup> but requires a voltage of less than 1.8V at currents of up to 1000A

This thesis produced hardware capable of creating 550A at a voltage of 1.8V, giving over a 1kW power rating, with an input voltage of 340V dc. The converter designed was a bidirectional asymmetrical half-bridge flyback converter allowing for isolation at these high step down ratios. The converter was used to charge a bank of 17,000F supercapacitors from 0V to 1.8V, with an initial charging step down ratio in excess of 340:1 falling to 190:1 as the load charged.

A novel Asymmetrical Half-Bridge Coupled-Inductor Buck converter is presented as the ideal solution for large step-down ratios with analysis comparing the ability to efficiently step down a voltage with other common converters, the buck and flyback converters.

A comparison between a single-ended coupled-inductor buck converter employing a buck-boost voltage clamp and the novel asymmetrical half-bridge coupled-inductor buck converter circuit shows that the asymmetrical half-bridge converter is a more efficient circuit as leakage energy is recovered; the switch voltages are clamped to within the dc voltage rating of the bridge and the control strategy is simple.

Passive and active snubbers are reviewed for efficiency, switch ratings and management of the effects of leakage inductance and compared against the novel designs presented.

In the desalination application isolation is required so the flyback circuit is used. An isolated three switch bidirectional converter is constructed using silicon carbide MOSFETs and diodes switching at 40kHz. The converter uses novel current measuring techniques, an on-board microprocessor and closed loop control designed into the final DC-DC converter.

# List of Symbols

| Symbol                    | Term                                                 | Unit  |

|---------------------------|------------------------------------------------------|-------|

| А                         | Area                                                 | $m^2$ |

| $\mathbf{B}_{\mathbf{s}}$ | Magnetic Flux Density                                | Т     |

| С                         | Capacitance                                          | F     |

| δ                         | Duty Cycle                                           |       |

| $\delta_b$                | Buck Duty Cycle                                      |       |

| $\delta_{ci}$             | Coupled-Inductor Buck converter Duty Cycle           |       |

| $\delta_{\rm fb}$         | Flyback Duty Cycle                                   |       |

| f                         | Frequency                                            | Hz    |

| Н                         | Applied Magnetic Field                               | A/m   |

| Iload                     | Load Current                                         | А     |

| $I_{max}$                 | Maximum Current                                      | А     |

| $\mathbf{I}_{min}$        | Minimum Current                                      | А     |

| $I_1$                     | Current flowing in inductor L1                       | А     |

| $I_2$                     | Current flowing in inductor L2                       | А     |

| 1                         | Length                                               | m     |

| L                         | Inductance                                           | Н     |

| L <sub>t</sub>            | Total inductance of coupled inductor                 | Н     |

| $\text{MMF}_{\text{ci}}$  | Magneto Motive Force Coupled-Inductor Buck Converter | А     |

| $MMF_{fb} \\$             | Magneto Motive Force Flyback Converter               | А     |

| $\mu_0$                   | Permeability of a Vacuum                             | H/m   |

| $\mu_r$                   | Relative Permeability                                | H/m   |

| Ν                         | Number of inductor turns                             |       |

| $N_{I}$                   | Number of turns in inductor L1                       |       |

| $N_2$                     | Number of turns in inductor L2                       |       |

| n                         | Number of transformer turns                          |       |

| SDR                       | Step Down Ratio                                      |       |

| $T_s$                     | Switching Time Period                                | S     |

| R                         | Electrical Resistance                                | Ω     |

| $\mathbf{V}_{in}$         | Input Voltage                                        | V     |

| $V_{\text{out}}$          | Output Voltage                                       | V     |

# List of Abbreviations

| Abbreviation | Term                                              |  |

|--------------|---------------------------------------------------|--|

| AC           | Alternating Current                               |  |

| ССМ          | Continuous Conduction Mode                        |  |

| CDI          | Capacitive Deionisation                           |  |

| DC           | Direct Current                                    |  |

| DCDL         | Diode Capacitor Diode Inductor                    |  |

| DCM          | Discontinuous Conduction Mode                     |  |

| EMI          | Electromagnetic Interference                      |  |

| IGBT         | Insulated Gate Bipolar Transistor                 |  |

| LED          | Light Emitting Diode                              |  |

| MOSFET       | Metal Oxide Semiconductor Field Effect Transistor |  |

| PCB          | Printed Circuit Board                             |  |

| PI           | Proportional Integral                             |  |

| PID          | Proportional Integral Derivative                  |  |

| PWM          | Pulse Width Modulation                            |  |

| RCD          | Resistor Capacitor Diode                          |  |

| RMS          | Root Mean Square                                  |  |

| SiC          | Silicon Carbide                                   |  |

| SMPS         | Switched Mode Power Supply                        |  |

| ZRC          | Zener Resistor Capacitor                          |  |

|              |                                                   |  |

### Chapter 1 Introduction

This thesis presents comparative analysis of DC-DC converters with large step-down voltage ratios. This research analysis includes detailed evaluation of the potential use of large step-down ratio converters in water desalination. There are many single stage DC-DC converter topologies, whence analysis of both isolated and non-isolated versions are presented. Also, the main limitation of large step-down DC-DC converters, namely switch over-voltage due to leakage inductance, is evaluated.

### **1.1 Water Desalination Background**

This research investigates power electronics' suitability for application in water desalination (process of salt removal) through *Capacitive Deionisation* [1]. Water scarcity is thought to be one of the biggest challenges facing our generation. About 4 billion people, representing nearly two-thirds of the world population, experience severe water scarcity during at least one month of the year and this could increase to some 4.8-5.7 billion people in 2050. [2], [3]. Turning sea or waste water into drinking water is vital for continued life, growth and prosperity globally. Fresh water is also a fundamental resource for non-anthropological applications, steam turbines in power stations and farming irrigation for example, therefore for arid or semi-arid geographical regions, desalination is an evident solution. In such regions of low precipitation, a high UV Index is common. When coupled with investment in solar driven power, an electrical method of desalination holds great potential. This thesis will outline said process and a viable circuit topology for the application.

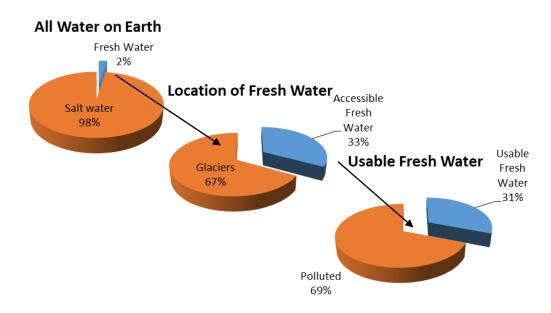

70% of the world's surface is covered by water, however only 2% of this water is fresh water and of this, only one third is readily accessible – with the inclusion of polluted water, this number again falls. Perhaps the fact that we should be teaching future generations is "how much of the world is made up of usable drinking water?" and its startling response, 0.205%, Fig. 1.1.

Fig. 1.1 Percentage of fresh water on Earth

Global water consumption is rising annually by about 1% [4], however the amount of readily available freshwater is not rising. Concurrently, an increasing world population is resulting in a mounting demand for fresh water.

Agriculture accounts for ~70% of global freshwater usage [5] and with an unyielding demand. According to [6], the Earth's population is predicted to increase by 1.5 billion to a global population of 9.7 billion by 2050 [7], with this, a predicted increase in food demand of 70% by 2050.

Remarkably, the second largest demand on our fresh water resource is generated by the electricity sector [8]. An estimated 1.1 billion [9] people at present, do not have access to electricity. An estimated increase in global energy consumption is in the region of ~49% from 2007 to 2035 with current thermal power plants and their water intensive requirements account for 78% of world electricity production. [10]–[12] As such, if current modes of electricity production are maintained, the volume of fresh water required will increase by 11.2%.[13] The culmination of these factors are leading to a global fresh water shortage and unless a financially viable and environmentally sustainable solution can be found, could prove cataclysmic .

One potential solution to fresh water shortage is the exploitation of wastewater or seawater. Desalination is the process of removing salt from saline solutions. Currently one percent of the world's drinking water is desalinated, and this is expected to increase to 14% by 2025. [4] However, desalination inherently is energy intensive, posing significant commercial and ecologic implications.

### **1.2 Energy Economics of Desalination**

Various methods of desalination are currently performed to deionise and thus remove salt from a solution.

The primary variants in water desalination regarding economics are sea water desalination and brackish water desalination. The key difference is the concentration of salt in the solutions. Sea water is around 35,000 ppm whereas brackish water is ~4000 ppm (variable depending on the sample's source). [14]

The minimum energy required to separate salt ions from a solution is about 1.1kWhm<sup>-3</sup> for average sea water samples and 0.12 kWhm<sup>-3</sup> for typical brackish water. [14] Energy versus ppm is a linear relationship however achieving these values is complex and expensive. [15] [16]

The significance of dissimilar salt concentration lies in the effect on desalination process efficiencies. However, processes that desalinate via heat are almost independent of concentration as this functions to remove the water from solution (via evaporation) as opposed to salt, therefore the energy is close to a constant. There is some variation in boiling point for different solution concentrations but this energy increase is minimal. As such when it comes to efficiencies, thermal methods can be far more viable for seawater desalination.

Other methods including reverse osmosis and electrochemical methods are more dependent on salt concentration. There is still scope for them to compete with thermal methods in sea water desalination and their efficiencies can be far better than the thermal techniques, particularly for brackish water desalination.

### **1.3** Methods of Desalination

There are three fundamental processes used in water desalination: thermal, pressure, and electrical. [17]

The thermal process, distillation, is perhaps the most widespread application for seawater at present. *Multistage flash distillation* is the evaporation and consequent condensation of a liquid. When applied to salt water, the condensed fluid is free from salt.

Pressure driven salt removal via *reverse osmosis* is a cost-effective desalination technique applicable to both sea and brackish water whereby water is pushed through a semipermeable membrane partitioning salt molecules and pure water on opposite membrane sides.

Electrical desalination involves electric field generation and the use of a semi-permeable membrane. When electric voltage is applied to a solution an electric field is produced, this causes ions present to disassociate and removed using a semi-permeable membrane.

The energy used in both the electrical and pressure process depends on the initial concentration of salt with 90% of current desalination plants employing reverse osmosis or multistage flash distillation. Both methods are highly energy-intensive but at present, shortage of drinking water outweighs this energy expenditure. Further methods include electrodialysis, multiple effect distillation, mechanical vapour compression, and capacitive deionisation.

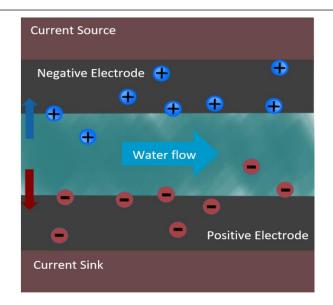

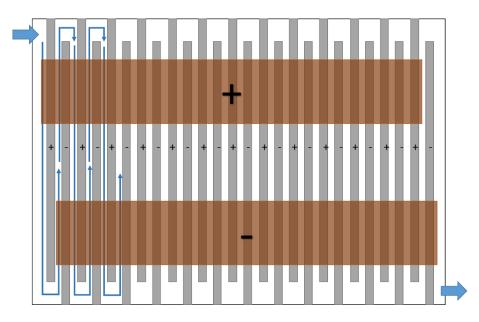

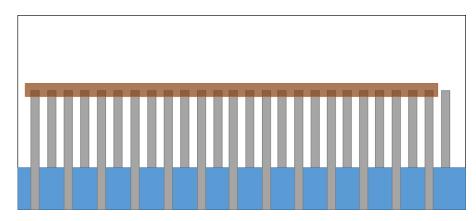

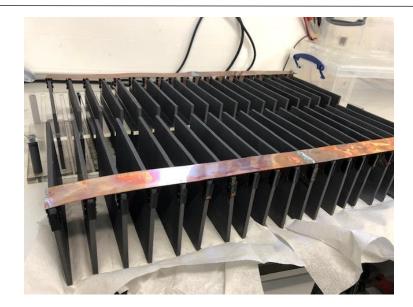

*Capacitive deionisation* [1], [18], [19] is an auxiliary electrical desalination method comprised of two stages: the adsorption stage, where desalination of feed water occurs, and the desorption stage, where the electrons are recuperated. CDI applies an electrical potential over parallel anodic and cathodic electrodes, commonly porous carbon, to form an electrolytic cell. In salt solution, the presence of sodium and chloride ions (Na<sup>+</sup> and Cl<sup>-</sup> respectively) enhances water conductivity and reduces the solution's resistance to electron flow. Anions, negatively charged chlorine ions, are removed from solution via assimilation onto the positively charged electrode. A simultaneous movement of positively charged sodium cations, supplement the cathode; the negatively polarised electrode. As the ions undergo electrosorption, this process renders the salt-water solution salt free, Fig. 1.2.

Fig. 1.2 Capacitive deionisation electrode cross section

The desorption phase is initiated when the electrodes reach saturation point and the electrodes are discharged. When discharging the cell, the ions migrate back into the water stream increasing the waste solution salinity. Cell discharging can recover up to 60% of the initial energy used to remove the ions. The highly saline water stream created is then returned to the sea as waste water. The process can be likened to that of charging and discharging a super capacitor due to the linear charge/discharge cycles and process repeatability.

Presently, the predominant use for CDI is desalination of low to moderate salt concentration (~10gL<sup>-1</sup>) water (brackish). [20]–[22] This owes to CDI efficiently removing salt ions from water in contrast to other methods which remove water from the saline solution. In CDI, the energy consumption per unit volume of salt water is proportionate to the amount of removed salt. This contrasts with the previously presented desalination methods, such as RO, where the energy use and water volume feed water is less proportional.

Membrane CDI (MCDI) is a variant of CDI which involves the insertion of ion-exchange membranes in front of the electrodes. This adjustment enhances the CDI unit by numerous means: MCDI requires less energy input than CDI [1], and the presence of a membrane ensures that ions remain in the electrode pores. This concurrently results in enhanced

migration of the remaining ions in solution through the membrane, and overall increased salt-adsorption efficiency, Fig. 1.3.

| Current Source       |                    |

|----------------------|--------------------|

| NegativeElectrode  🕂 | ÷                  |

| + + Catic            | +<br>on membrane   |

| +                    |                    |

| Water flow           | •                  |

| Anior                | membrane           |

|                      | Positive Electrode |

|                      | Positive Electrode |

| Current Sink         |                    |

Fig. 1.3 Membrane Capacitive Deionisation cross section

For elevated CDI performance, electrode material selection is important and is undergoing continuing research. The most elementary electrode material is porous carbon. In deionisation, high electrosorption capacity is paramount - this is achieved via optimal transfer of ions through a highly conductive medium. To increase percentage time of desalination against time required to reset the cell, the pore size distribution must consist of large pores with a high specific surface area. Also, through chemical stability, the porous material used should have low degeneracy rates in the functioning voltage range.

Recently hydrogels, known as Aerogels and Xerogels, have gained interest [23]–[25]. The gels have extremely low density and electrical resistivity, and are consequently of interest within optimising electrode functionality research.

### **1.4 Summary of Techniques**

| Process                       | Power consumption          | Water Impurity     |

|-------------------------------|----------------------------|--------------------|

| Reverse Osmosis               | 2.9–3.7 kWhm <sup>-3</sup> | Sea/Brackish Water |

| Multistage Flash Distillation | 13.5 kWhm <sup>-3</sup>    | Sea Water          |

| Electrodialysis               | 1.7 kWhm <sup>-3</sup>     | Brackish Water     |

| Multiple-Effect Distillation  | 6 kWhm <sup>-3</sup>       | Sea Water          |

| Mechanical Vapour Compression | 6 kWhm <sup>-3</sup>       | Sea Water          |

| Capacitive Deionisation       | 1 kWhm <sup>-3</sup>       | Brackish Water     |

Table 1.1 Summary of desalination techniques.

The electrochemical processes, *capacitive deionisation* (CDI) and *electrodialysis*, are areas out with this project that require most investigation; with both methods presenting energy saving potential in contrast to current methods of desalination. CDI is particularly attractive. By recouping the energy from the separated ions, the net energy required for the process is reduced to a value correlated with system losses, so could be adopted for affordable desalination. Both electrochemical process requires further filtration to remove bacteria and potentially any pollutants as the process only removes ionic salts from the water.

### **1.5** Requirements of Electrochemical Methods of Desalination

Both discussed electrochemical water desalination processes, CDI and EDI, theoretically operate at under 1.23V DC (Nernst Voltage). The Nernst Voltage is the voltage at which the hydrogen bonds between H and O break in a water molecule (H<sub>2</sub>O); above this point, electrolysis occurs and requires surplus energy. However, this critical voltage must be applied directly across the water molecule, and to mitigate the voltage drop effects of impurities and resistance of the solution, voltages between 1.23 to 1.8V DC are commonly used.

The methods to produce the input of 1.8V are important. A simple configuration would be an in-series cell arrangement to summate smaller voltages to achieve a large input voltage. The cells have capacitive properties as they are effectively charge ions being stored on parallel electrodes so cell balancing circuits must be fitted to ensure even distribution of current and voltage.

The difficulty of creating a 1.8V supply voltage depends upon the voltage input, as the power source for the desalination process dictates the electronics required for the given application, be it AC or DC.

The energy required for desalination can be as low as 1kWhm<sup>-3</sup> for 4,000ppm. The voltage required for CDI must be less than 1.8V to stop hydrogenisation (formation of hydrochloric acid and sodium hydroxide). This low voltage present challenges for the electronics to achieve the required power levels into the electrodes; high currents are required potentially in excess of 1000A per cell [19].

The three most probable inputs - are: three phase AC supply, single phase AC supply, or a solar panel array.

*A three-phase AC supply*: Three sinusoidal voltages at (conventionally) 50Hz and 120° out of phase. Such supply requires rectification (conversion from AC to DC) to provide a 600V DC input. As any input must be reduced, a 600V input is the weakest aspect for the application as the voltage step-down ratio has a maximum of 600:1. Such a large step down would normally create high peak currents or large over-voltages due to leakage inductance of a wound magnetic component. The use of a three-phase step-down transformer adds cost, volume, and reduced efficiency, but does afford isolation.

*The single-phase AC supply:* would also need to be rectified from 240V AC to 340V DC. This is a lesser, and consequently easier step-down ratio. However, the single phase supply is primarily reserved for domestic or small-scale plant use, therefore for the vast quantities involved in water desalination its preference is diminished.

A *solar panel array* of photovoltaic cells exhibits potential, primarily areas where desalination is necessary; low precipitation rate is associated with areas that have a high UV index. A solar panel is comprised of photovoltaic cells which utilise UV light energy to produce DC voltage. This voltage output is variable but 48V is a widely used standard. A 48V input voltage battery would necessitate a smaller step down ratio, however this

generates a higher current draw from the supply than a larger step down ratio would for the same output current. Current draw is critical in battery supplies as high current over prolonged time periods reduces the lifecycle of a battery bank therefore this aspect should be considered in input selection.

The primary argument for a solar panel array is its environmental sustainability. Firstly, the source of electrical supply has a comparatively low carbon footprint. To ensure maximal symbiosis, the panels could be installed on the roof of the desalination facility, reducing the travel of electricity and subsequent losses of energy, as well as the installation foot print.

Following comparative analysis, the 600V input circuit topology was deemed to be of most value to investigate due to its complexity. So if such technology could function from 600V, the resultant equipment could cater for lower voltage levels.

When approaching the problem of capacitive deionisation, both small-scale and largescale industrial plants must be considered to fashion the most efficient design of both desalination cells and their electronics.

In water desalination, cells can be in both parallel or series physical arrangement. In series, water flows from one cell into the next and in parallel, water is forced through one cell or another but not both. Connecting the cells in series allows for greater ion removal from the water stream at a constant flow rate. A parallel cell arrangement allows for a greater volume of water to be desalinated but does not change the amount of salt removed from a given volume of water as this is proportional to the current flowing into the cells.

As well as the physical layout, cells can be electrically connected either in series, parallel, or under individual control.

In a series array, the voltage across the cells is summated and the operating output voltage required can be increased to reduce the step-down ratio of the converter. However, when electrically connected in series, the characteristic of each cell will determine the amount of voltage each cell experiences and imbalanced energy distribution can result.

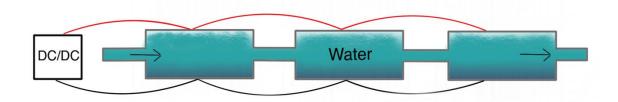

In parallel electrical connection, voltages are not summated, so the 1.8V input voltage requirement is fixed. This presents the benefit that one DC-DC converter can be used for all cells connected in parallel with no additional electronics, with the consequences of

ease of control. When the cell layout is series in physicality and parallel electrically Fig. 1.4, the amount of salt removed can be calculated using the total current from the single converter.

Fig. 1.4 Water desalination cells arranged in series electrically connected in parallel

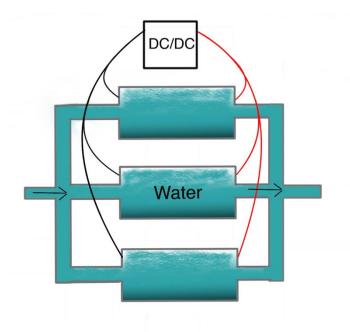

For increased flow rate additional sets of cells can be physically added in parallel to the previous arrangement Fig. 1.5. This gives more area for the water to flow over and if the electrical current supply is doubled then the rate of water desalinated per time will double.

Fig. 1.5 Water desalination cells connected in parallel, electrically connected in parallel

For both layouts, if the currents became too large an additional DC-DC converter could be used to control this additional water stream and effectively create a stand-alone desalination unit. This would also allow for greater control in the case where the water flowing through each unit begins to differ. Aside from cell layout and electronics, the energy path must also be considered. Energy is converted from the input voltage down to the required 1.8V in all arrangements. This can be achieved via a single, high-powered circuit or separately within each individual circuit responsible for cell block control. Once the cell is held at the correct voltage level desalination then occurs.

However, a major component of the electrosorption process is the 'flushing' or discharging of the electrodes. This discharge can be achieved in two ways: energy is either transferred from one discharging cell into a charging cell with any loss replenished by the grid or the energy is stepped back up to the input voltage to be absorbed by the supply.

This research considers multiple series-connected cells (as in Fig. 1.4) under singular circuit control utilising grid charging-discharging. Such circuit design is entirely modular, for a given increase in volume, flowrate and concentration, an additional module (block of cells and circuit) is connected in parallel. These can all operate individually or as a combined system.

### 1.6 Summary

Fresh water paucity is a significant issue facing our generation. Water desalination is a viable solution to this problem. Following evaluation of existing methods of water desalination, it is evident that capacitive deionisation offers promise and further investigation is of consequence. As this is an electrochemical method, operational efficiency relies upon efficient, reliable electronics. In the most extreme scenario, a water sample may require a capacitive deionisation circuit to function with a 600:1 step-down ratio. Electrically, a voltage less than 1.8V is required and large currents in excess of 500A allow for a higher rate of desalination. The input voltage is likely to be either 600V DC from three phase AC rectified or 340V DC (single phase AC rectified). Chapter 2 will consider various DC-DC converters with such a step-down capability.

### **1.7** Converter Parameter Specification

Throughout the thesis the overarching electrical aim is to step down a high voltage to 1.8V. Initially 600V dc is the target input and as such is investigated as this is seen as the worst case scenario where a three phase AC supply is used. Throughout the thesis however this target is altered for various tests and experiments due to the hardware capabilities of the initial prototypes.

In Chapter 3 a step down ratio of smaller than 100:1 is investigated as this was noted to be the most significant point when comparing the three converters discussed. Above this point no significant change is seen compared to the results of 100:1.

In Chapter 4 an input voltage of 150V is used for the hardware testing and simulations as this is the maximum possible with the given hardware due to large leakage inductance. To achieve a circuit higher power through put, an output voltage of both 1.8V and later 2.6V are tested as the 2.6V allows for a higher current draw and thus higher power testing.

Chapter 5 again uses the same 150V input voltage but achieved a higher power through put to step down to the 1.8V.

Chapter 6 presents the final experimental setup which is designed to extend the power and step down ratio as high as possible. A 340V dc input voltage is reached, with a 550A output. This demonstrates a step down of 340V-1.8V dc which is seen as a significant step. Future iterations should allow for the full 600V-1.8V dc set out in the initial scope.

### **1.8 Thesis Structure**

This thesis includes an introduction to water desalination, comparative review of DC-DC converter topologies, switch voltage protection circuits and experimental assessment of a high current output DC-DC converter tested on a supercapacitive load, with the aim of determining the most appropriate circuit for capacitive deionisation.

- **Chapter 1** Outlines the contained research of the thesis and its structure. And provides a brief introduction to, and methods of, water desalination, and an overview of the electrical requirements for the application.

- Chapter 2 reviews DC-DC step-down converters from literature. Cursory analysis of each circuit is presented to determine the most befitting circuits for

application to water desalination. The chapter contains a review of passive snubber circuits suitable for protecting a switch against over-voltage.

- Chapter 3 presents a detailed comparison of the most viable circuit configurations (buck converter, coupled-inductor buck converter and flyback converter) for large voltage step-down ratio application. Initially, circuit duty cycles and consequential peak currents are compared, followed by examination of circuit performance at various turns ratios.

- **Chapter 4** investigates active snubbers; their efficiency enhancement, control benefits and ability to suppress the adverse effects of leakage inductance inherent with large step-down magnetically coupled converters.

- **Chapter 5** introduces the asymmetrical half-bridge coupled-inductor buck converter; a novel converter topology that offers an aside solution to leakage inductance with cost and potential efficiency savings over active snubbers.

- **Chapter 6** discusses the experimental equipment used in circuit testing throughout this research. The chapter discusses the evolution of the initial capacitive deionisation test rig to the final super capacitor load used.

- **Chapter 7** presents conclusions, the author's contribution, and suggestions for future research

### Chapter 2 DC-DC Converters for Voltage Step-Down Applications

Chapter 1 introduced water desalination and its applications. From this, the method of capacitive deionisation was selected for further investigation. Chapter 2 details analysis of capacitive deionisation, (CDI), electrical requirements. and introduces and evaluates a range of converter topologies that are suited to capacitive deionisation.

### 2.1 Circuit Design Scope

In addition to water desalination, there are many power conversion applications that require significant voltage step-down ratios, such as LED lighting or battery chargers. Such circuits require step-down ratios greater than 10:1. For example, if the circuitry is supplied from a rectified 230V single-phase AC to DC stage, the input voltage is 340V DC and the output voltage must be stepped down to 30V. Water desalination requires even greater step-down ratios due to typically low output voltage stipulations. For example, a step-down ratio of 190:1 is necessary to achieve the 1.8V output required for capacitive deionisation desalination from a single phase AC supply. [1] Conventionally, a flyback or multiple-stage buck converter [26] would be used to achieve such ratios. However a coupled-inductor buck circuit [27]–[29] or a dual active bridge may be considered as a more efficient voltage step-down converters are also considered and evaluated.

### 2.2 DC-DC Converters

A DC-DC converter is a circuit that transforms direct current, DC, from one voltage level to another whilst concurrently changing the current by the inverse of the same ratio. DC-DC converter circuits function through the switching of a semiconductor switch. The ratio

of switch on time to the switching period is used to determine the output voltage. Whether the input voltage is increased or decreased depends on the circuit arrangement. DC-DC converters can be evaluated by their power density, complexity, efficiency and resultant cost and reliability.

### 2.2.1 Comparison and Simulation of Converters

Being able to compare existing converters relies on defining the criteria to compare them against and describing the simulation so that it can be recreated and repeated.

The circuits are simulated using the software Pspice which allowed for accurate simulations of a variety of circuits using the same components thus allowing fair comparison.

The fundamental design parameters of all converters are stated in Table 2.1, unless stated otherwise. Individual component values are stated under each simulation. These apply to all the fundamental converters simulated in Chapter 2.

Table 2.1 Fundamental converter simulation parameters

| Variable        | Value |

|-----------------|-------|

| Coupling Factor | 0.95  |

| Frequency       | 40kHz |

| Duty Cycle      | 24%   |

| Input Voltage   | 300V  |

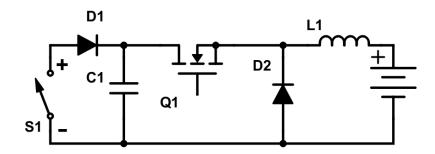

### 2.2.2 Buck Converter

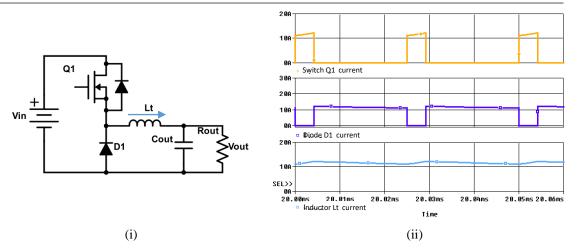

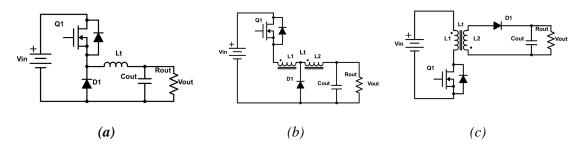

The simplest step-down converter is the buck converter, Fig. 2.1(a), which comprises three components: a semi-conductor switch, diode and an inductor and can be arranged in three forms: buck, boost, buck-boost. The buck circuit is a popular solution for applications with small voltage step-down ratios.

When the main switch Q1 is turned on (for period t<sub>on</sub>), current flows through it from Vin (input voltage), through the inductor Lt to the output capacitor C1 to support the output voltage (Vout). During this switch on-time (conduction time), energy is delivered from

the input to the inductor. As the current in the inductor increases linearly during the ontime, additional energy is stored in the inductor core.

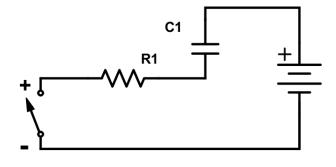

When Q1 turns off (for period t<sub>off</sub>), current flow through the inductor cannot step change instantaneously, it can only change continuously due to flux within the core. The inductor voltage can change instantaneously in order to maintain the current continuous. During the off-time, the voltage at the diode's cathode falls until the diode becomes forward-biased. The forward-biased diode conducts the current flowing through Lt thereby providing a continuous current path for the inductor current flow to the output capacitor and the load, R1. Typical waveforms of various circuit elements are shown in Fig. 2.1b.

Continuous conduction is a mode of operation where the inductor current never drops to zero for any period of time. In continuous conduction, the ratio of output to input voltage is the '*duty cycle*',  $\frac{V_{out}}{V_{in}} = \delta = \frac{t_{on}}{t_{on}+t_{off}}$ , where  $\delta$  is the switch on-state duty cycle. It is the percentage of time the switch is turned on during the cycle time period. Buck converters are used extensively in low voltage DC-DC power supplies and LED drivers due to their low cost and simplicity. In LED drivers, both the output voltage and continuous current in the output inductor are controlled by this topology. However, the current drawn from the supply is always discontinuous due to the main switch being connected to the input, so when the switch turns off, no input current can flow.

The buck converter [33] is conventionally limited to a duty cycle in the region of 10% to 90% of the switching period. Below 10%, the primary switch on-time is small, so the peak currents in Q1 become large compared to the average input current, while at the other duty cycle extreme, the peak diode current is large compared to the average output current, rendering the circuit inefficient.

*Fig. 2.1 Conventional buck converter: (i) Schematic and (ii) simulated currents of Q1, D1 and Lt.*

Table 2.2 Buck converter simulation parameters

| Component        |      |                        |

|------------------|------|------------------------|

| Primary Inductor | Lt   | 484µH                  |

| Load             | Rout | 2Ω                     |

| Output Capacitor | Cout | 6.8μF                  |

| MOSFET RDSon     | Q1   | 1μ $Ω$ (assumed ideal) |

#### 2.2.3 Buck-Boost Converter

The buck-boost converter is shown in Fig. 2.2. The circuit can provide both boost and buck functions. That is, it can both step-up and step-down. When the switch Q1 is on, the diode D1 is reverse biased and current flows from the supply Vin, storing energy in the inductor Lt. When the switch Q1 turns off the diode becomes forward biased and the inductor current then flows into the output capacitor C1 and load. In the buck-boost converter even when the inductor current is continuous, the current in both the supply side and output side is discontinuous. While operating with continuous current in the inductor  $\frac{V_{out}}{V_{in}} = \frac{-\delta}{1-\delta}$ , noting that the output is referred in the opposite direction (inverted). If the duty cycle less than 50% the converter will step down (in magnitude) the input voltage, whereas if the duty cycle is above 50% the converter is inverted its application is limited. Also, both Q1 and D1 have to be rated to support V<sub>in</sub>+|V<sub>out</sub>|, whereas in the buck converter Q1 and D1 only have to support Vin.

Fig. 2.2 Buck-boost converter

### 2.2.4 Flyback Converter

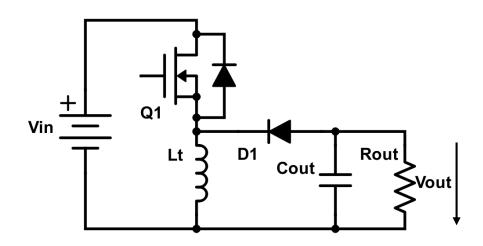

The flyback converter [34] is an isolated (coupled circuit) variant of the buck-boost converter. The inductor Lt in Fig. 2.3(a) is a pair of inductors wound on the same core forming an isolated coupled-inductor. The flyback converter can both step up and step down depending on the duty cycle. The coupled inductors both link the same core flux and therefore when Q1 is turned off the current which was flowing in the first inductor is replaced by a current in the second inductor. At any one time current only flows in one winding of the coupled pair of inductors. The energy stored in the core increases during the on-time of Q1 and decreases during its off-time. Fig. 2.3b shows typical circuit waveforms. The flyback converter is one of the most commonly used converters as it provides a wide range of output voltages by variation of the turns ratio of the coupled inductor.

When the flux in the core does not drop to zero  $\frac{V_{out}}{V_{in}} = \frac{N2}{N1} \frac{\delta}{1-\delta} = \sqrt{\frac{L2}{L1}} \frac{\delta}{1-\delta}$ , where N2 is the turns on L2, the secondary and  $N_I$  is the primary turns, forming L1. The maximum energy that can be transferred is limited by the maximum energy that can be stored in the core volume, viz.  $\frac{1}{2}BH \times Volume$ .

The current delivered to the output capacitor of the flyback converter is always discontinuous. Although the flyback converter does not have a continuous current path to

the load when the main switch is on, it does offer the isolation afforded by the magnetic component. A switch clamp circuit is advisable for efficiency and to protect the switches from over-voltages resulting from leakage inductance due to imperfect magnetic coupling [35], [36].

*Fig. 2.3 Single switch flyback converter: (i) schematic and (ii) simulation currents for switch Q1, diode D1 and the primary and secondary of Lt.*

Table 2.3 Flyback converter simulation parameters

| Component          |      |                     |

|--------------------|------|---------------------|

| Primary Inductor   | L1   | 484µH               |

| Secondary Inductor | L2   | 70µH                |

| Load               | Rout | 2Ω                  |

| Output Capacitor   | Cout | 6.8µF               |

| MOSFET RDSon       | Q1   | 1µΩ (assumed ideal) |

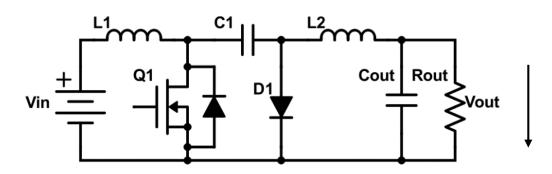

### 2.2.5 Cuk Converter

The Cuk converter [37] uses a coupled-inductor (L1 and L2) (coupling is optional), as shown in Fig. 2.4, and a capacitor C1 to provide a path for continuous input and output currents in both states of the switch Q1. The voltage transfer function of the Cuk converter is the same as the buck-boost converter  $\frac{V_{out}}{V_{in}} = \frac{-\delta}{1-\delta}$  with the output also inverted.

Fig. 2.4 Cuk converter

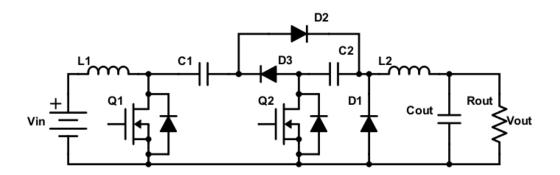

Fig. 2.5 shows an extension of the basic Cuk converter with the addition of a multistage capacitor [38] and [39], with the addition of a switch and diode to give a larger step-down ratio [40]. Reference [40] reports efficiencies of 77% and 71% at frequencies of 500kHz and 1MHz respectively. The circuit is simple and the control is the same as for a standard Cuk converter, so only requires one control signal as all switches are referenced to a common ground and can be controlled from the same gate driver. However, to obtain the higher efficiencies desired, and the step-down ratio required for desalination, would be a difficult challenge. Additionally, the circuit is not readily reversible. Both this circuit and the basic Cuk converter do however have transformer isolation versions.

Fig. 2.5 Multi-stage Cuk converter.

#### 2.2.6 Dual Active Bridge Converter

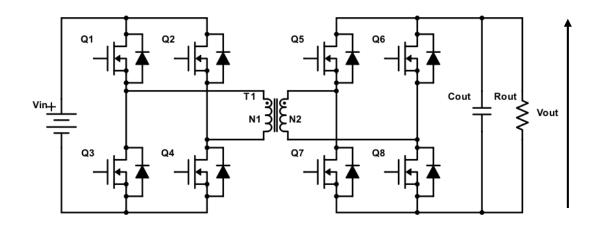

The dual active bridge [30], Fig. 2.6, has been proposed as an isolated and reversible DC-DC converter. With full bridges, one high voltage and one low voltage (for a step-down application) it offers complete control of the power flow in either direction. This flexibility comes at a price with a large number of devices and gate drive circuits. The step-down ratio of the dual active bridge is directly proportional to the turns ratio of the rectangular AC driven transformer. Therefore, for a large step-down ratio, a large turns ratio may impact on coupling factor, hence efficiency.

Fig. 2.6 Dual active bridge converter

### 2.3 Tapped Inductor Topologies

Utilising a coupled or tapped-inductor is a method to achieve large step down ratios. There are many variants of a coupled-inductor topology and these are presented in [41]. In total, 27 single switch/diode/inductor coupled (tapped) inductor buck, boost and buck-boost topologies are described. Each design is suited to different applications. The circuits were all considered to find the most suitable for the water desalination application. The boost topologies within the presented circuits are eliminated from further analysis as voltage step down is required. Equally the buck-boost topologies can step down but

employ some of their dynamic duty cycle range on boost, so only buck tapped inductor topologies need to be considered.

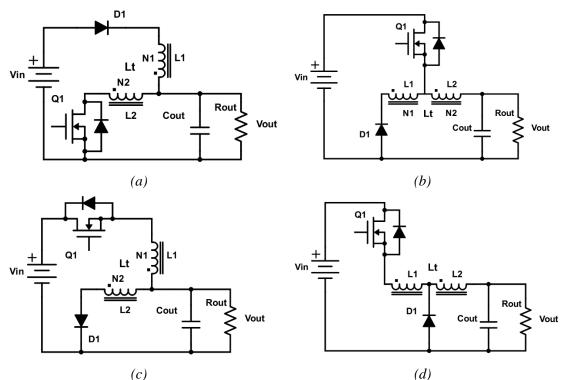

Within the remaining proposed topologies, the windings can either be arranged opposing or in concurrence. Windings arranged in opposition are not considered because they are less efficient due to a coupled current flowing in the opposite direction to the required output current [41]. So every cycle the current in the winding with the lowest number of turns of the two opposing windings must reverse. Although theoretical this is not an issue, this non-productive energy reversal transfer reduces the efficiency due to practical losses in the involved elements. This leaves four buck converters (in [41], termed T1b+, S1+/-, T1+ and S5+/-) in the four parts of Fig 3.7.

Fig. 2.7 four buck function circuits: (a) T1b+ output tap, (b) S1+/- switch tap, (c) T1+ output tap, (d) S5+/- diode tap [41]

The voltage transfer functions of the four tapped buck converters are [41]:

T1b+:

$$\frac{V_{out}}{V_{in}} = \frac{N(1-\delta)}{N(1-\delta) - \delta(1-N)}$$

(2.1)

S1 + /-:

$$\frac{V_{out}}{V_{in}} = \frac{\delta}{\delta + N(1 - \delta)}$$

(2.2)

T1 +/-:

$$\frac{V_{out}}{V_{in}} = -\frac{\delta(1-N)}{N(1-\delta) + \delta(1-N)}$$

(2.3)

S5 +/-:

$$\frac{V_{out}}{V_{in}} = \frac{\delta N}{\delta N + (1 - \delta)}$$

(2.4)

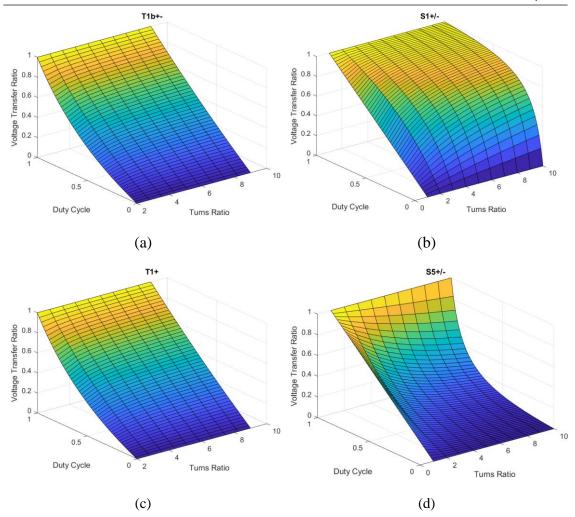

The four transfer functions are plotted in Fig. 2.8. All are a modification to the standard buck converter transfer function,  $\delta$ . The feature sought for high step down levels is reduced output sensitivity to wide duty cycle variation at low duty cycles. Converters that have the lowest gain at high turns ratio and low duty cycle are candidates, viz. only S5+/-

Additionally, T1+ can be eliminated because the output is inverted, which creates added complications but no additional benefits. Similarly, T1b+ is removed from consideration due to the switch not isolating the input from the output, so the output voltage is the input voltage when the power is first applied. This would create load cell safety issues as it removes a key fail safe aspect from the process.

For a given step down ratio S1+/- has a much higher output voltage than S5+/-. As a large step down ratio is desired S5+/- should be investigated further as a wide  $\delta$  range for a low, slow changing output voltage is optimal.

Fig. 2.8 Step down ratio versus duty cycle and turns ratio (a) T1b+/-,(b) S1+/-,(c) T1+,and (d) S5+/-.

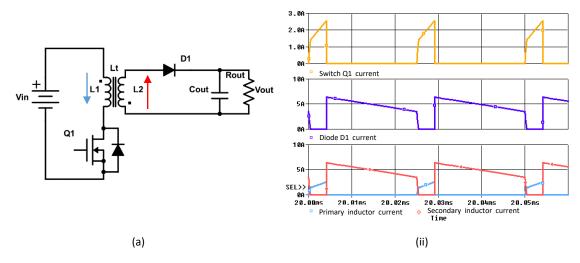

### 2.3.1 Coupled-Inductor Buck Converter

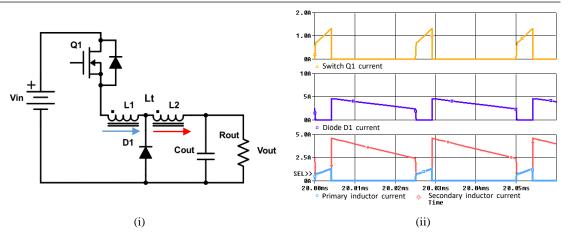

Fig. 3.9(a) (Fig. 3.7(d), S5+/-) shows a coupled-inductor version of the buck converter [42]–[45] in which the single inductor is split into two inductors wound on a single core. The freewheel diode is connected to a common node between the two inductors. This connection of inductors is also referred to as a tapped inductor. [46]

When switch Q1 in Fig. 2.9(a) is on, the current can flow from the input supply through Q1 and Lt (comprising  $N_1+N_2$  turns on a single core) to the output capacitor C1 and load R1. In this state the circuit functions like a standard buck converter with energy building up in the inductor Lt as the current increases. Typical circuit waveforms are shown in Fig. 2.9(b).

*Fig. 2.9. Coupled-inductor buck converter* S5+/- [46]: (*i*) *Schematic and* (*ii*) *simulated currents for switch Q1, diode D1 and the primary and secondary of Lt.*

Table 2.4 Coupled-inductor buck converter simulation parameters

| Component          |      |                     |

|--------------------|------|---------------------|

| Primary Inductor   | L1   | 484µH               |

| Secondary Inductor | L2   | 70µH                |

| Load               | Rout | 2Ω                  |

| Output Capacitor   | Cout | 6.8µF               |

| MOSFET RDSon       | Q1   | 1µΩ (assumed ideal) |

When Q1 is turned off, the diode D1 provides a freewheel path for the current in L2. At the point of switching the flux or MMF in the core must be maintained. The current in L2 increases to a higher value consistent with the terminated current in L1, thereby maintain the same core flux.

$$I_2 after Q1 switch of f = \frac{N1 + N2}{N2} I_1 before Q1 switching$$

(2.5)

With an appropriate choice of turns for L1 and L2, the current which can be delivered to the load during the switch off-time can be significantly higher than the current in the switch while it was conducting. Q1 in Fig. 2.9(a) is therefore rated for a current which can be significantly less than the current in the load.

The diode D1 must be rated to carry the high load current but unlike the buck converter the diode D1 is not rated at the output voltage. When Q1 is on, the supply voltage (minus the small output voltage) is dropped across the series combination of L1 and L2, thereby increasing the voltage rating of D1 in the coupled-inductor buck converter to Vout+VL2.

As with the conventional buck converter in Fig. 2.1, an inductor combines with the output capacitance to create a low-pass output filter. The coupled inductors enable the voltage step-down ratio at a given duty cycle to be greater than that of the conventional variant, as the turns-ratio of the coupled inductor contributes to the overall step-down ratio of the circuit. A feature of the coupled-inductor buck converter is that energy is transferred into the output during both the switch on and off times, due to the output being continuous compared to the flyback converter which has discontinuous output current, but provides isolation. Both the flyback and tapped inductor converters are reversible, once a second switch is utilised across the output diode (both reversibility and synchronous rectification result).

### 2.4 The Need for Switch Protection

There are two main causes for overvoltage on the primary side of either the coupledinductor buck or the flyback converter. Either transformer action referring the voltage across the secondary back to the primary or the leakage inductance on the primary winding. The flyback is easier to comprehend so is analysed below.

### 2.4.1 Transformer Action

To analyse the voltage referred back to the primary side, the total voltage on the secondary side should be evaluated.

Using the arrow directions of Fig. 2.10 (arrow head is positive), the voltage across the secondary winding is

$$V_{L_2} = V_{out} + V_{D1} + V_{Lstray2a} + V_{Lstray2b} + V_{LeakL2} + I_2 R_{L_2}$$

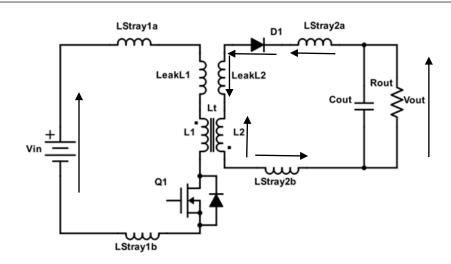

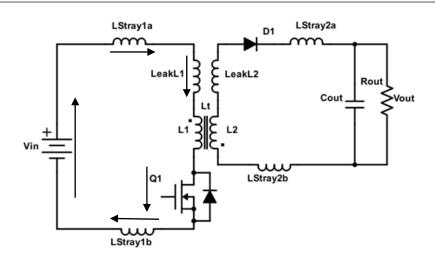

Fig. 2.10 Non ideal voltages seen by flyback converter

During the off time of the switch Q1 there are two situations:

1. The initial transition when there is a large di/dt which develops significant voltages on the leakage inductance of L2 and the stray inductances of the secondary loop. The voltage across the ideal part of the coupled flyback inductor is:

$$V_{L_{2}} = V_{out} + V_{D1} + V_{Lstray2a} + V_{Lstray2b} + V_{LeakL2} + I_{2}R_{L_{2}}$$

2. The steady state when current has transferred to the secondary, the di/dt is relatively small. The voltage across the ideal part of the coupled flyback inductor is

$$V_{L_2} = V_{out} + V_{D1} + I_2 R_{L_2}$$

In the case of a large step down converter with a very high secondary current and low output voltage, the voltage across the diode and the voltage across the winding resistance of  $L_2$  will be significant. The winding resistance must be minimised and the diode will need to be a synchronous diode function with low channel resistance.

In both these cases the voltage referred back to the primary winding will be in the direction shown in Fig. 2.11 which can then be used to calculate the voltage seen across the main switch Q1.

Fig. 2.11 Non idealities on primary side of flyback converter, referred back from the secondary The referred voltage is givens by

$$V_{L_1} = \frac{N_1}{N_2} V_{L_2} = \frac{N_1}{N_2} \left[ V_{out} + V_{D1} + V_{Lstray2a} + V_{Lstray2b} + V_{LeakL2} + I_2 R_{L_2} \right]$$

During the primary to secondary transfer of energy, the primary side di/dt is large and negative, inducing voltages in the direction shown across the primary side stray inductances and the primary side leakage inductance.

However once the energy transfer is complete the di/dt on the primary side disappears but a referred voltage from the secondary to primary remains. The steady state voltage across Q1 during its off condition is therefore

$$V_{Q_{1off}} = V_{in} + \frac{N_1}{N_2} \left[ V_{out} + V_{D1} + I_2 R_{L_2} \right]$$

It is vital therefore that the switch protection circuit should avoid clamping the voltage across the switch to lower than this, which would prevent the complete transfer of energy from the primary to secondary. This voltage is shown in the simulations to follow where an ideal inductor is used in series with the load and the diode.

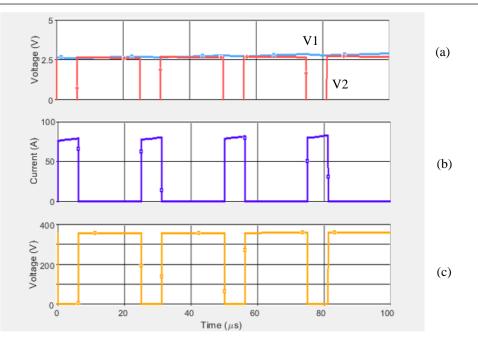

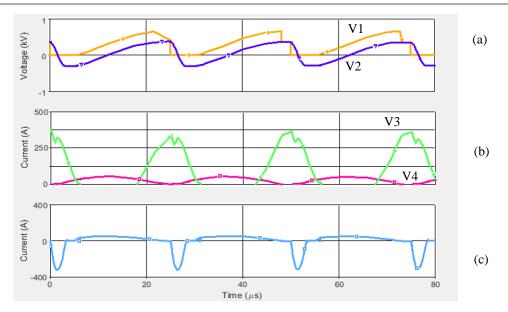

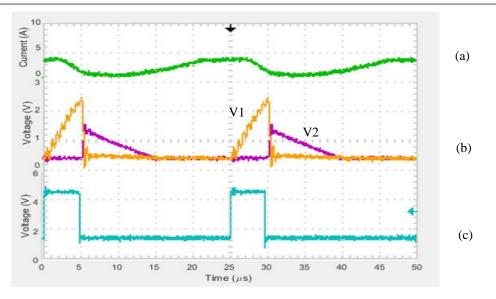

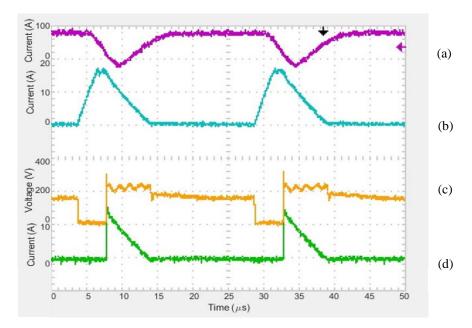

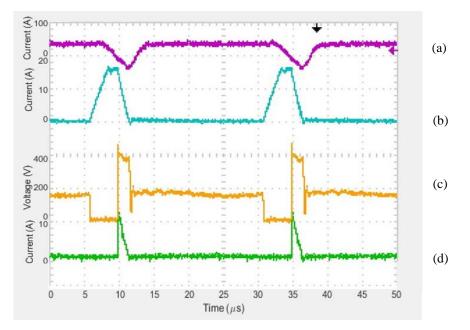

*Fig. 2.12 simulation showing referred voltage (a)(V1) Output Voltage (Vout), (a)(V2) Diode Voltage (VD1), (b) Primary (L1) inductor current, (c) Q1 Switch Voltage (Vds)*

In the case in Fig. 2.12, with a turns ratio of 10:1, an output voltage of 2.5V and diode loss of 2.5V creating a total of 5V at the output side which referred back through the inductor; creates an additional 50V across the main device. With an input of 300V this explains the 350V seen across the main device during its off time.

### 2.4.2 Leakage Inductance

Using such an inductor allows for the main switch in the converter to have lower peak and average current. However, the winding of this inductor produces a leakage inductance (the windings are not perfectly coupled) which appears in series with any coupled turns. During the transfer of current from the primary winding to the secondary winding an additional voltage is developed across the leakage inductance; this adds to the voltage across the main switch during the switch off process. This voltage could be in excess of double the input voltage depending on the size of the leakage inductance. For example, for a 600V input the voltage across the switch could be over 1700V for a poorly coupled inductor. An in-depth look at the snubber circuits [47]–[49] used to protect switching devices in coupled-inductor circuits is introduced.

### 2.4.3 Solutions

A snubber is a circuit that is added to a switching circuit to provide device protection from over-voltage. It limits and modifies the switch VI trajectory and by limiting the sharp rise of voltage across a current switching device in an inductive system; by providing an alternative current path for the device current while the voltage across the device rises. This soft switching characteristic reduces the dv/dt causing the over-voltage. Another method of protecting a switch against over-voltage is by adding some form of voltage clamping. These circuits provide switch protection by providing an alternative current path but only when a certain voltage is reached and so the current from the leakage inductance will only flow into a voltage clamp when the voltage has risen above the voltage level of the clamp. This can be achieved by using a diode back to the supply rail or by creating an additional rail voltage. Circuits which provide protection using additional active components are described in Chapter 4. This section concentrates on snubbers which use passive energy management [44] during the switching transition.

# 2.5 Large Step-Down Voltage Ratio Coupled-Inductor Buck Topology Circuit – snubber and clamping circuits

The circuits in Section 2.2 are common but not necessarily used for high step-down ratios. Various papers have been written adapting some of these circuits to enable large stepdown ratios. Some of their findings, concerning snubbers, are outlined in this section. Simulations and experimental results of the proposed tapped inductor topology, S5+/-, and possible switch protection circuits are presented.

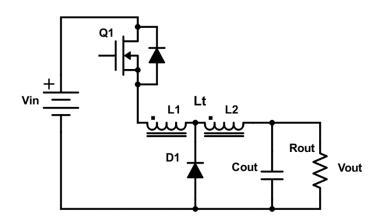

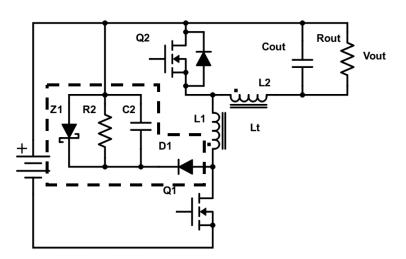

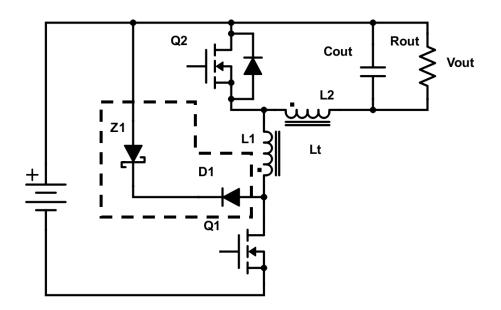

Fig. 2.13 (Fig. 2.9(a)) shows the simplest form of the coupled-inductor buck circuit, S5+/-, where Q1 is the main switching device and D1 is the freewheel diode. The coupled inductor Lt with primary L1 and L2 and output capacitor C1 and load R1. The leakage inductance energy causes voltage overshoot on the semiconductors, but that same inductance functions as a turn-on snubber, that is, switch turn-on stressing is not a significant problem.

Fig. 2.13 Coupled-inductor buck converter, S5+/-

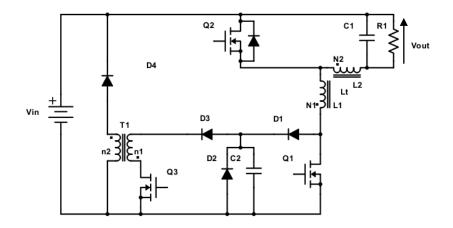

### 2.5.1 Ultrahigh Step-Down Converter [50]

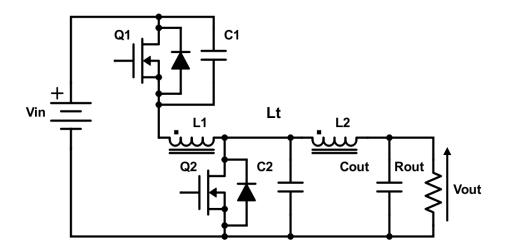

A novel design (Fig. 2.14) using a coupled inductor is presented in [50], where the circuit utilises an energy transferring capacitor which purportedly acts as a snubber capacitor. The main switch Q1 and synchronous rectifier Q2 have the same function as Q1 and D1 in Fig. 2.9. The capacitor C1 charges during the on-time of Q1, as shown in the waveform Fig. 2.15 and Fig. 2.16. When Q1 turns off an additional switch and diode conduct while the current in the primary leakage inductance drops to zero. At this point the current in the primary winding reverses and the capacitor partially discharges through Q2 and Q3. Q2 and Q3 turn off and Q1 turns back on for the next cycle. The use of the capacitor, switch Q3 and complementary switch Q2 in this circuit provides clamping of the voltage across the main switch Q1 while providing the path for the current in the leakage inductance. However, the reverse current which flows in the primary winding is detrimental to the overall energy flow and leads to an efficiency reduction.

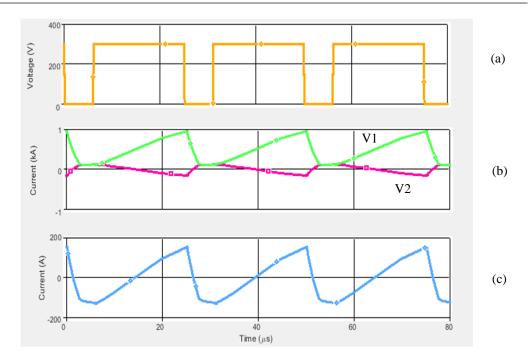

Although the converter utilises the capacitor in series with the switch and coupled inductor to ensure switch protection, the capacitor is also used for the energy transfer. The significant disadvantage of this converter is this method of switch protection. The switch is clamped using the supply rails to  $V_{in}$ , whence the switch is always protected. However, this is also the maximum voltage that is applied across the coupled inductor. A lower voltage across the inductor during the transition increases the time it takes for the transition from the primary to the secondary. In the simulation of this circuit, (Fig. 2.15

and Fig. 2.16) the energy does not finish coupling before the next transition. Various component values were assessed and due to limiting voltage,  $V_{in}$ , across the inductor, no improvement was gained. The circuit continues to function with switch protection.

The authors derive an expression for the output voltage, which increases linearly with the main switch duty ratio. According to the simulations this is incorrect as at higher duty ratios the capacitor C1, charges so as to oppose the supply voltage. Thus reducing the voltage applied to the coupled inductor. When the duty ratio is one, the output voltage is zero. The limited operating range and negative primary currents outweigh the main switch snubbering benefits of this circuit.

The desalination application requires the circuit to reverse the power flow to clean and flush the electrodes. Any snubber on the main switch would need to be replicated on the high current low voltage side when the circuit is used to reverse the power flow.

Fig. 2.14 Ultra high step-down ratio converter [50]

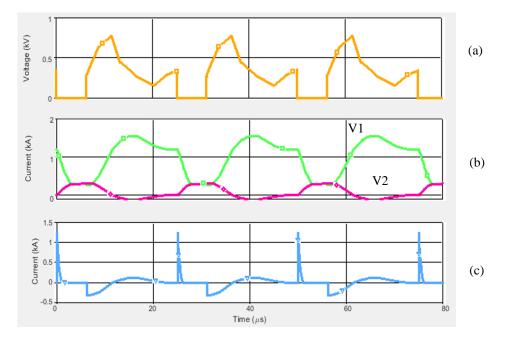

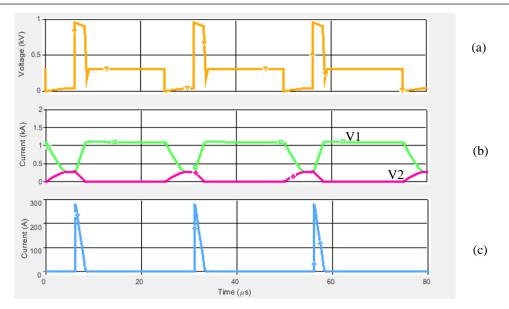

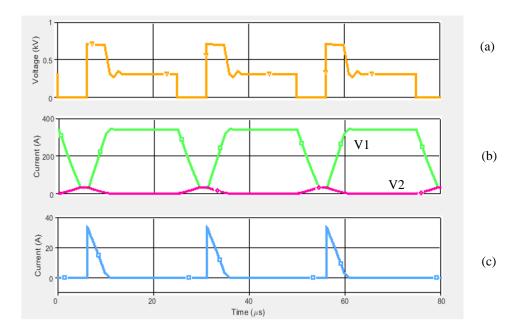

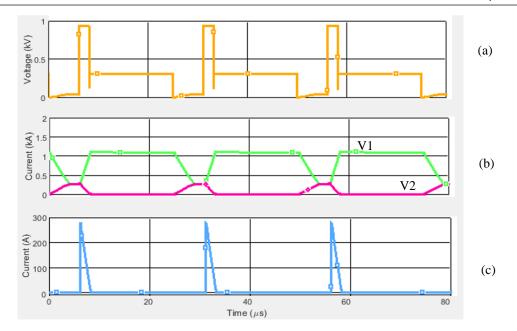

Fig. 2.15 Ultra high stepdown converter simulated with 3:1 turns ratio. (a) Q1 Switch Voltage (Vds), (b)(V1) Secondary (L2) inductor current, (b)(V2) Primary (L1) inductor current, (c) Snubber capacitor (Cs) current

Fig. 2.16 Ultra high stepdown converter simulated with 10:1 turns ratio. (a) Q1 Switch Voltage (Vds), (b)(V1) Secondary (L2) inductor current, (b)(V2) Primary (L1) inductor current, (c) Snubber capacitor (Cs) current

| Component          |          |                              |

|--------------------|----------|------------------------------|

| Primary Inductor   | L1       | 470μΗ                        |

| Secondary Inductor | L2       | 4.7μH                        |

| Snubber Capacitor  | C1       |                              |

| Load               | Rout     | 0.005Ω                       |

| Output Capacitor   | Cout     | 50mF                         |

| MOSFET RDSon       | Q1/Q2/Q3 | $1\mu\Omega$ (assumed ideal) |

Table 2.5 Ultra high step-down converter simulation parameters

## 2.5.2 High Voltage Tapped-inductor Buck Converter – shunt capacitors

Fig. 2.17, [51] is a coupled-inductor buck for a 3kV to 100V step-down converter. Two resonant capacitors C1 and C2 around the high voltage switch and across the low voltage switch allow zero voltage turn-off. However, the capacitor charging time delays the transfer of energy to the secondary of the coupled inductor, making energy transfer less efficient. As a result of these limitations the switching frequency of the converter in [51] was restricted to less than 20kHz.

*Fig. 2.17* High Voltage coupled-inductor buck converter *S5*+/- with additional shunt capacitors [51]

Circuit topology improvements are suggested in [52], where the gate drive to the high voltage switch can be made autonomous. The high voltage switch is made up of series connected low voltage MOSFETs, each having an autonomous gate driver which makes

it possible to series connect the MOSFETs to make the high voltage switch, each MOSFET having its own self powered and self-timed gate driver. The paper acknowledges that the autonomous gate drive does not provide the accurate timing required for high frequency operation. High frequency operation is advantageous in the coupled-inductor circuits as the inductor physical size and inductance decrease with a higher frequency.

Reference [52] acknowledges the main issue with coupled-inductor circuits which is the over-voltage on the main switch caused by leakage inductance and investigates a different method of minimising the voltage across the high side. It presents the idea of cascading multiple switches. This does not remove the voltage across the switch but simply shares the voltage across the switches. This technique is adequate if it can be assured that the switches turn on and off at the same time otherwise one switch will quickly take the full voltage and fail. It is also less fault tolerant, since if one switch fails it is likely all the switches will then fail.

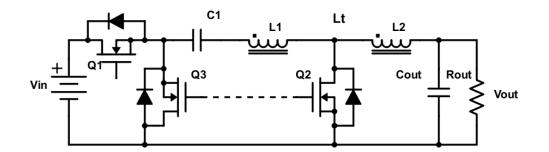

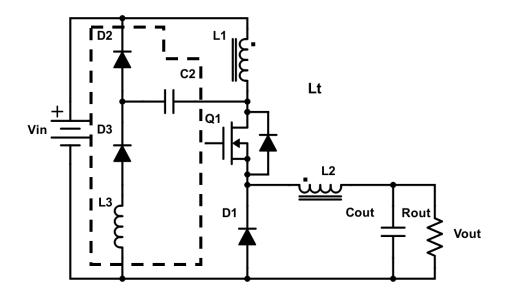

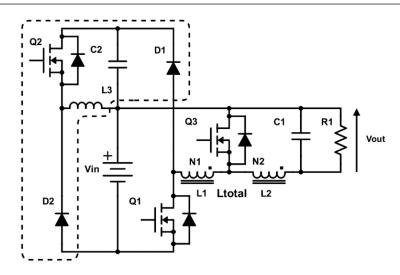

# 2.5.3 Tapped-Inductor Buck Converter for High-Step-Down Ratio dc-dc Conversion

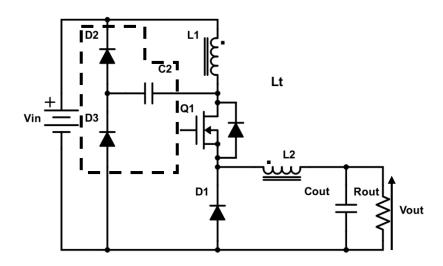

In [44] the authors describe how the coupled-inductor buck extends the duty ratio of the main switch when a high step-down ratio is required but highlights that the coupled-inductor buck suffers from two major problems. Firstly, a large voltage overshoot occurs at turn off of the main high voltage switch due to the leakage inductance between the coupled inductor primary and secondary. Secondly, the gate driver of the high voltage switch requires a floating source which means that low cost bootstrap gate drive ICs cannot be used due to the source of the device being connected directly to an inductor. [44] presents a rearranged coupled-inductor circuit topology which allows the uses of a bootstrap gate drive IC. With the rearranged coupled-inductor buck topology a simple lossless snubber is proposed which clamps the turn off voltage spike and recovers the leakage energy.

The proposed circuitry interchanges the inductor and main switch (compare Fig. 2.17 and Fig. 2.18, (Fig. 4 in [44])) which then allows for a diode capacitor diode snubber to be

implemented. The circuit still operates as a conventional coupled-inductor buck converter with the turns ratio of the inductors L1 and L2 still being used in combination with the duty cycle of the converter to step down the input voltage by a large ratio. The issue of leakage inductance is most significant when the primary side switch is turned off as that is when the stored energy associated with the leakage energy is maximum. The proposed snubber uses a capacitor C2 and two diodes, D2 and D3. The capacitor is used to both indirectly protect the device and then to increase the switch on-time current flowing through L2 and the load.

With the primary winding L1 moved to the DC power supply side, the source of Q1 is now connected to the drain of Q2. This means that a conventional bootstrap gate drive IC can be used. Diodes D2 and D3 are added with a voltage clamping capacitor C2 to provide a lossless clamp circuit.

Fig. 2.18 Coupled-inductor buck converter S5+/- with DCD snubber, (Fig. 4 in [44]).

The built experimental 12V to 1.5V/50A circuit [44] for desalination showed that the coupled-inductor circuit with the lossless voltage clamp was more efficient than the coupled-inductor buck without voltage clamp and significantly more efficient than the standard buck converter. Also their coupled-inductor design used planar tracks on the PCB with an E-core and I-core ferrite completing the magnetic path. An interleaved control strategy for a four phase converter was used, and two pairs of coupled inductors share the same core.

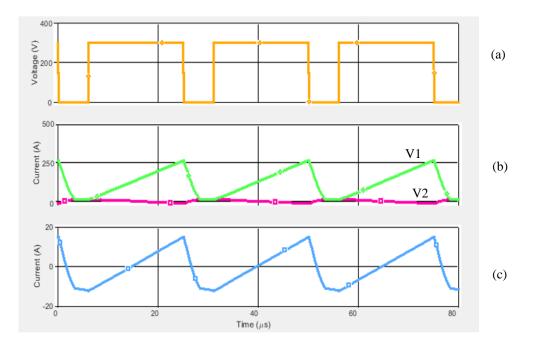

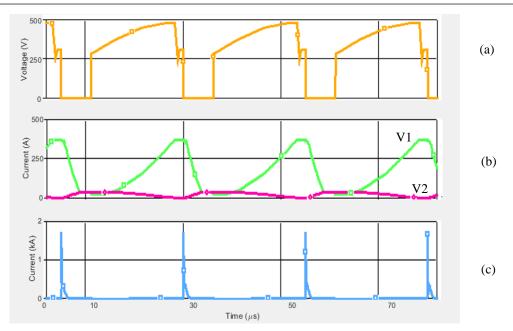

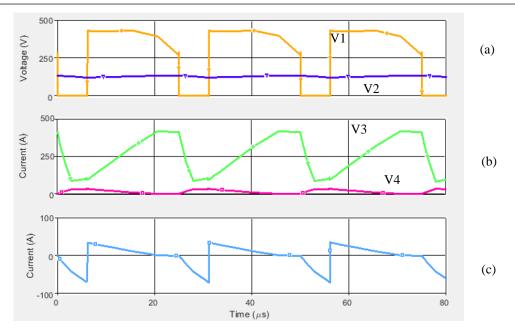

Although the snubber is effective, the simulations in Fig. 2.19 and Fig. 2.20 show high switch current flowing in Q1 when Q1 is turned on. The snubber capacitor has been charged after the previous turn off action. When Q1 is turned back on the current in inductor L2 flows from the capacitor Cs until the current builds (due to leakage) up in L1. In the case of using this circuit for a large step-down ratio, the discharge current flowing through Q1 during the initial part of the switch on time can reach the high load current level, specifically the current level in L2. This is a significant disadvantage as one of the key features of the coupled-inductor buck circuit is the ability for the primary switch to only see low currents and high voltage and similarly the secondary switch Q1 would have to be rated to both the maximum voltage and the maximum load current which would significantly increase in cost and decrease efficiency due to the higher  $R_{DS(on)}$  associated with higher voltage rated devices.

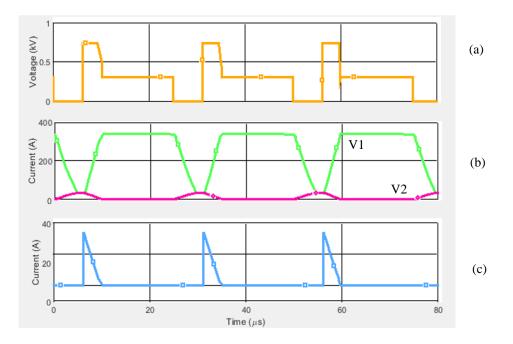

Fig. 2.19 Coupled-inductor buck converter simulated with 3:1 turns ratio in N1:N2. A 1000A capacitor current flows through Q1. (a) Q1 Switch Voltage (Vds), (b)(V1) Secondary (L2) inductor current, (b)(V2) Primary (L1) inductor current, (c) Snubber capacitor (Cs) current

Fig. 2.20 Coupled inductor buck converter simulated with 10:1 turns ratio in N1:N2. A 1500A current pulse flows through Q1. (a) Q1 Switch Voltage (Vds), (b)(V1) Secondary (L2) inductor current, (b)(V2) Primary (L1) inductor current, (c) Snubber capacitor (Cs) current

| Table 2.6 DCD snubbere | ed converter simulation | parameters |

|------------------------|-------------------------|------------|

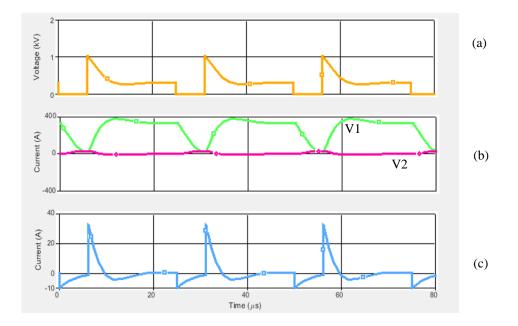

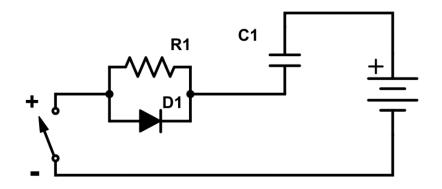

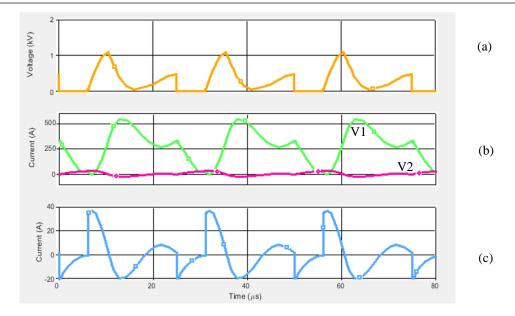

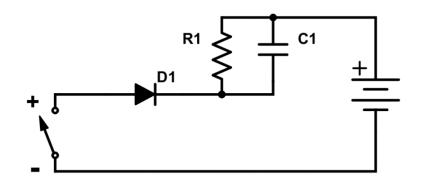

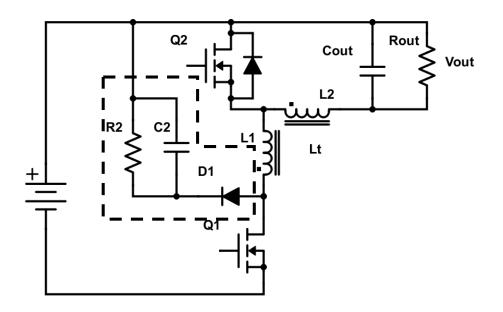

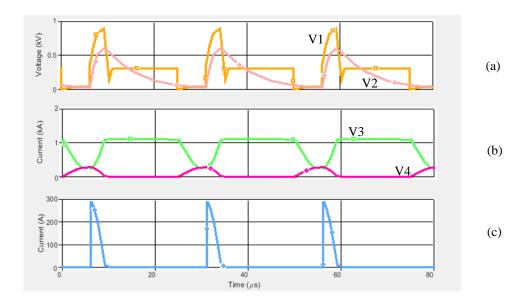

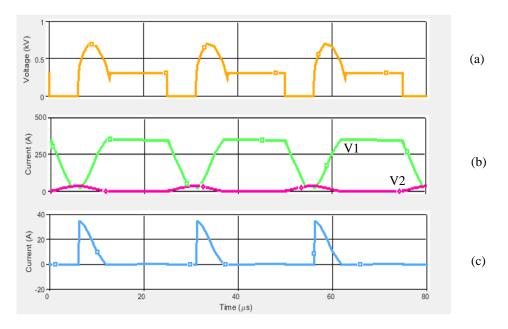

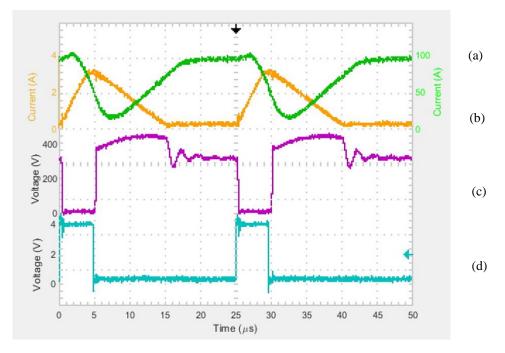

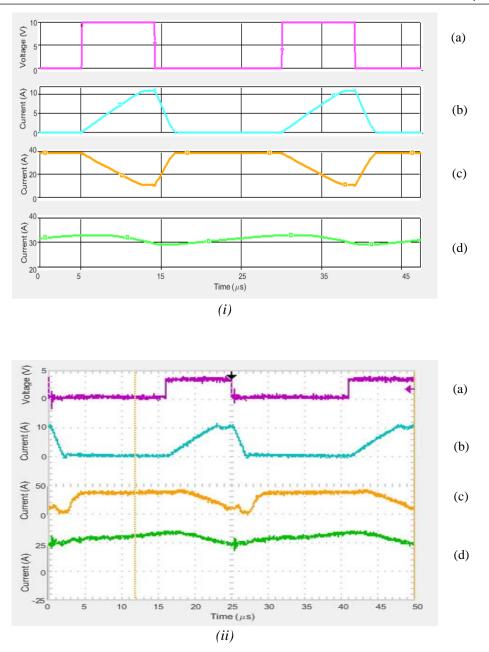

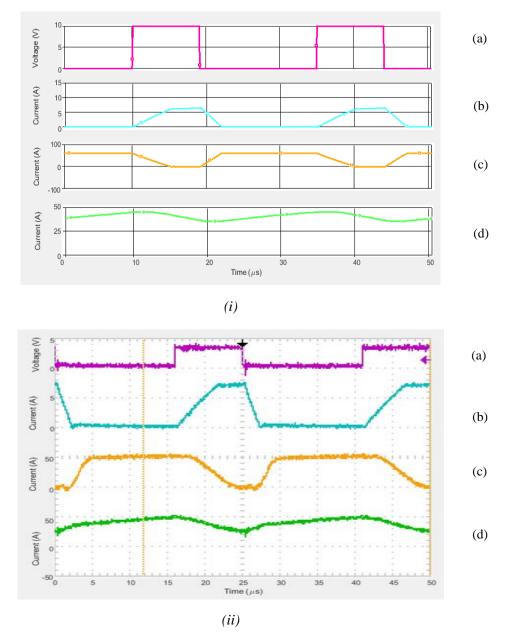

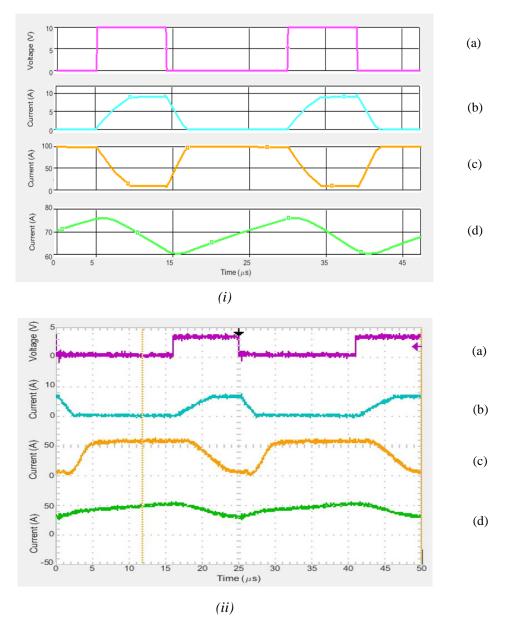

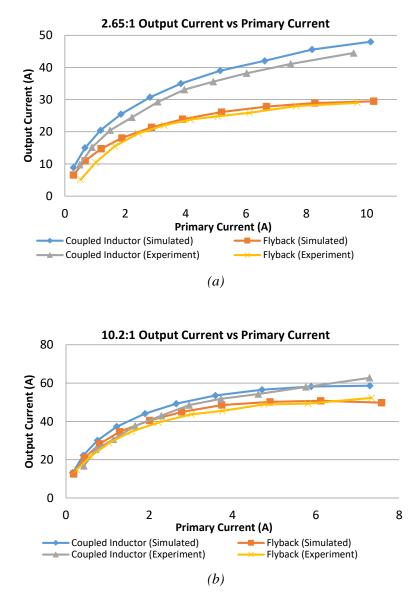

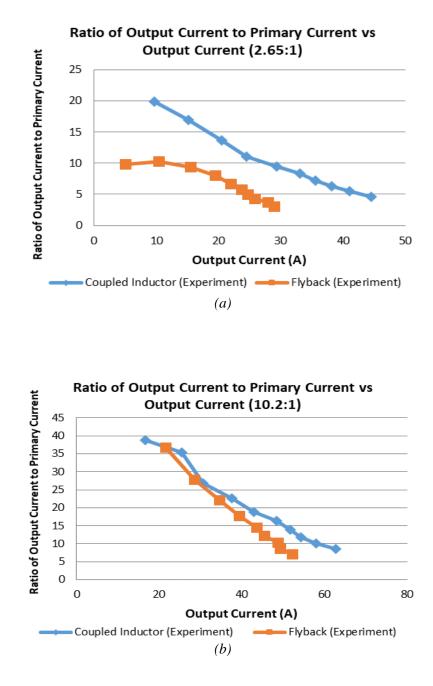

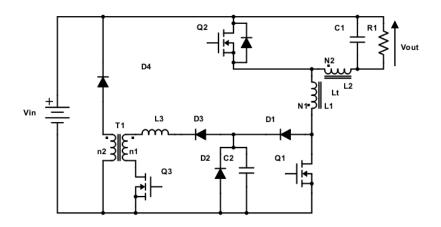

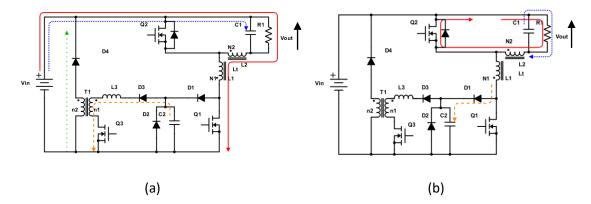

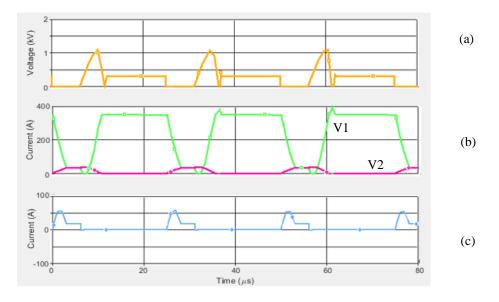

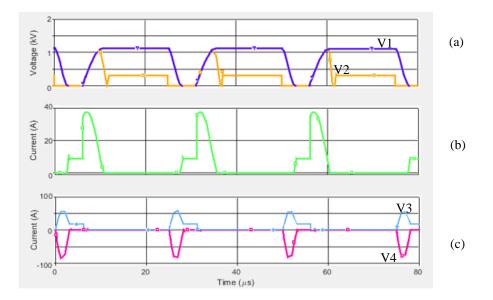

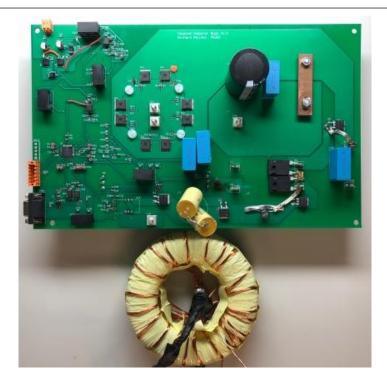

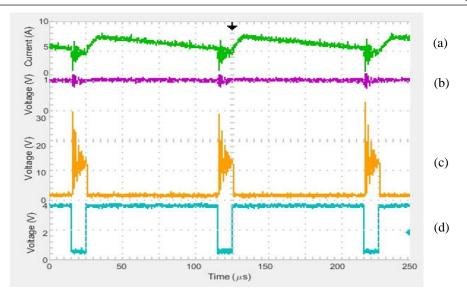

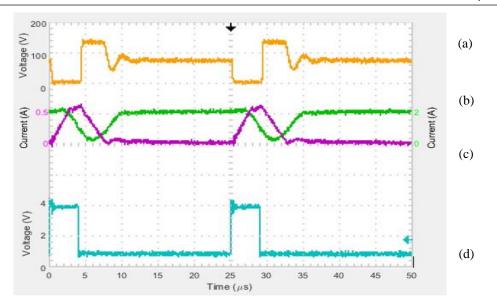

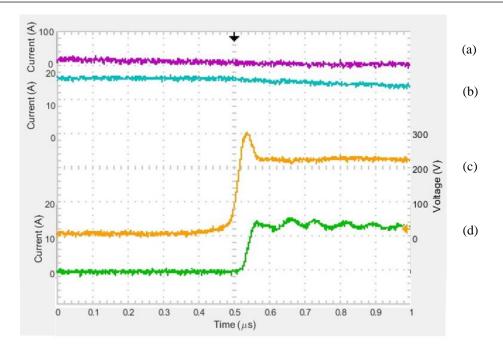

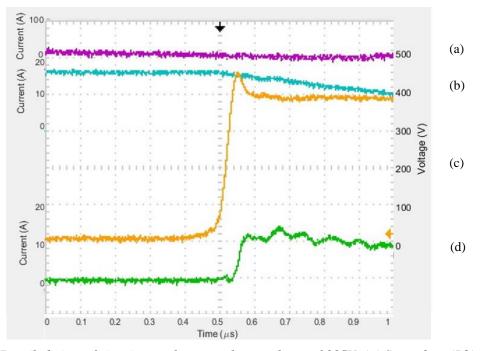

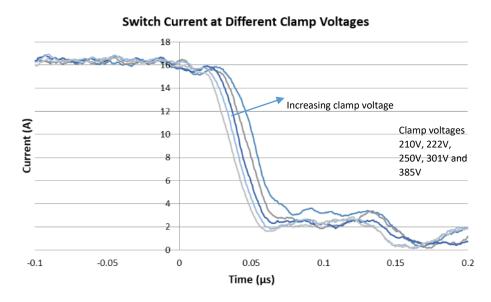

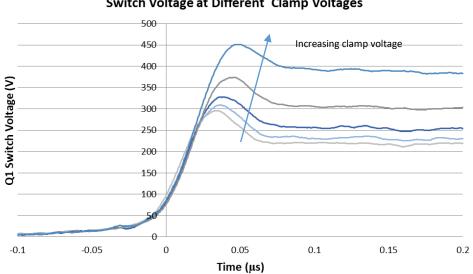

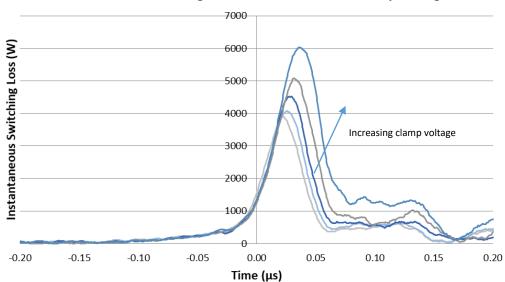

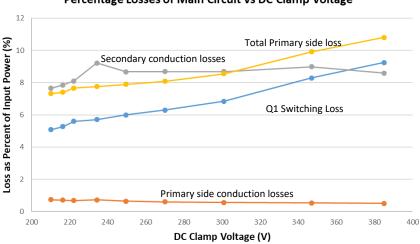

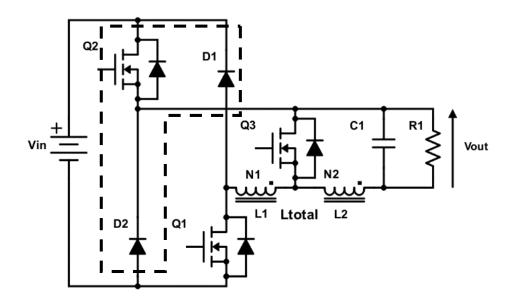

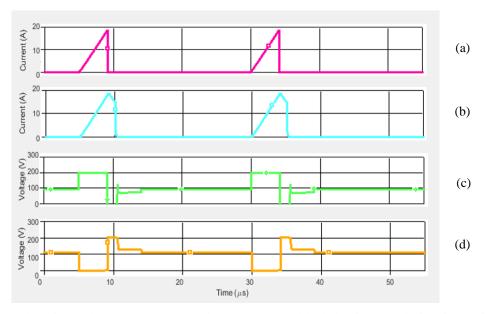

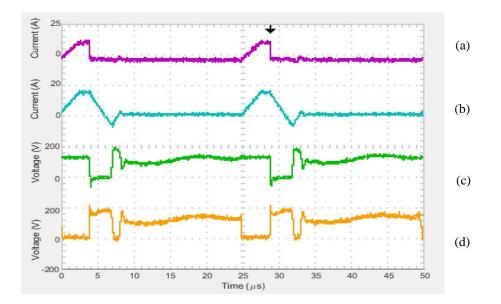

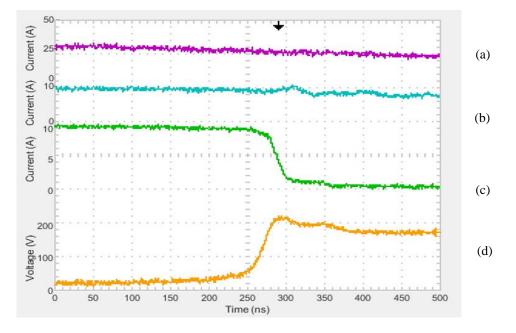

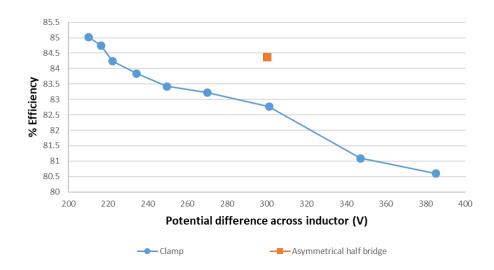

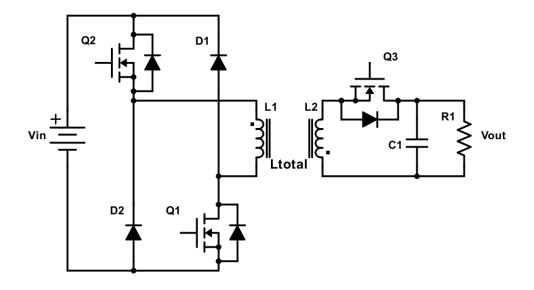

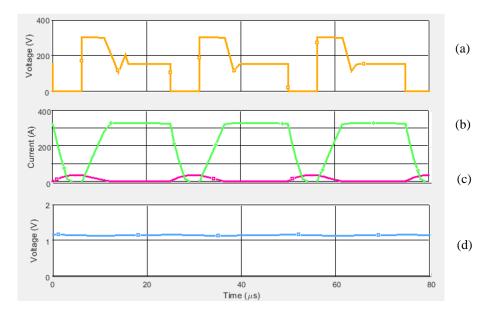

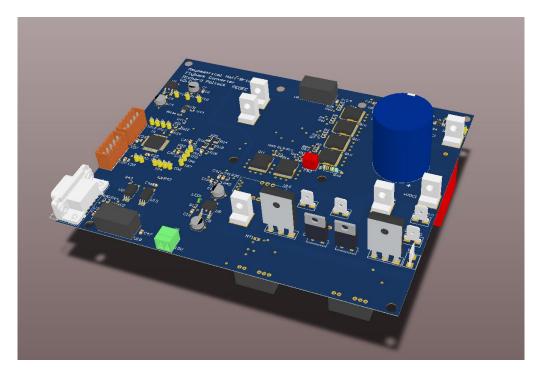

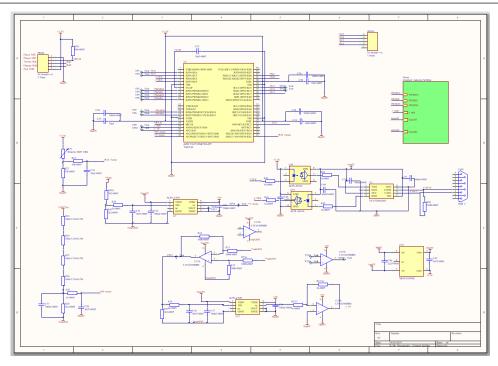

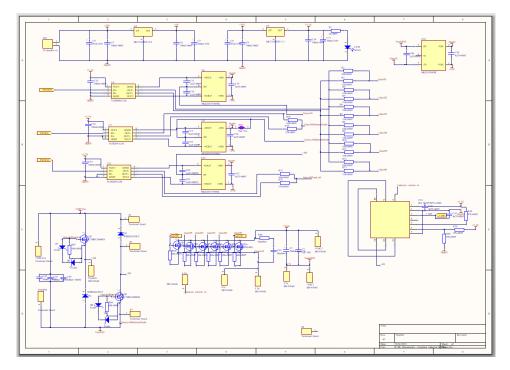

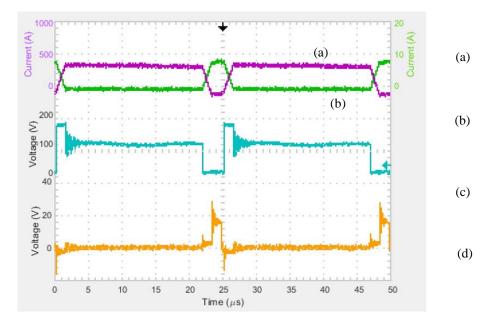

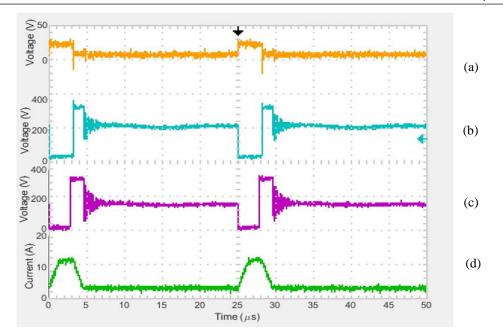

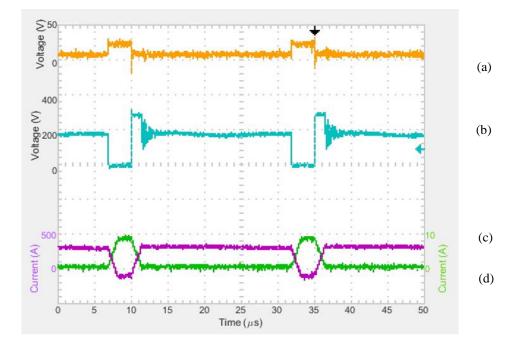

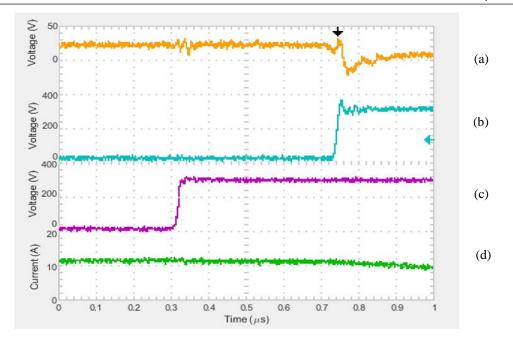

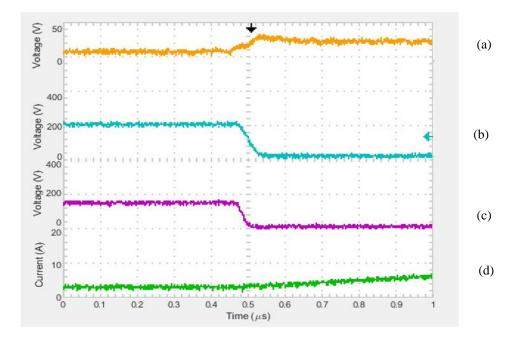

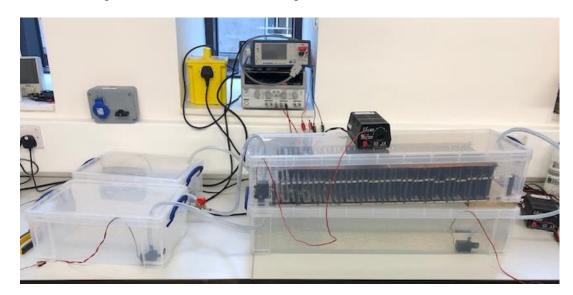

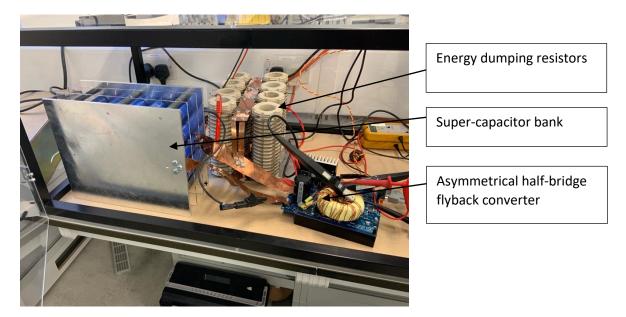

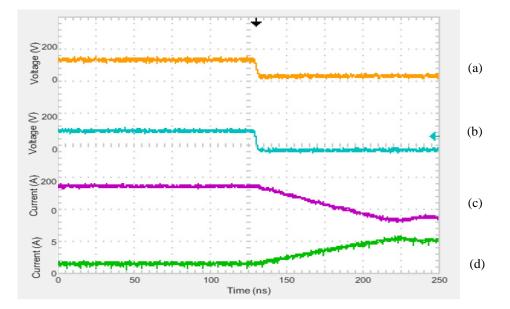

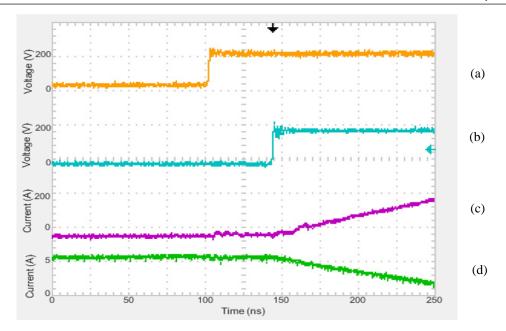

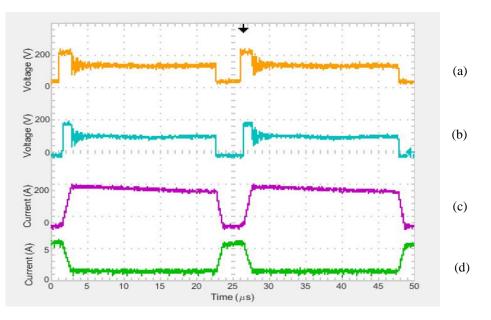

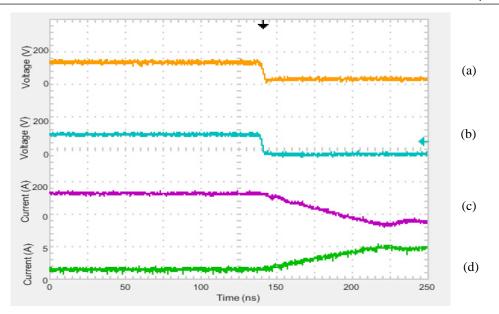

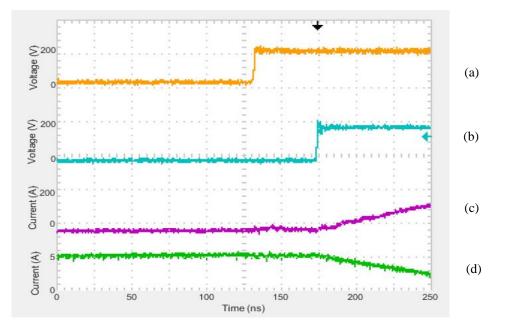

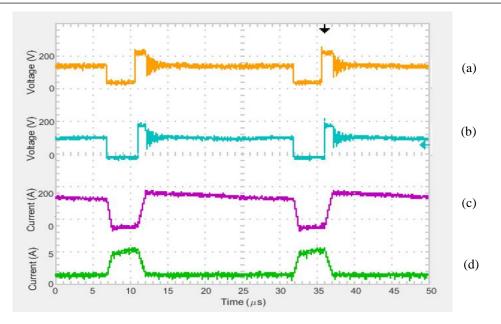

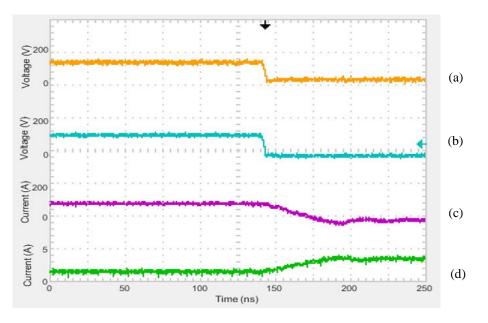

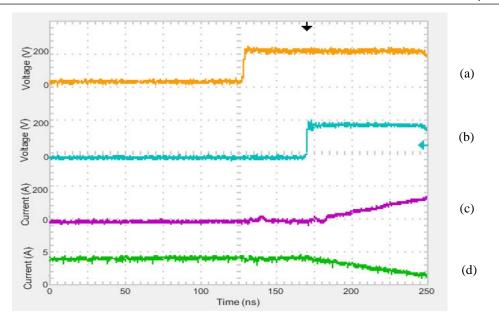

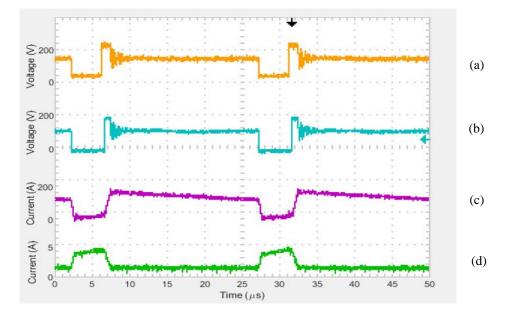

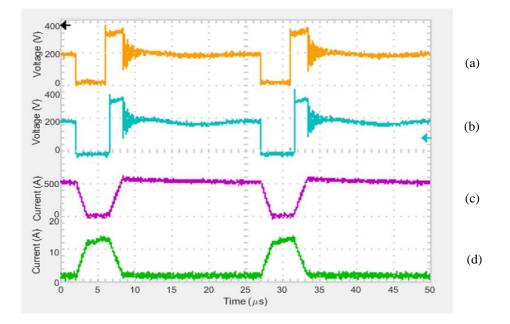

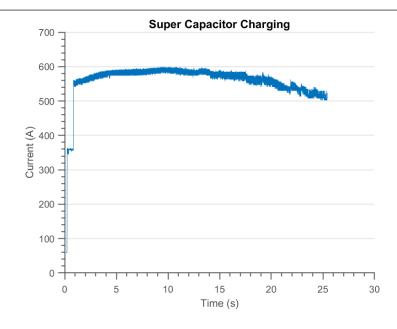

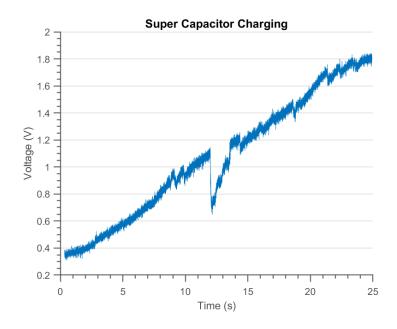

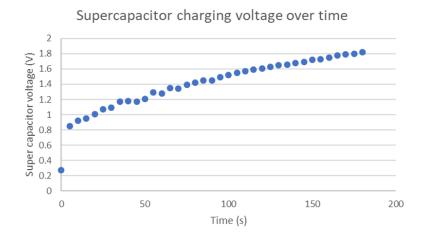

|------------------------|-------------------------|------------|