# Protection and Fault Location Schemes Suited to Large-Scale Multi-Vendor High Voltage Direct Current Grids PhD Thesis

Vasileios Psaras

A thesis submitted for the degree of Doctor of Philosophy to Department of Electronic and Electrical Engineering

University of Strathclyde, Glasgow

November 9, 2021

This thesis is the result of the author's original research. It has been composed by the author and has not been previously submitted for examination which has led to the award of a degree.

The copyright of this thesis belongs to the author under the terms of the United Kingdom Copyright Acts as qualified by University of Strathclyde Regulation 3.50. Due acknowledgement must always be made of the use of any material contained in, or derived from, this thesis.

Signed: Vasileios Psaras Date: 9/11/2021

## Abstract

Recent developments in voltage source converter (VSC) technology have led to an increased interest in high voltage direct current (HVDC) transmission to support the integration of massive amounts of renewable energy sources (RES) and especially, offshore wind energy. VSC-based HVDC grids are considered to be the natural evolution of existing point-to-point links and are expected to be one of the key enabling technologies towards expediting the integration and better utilisation of offshore energy, dealing with the variable nature of RES, and driving efficient energy balance over wide areas and across countries. Despite the technological advancements and the valuable knowledge gained from the operation of the already built multi-terminal systems, there are several outstanding issues that need to be resolved in order to facilitate the deployment of large-scale meshed HVDC grids. HVDC protection is of utmost importance to ensure the necessary reliability and security of HVDC grids, yet very challenging due to the fast nature of development of DC faults and the abrupt changes they cause in currents and voltages that may damage the system components. This situation is further exacerbated in highly meshed networks, where the effects of a DC fault on a single component (e.g. DC cable) can quickly propagate across the entire HVDC grid.

To mitigate the effect of DC faults in large-scale meshed HVDC grids, fast and fully selective approaches using dedicated DC circuit breaker and protection relays are required. As the speed of DC fault isolation is one order of magnitude faster than typical AC protection (i.e. less than 10 ms), there is a need for the development of innovative approaches to system protection, including the design and implementation of more advanced protection algorithms. Moreover, in a multi-vendor environment (in which different or the same type of equipment is supplied by various manufacturers), the impact of the grid elements on the DC fault signature may differ considerably from case to case, thus increasing the complexity of designing reliable protection algorithms for HVDC grids. Consequently, there is a need for a more fundamental approach to the design and development of protection algorithms that will enable their general applicability. Furthermore, following successful fault clearance, the next step is to pinpoint promptly the exact location of the fault along the transmission medium in an effort to expedite inspection and repair time, reduce power outage time and elevate the total availability of the HVDC grid. Successful fault location becomes increasingly challenging in HVDC grids due to the short time windows between fault inception and fault clearance that limit the available fault data records that may be utilised for the execution of fault location methods.

This thesis works towards the development of protection and fault location solutions, designed specifically for application in large-scale multi-vendor HVDC grids. First, a methodology is developed for the design of travelling wave based non-unit protection algorithms that can be easily configured for any grid topology and parameters. Second, using this methodology, a non-unit protection algorithm based on wavelet transform is developed that ensures fast, discriminative and enhanced protection performance. Besides offline simulations, the efficacy of the wavelet transform based algorithm is also demonstrated by means of real-time simulation, thereby removing key technical barriers that have impeded the use of wavelet transform in practical protection applications. Third, in an effort to reinforce the technical and economic feasibility of future HVDC grids, a thorough fault management strategy is presented for systems that employ efficient modular multilevel converters with partial fault tolerant capability. Finally, a fault location scheme is developed for accurately estimating the fault location in HVDC grids that are characterised by short post-fault data windows due to the utilisation of fast acting protection systems.

## Acknowledgements

First and foremost, I would like to express my deepest gratitude to my supervisor Prof Graeme Burt for his tremendous guidance, support and encouragement throughout the course of the PhD. His willingness and continuing motivation urged me to work hard to improve my research and evolve into an independent researcher. My immense gratitude extends to my former supervisors Dr. Abdullah Emhemed and Dr. Grain Adam for their relentless support, technical discussions, insightful conversations, and their in-depth review of my work. I am more than grateful that I had three inspiring supervisors with such friendly and warm personalities.

I am also thankful to my colleagues and friends Dr. Dimitrios Tzelepis and Dr. Dimitrios Vozikis for all the collaborative work we carried out together. Their significant experience and invaluable input greatly contributed to my research work.

I would also like to thank all my colleagues from the DC grids team of the Institute for Energy & Environment group, especially for the countless discussions with Ahmad Makkieh and Dr. Dong Wang that provided a great insight into my research. Furthermore, I owe a lot to all the rest colleagues and friends from the University of Strathclyde for their support that made my PhD life far more pleasant.

I am also very grateful to the EPSRC Centre for Doctoral Training in Future Power Networks and Smart Grids for providing me the opportunity to conduct my research and work in such a great environment with excellent colleagues from both the University of Strathclyde and the Imperial College London. Moreover, I greatly appreciate the support received through the secondment at the National HVDC Centre. The work undertaken, the RTDS training and all the interesting discussions with the colleagues from the centre significantly contributed towards shaping my ideas and research directions.

Last but not least, I would like to thank my family for their unconditional support and love that guided me throughout the course of the PhD. I am immensely grateful for their belief and trust in me all these years. I owe special thanks to Angeliki who was always there for me and eagerly offered her unlimited support in her own special way.

| С             | onter              | ts                                                 | v   |  |

|---------------|--------------------|----------------------------------------------------|-----|--|

| $\mathbf{Li}$ | List of Figures vi |                                                    |     |  |

| $\mathbf{Li}$ | st of              | Tables                                             | vii |  |

| 1             | Intr               | oduction                                           | 1   |  |

|               | 1.1                | Research Context                                   | 1   |  |

|               | 1.2                | Motivation of the Work                             | 3   |  |

|               | 1.3                | Contributions to Knowledge                         | 5   |  |

|               | 1.4                | Thesis Overview                                    | 6   |  |

|               | 1.5                | List of Publications                               | 8   |  |

| <b>2</b>      | $\mathbf{HV}$      | OC Grid Technologies and Modelling                 | 10  |  |

|               | 2.1                | HVDC Basics                                        | 10  |  |

|               | 2.2                | VSC Technology                                     | 12  |  |

|               |                    | 2.2.1 Classic Two-level VSC                        | 13  |  |

|               |                    | 2.2.2 Neutral Clamped Converter                    | 14  |  |

|               |                    | 2.2.3 Modular Multi-Level Converter                | 15  |  |

|               |                    | 2.2.4 VSC Control                                  | 16  |  |

|               |                    | 2.2.5 Converter Modelling                          | 18  |  |

|               | 2.3                | HVDC Grids Layout                                  | 21  |  |

|               |                    | 2.3.1 HVDC Grid Configurations                     | 21  |  |

|               |                    | 2.3.2 Grounding Practices                          | 24  |  |

|               | 2.4                | HVDC Grid Control                                  | 25  |  |

|               |                    | 2.4.1 Basic Converter Control Strategies           | 26  |  |

|               |                    | 2.4.2 Power Sharing Control Schemes for HVDC Grids | 27  |  |

|               | 2.5                | HVDC Circuit Breakers                              | 29  |  |

|               |                    | 2.5.1 Mechanical Circuit Breakers                  | 30  |  |

|               |                    | 2.5.2 Solid-state Circuit Breakers                 | 31  |  |

|   |     | 2.5.3  | Hybrid Circuit Breakers                                                                                                                | 32 |

|---|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 2.5.4  | DC Circuit Breaker Modelling                                                                                                           | 33 |

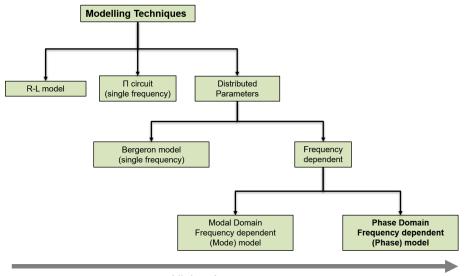

|   | 2.6 | Transı | mission Line Models                                                                                                                    | 34 |

|   |     | 2.6.1  | Distributed Parameter Models                                                                                                           | 35 |

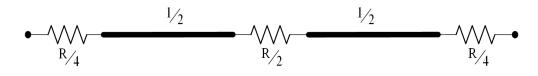

|   |     | 2.6.2  | Frequency Dependent Models                                                                                                             | 36 |

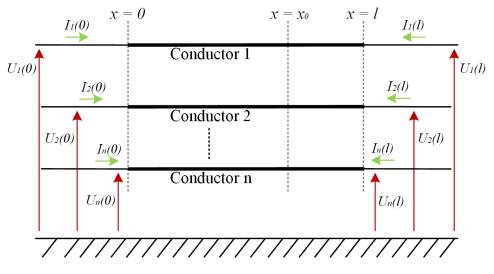

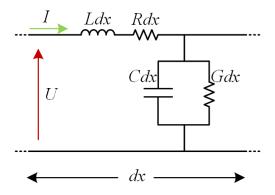

|   |     | 2.6.3  | Mathematical Formulation                                                                                                               | 37 |

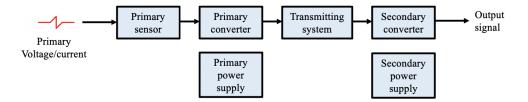

|   | 2.7 | DC Vo  | oltage and Current Measurement                                                                                                         | 43 |

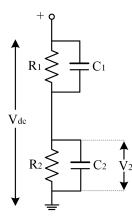

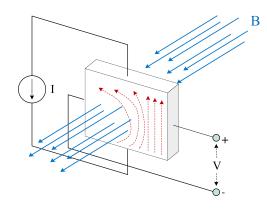

|   |     | 2.7.1  | Voltage Measuring Technologies                                                                                                         | 44 |

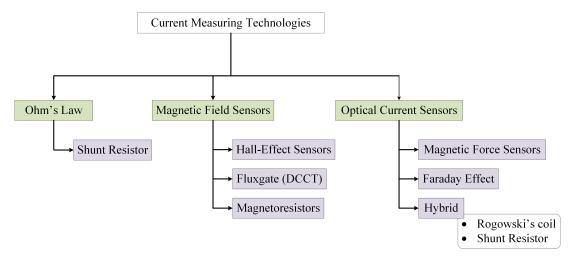

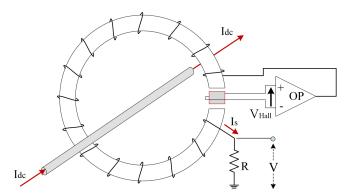

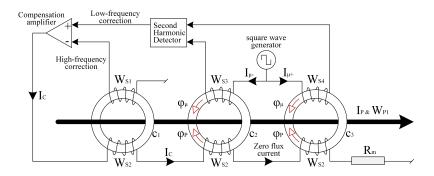

|   |     | 2.7.2  | Current Measuring Technologies                                                                                                         | 46 |

|   | 2.8 | Summ   | ary                                                                                                                                    | 56 |

| 3 | HV  | DC Gi  | rid Protection and Fault Location                                                                                                      | 58 |

|   | 3.1 | Introd | $uction \ldots \ldots$ | 58 |

|   | 3.2 | DC Fa  | aults in HVDC Grids                                                                                                                    | 61 |

|   |     | 3.2.1  | DC Fault Types                                                                                                                         | 61 |

|   |     | 3.2.2  | Fault Behaviour of VSCs                                                                                                                | 61 |

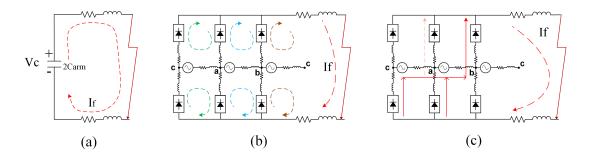

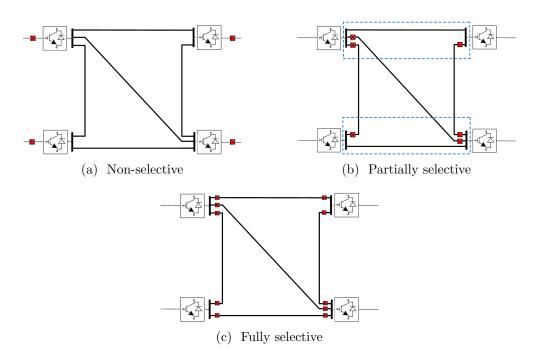

|   |     | 3.2.3  | Fault Clearing Strategies                                                                                                              | 64 |

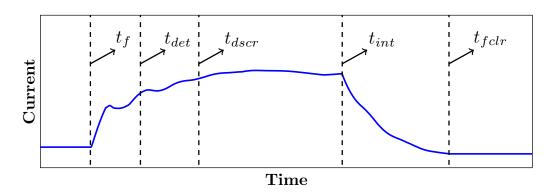

|   |     | 3.2.4  | DC Fault Clearing Sequence                                                                                                             | 66 |

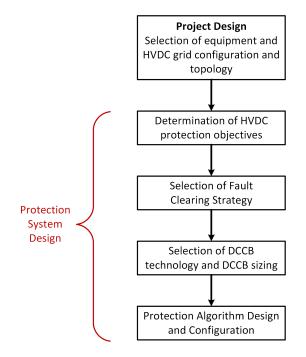

|   | 3.3 | Design | and Implementation of HVDC Protection                                                                                                  | 67 |

|   |     | 3.3.1  | HVDC Protection Design                                                                                                                 | 67 |

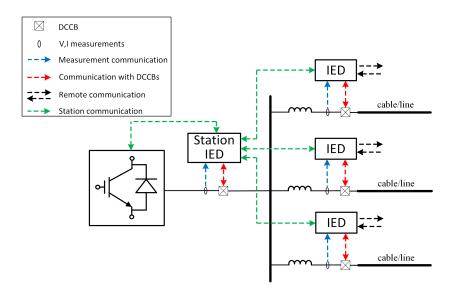

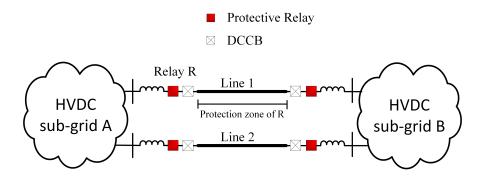

|   |     | 3.3.2  | Implementation of HVDC Grid Protection                                                                                                 | 71 |

|   |     | 3.3.3  | Interoperability of HVDC Protection                                                                                                    | 72 |

|   | 3.4 | Review | w of HVDC Protection Algorithms                                                                                                        | 74 |

|   |     | 3.4.1  | Non-unit Protection                                                                                                                    | 74 |

|   |     | 3.4.2  | Unit Protection                                                                                                                        | 79 |

|   |     | 3.4.3  | Challenges and Discussion                                                                                                              | 82 |

|   | 3.5 | Review | w of HVDC Fault Location Methods                                                                                                       | 83 |

|   |     | 3.5.1  | Travelling-Wave based Fault Location Methods                                                                                           | 83 |

|   |     | 3.5.2  | Model-based Fault Location Methods                                                                                                     | 85 |

|   |     | 3.5.3  | Frequency-Domain based Fault Location Methods $\ \ldots \ \ldots \ \ldots$                                                             | 86 |

|   |     | 3.5.4  | Reflectometry                                                                                                                          | 86 |

|   |     | 3.5.5  | Learning-based Fault Location Methods                                                                                                  | 87 |

|   |     | 3.5.6  | Challenges and Discussion                                                                                                              | 89 |

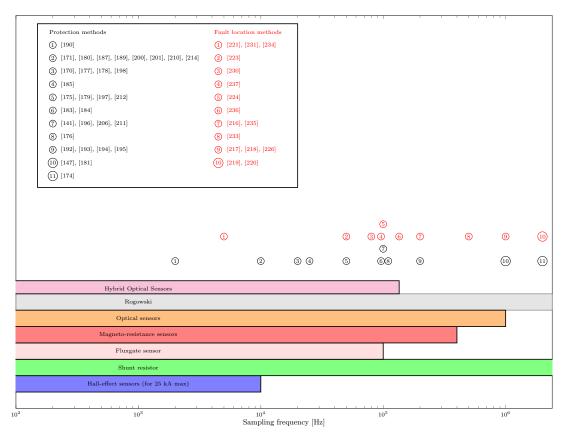

|   | 3.6 | Review | w of Measurement Technologies for HVDC Protection and Location                                                                         | 91 |

|   | 3.7 | Simula | ation Analysis of DC Faults in HVDC Grids                                                                                              | 94 |

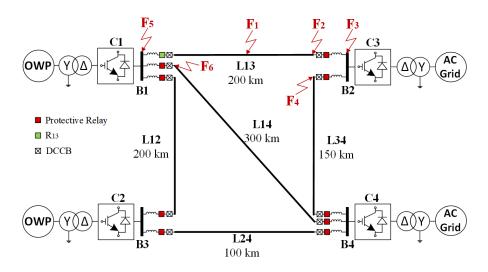

|   |     | 3.7.1  | HVDC Grid Test Network                                                                                                                 | 94 |

|   |     | 3.7.2  | Characterisation of HVDC Grid Fault Response                                                                                           | 95 |

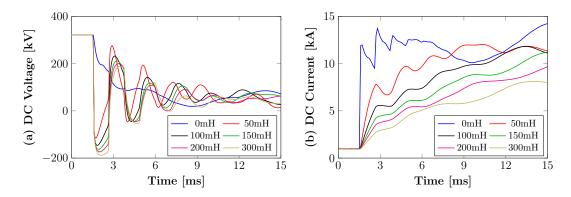

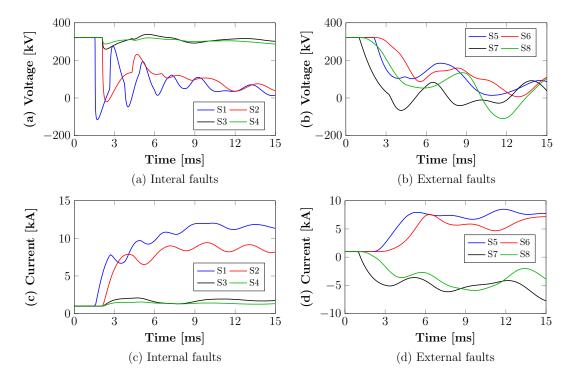

|   |     | 3.7.3  | Impact of Fault Characteristics and Inductive Termination                                                                              | 98 |

|   |     |        |                                                                                                                                        |    |

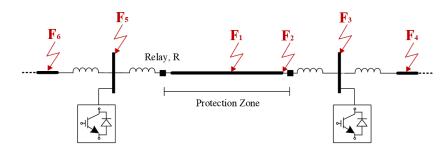

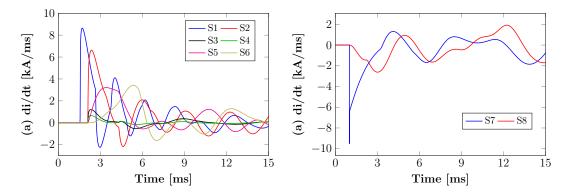

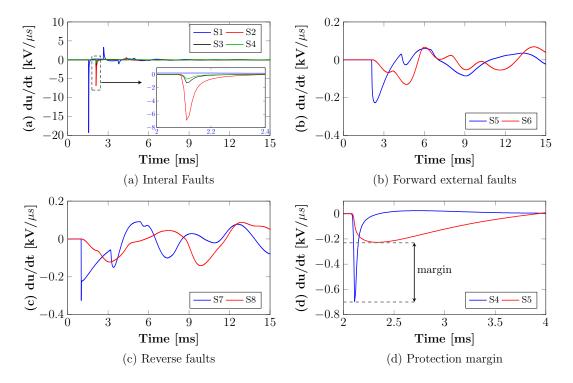

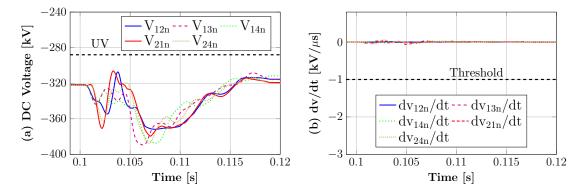

|          |                | 3.7.4    | Analysis of Non-unit Protection                                                                                                               | . 100       |

|----------|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|          | 3.8            | Summ     | ary                                                                                                                                           | . 106       |

| 4        | $\mathbf{Des}$ | ign of ' | Travelling Wave based Non-unit Protection Using Frequen                                                                                       | cy          |

|          | Dor            | nain A   | nalysis                                                                                                                                       | 108         |

|          | 4.1            | Introd   | $uction \ldots \ldots$ | . 109       |

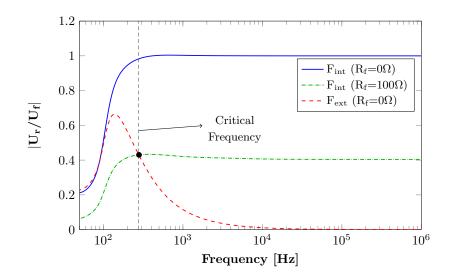

|          | 4.2            | Freque   | ency Domain Analysis                                                                                                                          | . 110       |

|          |                | 4.2.1    | Cable Modelling                                                                                                                               | . 111       |

|          |                | 4.2.2    | Converter Modelling                                                                                                                           | . 111       |

|          |                | 4.2.3    | Transient Voltage Characteristic                                                                                                              | . 112       |

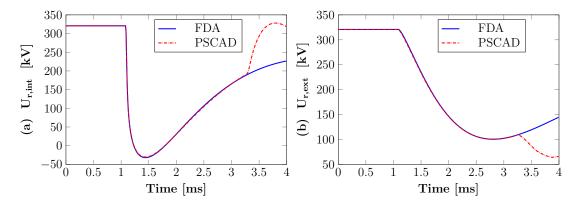

|          |                | 4.2.4    | Validation of Frequency Domain Analysis                                                                                                       | . 115       |

|          |                | 4.2.5    | Methodology for Analysis of Non-unit Protection                                                                                               | . 116       |

|          | 4.3            | Impac    | t of System and Fault Parameters on Transient Voltage Frequency                                                                               |             |

|          |                | Respo    | nse                                                                                                                                           | . 117       |

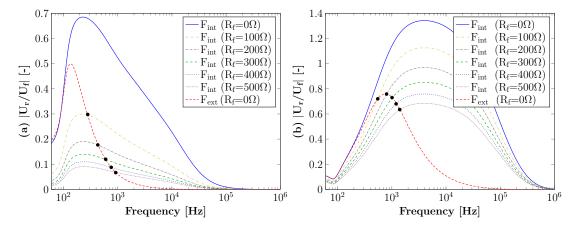

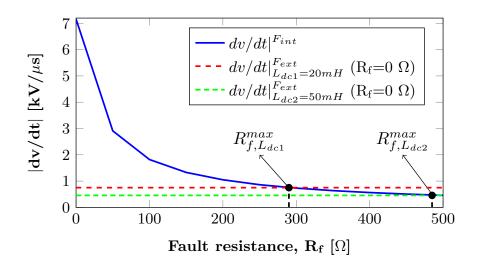

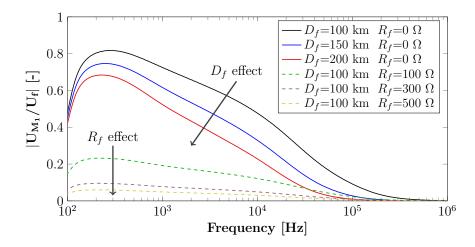

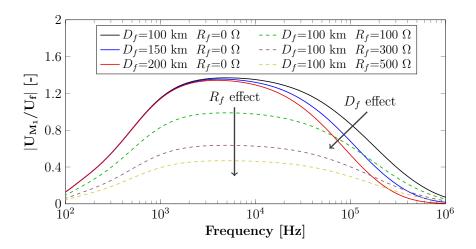

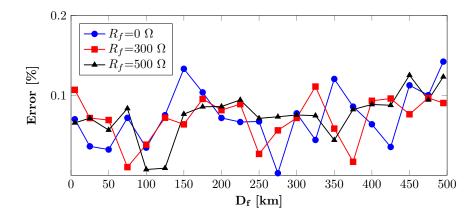

|          |                | 4.3.1    | Fault Resistance                                                                                                                              | . 118       |

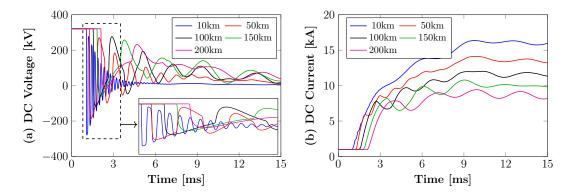

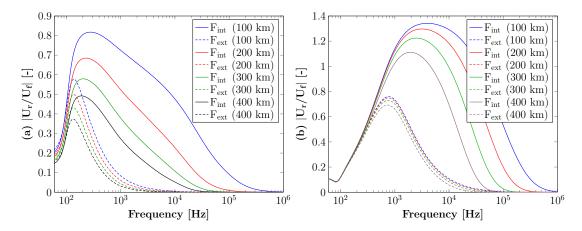

|          |                | 4.3.2    | ${\rm Medium} \ {\rm Length} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                          | . 119       |

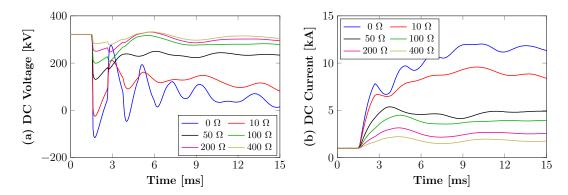

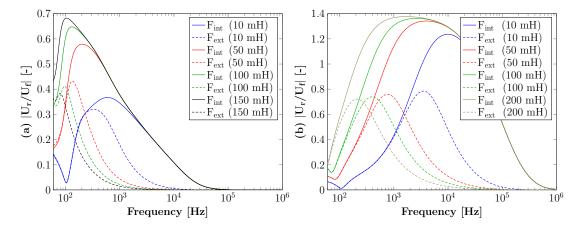

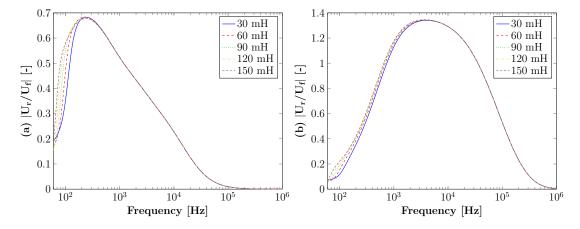

|          |                | 4.3.3    | Series Inductor Size                                                                                                                          | . 120       |

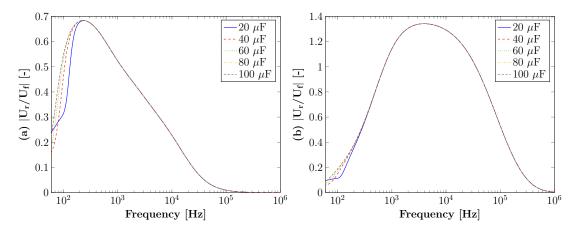

|          |                | 4.3.4    | Arm Inductance and Capacitance                                                                                                                | . 121       |

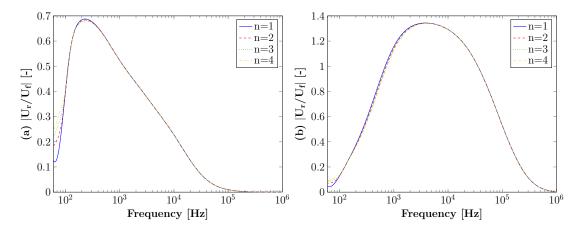

|          |                | 4.3.5    | Number of Feeders                                                                                                                             | . 122       |

|          | 4.4            | Guide    | lines for Non-unit Protection Design                                                                                                          | . 123       |

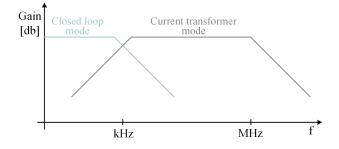

|          |                | 4.4.1    | Sampling Frequency and Filtering Requirements                                                                                                 | . 123       |

|          |                | 4.4.2    | Protection Threshold Determination                                                                                                            | . 124       |

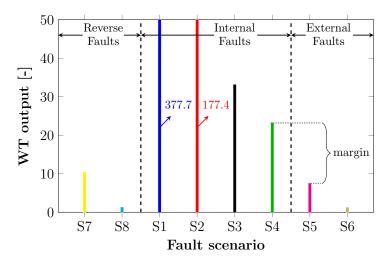

|          |                | 4.4.3    | Protection Margin Improvement                                                                                                                 | . 125       |

|          |                | 4.4.4    | Configuration of Non-unit Protection Algorithms                                                                                               | . 126       |

|          |                | 4.4.5    | Adapta<br>bility and Extensibility of Non-unit Protection $\ . \ . \ .$                                                                       | . 127       |

|          | 4.5            | Summ     | ary                                                                                                                                           | . 128       |

| <b>5</b> | Ana            | alytical | l Design of Wavelet Transform-based Non-unit HVDC Pr                                                                                          | ' <b>0-</b> |

|          | tect           | ion      |                                                                                                                                               | 130         |

|          | 5.1            | Motiv    | ation                                                                                                                                         | . 130       |

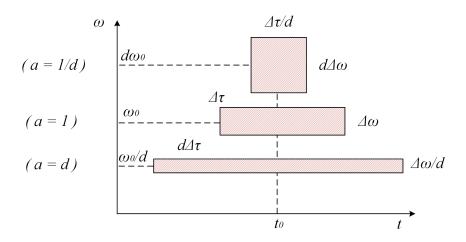

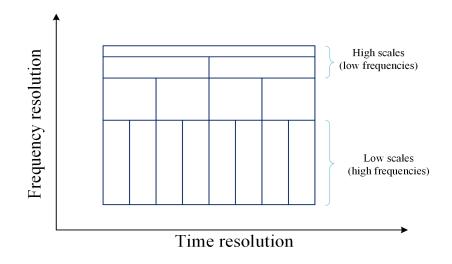

|          | 5.2            | Wavel    | et Transform Theory                                                                                                                           | . 132       |

|          |                | 5.2.1    | Characteristics of Wavelet Transform                                                                                                          | . 134       |

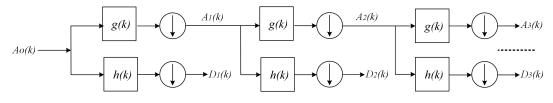

|          |                | 5.2.2    | Discrete Wavelet Transform                                                                                                                    | . 135       |

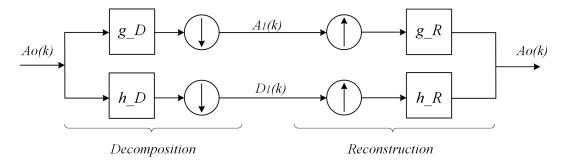

|          |                | 5.2.3    | Wavelet Reconstruction                                                                                                                        | . 137       |

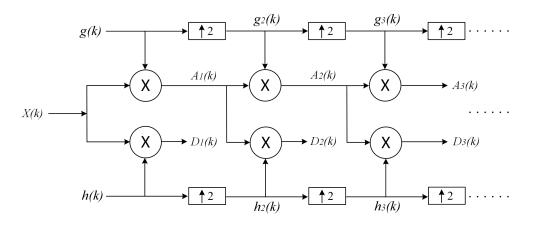

|          |                | 5.2.4    | DWT principles                                                                                                                                | . 138       |

|          |                | 5.2.5    | Stationary Wavelet Transform                                                                                                                  | . 139       |

|          | 5.3            | Analy    | tical Design of WT-based HVDC Protection                                                                                                      |             |

|          |                | Schem    | nes                                                                                                                                           | . 140       |

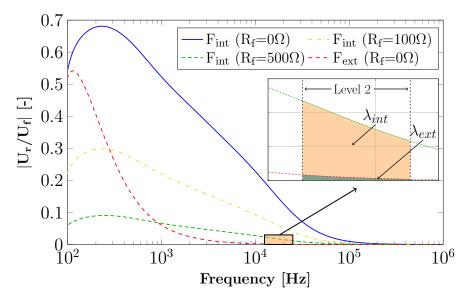

|   |                                                                             | 5.3.1                                                                                                                                | Selection of Decomposition Level                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                             | 5.3.2                                                                                                                                | Threshold Selection $\ldots \ldots 142$                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                             | 5.3.3                                                                                                                                | Wavelet Selection                                                                                                                                                                                                                                                                                                                                                                                                                                        |

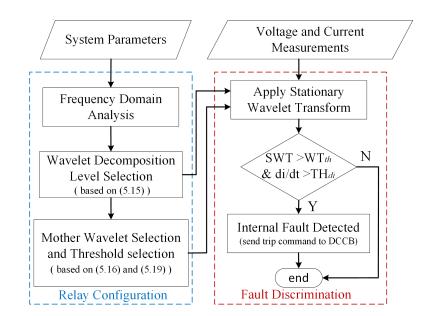

|   |                                                                             | 5.3.4                                                                                                                                | Proposed Protection Scheme                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 5.4                                                                         | Simula                                                                                                                               | ation Studies $\ldots \ldots 148$                                                                                                                                                                                                                                                                                                                             |

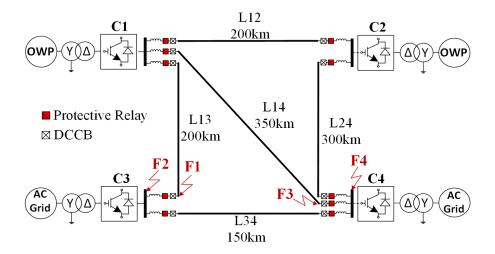

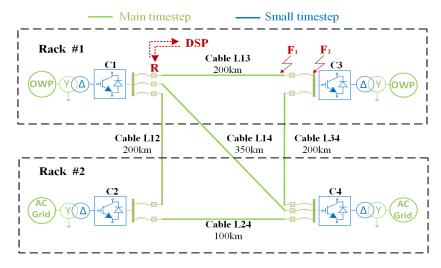

|   |                                                                             | 5.4.1                                                                                                                                | HVDC Grid Test System and Methodology 148                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |                                                                             | 5.4.2                                                                                                                                | Relay Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                      |

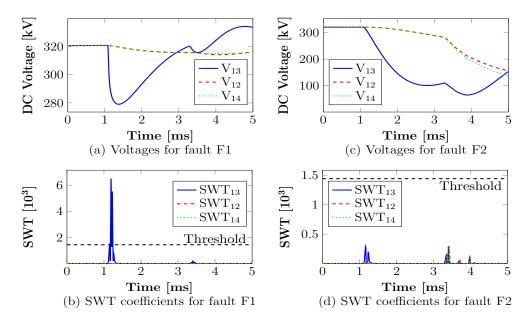

|   |                                                                             | 5.4.3                                                                                                                                | Selectivity of the Proposed Method                                                                                                                                                                                                                                                                                                                                                                                                                       |

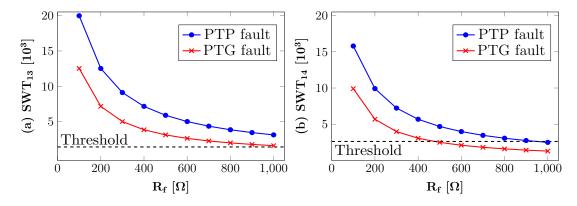

|   |                                                                             | 5.4.4                                                                                                                                | Influence of Fault Resistance                                                                                                                                                                                                                                                                                                                                                                                                                            |

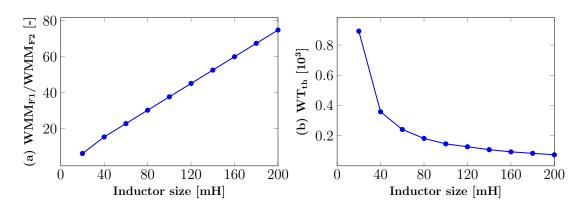

|   |                                                                             | 5.4.5                                                                                                                                | Influence of Inductor Size                                                                                                                                                                                                                                                                                                                                                                                                                               |

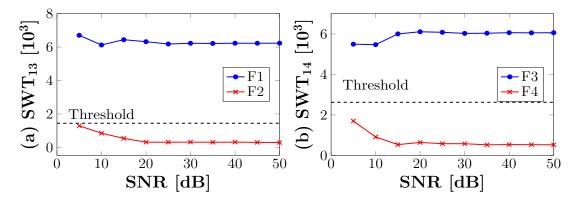

|   |                                                                             | 5.4.6                                                                                                                                | Influence of Noise                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                                             | 5.4.7                                                                                                                                | Influence of Sampling Frequency and Comparison                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                                             | 5.4.8                                                                                                                                | Robustness of the Proposed Method                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 5.5                                                                         | Imple                                                                                                                                | mentation and Validation of Real-time SWT-based Non-unit Pro-                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                             | tection                                                                                                                              | n                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

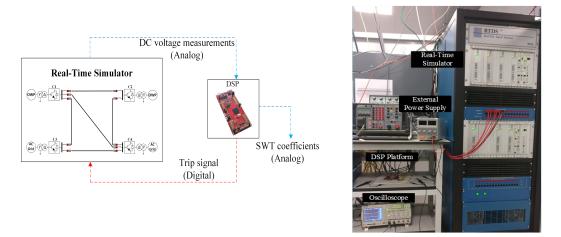

|   |                                                                             | 5.5.1                                                                                                                                | Real-time SWT Implementation                                                                                                                                                                                                                                                                                                                                                                                                                             |

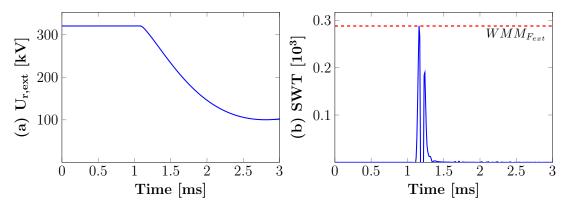

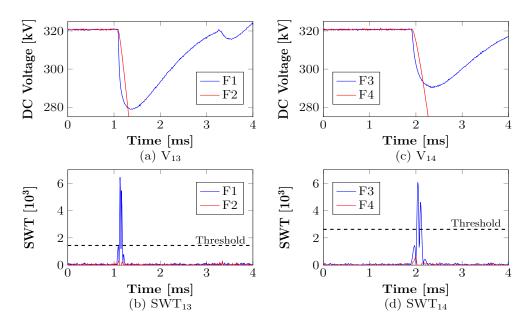

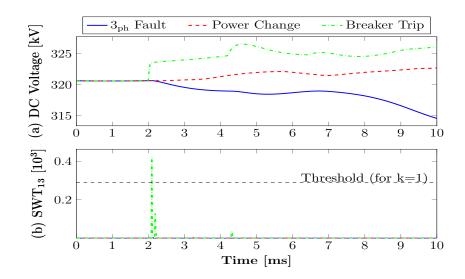

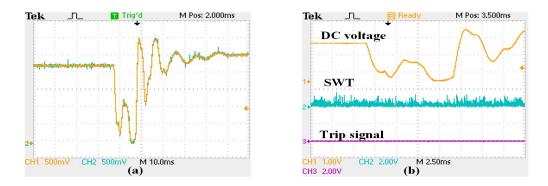

|   |                                                                             | 5.5.2                                                                                                                                | Functional Testing of SWT Implementation                                                                                                                                                                                                                                                                                                                                                                                                                 |

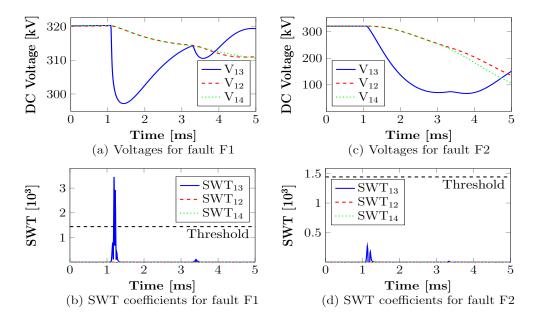

|   |                                                                             | 5.5.3                                                                                                                                | Validation of SWT-based HVDC Grid Non-unit Protection $\ .$ 163                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 5.6                                                                         | Summ                                                                                                                                 | hary                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6 | DC                                                                          | Fault                                                                                                                                | Management Strategy for Continuous Operation of HVDC                                                                                                                                                                                                                                                                                                                                                                                                     |

| U |                                                                             |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                                                             | ns nas                                                                                                                               | ed on Customised Hybrid MMCs 168                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                                                                             |                                                                                                                                      | ed on Customised Hybrid MMCs 168<br>ation 169                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 6.1                                                                         | Motiv                                                                                                                                | ation $\ldots \ldots 169$                                                                                                                                                                                                                                                                                                                       |

|   |                                                                             | Motiv<br>Custo                                                                                                                       | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

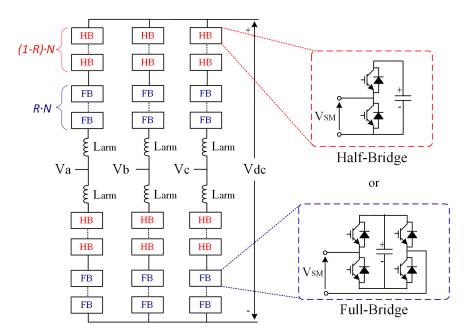

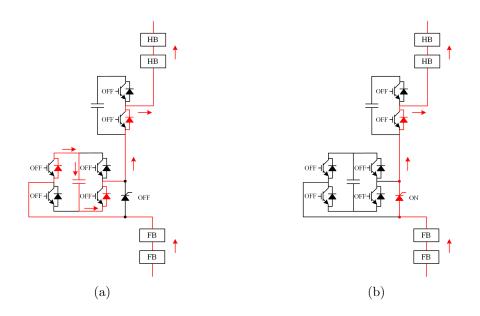

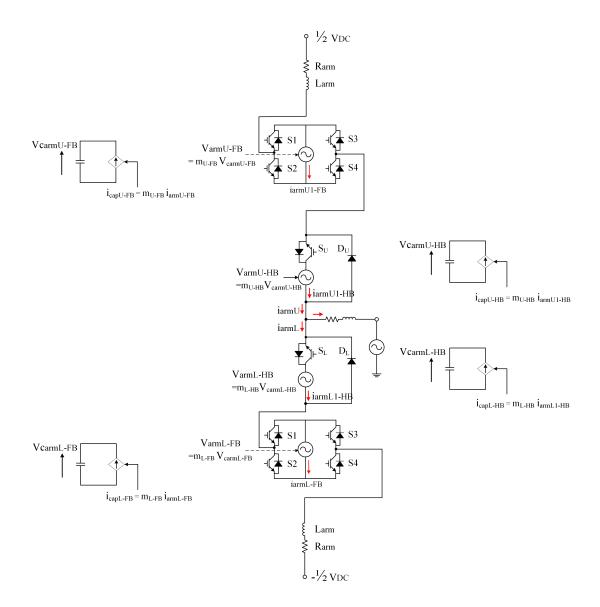

|   | 6.1                                                                         | Motiv<br>Custo<br>6.2.1                                                                                                              | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171                                                                                                                                                                                                                                                                                                                                                                 |

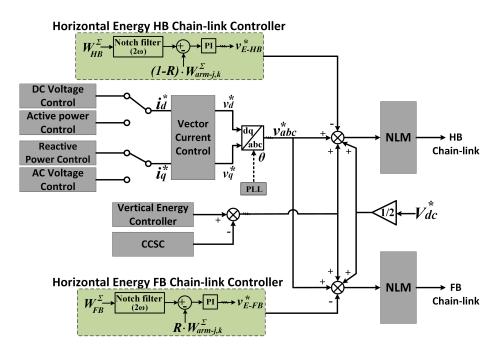

|   | 6.1<br>6.2                                                                  | Motiv<br>Custo<br>6.2.1<br>6.2.2                                                                                                     | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173                                                                                                                                                                                                                                                                                                                                             |

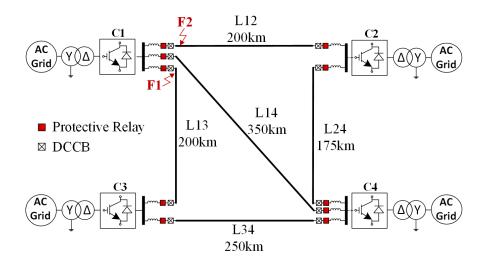

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                               | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDO                                                                                             | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology175                                                                                                                                                                                                                                                                                                                           |

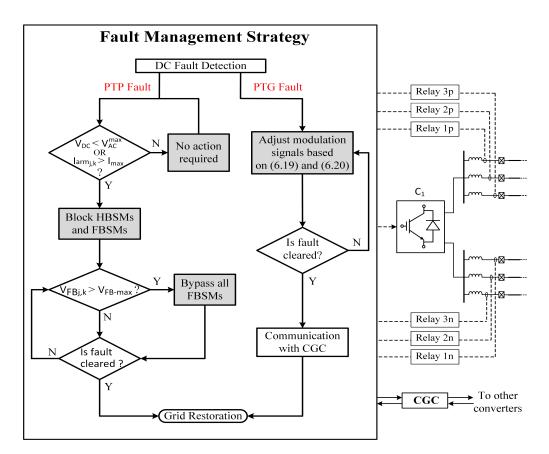

|   | 6.1<br>6.2                                                                  | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDO<br>DC Fa                                                                                    | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology175ault Management Strategy176                                                                                                                                                                                                                                                                                                |

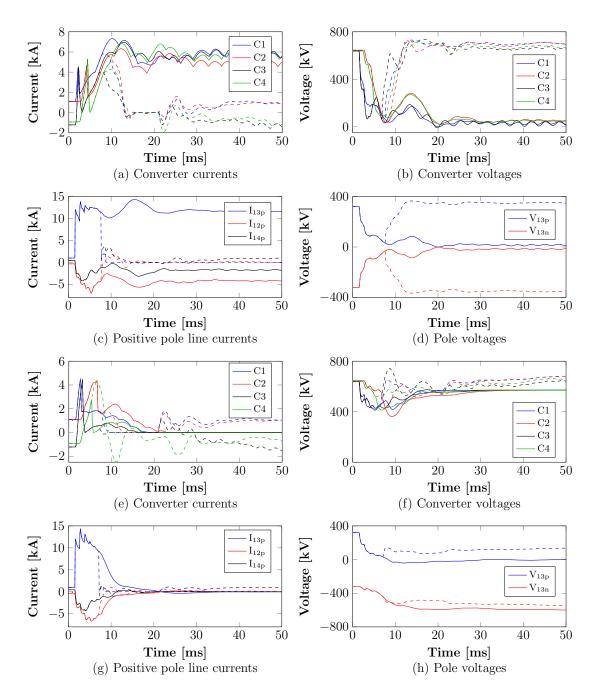

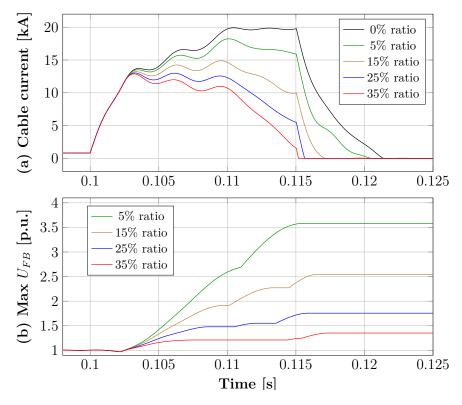

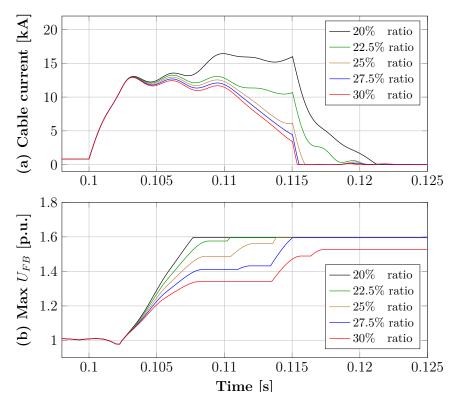

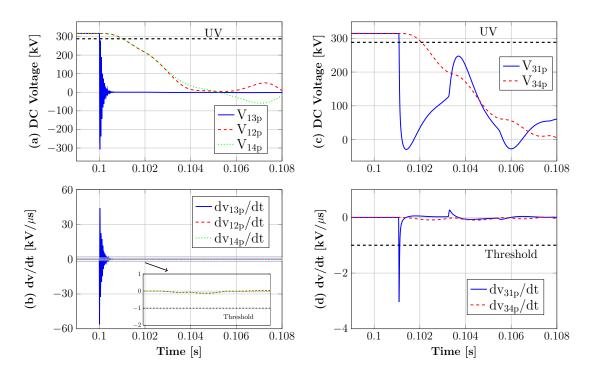

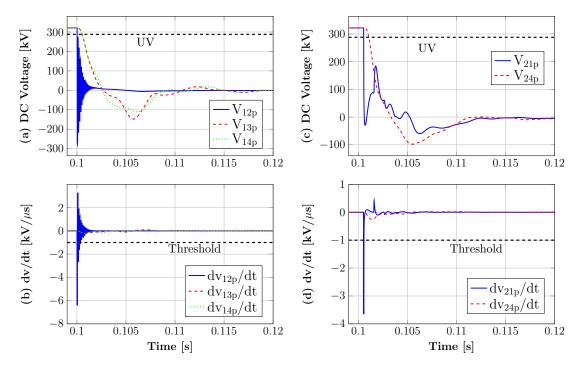

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                               | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDC<br>DC Fa<br>6.4.1                                                                           | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology175ault Management Strategy176CH-MMC Behaviour During Pole-to-pole Faults176                                                                                                                                                                                                                                                  |

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                               | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDC<br>DC Fa<br>6.4.1<br>6.4.2                                                                  | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology175ault Management Strategy176CH-MMC Behaviour During Pole-to-ground Faults181                                                                                                                                                                                                                                                |

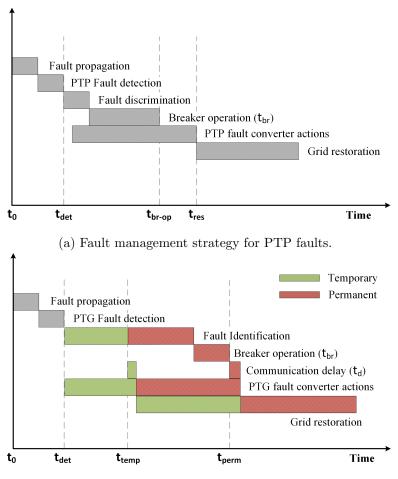

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                   | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDO<br>DC Fa<br>6.4.1<br>6.4.2<br>6.4.3                                                         | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology175ault Management Strategy176CH-MMC Behaviour During Pole-to-pole Faults176CH-MMC Behaviour During Pole-to-ground Faults181Proposed DC Fault Management Strategy for HVDC Grids183                                                                                                                                           |

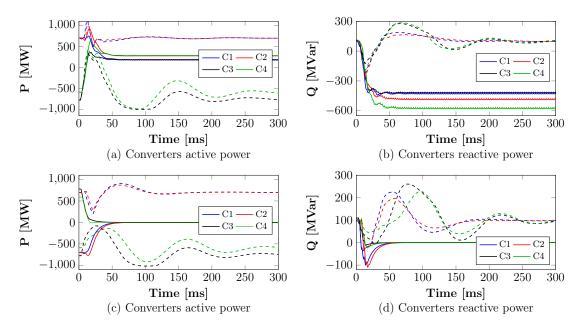

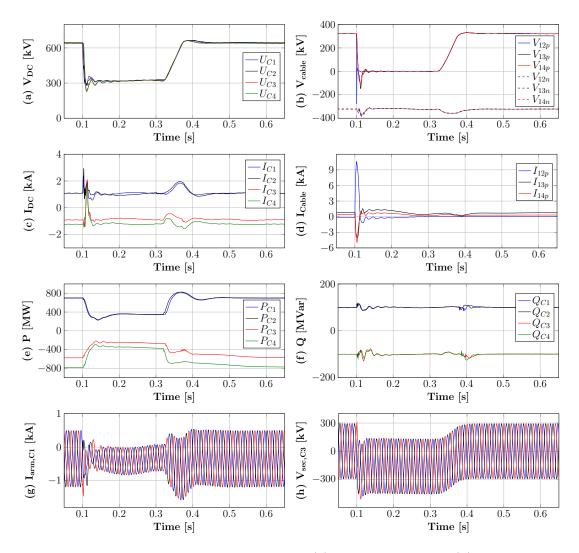

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                               | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDC<br>DC Fa<br>6.4.1<br>6.4.2<br>6.4.3<br>Perfor                                               | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology173C Grid Topology175ault Management Strategy176CH-MMC Behaviour During Pole-to-pole Faults176CH-MMC Behaviour During Pole-to-ground Faults181Proposed DC Fault Management Strategy183mance of DC Fault Management Strategy187                                                                                                |

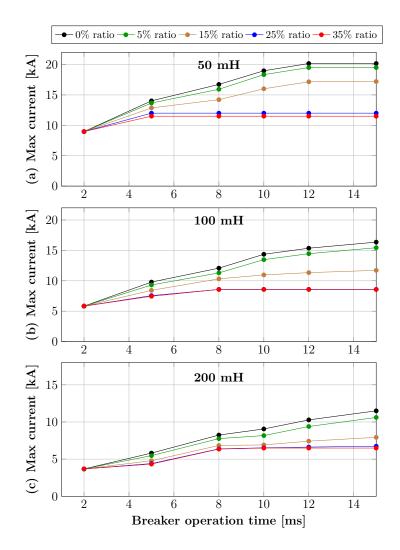

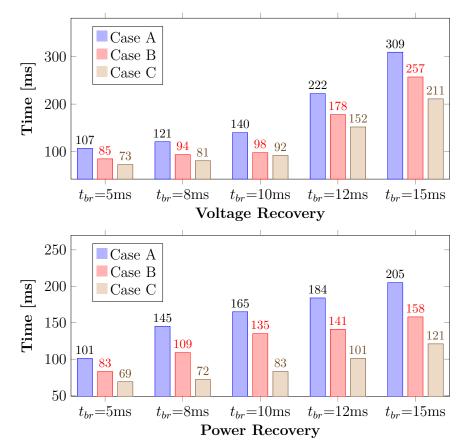

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                   | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDC<br>DC Fa<br>6.4.1<br>6.4.2<br>6.4.3<br>Perfor<br>6.5.1                                      | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology175cult Management Strategy176CH-MMC Behaviour During Pole-to-pole Faults176CH-MMC Behaviour During Pole-to-ground Faults181Proposed DC Fault Management Strategy183mance of DC Fault Management Strategy187Impact of Series Inductor187                                                                                      |

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                   | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDO<br>DC Fa<br>6.4.1<br>6.4.2<br>6.4.3<br>Perfor<br>6.5.1<br>6.5.2                             | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology175ault Management Strategy176CH-MMC Behaviour During Pole-to-pole Faults176CH-MMC Behaviour During Pole-to-ground Faults181Proposed DC Fault Management Strategy183mance of DC Fault Management Strategy187Impact of Series Inductor187Fault Management Strategy Evaluation for Pole-to-pole Faults189                       |

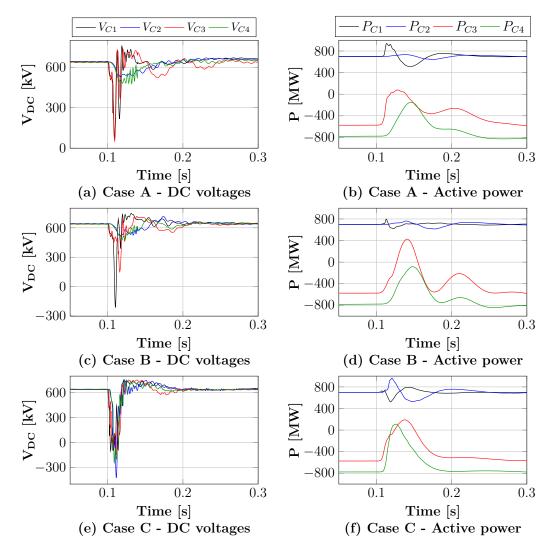

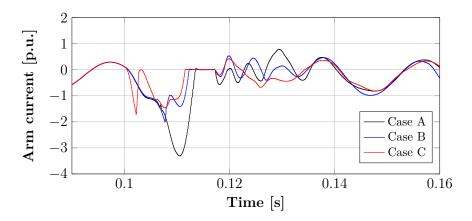

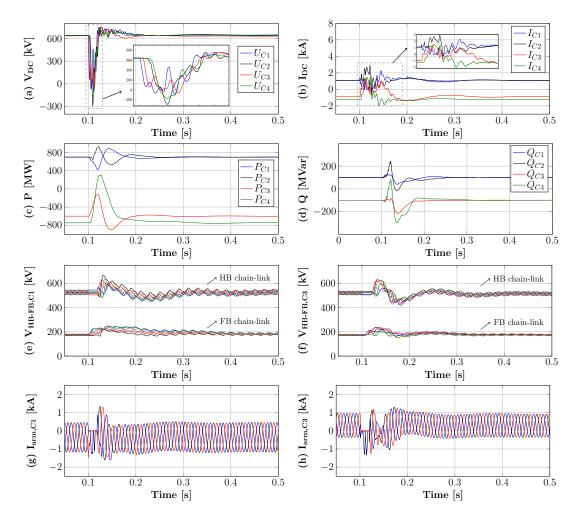

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                   | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDC<br>DC Fa<br>6.4.1<br>6.4.2<br>6.4.3<br>Perfor<br>6.5.1<br>6.5.2<br>6.5.3                    | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology175ault Management Strategy176CH-MMC Behaviour During Pole-to-pole Faults181Proposed DC Fault Management Strategy183mance of DC Fault Management Strategy187Impact of Series Inductor187Fault Management Strategy Evaluation for Pole-to-pole Faults189Example Pole-to-pole Fault193                                          |

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                   | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDC<br>DC Fa<br>6.4.1<br>6.4.2<br>6.4.3<br>Perfor<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4           | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology175ault Management Strategy176CH-MMC Behaviour During Pole-to-pole Faults176CH-MMC Behaviour During Pole-to-ground Faults181Proposed DC Fault Management Strategy187Impact of Series Inductor187Fault Management Strategy Evaluation for Pole-to-pole Faults189Example Pole-to-ground Fault193Example Pole-to-ground Fault196 |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul> | Motiv<br>Custo<br>6.2.1<br>6.2.2<br>HVDO<br>DC Fa<br>6.4.1<br>6.4.2<br>6.4.3<br>Perfor<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>Discus | ation169mised Hybrid Modular Multilevel Converter171Fundamentals and Circuit Topology171Converter Control173C Grid Topology175ault Management Strategy176CH-MMC Behaviour During Pole-to-pole Faults181Proposed DC Fault Management Strategy183mance of DC Fault Management Strategy187Impact of Series Inductor187Fault Management Strategy Evaluation for Pole-to-pole Faults189Example Pole-to-pole Fault193                                          |

| 7 | Sing          | gle-end        | led Fault Location for HVDC Grids Embedding High-speed         |     |

|---|---------------|----------------|----------------------------------------------------------------|-----|

|   | $\mathbf{DC}$ | $\mathbf{CBs}$ |                                                                | 202 |

|   | 7.1           | Motiv          | ation $\ldots$                                                 | 202 |

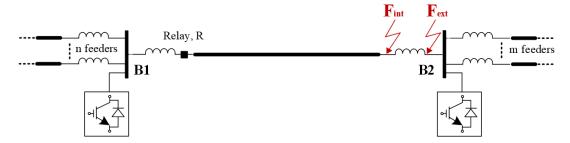

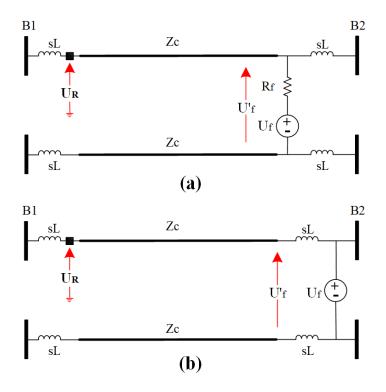

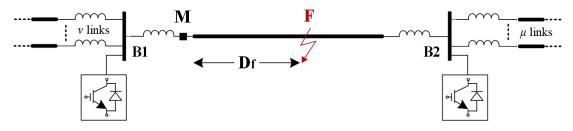

|   | 7.2           | Freque         | ency Domain Profile of Transient Voltage                       | 203 |

|   |               | 7.2.1          | Transient Voltage Characteristic Representation                | 203 |

|   |               | 7.2.2          | Frequency Response of Voltage Transfer Function                | 206 |

|   | 7.3           | Propo          | sed Fault Location Method                                      | 207 |

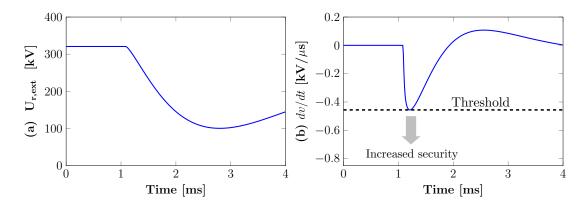

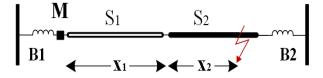

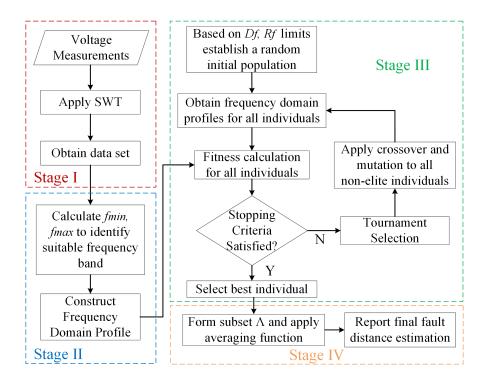

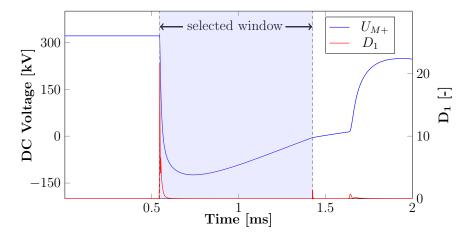

|   |               | 7.3.1          | Stage I: Data Window Determination                             | 207 |

|   |               | 7.3.2          | Stage II: Frequency Domain Profile Construction                | 209 |

|   |               | 7.3.3          | Stage III: Genetic Algorithm                                   | 211 |

|   |               | 7.3.4          | Stage IV: Fault Location Estimation                            | 215 |

|   | 7.4           | Simula         | ation Results                                                  | 216 |

|   |               | 7.4.1          | HVDC Grid Test System and Methodology                          | 216 |

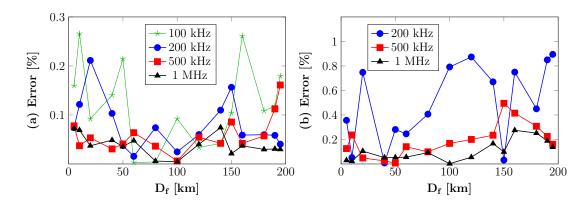

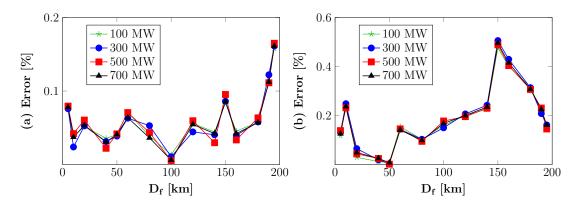

|   |               | 7.4.2          | Fault Location Results for Different Transmission Line Media   | 217 |

|   |               | 7.4.3          | Fault Location Results for Greater Line Lengths                | 221 |

|   |               | 7.4.4          | Fault Location Results for a Three-segment Line                | 221 |

|   |               | 7.4.5          | Impact of Sampling Frequency                                   | 222 |

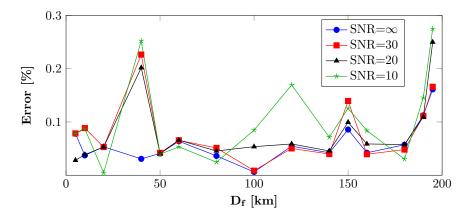

|   |               | 7.4.6          | Impact of Noisy Measurements                                   | 223 |

|   |               | 7.4.7          | Impact of Transmission Line Loading                            | 224 |

|   |               | 7.4.8          | Comparison with Existing Methods                               | 225 |

|   | 7.5           | Summ           | nary                                                           | 227 |

| 8 | Cor           | nclusio        | ns and Future Research                                         | 228 |

|   | 8.1           | Concl          | usions                                                         | 229 |

|   |               | 8.1.1          | Identifying the Capabilities of Existing Measuring Instruments |     |

|   |               |                | for HVDC Protection and Location Applications                  | 229 |

|   |               | 8.1.2          | Analytical Design and Development of Generally Applicable and  |     |

|   |               |                | Optimised Non-Unit Protection Algorithms                       | 229 |

|   |               | 8.1.3          | Fault Management Strategy for Improving the Technical and Eco- |     |

|   |               |                | nomical Feasibility of HVDC Grids                              | 232 |

|   |               | 8.1.4          | Accurate Fault Location Method for HVDC Grids with Minimal     |     |

|   |               |                | Time Window Requirements                                       | 234 |

|   | 8.2           | Future         | e Research                                                     | 236 |

|   |               | 8.2.1          | Further Assessment of Sampling Frequency Requirements for HVDC | ;   |

|   |               |                | Grid Protection and Location                                   | 236 |

|   |               | 8.2.2          | Extending Frequency Domain Analysis                            | 236 |

|   |               | 8.2.3          | Development of Back-up Protection Measures                     | 237 |

|   |               | 8.2.4          | Investigation of Fault Location Under Non-optimal Conditions . | 237 |

|   |               |                |                                                                |     |

| References                                     | 238 |

|------------------------------------------------|-----|

| Appendices                                     | 265 |

| Appendix A Equivalent Converter Models for FDA | 266 |

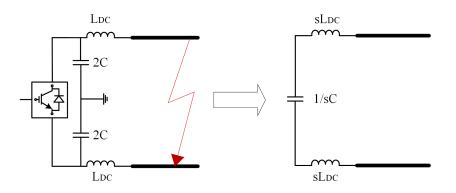

| A.1 Equivalent Model of Two-Level Converter    | 266 |

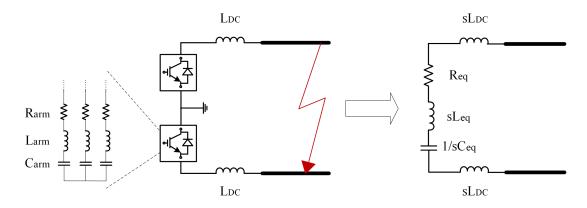

| A.2 Equivalent Model of MMCs                   | 267 |

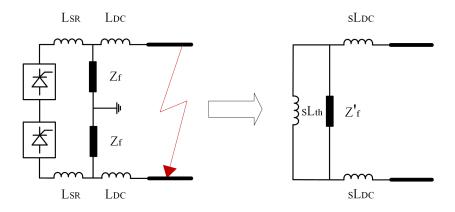

| A.3 Equivalent Model of LCCs                   | 268 |

| Appendix B Average Modelling of the CH-MMC     | 269 |

# List of Figures

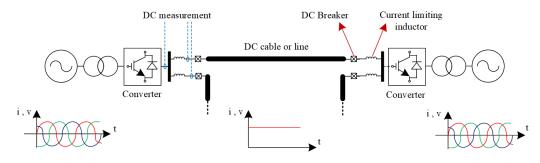

| Typical structure and equipment of HVDC grids                                 | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

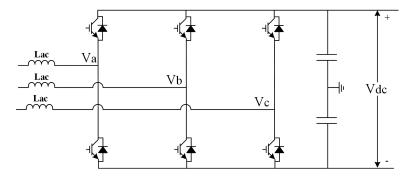

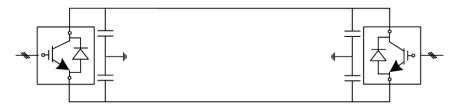

| Classic two-level converter.                                                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

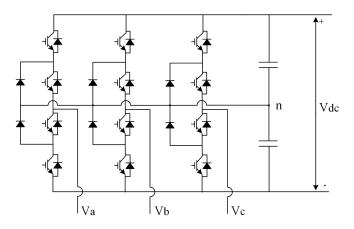

| A typical three-level neutral-point clamped converter                         | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

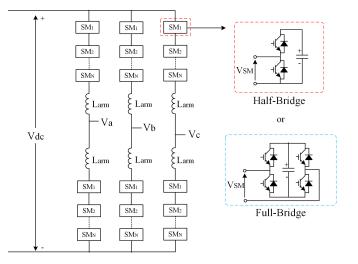

| Three phase modular multilevel converter with HB or FB sub-modules.           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

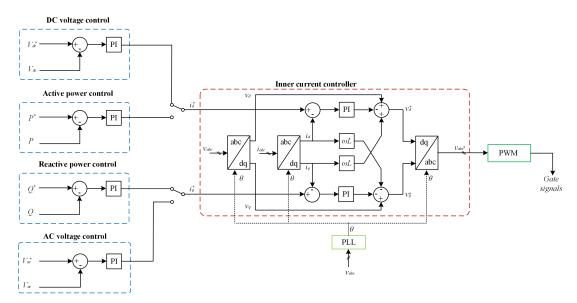

| Current vector control for two-level converter (grid-following mode). $\ .$ . | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

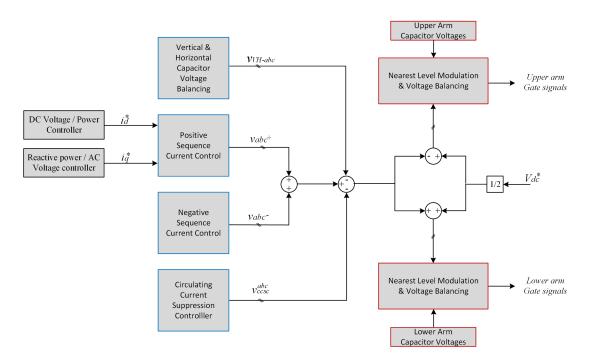

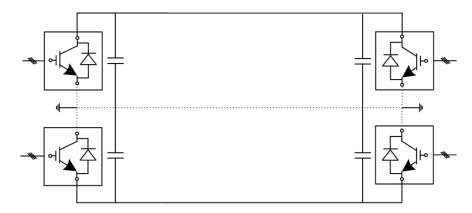

| Upper and lower level control of HB-MMC                                       | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

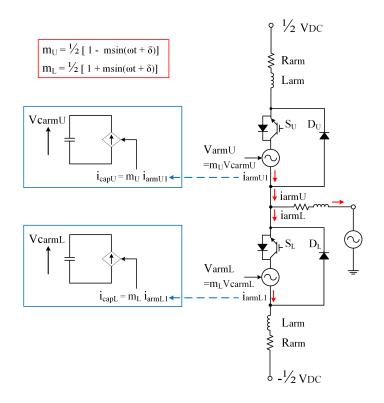

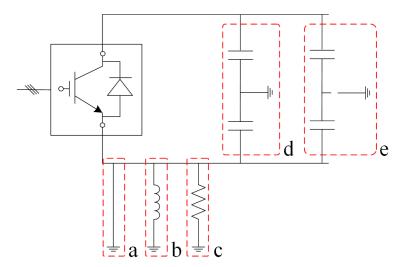

| Illustration of one phase of the HB-MMC average model                         | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Asymmetrical monopolar configuration.                                         | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Symmetrical monopolar configuration.                                          | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bipolar configuration.                                                        | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Grounding options                                                             | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

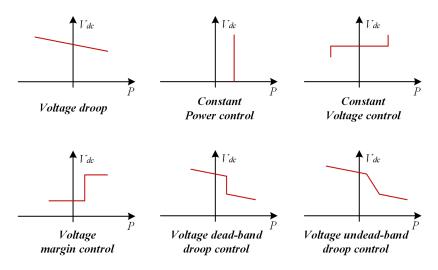

| Basic converter control strategies                                            | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

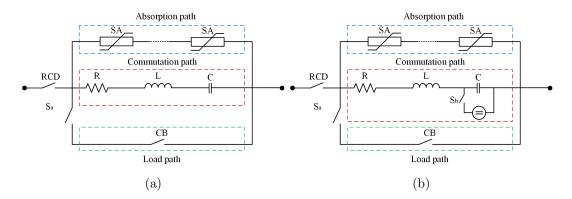

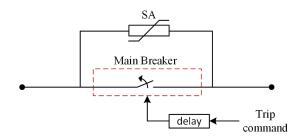

| a) Passive and b) Active Mechanical DC breakers                               | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

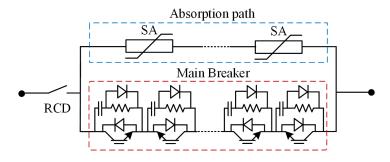

| Solid-state DC breaker.                                                       | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Typical hybrid HVDC breaker.                                                  | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

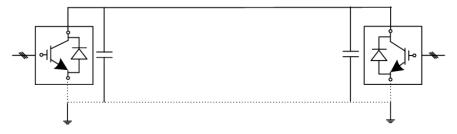

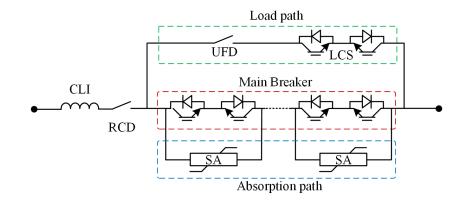

| Simplified model for HV DCCBs                                                 | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Transmission line models                                                      | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

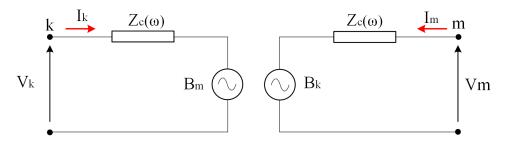

| Bergeron model.                                                               | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

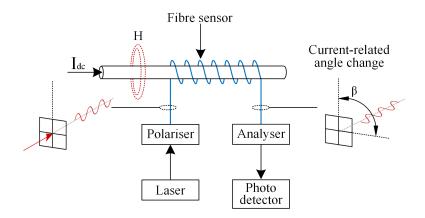

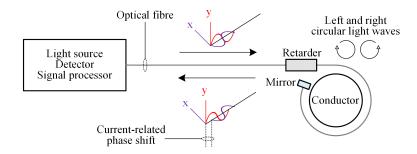

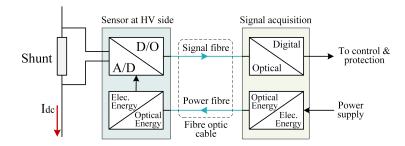

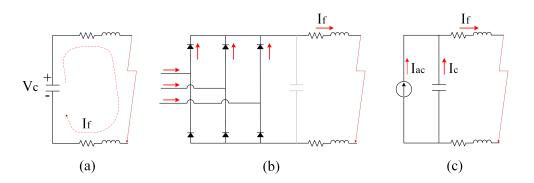

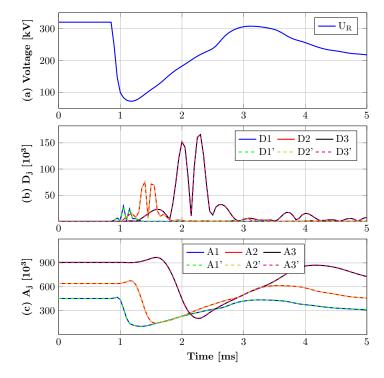

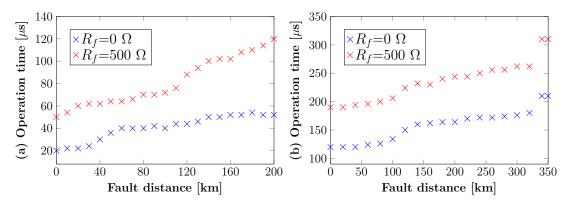

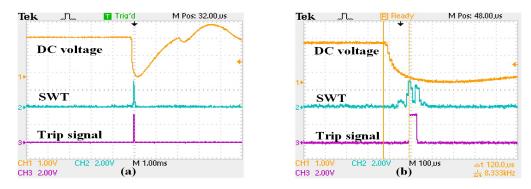

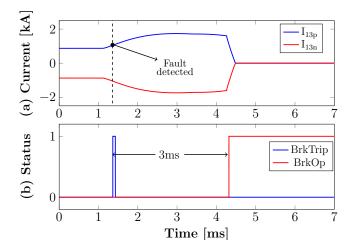

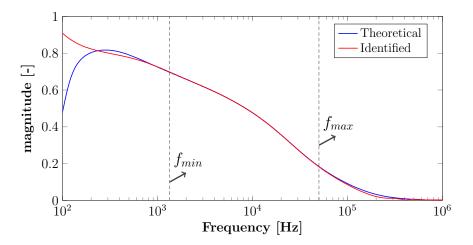

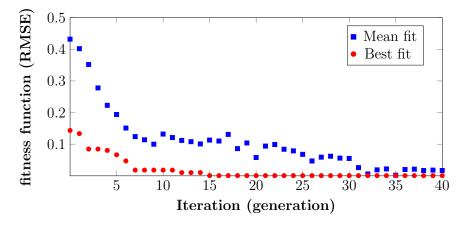

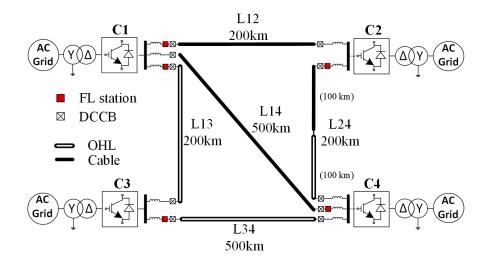

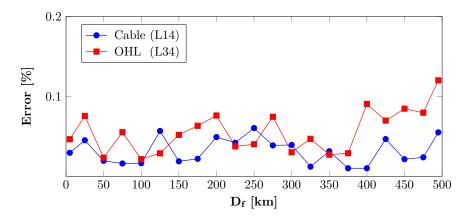

| Multi-conductor transmission system.                                          | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |