# University of Strathclyde Department of Electronics and Electrical Engineering

# Design of Module Level Converters in Photovoltaic Power Systems

Yachao Wang

A thesis presented in fulfilment of the requirements for the Degree of Doctor of Philosophy

January 2021

This thesis is the result of the author's original research. It has been composed by the

author and has not been previously submitted for examination which has led to the

award of a degree.

The copyright of this thesis belongs to the author under the terms of the United

Kingdom Copyright Acts as qualified by University of Strathclyde Regulation 3.50.

Due acknowledgement must always be made of the use of any material contained in,

or derived from, this thesis.

Signed: Yachao Wang

Date: 10/1/2021

# Acknowledgement

I want to express my sincere gratitude to my supervisors Prof. Barry Williams and Dr. Derrick Holliday for their constructive supervision and continuous support. Special thanks to Dr. Ahmed Darwish for his invaluable suggestions based on his profound knowledge.

Thanks to every PEDEC members for all the fruitful academic discussions and team building activities.

Deepest love goes to my family for their unconditional support; and I want to extend the best wishes for their health and happiness.

# **Abstract**

The application of distributed maximum power point tracking (DMPPT) technology in solar photovoltaic (PV) systems is a hot topic in industry and academia. In the PV industry, grid integrated power systems are mainstream. The main objective for PV system design is to increase energy conversion efficiency and decrease the levelized cost of electricity of PV generators.

This thesis firstly presents an extensive review of state-of-the-art PV technologies. With focus on grid integrated PV systems research, various aspects covered include PV materials, conventional full power processing DMPPT architectures, main MPPT techniques, and traditional partial power processing DMPPT architectures.

The main restrictions to applying traditional DMPPT architectures in large power systems are discussed. A parallel connected partial power processing DMPPT architecture is proposed aiming to overcome existing restrictions. With flexible 'plugand-play' functionality, the proposed architecture can be readily expanded to supply a downstream inverter stage or dc network. By adopting smaller module integrated converters, the proposed approach provides a possible efficiency improvement and cost reduction. The requirements for possible converter candidates and control strategies are analysed. One representative circuit scheme is presented as an example to verify the feasibility of the design. An electromagnetic transient model is built for different power scale PV systems to verify the DMPPT feasibility of the evaluated architecture in a large-scale PV power system.

Voltage boosting ability is widely needed for converters in DMPPT applications. Impedance source converters (ISCs) are the main converter types with step-up ability. However, these converters have a general problem of low order distortion when applied in dc-ac applications. To solve this problem, a generic plug-in repetitive control strategy for a four-switch three-phase ISC type inverter configuration is developed. Simulation and experimental results confirm that this control strategy is suitable for many ISC converters.

# **Table of Contents**

| CHAPTER 1     | Introduction                                                   | 1    |

|---------------|----------------------------------------------------------------|------|

| 1.1           | Background and Motivation                                      | 2    |

| 1.2           | Photovoltaic Technologies                                      | 3    |

| 1.3           | Classification of Grid Connected PV Systems                    | 6    |

| 1.4           | Main Barriers and Research Objectives                          | 10   |

| 1.5           | Thesis Outline                                                 | 13   |

| 1.6           | References                                                     | 15   |

| CHAPTER 2     | Review of Module Integrated Converters for Full Po             | wei  |

| Processing DM | IPPT Architectures                                             | 19   |

| 2.1           | Background                                                     | 20   |

| 2.2           | Standards and requirements for grid-connected PV systems       | 22   |

| 2.3           | Parallel connected module integrated inverters                 | 25   |

| 2.3.1         | Power decoupling requirements for single phase PV inverter     | 26   |

| 2.3.2         | Isolated topologies with different power decoupling techniques | . 29 |

| 2.3.3         | Transformer-less step-up topologies                            | 37   |

| 2.4           | Series connected module level PV system                        | 42   |

| 2.4.1         | Cascaded DC-DC converter                                       | 42   |

| 2.4.2         | Cascaded DC-AC converter                                       | 45   |

| 2.5           | Review of Impedance Source Converters                          | 46   |

| 2.5.1         | Operation principles of typical HOWO-ISC topologies            | 46   |

| 2.5.2         | Constraints of HOWO-ISCs                                       | 48   |

| 2.6           | Summary                                                        | 50   |

| References.   |                                                                | 51   |

| CHAPTER 3.    |                                                                | 58   |

| 3.1                     | Background                                                                 |

|-------------------------|----------------------------------------------------------------------------|

| 3.2                     | Mismatch Loss for PV Modules 60                                            |

| 3.2.1                   | PV Cell Characteristics 60                                                 |

| 3.2.2                   | PV Module Connection Type and Mismatch Loss Mechanism 64                   |

| 3.3                     | MPPT Strategies for Mismatched Conditions                                  |

| 3.4                     | Partial Power Processing DMPPT Implementation                              |

| 3.4.1                   | Current Balancing Differential Converters76                                |

| 3.4.2                   | Voltage Balancing Differential Converters                                  |

| 3.5                     | Summary                                                                    |

| References.             | 83                                                                         |

| CHAPTER 4 Power Process | Proposed Parallel Connected DMPPT Architecture with Partial ing Converters |

| 4.1                     | Background                                                                 |

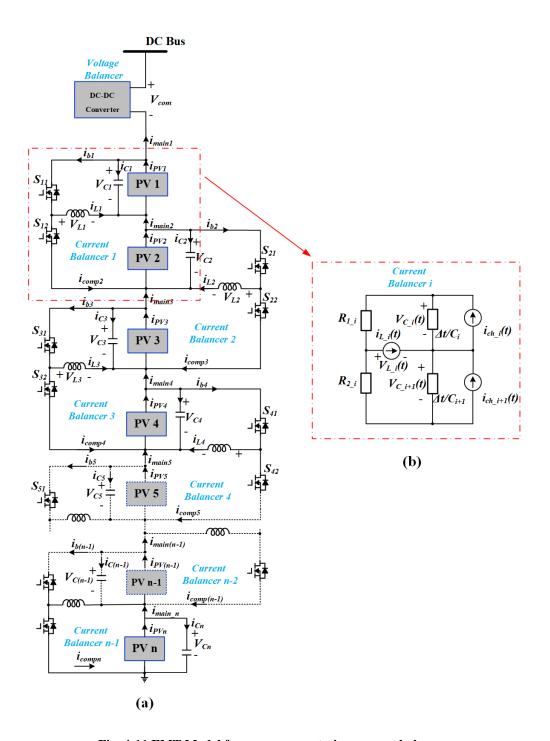

| 4.2                     | Implementation of the Proposed Architecture90                              |

| 4.2.1                   | Conceptual Illustration of the proposed architecture90                     |

| 4.2.2                   | Circuit Realization for Voltage Balancers                                  |

| 4.2.3                   | Circuit Realization for Current Balancers96                                |

| 4.2.4                   | A Representative Circuit Schematic                                         |

| 4.3                     | EMT Modelling for a Large-Scale PV Power System 102                        |

| 4.3.1                   | Comparison of the different modelling techniques                           |

| 4.3.2                   | An Efficient EMT model                                                     |

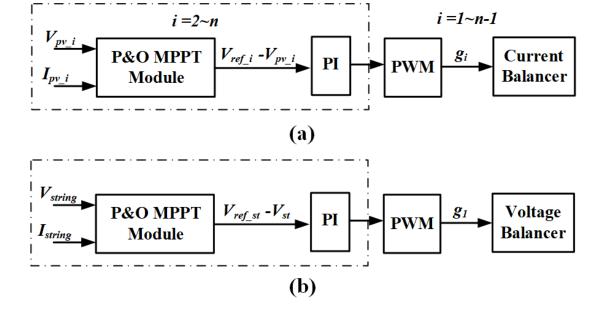

| 4.3.3                   | MPPT Implementation and Control Strategy                                   |

| 4.4                     | Simulation Verification and Performance Evaluation                         |

| 4.4.1<br>Balancer.      | A Simple Two-Module PV System with Bipolar Output Voltage                  |

| 4.4.2                   | Single PV String Power System Modelling                                    |

| 4.4.3          | Multi-String Multi-Inverter PV Power System            | 126      |

|----------------|--------------------------------------------------------|----------|

| 4.5            | Summary                                                | 128      |

| 4.6            | References                                             | 129      |

| CHAPTER 5      | Plug-in Repetitive Control Strategy for Impedance      | e Source |

| Converters: an | n Islanded Mode Case Study                             | 133      |

| 5.1            | Background                                             | 134      |

| 5.2            | Operation of the Four-Switch Three-Phase SQZS Inverter | 136      |

| 5.2.1          | Operation Principle of the FSTP Inverter               | 136      |

| 5.2.2          | Modelling of the SQZS converter                        | 137      |

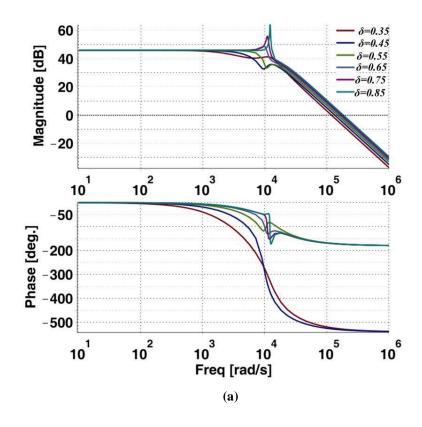

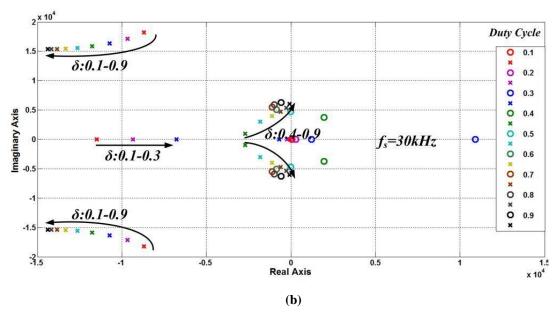

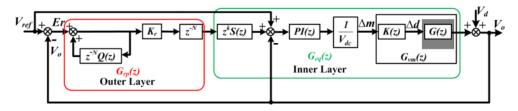

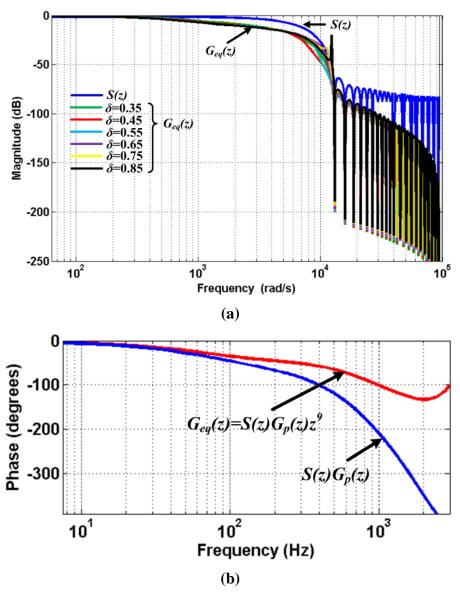

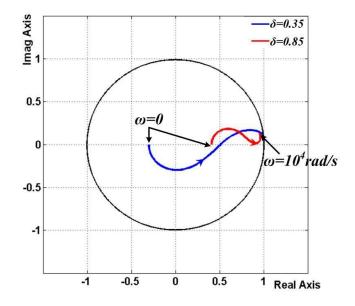

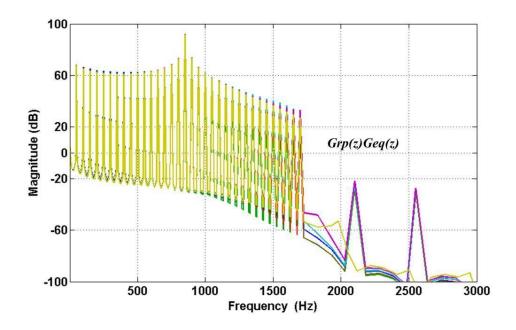

| 5.3            | Design of Plug-in Repetitive Controller                | 142      |

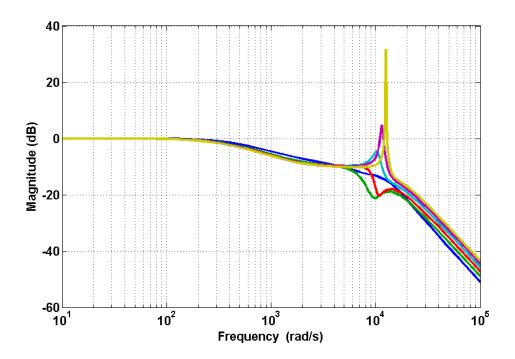

| 5.3.1          | Compensation Network for Modifying the Converter Plan  | t 143    |

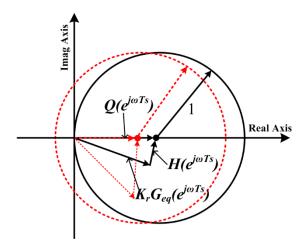

| 5.3.2          | Internal Model Design for Plug-in Repetitive Control   | 146      |

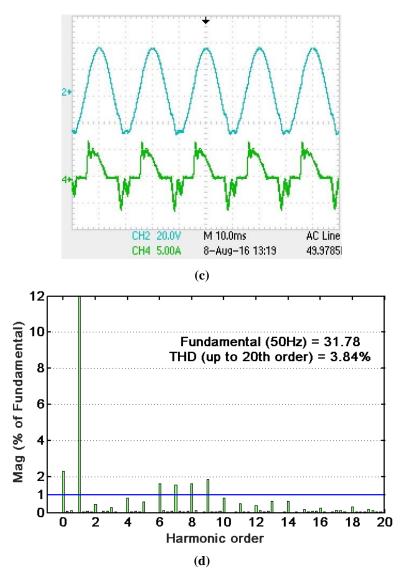

| 5.4            | Simulation and Experiment Verification                 | 150      |

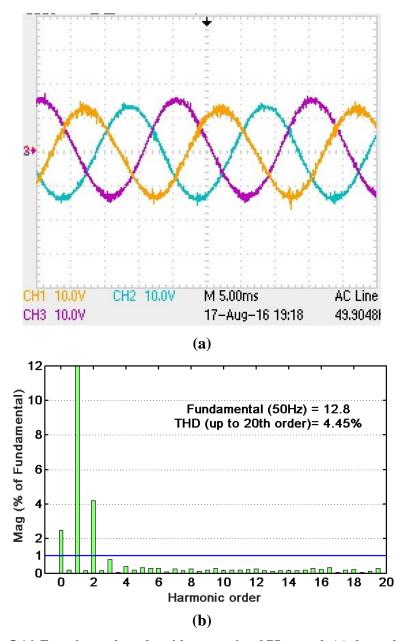

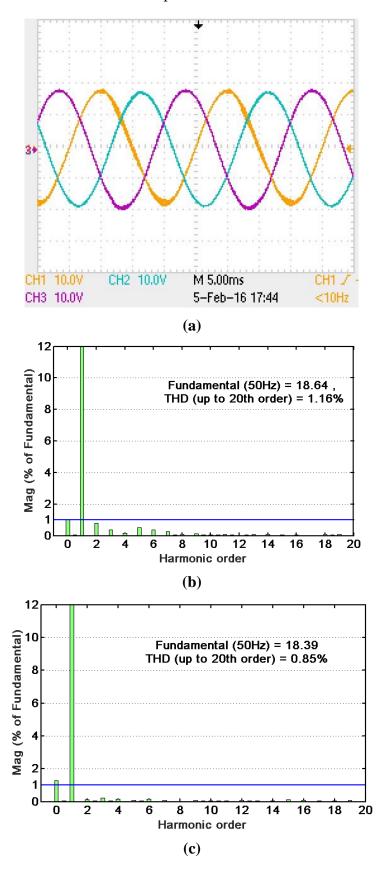

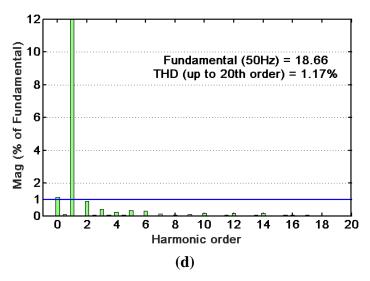

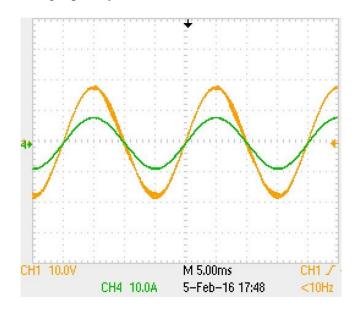

| 5.4.1          | Simulation Tests                                       | 150      |

| 5.4.2          | Experimental Results                                   | 156      |

| 5.5            | Summary                                                | 163      |

| References     |                                                        | 164      |

| CHAPTER 6      | Conclusions                                            | 166      |

| 6.1            | General Summary                                        | 166      |

| 6.2            | Author's contribution and future research plan         | 168      |

| Appendices     |                                                        | 170      |

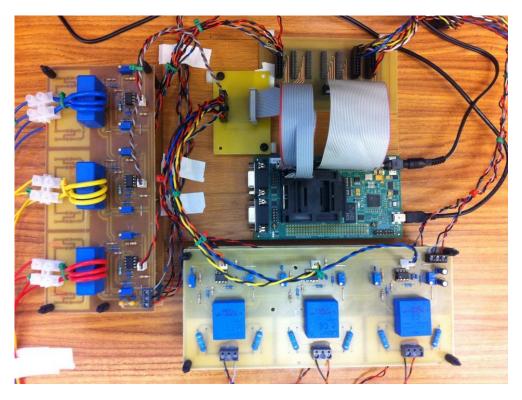

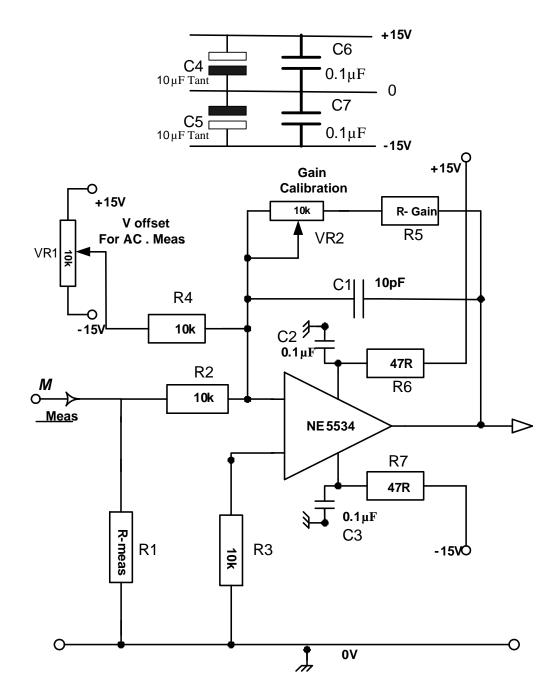

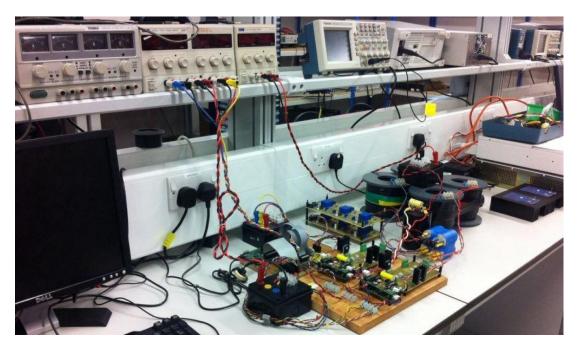

| Appendix A.    | Test Rig Details for FSTP-SQZS Inverter                | 170      |

| I. The D       | OSP control system                                     | 170      |

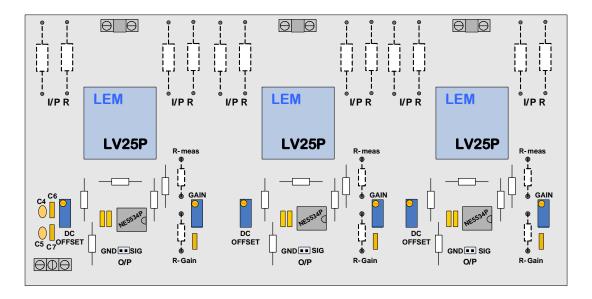

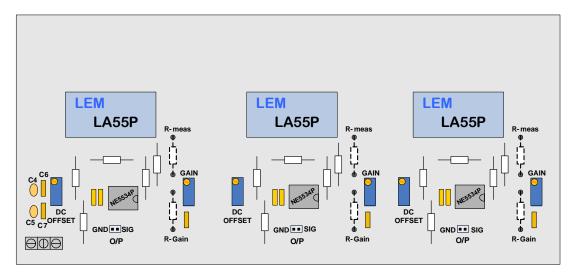

| II. The        | e sensor system                                        | 170      |

| III. The       | e overall setup of test rig                            | 172      |

| Appendix B.    | Sample Code for Verifications                          | 174      |

| The EMTP       | P model for buck-boost converters in a PV string       | 174      |

| Appendix C. Perturb and Observe or Hill-Climbing algorithm | 176 |

|------------------------------------------------------------|-----|

| Appendix D. List of Figures                                | 178 |

| Appendix E. List of Tables                                 | 184 |

| Appendix F. Publication Output                             | 185 |

## **CHAPTER 1** Introduction

With increasing concerns for energy security and environmental issues, the development of renewable energy has significantly grown all over the world to reduce the usage of fossil fuel energy. Solar photovoltaic energy is a promising renewable resource of near infinite reserve.

At present, grid integrated photovoltaic power systems are mainstream in the PV industry. Relatively high levelized electricity cost and low energy conversion efficiency are the main barriers for solar power to compete with traditional generation types in the wholesale electricity market. The intrinsic variable nature of PV technology needs a maximum power point tracking (MPPT) function to be included in PV systems which also increases the difficulty for PV systems to be widespread installed. To increase competitiveness, large power scale PV systems with distributed MPPT modules have always been a hot topic and much has been done to optimise this type of systems. Novel topologies and system architecture with advanced control methodologies are demanded to maintain a balance between cost and efficiency. Studies in these aspects have attracted much attention in academia and industry.

### 1.1 Background and Motivation

The dominant driving force of modern industrialization is based on the combustion of exhaustible fossil fuels which has caused serious global problems such as environmental pollution, greenhouse gas emissions, global warming, and so on. According to the 2019 Edition of the global energy trends published by Enerdata, driven by steady economic growth, a historically high energy consumption 11.2 Gt and CO<sub>2</sub> emissions 27 Gt have been recorded in 2018 for G20 countries. However, fossil fuels still represent 80% of primary energy mix. Demand for electricity has been seen an increase of 3.7% and accounts for 20% in final energy consumption. There is strong growth in the renewable energy (solar and wind power production) sector and greater potential is expected [1].

The 2020 energy market has been greatly impacted by the covid19 pandemic according to newly released data, September 2020. The world economy is experiencing a bigger crisis than 2008-2009. With focused analysis in G20s, the final energy consumption has been seen a decrease by around 5%, while electricity demand has only dropped by 1.5% [2].

Although influenced by the pandemic in the short term, global energy consumption will still grow in the future and this growth trend will exert more pressure to combat global warming and meet the Paris Agreement's objectives [3].

Different types of renewables have been widely installed as promising solutions to tackle the global energy crisis. As the second largest deployed renewable technology in the world, the global PV market is continuously increasing at a high growth rate in terms of cumulative global installed capacity. At the end of 2019, global PV installations reached 623.2 GW [4].

Grid integration of PV systems represent the future advancement direction, driven by lower system costs. Grid connected PV systems account for approximately 99% of the PV market. Off-grid PV systems are not comparable and are mainly deployed in developing countries and remote areas [5].

Grid-connected centralized PV generators have dominated the global market since 2013, mainly promoted by the rapid development of utility-scale PV systems [6]. In recent years, the deployment of rooftop PV systems has reduced during this trend.

Compared with grid connected distributed PV generators, cheaper capital investment, faster plants construction and quicker use of PV electricity, are the main drivers for centralized PV generators to be built.

Generally, centralized PV generators are restricted by lower solar energy capture ability as central MPPTs are the main choice for this type of systems [7]. While distributed PV generators can implement distributed MPPT at the PV string or panel level to increase solar energy extraction efficiency. Distributed MPPT technologies usually come with higher initial equipment deployment cost [8]. Much research has been undertaken to deal with the issues of the higher levelized cost of distributed PV systems and the lower energy extraction efficiency of centralized PV systems [8][9][10]. With a growing penetration level of PV technologies in electricity networks, a bright future for the development of the PV industry is anticipated.

### 1.2 Photovoltaic Technologies

For photovoltaic (PV) electricity generation, the elementary mechanism is the photovoltaic effect, which is the process that converts electromagnetic radiation (sun light) directly into dc electricity. The basic photovoltaic producing device is the photovoltaic cell, also called a solar cell, which features a p-n junction fabricated from a semiconductor material [11].

Generally, the materials of PV cells can be divided into crystalline, thin-film and organic types. Crystalline silicon (single crystal and multi-crystalline silicon) makes up more than 90% of the world's cell production with commercial efficiencies from 16% to 25% [6]. The relatively low conversion efficiency of present PV materials is a barrier to PV industry growth. Research and progress into high efficiency materials and low cost production processes has been continuous since the first silicon PV cell was discovered in 1954 [12].

Table 1-1 gives a basic comparison of the primary commercial materials on the PV market. Although some advancements have been made experimentally, the PV market is still waiting for stable and commercial products with lower cost and higher efficiency [13].

Table 1-1 Comparison of dominating materials of commercial Photovoltaic cells

| Materials              |                                   | Efficiency                     | Features                           |

|------------------------|-----------------------------------|--------------------------------|------------------------------------|

| Crystalline<br>Silicon | Single Silicon (sc-Si)            | 16%-25%                        | Main commercial material with      |

|                        | Multi-crystalline Silicon (mc-Si) | 14%-18%                        | less expensive produce cost        |

| III-V Compound GaAs-Ge |                                   | II-V Compound GaAs-Ge Over 40% |                                    |

| Thin Film Cells        | Cadmium Telluride<br>(CdTe)       | 22% in the lab                 | Less expensive to manufacture      |

|                        | Organic Thin-film                 | 22% in the lab                 | than crystalline cells potentially |

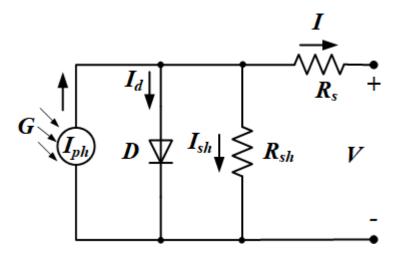

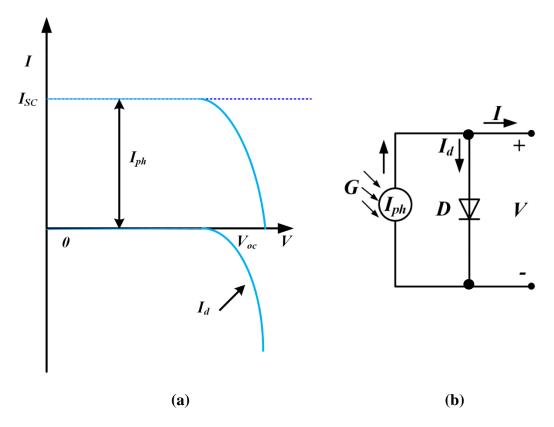

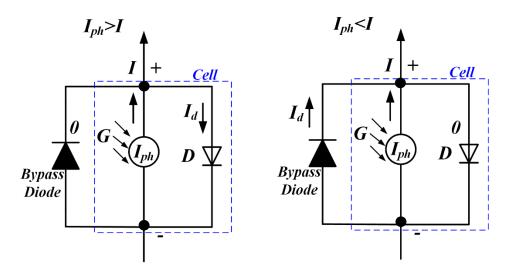

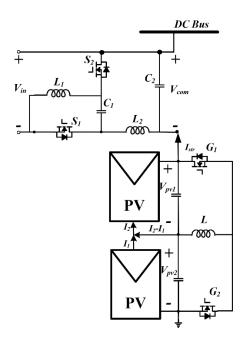

There are several ways to model the PV cell electricity characteristic. A simple equivalent electrical model of one single PV cell is shown in Fig. 1-1, comprising a parallel connected current source and diode [14]. The output of the ideal photocurrent  $I_{ph}$  is proportional to the sun irradiance (solar energy) that hits the surface of the solar cell. The ideal current source and the reversed saturation current of the diode are both influenced by the ambient temperature. The series resistance  $R_s$  and shunt resistance  $R_{sh}$  are parasitic parameters whose magnitudes and impact are dependent on the geometry of the PV cell. Ideally, it can be assumed that  $R_s$  is zero and  $R_{sh}$  is infinite to simplify the model.

Fig. 1-1. Equivalent Circuit diagram of a basic PV cell

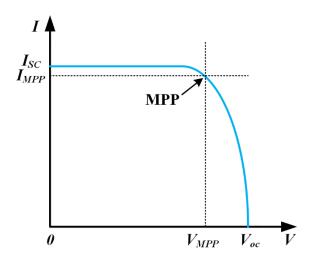

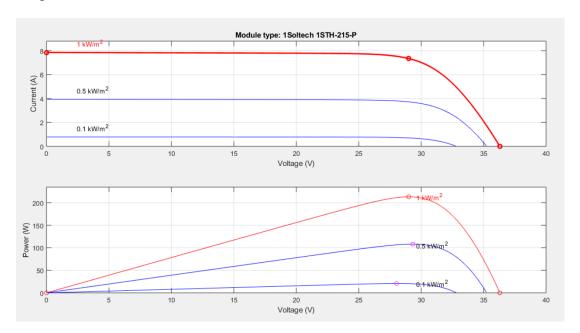

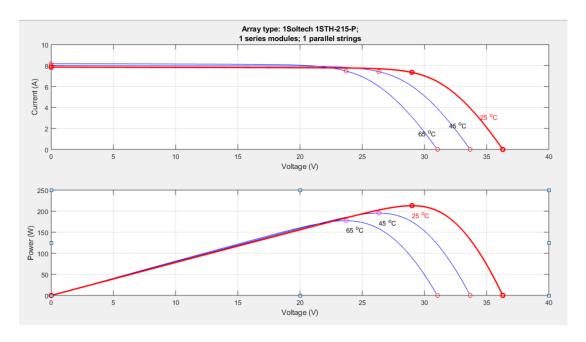

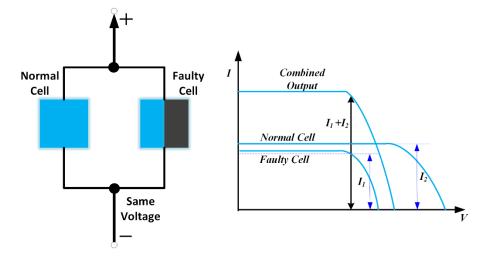

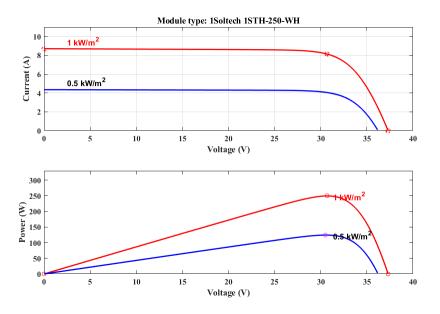

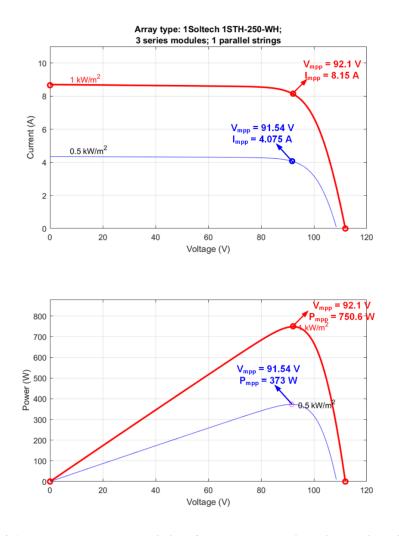

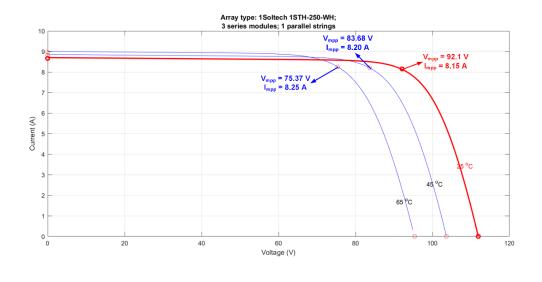

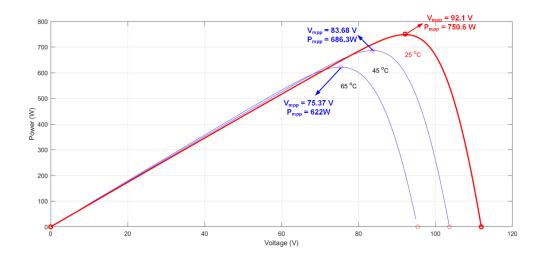

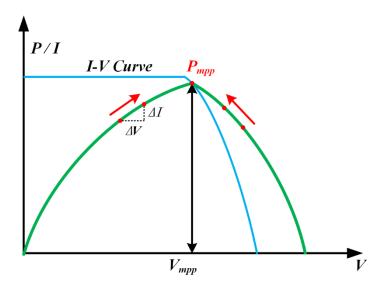

The electrical characteristic of the output current I and output voltage V is illustrated by the I-V curve in Fig. 1-2. The non-linear relationship between I and V is influenced by environmental parameters, such as ambient temperature and sun irradiance.

Fig. 1-2. Characteristic of I-V curve for a PV cell

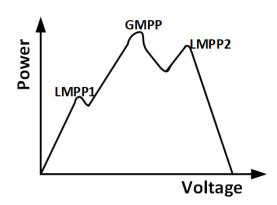

The non-linear relationship between PV output current and voltage, necessitate techniques to achieve maximum energy output in practice. A maximum power point tracking (MPPT) algorithm is usually implemented in PV systems to deal with the non-linear feature of the PV material. MPPT can guarantee that the maximum power output can be extracted when environmental parameters vary [7]. Different MPPT techniques have been developed to improve the energy capture efficiency for different PV applications, and these will be reviewed in subsequent chapters.

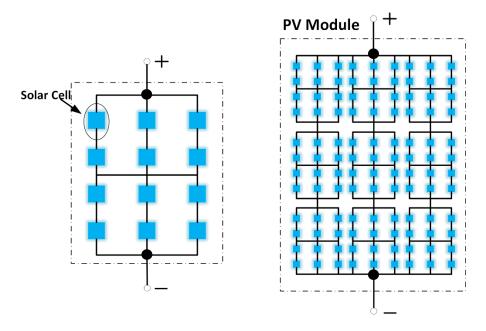

The voltage magnitude of one single PV cell is low (usually less than 1 V) for most PV materials. Hence, the PV module, also called PV panel, is produced as the commercial elementary component for end users, which generally comprises multiple PV cells serially and parallel interconnected together to increase the output voltage and current level. Available commercial PV modules have different specifications considering different cost and demands of clients. The modules usually include 48, 54, 60, or 72 cells in industry. As mentioned, the present photovoltaic (PV) technologies in the market are mostly either monocrystalline or polycrystalline silicon modules. The open circuit voltages of such silicon modules range from 18 V to 26 V for a module of 36 cells or from 38 V to 46 V for one consisting of 72 cells [15].

To further boost the voltage level, the PV string is introduced with several PV modules connected in series. As with commercial PV modules, PV strings also have different specifications in commercial use.

For large scale PV systems, several PV strings are connected in parallel to form a PV array to cumulate a higher power level. There are also other terms to describe different types of PV generators, such as submodule and subarray. The design objective of a PV array is to increase the output voltage level by connecting PV modules in series and increase output current level by connecting PV strings in parallel. Usually, PV strings can be applied in a string level decentralized PV inverter system and PV arrays are used for a centralized PV inverter system. The detailed classification of different grid integrated PV systems is given in the following section.

## 1.3 Classification of Grid Connected PV Systems

Conceptually, a photovoltaic system is comprised of large number of PV modules connected to a utility grid (grid-connected system) or a series of loads (off-grid system). Compared with fast-evolved grid integrated PV systems, the share of off-grid PV installations is small. Off-grid systems can provide electricity for areas without a utility electricity network and storage batteries are usually demanded for off-grid applications.

Grid-connected PV systems represent approximately 99% of the global PV market. According to the IEA-PVPA 2020 report, the cumulative installed nominal PV power worldwide was more than 632 GW by the end of 2019, and most of the power is from grid-connected systems [5].

Grid-integrated PV systems can generally be classified into different types by power level. There are small PV systems (less than 50 kW), intermediate systems (between 50 kW and 1 MW), and large-scale systems (over than 1 MW). However, system boundaries with different power levels are not explicit due to the modularity nature and separated installation of PV systems [16].

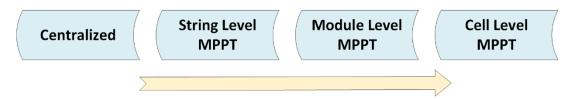

In terms of MPPT implementation, grid-connected PV systems can also be classified into two main groups: centralized MPPT (CMPPT) and distributed MPPT (DMPPT) [11][8][17]. As shown in Fig. 1-3, the DMPPT category is defined based on the level at which MPPT is implemented: string, module, submodule and even cell

level where the MPPT function is applied. The future trends for MPPT implementation are dictated as the arrow direction towards finer granularity.

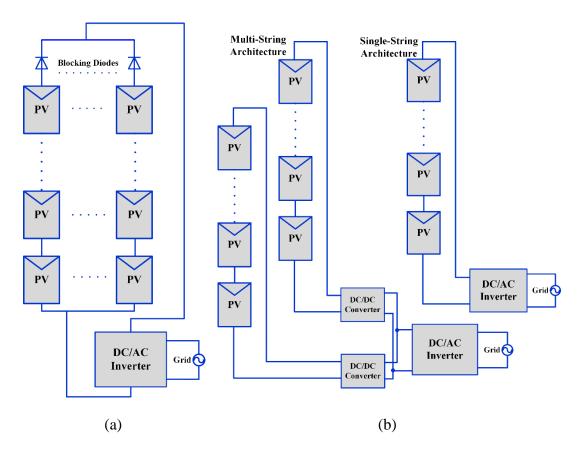

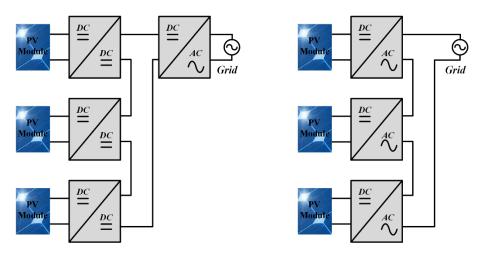

Fig. 1-3 Trends towards finer DMPPT

Inverters are needed to convert electricity from direct current (dc) power generated by PV modules to alternating current (ac) power supplied to the utility grid. Inverter based power configuration types fit into three broad categories: centralized inverter for the whole PV array, string inverter used for each string of modules, and distributed module integrated converters [18]–[21]. The centralized inverter is illustrated in Fig. 1-4 (a) with blocking diodes, often referred to as string diodes, connected in series with each string to prevent possible reversed current flow. As seen in Fig. 1-4 (b), the single-string and multi-string structures can be regarded as reduced versions of a centralized inverter. However, the MPPT function can be applied at the string level to increase operational efficiency. For larger utility-scale PV systems, 3-phase centralized inverters which have a typical power rating from 2 to 5 MW are the common choice. Installation of string inverter based configurations have grown rapidly, especially in the Asia-Pacific region [6].

Fig. 1-4. Inverter configurations. (a) Centralized inverter, (b) Single-string and Multi-string inverter.

A centralized inverter is sourced by a PV array while a string inverter is supplied by a PV string, which means MPPT cannot be applied at the module level for both configurations [22]. Partial shading and PV module mismatching can have a disproportionate impact on system performance, since the least efficient PV modules (shaded or defective) will decide the whole system energy capture efficiency. In a centralized inverter system, several PV strings are parallel connected by string diodes to avoid reversed power flow, which causes losses in the diodes.

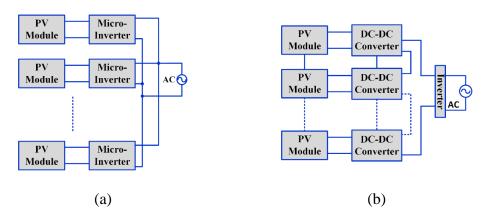

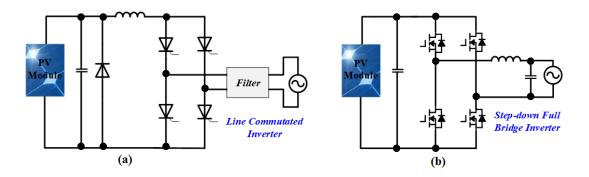

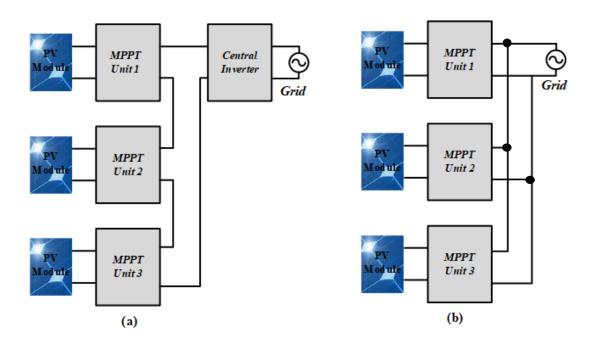

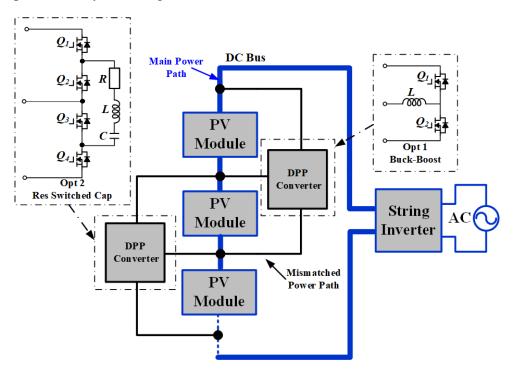

Module level distributed MPPT systems attempt to solve the mentioned problems in centralized and string level inverter systems. The module integrated converter (MIC) based DMPPT configuration is commercially available at present. There are different types of MIC DMPPT system architectures. They mainly consist of AC modules (microinverters) and dc optimizers, which are increasingly expanding, especially in the USA. The AC module, namely microinverter, directly converts the low PV module voltage, typically 22-45V, to the single phase AC grid level (100 to 240 V AC usually) [19][23][24]. The dc optimizer is a voltage boosting dc/dc

converter connected to the PV module [25][8]. These commercial MIC configuration types are illustrated in Fig. 1-5. The per module per converter structure removes the mismatch losses between PV modules and enables the 'plug and play' feature which makes it easier to enlarge the system. Although facilitating a significant boost of captured photovoltaic power, the AC module and DC optimizer based DMPPT architectures have limitations in terms of high initial equipment cost, high voltage conversion ratios and relatively low conversion efficiencies.

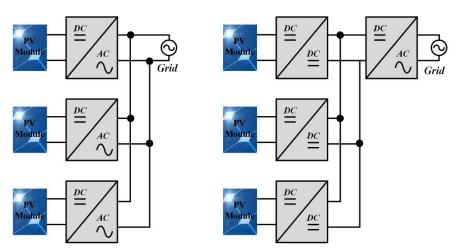

Fig. 1-5. Commercial Module Integrated Converter Configurations. (a) Parallel connected Micro-inverter and (b) series connected DC optimizer.

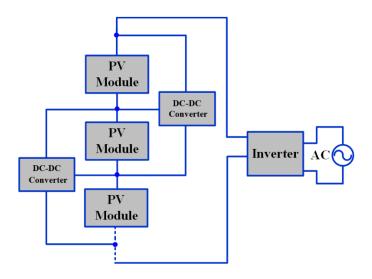

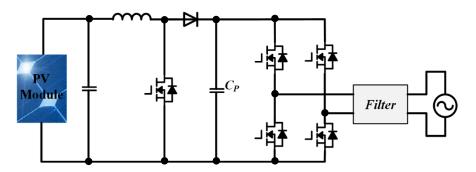

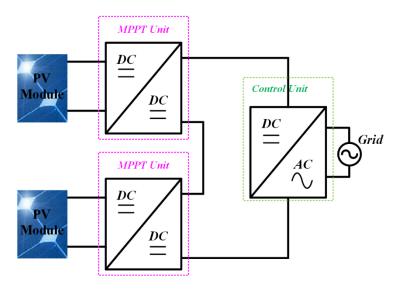

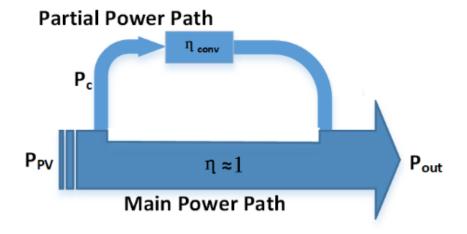

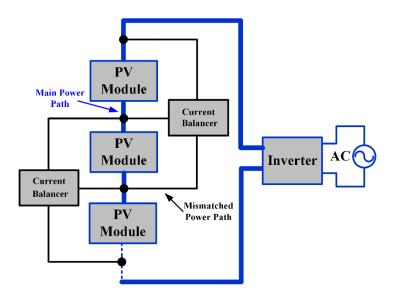

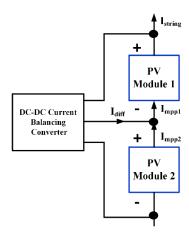

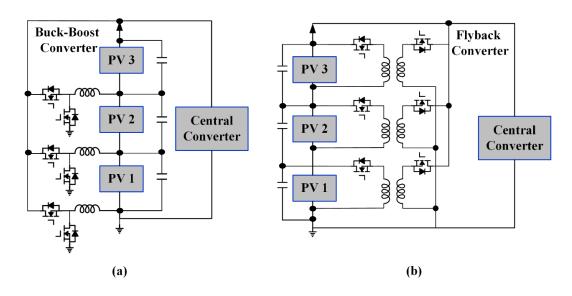

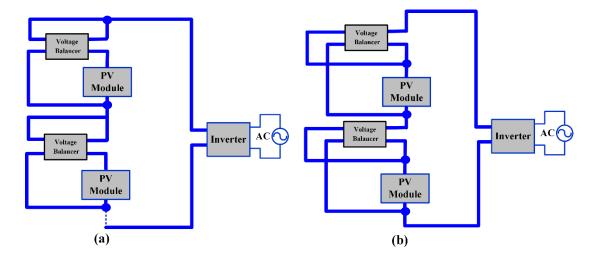

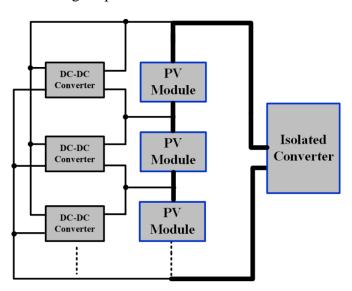

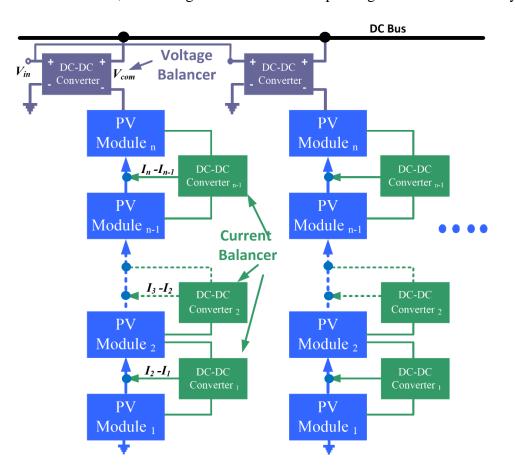

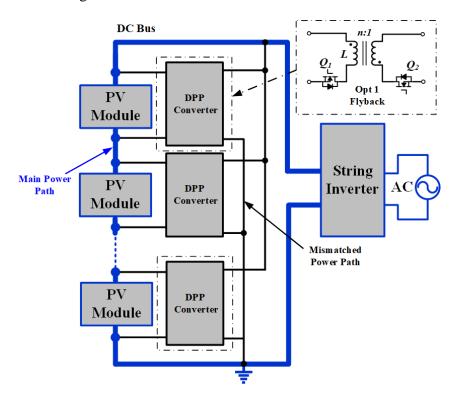

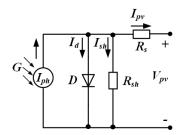

To retain the benefits of the MIC architecture and minimize potential cost and efficiency penalties induced by auxiliary converters, another module level DMPPT architecture, classified as partial or differential power processing PV systems, has been proposed. There are different connection types for partial power processing DMPPT system. The representative architecture is shown in Fig. 1-6. The auxiliary dc-dc converters are parallel interconnected within the PV string to balance unequal module operation points. Different from AC modules and DC optimizers, these auxiliary dc-dc converters do not process the full power generated by the PV module. They only process the mismatched power between two adjacent PV modules. The connection completeness of the associated PV string will not be broken by the shuffling converters which provides benefits related to grounding issues and system expansion. Under the 'no mismatch, no processing' principle, the required power rating, size and manufacturing cost for the auxiliary converters can be significantly reduced [8], [26]–[28]. Thus, the overall energy conversion efficiency can be increased.

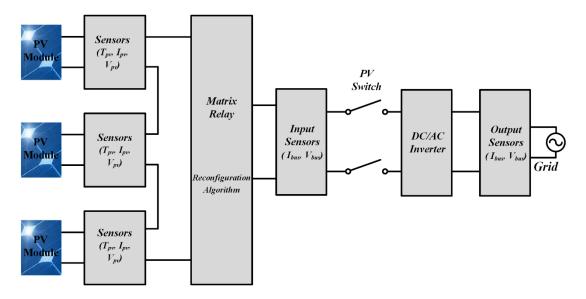

Fig. 1-6. A Representative diagram of the partial power processing configuration.

Despite the evident merits of partial power processing architectures, there are still limitations especially when implemented in utility scale PV systems. The typical architecture shown in Fig. 1-6 with mismatching current balancing ability can only be installed with a single-string inverter to ensure the possible maximum power output for every PV string, while multi-string inverter configurations are more desirable for large-scale power systems.

Centralized or multi-string inverters benefit from higher converter conversion efficiency, higher power density, and lower cost. Accordingly, for large-scale PV grid integration systems, it is a better strategy to integrate the partial power processing with centralized or multi-string inverters architectures. This concept presents emerging challenges for future PV system design, taken into consideration the appropriate converter topologies, novel system architecture, modelling and control.

#### 1.4 Main Barriers and Research Objectives

To compete with traditional grid integrated electricity generators, photovoltaic powered generators present two main barriers: 1) lower energy conversion efficiency and 2) higher deployment cost. To achieve a higher penetration level for grid integrated PV systems, the following major obstacles should be addressed.

High cost – The target of PV grid parity is to lower the levelized electricity cost of PV power at a price equal to or even below the cost of the on-grid price of conventional electricity generators [22][29]. If achieving this goal, large utility-scale PV systems have a bright future [30]. With the downward

- tendency of the price per watt of a crystalline PV module, the price of PV inverters is more visible.

- Output power fluctuation The intermittent nature of PV power may cause reliability and power quality issues for the electricity network. Therefore, investigation and analysis of different operation modes must be made for PV systems to comply with international grid connection codes and standards. In some cases, electricity storage equipment with a relatively short lifespan is needed which may increase the overall system cost.

- Low dc voltage –The distribution voltage level of ac grids in most countries is around 100 V to 240 V, while the transmission voltage level is usually over several kilo-volts. These are way higher than the voltage level of a typical PV module. Consequently, the primary drive for system design and optimization is to seek appropriate solutions to effectively and efficiently convert the low dc voltage power to a high ac voltage power [17].

- Low energy conversion efficiency of PV modules and short lifetime of PV inverters. Although some new PV materials have reported with over 44% energy efficiency in lab experiments, the energy conversion efficiencies for commercially available PV materials are only 16% to 25%. This is the most important reason for the low utilization factor of PV systems and can only be solved by advancement of PV materials and manufacturing industries. Modern PV modules usually have more than 25 years guaranteed operation time. While PV inverters lifespan vary from 10-15 years for sting level inverters to 20-25 years for DC optimizers. Some off-grid inverters have lower life-times, 2-10 years [31][32]. This contradiction of lifespan between PV modules and PV inverter is adverse for the balance of PV systems. It is necessary to prolong the lifetime of PV inverters to get a better system balance.

It can be concluded that, except for the low efficiency of the PV materials, the most important factors which hinder the development of the PV industry are the low dc voltage of a single PV cell and the intermittent nature of PV electricity.

Actually, these two factors interact. To increase the power level of PV systems, modules need to be connected in series and parallel forms to generate a PV string or PV array. In PV string or PV array based solar systems, string level or array level

MPPT is usually implemented. However, the intermittent nature of solar electricity needs module level or even cell level MPPT to increase the energy capture capability. These two requirements are difficult to realize in a commercially fabricated PV string or PV array, at present. The aim is to find a good solution to deal with this contradiction.

On the other hand, if central MPPT is used at the string level, the mismatch of PV modules will deteriorate MPPT performance and lower system efficiency. The low efficiency issue of PV systems will eventually increase PV electricity cost. A hopeful option is to implement module level DMPPT in large scale grid integrated PV systems. However, most of the present DMPPT schemes have higher initial equipment installation cost which may adversely increase PV electricity price.

To lower PV electricity cost and improve the system efficiency, one prospect of future PV technologies is to investigate a cost-effective method to implement module level DMPPT in larger-scale grid integrated PV systems. The multi-string or central inverter is widely used in the PV industry for higher conversion efficiency and lower system cost. It is the future trend to add modular features in centralized or multi-string inverter dominated PV systems to accomplish this objective. Several aspects aiming to realize this goal have been researched and more detailed reviews will be given in the following chapters. The main objective in this thesis is to find a good solution based on this promising prospect, as discussed in the following points:

- Converters with voltage boosting abilities are required to act as module integrated converters for DMPPT functions. Various step-up converter topologies are assessed focusing on their potential to be used in distributive utility scale PV systems. The dc-dc module integrated converters which can be integrated with centralized or multi-string inverters will be particularly reviewed and designed for a novel PV system architecture. The traditional large power centralized and string level inverter topologies have been widely analyzed and obtained some common agreement, so they will not be discussed in detail in this thesis.

- With increased dc link voltage utilization, impedance source converters have been widely studied and applied within PV systems. The general characters are examined considering passive impedance networks. Traditional control methods are compared and an advanced repetitive control strategy is imposed

- for enhanced harmonic emission capability. Quantified analysis is performed with detailed modelling, circuit specification, and experimental realization.

- To combine the dc-dc MIC with centralized and string inverters efficiently, the

partial power processing DMPPT architecture is a suitable choice. A variety of

converter candidates for partial power processing systems are analyzed and

compared. A novel partial power processing architecture is proposed to give a

convenient connecting method with large scale centralized PV inverters. With

reduced power ratings auxiliary converters, the system cost can be decreased

and module level MPPT is achieved.

- A large-scale grid integration of PV system utilizing the proposed architecture is analysed in simulation to gain system performance evaluation. A simulation model is established to investigate the impact and potential problems for the utility grid that may arise due to the installation power capacity of the PV systems. At different operation modes, distributive control methods and an EMTP model are implemented with fault ride through ability.

# 1.5 Thesis Outline

This thesis is comprised of six chapters. Each chapter can be briefly described as follows:

Chapter 1 gives an overview of the state-of-the-art for photovoltaic power systems. To combat global energy problems, it is needed to develop new PV technologies to achieve a grid parity goal for PV electricity generators in global energy. The main barriers and present PV technologies are discussed to give a picture of the PV industry. It is found that large-scale grid integrated PV systems are the future trend. The main problem of a centralized-inverter-based PV system is low energy conversion efficiency. Various present solutions for this problem are reviewed and a promising prospect has been provided to give guidelines for further research in this thesis.

Chapter 2 reviews module integrated converter topologies and PV system configurations based on the module integrated converter (MIC). Standards and requirements are discussed regarding the possible influences of connecting PV generators to the utility grid. PV system connection types and MIC topologies are compared in three categories to give a clearer view of the application background and

restrictions. The main drive for innovative topologies and system configurations is to improve solar energy efficiency (independent on the PV cell technology) by using cost effective solutions. Another important factor is to match PV inverter lifetime with that of PV modules. Impedance source converters are also reviewed in this chapter to emphasise the control challenge for this type of converter. The proposed solution is given in Chapter 5 with detailed analysis of this general problem. This chapter provides background information and direction for the following research to combine MICs with centralized inverters for better PV system performance.

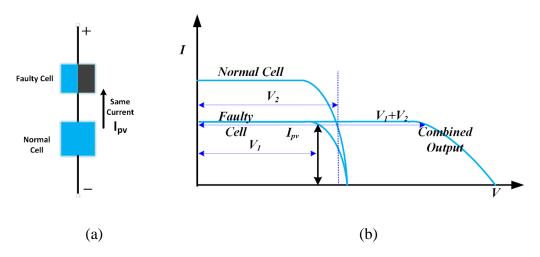

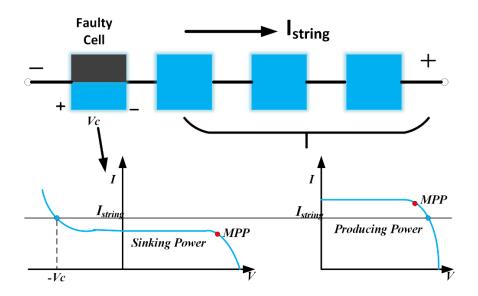

Chapter 3 gives a literature review and comprehensive analysis of the mismatch mechanism in PV systems. The composition feature of the fundamental building block in a PV system is illustrated to clarify the base reason for mismatched losses. The hot spot phenomenon caused by non-identical PV cells is analysed and conventional detection and protective methods are discussed. Two compensation solutions based on module integrated converters are reviewed respectively for series and parallel connected PV modules. The advantages and challenging aspects are concluded to give insight for future research.

In Chapter 4, a new partial power processing distributed MPPT architecture is proposed where the per PV string per central converter configuration is avoided. All the associated converters can be configured as partial power processors with reduced power rating. This architecture is convenient for parallel connection of PV strings to achieve increased power output. This novel architecture can combine the MIC with centralized PV inverters and then can be used in large-scale PV grid integrated power systems. Distributed control, improved reliability and smart grid functionality assistance can be realized. Modelling, control and performance evaluation are given and this system configuration is verified experimentally.

Chapter 5 investigates the control challenges for a set of high-order wide-output (HOWO) impedance source converters (ISCs) with comparison of different control strategies. Different impedance source converters with voltage boosting ability are applied in PV applications. The intrinsic passive impedance network provides lower order distortion of the ac output power which results in controller design difficulty. Generic digital repetitive control is used to solve the prominent second harmonic

problems of ISCs. Simulation and experimental validation are performed on a topology based on the semi-quasi Z source converter.

Chapter 6 presents the conclusion and future research plan. The authors contributions are highlighted. The restrictions for PV technologies and possible solutions are summarised. A promising prospect is expected for the future PV electricity market.

#### 1.6 References

- [1] "2019 Energy Trends Edition | 2019 Energy World | Enerdata." [Online]. Available: https://www.enerdata.net/publications/reports-presentations/2019-energy-trends.html. [Accessed: 04-Apr-2021].

- [2] "Global Energy Trends 2020 Update | Enerdata." [Online]. Available: https://www.enerdata.net/publications/reports-presentations/world-energy-trends.html. [Accessed: 05-Apr-2021].

- [3] "The Paris Agreement | UNFCCC." [Online]. Available: https://unfccc.int/process-and-meetings/the-paris-agreement/the-paris-agreement. [Accessed: 31-Mar-2021].

- [4] IEA-Pvp, "Snapshot of Global PV Markets 2020," Www.Iea-Pvps.Org, pp. 1–16, 2020.

- [5] I. PVPS Task, IEA PVPS report Trends in Photovoltaic Applications 2020. .

- [6] IEA-PV, "TRENDS 2017 IN PHOTOVOLTAIC APPLICATIONS," 2017.

- [7] M. A. G. de Brito, L. Galotto, L. P. Sampaio, G. d. A. e Melo, and C. A. Canesin, "Evaluation of the Main MPPT Techniques for Photovoltaic Applications," *IEEE Trans. Ind. Electron.*, vol. 60, no. 3, pp. 1156–1167, 2013.

- [8] D. Shmilovitz and Y. Levron, "Distributed Maximum Power Point Tracking in Photovoltaic Systems Emerging Architectures and Control Methods," *Autom. J. Control. Meas. Electron. Comput. Commun.*, vol. 53, no. 2, 2012.

- [9] E. Roman, R. Alonso, P. Ibanez, S. Elorduizapatarietxe, and D. Goitia, "Intelligent PV Module for Grid-Connected PV Systems," *IEEE Trans. Ind. Electron.*, vol. 53, no. 4, pp. 1066–1073, 2006.

- [10] S. Saha and V. P. Sundarsingh, "Novel grid-connected photovoltaic inverter," *IEE Proc. Gener. Transm. Distrib.*, vol. 143, no. 2, pp. 219–224, 1996.

- [11] W. Xiao, *Photovoltaic Power System*. Hoboken, NJ, USA: John Wiley & Sons, Inc., 2017.

- [12] S. Almosni *et al.*, "Material challenges for solar cells in the twenty-first century: directions in emerging technologies," *Sci. Technol. Adv. Mater.*, vol. 19, no. 1, pp. 336–369, 2018.

- [13] V. Benda, "Photovoltaics towards terawatts -2013; progress in photovoltaic cells and modules," *IET Power Electron.*, vol. 8, no. 12, pp. 2343–2351, 2015.

- [14] S. B. Kjær, "Design and Control of an Inverter for Photovoltaic Applications," 2005.

- [15] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "Power inverter topologies for photovoltaic modules-a review," in *Conference Record of the 2002 IEEE Industry Applications Conference. 37th IAS Annual Meeting (Cat. No.02CH37344)*, vol. 2, pp. 782–788 vol.2.

- [16] W. Xiao, *Photovoltaic Power System Modelling, Design, and Control*, Chapter 1. Australia: JohnWiley & Sons Ltd, 2017.

- [17] J. M. Carrasco *et al.*, "Power-Electronic Systems for the Grid Integration of Renewable Energy Sources: A Survey," *IEEE Trans. Ind. Electron.*, vol. 53, no. 4, pp. 1002–1016, 2006.

- [18] L. Bangyin, D. Shanxu, and C. Tao, "Photovoltaic DC-Building-Module-Based BIPV System-Concept and Design Considerations," *Power Electron. IEEE Trans.*, vol. 26, no. 5, pp. 1418–1429, 2011.

- [19] F. B. Soeren Baekhoej Kjaer John K. Pedersen, "A Review of Single-Phase Grid-Connected Inverters for Photovoltaic Modules," 2005.

- [20] T. Remus, L. Marco, and R. guez Pedro, "Photovoltaic Inverter Structures," in *Grid Converters for Photovoltaic and Wind Power Systems*, Wiley-IEEE Press, 2011, p. 416.

- [21] J. M. A. Myrzik and M. Calais, "String and module integrated inverters for single-phase grid connected photovoltaic systems a review," in *2003 IEEE* 16

- Bologna Power Tech Conference Proceedings, 2003, vol. 2, p. 8 pp. Vol.2.

- [22] G. G. M. L. S. S. Yaosuo Xue Kurthakoti C. Divya and M. Manjrekar, "Towards Next Generation PV Inverters," 2011.

- [23] H. Hu, S. Harb, N. Kutkut, I. Batarseh, and Z. J. Shen, "A Review of Power Decoupling Techniques for Microinverters With Three Different Decoupling Capacitor Locations in PV Systems," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2711–2726, 2013.

- [24] Q. Li and P. Wolfs, "A Review of the Single Phase Photovoltaic Module Integrated Converter Topologies With Three Different DC Link Configurations," *IEEE Trans. Power Electron.*, vol. 23, no. 3, pp. 1320–1333, 2008.

- [25] G. R. Walker and P. C. Sernia, "Cascaded DC-DC converter connection of photovoltaic modules," *IEEE Trans. Power Electron.*, vol. 19, no. 4, pp. 1130– 1139, 2004.

- [26] P. S. Shenoy, K. A. Kim, B. B. Johnson, and P. T. Krein, "Differential Power Processing for Increased Energy Production and Reliability of Photovoltaic Systems," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2968–2979, 2013.

- [27] H. Zhou, J. Zhao, and Y. Han, "PV Balancers: Concept, Architectures, and Realization," *IEEE Trans. Power Electron.*, vol. 30, no. 7, pp. 3479–3487, 2015.

- [28] C. Olalla, D. Clement, M. Rodriguez, and D. Maksimovic, "Architectures and Control of Submodule Integrated DC-DC Converters for Photovoltaic Applications," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2980–2997, 2013.

- [29] Q. Tu, J. Mo, R. Betz, L. Cui, Y. Fan, and Y. Liu, "Achieving grid parity of solar PV power in China- The role of Tradable Green Certificate," *Energy Policy*, vol. 144, p. 111681, Sep. 2020.

- [30] T. Kerekes, E. Koutroulis, D. Séra, R. Teodorescu, and M. Katsanevakis, "An Optimization Method for Designing Large PV Plants," *IEEE J. Photovoltaics*, vol. 3, no. 2, pp. 814–822, 2013.

- [31] "How Long Do Solar Inverters Last? ( 2020 Guide )." [Online]. Available: https://thosesolarguys.com/how-long-do-solar-inverters-last/. [Accessed: 10-

Apr-2021].

[32] A. Sangwongwanich, Y. Yang, D. Sera, and F. Blaabjerg, "Lifetime Evaluation of Grid-Connected PV Inverters Considering Panel Degradation Rates and Installation Sites," *IEEE Trans. Power Electron.*, vol. 33, no. 2, pp. 1225–1236, 2018.

#### **CHAPTER 2**

# Review of Module Integrated Converters for Full Power Processing DMPPT Architectures

This chapter reviews PV systems based on module integrated converters. With increasing penetration of grid integrated PV systems, the requirements for PV power regulation are more complex. However, due to the high cost of solar electricity, the main drive for the development of innovative topologies and system architectures is to pursue high energy convention efficiency. Module level distributed MPPT is widely applied, trying to deliver maximum PV generated power to ac grid.

Another important factor is to improve PV inverter lifetime to match the relative long lifetime of PV modules which usually has a guaranteed operation time of better than 20 years. The PV system based on module integrated converters is the future trend for higher efficiency and longer lifetime with anticipated system performance improvements, and can be applied in applications with different power levels.

This chapter discusses the demands and related standards for PV integrated inverters with functions to deal with possible power quality issues, such as anti-islanding, current harmonics and so on. Based on these functionality requirements, a conceptual comparison on basic operation principles of state of the art MIC topologies with emphasis on efficiency and system cost, will be developed.

### 2.1 Background

A central inverter is the dominant type for medium or large power grid integrated PV systems. Compared with distributed PV architectures, the lower initial installation cost and higher power inverter efficiency have made central inverter based PV architectures the main stream choice in the PV market. The main limitation is its central MPPT performance which can be severely worsened by mismatched PV modules within the PV array.

To overcome this problem, the string level inverter has been introduced to implement string level MPPT. As the basic commercial PV unit in a PV system, the PV module is usually treated as the basic operating cell for system optimization. To assist module level MPPT implementation, numerous dc-dc and dc-ac converters have been applied in different PV system architectures to gain the best solar power usability.

Conventional module level converters have to process all the power generated by the PV module which can make for high equipment costs. The trade-off between energy extraction ability and equipment cost has driven the development of partial power processing module level converters. In this thesis, module level DMPPT converters are analysed separately as full power and partial power processing types.

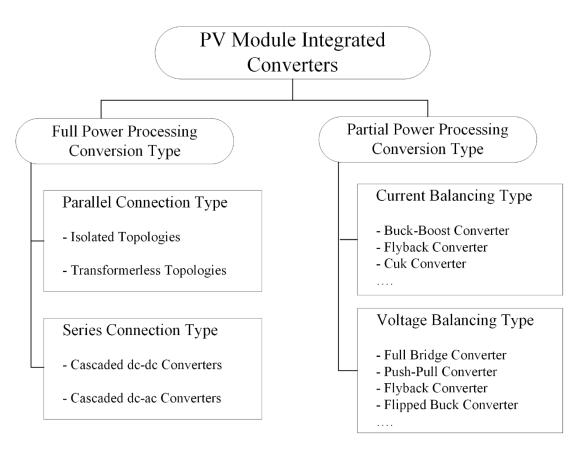

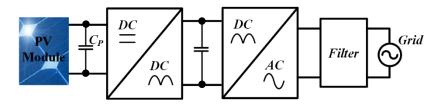

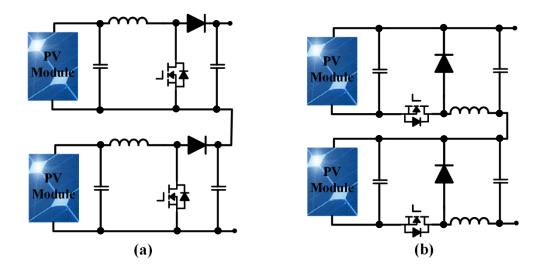

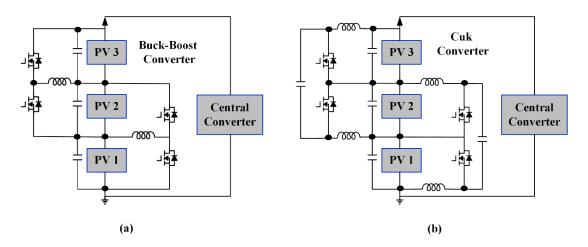

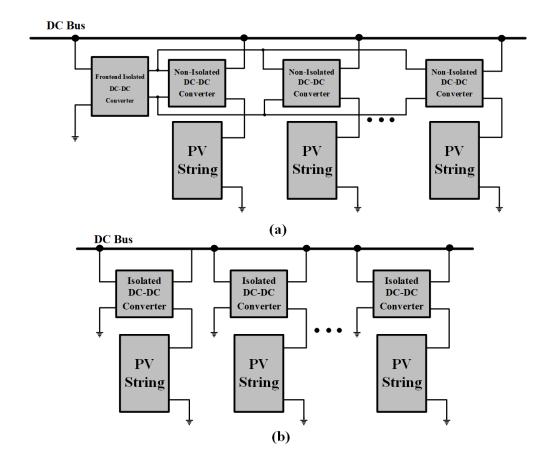

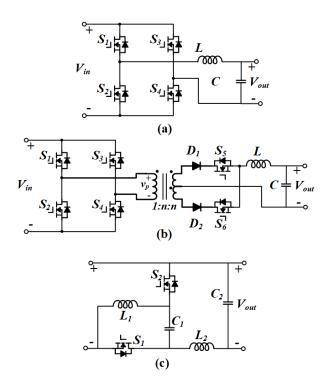

Compared with conventional full power processing converters, partial power processing converters can reduce equipment cost as well as realizing module level MPPT. However, the system connection is more complex and the control strategy is usually more difficult to implement. The classification of module level DMPPT architectures depends on the power processing types, as shown in Fig. 2-1. In this chapter, the full power processing conversion type will be reviewed, while the partial power processing conversion type will be discussed in Chapter 3.

Fig. 2-1 Classification of PV module integrated converters according to power processing type.

Full power processing converters can be grouped into two categories according to the connection types. The converters of the parallel connection type mainly have a module level inverter structure which are also called AC modules or micro inverters. AC module based architectures are mainly used for single-phase low or medium power PV applications. Because of the relatively low dc voltage of a single PV module, high voltage boosting ability is necessary. The voltage boosting function can usually be achieved by isolated transformers or multi-stage transformer-less inverter topologies.

The series connected full power modules can be cascaded dc-dc converters or dc-ac converters. The basic converter cells for this series type are primarily buck, boost and buck-boost converters.

The concept of partial power processing is introduced to ensure module level MPPT can be achieved with a low level equipment cost. By implementing voltage balancing and current balancing ideas, the module level converters do not need to process all the power generated by its associated PV modules. The converters with

lower power ratings only need to operate when mismatch occurs between adjacent PV modules. If the module level converter is intelligent enough to operate only when it is needed, the power rating and size of the module level converters can be significantly decreased. Based on no mismatch, no power processing principle, several new PV architectures have been proposed which are called differential or partial power processing PV systems. The classifications and main converter types are shown in Fig. 2-1 and a detailed review is presented in Chapter 3.

The main standards and requirements for PV system operation will be listed in the next section, to give guidelines for the discussion that follows. Full power processing architectures will be reviewed mainly based on converter characteristics, system requirements and control implementation [1][2]. By reviewing previous research, it can be assessed that there is a possibility to increase energy efficiency by implementing module level MPPT. The main drawback is the increased equipment cost caused by installing many module converters. It is always a task to get a balance when designing such full power processing DMPPT PV systems.

# 2.2 Standards and requirements for grid-connected PV systems

It is a basic requirement for PV processers to meet the demands defined by the PV modules. For grid connected PV systems, another important requirement is to satisfy the grid connection standards defined by the utility supplier. There are several different standards and guidelines created by different areas and organizations. Their main objective is to guarantee the safety and reliability of the grid supply connected with PV generators. Various protective measures and equipment are stipulated specifically for PV grid integration systems. As an important member of distributed generation (DG) systems, the demands for general DG systems also apply to PV generation [3][4].

In this section, the world acknowledged standards are discussed. These standards cover most aspects of PV grid connecting issues regarding power quality, operation safety, islanding detection, and other considerations. A list of important standards and their publication organization are given, as an overview, in Table 2-1 [3][5].

Table 2-1 Standards List for PV- Grid Integration Systems

| IEEE 1547TM-2003 (R2008)                                               | IEEE Standard for interconnecting DRs with electric power systems                                                                                                              |  |  |  |  |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| IEC 61727-2004                                                         | PV systems — characteristics of the utility interface                                                                                                                          |  |  |  |  |

| IEC 61000-3-2:2018                                                     | Electromagnetic compatibility (EMC) – Part 3-2: Limits – Limits for harmonic current emissions (equipment input current ≤ 16A per phase)                                       |  |  |  |  |

| IEEE 929-2000                                                          | Recommended practice for utility interface of PV systems                                                                                                                       |  |  |  |  |

| CSA C22.3 No. 9-08 (R2015)<br>Canada                                   | Interconnection of DRs and electricity supply systems                                                                                                                          |  |  |  |  |

| ENA Engineering<br>Recommendation G83 Issue<br>2-2012 (EREC G83)<br>UK | Recommendations for the connection of type tested SSEG (up to 16 A per phase) in parallel with LV distribution systems                                                         |  |  |  |  |

| VDE-AR-N 4105-2011-08<br>German                                        | Power generation systems connected to the LV distribution network  – Technical minimum requirements for the connection to and parallel operation with LV distribution networks |  |  |  |  |

| GB/T 19939-2005<br>China                                               | Technical requirements for grid connection of PV system                                                                                                                        |  |  |  |  |

| KEPCO Technical Guideline<br>Korea                                     | Korea Electric Power Corporation Technical Guideline for integrating DRs with the Grid                                                                                         |  |  |  |  |

| JEAC 9701-2012                                                         | Grid-interconnection Code                                                                                                                                                      |  |  |  |  |

IEEE 1547-2008 with its amendment 2014 is the most widely used standard for integrating distributed resources within 10MVA electrical systems[6]. For low-voltage low-power PV systems below 10kVA, IEC 61727 is generally used to specify the related technical issues [7]. IEC 61000-3-2 regulates the limitations for harmonics injected into the public supply system[8]. IEEE 929 gives guidelines for small PV power systems in terms of many practical aspects such as personnel safety and equipment protection [9]. As well as these international regulations, many countries have created their own standards based on the international code, such as China, the UK, Germany and some other countries [3].

Considering the possible influences of connecting PV generators to the utility grid, the following points are usually covered in the mentioned standards:

- 1) Voltage regulating and frequency related control;

- 2) Current harmonics and dc current injection;

- 3) Islanding detection and operation;

- 4) Reliability and safety issues;

- 5) Malfunction of equipment;

- 6) Protective measures for overcurrent and overvoltage; and

- 7) Dispatching and planning schemes for PV generated power.

The main constraints for PV connected systems are summarized in Table 2-2 regarding different standards and their associated power ratings.

Table 2-2 A summary of main points in important standards

| Table 2-2 A summary of main points in important standards |                                                                                                                                                                       |                                           |                                                                                                                   |            |                                                            |             |           |              |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------|-------------|-----------|--------------|

| Stan No.                                                  | IEEE 1547                                                                                                                                                             |                                           | IEEE                                                                                                              | 929        | IEC 617                                                    | 727         | EN610     | 000-3-2      |

| Power<br>Ratings                                          | 10 MVA                                                                                                                                                                |                                           | 10 kW 10 i                                                                                                        |            | 10 kV                                                      | A           | 16A@230V  |              |

|                                                           |                                                                                                                                                                       |                                           |                                                                                                                   |            |                                                            |             | Order (h) | Limit<br>(A) |

|                                                           | 3-9                                                                                                                                                                   | <4.0%                                     |                                                                                                                   |            | <4.0%                                                      |             | 3         | 2.3          |

|                                                           | 11-15                                                                                                                                                                 |                                           | <2.0%                                                                                                             |            | <2.0%                                                      |             | 5         | 1.14         |

|                                                           | 17-21                                                                                                                                                                 |                                           | <1.5%                                                                                                             |            | <1.5%                                                      |             | 7         | 0.77         |

| Odd<br>Harmonic                                           | 23-33                                                                                                                                                                 |                                           | <0.6%                                                                                                             |            | <0.6%                                                      |             | 9         | 0.4          |

|                                                           | >33                                                                                                                                                                   | <0.3%                                     |                                                                                                                   |            |                                                            | 11          | 0.33      |              |

|                                                           |                                                                                                                                                                       |                                           |                                                                                                                   |            |                                                            |             |           | 0.21         |

|                                                           |                                                                                                                                                                       |                                           |                                                                                                                   |            |                                                            | (15-<br>39) | 2.25/h    |              |

|                                                           | 2-8                                                                                                                                                                   | Less than 25% of the odd harmonic limits  |                                                                                                                   |            | <1.0%                                                      | 6           | 2         | 1.08         |

| Even<br>Harmonic                                          | 10-32                                                                                                                                                                 |                                           |                                                                                                                   |            | <0.5%                                                      |             | 4         | 0.43         |

|                                                           |                                                                                                                                                                       |                                           |                                                                                                                   |            |                                                            |             | 6         | 0.3          |

| THD (%)                                                   |                                                                                                                                                                       | <5%                                       |                                                                                                                   |            |                                                            |             | 8-40      | 1.84/h       |

| DC<br>Injection                                           |                                                                                                                                                                       | No more than 0.5% of rated output current |                                                                                                                   |            | No more than 1% of rated output current                    |             | <0.22A    |              |

| Voltage                                                   | Range (%)                                                                                                                                                             | Trip<br>time                              | Range (%)                                                                                                         | Trip time  | Range (%)                                                  | Trip time   |           |              |

|                                                           | V<50                                                                                                                                                                  | 0.16s                                     | V<50                                                                                                              | 6 cycles   | V<50                                                       | 0.1s        |           |              |

|                                                           | 50≤V<88                                                                                                                                                               | 2s                                        | 50≤V<88                                                                                                           | 120 cycles | 50≤V<85                                                    | 2s          | -         |              |

|                                                           | 110≤V<120                                                                                                                                                             | 1s                                        | 110≤V<137                                                                                                         | 120 cycles | 110≤V<135                                                  | 2s          |           |              |

|                                                           | 120≤V                                                                                                                                                                 | 0.16s                                     | 137≤V                                                                                                             | 2 cycles   | 135≤V                                                      | 0.05s       |           |              |

| Frequency                                                 | Range (Hz)                                                                                                                                                            | Trip<br>time                              | Range (Hz)                                                                                                        | Trip time  | Range (Hz)                                                 | Trip time   |           | -            |

| 1 7                                                       | 59.3 <f<60.5< td=""><td>0.16s</td><td>59.3<f<60.5< td=""><td>6 cycles</td><td>49<f<51< td=""><td>0.2s</td><td colspan="2"></td></f<51<></td></f<60.5<></td></f<60.5<> | 0.16s                                     | 59.3 <f<60.5< td=""><td>6 cycles</td><td>49<f<51< td=""><td>0.2s</td><td colspan="2"></td></f<51<></td></f<60.5<> | 6 cycles   | 49 <f<51< td=""><td>0.2s</td><td colspan="2"></td></f<51<> | 0.2s        |           |              |

Note: THD - Total harmonic distortion

Islanding is the situation in which distributed generators such as PV panels and wind turbines continue to supply power to utility grid when the electricity of the main grid is not present. It is required in most standards for PV systems to detect islanding and stop feeding the main electrical network within 2 seconds. There are usually three types of islanding detection methods, viz., passive, active and hybrid protection. The present active methods mainly include frequency shift, power variation and current injection. The passive protecting methods generally monitor voltages and frequency

changing rate. In many countries, it is required to combine active and passive methods to enhance islanding detection. In addition, a specified holding period after fault clearance is required by the grid-connection code before reclosing the main switch.

With an increasing PV system penetration level, it is important for manufacturers to understand and follow the relevant standards for safety and reliability reasons. These requirements and codes mainly cover three parts: the utility grid, PV modules and the operators or clients. The following sections will analyse how these demands and standards are achieved by existing inverter topologies and system configurations. The main objective is to recognize the most suitable solutions for interfacing PV systems to the grid.

# 2.3 Parallel connected module integrated inverters

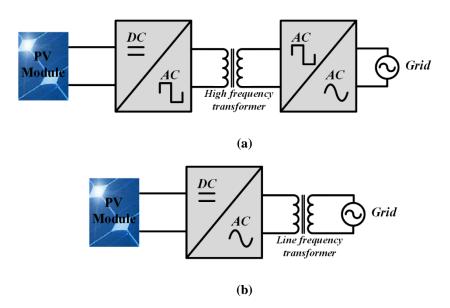

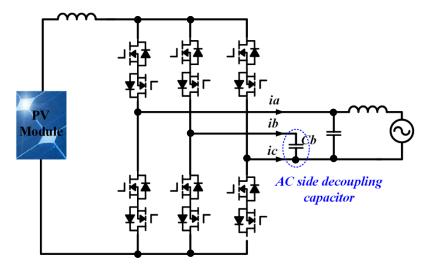

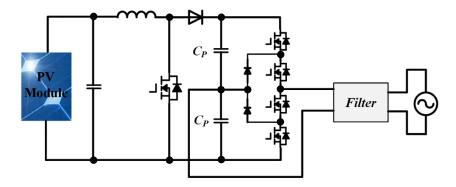

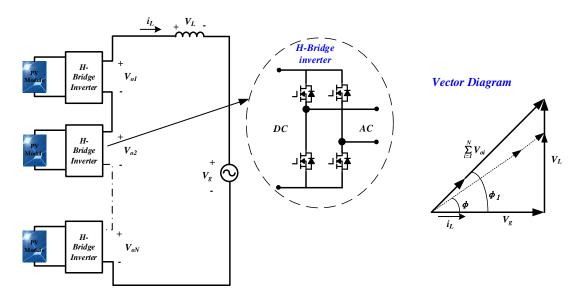

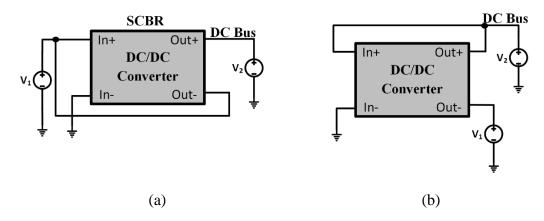

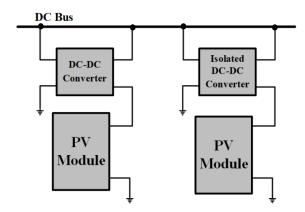

As shown in Fig. 2-2, several micro-inverters can be parallel connected to the ac grid, or several dc-dc converters are parallel connected to one single central grid interfacing inverter. Restricted by the low voltage of a single PV module, this parallel connection type is mostly used for single phase PV applications.

Fig. 2-2 Architectures for parallel connected module level converters: (a) parallel connected micro inverters and (b) parallel connected dc-dc converters with central inverter.

One single PV module with low dc voltage can be interfaced to a single phase ac grid with a higher voltage rating (110V-400V). The module level converters applied in parallel architectures need high voltage boosting ability. Hence, transformer isolated converters are usually a common choice to achieve a high step-up voltage ratio and safety requirements for single phase applications. Many transformer-less topologies have also been introduced to increase efficiency and reduce cost and size [5]. From a

modularity perspective, the transformer-less version can be seen as the future trend. Another important factor that needs to be considered is the low frequency harmonics in single phase PV applications. The power decoupling capacitor is a general solution and must be carefully selected during single phase PV inverter design. From the power stage view, multi-stage power conversion is usually selected to increase the voltage boosting ability, but single-stage novel topologies are also being widely researched [10][11][12].

Thus, parallel connected module level converters can be categorized and compared based on the following perspectives:

- 1) Transformer isolated or transformer-less topologies;

- 2) Positions of the DC decoupling capacitors; and

- 3) The number of cascaded power processing stages.

Firstly, the requirements and operation principle for dc decoupling will be analysed to provide background information for single phase PV applications. Secondly, the isolated single phase PV inverter will be discussed with consideration to three different positions of the dc decoupling capacitors. Then, transformer-less micro inverter topologies will be reviewed based on their basic step-up converter cells. The power stages will also be compared. Then the advantages and disadvantages will be drawn up for parallel connected full power processing module converters.

## 2.3.1 Power decoupling requirements for single phase PV inverter

# a) Power decoupling principle

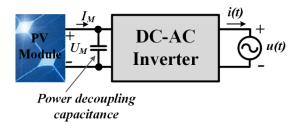

A generic grid-connected, single-phase PV inverter is shown in Fig. 2-3. For the MPPT algorithm, the output of PV module is a constant DC power. At a specific condition, the constant power is equal to  $I_M$  times  $U_M$  which are the current and voltage at this maximum power point.

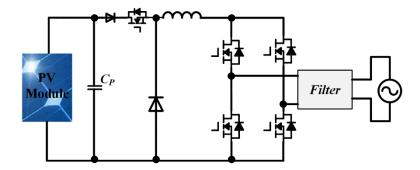

Fig. 2-3 Power decoupling in a generic single-phase PV inverter.

When the grid side voltage and current are expressed in the form of equation (1), where the  $\omega$  is the line angular frequency.

$$\begin{cases} u(t) = U \sin \omega t \\ i(t) = I \sin(\omega t + \varphi) \end{cases}$$

(1)

The AC side time varying power can be obtained by multiplying the grid voltage u(t) and injected grid current i(t), as in (2).

$$P_{o}(t) = \frac{1}{2}UI\cos\varphi - \frac{1}{2}UI\cos(2\omega t + \varphi)$$

(2)

Assuming the phase shift  $\varphi$  is zero, the grid power can be simplified to

$$P_{o}(t) = \frac{1}{2}UI - \frac{1}{2}UI\cos 2\omega t$$

(3)

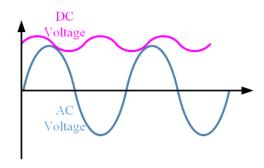

If the power loss of the inverter is neglected, the average power part  $P_{av} = \frac{1}{2}UI$  is equal to the DC power generated by the PV module. The pulsating power part  $-\frac{1}{2}UI\cos 2\omega t$  oscillates at twice the grid frequency. To balance the power difference between the DC and AC side, energy storage components are needed as the decoupling device, which are usually decoupling capacitors [13][14]. The waveform of the total AC power  $P_o(t)$  is plotted in Fig. 2-4.

Fig. 2-4 The power balancing achieved by the decoupling capacitance

Due to the MPPT function, the average power output  $P_{av}$  is the value of  $V_{MPP} \times I_{MPP}$  which is the maximum DC output power  $P_{dc}$  of the associated PV module. When  $P_{av}$  is greater than the instantaneous AC output power  $P_o(t)$ , the excess DC power will be stored in the decoupling capacitor. For the other half cycle of  $P_o(t)$ , the stored energy can be delivered to compensate the shortage of DC power.

To eliminate the relatively large second harmonic ripple of the ac output power, electrolytic capacitors are usually used and the capacitor voltage is depicted in Fig. 2-4. The capacitor can be selected according to the energy balancing principle considering the voltage ripple applied to it.

$$E = 2\int_{0}^{\frac{T}{8}} (P_{o}(t) - P_{dc}) dt$$

$$= \frac{1}{2}CV_{dc_{\text{max}}}^{2} - \frac{1}{2}CV_{dc_{\text{min}}}^{2}$$

$$= \frac{1}{2}C(V_{dc} + \Delta v)^{2} - \frac{1}{2}C(V_{dc} - \Delta v)^{2}$$

(4)

where T is the fundamental period of ac side voltage and  $\Delta v$  is the absolute voltage ripple value of dc side voltage. Subtracting (3) from (4), the capacitance can be obtained as follows. The capacitor value can be influenced by factors: output DC power, line frequency, applied DC voltage to the capacitor, and absolute DC voltage ripple [13].

$$C = \frac{P_{dc}}{2\omega V_{dc} \Delta v} \tag{5}$$

### b) DC decoupling capacitor selection

As a key component for the single phase micro inverter to deal with low frequency harmonics, the DC decoupling capacitor will affect the reliability, efficiency and control strategies of the PV system. Another influence is the PV system lifetime. Each micro inverter is often manufactured onto the back of a PV module for a 'Plug-N-Play' function, hence, it is required to match the lifetime of the two. It is widely known that the lifetime of micro inverter is mainly evaluated by the size of the decoupling capacitors, and the amount of current they carry. A high current involves high power loss and increased temperature inside the capacitor which is the main factor to determine the lifetime [14].

The normal choice is an electrolytic capacitor which offers a higher energy volume. However, the lifetime of electrolytic capacitors varies greatly among different materials, power ratings and applied environment. The electrolytic capacitor is the weakest element inside the inverter with a relatively short operational lifetime [15]. In industry, the trend is to replace electrolytic capacitors with film capacitors for a longer operational lifespan of the latter [16][17].

### 2.3.2 Isolated topologies with different power decoupling techniques

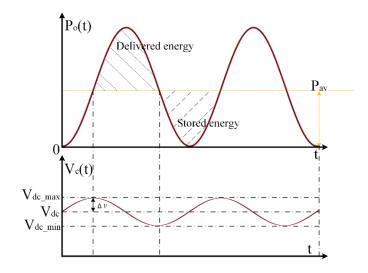

The transformer isolated topology is a typical version of the micro inverter, to amplify the low DC voltage level of PV module to the higher AC grid. As shown in Fig. 2-5, a high frequency or line frequency transformer can be implemented depending on the converter structure. Nowadays, to improve modularity and increase systematic efficiency, the high frequency transformer isolated micro inverter is the main type. Hence, discussion of high frequency isolated topologies on reliability, efficiency and control complexity will be given in the following section, with regard to different DC decoupling locations.

Fig. 2-5 Isolated PV module integrated inverters: a) high frequency transformer version and b) line frequency transformer version.

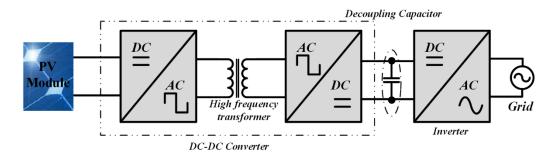

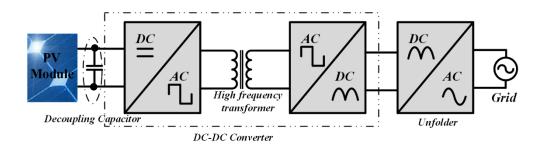

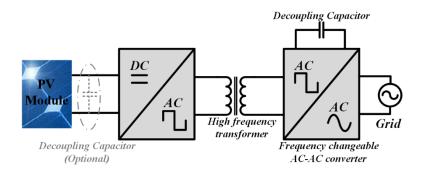

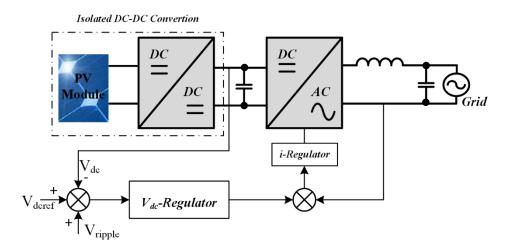

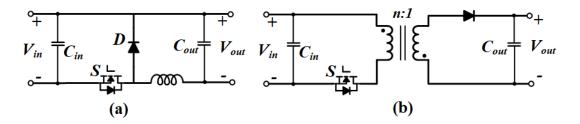

Micro inverter topologies can be categorized by different principles such as the number of cascaded power stages and AC grid interface features. The topology with a pseudo DC link shown in Fig. 2-7 can be seen as a single power stage structure, with AC grid interfacing involving twice the line frequency. The DC link or AC link topologies shown in Fig. 2-6 and Fig. 2-8 are both multi power processing stages and their associated grid interfaces are high frequency PWM inverters.

A variety of high frequency isolated topologies have been presented to deal with power decoupling problems in single phase PV applications, with different features and efficiencies. According to the DC coupling capacitor positions, these topologies can fit into three groups, when referring to different topology configurations [14] [18]:

- 1. DC side decoupling for a micro-inverter with DC link;

- 2. AC side decoupling for a circuit without a DC link;

- 3. PV side decoupling for a topology with a pseudo DC link or without a DC link.

Fig. 2-6 Diagram of multi-stage topology with DC link configuration

Fig. 2-7 Micro inverter topology with pseudo DC link configuration

Fig. 2-8 Multi-stage micro inverter topology without DC link configuration

Different DC link configurations are designed for the single phase micro inverter to help reduce the decoupling capacitance. The representative topologies for three different positions of decoupling capacitors will be comparatively discussed.

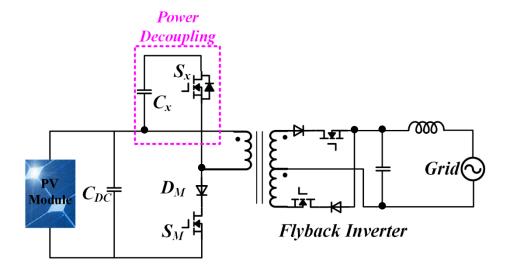

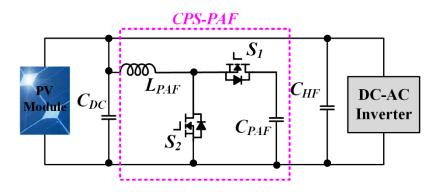

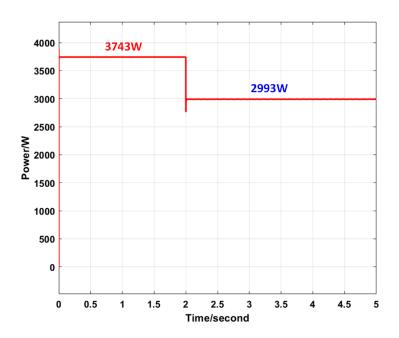

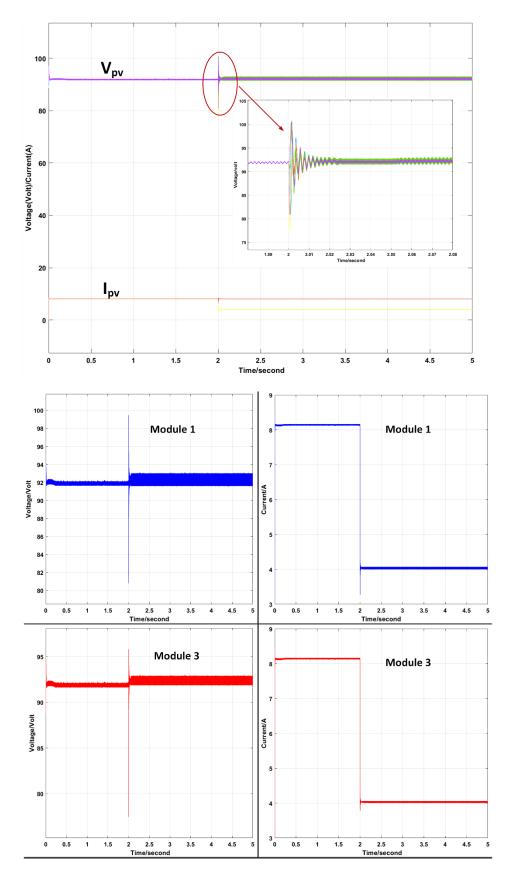

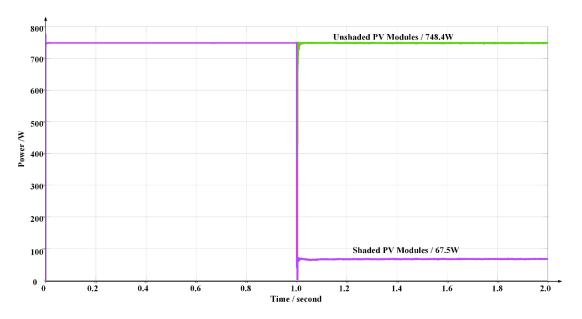

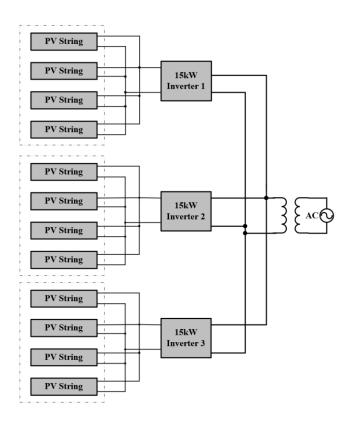

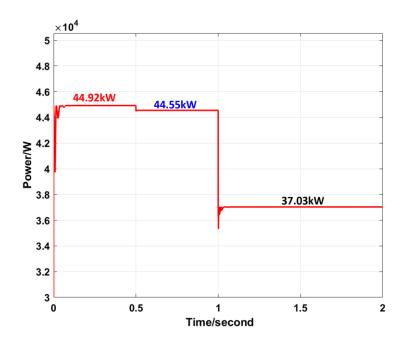

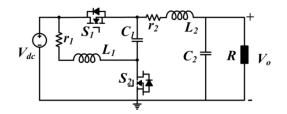

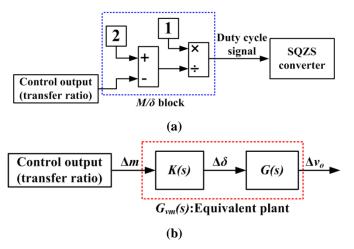

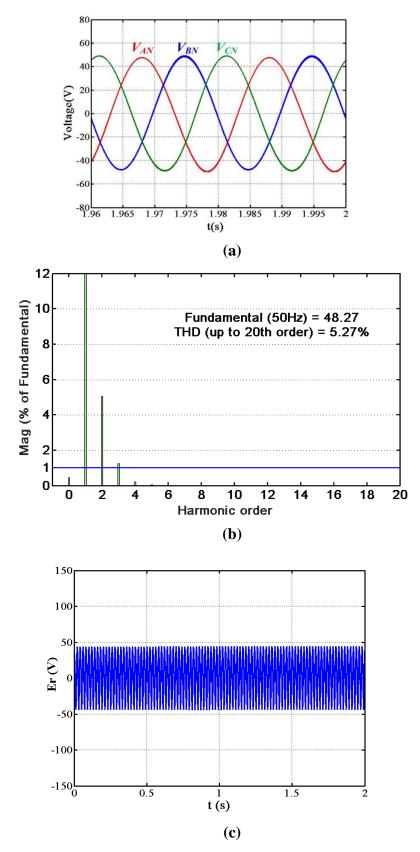

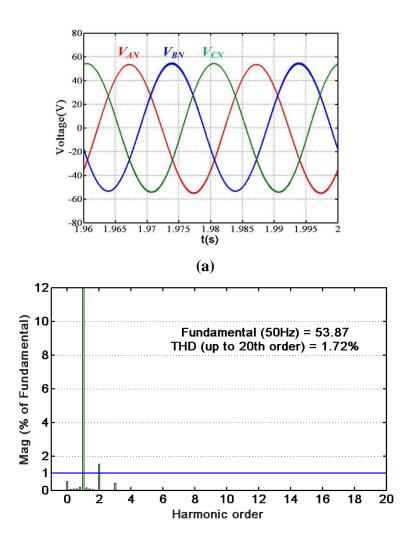

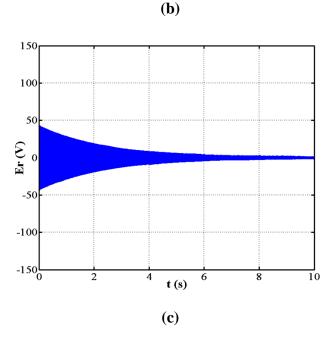

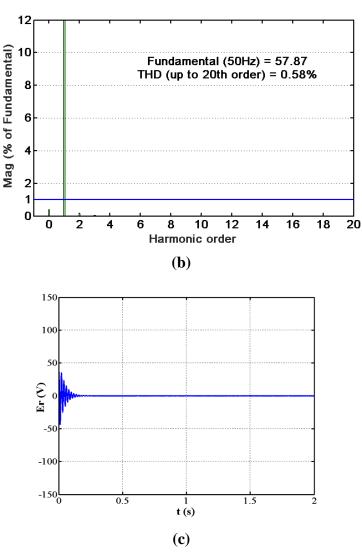

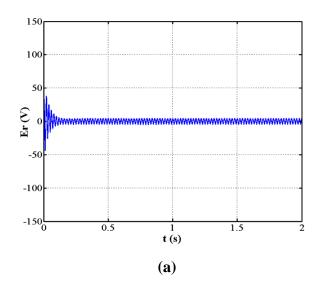

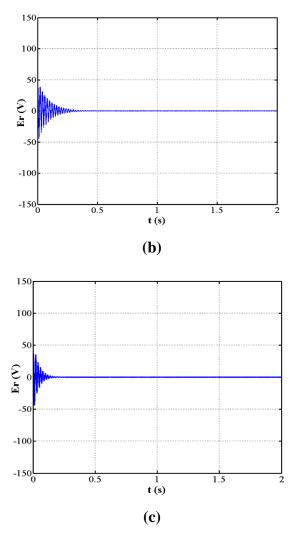

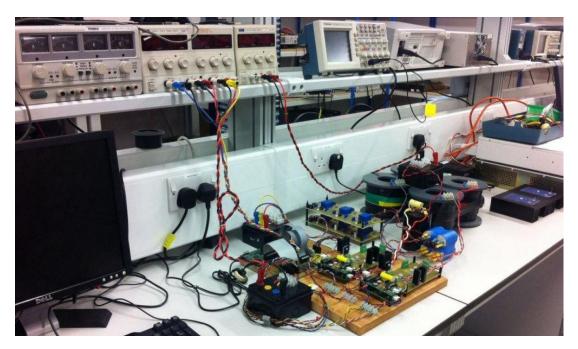

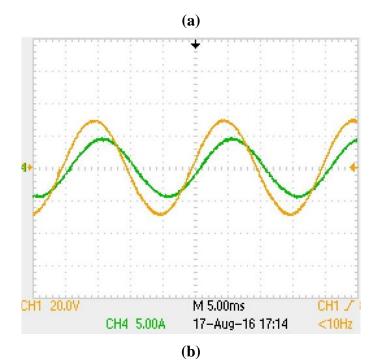

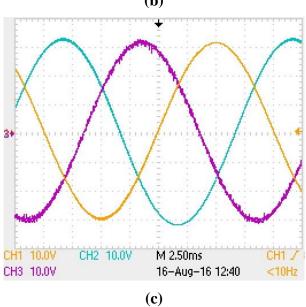

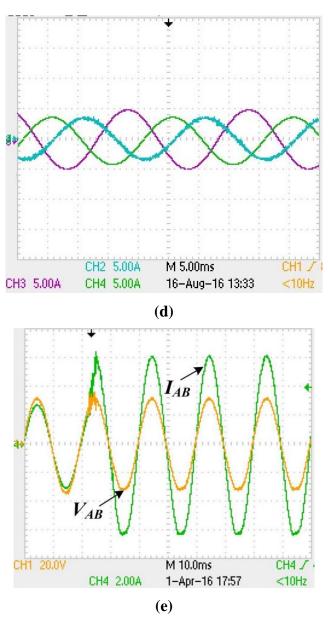

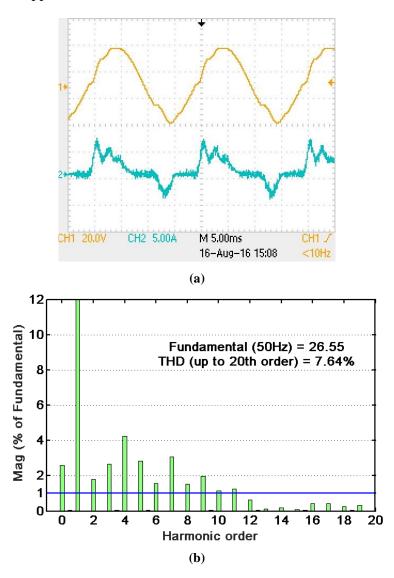

## a) PV side decoupling capacitor