# University of Strathclyde Department of Electronic and Electrical Engineering

# High-Voltage Pulse Generators Incorporating Modular Multilevel Converter Sub-Modules

by

## **Mohamed Atef Elgenedy**

B.Sc. (first class honors), M.Sc.

A thesis presented in fulfilment of the requirements for the degree of Doctor of Philosophy

2018

This thesis is the result of the author's original research. It has been composed by the author and has not been previously submitted for examination which has led to the award of any degree.

The copyright of this thesis belongs to the author under the terms of the United Kingdom Copyright Acts as qualified by University of Strathclyde Regulation 3.50. Due acknowledgement must always be made of the use of any material contained in, or derived from, this thesis.

Signed: M. Atef

Date: 10/06/2018

"Over every possessor of knowledge is one [more] knowing" [Qur-ān, Yusuf 12:76]

"Everything Should Be Made as Simple as Possible, But Not Simpler"

[Albert Einstein]

## Dedication

To the ancestors who paved the path before me upon whose shoulders I stand.

To the successors who will benefit from this work.

## Acknowledgements

All praise is due to *Allah*, whose praise cannot be described by those who speak, whose blessings cannot be enumerated by those who count.

I would like to express my deepest and sincerest gratitude to my first supervisor **Prof. Barry Williams** who supported patiently, guided open handedly, encouraged big heartedly, and helped generously. I would like to express my deepest appreciation to my second supervisor **Dr. Derrick Holliday** who has been very helpful and supportive to my requests and needs during my research period.

I would like to express my deepest and sincerest gratitude and regards for the help, advice and encouragement of *Dr. Ahmed Massoud*, *Dr. Shehab Ahmed*, *Dr. Ayman Samy* and *Dr. Ahmed Elserougi*, who showed me the correct way to effective scientific research before starting my PhD journey, and supported me endlessly during my PhD research.

Gracious acknowledgement is made to *Dr. Ahmed Darwish* who provided me with assistance and valuable discussion during my research period. Thanks to colleagues and staff in *PEDEC* for assistance, useful discussion, and an encouraging atmosphere.

Sincere gratitude belongs to my *family* for their unconditional support and great love; and I want to extend the best wishes for their health and happiness. Special thanks and love to my wife *Esraa* who, with her indebted patience and imperative support, stand by me and encouraged me a great deal throughout my life. Last but not least, thanks to my little man *Loay* and my expected baby girl *Lenore* for giving me willpower.

M. Atef June 2018

# List of Symbols

| $C_{SM}$                         | MMC sub-module capacitance                                                  | F      |

|----------------------------------|-----------------------------------------------------------------------------|--------|

| $C_{Arm}$                        | Arm equivalent capacitance                                                  | F      |

| $E_L$                            | Energy transferred to load during pulse                                     | J      |

| $E_{SM}$                         | SM capacitor energy                                                         | J      |

| E <sub>Arm</sub>                 | Arm equivalent capacitor energy                                             | J      |

| $E_r$                            | Energy dissipated during SM capacitor charging                              | J      |

| Es                               | Energy supplied by the input source during SM capacitor charging            | J      |

| D                                | Converter's duty ratio                                                      | J      |

| f <sub>s</sub><br>i              | Pulse repetition frequency                                                  | Hz     |

| i                                | SM capacitor charging current                                               | A      |

| i <sub>s</sub>                   | HV DC supply input current                                                  | A      |

| i <sub>o</sub><br>i <sub>L</sub> | Output load current.                                                        | A      |

|                                  | Input inductor energising current                                           | A      |

| i <sub>Arm</sub>                 | Arm current                                                                 | A      |

| $I_L$                            | Input inductor maximum energising current                                   | A      |

| $I_P$                            | Output peak pulse current                                                   | A      |

| $I_s$                            | Average supply current                                                      | A      |

| $I_{\chi}$                       | SM capacitor peak charging current<br>SM capacitor peak discharging current | A<br>A |

| $I_y$                            |                                                                             |        |

| I <sub>o</sub>                   | RMS output current<br>Arm inductance                                        | A<br>H |

| L <sub>a</sub>                   |                                                                             |        |

| L <sub>s</sub>                   | Input HV DC supply inductance                                               | Н      |

| $L_i$                            | Input LV DC supply inductance.                                              | Н      |

| т                                | Number of bypassed SMs/arm during multipulse waveform                       |        |

|                                  | generation                                                                  |        |

| Ν                                | Number of SMs per arm                                                       |        |

| n                                | Transformer turns ratio                                                     |        |

| $P_L$                            | Load pulse power.                                                           | W      |

| r                                | Inductor internal resistance                                                | Ω      |

| $R_L, R$                         | Load Resistance                                                             | Ω      |

| $T_s, t_s$                       | Pulse repetition time                                                       | S      |

| $T_Q$                            | PWM carrier repetition time                                                 | S      |

| $t_p$                            | Positive polarity pulse duration                                            | S      |

| $t_n$                            | Negative polarity pulse duration                                            | S      |

| $t_{pz}$                         | Positive polarity null load voltage duration                                | S      |

| $t_{nz}$                         | Negative polarity null load voltage duration                                | S      |

| $t_{pl}$                         | Pulse duration                                                              | S      |

| $t_x$                            | Step voltage-level applying time                                            | S      |

| $t_m$                            | pulse plateau time                                                          | S      |

| $t_L$                            | Inductor energising time                                                    | S      |

| t <sub>c</sub>                   | SM capacitor charging time                                                  | S      |

| $V_s, V_{in}$                    | HV/LV DC input supply voltage                                               | V      |

| $V_{SM}$                         | Charged SM capacitor voltage                                                | V      |

| $v_P$        | Output pulse voltage                                        | V |

|--------------|-------------------------------------------------------------|---|

| $V_P$        | Output pulse peak-voltage                                   | V |

| $\dot{V_p}$  | Positive pulse peak-voltage                                 | V |

| $V_n$        | Negative pulse peak-voltage                                 | V |

| $V_0$        | SM capacitor voltage after contributing to pulse generation | V |

| $V_{\alpha}$ | SM capacitor voltage drop after contributing to pulse       | V |

|              | generation                                                  |   |

| ν            | Percent SM capacitor voltage ripple                         |   |

- γ α

- Percent SM capacitor voltage ripple Safety factor, damping factor Per unit SM capacitor remaining voltage Pulse duty ratio Voltage boosting ratio

- β δ λ

## **List of Abbreviations**

| AC            | Alternating current                                           |  |

|---------------|---------------------------------------------------------------|--|

| BMPG          | Voltage boost mode pulse generator                            |  |

| BPG           | Voltage-boost capability pulse generator                      |  |

| CPG           | Clamping pulse generator                                      |  |

| DC            | Direct current                                                |  |

| $\mathbf{FB}$ | Full bridge                                                   |  |

| GPG           | Generic pulse waveform generator                              |  |

| HB            | Half bridge                                                   |  |

| HV            | High voltage                                                  |  |

| HVDC          | High voltage direct current                                   |  |

| IPG           | Isolated dc input sources based pulse generator               |  |

| IGBT          | Insulated gate bipolar transistor                             |  |

| MMC           | Modular multilevel converter                                  |  |

| NLV           | Null load voltage                                             |  |

| NLC           | Nearest level control                                         |  |

| PEF           | Pulsed electric field                                         |  |

| PG            | Pulse generator                                               |  |

| PI            | Proportional integral                                         |  |

| PWM           | Pulse width modulation                                        |  |

| SM            | Sub module                                                    |  |

| SPG           | Sequentially charged pulse generator                          |  |

| SMPS          | Switched mode power supply                                    |  |

| SUPG          | Voltage step-up pulse generator                               |  |

| TSPG          | Transform based pulse generator with sequentially charged SMs |  |

| UPG           | Universal pulse waveform generator                            |  |

|               |                                                               |  |

## Abstract

Recent research established the effectiveness of applying a pulsed electric field to deactivate harmful microorganisms (such as bacteria and E. coli). Successful deactivation is achieved by lethal electroporation; a process that produces electric pores in the biological cell membrane of the harmful microorganisms when subjected to high-voltage (HV) pulses. The HV pulses are designed to create pores beyond a critical size at which the biological cell can reseal. In contrast when applying non-lethal electroporation, the cell-membrane survives after the electroporation process. This is required, for example, when inserting protein cells in the cell-membrane. In both lethal and non-lethal electroporation, HV pulses in the kilo-Volt range (1-100 kV) with durations ranging between nanoseconds and milliseconds are required.

This thesis proposes nine pulse generator (PG) topologies based on power electronic devices and modular multilevel converter sub-modules. The proposed topologies are divided into two main groups namely: PGs fed from a HV DC supply and PGs fed from an LV DC supply. The first group presents a new family of HV DC fed topologies that improve the performance of existing HV DC fed PGs, such as flexible pulse-waveform generation and full utilisation of the DC link voltage. The second group is dedicated to a new family of LV DC fed PG topologies which have flexible pulse-waveform generation, controlled operation efficiency, and high voltage gain.

All the proposed PG topologies share the important aspect in the newly developed HV PGs, that is modularity, which offers redundancy and robust pulse generation operation.

The presented PG topologies are supported by theoretical analysis, simulations, and experimentation.

## Contents

| Dedica  | ation                                           | iv   |

|---------|-------------------------------------------------|------|

| Ackno   | wledgements                                     | V    |

| List of | Symbols                                         | vi   |

| List of | Abbreviations                                   | viii |

| Abstra  | act                                             | ix   |

| Conte   | nts                                             | X    |

| Chapte  | er 1 Introduction                               | 1    |

| 1.1     | The Electroporation Process                     | 1    |

| 1.2     | Electroporation Applications                    | 2    |

| 1.3     | Electroporation Load Modelling                  | 4    |

| 1.4     | Research Motivation and Objectives              | 5    |

| Chapte  | er 2 Review of High-Voltage Pulse Generators    | 7    |

| 2.1     | Classical High-Voltage Pulse Generators         | 7    |

| 2.2     | Power Electronics-Based HV Pulse Generators     | 9    |

| 2.3     | Summary                                         |      |

| Chapte  | er 3 New MMC Based PGs Fed from an HV DC Source | 24   |

| 3.1     | Clamping Based Pulse Generator                  | 24   |

| 3.2     | Generic Pulse Waveform Generator                |      |

| 3.3     | Universal Pulse Waveform Generator              | 47   |

| 3.4     | Summary                                         | 68   |

| Chapte  | er 4 New Hybrid PGs Fed from an LV DC Source    | 69   |

| 4.1     | Sequentially Charged MMC HB-SMs PG              | 69   |

| 4.2                                       | SPG Operation in Voltage Boost Mode                             |              |

|-------------------------------------------|-----------------------------------------------------------------|--------------|

| 4.3                                       | Generic HV PG with Voltage Boost Capability                     |              |

| 4.4                                       | Summary                                                         | 115          |

| Chapte                                    | er 5 New HV-PGs Utilising the Transformer                       | 117          |

| 5.1                                       | Transformer Utilisation in a Sequentially Charged SM Topolog    | y117         |

| 5.2                                       | Transformer Utilisation for Isolated DC Input Sources PG        | 125          |

| 5.3                                       | Isolated Input-Parallel/Output-Series Voltage Boosting Module   |              |

| 5.4                                       | Summary                                                         | 154          |

| Chapte                                    | er 6 Conclusion and Future Research                             | 156          |

| 6.1                                       | Conclusions                                                     | 156          |

| 6.2                                       | Author's Contribution                                           |              |

| 6.3                                       | Future Research                                                 |              |

| Refere                                    | nces                                                            |              |

| Appen                                     | dix A High Voltage DC Supplies for HV DC Fed PG                 | <b>s</b> 168 |

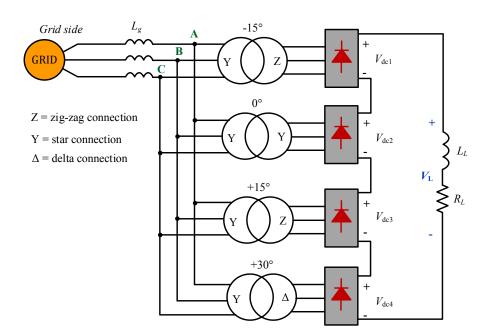

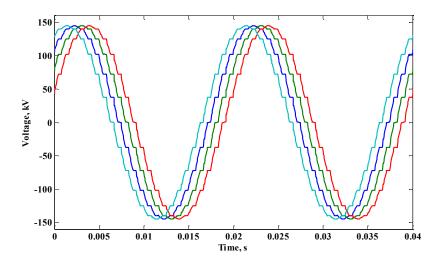

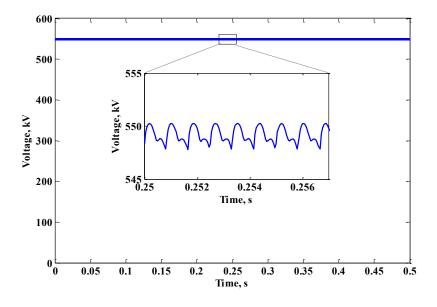

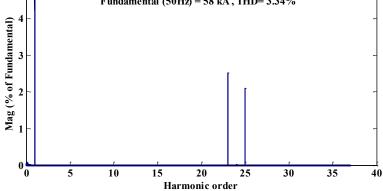

| A.1                                       | 24 Pulse Diode Rectifier                                        | 169          |

| A.2                                       | Fully Controlled and Half Controlled 24 Pulse Rectifier         | 171          |

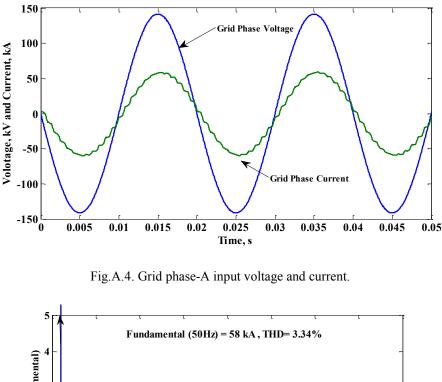

| A.3                                       | The Power Factor and the Harmonics at Grid Side                 |              |

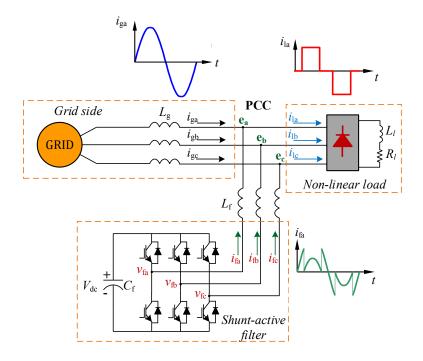

| A.4                                       | AC-DC Converter with Shunt Active Compensation                  |              |

| Appen                                     | dix B Comparison between Sequentially Charged Hy                | ybrid PGs    |

| and Cl                                    | narging Inefficiency Aspects                                    | 174          |

| B.1                                       | Comparison Steps between Sequential Charging Hybrid PGs         | 174          |

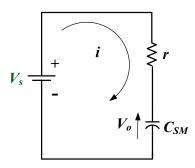

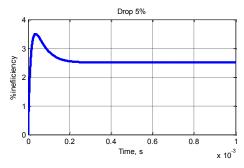

| B.2<br>Ineffi                             | Effect of Charging element and Charging Response Type of ciency |              |

| Appendix C Test Rigs and Software Control |                                                                 |              |

| C.1   | Digital Signal Processor (DSP)                                |     |  |

|-------|---------------------------------------------------------------|-----|--|

| C.2   | Voltage Sensors                                               | 186 |  |

| C.3   | IGBTs Gate Drive Circuit                                      |     |  |

| C.4   | Estimating Transformer Leakage Inductance                     | 188 |  |

| C.5   | Sample Software Codes for Simulation and Experimental Results | 189 |  |

| Appen | <i>dix</i> D List of Figures and Tables                       | 200 |  |

| D.1   | List of Figures                                               | 200 |  |

| D.2   | List of Tables                                                | 206 |  |

| Appen | dix E Author's PG Publications                                | 208 |  |

| E.1   | IEEE Transaction Papers in print                              | 208 |  |

| E.2   | IEEE Transaction Papers Under-review                          | 211 |  |

| E.3   | Accepted International/National Conference Papers             | 212 |  |

## Chapter 1

## Introduction

This chapter explores the concept, the process and the applications of electroporation. Electroporation pulse generator load modelling and essential background for the following chapters are highlighted. Subsequent thesis chapters are dedicated to high voltage pulse generators.

#### **1.1 The Electroporation Process**

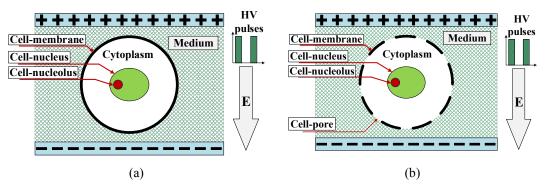

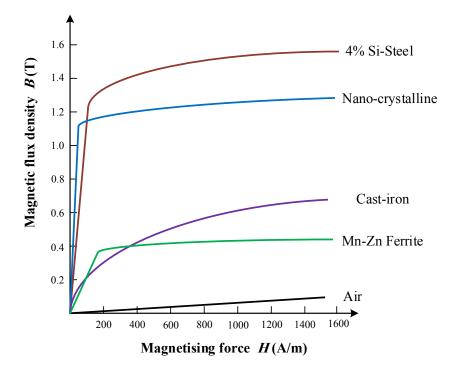

Electroporation is the process where a biological cell-membrane is subjected to high electric field strength via a train of sufficiently high-voltage (HV) pulses [1]. The applied pulsed electric field (PEF) produces micropores in the cell-membrane as shown in Fig.1.1. In Fig.1.1, a schematic representation of a cell-membrane in a medium is depicted. At the beginning of the electroporation process, Fig.1.1a, the cell is intact, however, after sufficient time of PEF application the pores start to appear in the cell-membrane as shown in Fig.1.1b [1]-[4].

There are two types of electroporation, namely: reversible (or, non-lethal) and irreversible (or, lethal). In reversible electroporation, the cell-membrane survives after the electroporation process and reseals its pores [5]. In contrast, irreversible electroporation is lethal, as the cell-membrane dies [5]. For each cell-membrane, there is a critical electric field  $E_{cr}$ , beyond which the cell-membrane cannot reseal if the applied electric field  $E > E_{cr}$ . Depending on the biological cell characteristics, a suitable PEF can be applied for the suitable electroporation type [6].

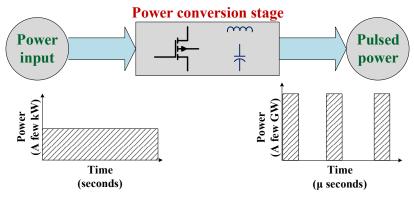

In order to create an electric field across the treatment chamber for electroporation, a high voltage for sufficient time should be applied. Recent research confirms the effectiveness of applying HV-pulses in the kilo-volt range (1-100kV) with pulse duration ranges between nanoseconds and milliseconds [7]. Generally, the higher the voltage, the shorter the necessary pulse duration. Then both the energy efficiency and the electroporation criteria are met. Therefore a low power long-time input is used to

provide high-power short-time pulses through power conversion stage for electroporation, as illustrated in Fig.1.2 [8].

Fig.1.1. Effect of electroporation on a biological cell-membrane. (a) At the beginning of electroporation. (b) After electroporation.

Fig.1.2. Pulsed power energy concept.

## **1.2 Electroporation Applications**

Several applications can benefit from the electroporation process in its lethal and non-lethal forms [9]-[14]. Generating electroporation pulses is primarily controlled by the applied HV across the cell-membrane, pulse-waveform shape, and pulse application time. Therefore, there is a wide range of pulses, where a specific pulse suites a specific application.

### **1.2.1** Lethal Electroporation Applications

Lethal electroporation targets the deactivation of any parasites, bacteria, and viruses. Two applications are:

- *Water treatment*: In water treatment, disinfection is a crucial step before piping water to homes and businesses, where a disinfectant (for example, chlorine or chloramine) is added to the water. Alternatively, disinfection can be achieved by applying lethal electroporation to the water [10].

- *Food Sterilization*: Thermal treatments are used in the food industry for preservation, but with adverse effects on food nutritional values. Therefore, applying PEF with a suitable waveform can preserve food nutritional values and eliminate bacteria and microbes [11].

## 1.2.2 Non-Lethal Electroporation Applications

Applying non-lethal PEF is required when keeping the biological cell alive, for ecological or treatment reasons. The two examples are:

- *Bio-fouling prevention*: The bio-fouling phenomenon is evident in watercooling systems, where an uncontrolled growth of aquatic nuisance species (such as algae, barnacles and Zebra mussels) may clog pipes. For ecological purposes, non-lethal electroporation can be used to prevent bio-fouling. Stunning action can be applied with electrodes placed at the intake of untreated water system and repetitive electrical pulses are applied such that each volume of water that passes between the electrodes is exposed at least once to the electric field [12].

- *Medical treatment*: Molecular therapies require that the effective drug reaches target cells. This can be achieved by several delivery methods such as injections, inhalations, or creams. The drug agent is more effective when entering the targeted cells, and the cell-membrane is the primary barrier against entry. Non-lethal electroporation creates pores in the cell-membrane which can be utilised for drug insertion [13]-[14].

## 1.2.3 Pulse Waveform Shapes

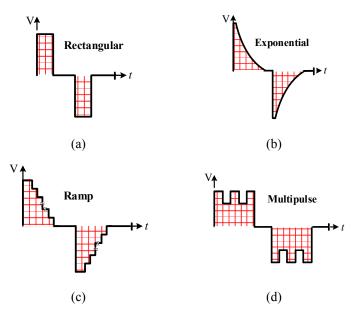

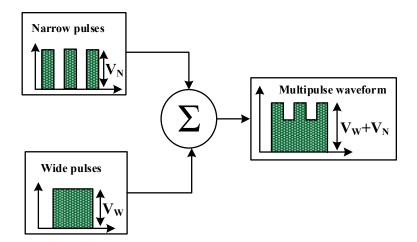

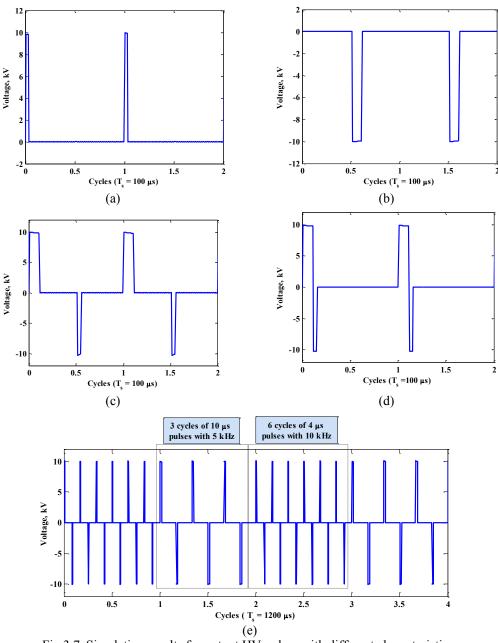

Among the wide range of possible HV pulse-waveforms for electroporation; rectangular, exponential, combined narrow and wide pulse duration (or, multipulse) and ramp pulses are commonly used [15], shown in Fig.1.3. The rectangular pulse waveform in Fig.1.3a is the most common pulse waveform due to its effective pulse area compared with the exponential pulse waveform shown in Fig.1.3b.

Fig.1.3. Common pulse waveforms in PEF applications. (a) Rectangular. (b) Exponential. (c) Ramp. (d) Multipulse.

Normally, the exponential waveform is created across the load due to the nature of classical pulse generators (PGs), which is formed of an *RC* network. With proper selection of *RC* values, the exponential waveform plateau, rise and tail times are controlled. In recent PGs, exponential waveform characteristics (rise, plateau and tail times) can be imitated by ramping waveforms, shown in Fig.1.3c. Multipulse waveform, shown in Fig.1.3d, formed of wide-pulses combined with a train of narrow pulses is preferred in food sterilization applications in order to minimize the amount of heat generated during electroporation, without altering the food nutrition value [16]-[18].

The HV pulses can be either unipolar or bipolar. Bipolar pulses are advantageous in terms of subjecting the microorganisms under treatment to reversing mechanical stresses in addition to the electrical stresses which expedite the electroporation process [19].

## 1.3 Electroporation Load Modelling

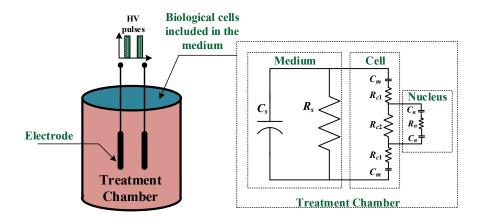

In order to model the PG load, a breakdown of the treatment chamber elements is essential. As depicted in Fig.1.1, a treatment chamber contains a medium and at least a biological cell. The medium can be described by resistance  $R_s$  and a capacitance

$C_s$  which are linearly related to the resistivity of the medium and its dielectric constant, respectively [6]. The biological cell is formed of three substructures, namely: the cell-membrane, the cytoplasm, and the nucleus. Taking the cell substructures into account, the cell interior can be modelled as resistors ( $R_{c1}$  and  $R_{c2}$ ) and the membranes surrounding the cell, modelled as capacitors,  $C_m$ . Both elements are in series to resistance describing the cytoplasm outside the nucleus, which again can be modelled by resistor  $R_n$  and its surrounding membrane by capacitors  $C_n$  [6]. Fig.1.4 shows the detailed electrical model of a biological cell under treatment [6].

Basically, the sample under treatment, along with the medium, are modelled by resistance and capacitance. But its modelling is dependent on the applied PEF duration. For pulse durations comparable to the dielectric relaxation time (which is typically in nanosecond order) of the medium, the capacitive component of the impedance can be neglected [20]. For the assessment of the proposed PGs, the load is described by resistance, since the targeted range of pulse durations is microseconds and longer.

Fig.1.4. Electrical modelling of a biological cell in a medium.

### 1.4 Research Motivation and Objectives

PEF applications are well-established, where classical methods of HV pulse generation dominate. In classical PGs, charging a group of capacitors in parallel, then discharging them in series, provides the HV pulses between the connection terminals. These PGs are bulky, inflexible, and inefficient. The main generated pulse waveform is either exponential or rectangular and unipolar.

The research in this thesis exploits the evolution of power electronic switches, with their high voltage withstand capability and fast on/off switching operation, to introduce a new family of PGs suitable for electroporation. The main objectives of this thesis are:

- Present scalable, modular, redundant and flexible PGs with a reduced footprint.

- Provide a detailed description of the proposed PG topologies.

- Propose PGs, which can either be fed from an existing HV DC input, or from an LV DC input.

- Establish a generic pulse wave generation methodology suitable for wide ranging pulse generation applications.

- Compare the proposed PGs with state-of-the-art solid-state based PGs and highlight key features and limitations.

- Provide conclusions and recommendations for future extension of the research undertaken in this thesis.

## **Review of High-Voltage Pulse Generators**

Marx generators, pulse forming networks, and Blumlein lines are commonly used classical high-voltage (HV) pulse generators (PGs). With ongoing HV semiconductor switch development (silicon and silicon carbide), mainly increased voltage rating and higher switching frequency capability, it is possible to generate HV pulses with power electronics-based converters. This chapter reviews classical PGs and newly developed power electronics based-PGs for electroporation applications.

#### 2.1 Classical High-Voltage Pulse Generators

Classical PGs are mainly based on charging a group of capacitors in parallel then discharging them in series so that a high voltage pulse is developed across the connected load.

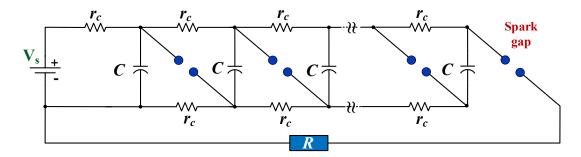

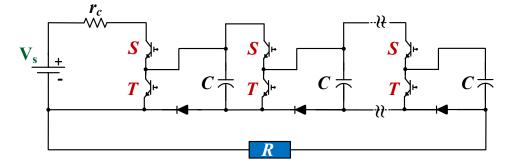

#### 2.1.1 Marx Generator

The basic Marx generator was invented by Erwin Marx in 1923. As illustrated in Fig.2.1 it is comprised of a group of N capacitors, C, which are charged in parallel from the input supply  $V_s$  through the charging resistor  $r_c$ . The switching action takes place with the help of the spark gaps between stages, which have a break down voltage slightly higher than  $V_s$ . The HV pulse is formed when cascaded voltage break down of the spark gaps results when connecting the charged capacitors in series [21]-[23]. In order for cascade break down, the first spark gap is intentionally triggered, exposing  $2V_s$  voltage across the second spark gap forcing it to conduct. The process continues until all the spark gaps are shorted, hence a voltage pulse of  $NV_s$  is impressed across load R.

The basic Marx PG generates unipolar pulses. If bipolar pulses are required, another similar stack fed from  $-V_s$  is used and the load is connected differentially between the two stack outputs [24]-[25]. The charging resistors are the control

element in the Marx generator, if faster and shorter pulses are required, the charging resistances are reduced.

Fig.2.1. Classical Marx generator.

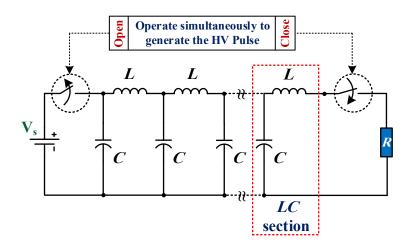

### 2.1.2 Pulse Forming Network

The nature of the generated HV pulse in a Marx generator is exponential. If near rectangular pulses are required, pulse forming network (PFN) can be used. The PFN is formed of *N* cascaded *LC* sections, as illustrated in Fig.2.2, connected to an input voltage source  $V_s$ . After storing the energy in the *LC* branches, an HV switch is closed across the load after disconnecting the input supply, such that the required pulse voltage is delivered [26]-[29].

A PFN mimics lossless transmission lines (TLs), thus the network impedance is

$$Z_o = \sqrt{L/C} \tag{2.1}$$

where  $Z_o$  is the PFN characteristic impedance. The pulse duration is calculated from

$$t_p = 2N\sqrt{LC} \tag{2.2}$$

where  $t_p$  is the generated pulse duration.

The PFN has the advantage of a simple structure and the ability to generate a near rectangular waveform. The main limitations are the limited pulse width range, (*LC* value adjustment is required when different pulse characteristics are needed) and the generated pulse peak is half the input supply due to a load matching requirement  $(R = |Z_o|)$ . In order to increase the pulse peak voltage, the PFN can be of several cascade stages in conjunction with a Marx generator [30]-[31]. The pulse edges can be sharpened by allowing the cored inductor component to saturate.

Fig.2.2. Classical PFN layout.

Similar to PFNs, TLs can be used to generate HV pulses, depending on their inherent distributed *LC* parameters [32]-[34]. However, for near rectangular pulses, load impedance matching is required, hence, the maximum pulse voltage is half the input voltage. A solution for pulse peak voltages equal to the input voltage was provided by Alan Blumlein in 1937. The load is connected in series between two TLs, which are energised by an input voltage at one end. For proper Blumlein line operation, both TLs must be identical and the load impedance must equal twice the characteristic impedance of one line ( $R = 2Z_o$ ) [35]-[37].

### 2.2 Power Electronics-Based HV Pulse Generators

With the evolution of power electronic switches, with high voltage withstand and fast on/off switching operation, numerous solid-state based HV pulse generators have been proposed. The fast on/off switching of the power electronic switches allows fast charging of the utilised capacitors and narrow output HV pulse generation. Examples of power electronics-based PGs vary from mimicking the classical generators, such as the Marx generator, to emerging new topologies and converters.

An important aspect in the newly developed HV PGs is modularity, which offers redundancy, scalability and robust pulse generation operation. A group of the newly emerged PG topologies exploited the inherent modularity of multilevel converter sub-modules (SMs).

Generally, the power electronics-based PGs can be collated into three main groups, namely: Non modular multilevel converter (MMC) based, MMC-based, and hybrid

topologies. MMC-based refers to topologies that adopt existing MMC phase-legs used in HVDC transmission applications, to HV pulse generation. The hybrid term refers to PGs that incorporate the MMC SMs as a stage of pulse generation within the topology. A comparison between the main features and limitations of the three groups is given in Table 2.1. Generally, MMC-based topologies are fed from an HV DC input whereas the hybrid, and the non MMC-based are fed from a low voltage DC input.

| Attribute                                                                               | Non MMC-based                                                                                                                                                                                                 | MMC-based                                                                                                                                                                              | Hybrid                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Examples                                                                                | [38]-[54]                                                                                                                                                                                                     | [61]-[63]                                                                                                                                                                              | [64]-[68]                                                                                                                                                                                             |

| Features                                                                                | <ul> <li>* No voltage sensors<sup>1</sup></li> <li>* Simple control</li> <li>* Small footprint<sup>2</sup></li> <li>* LV DC supply fed</li> </ul>                                                             | <ul> <li>* Scalable</li> <li>* Modular</li> <li>* Redundant</li> <li>* Reduced semiconductor<br/>ratings</li> <li>* Generate different pulse<br/>waveforms</li> </ul>                  | <ul> <li>* MMC modules are<br/>connected across the load to<br/>form the pulses</li> <li>* No HV switches for HV<br/>DC chopping</li> <li>* Moderate footprint</li> <li>* LV DC supply fed</li> </ul> |

| Limitations                                                                             | <ul> <li>* Parameter change<br/>sensitivity</li> <li>* Lacks modularity</li> <li>*HV switches</li> <li>* Generated pulses mainly<br/>rectangular</li> <li>* Inflexible pulse<br/>characterizations</li> </ul> | <ul> <li>* HV DC supply fed</li> <li>* Essential SM capacitor voltage balancing</li> <li>*Large footprint</li> <li>* Possibly complicated control with sensorless operation</li> </ul> | <ul> <li>Different pulse waveforms<br/>if SM capacitors are charged<br/>independently, otherwise<br/>drift in HV levels</li> <li>*Sensors to avoid capacitor<br/>voltage drift</li> </ul>             |

| <sup>1</sup> Under open loop conditions. <sup>2</sup> In comparison with MMC based PGs. |                                                                                                                                                                                                               |                                                                                                                                                                                        |                                                                                                                                                                                                       |

Table 2.1: General Features Comparison of Pulse Generator Topology Groups

#### 2.2.1 Non MMC-Based PG Topologies

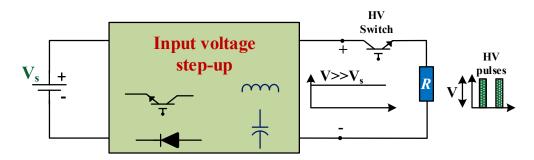

The basic approach of non MMC-based PG topologies is to find a way to step up the voltage, thereafter, an HV switch in series with the load chops the HV. The HV switch is normally switched OFF, and is switched ON during pulse generation, as shown in Fig.2.3. As a result, series connection of semiconductor devices is inevitable, which represents the main drawback of such topologies.

Fig.2.3. Basic concept of non MMC based pulse generators.

Fig.2.4. Solid-state based Marx generator.

## A. Solid-state Marx Generator

Mimicking the classical Marx generator, the solid-state Marx generator has been extensively studied [38]-[42]. The core idea is to replace the spark gaps, shown in Fig.2.1, with power electronic switches such as insulated gate bipolar transistors (IGBTs), as illustrated in Fig.2.4.

A controllable charging/discharging mechanism of the capacitors is obtained, such that switches S allow charging of the capacitors while switches T allow pulse generation across the load. The original topology generates unipolar rectangular pulses, however, in [41], an H-bridge around each capacitor allows bipolar pulse generation. In [42], bipolar pulse generation is achieved by charging two capacitor groups from two DC sources, such that each group is charged to the same voltage but with reverse polarity.

Solid-state Marx PGs have a simple structure, but careful IGBT selection is essential. For example, in Fig.2.4, IGBT ratings are not identical as the current stresses of S switches closer to  $V_s$  are higher due to parallel capacitor charging.

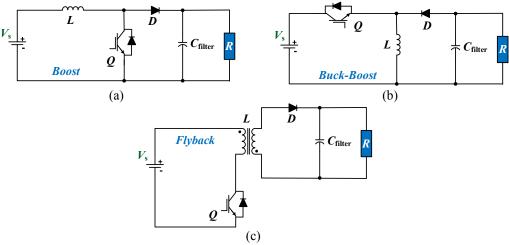

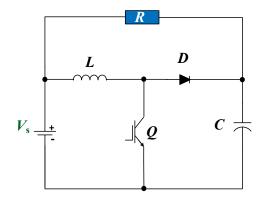

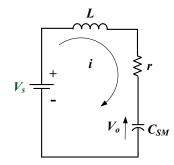

## B. Switched-Mode Power Supply-Based PGs

Utilising basic switched-mode power supply (SMPS) circuits in HV pulse generation topologies [43]-[51] has been researched. Particular attention has been given to boost, buck-boost and the isolated buck-boost (or the flyback) SMPS circuits, shown in Fig.2.5, due to their voltage step-up capabilities.

Fig.2.5. Commonly SMPS circuits in HV pulse generation. (a) Boost. (b) Buck-Boost. (c) Flyback.

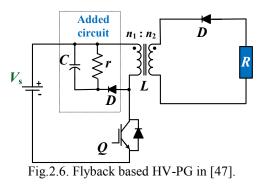

In [47], the basic flyback converter shown in Fig.2.5c has been modified by removing the output filter capacitor and adding an RCD circuit across the transformer primary side, as shown in Fig.2.6. Unlike typical DC-DC converter applications, the output voltage is not a constant DC voltage, therefore, in HV pulse generation, the output filter capacitor can be removed. The RCD circuit, the transformer inductance, and the switch Q form a buck-boost converter. The switch Q is operated with a high duty ratio ( $0.9 \le \delta < 1$ ), when Q is ON, the transformer

primary is exposed to  $V_s$ . When Q is OFF, the transformer primary is exposed to  $-V_c$  where,  $V_c$  is the *RCD* capacitor voltage such that

$$V_c = \frac{\delta}{1 - \delta} V_s \tag{2.3}$$

A negative unipolar HV pulse is generated across load R, with further voltage step up due to the transformer turns ratio, when Q is OFF

$$V_p = \frac{-n_2}{n_1} V_c \tag{2.4}$$

where  $V_p$  is the generated pulse voltage across load *R*. The *Q* duty ratio must be properly selected, in the high range, such that transformer core reset and the voltage rating of *Q* alleviate the need of series connection switches.

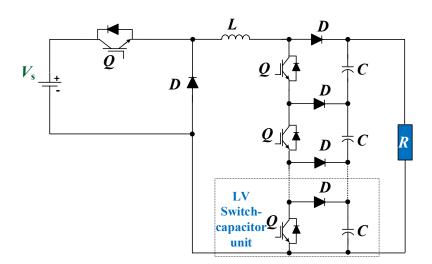

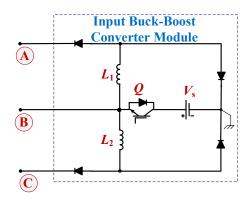

In [48]-[49], an input buck-boost converter feeds a stack of LV switch–capacitor units at the output stage, as shown in Fig.2.7. With proper control of the series switches Q, an HV pulse is impressed across the load with controllable dv/dt. But a complicated control algorithm is required and only unipolar pulses are generated.

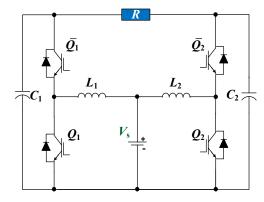

In [50], two boost converters are connected front-to-front while the load is connected differentially between the two outputs as shown in Fig.2.8. The topology can generate bipolar pulses, but requires careful parameter selection.

Fig.2.7. The buck-boost converter-based PG in [48]-[49].

In [51], the boost converter-based circuit in Fig.2.9 operates in a discontinuous conduction mode. The load is differentially connected between the input and output. The topology generates unipolar pulses, and no HV switch to create the HV pulses.

Fig.2.8. Front to front boost converter PG in [50].

Fig.2.9. Boost converter based PG in [51].

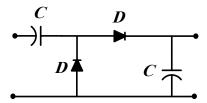

Fig.2.10. Basic CDVM module.

The basic capacitor-diode voltage multiplier (CDVM) module, shown in Fig.2.10, has been incorporated in PG topologies [52]-[54]. Basically, the LV DC input voltage is used to charge the CDVM modules to generate HV DC then a high voltage rated switch is employed to chop the HV DC into unipolar rectangular pulses of the desired rate and width. For bipolar pulses, an H-bridge can be utilised at the output stage. Further voltage boosting can be obtained if the cascaded CDVM modules are preceded by a boost/buck-boost converter.

All the mentioned non-MMC-based PG topologies target unipolar/bipolar rectangular waveform pulse generation. Generation of multipulse waveforms has been addressed in literature by incorporating two converters, one generates the wide pulses and the other generates narrow pulses, then the combination generates multipulse waveforms [16], as shown in Fig.2.11.

Fig.2.11. Conceptual generation of multipulse waveforms using two rectangular pulse waveforms.

As summarised in Table 2.1 and illustrated through the explored non-MMC-based PGs, the need for an HV switch in the output stage and parameter dependent operation are two limitations. The operation of these PGs is simple and their footprint is small.

## 2.2.2 MMC Based PG Topologies

Multilevel voltage source converters (VSCs), such as the diode clamped; flying capacitors, and cascaded full-bridges, are proposed to overcome the main limitations of the two-level VSC in medium-voltage and high-voltage applications [55]; limitations such as bulky input DC capacitor, bulky output ac filter, and high dv/dt. By adding additional levels, the input capacitance is reduced, as is the harmonic filter size (if not eliminated) and the dv/dt problem is mitigated [56].

## A. MMC Operation Background

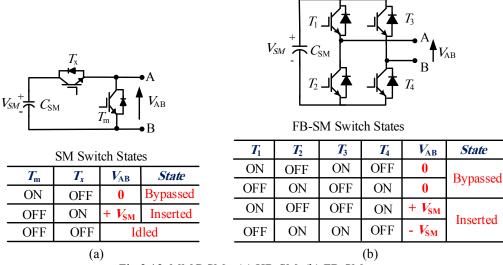

The MMC, an attractive structure multilevel VSC, was invented by Rainer Marquardt in 2001. The MMC hardware structure is based on two SM types, which are the building blocks of MMC topologies, namely: the half-bridge sub-module (HB-SM) and the full-bridge sub-module (FB-SM). Both SM types, along with their switch states, are shown in Fig.2.12 [57]-[60].

The HB-SM, shown in Fig.2.12a, has a capacitor  $C_{SM}$  in series with an auxiliary IGBT switch/diode  $T_x$  and both are paralleled to a main IGBT switch/diode  $T_m$ . Each

HB-SM can operate in any of three switch states; bypass, insertion and idle. The bypass state (when the main IGBT is ON and the auxiliary IGBT is OFF) implies that the SM is a short circuit and the voltage across the SM terminal  $V_{AB}$  is near zero. The insertion state (when the main IGBT is OFF and the auxiliary IGBT is ON) connects the SM-capacitor to  $V_{AB}$ , hence, the SM voltage is  $V_{AB} = V_{SM}$ . The idle state (when both the main and auxiliary IGBTs are OFF) introduces an open circuit (in the direction A to B) across the SM terminal at steady-state, thus, hindering the current flow through the SM terminals (in the direction A to B).

Fig.2.12. MMC-SMs. (a) HB-SM. (b) FB-SM.

As illustrated in Fig.2.12b, the FB-SM is formed of four IGBTs/diodes connected to a capacitor. The FB-SM terminals, A and B, are short-circuited (bypassed  $V_{AB} =$ 0) in two cases when  $T_1$  and  $T_3$  or  $T_2$  and  $T_4$  are switched ON with the other two switches OFF simultaneously. A positive capacitor voltage is applied,  $V_{AB} = +V_{SM}$ , across terminals A and B when  $T_1$  and  $T_4$  are ON and  $T_2$  and  $T_3$  are OFF. When  $T_1$  and  $T_4$  are OFF and  $T_2$  and  $T_3$  are ON a reverse polarity capacitor voltage appears across terminals A and B,  $V_{AB} = -V_{SM}$ . Thus, with control of the SM switches, zero, positive, and negative voltages can be applied across terminals AB.

Both SM types have been studied for MMC-based HVDC transmission applications, where the features of each SM type have been elucidated [58]. Whereas

the HB-SM has half the number of semi-conductor switches, the FB-SM can generate a negative voltage at its terminals, which can be used to block HVDC DC fault current.

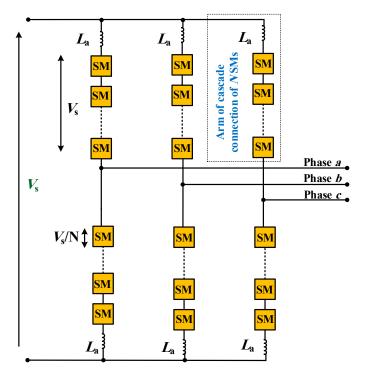

Fig.2.13. Conventional three-phase MMC topology.

The conventional three-phase MMC topology, shown in Fig.2.13, is formed of three phase legs each comprised of two arms of cascade connection of SMs (either HB, FB or both). Each MMC arm has inductor  $L_a$  which has two functions, namely: limit arm inrush current during capacitor voltage balancing processes and reduce circulating current between the phases in a three-phase system [55]. Each arm must be able to support the full DC link voltage  $V_s$ , thus, for N series SMs per arm, each SM capacitor and switching device must be rated at

$$V_{SM} = \frac{V_s}{N} \tag{2.5}$$

MMC operation necessitates correct insertion/bypass of the SMs by applying modulation techniques while assuring SM capacitor voltage balance. Several MMC modulation techniques have been proposed, such as sinusoidal pulse width modulation (SPWM), space vector modulation (SVM), selective harmonic

elimination (SHE), and nearest-level control (NLC) [59]. The NLC is preferred for a large number of SMs per arm. The NLC approach determines the voltage levels that must be synthesized and the required number of SMs to be inserted for a given voltage step,  $V_{SM}$ , by tracking reference signals. The voltage across the upper and the lower arms can be defined as

$$v_{x1} = \frac{1}{2}V_s(1 - m\sin(\omega t + \varphi))$$

(2.6)

$$v_{x2} = \frac{1}{2}V_s(1 + m\sin(\omega t + \varphi))$$

(2.7)

where  $v_{x1}$  and  $v_{x2}$  are the upper and lower arm voltages, respectively, *m* is the modulation index, and  $\varphi$  is the phase shift which is 0°, -120° and 120° for a three phase MMC. Based on the reference arm voltages and the step voltage, the NLC modulation technique is able to determine the number of SMs to be inserted per arm to synthesis the voltage level

$$N_{x1} = round(\frac{v_{x1}}{V_{SM}}) \tag{2.8}$$

$$N_{x2} = round(\frac{v_{x2}}{V_{SM}}) \tag{2.9}$$

where  $N_{x1}$  and  $N_{x2}$  are the SM number to be inserted in the upper and lower arm, respectively.

Before insertion of the selected SMs to form the required voltage-level with NLC, the SM voltages must be sorted, as it is desired to keep capacitor voltages within a certain band. Therefore, each SM voltage in each arm is continuously measured and compared with other SM voltages in that arm, and the capacitor voltages are sorted (based on magnitude) depending on arm current direction. If the arm current direction indicates SM capacitors discharging, progressively the highest voltage capacitor among the available remaining capacitors is inserted at each voltage level during synthesizing the NLC voltage-levels. Otherwise, the SM capacitors are charged, hence, progressively the lowest voltage capacitor is inserted [60].

### **B.** Phase-leg MMC-Based PG topologies

The main features promoting the MMC for pulse power applications can be summarised as follows:

• inherent capacitor in each MMC-SM.

- structure modularity and redundancy.

- input/output voltage level scalability.

- avoidance of series-connected semi-conductor switches.

- possibility of generating any pulse-waveform by using a suitable reference signal to insert/bypass SMs.

The potential challenges are:

- need for an HV DC input, as the MMC cannot boost the input voltage.

- essential SM capacitor voltage balancing.

- large footprint.

Fig.2.14. Phase-leg MMC based PG topology structure [61]-[63].

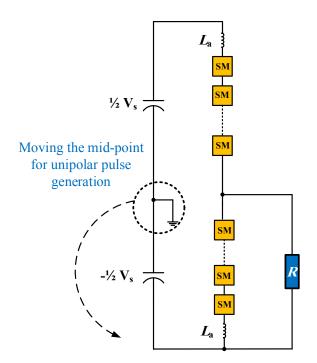

By using one phase-leg of a three phase MMC based inverter, shown in Fig.2.13, conventional pulse waveforms can be generated. Changing the modulating reference waveform, which is responsible MMC SM insertion/bypass, allows mimicking of the modulating signal across the load. A phase-leg MMC based PG topology, illustrated in Fig.2.14 fed from HV DC input,  $V_s$ , suffers from the following limitations:

- Two bulky capacitors are required to form  $\pm \frac{1}{2}V_s$  with a mid-point connection.

- generated pulses are bipolar by the default connection, however, for unipolar pulses the reference point is moved to ground. Thus the converter cannot generate both unipolar and bipolar pulses without physically changing the power topology.

- generated bipolar pulse peak voltage is half the HV DC input.

Sensorless SM capacitor voltage balance in MMC based PG topologies are presented in [61]-[63] using HB-SMs. In [61]-[62], the SM-capacitor voltages are balanced by adding a diode between adjacent HB-SMs when employing a specific ON/OFF switching sequence on MMC HB-SM switches.

For converter cost reduction, a conventional phase-leg of MMC HB-SMs is operated in a sensorless mode using phase disposition PWM technique [63]. For each reference pulse waveform, the ON/OFF switching sequence of the SMs is studied, such that the SMs are inserted based on the same loading conditions resulting in balanced capacitor voltages. MMC phase-leg sensorless operation is attractive in terms of reducing hardware costs and complexity. But control complexity is increased as the number of the SMs is increased, and operation is adversely affected under SM failure.

Reference [64] attempts to obtain a pulse peak voltage higher than the input DC link voltage, with phase-leg MMC topology. The two arms of the phase-leg are comprised of a series combination of FB and HB SMs, the pulse peak voltage can be either equal to or integer multiples of the input DC link voltage by selecting the proper FB and HB SMs number per arm. But, the topology requires pre-charging of the SM-capacitors before operation while a complicated balancing algorithm is necessary for a large number of SMs.

### 2.2.3 Hybrid PG Topologies

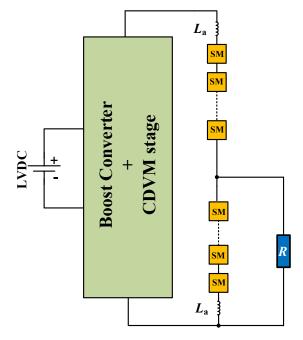

MMC based PG topologies alleviates the need for HV switches and avoids the series connection challenges of non MMC-based PG topologies. But the main limitation is the need of an HV DC input and an MMC phase-leg can only generate bipolar pulses with a peak voltage of half the input HV DC. A solution to these limitations involves hybrid PG topologies, in which an LV DC is the input stage followed by a voltage

boosting mechanism. MMC SMs can be either incorporated at the voltage boosting stage or at the HV pulse creation stage, or both. The MMC SMs are employed to store energy in their inherent capacitors, from the input supply, then transfer it to the load during HV pulse generation. Hence, HV pulses are created across the load without semi-conductor series connection, while gaining MMC features such as modularity, scalability, and redundancy.

Fig.2.15. Hybrid MMC based PG using boost inverter and CDVM stages to feed an MMC phaseleg [65].

Fig.2.16. Sequential charging MMC SMs fed from an LV DC supply and a charging resistor [66].

Fig.2.17. Two series groups of MMC HB-SMs charged sequentially to positive and negative voltages by an input H-bridge and LV DC supply and a charging resistor [68].

A boost converter fed from an LV DC source followed by a CDVM stage is proposed in [65] such that HV DC is obtained, as shown in Fig.2.15. The generated HV DC is then applied to the terminals of an MMC phase-leg. MMC SMs are employed to create the HV pulses across the load, hence, a solution for HV DC generation is provided while the MMC phase-leg is operated as in sectionB B2.2.2B.

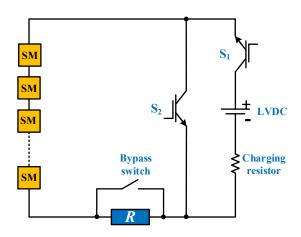

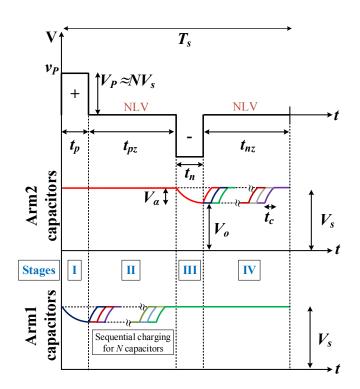

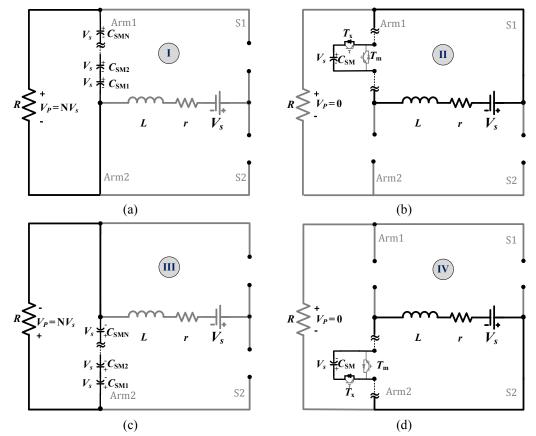

In [66], a specific number of HB-SMs (according to the required pulse peak voltage) are charged sequentially from an LV DC input then discharged in series across the load, forming unipolar HV pulses, as shown in Fig.2.16. During the progressive sequential SM charging, the SM to be charged is inserted while the other series SMs are bypassed, while the load is bypassed and switches  $S_1$  and  $S_2$  are turned ON and OFF, respectively. During HV pulse generation, all the charged SMs are inserted simultaneously and switches  $S_1$  and  $S_2$  are turned OFF and ON, respectively, thus, a unipolar rectangular HV pulse appears across the load. But the charging mechanism is achieved via a relatively high charging resistances to limit the charging current. Consequently, capacitor charging time is elongated, which limits the pulse generation repetition rate and/or the number of utilised SMs.

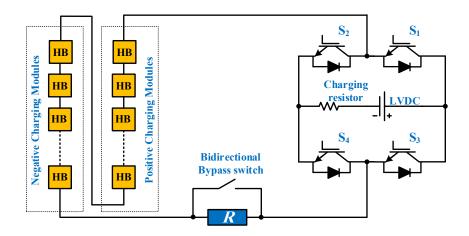

In [67], the HB-SMs are replaced with FB-SMs to allow bipolar HV pulse generation across the load. Alternatively, two groups of series connected HB-SMs are employed in [68], such that one group is responsible for generating the positive pulse polarity and the other generates the negative pulse polarity. Charging the HB-

SMs in each group is by using an H-bridge across the LV DC supply and a charging resistor as shown in Fig.2.17.

The MMC sequential charging PG topologies in [66]-[68], utilise a bypass switch across the load during individual SM charging. The bypass switch is comprised of diodes in [66], thyristors in [67], and back-to-back thyristors in [68], respectively. The bypass switches are rated at the HV pulse level.

## 2.3 Summary

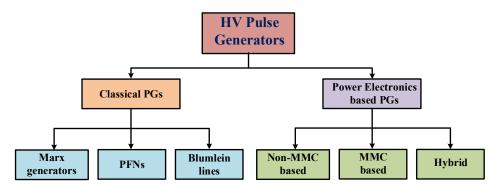

Electroporation applications require HV pulses with specific characteristics, hence, HV PGs are the key element in such applications. This chapter presented the main available topologies for HV pulse generation. Two major PG categories are presented namely: classical PGs and power electronics based PGs, as shown in Fig.2.18. Power electronics-based PGs are collated into three main groups, namely: non MMC-based, MMC-based, and hybrid topologies. The main features and limitations for each category were highlighted.

Fig.2.18. Classification of HV PGs in the literature.

## Chapter 3

## New MMC Based PGs Fed from an HV DC Source

In this chapter, a new family of HV DC fed MMC based PGs is introduced. The proposed topologies address limitations facing existing MMC based topologies. The HV DC source is assumed to exist. The research is focused on generating flexible HV pulses with full utilisation of the input HV DC while assuring SM capacitor voltage balance.

#### 3.1 Clamping Based Pulse Generator

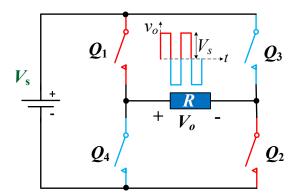

A DC source feeding an H-bridge comprising four semi-conductor switches, generates AC rectangular voltage waveform across the load, as illustrated in Fig.3.1. Turning on  $Q_1$  and  $Q_2$  while turning off  $Q_3$  and  $Q_4$  simultaneously impose  $+V_s$  across the load, while  $-V_s$  is imposed across the load when  $Q_1$  and  $Q_2$  are turn off while turning on  $Q_3$  and  $Q_3$ , simultaneously. This is the basic approach for inverting a DC voltage input to AC with a peak voltage equal to the DC input voltage. But, extending this approach to invert HV DC requires series switch connection forming the H-bridge. Additionally, dynamic and static voltage charging across the switches must be catered for by using snubber circuits.

Fig.3.1. Generating AC voltage from DC input voltage using H-bridge circuit.

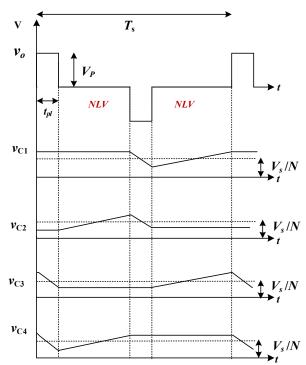

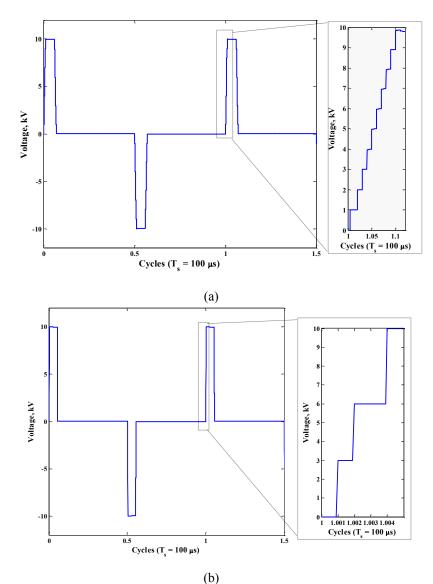

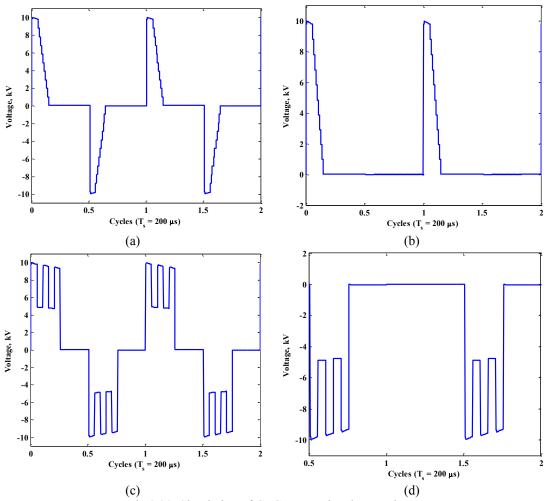

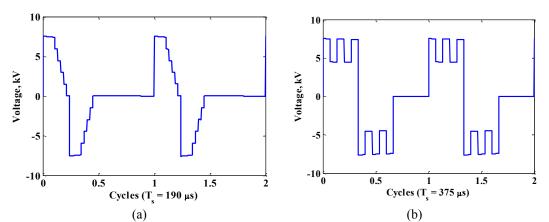

Fig.3.3. Generated HV pulses: (a) Bipolar rectangular. (b) Unipolar rectangular.

#### 3.1.1 Clamping PG Converter Topology

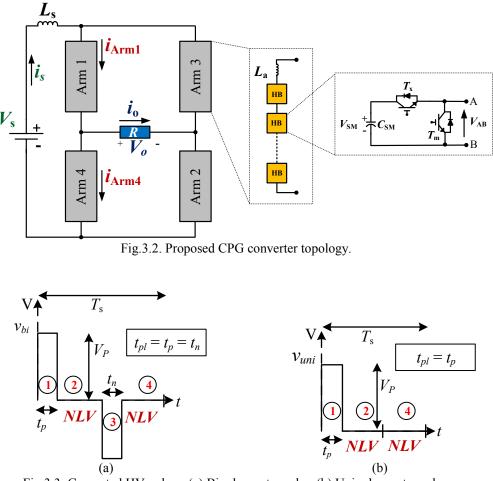

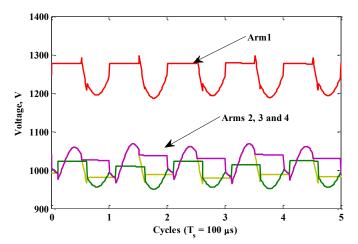

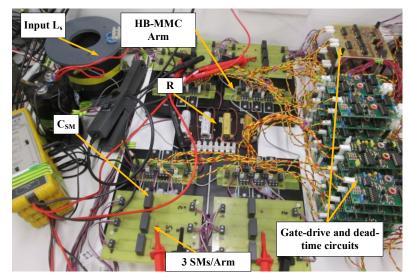

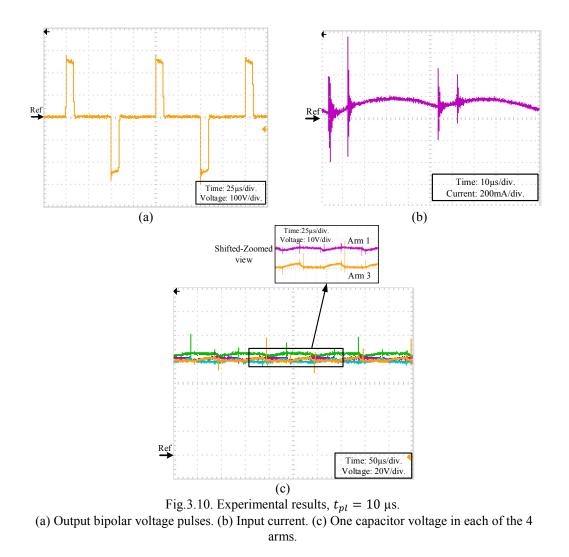

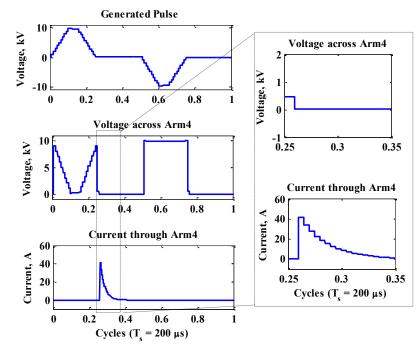

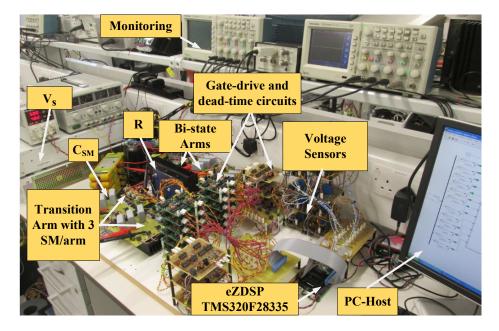

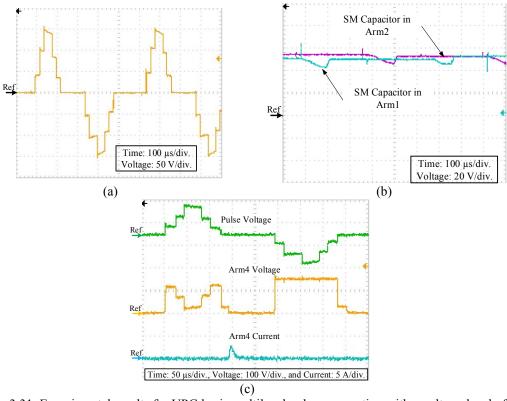

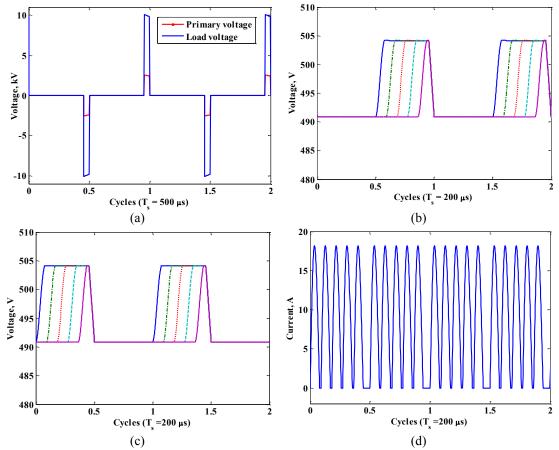

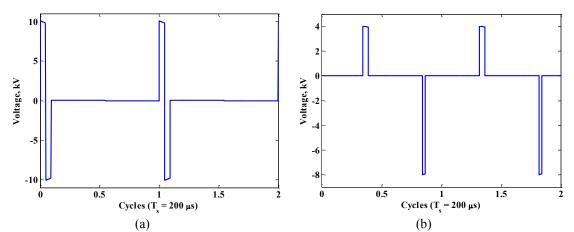

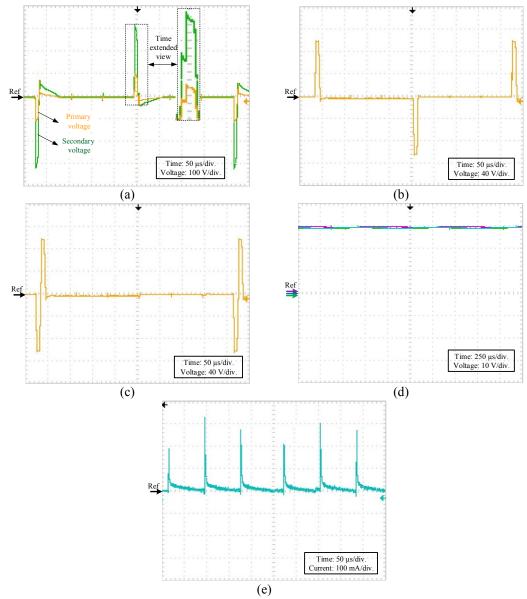

In order to avoid series device connection challenges, a clamp based PG (CPG) topology is proposed to generate rectangular HV pulses based on MMC HB-SMs without voltage sensors as shown in Fig.3.2 [69]. It consists of four MMC arms (Arm z, where  $z \in \{1, 2, 3, 4\}$ ) forming an H-bridge connected to HVDC supply  $V_s$  via an inductor  $L_s$ . Each arm is of N series connected MMC HB-SMs and an arm inductor  $L_a$  to suppress inrush current between SM capacitors during their insertion. Depending on the switching sequence of the complimentary switches  $T_m$  and  $T_x$ , the SM-terminal voltage  $V_{AB}$  is either equal to the capacitor-voltage  $V_{SM}$  or zero, as illustrated in the HB-SM switching table in Fig.2.12a.

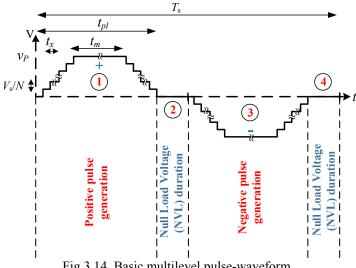

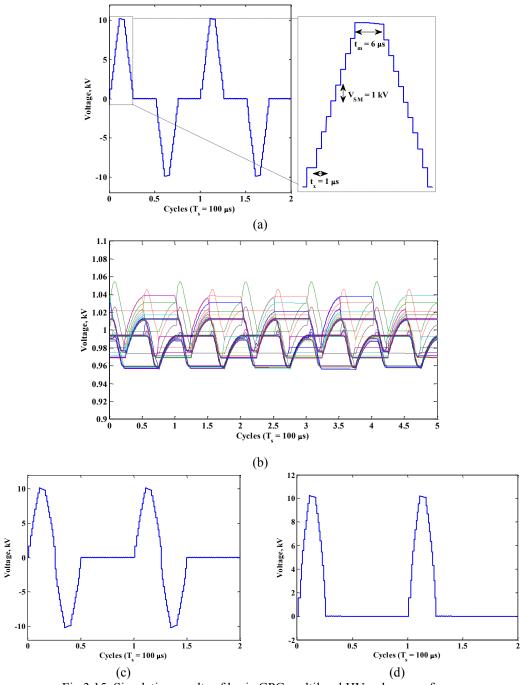

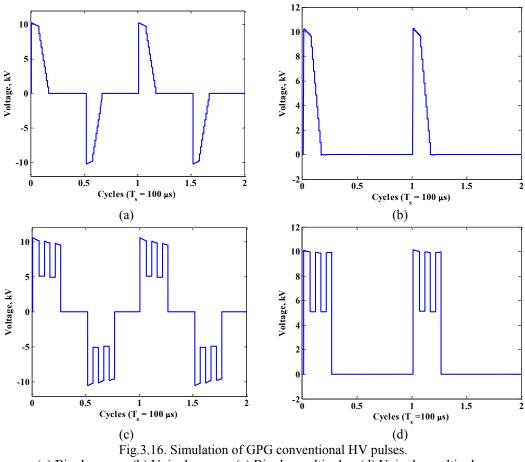

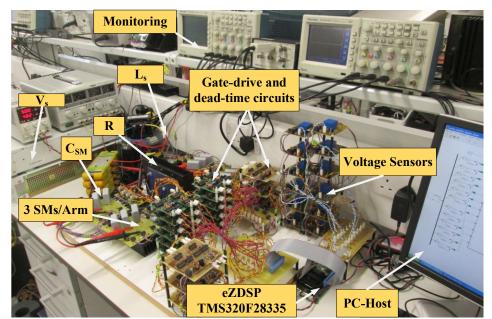

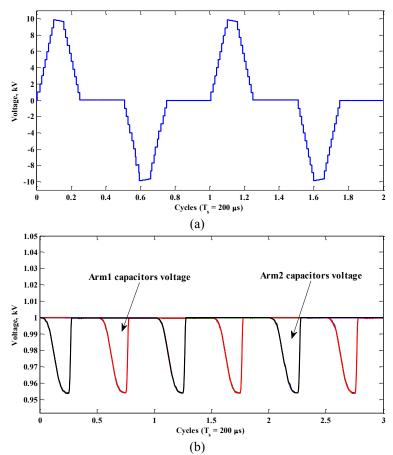

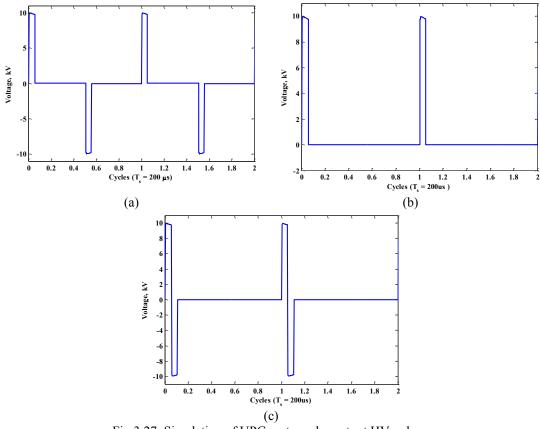

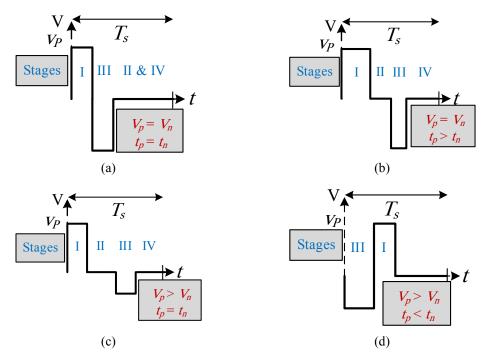

The proposed converter is capable of generating the rectangular bipolar  $(v_{bi})$  and unipolar  $(v_{uni})$  HV pulses shown in Fig.3.3a and Fig.3.3b, respectively. The

controlling parameters are: repetition time  $T_s$  and pulse duration  $t_{pl}$ . For flexibility, each pulse polarity has a dedicated pulse duration,  $t_p$  and  $t_n$  for the positive and negative pulse polarities, respectively. If symmetrical pulse polarity durations are generated as in Fig.3.3a, then  $t_p = t_n = t_{pl}$ . The generated pulses can be defined by the time durations in (3.1) and (3.2), where each pulse polarity is followed by a null load voltage (NLV) duration (of 0V), for bipolar and unipolar pulses respectively, see Fig.3.3.

$$v_{bi} = \begin{cases} +V_{P} &, & 0 \le t < t_{pl} \\ 0 \text{ (positive NLV)}, & t_{pl} \le t < \frac{1}{2}T_{s} \\ -V_{P} &, & \frac{1}{2}T_{s} \le t < \frac{1}{2}T_{s} + t_{pl} \\ 0 \text{ (negative NLV)}, & \frac{1}{2}T_{s} + t_{pl} \le t < T_{s} \end{cases}$$

$$v_{uni} = \begin{cases} \pm V_{P} &, & 0 \le t < t_{pl} \\ 0 \text{ (positive NLV)}, & t_{pl} \le t < \frac{1}{2}(T_{s} + t_{pl}) \\ 0 \text{ (negative NLV)}, & \frac{1}{2}(T_{s} + t_{pl}) \le t < T_{s} \end{cases}$$

(3.1)

$$(3.1)$$

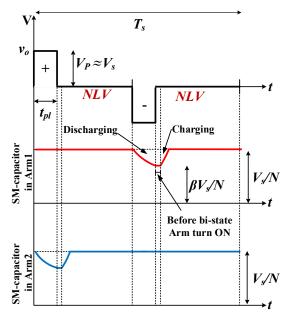

### 3.1.2 CPG Operating Principle

The same methodology is used to generate unipolar and bipolar rectangular pulses. The only difference is the omission of one polarity during pulse generation. Accordingly, the following discussion will consider bipolar pulse generation to illustrate the basic concept. The load is modelled as a resistive load R as illustrated in Chapter 1. For proper operation, each arm should be able to withstand the DC-link voltage  $V_s$ , therefore, each SM-capacitor voltage is:

$$V_{SM} = \frac{V_s}{N} \tag{3.3}$$

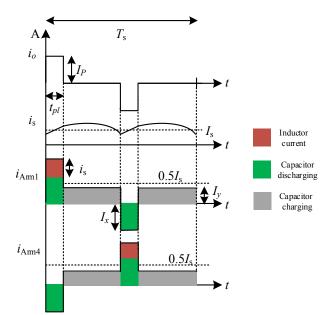

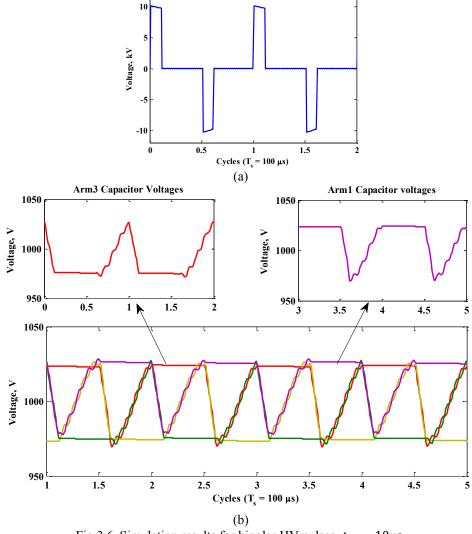

Table 3.1 shows the circuit configuration and summarises the operating sequence in each period. Generally, during positive pulse generation Arm3 and Arm4 capacitors are inserted to discharge across the load, while Arm1 and Arm2 are inserted during negative pulse generation. The positive and negative NLV durations in (3.1) allow charging of the lower arms and the upper arms, respectively.

The utilised MMC SMs in each arm are all inserted/bypassed simultaneously, therefore, each IGBT switch is subjected only to the SM voltage. Thus, the SM capacitor clamps the IGBT voltage and enforces a symmetrical series voltage distribution. In both charging and discharging, the arm SM capacitors are inserted together presenting a total capacitance of  $C_{SM}/N$  per arm.

|                | Circuit configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Sequence of operation                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Positive Pulse | $\begin{array}{c} 1 \\ \hline \\ I \\ \hline \\ V_{s} \\ \hline \\ V_{s} \\ \hline \\ \hline \\ C_{4} \\ \hline \\ C_{4} \\ \hline \\ \hline \\ C_{4} \\ \hline \\ \hline \\ C_{4} \\ \hline \\ \hline \\ \\ C_{4} \\ \hline \\ \hline \\ \\ \hline \\ \\ C_{4} \\ \hline \\ \hline \\ \\ \\ \hline \\ \hline \\ \\ \hline \\ \hline \\ \\ \hline \\ \\ \hline \\ \hline \\ \\ \hline \\ \hline \\ \hline \\ \\ \hline \\ \hline \\ \hline \\ \\ \hline \\ \hline \\ \\ \hline \\ \hline \\ \hline \\ \hline \\ \\ \hline \\ \\ \hline \hline \\ \hline \hline \\ \hline \\ \hline \\ \hline \\ \hline \hline \\ \\ \hline \hline \\ \hline \\ \hline \\ \hline \\ \hline \hline \\ \hline \hline \\ \hline \\ \hline \hline \\ \hline \\ \hline \hline \\ \hline \hline \\ \hline \\ \hline \hline \hline \\ \hline \hline \\ \hline \hline \hline \hline \\ \hline \hline \hline \\ \hline \hline \hline \hline \\ \hline \hline \hline \\ \hline \hline \hline \hline \\ \hline \hline \hline \hline \hline \hline \\ \hline \hline$ | <ul> <li>Arm3 and Arm4, C<sub>3</sub> and C<sub>4</sub>, capacitors are inserted simultaneously while Arm1 and Arm2 are bypassed such that load voltage is +V<sub>s</sub>.</li> <li>Load current flows due to a combination of three energy sources; C<sub>3</sub>, C<sub>4</sub> and L<sub>s</sub>.</li> <li>C<sub>3</sub> and C<sub>4</sub> discharge during this period.</li> </ul> |

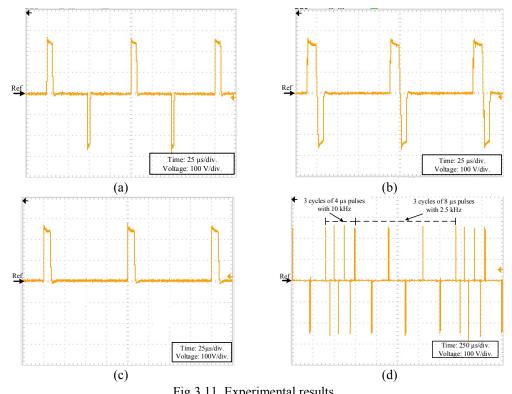

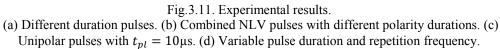

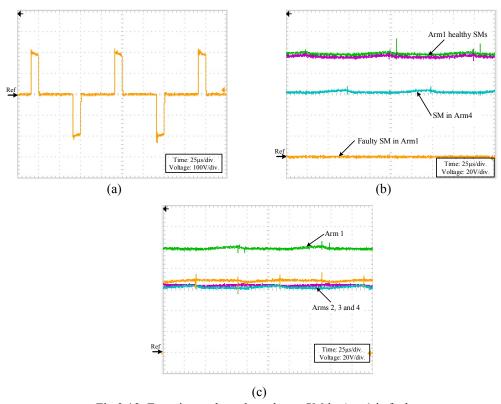

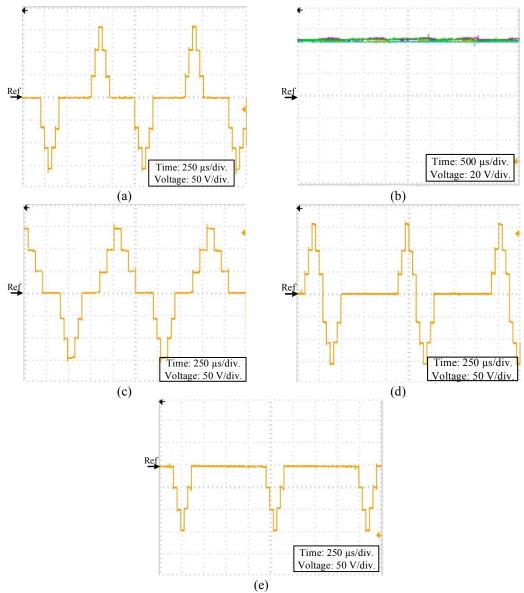

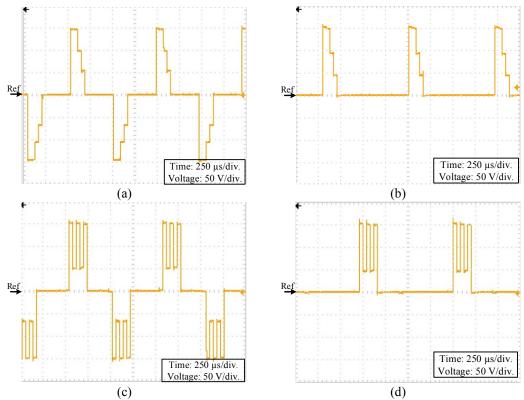

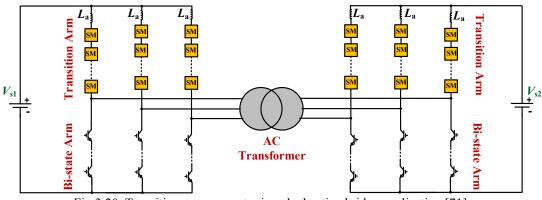

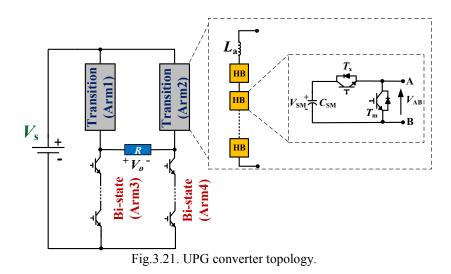

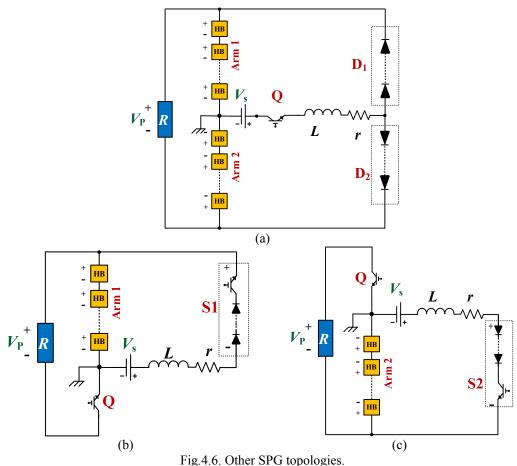

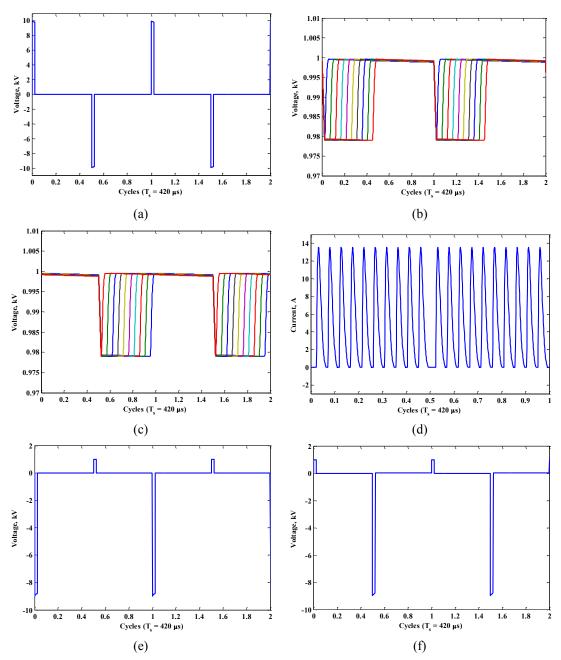

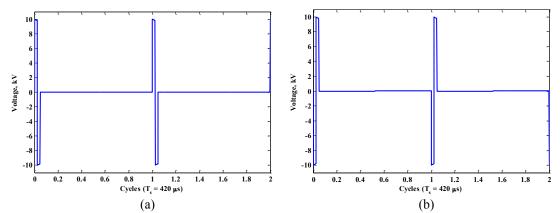

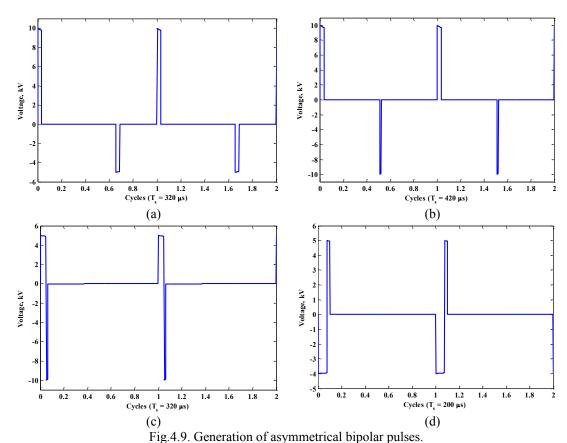

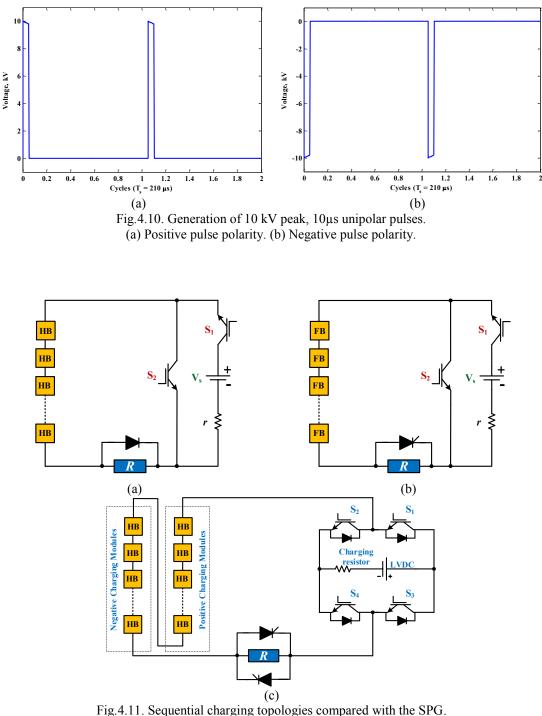

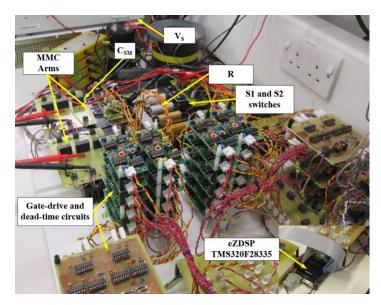

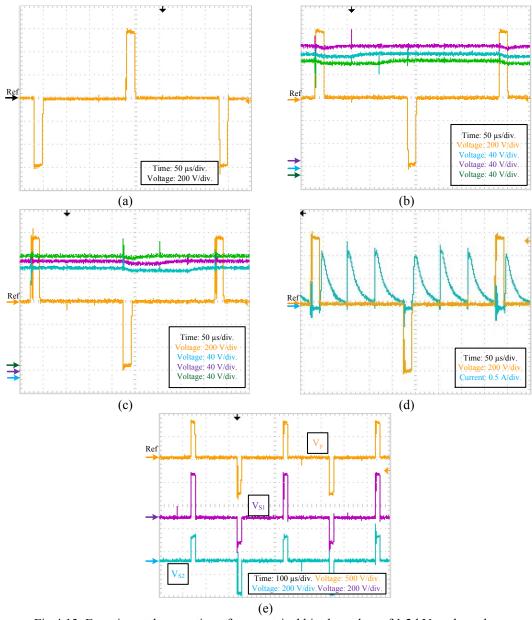

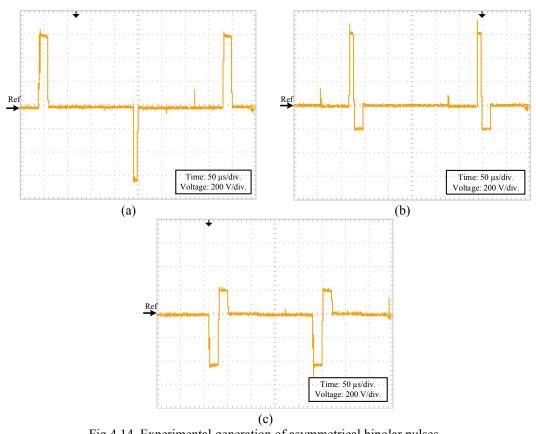

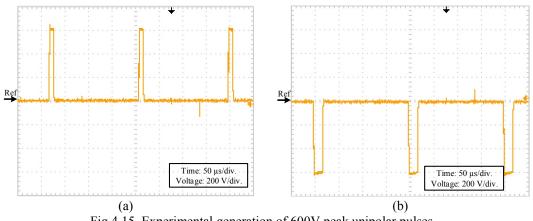

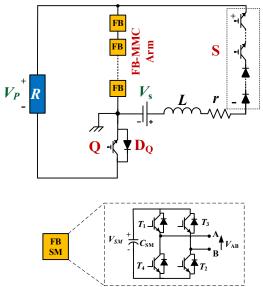

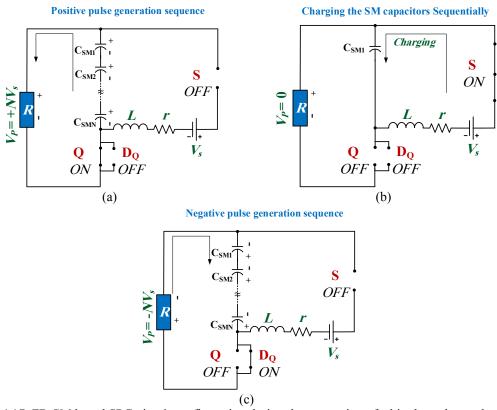

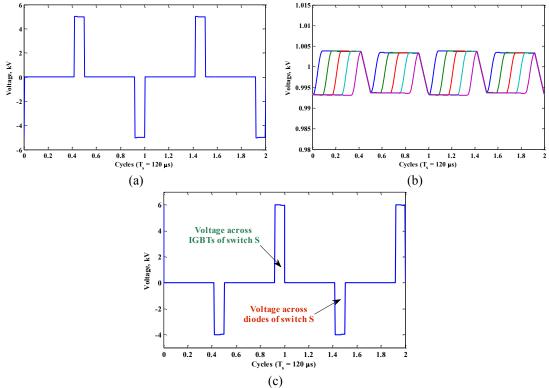

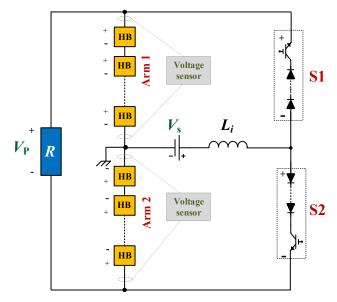

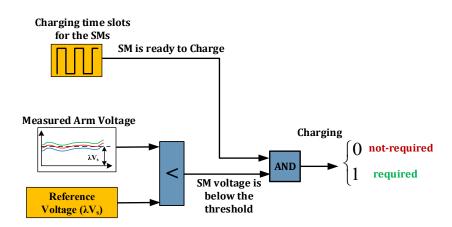

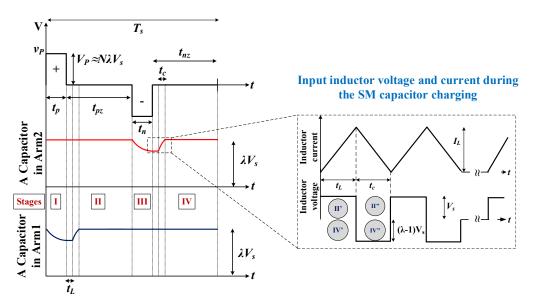

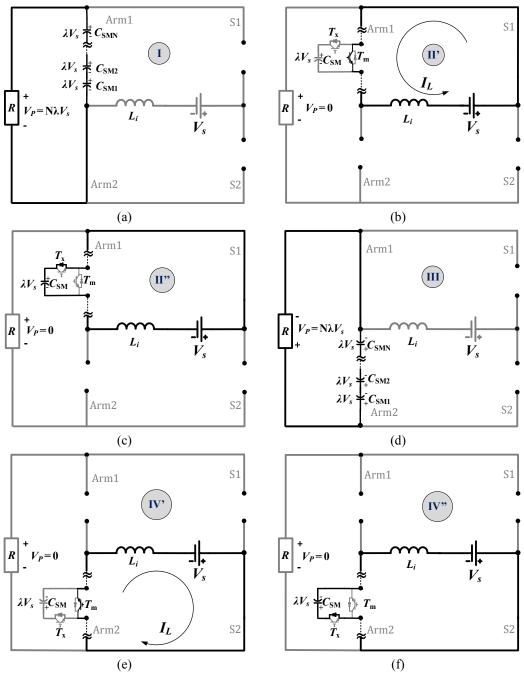

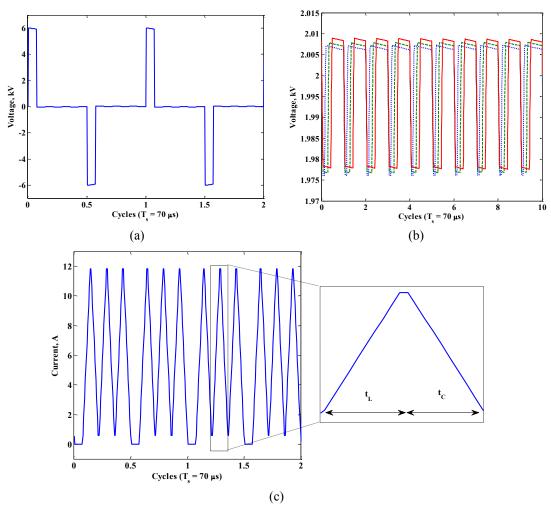

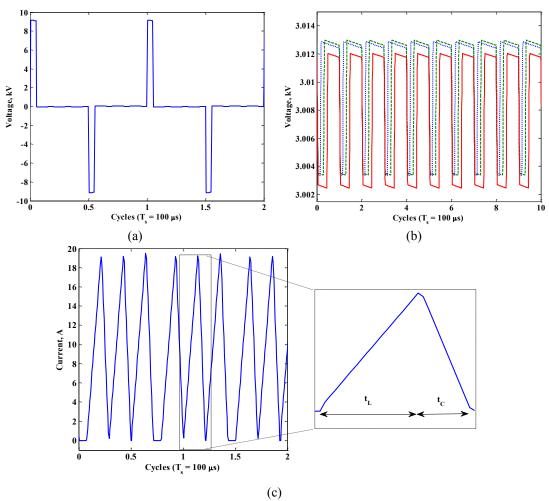

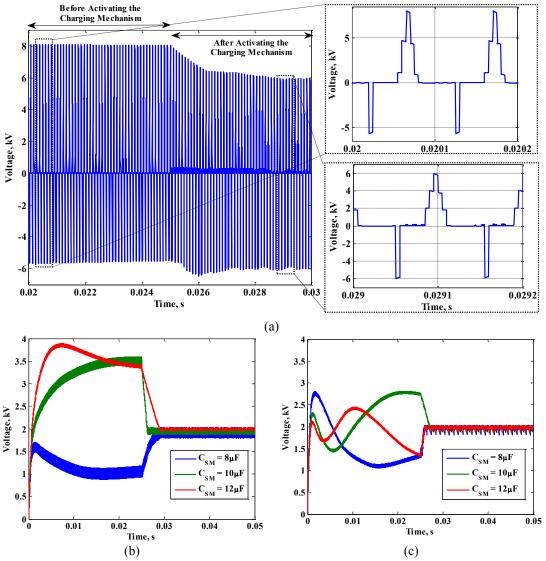

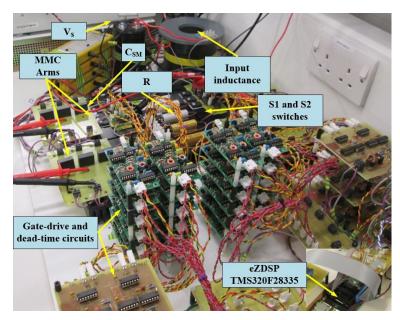

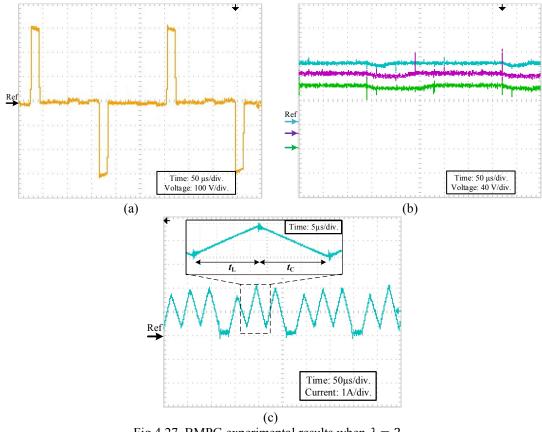

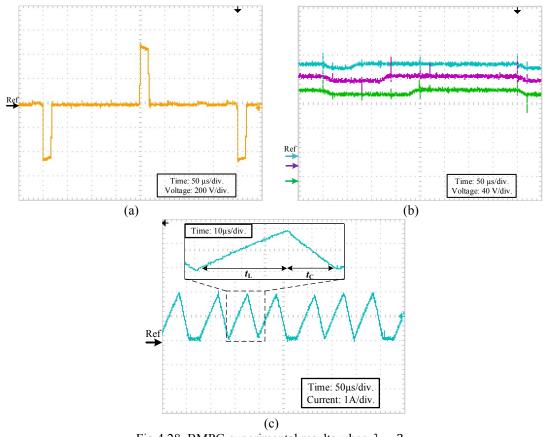

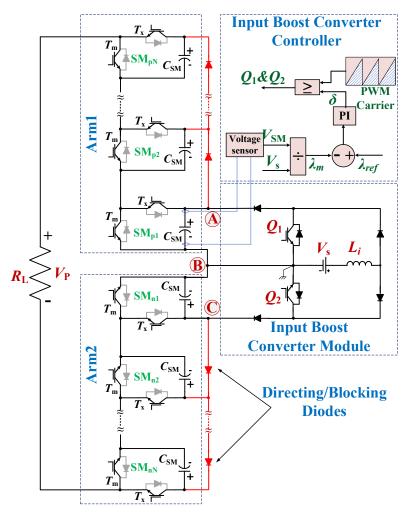

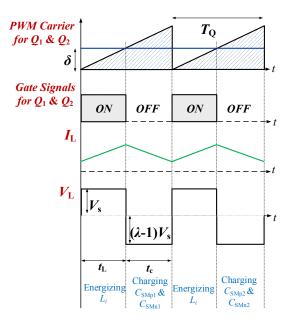

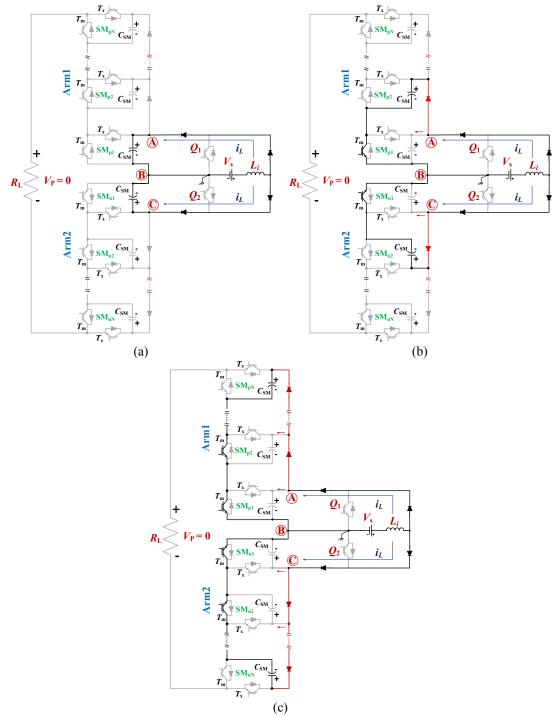

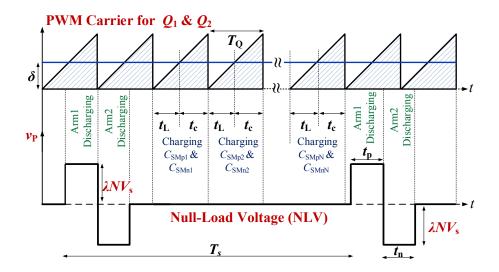

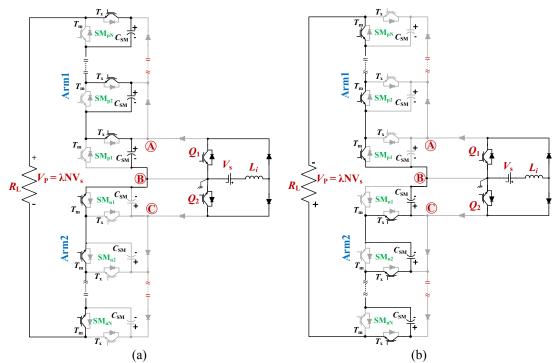

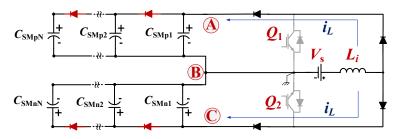

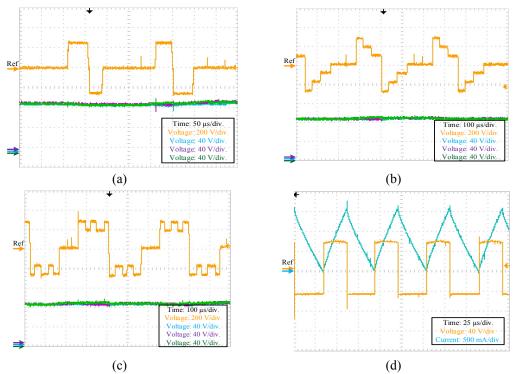

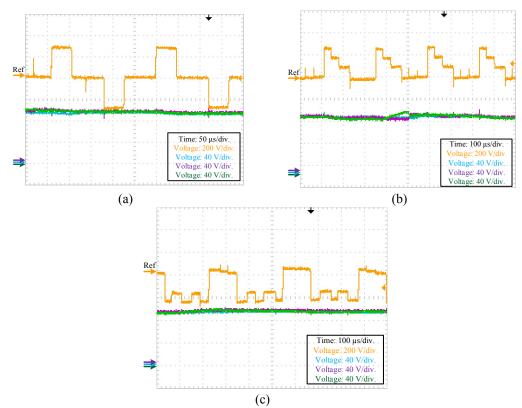

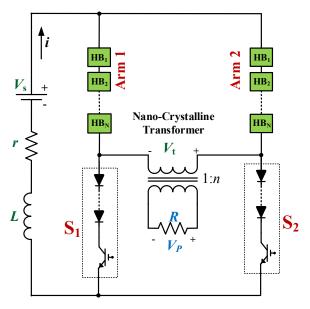

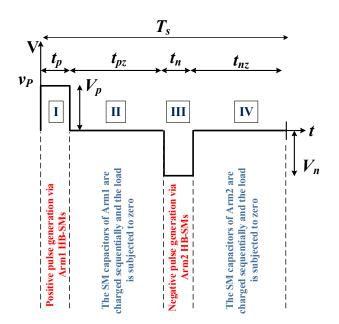

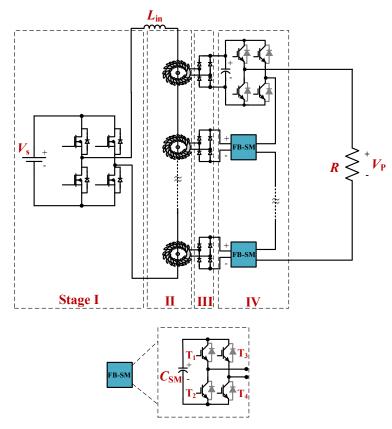

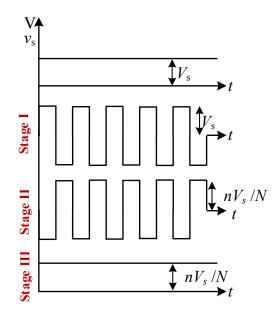

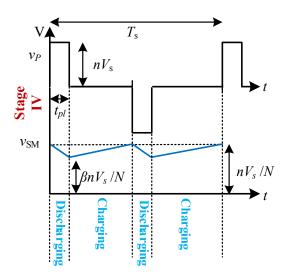

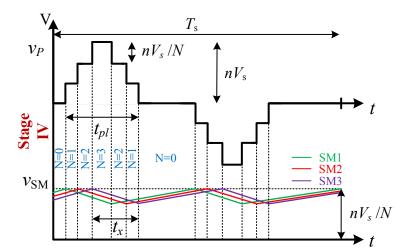

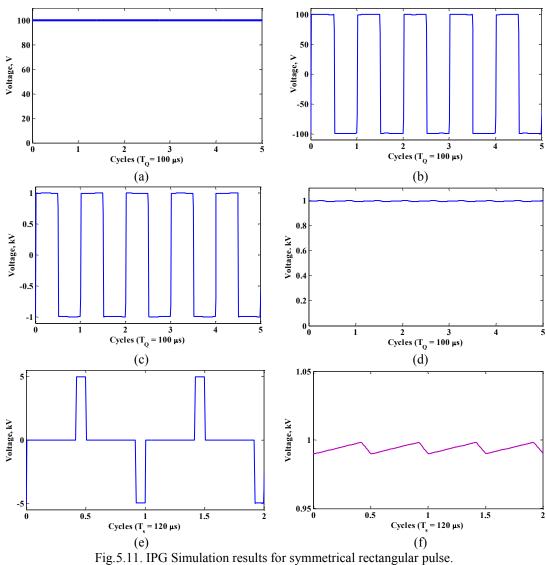

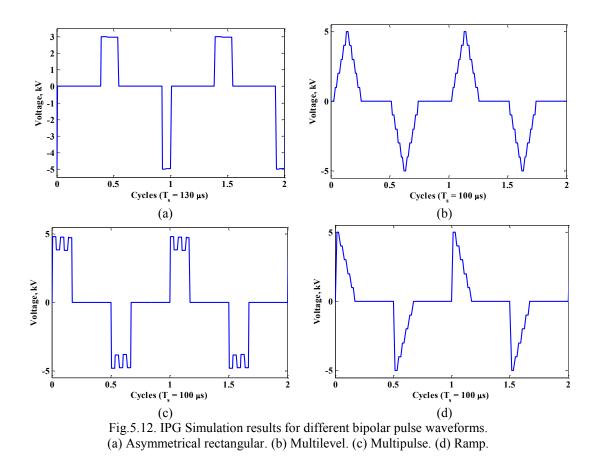

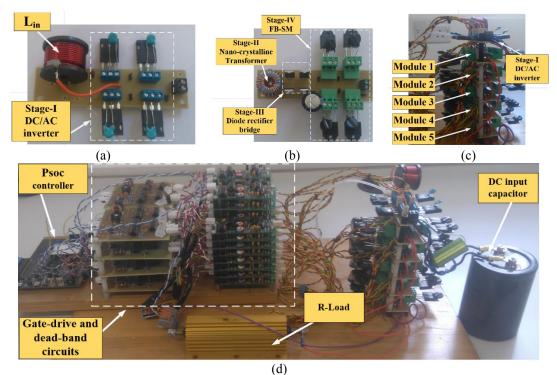

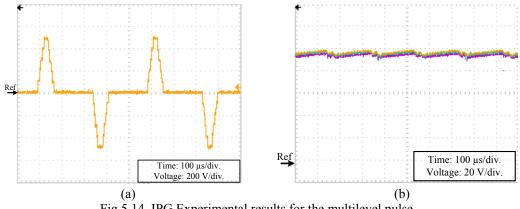

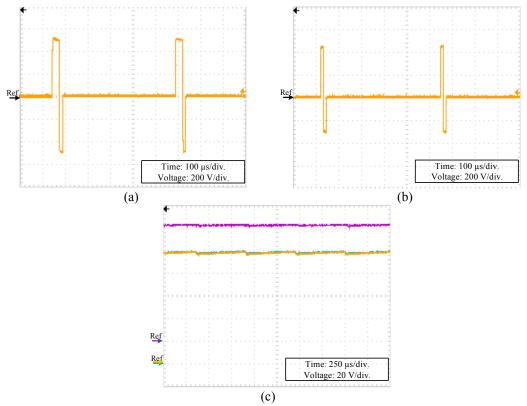

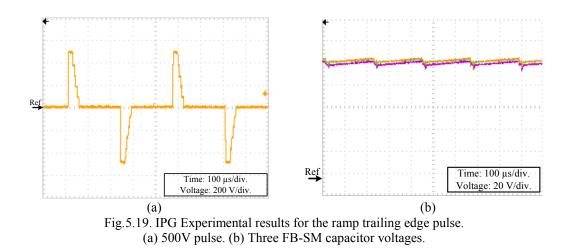

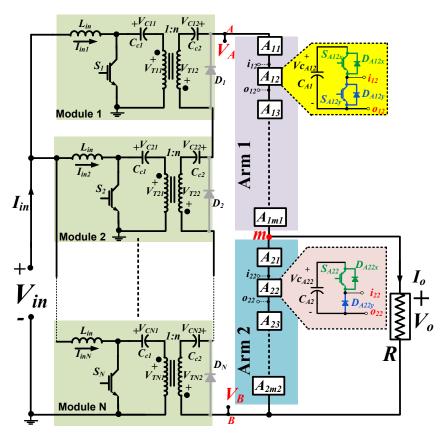

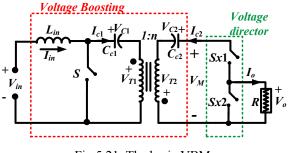

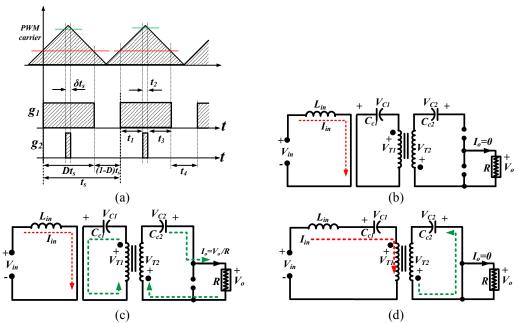

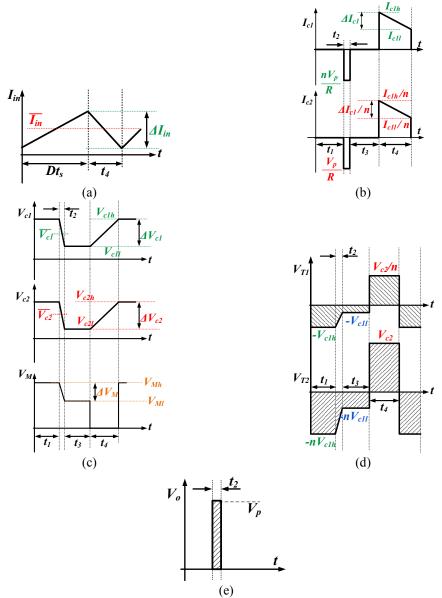

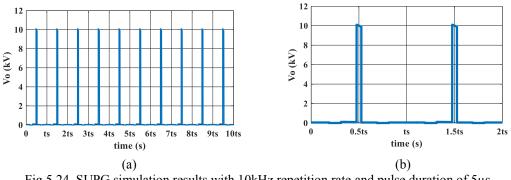

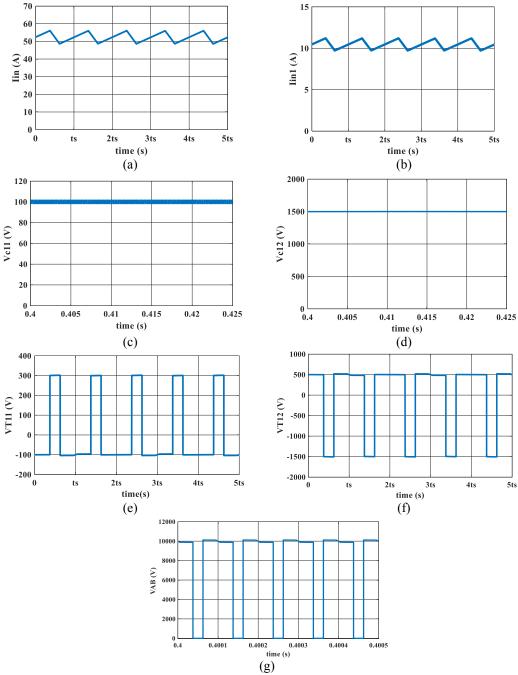

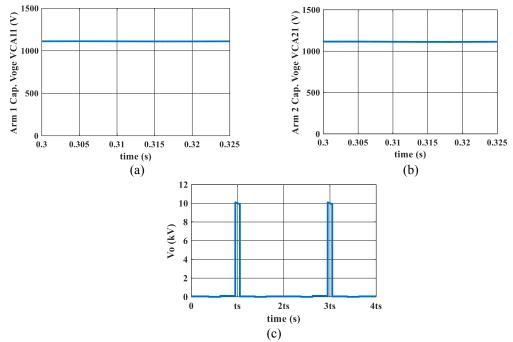

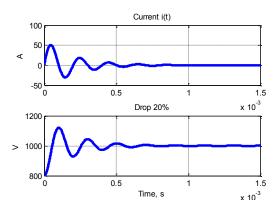

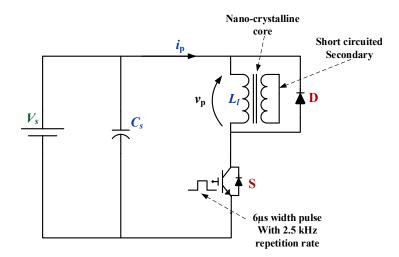

| Positive NLV   | $\begin{array}{c} \mathbf{L}_{s} \\ \hline 2 \\ \mathbf{V}_{s} \\ \mathbf{V}_{$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>Arm2 and Arm4, C<sub>2</sub> and C<sub>4</sub>, capacitors are inserted, Arm1 and Arm3 are bypassed, hence the load voltage is nullified.</li> <li>The load current is zero.</li> <li>C<sub>2</sub> and C<sub>4</sub> are charged through L<sub>s</sub> during this period.</li> </ul>                                                                                        |