Research and Development of Diagnostic Algorithms to Support Fault Accommodating Control for Emerging Shipboard Power System Architectures

Ruturaj R. Soman

A thesis submitted for the degree of Doctor of Philosophy to Institute for Energy and Environment University of Strathclyde

June 2013

This thesis is the result of the author's original research. It has been composed by the author and has not been previously submitted for examination which has led to the award of a degree.

The copyright of this thesis belongs to the author under the terms of the United Kingdom Copyright Acts as qualified by University of Strathclyde Regulation 3.50. Due acknowledgement must always be made of the use of any material contained in, or derived from, this thesis.

Signed:

Date:

### Abstract

The U.S. Navy has proposed development of next generation warships utilising an increased amount of power electronics devices to improve flexibility and controllability. The high power density finite inertia network is envisioned to employ automated fault detection and diagnosis to aid timely remedial action. Integration of condition monitoring and fault diagnosis to form an intelligent power distribution system is anticipated to assist decision support for crew while enhancing security and mission availability.

This broad research being in the conceptual stage has lack of benchmark systems to learn from. Thorough studies are required to successfully enable realising benefits offered by using increased power electronics and automation. Application of fundamental analysis techniques is necessary to meticulously understand dynamics of a novel system and familiarisation with associated risks and their effects. Additionally, it is vital to find ways of mitigating effects of identified risks.

This thesis details the developing of a generalised methodology to help focus research into artificial intelligence (AI) based diagnostic techniques. Failure Mode and Effects Analysis (FMEA) is used in identifying critical parts of the architecture. Sneak Circuit Analysis (SCA) is modified to provide signals that differentiate faults at a component level of a dc-dc step down converter. These reliability analysis techniques combined with an appropriate AI-algorithm offer a potentially robust approach that can potentially be utilised for diagnosing faults within power electronic equipment anticipated to be used onboard the novel SPS.

The proposed systematic methodology could be extended to other types of power electronic converters, as well as distinguishing subsystem level faults. The combination of FMEA, SCA with AI could also be used for providing enhanced decision support. This forms part of future research in this specific arena demonstrating the positives brought about by combining reliability analyses techniques with AI for next generation naval SPS.

## Acknowledgments

Foremost, I would like to thank Prof. Stephen McArthur for giving me an opportunity to undertake a PhD programme at the University of Strathclyde and for his constant support, supervision and encouragement. I would also like to thank Mr. Euan Davidson for his valuable inputs and guidance during the entire research work. Thanks are due to Dr. John Fletcher for his unwavering help with technical issues and especially hardware tests. I would also like to thank Mr. Alex Mair for expert advice on Weka.

Further, I would like to thank researchers at Center for Advanced Power Systems (CAPS) – Florida State University (FSU), USA, Dr. Dave Cartes, Dr. Sanjeev Srivastava and Dr. Karl Schoder for their periodic assistance during the entire PhD research.

I am grateful to my family, for their untiring, unconditional love and support, without which I would have accomplished nothing.

## Contents

| List o | f Figure | S                                                                | VIII |

|--------|----------|------------------------------------------------------------------|------|

| List o | f Tables |                                                                  | XI   |

| List o | f Equat  | ons                                                              | XIII |

| Gloss  | ary of A | bbreviations                                                     | XIV  |

| Chap   | ter 1 R  | esearch Background                                               | 1    |

| 1.1    | Intro    | duction to research arena                                        | 1    |

| 1.2    | Justi    | ication and rationale for research                               | 2    |

| 1.3    | Rese     | arch novelty and contribution                                    | 3    |

| 1.4    | Thes     | s structure                                                      | 5    |

| 1.5    | Asso     | ciated publications                                              | 6    |

| Chap   | ter 2 L  | iterature Review                                                 | 8    |

| 2.1    | Intro    | duction                                                          | 8    |

| 2.2    | Envis    | sioned SPS analyses, modelling, stability and risk assessment    | 8    |

|        | 2.2.1    | Discussion                                                       | 14   |

| 2.3    | SPS a    | automated reconfiguration, restoration and load shedding         | 14   |

|        | 2.3.1    | Discussion                                                       | 20   |

| 2.4    | SPS 1    | related automated fault detection, diagnosis and prognosis       | 20   |

|        | 2.4.1    | Discussion                                                       | 31   |

| 2.5    | Chap     | ter summary and conclusion                                       | 31   |

| Chap   | ter 3 L  | iterature Review: Power electronics                              |      |

| 3.1    | Intro    | duction                                                          | 33   |

| 3.2    | Powe     | er electronics development and device/component level diagnostic |      |

| rese   | arch     |                                                                  | 33   |

|        | 3.2.1    | Discussion                                                       | 44   |

| 3.3    | Conc     | ept of fault accommodation                                       | 45   |

|        | 3.3.1    | Discussion                                                       | 46   |

| 3.4   | Related research publications                        | 48 |

|-------|------------------------------------------------------|----|

|       | 3.4.1 Discussion                                     | 49 |

| 3.5   | Chapter summary and conclusion                       | 50 |

| Chapt | ter 4 Application of reliability analysis techniques |    |

| 4.1   | Introduction                                         |    |

| 4.2   | FMEA applications and research                       | 53 |

|       | 4.2.1 Discussion                                     | 63 |

| 4.3   | Sneak circuit analysis applications and research     | 64 |

|       | 4.3.1 Discussion                                     | 68 |

| 4.4   | Chapter summary and conclusions                      | 68 |

# Chapter 5Application of FMEA for the Shipboard Power System modelstudied70

| 5.1 | Intro | duction                                                 | 70  |

|-----|-------|---------------------------------------------------------|-----|

|     | 5.1.1 | Medium voltage zonal shipboard power system topologies  | 70  |

|     | 5.1.2 | FMEA process                                            | 75  |

|     | 5.1.3 | Two sub-parts of a detailed FMEA                        | 79  |

| 5.2 | Func  | tional FMEA (F-FMEA)                                    | 81  |

|     | 5.2.1 | Ranking of sub-sections and devices to create hierarchy | 81  |

|     | 5.2.2 | F-FMEA at subsystem (zone) level                        | 87  |

|     | 5.2.3 | F-FMEA at device level                                  | 93  |

| 5.3 | Inter | pretation of F-FMEA results                             | 103 |

|     | 5.3.1 | Summary of high-severity functional failure modes       | 104 |

|     | 5.3.2 | Discussion and conclusions                              | 106 |

| 5.4 | H-FN  | MEA for buck converter                                  | 107 |

|     | 5.4.1 | Existing research on component level fault studies      | 108 |

|     | 5.4.2 | H-FMEA in tabular format                                | 112 |

|     | 5.4.3 | Summary of high-severity failure modes                  | 114 |

|       | 5.4.4              | Discussion                                                                   | 115 |

|-------|--------------------|------------------------------------------------------------------------------|-----|

| 5.5   | Chap               | ter summary and conclusions                                                  | 115 |

| Chap  | ter 6 U            | tilisation of Sneak Circuit Analysis for the Fault Accommodating             |     |

| Conti | rol Syste          | m                                                                            | 117 |

| 6.1   | Intro              | luction                                                                      | 117 |

| 6.2   | Sneal              | c circuit analysis (SCA)                                                     | 118 |

| d     | 6.2.1<br>irected g | Obtaining sneak paths for an electrical circuit by constructing its raph     | 118 |

| 6.3   | Simu               | lation studies using proposed approach                                       | 126 |

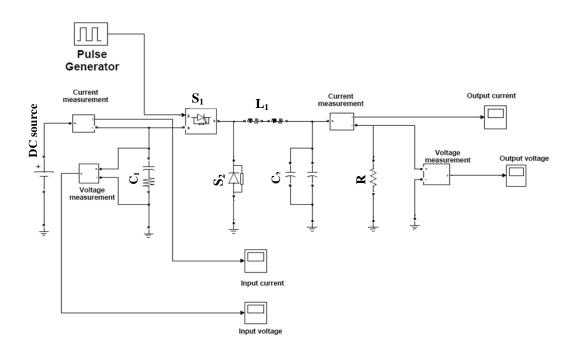

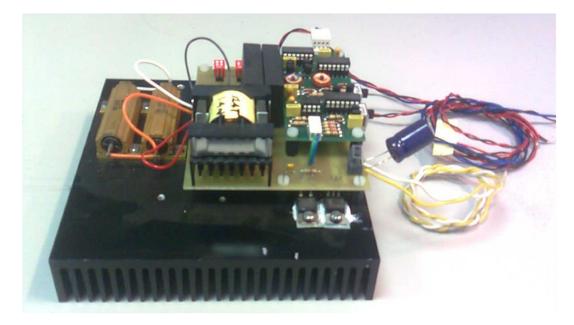

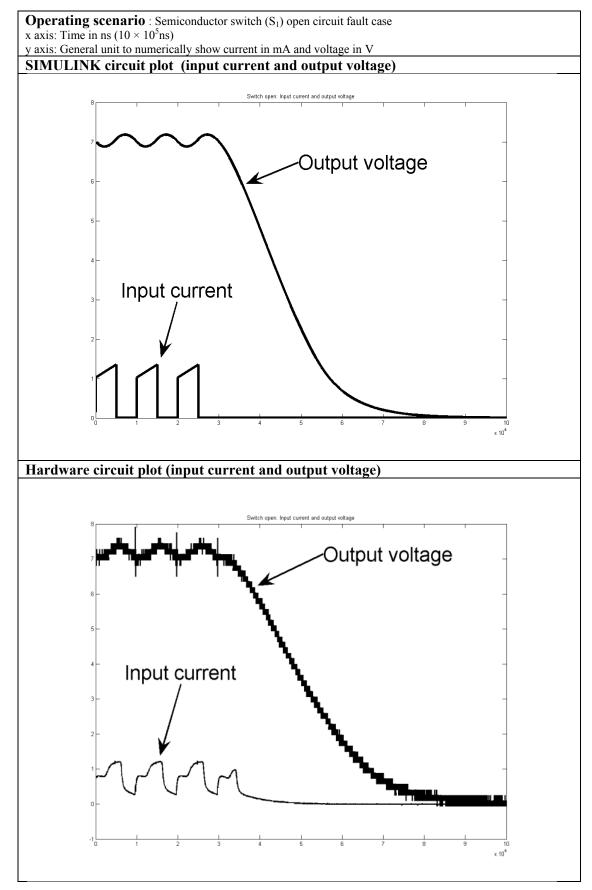

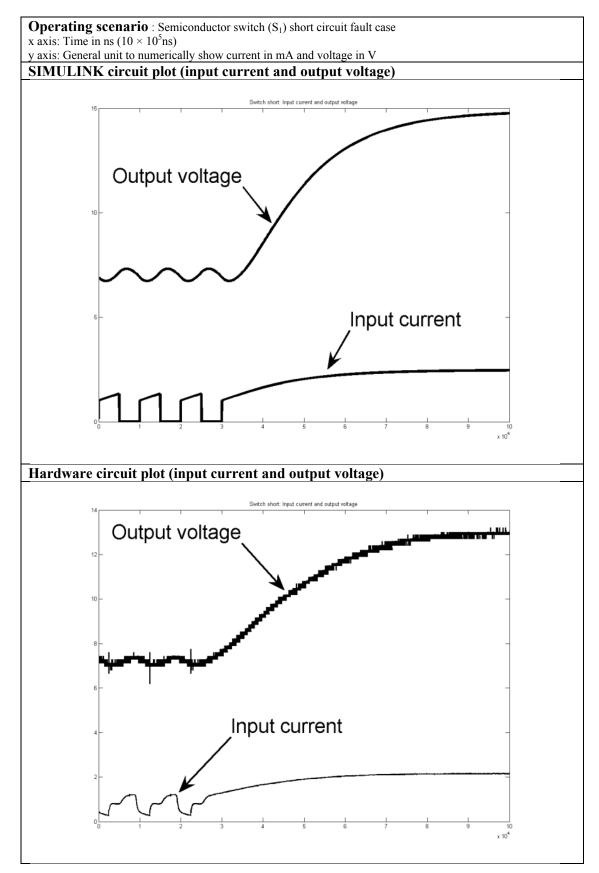

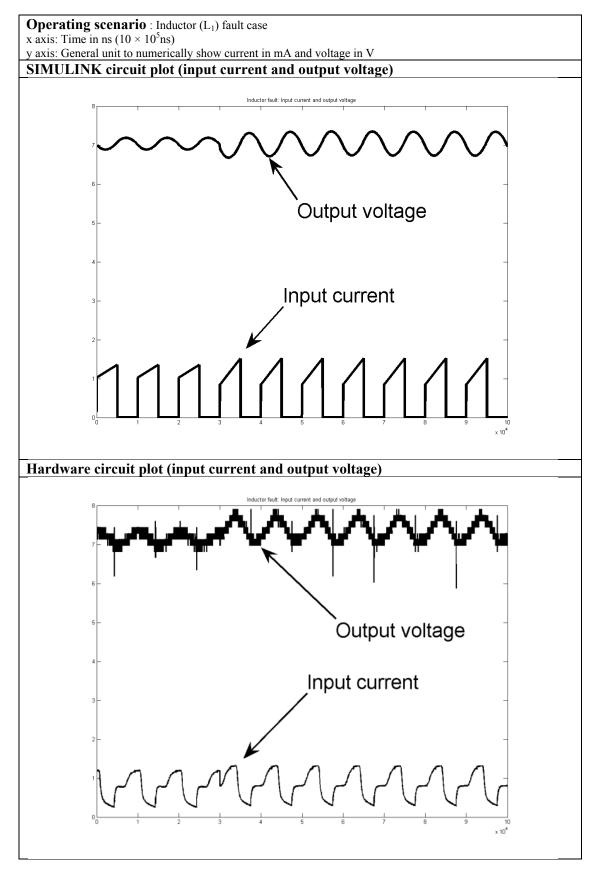

| С     | 6.3.1<br>orrespon  | Buck converter modelled in SIMULINK to generate data and ding hardware setup | 126 |

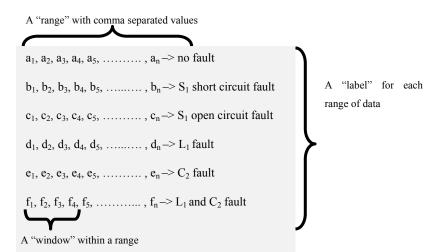

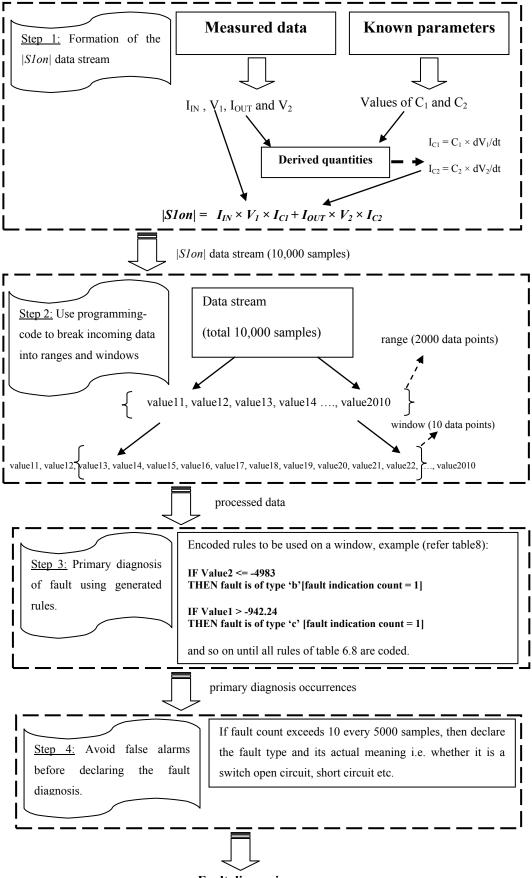

|       | 6.3.2              | Data preparation for heuristic classification                                | 130 |

|       | 6.3.3              | Comparison of classification results and their interpretation                | 136 |

|       | 6.3.4              | Application of results and avoiding false alarms                             | 139 |

|       | 6.3.5              | Training hardware data on software data generated rules                      | 140 |

| 6.4   | Gene               | ration of rules for different duty cycles of buck converter                  | 149 |

|       | 6.4.1              | Heuristics for duty cycles ranging from 10% to 95%                           | 149 |

|       | 6.4.2              | Training rules on data of a particular duty cycle to test on another         | 164 |

| 6.5   | Discu              | ission and issues                                                            | 171 |

|       | 6.5.1              | Rationale for using SCA alongside FMEA                                       | 171 |

|       | 6.5.2              | Relevance and benefits of proposed approach                                  | 172 |

|       | 6.5.3              | Fault introduction procedure in hardware circuit and avoiding false          |     |

| a     | larms              | 172                                                                          |     |

|       | 6.5.4              | Results of training hardware data on software rules                          | 173 |

|       | 6.5.5              | Observability condition and effective series resistance (ESR)                | 174 |

|       | 6.5.6              | Scalability issue of proposed method                                         | 175 |

|       | 6.5.7              | Application of proposed method for other DC-DC converters                    | 175 |

|       | 6.5.8              | Expanding rule set for different duty cycles                                 | 182 |

| 6.6    | Summary and conclusions                               |     |

|--------|-------------------------------------------------------|-----|

|        | 6.6.1 Future research plans                           |     |

| Chapt  | er 7 Research Summary, On-going and Future Directions |     |

| 7.1    | Summary of chapters                                   |     |

| 7.2    | Re-emphasizing benefits of FMEA                       |     |

| 7.3    | Revisiting the research novelty                       | 191 |

| 7.4    | Ongoing research that extends from this thesis        |     |

| 7.5    | Future research                                       |     |

| 7.6    | Overall conclusions                                   |     |

| Refere | ences 199                                             |     |

# List of Figures

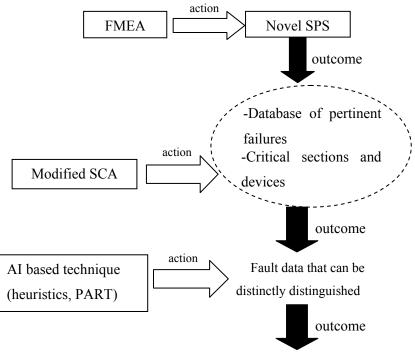

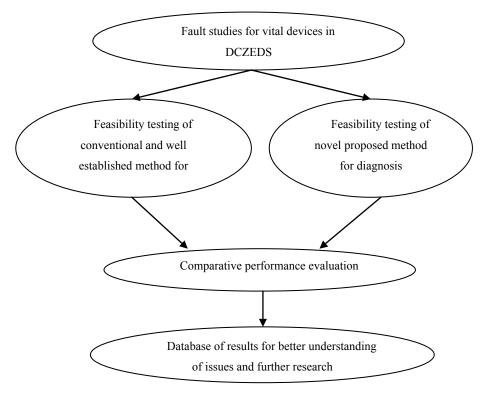

| Figure 1.1: Approach proposed in this thesis for developing a potentially robust    |

|-------------------------------------------------------------------------------------|

| methodology to help diagnose faults                                                 |

| Figure 2.1: (a) ACZEDS representation [16], (b) DCZEDS representation [16] 10       |

| Figure 2.2: Two layered MAS for SPS with devices having their own software agents   |

| [23]                                                                                |

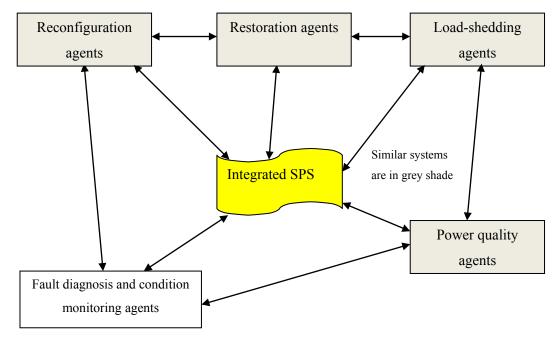

| Figure 2.3: Various MAS applications for SPS sub-systems [32]22                     |

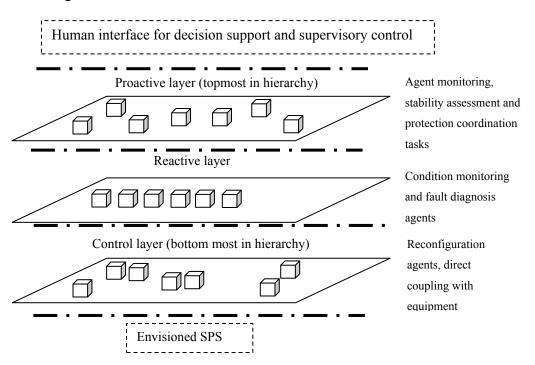

| Figure 2.4: Three layered MAS architecture for SPS [37]25                           |

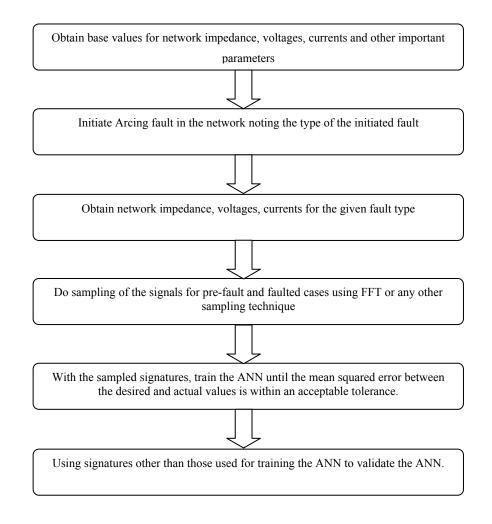

| Figure 2.5: Methodology using well established methods applied to SPS along with    |

| known AI based techniques [38]                                                      |

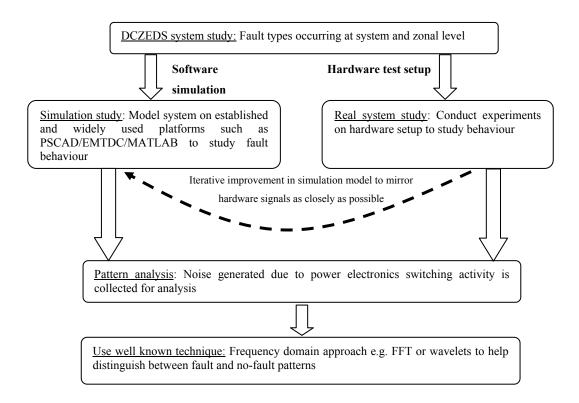

| Figure 2.6: Methodology involving both computer models and matching hardware        |

| setups                                                                              |

| Figure 2.7: Performance evaluation and comparison between conventional and new      |

| methods for DCZEDS fault analysis [42]                                              |

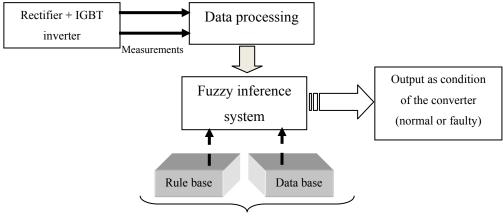

| Figure 3.1: Fuzzy based diagnostic approach for power electronic converter using    |

| heuristic knowledge base [54]40                                                     |

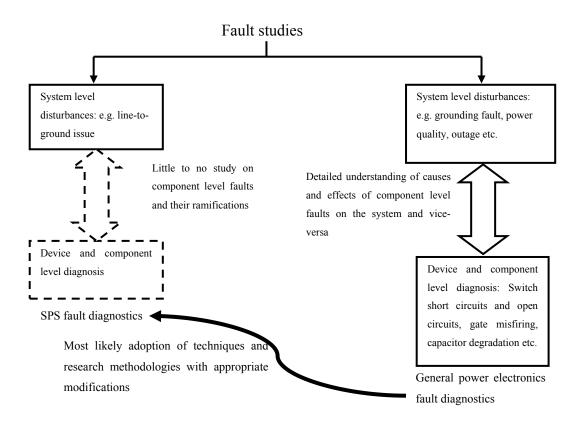

| Figure 3.2: Learning from well established power electronics diagnosis research for |

| application to SPS studies                                                          |

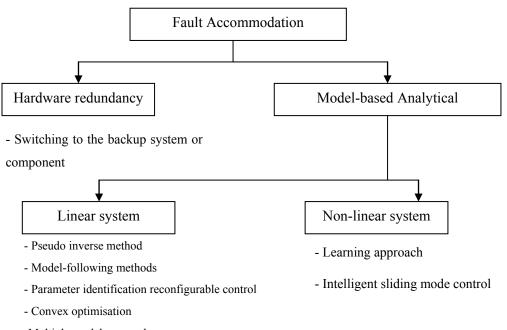

| Figure 3.3: Known fault accommodation techniques [65]47                             |

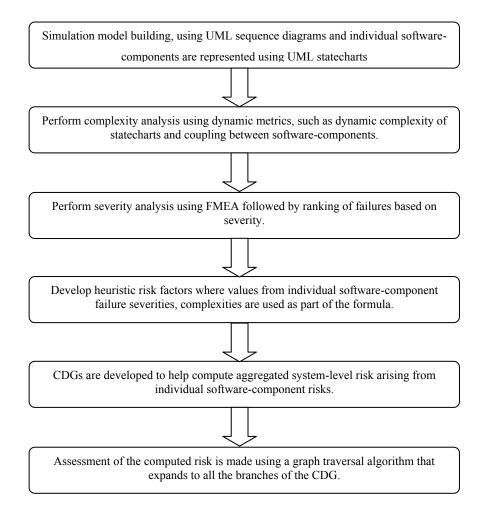

| Figure 4.1: Methodology for risk assessment proposed in [78]                        |

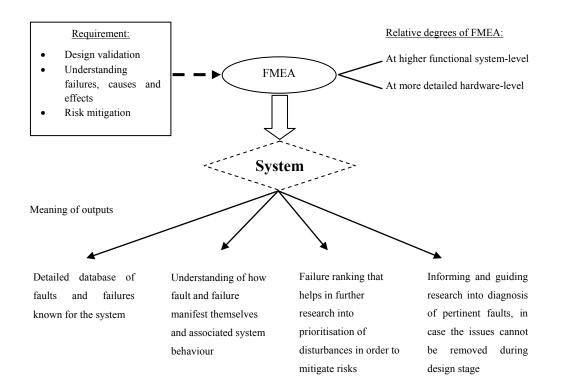

| Figure 4.2: Need for FMEA, its varying degrees and meaning of FMEA outputs for      |

| research                                                                            |

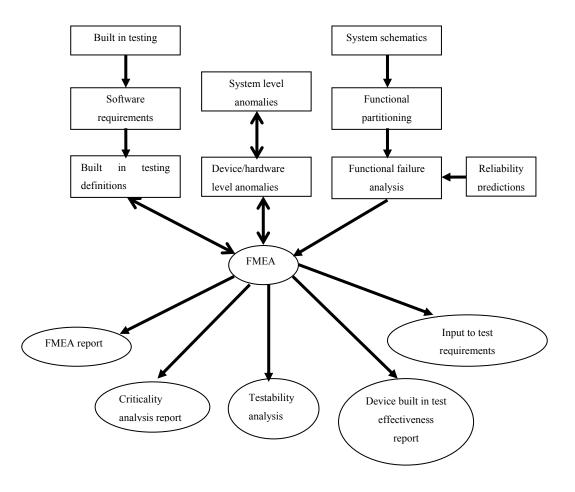

| Figure 4.3: Overview of FMECA [81] with directional arrows that indicate flow of    |

| data                                                                                |

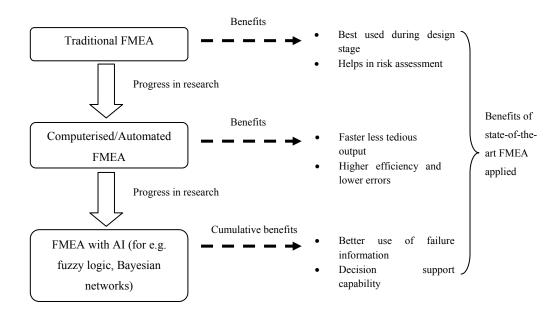

| Figure 4.4: Progress of FMEA research and cumulative benefits of state-of-the-art   |

| FMEA                                                                                |

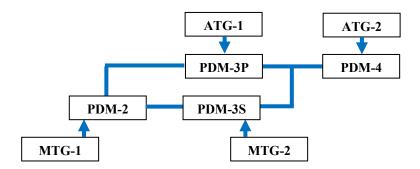

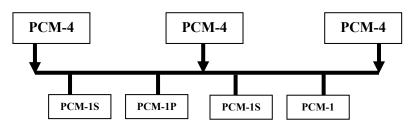

| Figure 5.1: RTDS e-ship model subsystem partitioning (courtesy: CAPS-FSU).          |

| Abbreviations explained in table 5.3                                                |

| Figure 5.2: Alternate majority DC zonal topology modelled on RTDS (courtesy:        |

| CAPS-FSU). Abbreviations similar to those in table 5.3                              |

| Figure 5.3: Load centres (courtesy: CAPS-FSU)75                                     |

| Figure 5.4: Subtle difference between F-FMEA and H-FMEA that add up to produce      |

| a detailed FMEA                                                                     |

| Figure 5.5: Line diagram to represent the modelled SPS                                                    |

|-----------------------------------------------------------------------------------------------------------|

| Figure 5.6: Zone 1-line diagram                                                                           |

| Figure 5.7: Zone 2-line diagram                                                                           |

| Figure 5.8 Zone 3-line diagram                                                                            |

| Figure 5.9: Zone 4, 5 and 6-line diagram                                                                  |

| Figure 5.10: Zone 7 and 8-line diagram                                                                    |

| Figure 5.11: AC power generation ring line diagram                                                        |

| Figure 5.12: DC busses sub-section                                                                        |

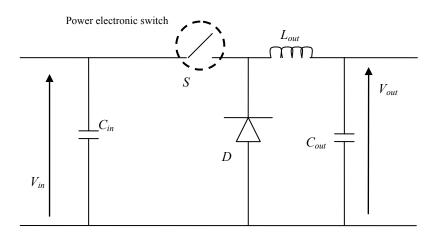

| Figure 5.13: A standard dc-dc buck converter circuit                                                      |

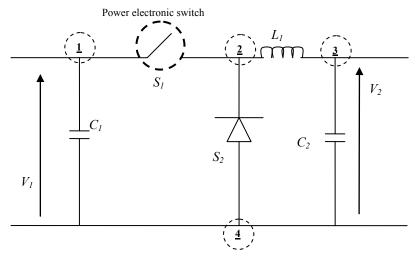

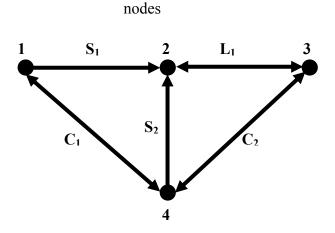

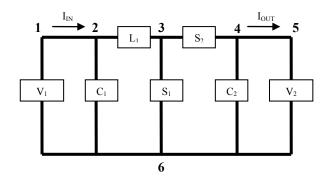

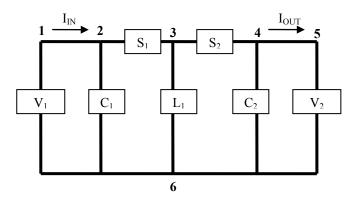

| Figure 6.1: Standard buck converter (dc-dc step down) circuit with numbered nodes                         |

|                                                                                                           |

| Figure 6.2: Directed graph of standard buck converter circuit                                             |

| Figure 6.3: GCM for buck converter directed graph121                                                      |

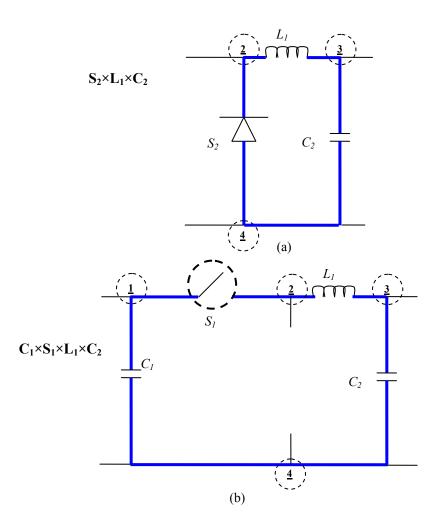

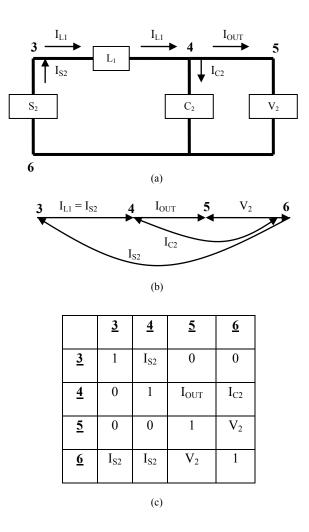

| Figure 6.4: (a) The physical illustration of path represented by term $S_2 \times L_1 \times C_2$ (b) the |

| path represented by term $C_1 \times S_1 \times L_1 \times C_2$                                           |

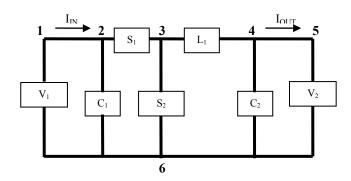

| Figure 6.5: Standard buck converter circuit represented to use for SCA analysis 123                       |

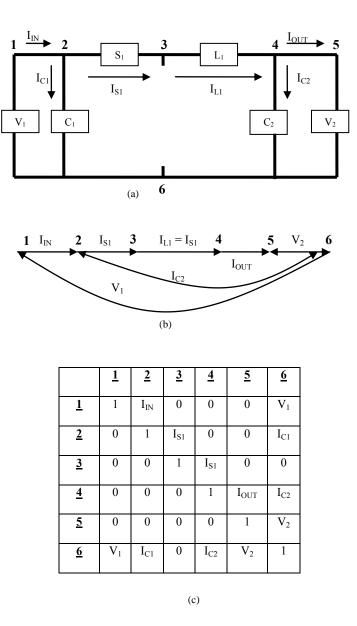

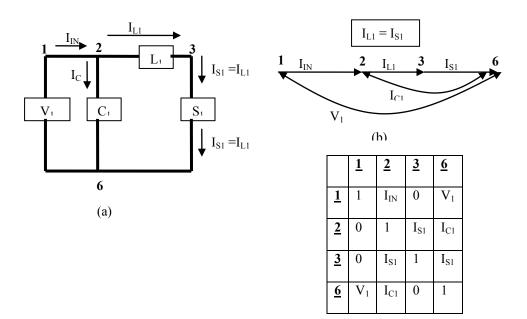

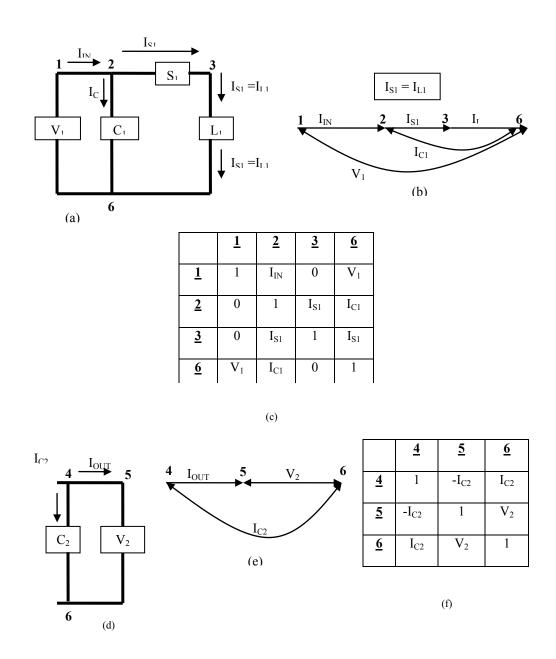

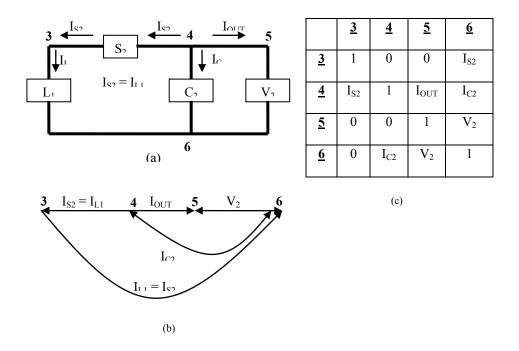

| Figure 6.6: (a) ON state equivalent circuit in which case $I_{S1} = I_{L1}$ (b) ON state                  |

| modified directed graph (c) ON state modified GCM 124                                                     |

| Figure 6.7: (a) S1-OFF state equivalent circuit, in which $I_{S2} = I_{L1}$ (b) OFF state                 |

| modified directed graph (c) OFF state modified generalised connection matrix 125                          |

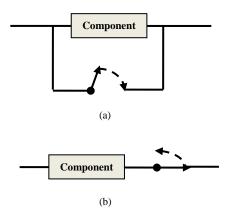

| Figure 6.8: (a) When switch closes; the component is bypassed simulating a short                          |

| circuit (b) When switch opens; the component is cut-off simulating an open circuit                        |

|                                                                                                           |

| Figure 6.9: Buck converter circuit in SIMULINK                                                            |

| Figure 6.10: Buck converter hardware setup                                                                |

| Figure 6.11: Example of building an arff. file for classification using PART                              |

| algorithm in Weka131                                                                                      |

| Figure 6.12: (a) Confusion matrix for  S1off  equation for hardware circuit data (b)                      |

| Confusion matrix for  S1off  equation for SIMULINK circuit data                                           |

| Figure 6.13: (a) Confusion matrix for  S10n  equation for hardware circuit data (b)                       |

| Confusion matrix for  S10n  equation for SIMULINK circuit data                                            |

| Figure 6.14: Example of encoding classifier results to test on a data stream                              |

| Figure 6.15: (a) Confusion matrix for   <i>Slon</i>   equation for hardware circuit data (b)              |

| Confusion matrix for  S1on  equation for SIMULINK circuit data (c) Confusion                              |

| matrix for  S10n  equation to check performance of software rules on hardware data              |

|-------------------------------------------------------------------------------------------------|

|                                                                                                 |

| SIMULINK                                                                                        |

| Figure 6.17: Confusion matrix for duty cycle 25% using  S1off  equation for                     |

| SIMULINK                                                                                        |

| Figure 6.18: Confusion matrix for duty cycle 40% using  S1off  equation for                     |

| SIMULINK                                                                                        |

| Figure 6.19: Confusion matrix for duty cycle 75% using  S1off  equation for                     |

| SIMULINK                                                                                        |

| Figure 6.20: Confusion matrix for duty cycle 95% using  S1off  equation for                     |

| SIMULINK                                                                                        |

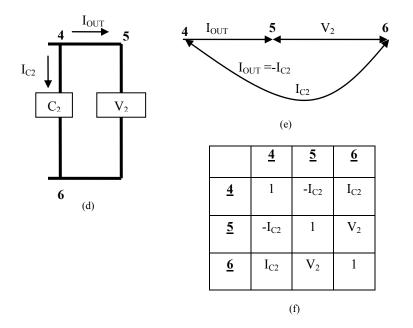

| Figure 6.21: Boost converter circuit represented to conduct SCA                                 |

| Figure 6.22: (a) and (d) S1-ON state equivalent circuit, in which $I_{S1} = I_{L1}$ (b) and (e) |

| corresponding modified directed graph (c) and (f) corresponding modified                        |

| generalised connection matrix                                                                   |

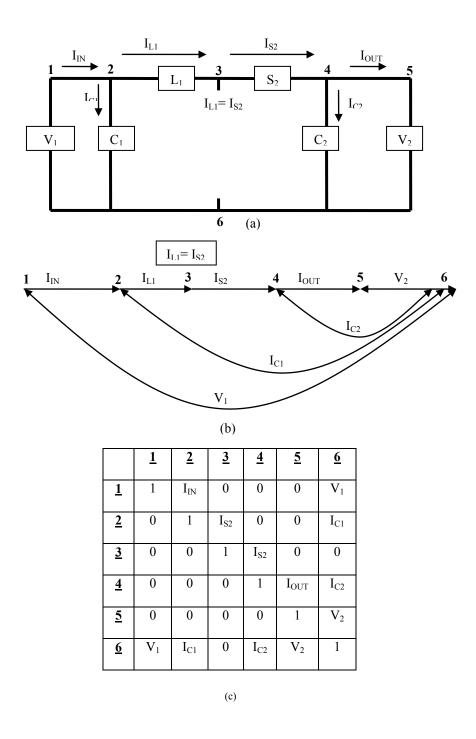

| Figure 6.23: (a) S1-OFF state equivalent circuit, in which $I_{S2} = I_{L1}$ (b) OFF state      |

| modified directed graph (c) OFF state modified generalised connection matrix 178                |

| Figure 6.24: Buck-boost converter equivalent circuit                                            |

| Figure 6.25: (a) and (d) S1-ON state equivalent circuit, in which $I_{S1} = I_{L1}$ (b) and (e) |

| corresponding modified directed graph (c) and (f) corresponding modified                        |

| generalised connection matrix                                                                   |

| Figure 6.26: (a) S1-OFF state equivalent circuit, in which $I_{S2} = I_{L1}$ (b) OFF state      |

| modified directed graph (c) OFF state modified generalised connection matrix 181                |

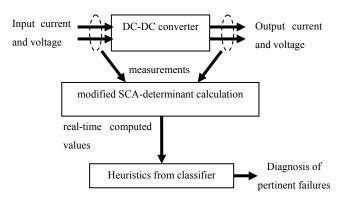

| Figure 6.27: A real-time diagnostic setup following proposed modified SCA-based                 |

| heuristics technique [70]                                                                       |

| Figure 6.28: System with loads to test feasibility of proposed dc-dc converter                  |

| diagnosis technique in a more complex set-up [70]186                                            |

| Figure 7.1: Methodology proposed in this thesis to address driving requirements of              |

| research arena                                                                                  |

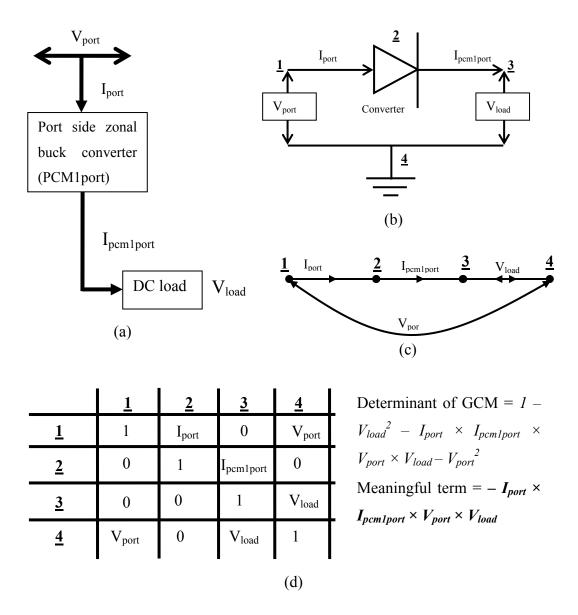

| Figure 7.2: Example of modified-SCA based approach applied at a zonal level                     |

| (subsystem) (a)Port-side load supply connection (b) Equivalent diagram for                      |

| modified-SCA (c) Directed graph (d) GCM and corresponding derivation of usable                  |

| terms                                                                                           |

# List of Tables

| Table 4.1: Example of FMEA for design evaluation [71]                            | 54     |

|----------------------------------------------------------------------------------|--------|

| Table 4.2: Example of non-annunciating failure that need means to detect them    | ı [71] |

|                                                                                  | 54     |

| Table 5.1: Example of a detailed and standard FMEA table as given in [71]        |        |

| Table 5.2: Relatively less detailed FMEA table as given in [72]                  |        |

| Table 5.3: List of devices modelled on the RTDS as part of the notional zonal    | SPS,   |

| refer fig. 5.1 and fig. 5.5                                                      | 84     |

| Table 5.4: List of devices with abbreviations used and corresponding functions   | refer  |

| fig. 5.1 and fig. 5.5.                                                           | 85     |

| Table 5.5: List of sub-sections of the modelled SPS with constituent devices, re | efer   |

| fig. 5.1 and fig. 5.5.                                                           | 86     |

| Table 5.6: Zone 1 F-FMEA details                                                 | 87     |

| Table 5.7 Zone 2 F-FMEA details                                                  | 88     |

| Table 5.8: Zone 3 F-FMEA details                                                 | 89     |

| Table 5.9: Zone 4, 5 and 6 F-FMEA details                                        | 90     |

| Table 5.10: Zone 7 and 8 F-FMEA details                                          | 91     |

| Table 5.11: AC-power generation ring F-FMEA details                              |        |

| Table 5.12: DC-busses F-FMEA details                                             |        |

| Table 5.13: PDM-2 F-FMEA details                                                 |        |

| Table 5.14: PDM-4 F-FMEA details                                                 |        |

| Table 5.15: PDM-3P F-FMEA details                                                |        |

| Table 5.16: PDM-3S F-FMEA details                                                |        |

| Table 5.17: PCM-4 in zone 1 F-FMEA details                                       | 96     |

| Table 5.18: PCM-4 in zone 2 F-FMEA details                                       | 96     |

| Table 5.19: PCM-4 in zone 3 F-FMEA details                                       | 96     |

| Table 5.20: PCM-1P and PCM-1S in zones 4, 5 and 6 F-FMEA details                 |        |

| Table 5.21: PCM-1P and PCM-1S in zones 7 and 8 F-FMEA details                    |        |

| Table 5.22: PCM-2 in zones 7 and 8 F-FMEA details                                |        |

| Table 5.23: MTG-1 F-FMEA details                                                 |        |

| Table 5.24: MTG-2 F-FMEA details                                                 |        |

| Table 5.25: ATG-1 F-FMEA details                                                 |        |

| Table 5.26: ATG-2 F-FMEA details                                                 | 100    |

| Table 5.27: PM-P F-FMEA details                                                  | 100   |

|----------------------------------------------------------------------------------|-------|

| Table 5.28: PM-S F-FMEA details                                                  | 100   |

| Table 5.29: PL F-FMEA details                                                    | 101   |

| Table 5.30: RAD F-FMEA details                                                   | 101   |

| Table 5.31: DCLL F-FMEA details                                                  | 102   |

| Table 5.32: ACLL F-FMEA details                                                  | 102   |

| Table 5.33: ES F-FMEA details                                                    | 103   |

| Table 5.34: Summary of high severity functional failure modes at a sub-system le | evel  |

|                                                                                  | 104   |

| Table 5.35: Summary of high severity functional failure modes at a device level  |       |

| sorted as per percentage of high severity functional failures                    | 104   |

| Table 5.36: Summary of high severity functional failure modes for individual dev | vices |

|                                                                                  | 105   |

| Table 5.37: Standard dc-dc buck converter components and their functions         | 108   |

| Table 5.38: Semiconductor switch FMEA                                            | 113   |

| Table 5.39: Input capacitor FMEA                                                 | 113   |

| Table 5.40: Output capacitor FMEA                                                | 113   |

| Table 5.41: Inductor FMEA                                                        | 114   |

| Table 5.42: Freewheeling diode FMEA                                              | 114   |

| Table 5.43: Summary of high severity failure modes for individual components o   | fa    |

| buck converter                                                                   | 114   |

| Table 6.1: Description of required quantities to form modified-SCA equations     | 128   |

| Table 6.2: Faults studied for comparison between SIMULINK and hardware buck      | ζ     |

| converter circuits [70]                                                          | 130   |

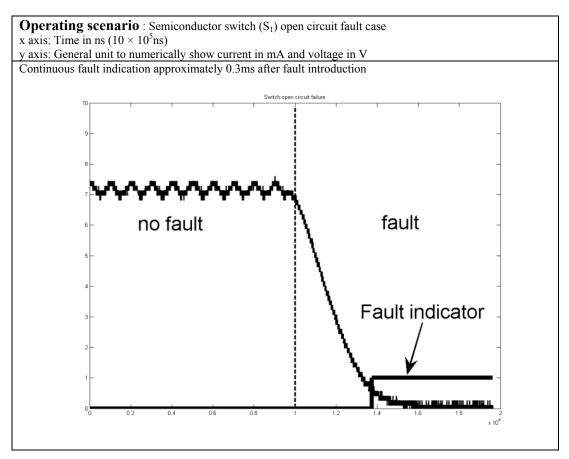

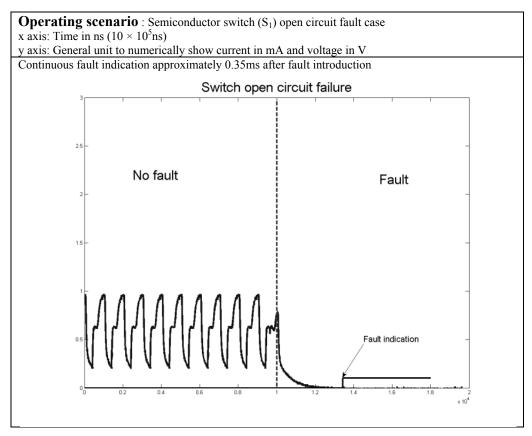

| Table 6.3: Switch open circuit fault, data plots comparison                      | 132   |

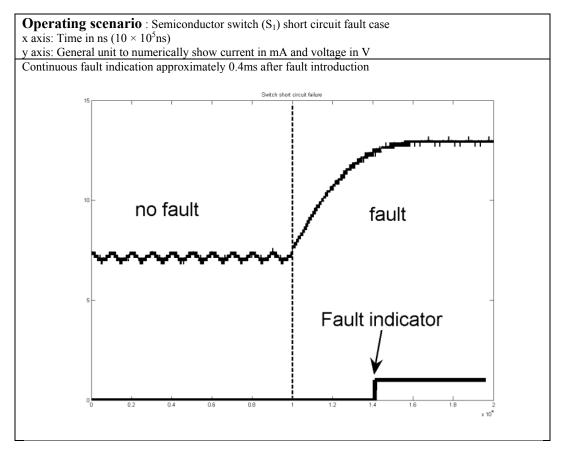

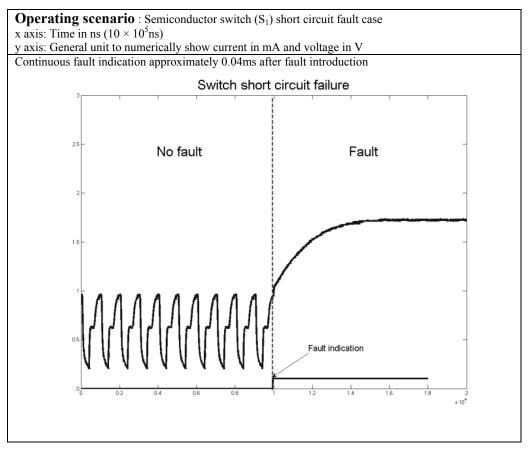

| Table 6.4: Switch short circuit fault, data plots comparison                     | 133   |

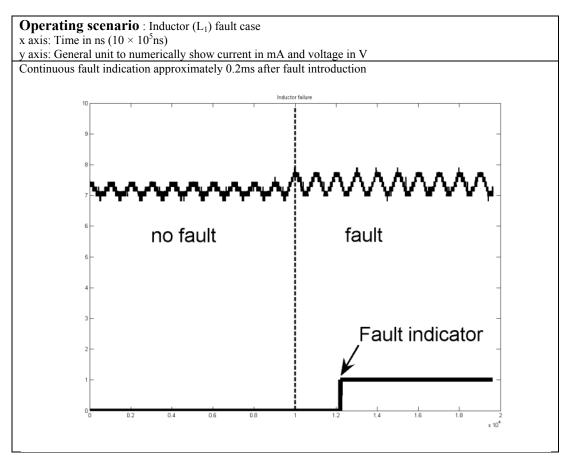

| Table 6.5: Inductor fault, data plots comparison                                 | 134   |

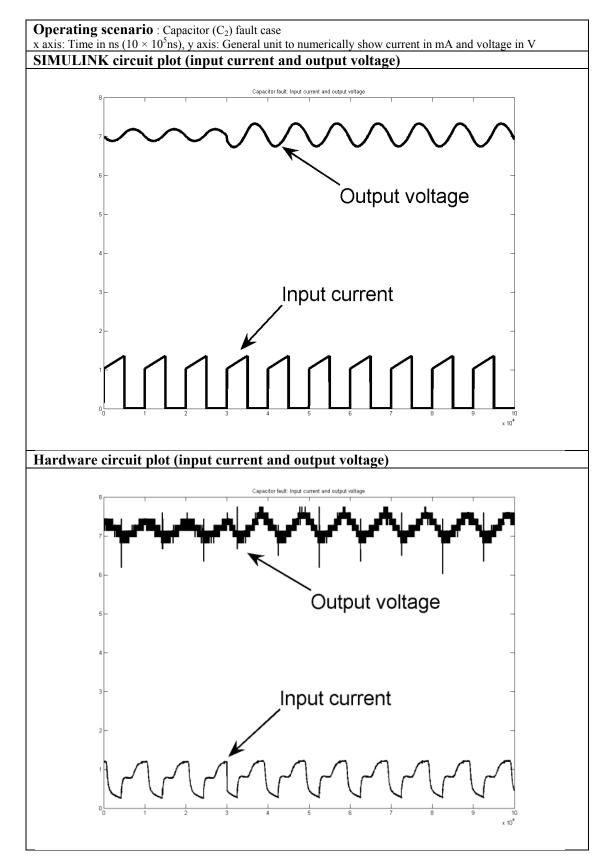

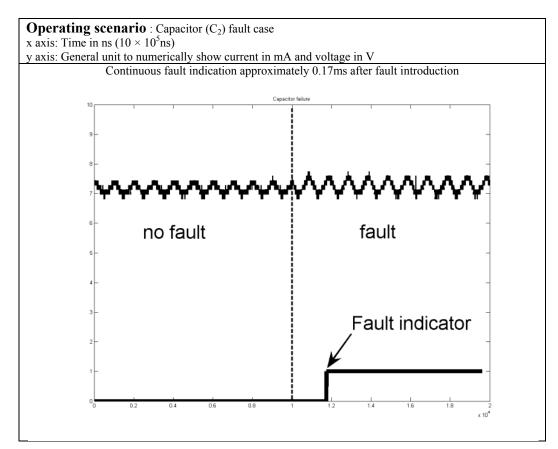

| Table 6.6: Capacitor fault, data plots comparison                                | 135   |

| Table 6.7: Rules generated using  S1off  for hardware data                       | 138   |

| Table 6.8: Rules generated using  S1on  for hardware data                        | 138   |

| Table 6.9: Fault indication for switch open circuit fault case                   | 142   |

| Table 6.10: Fault indication for switch short circuit fault case                 | 142   |

| Table 6.11: Fault indication for inductor fault case                             | 143   |

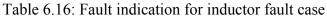

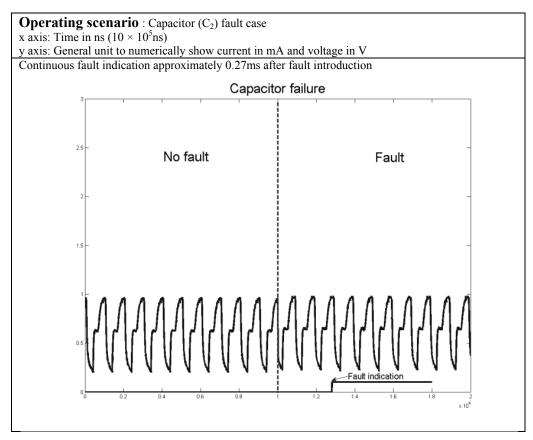

| Table 6.12: Fault indication for capacitor fault case                            | 143   |

| Table 6.13: Comparison of rules after training on software data and testing on  |     |

|---------------------------------------------------------------------------------|-----|

| hardware data                                                                   | 145 |

| Table 6.14: Fault indication for switch open circuit fault case                 | 146 |

| Table 6.15: Fault indication for switch short circuit fault case                | 146 |

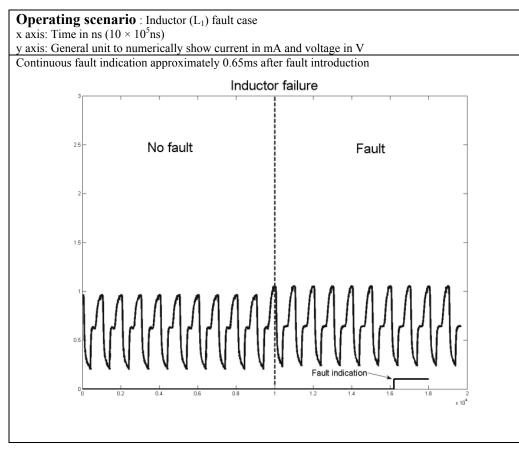

| Table 6.16: Fault indication for inductor fault case                            | 147 |

| Table 6.17: Fault indication for capacitor fault case                           | 147 |

| Table 6.18: Fault indication for capacitor fault case                           | 148 |

| Table 6.19: Different duty cycles for further tests                             | 149 |

| Table 6.20: Rule set for duty cycle = $10\%$                                    | 152 |

| Table 6.21: Rule set for duty cycle = 25%                                       | 155 |

| Table 6.22: Rule set for duty cycle = $40\%$                                    | 159 |

| Table 6.23: Rule set for duty cycle = 75%                                       | 162 |

| Table 6.24: Rule set for duty cycle = 95%                                       | 164 |

| Table 6.25: Generalisation results for data trained on rules for 10% duty cycle | 165 |

| Table 6.26: Generalisation results for data trained on rules for 25% duty cycle | 166 |

| Table 6.27: Generalisation results for data trained on rules for 40% duty cycle | 167 |

| Table 6.28: Generalisation results for data trained on rules for 75% duty cycle | 168 |

| Table 6.29: Generalisation results for data trained on rules for 95% duty cycle | 169 |

| Table 6.30: Generalisation results for data trained on rules for 50% duty cycle | 170 |

| Table 6.31: Summary of modified-SCA based equations for dc-dc converters        | 187 |

# List of Equations

| Equation 3.1 | 4 |

|--------------|---|

| Equation 6.1 | 1 |

| Equation 6.2 | 4 |

| Equation 6.3 | 5 |

| Equation 6.4 | 6 |

| Equation 6.5 | 9 |

| Equation 6.6 | 0 |

| Equation 6.7 | 1 |

## **Glossary of Abbreviations**

- AC Alternating Current

- ACZED AC zonal electrical distribution system

- AI Artificial Intelligence

- CAPS Centre for Advanced Power Systems

- CBM Condition Based Maintenance

- CDG Component Dependency Graphs

- DC Direct Current

- DCZED DC zonal electrical distribution system DF Dissipation Factor

- EMTDC Electromagnetic Transient and DC

- ESR Effective Series Resistance

- FA Fault Accommodation

- FACS Fault Accommodating Control System

- FMEA Failure Mode and Effects Analysis

- FFT Fast Fourier Transform

- F-FMEA Functional FMEA

- FMECA Failure Mode Effect and Criticality Analysis

- FPGA Field Programmable Gate Array

- FSU Florida State University

- GA Genetic Algorithm

- GCM Generalized Connection Matrix

- GIS Geographical Information System

- GTO Gate Turn Off thyristor

- H-FMEA Hardware FMEA

- HIL Hardware In Loop

- IFTP Integrated Fight Through Power

- IGBT Insulated Gate Bipolar Transistor

- IGCT Integrated Gate Commutated Thyristor

- IPS Integrated Power System

- JADE Java Agent Development Environment

- LC Inductor-Capacitor

- LSA Latent Semantic Analysis

- MAS Multi Agent System

- MM Multiple Model

- MOSFET Metal Oxide Semiconductor Field Effect Transistor

- MVAC Medium Voltage AC

- MVDC Medium Voltage DC

- NLP Natural Language Processing

- NN Neural Network

- ONR Office of Naval Research

- PART Projective Adaptive Resonance Theory

- PCA Principal Component Analysis

- PEBB Power Electronics Building Blocks

- PEC Power Electronic Converter

- PMS Platform Management System

- PSCAD Power System Computer Aided Design

- RMS Root Mean Square

- RPNRisk Priority NumberRTDSReal Time Digital SimulatorSCASneak Circuit AnalysisSPSShipboard Power SystemSVMSpace Vector Machines

- US United States

- UML Unified Modelling Language VTB Virtual Test Bed

## **Chapter 1 Research Background**

#### **1.1 Introduction to research arena**

The preference for integrated electric propulsion architectures aboard naval vessels has been proposed since approximately 1995 onwards through a series of papers titled "The Electric Warship" mainly by C.G. Hodge [1-7]. This research forms one of the primary works that provide the impetus to move from conventional mechanical propulsion to fully integrated electrical propulsion [1]. The authors make the case for DC power distribution aboard modern warships providing meticulous calculations to compare the benefits of DC over AC [2], [6]. The papers elaborate on advances in motors (especially permanent magnet technology) to help increase propulsion efficiency as well as energy storage issues to support advanced high power weaponry. The recurring emphasis however, is on the extensive use of power electronics devices as the major enabling technology [1], [3-5], [7] and [8]. The work by Hodge et al. forms the base of this research field and the recommendations can be summarised into three parts.

- 1. Move from standard mechanical propulsion to electric propulsion for naval vessels.

- 2. Preference for DC power distribution along the ship.

- 3. Extensive use of power electronics devices onboard, especially converters.

Progressing on from this preliminary research, concepts such as integrated propulsion system and medium voltage AC and/or DC zonal distribution have come into prominence. The U.S. navy has proposed designs of future warships that heavily rely on power electronics devices and novel distribution architectures [9]. Next generation naval vessels have been envisioned with a reduction in crew (by 75% - 90% [10]) thereby implying increased computational intelligence and automation to achieve mission goals with high efficiency. This puts an emphasis on the system being able to provide decision support and aid remedial action in contingency scenarios.

The overall research efforts are along the lines of the U.S. Office of Naval Research's (ONR) control challenge problem statement, wherein the essential goal is [11];

"To provide continuous mobility, power, and thermal management for shipboard combat systems despite major disruptions involving cascading failures."

As such, the control architecture is expected to accurately diagnose faults and mitigate the risks posed thereby effectively accommodating disturbances within the shipboard power system (SPS). This requirement gives rise to a term, fault accommodating control system (FACS), which could be defined as a system capable of the following automated tasks:

- 1. Accurate fault diagnosis which includes fault detection and identification.

- 2. Timely fault isolation which is a task of the onboard protection system.

- 3. Remedial action which aims at reconfiguring the system in order to best utilise available resources to achieve the present mission's goal(s).

Keeping in mind the need for decision support alongside increased automation, leads this research into the realm of artificial intelligence (AI) based capabilities. The search for suitable AI technique(s) to diagnose faults aboard a novel shipboard power distribution system requires meticulous understanding of AI used on general power system applications such as terrestrial networks. From this stage, the study continues into checking feasibility of known AI methods to diagnose faults for a relatively unknown system or the need to develop new diagnostic techniques. Devising fault diagnosis techniques to differentiate and identify various types of disturbances in the novel shipboard architecture forms the driving requirement for this research and delivers the underlying novelty in the work.

### **1.2** Justification and rationale for research

The development of DC power distribution SPS architectures is still in a conceptual phase with a lack of actual benchmark systems. Research is ongoing in this field with work centred on:

- Analysing the fundamental aspects of such a paradigm shift.

- Issues related to supervisory control and decision support capabilities.

- Protection coordination and automation.

- Power system reconfiguration and restoration.

Detailed studies need to be conducted to understand fundamental differences between terrestrial power networks, conventional SPS and the proposed SPS. The overall aim of this research is the development of the FACS, for which a detailed study needs to be conducted across inter-related domains. The emphasis on increased use of power electronics devices and automation for the proposed architecture makes it imperative to understand and mitigate risks. As a result, this requires studies within reliability analyses and power electronics domains. FMEA and SCA are used in this research which falls under the reliability analyses domain.

Another vital requirement is the establishment of a meticulous research methodology which could be ideally generalised to study similar envisioned SPS of next generation warships. An ideal approach would be one that takes into account risks at all levels i.e. component, device, sub-system and system as a whole, then helps highlight pertinent disturbances on which AI based diagnostics could be focussed. Additional issues such as decision support for onboard crew also need to be addressed for which AI techniques could be employed as well. This forms part of future planned research in this particular field.

#### **1.3 Research novelty and contribution**

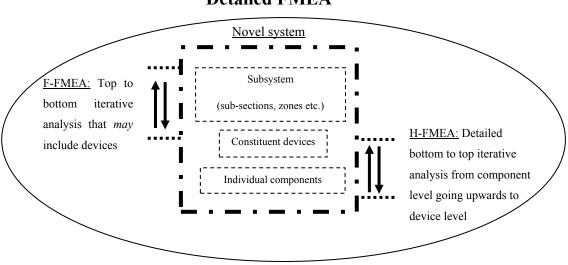

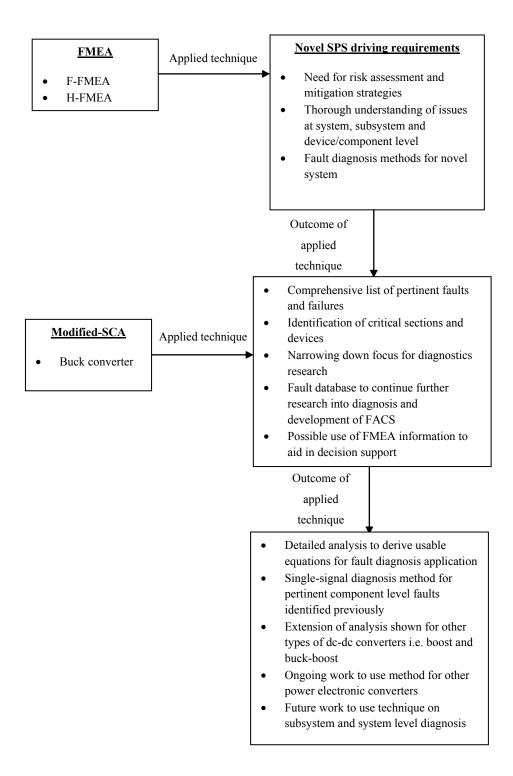

This research follows a methodology informed through a detailed FMEA for the novel shipboard power system architecture. FMEA is conducted initially at the system or sub-system level, gradually moving down to component levels. FMEA is one of two established reliability analysis techniques used in this research, the other being sneak circuit analysis (SCA).

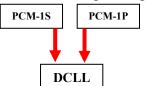

The initial functional FMEA helped narrow down critical devices of the network, which identified the dc-dc buck converters as vital devices to realise benefits of the proposed zonal distribution architecture. Hardware FMEA done on the buck converter was used to increase understanding about its component level faults and their effects, further narrowing down pertinent issues. This overall information is then used for simulating fault scenarios to generate data for further research and analysis into diagnostics. This approach of using FMEA to guide and inform further research into diagnostics attempts to lay the groundwork for further research in the field of SPS risk management.

The other aspect of novelty lies in the modification of SCA to output usable data that were effectively employed to differentiate between different fault scenarios. The modification differs from the convention of using component symbols to form the SCA generalised connection matrix (GCM) as actual current and voltage values are used to form the GCM instead. The determinant of the GCM outputs numeric values that are shown to differentiate between various operating scenarios of the buck converter circuit. The data produced with this modification is from a SIMULINK circuit and a corresponding hardware test setup. Standard sensor output is used to calculate circuit currents and voltages applying circuit laws and component models [12] by using local measurements (input/output currents and voltages) and values of component parameters. The advantage lies in the fact that additional sensors are not needed to obtain measurements of quantities required to be used for the modified SCA process.

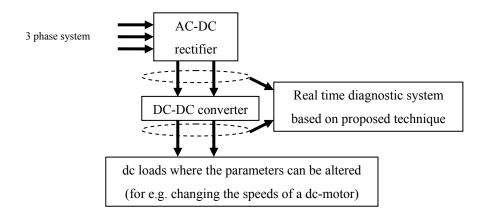

Employing the projective adaptive resonance theory (PART) algorithm [13], heuristics were generated utilising the software tool Weka [14]. Thereafter, these rules were encoded using conditional statements (if-else) and tested on the data offline to check the diagnostic efficiency. The results were promising in showing an ability to distinguish different component level faults which have been elaborated in later sections. Thus, FMEA helped narrow down critical sections to focus research, thereafter SCA was used to produce data that help differentiate component level faults in a buck converter when run through an AI based algorithm such as PART. This systematic research approach within this field of study is illustrated in fig.1.1.

Heuristics/conditional rules for fault diagnosis

Figure 1.1: Approach proposed in this thesis for developing a potentially robust methodology to help diagnose faults

#### **1.4 Thesis structure**

There are 7 chapters in this thesis. This chapter offered a concise introduction to the specific research arena along with the thesis outline. Chapter 2 provides a detailed coverage of efforts of researchers in this field that adhere to root concepts such as:

- Fundamental analysis, modelling and stability issues with risk assessment.

- Automation, reconfiguration of network, power restoration and load shedding.

- Fault diagnosis and prognosis

Chapter 3 gives relevant information on research conducted in the field that actively supports the novel SPS research, namely power electronics. In this chapter the emphasis is laid on power electronics fault diagnosis at a device as well as component level. Further, the concept of fault accommodation as outlined in the power electronics domain is described by referencing relevant publications.

Chapter 4 highlights research in reliability analysis, which forms the basis for studying envisioned SPS from a risk management point of view. The two major reliability analyses methods outlined here are failure mode and effects analysis (FMEA) and sneak circuit analysis (SCA).

Chapter 5 demonstrates utilisation of FMEA on the proposed zonal SPS studied in this research. A meticulous methodology is followed which helps understand possible failures and faults. This aids to further focus research into diagnosing pertinent failures and issues. This methodology is a systematic approach applied in this particular research arena.

Chapter 6 explains the modification of conventional SCA to aid in producing diagnostic indicators that helps differentiate types of faults at a component level within a dc-dc buck converter. This forms a novel aspect of this research added to the methodology stemming from FMEA. This chapter also discusses results of the proposed approach applied to both a computerised model (MATLAB-SIMULINK) as well as a representative hardware system. The results are compared after applying Weka (open source data mining software) to generate diagnostic rules with the help of modified SCA elaborated in the previous chapter.

Chapter 7 concludes the Ph.D. research and the thesis by summarising the justifications and novelties of this work. Discussions are presented on the possible future paths that could be derived and undertaken from this research work.

#### **1.5** Associated publications

The following publications have arisen as a result of studies conducted and elaborated in this thesis.

#### **Conference papers:**

1. Soman, R.R.; Davidson, E.M.; McArthur, S.D.J.; , "Using functional failure mode and effects analysis to design the monitoring and diagnostics architecture for the zonal MVDC shipboard power system," *Electric Ship Technologies Symposium*, 2009. *ESTS 2009. IEEE*, vol., no., pp.123-128, 20-22 April 2009

2. Mair, A.J., Soman, R.R., Davidson, E.M., Srivastava, S.K., Schoder, K., McArthur, S.D.J. and Cartes D.A.; "Intelligent distributed control for shipboard

power systems based on fault diagnosis and condition monitoring," *Engine as a weapon III, Portsmouth*, UK, 23-24 June, 2009.

3. Mair, A.J., Soman, R.R., Davidson, E.M., Srivastava, S.K., Schoder, K., McArthur, S.D.J., Cartes D.A. and Edrington, C.S.; "Fault Classification and Accommodation in Shipboard Power Systems," *Proceedings of the International Simulation Conference*, Turkey, 13-16 July, 2009.

4. Mair, A.J., Soman, R.R., Baker, P.C., Davidson, E.M., Srivastava, S.K., Schoder, K., McArthur, S.D.J., Cartes D.A. and Andrus, M.; "Progress in the development of adaptive control for shipboard power systems through modelling and simulations," *Proceedings of the Grand Challenges in Modelling and Simulation Conference*, 2010.

#### Journal paper:

1. Soman, R.R.; Davidson, E.M.; McArthur, S.D.J., Fletcher, J.E. and Ericsen, T.; "Model-based methodology using modified sneak circuit analysis for power electronic converter fault diagnosis", *Power Electronics, IET*, vol.5, no.6, pp.813-826, July 2012.

A detailed description of each publication and their relevance is presented in section 3.4.

## **Chapter 2 Literature Review**

#### 2.1 Introduction

The overall aim of this research is the development of a fault accommodating control system (FACS). The difference between this FACS and a classical fault tolerant control system is that the FACS will try to explicitly identify faults and incorporate this additional information to achieve system-wide robustness. Therefore, after a fault is diagnosed and located, it is believed that appropriate control actions can automatically be taken to mitigate the effects of that fault. It is envisaged that this will be achieved through the changing of controller parameters or by system reconfiguration such that the consequences of the fault can be avoided or minimised. It is also expected that the time by which remedial action can be taken in response to a fault will be greatly reduced.

Thus such a proposed system must have accurate fault diagnosis followed by an additional system that can reconfigure the network once the diagnosis is made. Another aspect of the research is to provide adequate decision support to the onboard crew by potentially using information gathered from the diagnosis and monitoring system. Apart from an accurate diagnostic capability, an open area of research is in prognostics. While a diagnostic system would concentrate on the timely detection and identification of the fault, a prognostic system would aim to predict the time remaining for failure by detecting potential precursors. This added capability of predicting behaviour to estimate the most likely outcome is highly advantageous in this research arena of the notional zonal SPS with a FACS.

To achieve the mentioned aim of building a FACS, detailed studies in a number of sub-domains have to be conducted. As expected, research is ongoing within these domains and has been elaborated upon in this and the next two chapters.

# 2.2 Envisioned SPS analyses, modelling, stability and risk assessment

An informative and detailed discussion about the challenges at design stages of the envisioned DC architecture for warships is presented in [15] by Amy explaining the analytical aspects of developing the US Navy's integrated power system (IPS). Here, a clear distinction between terrestrial power systems and shipboard power systems (SPS) is made highlighting the practical issues to be considered while analyzing each type. This paper is important to understand the fundamentals of shipboard power systems and to gain insight into the top-level requirement of the research field.

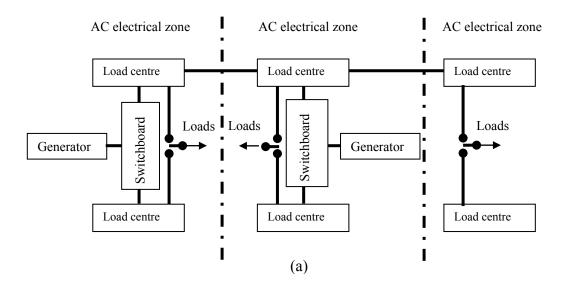

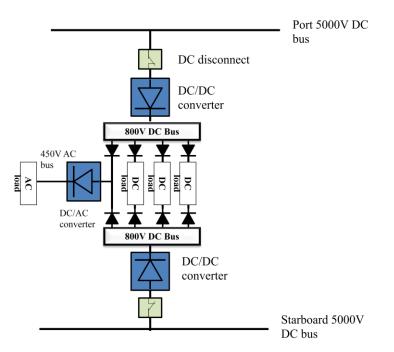

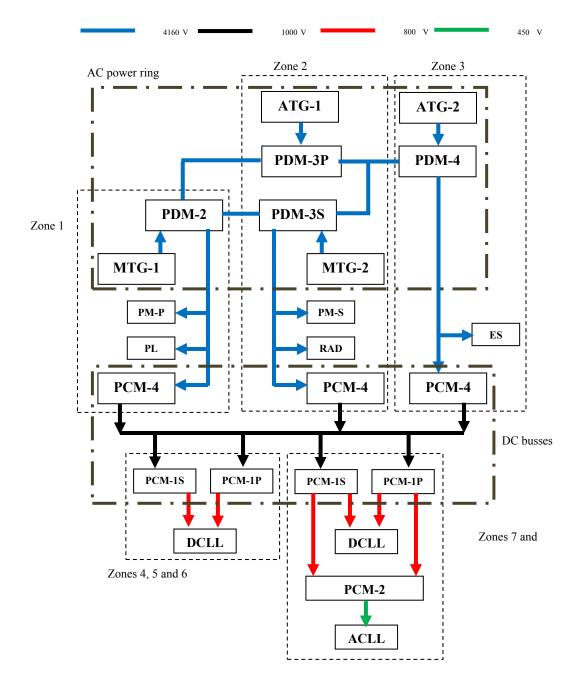

Hegner and Desai in [16] further elaborate on IPS development and introduce a new term namely integrated fight through power (IFTP). The IFTP idea explains the envisioned zonal SPS distribution concept wherein power electronic converters play a major role. The paper explains differences between the traditional radial power distribution system with the proposed method which uses starboard and port busses that supply power to zones. The diagrammatic comparison shown by the authors between proposed AC and DC zonal electrical distribution systems (ACZEDS and DCZEDS respectively) is shown in fig.2.1. A performance evaluation between ACZEDS and DCZEDS is made along with highlighting other practical aspects such as corresponding weights of the two setups. Furthermore, the advantage of choosing DCZEDS is clarified reporting on factors like isolation of the faulted zone during system level disturbances (e.g. grounding issues) to prevent fault propagation. These factors make the use of power electronic converters as power delivery devices vital for the envisioned SPS. A detailed description of the envisioned zonal SPS is provided in chapter 4.

Figure 2.1: (a) ACZEDS representation [16], (b) DCZEDS representation [16]

An important concept emphasizing the use of advanced power electronics for the notional warship was proposed by Ericsen et al. in [9] abbreviated as power electronic building blocks (PEBB). Owing to the extensive use of power electronic converters to facilitate various power needs of loads, the ship's mission goals are aimed to be achieved using the minimum number of PEBB 'boxes' instead of using a separate set of equipment for each separate mission type. The PEBB devices can be used during the design phase to produce different products by varying hardware configurations. This research in [9] outlines a detailed study of the PEBB concept shedding light on the modular and hierarchical design principles of each such device.

The emphasis is on producing advanced devices with interactive elements that fit in with the objectives of the envisioned SPS, vital among which are reduced manning and increased automation. A physics-based design model development approach is adopted where new designs will be built incrementally over time incorporating hardware-in-the-loop testing. This paper marks the crucial need for research into advanced power electronics devices (especially converters) with preferably built-in fault diagnostics at not only the system level but also at the sub-system and component level. The concept of PEBB devices and its modularity allow for building open and novel shipboard power distribution architectures that could include intelligent methods for protection, reconfiguration, restoration, fault diagnostics, condition monitoring and perhaps prognostics.

Ciezki and Ashton in [17] describe the move of the US navy from the traditional radial AC system to the notional DCZEDS. They also detail the various pros and cons in support of the DCZEDS. This argument forms a good base to understand the interest to adopt the DC zonal power architecture from an ideal viewpoint. However, the authors aim to touch upon the stability issues concerned with such a zonal system which is a crucial aspect owing to the lack of thorough understanding of the novel system's behaviour. One aspect outlined is the differences between the slow dynamics of the power source and the much faster dynamics of power electronic devices. This is a crucial point that needs emphasis while dealing with fault isolation as well as diagnostics. The authors admit that this research is still in its infancy and more work is needed to understand how to deal with these constraints imposed, when a large number of power electronics are utilized in an already lesser known DC architecture. Not much detail is provided on various stability issues, most probably due to the lack of benchmark systems and understanding of the notional power architecture.

Momoh et al. in [18] propose probabilistic security indices for the notional power system. The research is conducted to develop a more accurate load flow study method to take into account contingency situations. The method adopted for the power load flow analysis is called expected contingency margin which is able to handle the contingency probabilities and the priorities of the path causing the fault. Ten different contingency situations are studied namely, 5 cable losses, 3 generator outages and 2 converter failures. The IPS is modelled using MATLAB wherein a

portion of an entire network is simulated that includes the cables, generators and two converters. This paper reports a useful metric which provides a method to compute probabilities of occurrence of certain faults. However, there is no detailed explanation as to why only certain type of contingencies have been considered, further, there is no detail about the kind of converter faults (2 failures), a device which forms the crux of the zonal power distribution system. Perhaps this approach needs to be applied in much more detail to all possible faults that can happen in a given shipboard system employing ACZEDS or DCZEDS, thereafter an informed decision could be made as to which are the pertinent faults based on their probabilities computed. An initial rigorous methodology is needed to assess various possible faults that may occur in the novel SPS at all levels of the distribution architecture in order to thoroughly understand associated risks.

A different risk management aspect to [17] and [18] is presented in [19] by Schulz et al. from the monitoring and measurements point of view. Apart from faults occurring in the power equipment, loads, cables etc. and developing methods to diagnose and accommodate those faults, it is important to ensure that sensors and measurement devices are monitored too. This includes studies into sensor positioning and redundancy. In [19] a genetic algorithm approach is used to determine the minimum number of measurement meters required to estimate the state of the system. A contingency analysis is also done where meters are removed one by one and a check is done to ensure sufficient data to achieve the mission goal is being obtained. This research is aimed at providing means to enable efficient response to reconfiguration during a fault scenario where physical damage may occur to parts of the vessel resulting in loss of equipment. The approach simulated in MATLAB is useful to verify whether adequate data is available given the current topology of the power architecture during different operational scenarios. This paper however does not deal exclusively with restoration and reconfiguration aspects of the system, but the research presented may have potential uses for these activities.

MATLAB is again used to model AC and DC power systems by Schulz et al. in [20]. Here a more detailed attempt is made including models for protection system as well as hardware-in-the-loop (HIL) testing. This is a good example of combining the best of simulation as well as real hardware tests wherein an enhanced understanding of the interaction between real and virtual systems in a non-destructive and cost

effective way could be obtained. This paper reports overall research being conducted in the sub-domains that comprise the notional SPS namely:

- 1. Protection system

- 2. Reconfiguration system

- 3. Stability analysis

- 4. Power electronics

The emphasis on power electronic converters and interfaces is made for developing the IPS as per the proposed guidelines. A reference to the PEBB technology is made showing its use within research concentrating on protection, reconfiguration and stability issues.

The zonal power distribution architecture still being in the conceptual phase means that there is a lack of actual existing systems for reference. This means, meticulous research is needed to simulate the behaviour of such a system in various operational scenarios using purely virtual means or HIL inclusive techniques. In [21], Feliachi et al. aim to build a hardware prototype to conduct experimentation related to the US Navy AC/DC distribution, to help validate work done on automatic reconfiguration and to aid in studying embedded controls for these applications. Such an initiative is an important step towards getting more real-world data as opposed to only software simulation data. This paper describes the various tests that could be conducted on a hardware test-bed including control system experimentation. A higher level system employing intelligent software agents is also proposed that could potentially form a useful human-machine interface. Several researchers including Feliachi discuss variants of multi agent system (MAS) applications going hand in hand with the increased power electronics onboard the notional SPS. More on the application of MAS for managing tasks aboard the SPS [22-24] are discussed in section 1.3. The positives that arise by using software agents which by definition have *reactivity*, *proactivity* and *social ability* seem to fit in with the anticipated advanced capabilities the future's naval SPS is supposed to possess. Much work needs to be done though to make the agents intelligent enough to form an effective human-machine interface especially in the case of handling automated power reconfiguration, restoration and fault diagnosis.

#### 2.2.1 Discussion

The US ONR proposed IPS is still in its conceptual phase. Being a relatively unknown system without previous benchmarks, the start to the research thus must begin at a fundamental level beginning with assessing the differences between the envisioned system with its traditional and conventional counterparts. Researchers have conducted comparison studies between terrestrial power systems plus traditional SPS with the envisioned IPS to highlight analytical and practical differences that could impact applications such as condition monitoring and fault diagnostics. To advance research, it is absolutely vital to gain a strong understanding of the operational dynamics of the envisioned distribution system, after which studies into monitoring, diagnostics, decision support and prognostics could be successfully launched. The works of researchers highlighted in this section mainly deal with analysing the novel SPS idea from a scientific and mathematical viewpoint. Once the underlying theoretical understanding is gained, the next step is to develop computer aided tools for simulation studies and corresponding hardware test rigs to validate proposed analysis approaches and improve understanding.

The research described in this section is the important preliminary work in this field. After dealing with aspects of understanding fundamental theories, associated risks and their mitigation and stability issues, section 1.3 deals with the logical next step of system level power reconfiguration, restoration and load shedding schemes.

# 2.3 SPS automated reconfiguration, restoration and load shedding

This section outlines major research towards functional tasks such as power reconfiguration, restoration and load-shedding. The system reconfiguration problem is formulated as a variation of a fixed charge network flow problem by Butler-Purry et al. in [25] using load and path priorities along with various system constraints mentioned in the paper. In the paper, an illustration of the method is shown using a three-dimensional layout of the shipboard system generated with computer aided design and drafting aids. This layout integrates information from a relational database which contains the electrical parameters of the SPS. This integrated virtual system forms what is referred to by the authors as the geographical information system (GIS). By using well established and known design parameters, such a GIS

forms a feasible method to get close to mimicking an actual SPS. An automated self healing reconfiguration strategy for power system restoration aboard naval vessels is presented in [26] by the same researchers. The paper aims to address the goal of providing continuous mobility, power and thermal management for shipboard combat systems in the presence of major interruptions. Here, the authors discuss power system restoration in the event of a missile strike. On current shipboard systems when critical loads fail to obtain power due to faults, the restoration is done manually. In this paper automated restoration is proposed such that when subjected to a contingency, the system is able to assess its impact in order to contain it to restore the power system to the best possible state in that situation. What remains an open issue is the system behaviour in the presence of faults because there is no past knowledge existing in this case. The research in [25] and [26] however is based on the radial power distribution system and not the notional ACZEDS or DCZEDS. But nonetheless, the approach holds merit owing to the iterative nature of good quality research, thereby enabling enhancements to simulations. With appropriate advancements to the GIS from the information database modifications, a healthy understanding of system behaviour under various situations can potentially be studied.

An alternative method to reconfigure power to vital loads in the presence of a fault is presented in [27] utilising an expert systems approach. Here a rule based expert system does fault detection by comparing threshold values of voltages and currents measured. The research simulates a test case representing a missile strike by de-energising loads and demonstrates the method's capability of restoring power to them using load shedding operations. The paper however does not elaborate on fault diagnosis of more common faults such as ground faults or device level faults in equipment.

These papers show a technique that automatically suggests alternate paths to restore power to vital loads as per priority. The nature of contingency discussed is in the rare event of a missile hit. The power system architecture discussed is the radial system and not the envisioned DC zonal distribution system with increased use of power electronics. Further, the method is for a system-wide contingency and does not address fault diagnosis for sub-system or device level issues which are important owing to the fact that the DCZEDS is expected to isolate faults and prevent their

15

propagation, making zonal (sub-system) and device/component level diagnostic research a must.

An automated agent based reconfiguration method is proposed in [28]. The paper reports research done on the envisioned DCZEDS. Here five major faults are discussed, namely:

- 1. Primary DC bus zone fault

- 2. Secondary DC bus zone fault

- 3. Buck converter source side DC rail fault

- 4. Intra zonal fault

- 5. Generator fault

The agent based reconfiguration method is demonstrated for the most commonly occurring problems, namely the primary and secondary DC bus faults. The proposed method is run on a DC zonal system simulated on PSCAD. The paper effectively deals with power routing in the event of a fault using agents but does not report on diagnostics, decision support or prognostics. Neither is anything discussed about using the proposed methods on an actual hardware test setup (scaled down version for example) that produces more realistic signals than simulations.

A proposal for a decentralized multi-agent system (MAS) for reconfiguring the shipboard power architecture is reported in [29]. The agents are developed in MATLAB while the system is simulated on the virtual test bed (VTB). MATLAB-SIMULINK is extensively used to simulate power systems in part or whole using the various toolboxes available within the software. The use of MATLAB to build agents as presented in this paper makes this software in general promising to be utilized for analyzing and experimenting within this research field. This paper though attributes the adoption of decentralized MAS to counter battle damage scenarios where physical damage may render a centralized control system ineffective. This reasoning seems impractical owing to the fact that it is practically impossible to determine where a missile would strike. Also, there is no emphasis given to how the reconfiguration would take place which normally takes into account load priorities.

Feliachi et al. propose a distributed scheme with MAS based control agents in [22]. This is to aid the notion of automated reconfiguration and self-healing in the event of battle damage and other fault scenarios. With a system utilising agents, the crucial aspect is the information fed into individual software agents and its accuracy.

Here, the authors aim to implement a graph theoretic self-stabilising maximum flow algorithm as the agents' strategy to ensure efficient power management which would include considering constraints and load priorities. A layered agent architecture is proposed to form a logical hierarchy classified by functionalities. The topmost layer in this architecture forms the human-machine interface wherein aspects like interactivity and decision support may be explored and included.

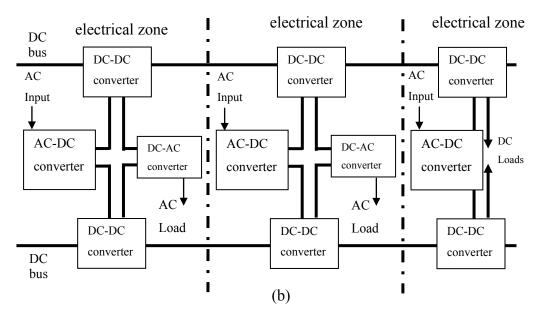

An MAS with two layers (shown in fig.2.2) for power system reconfiguration is proposed by Cartes et al. in [23]. One layer is the power system layer with a network of devices and the other layer is the one with software agents. Every device has its agent with whom information can be exchanged. The communication constraints on every agent are placed such that information exchange is possible only with a neighbouring agent. This paper is one of the first to introduce a layered MAS where the electrical devices in the hardware layer are mapped onto its respective agent in the MAS software layer. Simulations are carried out by the authors using a real time digital simulator (RTDS). The RTDS offers high fidelity simulation and is a high speed, real time testing framework on which control system simulations and general power network simulations can be carried out. The authors make use of iPAQs to implement the agents. A field programmable gate array (FPGA) is used as an interface between the device layer (on the RTDS) and the agent layer (MAS). Further, to test this proposed MAS, various operational scenarios are simulated on the RTDS to carry out automatic reconfiguration applying the proposed scheme. These detailed efforts are important in the overall research for the development of automated reconfiguration techniques. Cartes et al. systematically propose a structured methodology making use of state-of-the-art technology to provide a potentially promising intelligent system that may be adopted for the SPS not only for reconfiguration (as suggested in [23]) but for other tasks such as condition monitoring, fault diagnosis and perhaps prognosis as well. Using MAS could also aid in providing a decision support interface to the onboard crew. However, the type of information exchanged between agents is mentioned, but the methodology and data used to build an agent is not clearly explained. More detail regarding power system information needs to be incorporated into the agents such as topology information, power capacity information etc. as reconfiguration depends on the consideration of data like available power and load priorities. It may be interesting from the research point of view to extend this approach to conduct fault studies.

Figure 2.2: Two layered MAS for SPS with devices having their own software agents [23]

Due to a lack of real existing systems with the proposed zonal distribution, almost all of the reconfiguration and restoration studies conducted thus far have been on simulated systems that adhere to the set guidelines given by the US office of naval research (ONR). A positive from the research described in this section is the viability of software products such as MATLAB-SIMULINK to be used in this field of study for better understanding of operating scenarios in a safe non-destructive environment.

A SPS power system restoration scheme using an MAS is proposed by Momoh in [24]. The rationale given by the author to use an MAS is its decentralised network and local data processing capability which greatly reduce the computation time and network bandwidth. Another advantage is the ease of scalability in case newer loads/devices are added to the network and the subsequent ease of extensibility to carry out required tasks. The ONR control challenge reference system is used to test

the proposed MAS for power restoration. The MAS differs from [23] because here Momoh proposes a single negotiating agent, several load agents and several bus agents divided into two layers, the communication sub-system and operational subsystem. The three different agents communicate among one another and solve tasks using local information without a control centre. Simulated tests on the reference system are shown to be able to successfully restore power during a complete outage as well as partial outage. Though this methodology is elegant, it is tested on a highly simplified simulated system. The MAS's feasibility for a more complex network remains to be seen.

A detailed survey of reconfiguration methods is given by Nagaraj et al. in [30]. This work also highlights the important issue described by Amy in [15], i.e. of finite inertia in the case of SPS. The authors in this research adopt a theoretical stability based graphical approach as opposed to more hybridised approaches used by other researchers mentioned earlier. This work though in its initial stages offers a potentially important contribution by making high level comparisons between terrestrial system reconfiguration and that proposed by previously mentioned authors for SPS applications.

An expert system based load shedding scheme is presented by Cartes et al. in [31]. The dynamic prioritization of loads is obtained by combining both the significance level and critical natures of loads using analytical hierarchy. The authors present a detailed explanation of the various factors affecting the process of load prioritisation. The load priority list is based on the mission goal and nature of loads and is an advantage over traditionally used schemes which are less flexible. Once the loads that are to be shed have been determined, system knowledge and expert reasoning are required to find an optimal solution for switching actions to shed the loads. Thus, an expert system that emulates the search behaviour of human experts in solving a problem is a preferred choice for this scheme. Simulations are carried out on the validated SPS model on the RTDS and show promising results. To apply an expert system approach, the expert knowledge elicitation process needs to be detailed, rigorous and accurate. This research is demonstrated for one zone of the DCZEDS and needs to be applied to different types of zones with different load profiles to test feasibility. Also, a detailed expert knowledge elicitation methodology needs to be put

in place if the approach is to be applied for a variety of zones and eventually the system as a whole.

#### 2.3.1 Discussion

Power management which is inclusive of reconfiguring the system, restoring power and load shedding are the logical system related applications underpinned by the fundamental understanding of SPS architectures and behaviours. Publications associated with power managing aboard the notional SPS are described in this section. Numerous researchers propose using MAS architectures to fulfil the envisioned goals of the IPS. The structuring of the MAS varies and a layered architecture where every device has its individual mapped software agent to interface with the onboard crew is one of the most promising proposals. System modelling on platforms such as RTDS has made it possible to study high fidelity simulations of the notional SPS in a non-destructive and safe environment to test real time controls. It also paves the way for experimenting with new ideas which would otherwise be difficult to study using actual hardware setups. Formulating techniques to handle power delivery and ensure continuity of power to vital loads in the network is followed by going into further detail dealing with system and device level faults. An important positive from the research presented in this section is the viability of using software such as MATLAB-SIMULINK, PSCAD etc. for conducting SPS related experiments. Research related to fault studies specific to the notional SPS is described in the next section.

# 2.4 SPS related automated fault detection, diagnosis and

#### prognosis

Moving on, the next crucial study area on a system-wide basis is fault studies and particularly identification, location and diagnosis. Researchers such as Amy, Momoh, and Schulz have highlighted fundamental differences between terrestrial and shipboard power systems. Keeping these in mind, the need for understanding fault manifestations within the novel architecture becomes vital. Known methods to diagnose system wide faults, accommodate them and mitigate associated risks could be borrowed from terrestrial power system applications or from traditional shipboard systems. However, a careful analysis of faults and the system's associated behaviour is necessary owing to the fundamental differences between the envisioned architecture and the traditional shipboard power system as well as terrestrial networks. It is possible that well known fault diagnostic methods could need modifications to be applied to the studied system or completely new diagnostic methods may be needed to deliver efficient performance.

In [10], Logan outlines the various crucial needs to fulfil the proposed functions of the envisioned IPS architecture. Extensive use of PEBB technology is proposed to facilitate a plug-and-play hardware concept thereby reducing the cost and time for research related experimentation as well as benefitting application aboard the notional warship. An important figure mentioned by Logan is the reduction in manning by up to 90% compared to current vessels. As a result, the importance of decision support and automation in activities such as diagnostics, reconfiguration and restoration becomes very clear. In this paper, the extensive use of power electronic devices (e.g. converters) for the proposed SPS is highlighted. The use of artificial intelligence (AI) based algorithms for reconfiguration, survivability and fault diagnostics is emphasized which points towards importance of having detailed understanding of the network dynamics, fault cases and methods to mitigate or eliminate the associated risks. In the light of having a far reduced number of human personnel onboard, the paper reports on the major areas for the all electric ship where automated intelligent diagnostics related knowledge will be needed such as,

- 1. Sensors

- 2. Thermal management system

- 3. Power sources

- 4. Power transmission network

- 5. Control system

- 6. Power electronic devices

- 7. High power and vital loads (e.g. electric rail gun)

The high percentage of reduced manning proposed makes enhanced automation a necessity especially in activities such as system reconfiguration, power restoration and fault diagnostics in the event of a risk. The novelty of the proposed distribution architecture makes studies into network topologies and its modification during various operational scenarios followed by reconfiguration of the system an important research topic. Several researchers have proposed intelligent methods to analyse as well as reconfigure simulated versions of the proposed shipboard power system architecture.

Cartes et al. in [32] provide a more detailed overview of state-of-the-art developments in the IPS research arena emphasising fault diagnostics, prognostics and the informed transition of US navy ships towards condition based maintenance (CBM) systems that are able to intelligently identify when maintenance is needed. The use of intelligent systems such as MAS for various applications on the SPS is highlighted. The idea to match every major device or vital load in the SPS to its respective agent is proposed in this research. A clear list of tasks is highlighted for both diagnostic and prognostic agents. Application of agents is extended to various sub-systems of the SPS shown in fig.2.3. Numerous examples are given to explain functions of various agents constituting the MAS. This paper is important for emphasising the need for intelligent systems utilising schemes such as CBM onboard the warship. Further, the authors provide adequate detail with literature reviews about similar systems from which lessons could be learnt to develop the notional SPS. The encouragement for using agents adheres to one of the envisioned goals of reduced manning aboard the notional warship which can be replaced by the agents. Obviously, this means that a lot of work is needed to make agents intelligent and resourceful enough to take the place of human personnel. For this purpose more detailed and rigorous research is needed into understanding SPS behaviour in the presence of faults.

Figure 2.3: Various MAS applications for SPS sub-systems [32]