# GPU Accelerated Simulation of Transport Systems

Peter Thomas Heywood

A thesis submitted in partial fulfilment of the requirements for the degree of  $Doctor\ of\ Philosophy$

> The University of Sheffield Faculty of Engineering Department of Computer Science

> > February 2021

# Acknowledgements

I would first like to thank Dr Paul Richmond and Dr Steve Maddock for their support, guidance and perseverance as my academic supervisors.

Thank you to Rob, Mozhgan and other members of the Visual Computing research group and Research Software Engineering team for their assistance and for making the office an enjoyable place to be.

I would also like to thank my friends for making Sheffield such an enjoyable place to live and especially the kayakers for the many days spent on the water.

Most importantly I'd like to thank my family, including my sister Sarah and my parents for their unending support.

I am grateful to Ian Wright and David Swain of Atkins for access and insight into the SAT-URN macroscopic simulation tool and for providing access to the real-world road networks. I would also like to extend thanks to Jordi Casas and Mark Brackstone of Aimsun for providing guidance and access to Aimsun microscopic road network simulator.

This work was supported by a Department for Transport Transport Technology Research Innovation Grant (T-TRIG July 2016) "Accelerating Transport Microsimulation: Demonstrating the impact of future many core simulations" <sup>1</sup>, and additional support through EPSRC fellowship "Accelerating Scientific Discovery with Accelerated Computing" (EP/N018869/1)<sup>2</sup>.

<sup>&</sup>lt;sup>1</sup>https://www.gov.uk/government/publications/transport-technology-research-innovation-grantst-trig-funding-winners

<sup>&</sup>lt;sup>2</sup>https://gow.epsrc.ukri.org/NGBOViewGrant.aspx?GrantRef=EP/N018869/1

## Abstract

Computer modelling and simulation of road networks are a vital tool used to evaluate, design and manage road network infrastructure. Road network simulations are however computationally expensive, with simulation runtime imposing limits on the scale and quantity of simulations performed within a reasonable time frame. This thesis examines the appropriateness of manycore processing architectures (such as GPUs) for the acceleration of microscopic and macroscopic road network simulation, and the potential impact on the choice of modelling approach.

Fine-grained agent-based microscopic simulations of individual vehicles are parallelised using GPUs, achieving high performance through a novel graph-based communication strategy for data-parallel simulations. A minimal benchmark model and scalable road network are defined and used experimentally to evaluate performance compared to Aimsun, a commercial simulation tool for multi-core processors. Performance improvements of up to 67x are demonstrated for large scale simulations.

High-level macroscopic simulations model network flow rather than individual vehicles. Although less computationally demanding than microscopic models, simulation runtimes can still be significant, often due to the calculation of many shortest paths. A novel Many-Source Shortest Path (MSSP) algorithm is proposed to concurrently find multiple shortest paths through sparse transport networks using GPUs. This is embedded within a commercial multi-core CPU macroscopic simulation tool, SATURN, and the performance evaluated on large-scale real-world road networks, demonstrating assignment performance improvements of up to 8.6x when comparing multi-processor GPU and CPU implementations.

Finally, the impact of the performance improvements to both modelling techniques are evaluated using a common benchmark model and the relative improvements demonstrated by the benchmarking of each approach using different transport networks. These results suggest that GPUs will allow modellers to shift towards using finer-grained simulations for a broader range of modelling tasks.

# Declaration

I, the author, confirm that the Thesis is my own work. I am aware of the University's Guidance on the Use of Unfair Means (www.sheffield.ac.uk/ssid/unfair-means). This work has not been previously been presented for an award at this, or any other, university.

# Contents

## Preface

|          | Acki | nowledg  | gements                                                                                                                    |

|----------|------|----------|----------------------------------------------------------------------------------------------------------------------------|

|          | Abst | tract .  | ii                                                                                                                         |

|          | Decl | laration | · · · · · · · · · · · · · · · · · · ·                                                                                      |

|          | Con  | tents .  | iv                                                                                                                         |

|          | List | of Tabl  | les                                                                                                                        |

|          | List | of Figu  | res x                                                                                                                      |

|          | List | of Algo  | prithms                                                                                                                    |

| 1        | Intr | oducti   | ion 1                                                                                                                      |

|          | 1.1  | Aims a   | and Research Outline                                                                                                       |

|          | 1.2  | Contri   | bution to Knowledge                                                                                                        |

|          | 1.3  | Public   | $ations \dots \dots$ |

|          | 1.4  | Thesis   | Structure                                                                                                                  |

| <b>2</b> | Rela | ated W   | Vork 7                                                                                                                     |

|          | 2.1  | Trans    | port Network Modelling and Simulation                                                                                      |

|          |      | 2.1.1    | Complex System Modelling and Simulation                                                                                    |

|          |      | 2.1.2    | Calibration, Validation and Verification of Computer Simulations 9                                                         |

|          |      | 2.1.3    | Road Networks and Users                                                                                                    |

|          |      | 2.1.4    | Properties of Road Network Graphs 12                                                                                       |

|          |      | 2.1.5    | Sparse Graph Data-structures                                                                                               |

|          |      | 2.1.6    | Summary                                                                                                                    |

|          | 2.2  | Parall   | el and Distributed Processing                                                                                              |

|          |      | 2.2.1    | Parallel Processing Approaches and Paradigms                                                                               |

|          |      | 2.2.2    | Parallel Programming Models                                                                                                |

|          |      | 2.2.3    | NVIDIA GPUs and the CUDA Programming Model                                                                                 |

|          |      | 2.2.4    | Summary                                                                                                                    |

|          | 2.3  | Micros   | scopic Road Network Simulation                                                                                             |

|          |      | 2.3.1    | Architecture of a Microscopic Road Network Model                                                                           |

|   |                | 2.3.2 Road Network Agent Based Models and Properties                      | 28 |

|---|----------------|---------------------------------------------------------------------------|----|

|   |                | 2.3.3 Microscopic Road Network Simulation Software                        | 31 |

|   |                | 2.3.4 Agent Based Modelling Frameworks                                    | 32 |

|   |                | 2.3.5 Summary                                                             | 34 |

|   | 2.4            | Combined Macroscopic Road Network Assignment and Simulation               | 34 |

|   |                | 2.4.1 Architecture of a Macroscopic Assignment and Simulation Model       | 34 |

|   |                | 2.4.2 Shortest Path Algorithms for Road Network Assignment                | 38 |

|   |                | 2.4.3 Macroscopic Road Network Simulation Software                        | 45 |

|   |                | 2.4.4 Summary                                                             | 46 |

|   | 2.5            | Summary                                                                   | 46 |

| 3 | GP             | U Accelerated Microscopic Simulation                                      | 48 |

|   | 3.1            | Introduction                                                              | 48 |

|   | 3.2            | CPU-based Microsimulation                                                 | 49 |

|   |                | 3.2.1 Aimsun                                                              | 51 |

|   | 3.3            | Simplified Aimsun Model                                                   | 51 |

|   | 3.4            | Benchmark Network                                                         | 52 |

|   | 3.5            | Benchmark Experiments                                                     | 54 |

|   |                | 3.5.1 Grid-Scale Experiment                                               | 54 |

|   |                | 3.5.2 Input-Flow Experiment                                               | 54 |

|   | 3.6            | CPU Benchmark Results                                                     | 55 |

|   | 3.7            | GPU Microsimulation                                                       | 57 |

|   |                | 3.7.1 FLAME GPU                                                           | 57 |

|   |                | 3.7.2 FLAME GPU Implementation of the Gipps' Car Following model $\ldots$ | 59 |

|   |                | 3.7.3 FLAME GPU Implementation of the Simplified Aimsun Model             | 60 |

|   |                | 3.7.4 Cross Validation                                                    | 61 |

|   |                | 3.7.5 GPU Benchmark Results                                               | 64 |

|   | 3.8            | Summary                                                                   | 67 |

| 4 | $\mathbf{Net}$ | work-Based Communication for Data-Parallel ABM                            | 73 |

|   | 4.1            | Introduction                                                              | 73 |

|   | 4.2            | Agent Communication in FLAME GPU                                          | 74 |

|   | 4.3            | Graph Based Communication                                                 | 75 |

|   | 4.4            | Abstract Graph Communication Benchmark Model                              | 77 |

|   |                | 4.4.1 Benchmark Results                                                   | 80 |

|   | 4.5            | Application to Simplified Aimsun Model                                    | 82 |

|   |                | 4.5.1 Grid-Scale Experiment Results                                       | 82 |

|   |                | 4.5.2 Input-Flow Experiment Results                                       | 85 |

|          | 4.6                                                                                       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88                                                                                                                              |

|----------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| <b>5</b> | GP                                                                                        | U Accelerated Macroscopic Assignment and Simulation                                                                                                                                                                                                                                                                                                                                                                                                               | 92                                                                                                                              |

|          | 5.1                                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 92                                                                                                                              |

|          | 5.2                                                                                       | SATURN                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 94                                                                                                                              |

|          |                                                                                           | 5.2.1 Shortest Path Calculations                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96                                                                                                                              |

|          |                                                                                           | 5.2.2 Flow Accumulation                                                                                                                                                                                                                                                                                                                                                                                                                                           | 98                                                                                                                              |

|          | 5.3                                                                                       | Real-World Benchmark Models                                                                                                                                                                                                                                                                                                                                                                                                                                       | 98                                                                                                                              |

|          | 5.4                                                                                       | GPU Many Source Shortest Path for Sparse Graphs                                                                                                                                                                                                                                                                                                                                                                                                                   | 99                                                                                                                              |

|          | 5.5                                                                                       | GPU Flow Accumulation                                                                                                                                                                                                                                                                                                                                                                                                                                             | 104                                                                                                                             |

|          | 5.6                                                                                       | Multi-GPU Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                          | 108                                                                                                                             |

|          | 5.7                                                                                       | Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 109                                                                                                                             |

|          | 5.8                                                                                       | Benchmark Results                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 110                                                                                                                             |

|          |                                                                                           | 5.8.1 Performance Compared to the Serial Baseline                                                                                                                                                                                                                                                                                                                                                                                                                 | 115                                                                                                                             |

|          |                                                                                           | 5.8.2 Single-Processor Performance                                                                                                                                                                                                                                                                                                                                                                                                                                | 116                                                                                                                             |

|          |                                                                                           | 5.8.3 Multi-Processor Performance                                                                                                                                                                                                                                                                                                                                                                                                                                 | 117                                                                                                                             |

|          |                                                                                           | 5.8.4 Multi-GPU Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                           | 117                                                                                                                             |

|          | 5.9                                                                                       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 120                                                                                                                             |

| 6        | Cor                                                                                       | nparison of GPU Accelerated Road Network Simulation Approaches                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                 |

|          |                                                                                           | inparison of Gr O Accelerated Road Network Simulation Approaches                                                                                                                                                                                                                                                                                                                                                                                                  | 123                                                                                                                             |

|          | 6.1                                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                 |

|          | $6.1 \\ 6.2$                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 123                                                                                                                             |

|          |                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 123<br>124                                                                                                                      |

|          | 6.2                                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 123<br>124<br>127                                                                                                               |

|          | 6.2                                                                                       | Introduction       Introduction         Benchmark Network       Introduction         SATURN Grid Network       Introduction         6.3.1       Benchmark Model Parameters                                                                                                                                                                                                                                                                                        | 123<br>124<br>127                                                                                                               |

|          | 6.2                                                                                       | Introduction       Introduction         Benchmark Network       Introduction         SATURN Grid Network       Introduction         6.3.1       Benchmark Model Parameters                                                                                                                                                                                                                                                                                        | 123<br>124<br>127<br>128<br>128                                                                                                 |

|          | 6.2<br>6.3                                                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ol> <li>123</li> <li>124</li> <li>127</li> <li>128</li> <li>128</li> <li>132</li> </ol>                                        |

| 7        | <ul><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul>                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ol> <li>123</li> <li>124</li> <li>127</li> <li>128</li> <li>128</li> <li>132</li> </ol>                                        |

| 7        | <ul><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul>                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ol> <li>123</li> <li>124</li> <li>127</li> <li>128</li> <li>132</li> <li>136</li> <li>138</li> </ol>                           |

| 7        | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Corr</li> </ul>              | Introduction       Introduction         Benchmark Network       SATURN Grid Network Benchmarking         SATURN Grid Network Benchmarking       6.3.1         Benchmark Model Parameters       6.3.2         Galaxies       6.3.2         Macroscopic Assignment and Simulation Results       6.3.1         Performance Comparison of Microscopic and Macroscopic Simulations       6.3.1         Summary       Summary         Summary       Summary             | <ol> <li>123</li> <li>124</li> <li>127</li> <li>128</li> <li>128</li> <li>132</li> <li>136</li> <li>138</li> <li>141</li> </ol> |

|          | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Cont</li> <li>7.1</li> </ul> | Introduction       Introduction         Benchmark Network       SATURN Grid Network Benchmarking         SATURN Grid Network Benchmarking       6.3.1         Benchmark Model Parameters       6.3.2         Macroscopic Assignment and Simulation Results       6.3.2         Performance Comparison of Microscopic and Macroscopic Simulations       9.1         Summary       Summary         Summary of Main Findings       1.1         Future Work       1.1 | <ol> <li>123</li> <li>124</li> <li>127</li> <li>128</li> <li>128</li> <li>132</li> <li>136</li> <li>138</li> <li>141</li> </ol> |

# List of Tables

| 3.1  | Models selected for the Simplified Aimsun Model from the partial list of aimsun           |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | models and features. Aimsun publications and Documentation provide detailed               |    |

|      | descriptions of these functionalities $([143], [144], [243])$                             | 52 |

| 3.2  | Parameters for generation of the procedurally generated Manhattan-style grid              |    |

|      | road network                                                                              | 53 |

| 3.3  | Network and Model parameters used for the Grid-Scale microscopic experiments.             |    |

|      | Parameters such as the time step, reaction time and detector period were selected         |    |

|      | as values commonly used within microscopic modelling in the UK as informed                |    |

|      | by the Aimsun developers                                                                  | 54 |

| 3.4  | Network and Model parameters used for the Input-Flow microscopic experiments.             |    |

|      | Parameters such as the time step, reaction time and detector period were selected         |    |

|      | as values commonly used within microscopic modelling in the UK as informed by             |    |

|      | the Aimsun developers. Multiple grid sizes were used to assess the performance            |    |

|      | impact of the input flow parameter at multiple network scales. $\ldots$                   | 55 |

| 3.5  | Details of the networks used for cross-validation.                                        | 62 |

| 3.6  | Vehicle model parameters used for the deterministic cross-validation of the ${\rm FLAME}$ |    |

|      | GPU and Aimsun models                                                                     | 62 |

| 3.7  | Truncated normal distributions for vehicle parameters used for the stochastic             |    |

|      | cross-validation of the FLAME GPU and Aimsun models                                       | 63 |

| 3.8  | Key data for the Constant Entrance Flow validation models                                 | 63 |

| 3.9  | Key data for the Car Following Behaviour validation models                                | 63 |

| 3.10 | Velocity for the first vehicle in the 100m, 2250 vehicles per hour input flow, Car        |    |

|      | Following Behaviour validation model                                                      | 64 |

| 3.11 | Key data for the Turing Proportion validation model.                                      | 64 |

| 3.12 | Statistical summary data for the Deterministic Grid validation simulations                | 64 |

| 3.13 | Statistical summary data for the Stochastic Grid validation simulations                   | 64 |

| 5.1 | Serial Fortran per-routine run-time performance for large real-world benchmark          |

|-----|-----------------------------------------------------------------------------------------|

|     | model (5194 zones) sorted by time. The six longest-running routines are shown           |

|     | but with the mangled subroutine names removed. The most time consuming                  |

|     | subroutine $A$ is a key subroutine called within the assignment phase of the as-        |

|     | signment simulation loop. This subroutine finds the flow of vehicles per edge           |

|     | in the network, based on the origin-destination information and the state of the        |

|     | network from the previous assignment-simulation loop                                    |

| 5.2 | Properties of the real-world SATURN networks used during development and                |

|     | benchmarking. The number of vertices and edges are shown for both the original          |

|     | and Spider (contraction hierarchy) variants                                             |

| 5.3 | Validation metrics for the multi-core CPU and GPU implementations of the                |

|     | LoHAM large-scale model                                                                 |

| 5.4 | The hardware used to benchmark real-world performance. The FP64:FP32 Ra-                |

|     | tio column of the GPU properties describes the ratio of double precision float-         |

|     | ing point (FP64) units within the GPU compared to single precision floating             |

|     | point(FP32) units. Most GPU architectures include a relative low number of              |

|     | FP64 units, as they are often not used for computer graphics applications. For          |

|     | General Purpose Computing on Graphics Processing Units (GPGPU) codes which              |

|     | may make heavy use of FP64 operations, including the flow-accumulation phase            |

|     | of SATALL, choosing a Graphics Processing Unit (GPU) architecture with a                |

|     | higher ratio of FP64 units can have a significant impact on performance. $\ldots$ . 111 |

| 5.5 | Average runtimes in seconds for the total and assignment portions of SATALL             |

|     | application to complete across the three real-world road networks used for bench-       |

|     | marking, across a range of hardware. Note: Serial results are from a single run         |

|     | rather than an average due to runtime                                                   |

| 5.6 | Relative speed-up compared to the single-CPU single-core results for single-socket      |

|     | CPU and single-GPU. Note: Serial results are from a single run rather than an           |

|     | average due to runtime                                                                  |

| 5.7 | Relative speed-up compared to the single-socket multi-core Central Processing           |

|     | Unit (CPU) results (system P). Higher is better                                         |

| 5.8 | Relative speed-up compared to multi-socket CPU (DC)                                     |

| 5.9 | Relative speed-up compared to equivalent single-GPU results                             |

| 6.1 | Parameters used for macroscopic simulations benchmarks of the artificial road           |

|     | network                                                                                 |

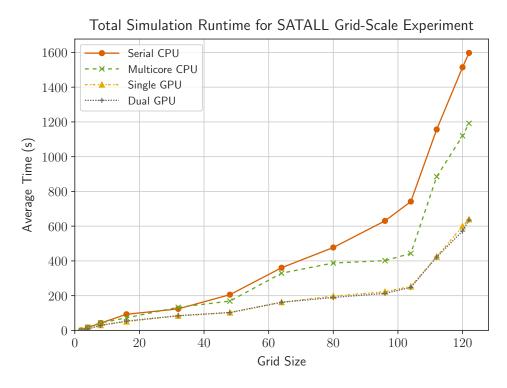

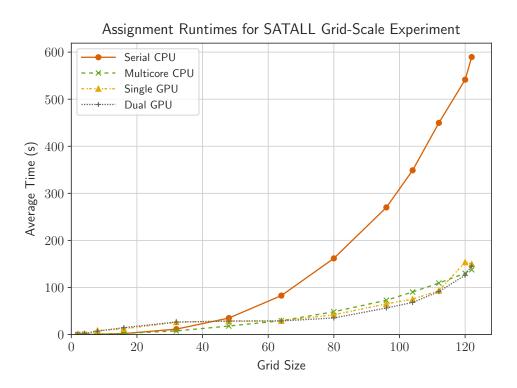

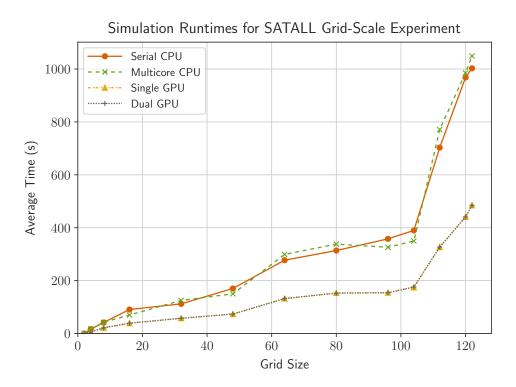

- 6.3 Average runtime (seconds) for the total runtime, assignment runtime and simulation runtime of each grid scale benchmark for the serial CPU (i7 6850k), multicore CPU (i7 6850k using 12 threads), single GPU and dual GPUs (NVIDIA Titan V) macroscopic road network simulation implementation (SATURN). . . . 131

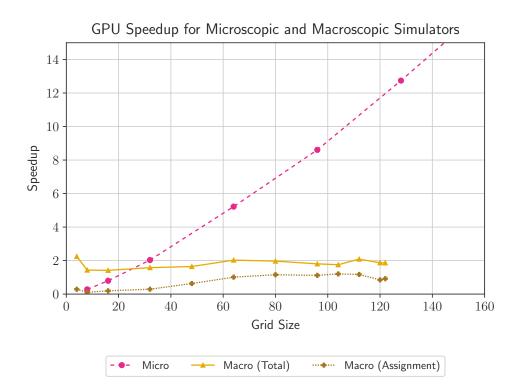

- 6.4 Relative performance improvement comparing simulator performance for a single Titan V GPU against a multi-core CPU implementation executed on an i7-6850k, for each timed phase of SATURN for the grid-scale macroscopic experiment . . . 132

# List of Figures

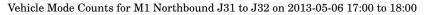

| 2.1 | Road network user mode distribution for a section of road in England (M1 North,               |    |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | J31 to J32) over the 1 hour period between 17:00 and 18:00 on the $6^{\rm th}$ May 2013       |    |

|     | (GB Road Traffic Counts data set [65]). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 11 |

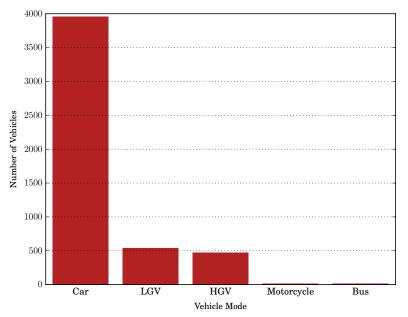

| 2.2 | The correlation between edges, vertices and zones for a small section of a one-way            |    |

|     | road network                                                                                  | 12 |

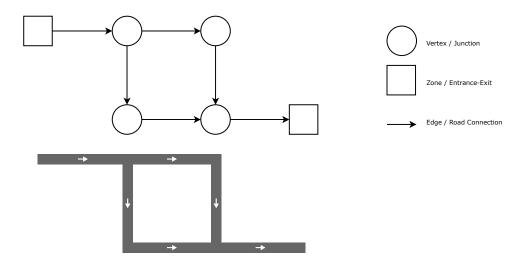

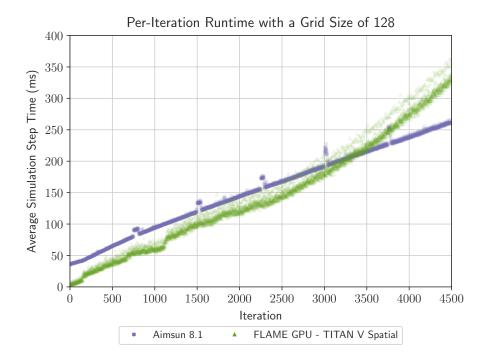

| 2.3 | An simple weighted directed graph and the associated representation of the sparse             |    |

|     | adjacency matrix in COO, Compressed Sparse Row (CSR), and Compressed                          |    |

|     | Sparse Column (CSC) formats. The graph contains 4 vertices and 6 weighted                     |    |

|     | edges. Vertices are indexed from 0 to 3, with edge weights in the range 4 to 9.               |    |

|     | Edges weights are uniquely coloured to aid readability.                                       | 14 |

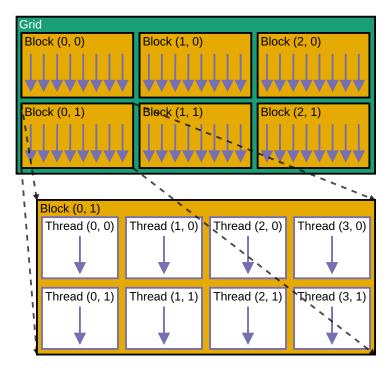

| 2.4 | An illustration of the CUDA thread hierarchy, for a 2D grid of 6 blocks, where                |    |

|     | each 2D block contains 8 threads. The arrangement of threads within a 2D block $$             |    |

|     | is shown for block (0, 1)                                                                     | 22 |

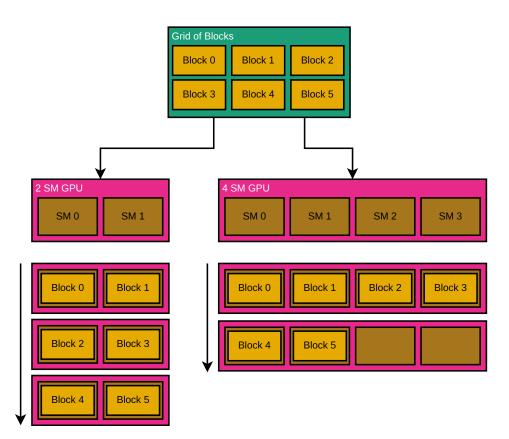

| 2.5 | An illustration showing how the CUDA thread hierarchy allows a kernel using a                 |    |

|     | grid of 6 thread-blocks to be executed on GPUs with 2 or 4 Streaming Multipro-                |    |

|     | cessors (SMs).                                                                                | 23 |

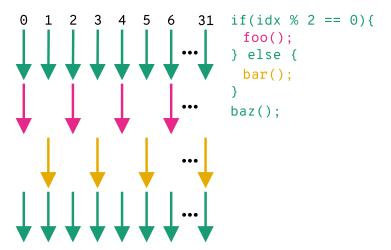

| 2.6 | An illustration of divergence occurring within an SM following the Single-Instruction $\cdot$ | -  |

|     | Multiple-Thread (SIMT) GPU architecture. Threads with odd indices perform                     |    |

|     | separate operations to those with even indices, and therefore must be executed                |    |

|     | independently, prior to re-converging for a warp-wide operation. GPU Architec-                |    |

|     | tures which support independent thread scheduling will not necessarily recon-                 |    |

|     | verge without explicit synchronisation.                                                       | 24 |

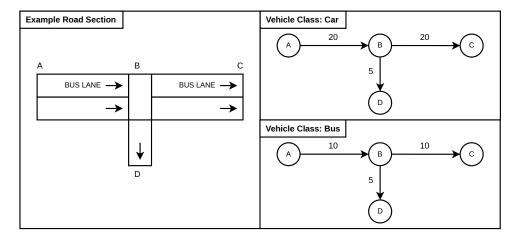

| 2.7 | An illustration of a section of road network containing 3 sections of one-way                 |    |

|     | road, two of which have vehicle class restrictions. The road network graphs                   |    |

|     | representing these sections of road are shown for two vehicle classes, with edge              |    |

|     | weights representing travel time along the section. Due to the presence of the                |    |

|     | bus lanes, the road network graphs have differing values for each vehicle class               | 36 |

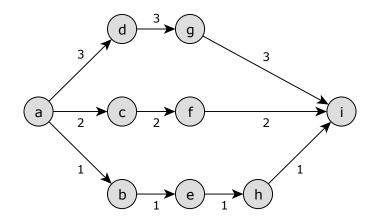

| 2.8 | A small directed weighted graph containing 9 vertices and and 10 weighted edges.              | 40 |

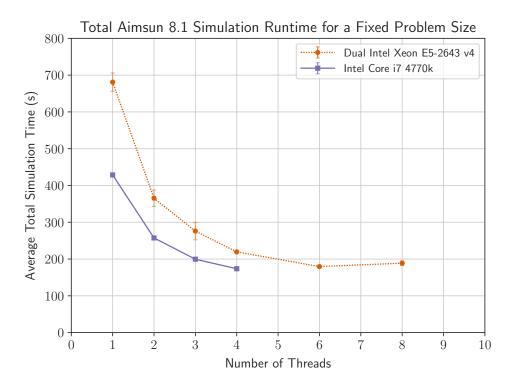

| 3.1 | The average simulation run-time to complete a one hour simulation a total de-                |    |

|-----|----------------------------------------------------------------------------------------------|----|

|     | mand of 64000 vehicles in Aimsun 8.1, for different processor thread counts. The             |    |

|     | average of three simulations is shown. Error bars show the first standard de-                |    |

|     | viation of the application runtime, but for some data points are smaller than                |    |

|     | the marker size. As processor thread count increases, total simulation time de-              |    |

|     | creases, but with diminishing returns. Note that the Intel Xeon $E5-2643$ is a               |    |

|     | dual-socket system. No performance improvements were observed when using                     |    |

|     | more processing threads than physical cores (Hyper-threading)                                | 50 |

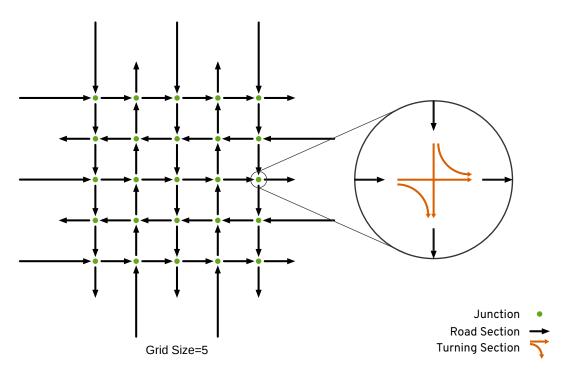

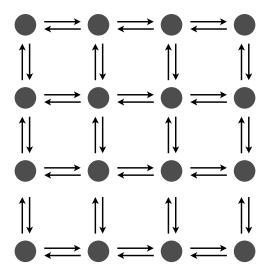

| 3.2 | A $5\times 5$ example of the procedurally-generated artificial grid network, showing the     |    |

|     | overall structure of the network and the arrangement of turning sections within a            |    |

|     | junction. The network can be scaled to any size, with networks of up to $576\times576$       |    |

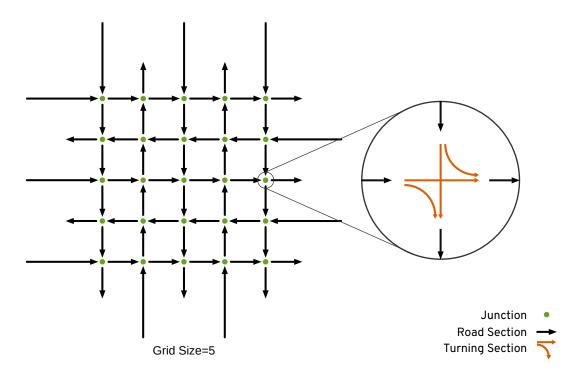

|     | used during benchmarking.                                                                    | 53 |

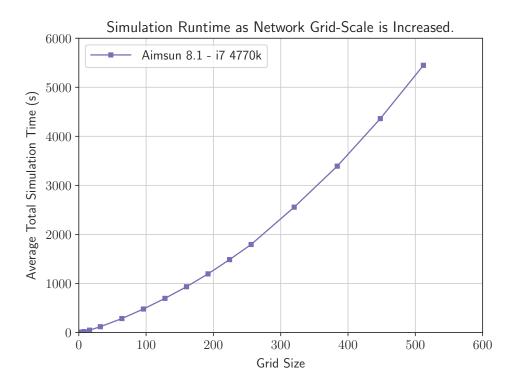

| 3.3 | Total simulation time for Aimsun 8.1 as the total scale of the simulation is in-             |    |

|     | creased. Values shown are the average from 3 repetitions. The model and network              |    |

|     | parameters used for this benchmark are shown in Table 3.3                                    | 56 |

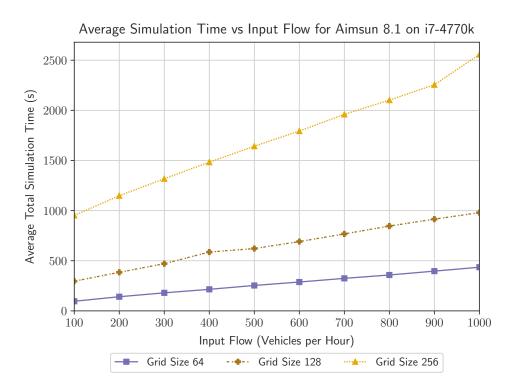

| 3.4 | Total simulation time for Aimsun 8.1 against input flow for procedurally gener-              |    |

|     | ated road networks of grid size 64, 128 and 256. Run times shown are the average             |    |

|     | from 3 repetitions. The model and network parameters used for this benchmark                 |    |

|     | are shown in Table 3.4. Transport for London guidance suggests maximum de-                   |    |

|     | sign capacities of between 900 and 1600 vehicles per hour per lane for urban,                |    |

|     | single carriage<br>way, one-way roads with speed limits of 30mph ( $\sim$ 50<br>kmph) [244]. |    |

|     | Benchmarks with input flows greater than 1000 vehicles per hour were not per-                |    |

|     | formed due to stop-sign induced queues preventing vehicles from entering the                 |    |

|     | simulated region of the artificial benchmark road network which occurred more                |    |

|     | frequently as input flows were increased.                                                    | 57 |

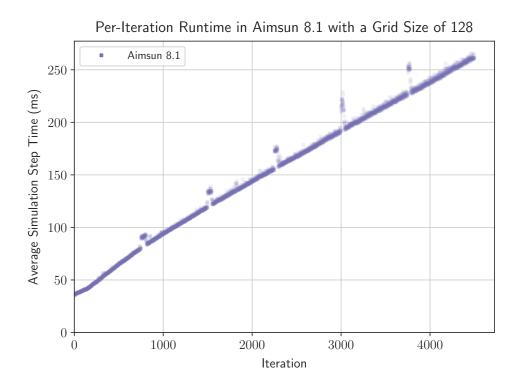

| 3.5 | Per-Iteration simulation time for a model with grid size $128$ and input flow $500$          |    |

|     | vehicles per hour                                                                            | 58 |

| 3.6 | Average iteration execution time for fixed grid of size $N = 16$ against agent               |    |

|     | population size, averaged over 100 iterations. Results generated using an NVIDIA $$          |    |

|     | Tesla K20c GPU                                                                               | 68 |

| 3.7 | Average iteration execution time per agent for fixed grid of size $N = 16$ against           |    |

|     | agent population size, averaged over 100 iterations. Results generated using an              |    |

|     | NVIDIA Tesla K20c GPU                                                                        | 68 |

|     |                                                                                              |    |

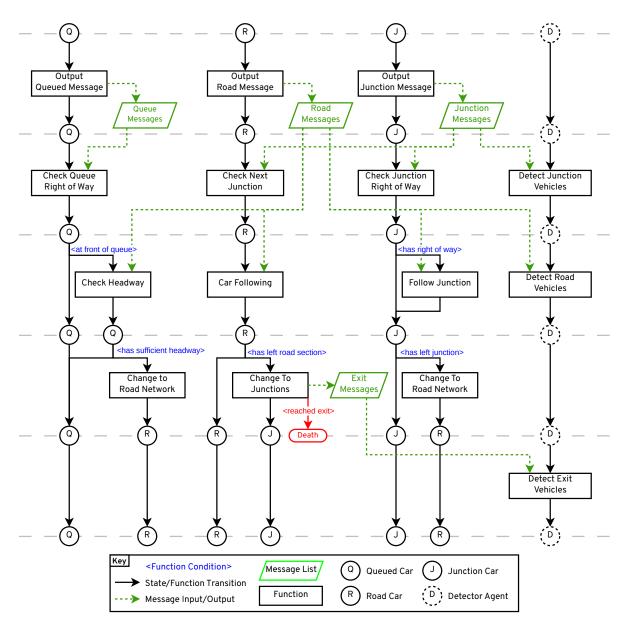

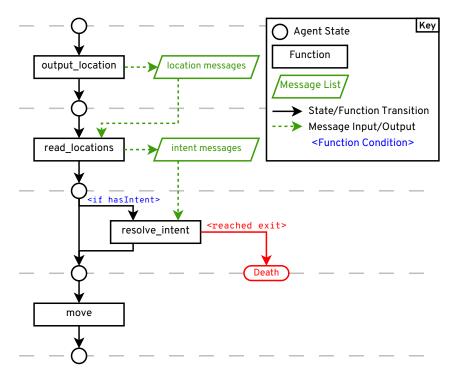

| 3.8  | Flexible Large-scale Agent Modelling Environment for Graphics Processing Unit                   |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | (FLAME GPU) per-iteration state diagram for <i>vehicle</i> and <i>detector</i> agents. Il-      |    |

|      | lustrates the logical control-flow of the agents within a single iteration of the               |    |

|      | simulation, arranged in simulation layers. Circles represent a type of agent in a               |    |

|      | given state, as described by the key. Agent functions are shown by rectangles,                  |    |

|      | which can result in a change of state. Message lists are shown in green, with                   |    |

|      | dotted arrows indicating the output and input of messages                                       | 69 |

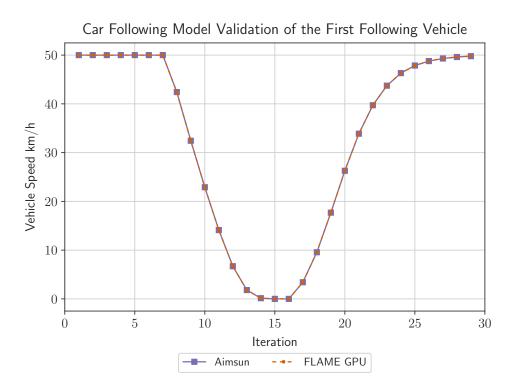

| 3.9  | Car Following Model Velocity validation. The velocity of the first vehicle in the               |    |

|      | $100 \mathrm{m}$ Car following behaviour validation model with input flow set to $2250$ vehicle |    |

|      | per hour were manually extracted from Aimsun and FLAME GPU. Comparable                          |    |

|      | results are shown                                                                               | 70 |

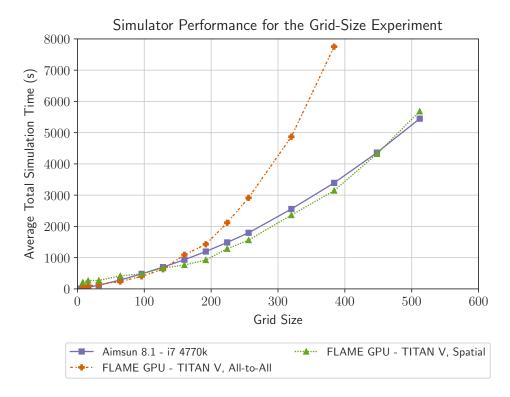

| 3.10 | Total simulation performance as the total scale of the simulation is increased, for             |    |

|      | each simulator. Values shown are the average from 3 repetitions. Executed using                 |    |

|      | alternate communication strategies available in FLAME GPU 1.4.                                  | 70 |

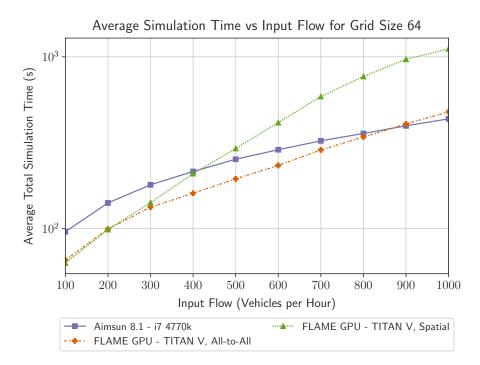

| 3.11 | Total simulation time against input flow for a procedurally generated road net-                 |    |

|      | work of grid size 64. Run times shown are the average from 3 repetitions, using                 |    |

|      | a logarithmic scale. The CPU simulation results from Aimsun 8.1 executed on                     |    |

|      | a 4-core, 8-thread Intel i7 4770k are shown in purple. These are compared to                    |    |

|      | results from the GPU simulations using all-to-all and spatially partitioned com-                |    |

|      | munication, shown by the orange and green series respectively, executed on an                   |    |

|      | NVIDIA Titan V GPU.                                                                             | 71 |

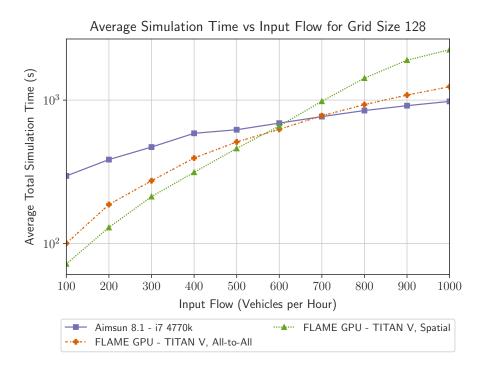

| 3.12 | Total simulation time against input flow for a procedurally generated road net-                 |    |

|      | work of grid size 128. Run times shown are the average from 3 repetitions, using                |    |

|      | a logarithmic scale. The CPU simulation results from Aimsun 8.1 executed on                     |    |

|      | a 4-core, 8-thread Intel i7 4770k are shown in purple. These are compared to                    |    |

|      | results from the GPU simulations using all-to-all and spatially partitioned com-                |    |

|      | munication, shown by the orange and green series respectively, executed on an                   |    |

|      | NVIDIA Titan V GPU.                                                                             | 71 |

| 3.13 | Total simulation time against input flow for a procedurally generated road net-                 |    |

|      | work of grid size 256. Run times shown are the average from 3 repetitions, using                |    |

|      | a logarithmic scale. The CPU simulation results from Aimsun $8.1$ executed on                   |    |

|      | a 4-core, 8-thread Intel i7 4770k are shown in purple. These are compared to                    |    |

|      | results from the GPU simulations using all-to-all and spatially partitioned com-                |    |

|      | munication, shown by the orange and green series respectively, executed on an                   |    |

|      | NVIDIA Titan V GPU.                                                                             | 72 |

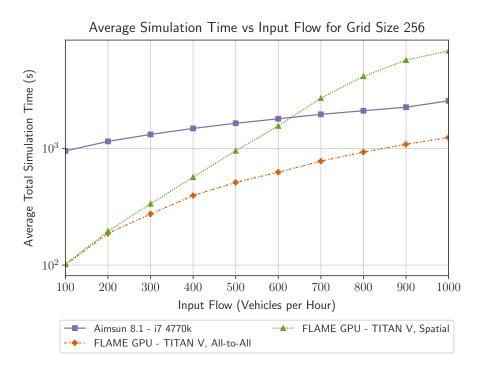

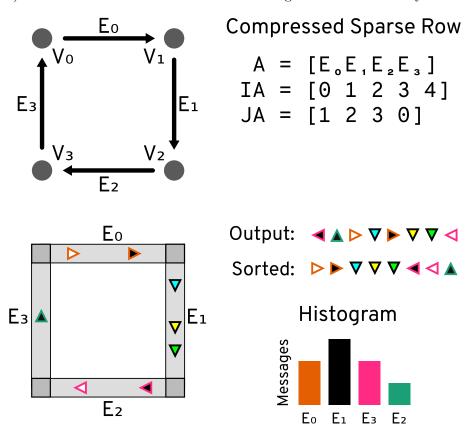

- 3.14 Per-Iteration simulation time for a model with grid size 128 and input flow 500 vehicles per hour. Executed using Aimsun 8.1 (purple) on an i7 4770k, and using the FLAME GPU implementation with Spatially Partitioned Communication, on an NVIDIA Titan V GPU.

72

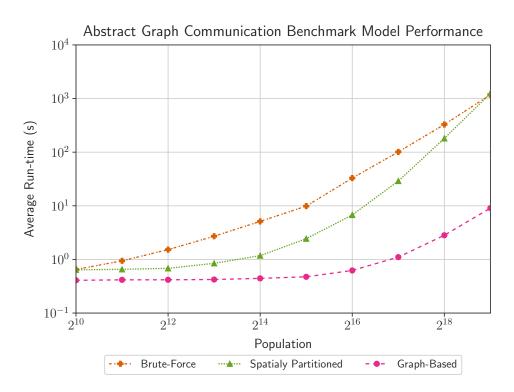

- 4.5 The effects of alternate FLAME GPU communication strategies on car following models is shown for a section of a grid-based road network, for a single agent represented in white. All-to-all communication results in 42 messages being parsed by the single agent. Spatially partitioned messaging results in the 18 messages from the agents in the blue shaded region, while the graph-based communication strategy results in only 5 messages from the orange bordered agents being processed. The spatially partitioned radius used for this illustration would be insufficient for accurate modelling, and is only used for illustrative purposes. . . 83

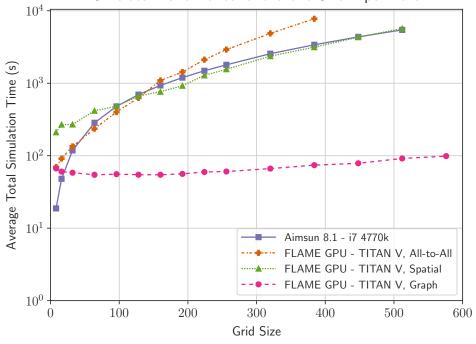

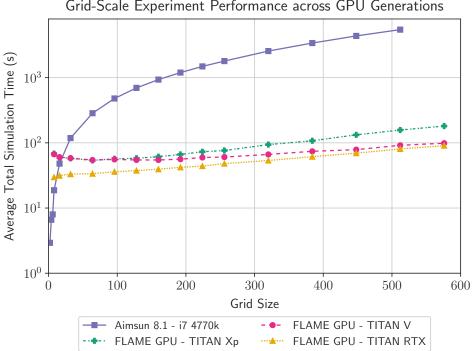

- 4.6 Total simulation performance as the total scale of the simulation is increased, showing the performance of the CPU simulations, and the alternate GPU simulations using a single GPU. Values shown are the average from 3 repetitions. A logarithmic scale is used to improve visibility of similar total simulation times. 84

- 4.7 Total simulation performance as the total scale of the simulation is increased, for each simulator. Values shown are the average from 3 repetitions, for the CPU simulator and for the graph-based messaging GPU simulator using multiple GPUs. A logarithmic scale is used to improve visibility of similar total simulation times.

85

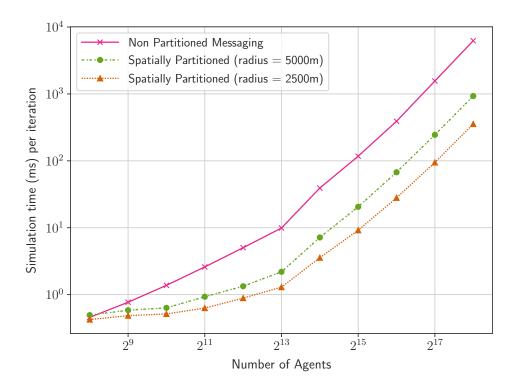

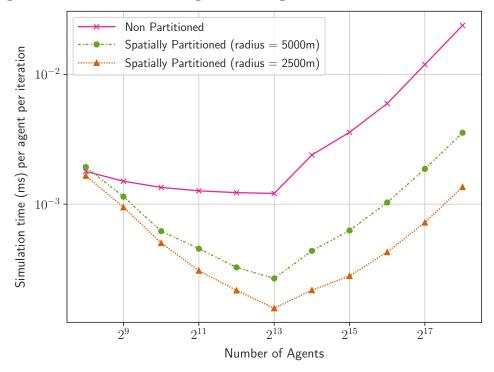

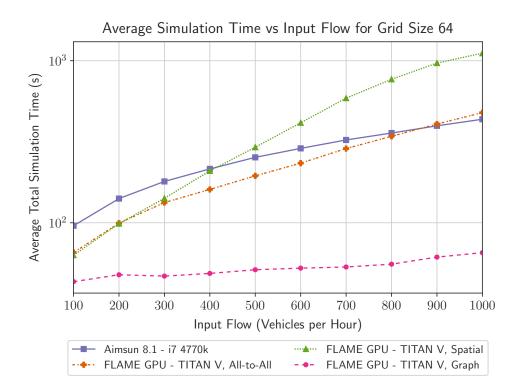

- 4.8 Total simulation time against input flow for a procedurally generated road network of grid size 64. Run times shown are the average from 3 repetitions. A logarithmic scale is used for the y axis. The results shown include the reference CPU simulator, Aimsun 8.1, executed on an i7-4770k (purple); and the results from FLAME GPU executed on an NVIDIA Titan V GPU using all-to-all (or-ange), spatial (green) and graph-based (pink) communication strategies. . . . . . 87

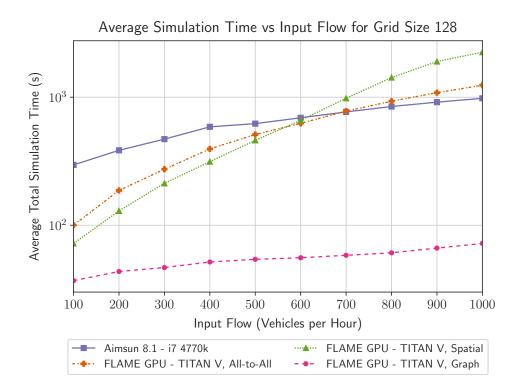

- 4.9 Total simulation time against input flow for a procedurally generated road network of grid size 128. Run times shown are the average from 3 repetitions. A logarithmic scale is used for the y axis. The results shown include the reference CPU simulator, Aimsun 8.1, executed on an i7-4770k (purple); and the results from FLAME GPU executed on an NVIDIA Titan V GPU using all-to-all (or-ange), spatial (green) and graph-based (pink) communication strategies. . . . . . 88

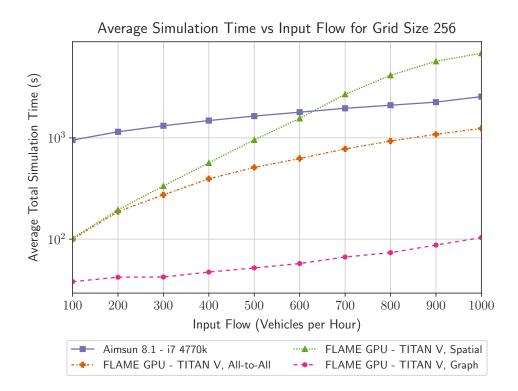

- 4.10 Total simulation time against input flow for a procedurally generated road network of grid size 256. Run times shown are the average from 3 repetitions. A logarithmic scale is used for the y axis. The results shown include the reference CPU simulator, Aimsun 8.1, executed on an i7-4770k (purple); and the results from FLAME GPU executed on an NVIDIA Titan V GPU using all-to-all (or-ange), spatial (green) and graph-based (pink) communication strategies. . . . . 89

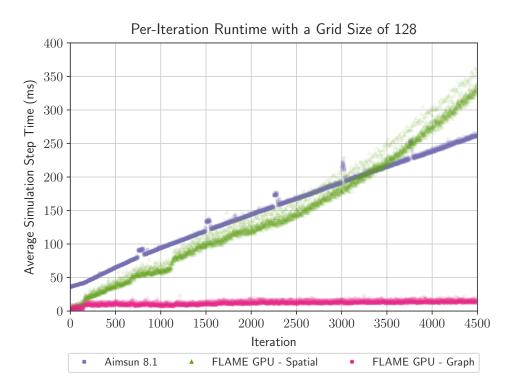

- 4.11 Per-Iteration simulation time for a model with grid size 128 and input flow 500 vehicles per hour. Executed using Aimsun 8.1 (purple) on an i7 4770k and using the FLAME GPU implementations with Spatially Partitioned communication (green) and Graph-based communication (pink) on an NVIDIA Titan V GPU.

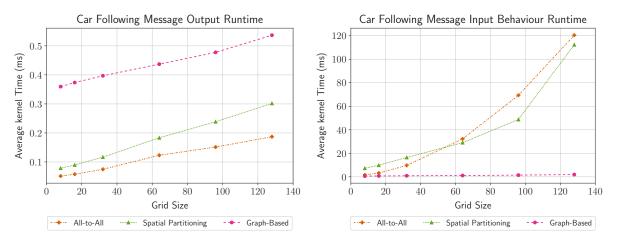

- 4.12 The impact of FLAME GPU communication specialisation on the performance of the Car Following Model implementation can be separated into the cost of the message output and the message iteration within the car following agent function. FLAME GPU was modified to accurately record the cost of each process, and the average of three repetitions at each scale is shown. The simulations were executed on an NVIDIA TITAN X (Pascal) GPU.

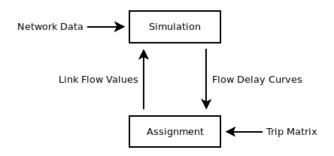

| 5.1  | The assignment-simulation loop within SATURN $[235]$                                                                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

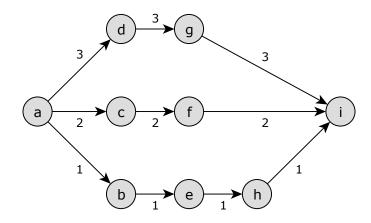

| 5.2  | A simple example graph to illustrate the use of a vertex-frontier                                                                                                              |

| 5.3  | The contents of the vertex-frontier for the Bellman-Ford algorithm, for origin                                                                                                 |

|      | vertex <b>a</b> of the example graph in Figure 5.2                                                                                                                             |

| 5.4  | The contents of the origin-vertex-frontier within the the Many Source Shortest                                                                                                 |

|      | Path (MSSP) algorithm, for origin vertices <b>a</b> and <b>b</b> of the example graph in                                                                                       |

|      | Figure 5.2                                                                                                                                                                     |

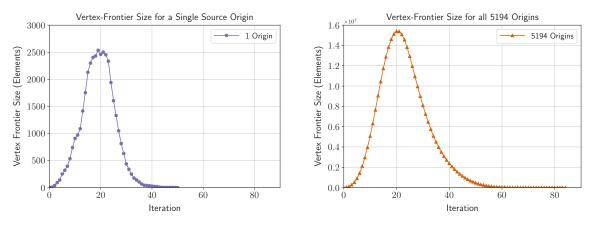

| 5.5  | The size of the vertex-frontier and origin-vertex-frontier at each iteration of the                                                                                            |

|      | modified Bellman-Ford algorithm for the LoHAM large road network, containing                                                                                                   |

|      | 5194 zones. The frontier size is shown for a single origin vertex and for all $5194$                                                                                           |

|      | origin vertices                                                                                                                                                                |

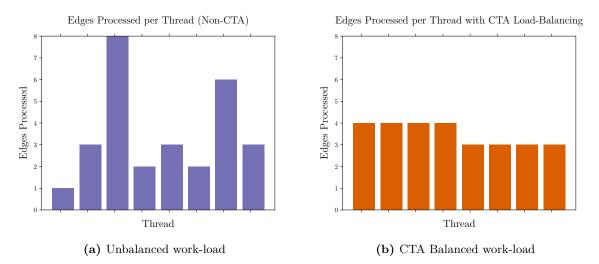

| 5.6  | The load-balancing effect of the cooperative thread array for 28 edges distributed                                                                                             |

|      | across 8 threads. The imbalance of work has been minimised from a maximum                                                                                                      |

|      | divergence of 7 edges to a single edge. $\ldots \ldots \ldots$ |

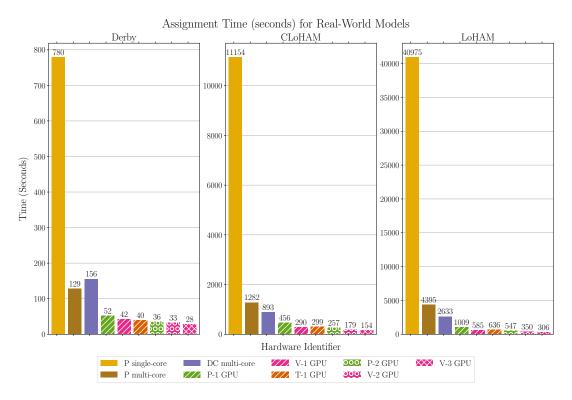

| 5.7  | The runtime (seconds) of the assignment phase of SATALL for the three real                                                                                                     |

|      | world models on various CPUs and GPUs. Lower times are better. Note that                                                                                                       |

|      | the Y axis is not shared between models                                                                                                                                        |

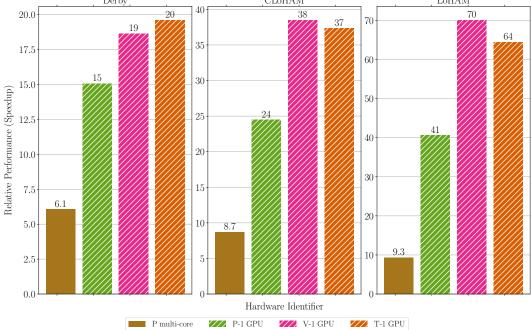

| 5.8  | The relative speed-up of the assignment phase of SATALL for three real world                                                                                                   |

|      | models compared to serial, single CPU core results. Higher is better                                                                                                           |

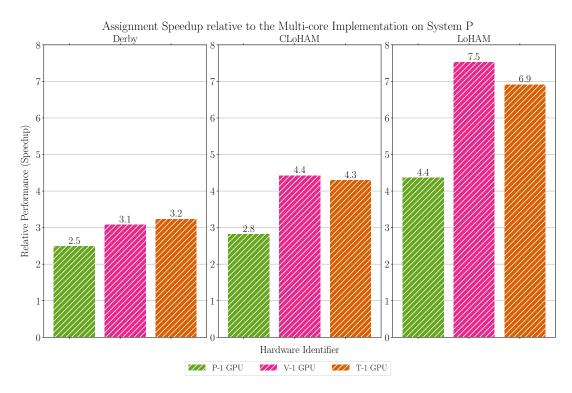

| 5.9  | The relative speed-up of the assignment phase of SATALL for three real world                                                                                                   |

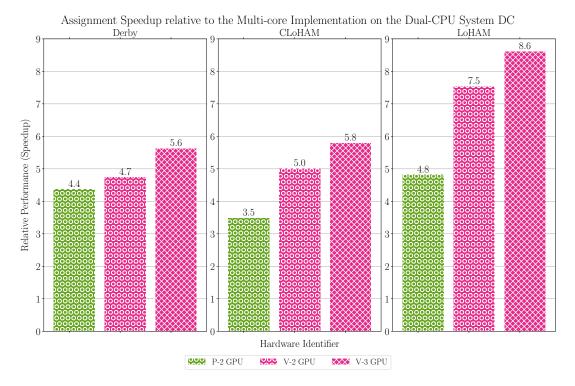

|      | models on single CPU and single-GPU systems compared to a single multi-core                                                                                                    |

|      | CPU                                                                                                                                                                            |

| 5.10 | The runtime of the assignment phase of SATALL for three real world models                                                                                                      |

|      | comparing multi-socket CPU and multi-GPU implementations                                                                                                                       |

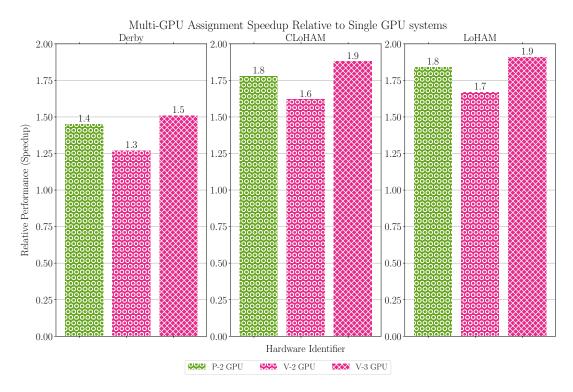

| 5.11 | The relative speed-up of the assignment phase of SATALL for three real world                                                                                                   |

|      | models on multi-GPU systems, compared to multi-socket CPU results 119                                                                                                          |

| 5.12 | The relative speed-up of the assignment phase of SATALL for three real world                                                                                                   |

|      | models on multi-GPU systems, compared to the matching single-GPU system $120$                                                                                                  |

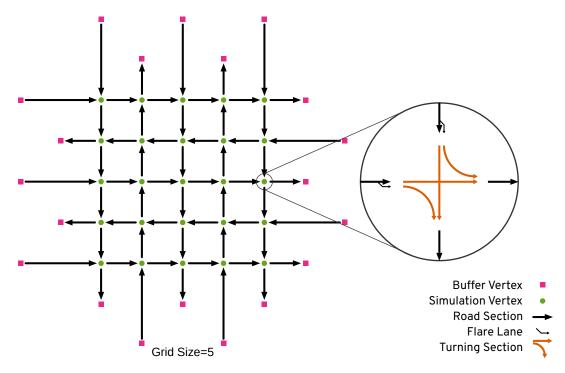

| 6.1  | A 5 $\times$ 5 example of the procedurally-generated artificial grid network used for                                                                                          |

|      | microscopic simulations, showing the overall structure of the network and the                                                                                                  |

|      | arrangement of turning sections within a junction. The network can be scaled to                                                                                                |

|      | any size, with networks of up to $576 \times 576$ used during benchmarking 125                                                                                                 |

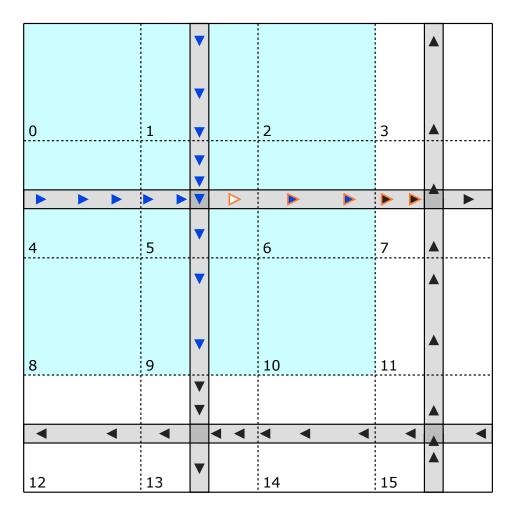

- 6.3 The average total runtime of SATURN for the grid-scale benchmark, for CPU and GPU implementations. Values shown are the average from 3 repetitions. . . 130

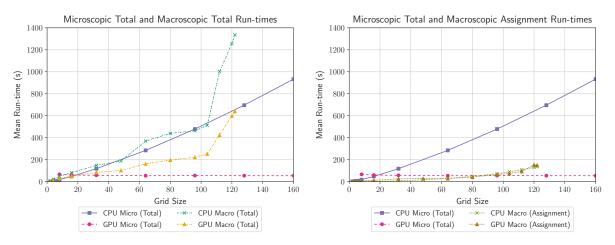

- 6.4 The average runtimes of the assignment portion of SATURN for the grid-scale benchmark, for CPU and GPU implementations. The simulation portion is always executed in serial on the CPU. Values shown are the average from 3 repetitions.132

- 6.5 The average runtimes of the simulation portion of SATURN for the grid-scale benchmark, for CPU and GPU implementations. The simulation portion is always executed in serial on the CPU. Values shown are the average from 3 repetitions.133

# List of Algorithms

| 1 | Dijkstra's SSSP Algorithm                                                             |

|---|---------------------------------------------------------------------------------------|

| 2 | D'Esopo-Pape Sequential SSSP Algorithm                                                |

| 3 | Original Bellman-Ford Single Source Shortest Path (SSSP) Algorithm $\ldots \ldots 44$ |

| 4 | Existing Serial SATALL algorithm                                                      |

| 5 | Sequential Flow Accumulation                                                          |

| 6 | Many Source Shortest Path (MSSP) algorithm based on the Bellman-Ford al-              |

|   | gorithm, using an Origin-Vertex Frontier for execution on Single-Instruction-         |

|   | Multiple-Thread (SIMT) architectures                                                  |

| 7 | GPU Flow Accumulation using double-precision atomic addition. This is suitable        |

|   | for Pascal-generation Nvidia GPUs and newer. $\ldots$                                 |

| 8 | GPU accelerated flow accumulation algorithm using a reduced number of double-         |

|   | precision atomic operations. This is suitable for hardware with poor double-          |

|   | precision atomic addition performance, such as Maxwell and Kepler generation          |

|   | Nvidia GPUs                                                                           |

## Chapter 1

# Introduction

Demand on transportation systems is increasing around the globe, for instance in the UK the Department for Transport (DfT) have projected increases of up to 42% in car ownership and up to 55% growth in UK road traffic demand between 2010 and 2040 [1]. Along with the increasing demand, existing network infrastructure is often underutilised resulting in reduced capacity available to transport network users [2].

The effects of increased demand and reduced capacity due to underutilisation can be countered through improved traffic management systems and improved network design tools [3]. Computer models and simulations allow transport authorities to perform virtual trials of proposed alterations prior to real world changes, removing the risk and cost of real world trials [4]. They may also be used to study the impacts of road network factors such as public health or the environment [5], [6]. Low-latency simulators can be integrated into automatic traffic management systems, reducing the need for human input to manage complex scenarios [7], [8].

Transport system simulators can typically be classified into one of three categories based on the granularity of the modelling: *macroscopic*, *mesoscopic* & *microscopic*. Macroscopic simulations use a *top-down* approach to accurately model the flow of transport through a network, using abstract representation such as modelling traffic as fluids [9], [10]. Mesoscopic simulations model use an intermediate resolution, often modelling the behaviours of groups (platoons) of individuals [11]. Microscopic simulations (*bottom-up*) are fine-grained models concerned with the behaviors of individuals and their local interactions [12].

Traditionally, macroscopic simulations were predominately used for transport modelling due to lower computational complexity than the finer-grained methodologies [13]. However, as computational resources have increased over time, microscopic simulators are becoming more prominent due to the benefits they provide, although the effectiveness and uptake of microscopic simulators is still limited by performance [14]. Microsimulations and Agent Based Modelling (ABM), a technique for naturally describing individual (agent) behaviours in a simulation [15], provide advantages over the more traditional macroscopic approaches for modelling transport systems, such as improved capability for accurately modelling congested systems where the position of individual vehicles is relevant.

The runtime of road network simulations can be considerable, leading to sacrifices being made in the number of scenarios being considered and subsequently simulated. A frequently used solution is to consider only a single "average day" of the year, which may not accurately reflect any individual day [16]. A suitable approach to improve performance of transport network simulations is to parallelise the simulation, executing instructions concurrently on parallel hardware to yield higher performance and reduced runtimes. Macroscopic, mesoscopic and microscopic simulations are all suitable for parallel processing to varying degrees. Although transport simulations are not *embarrassingly parallel*, modern many-core processing architectures such as Graphics Processing Units (GPUs) offer the potential for significant enhancements to simulation performance. GPUs are high-throughput co-processors, which use many relatively simple processing cores to provide high levels of concurrency for data-parallel applications, compared to modern multi-core Central Processing Unit (CPU) which provide much fewer cores with higher per-core performance.

Using GPUs for parallelisation offers many advantages, for example, within High Performance Computing (HPC) GPU based computers are dominating both the Top 500 [17] and Green 500 [18] as they are can provide a large amount of computational power with lower electrical power requirements than more traditional CPU based HPC solutions [19]. However, using GPUs to increase performance brings additional complexity to achieve the desired levels of performance. The programming model requires specialist knowledge which end-user modellers may not possess and considerations must be made during implementation to achieve high levels of performance. Ultimately, additional performance made available to simulations through General Purpose Computing on Graphics Processing Units (GPGPU) may enable larger-scale and morecomplex real-time (or better than real-time) simulations for use in transport system planning, management and analysis. Additionally, if GPGPU can successfully improve the simulation performance of road network simulations, the relative performance improvements to each modelling approach may influence the choice of modelling approach used. The high computational costs of fine-grained microscopic simulations is a significant factor in use of macroscopic approaches for large-scale simulations. If the performance gap between these opposing approaches is reduced, there may be a shift away from coarse simulation models towards finer-grained models, which can present modellers with additional information, potentially leading to more well-informed decisions.

## 1.1 Aims and Research Outline

This thesis aims to investigate and advance the use of many-core GPUs for the acceleration of road network simulations, considering both fine-grained microscopic models and coarse macroscopic modelling approaches. GPUs are highly parallel, high-throughput devices which must be provided with sufficiently high volumes of work to process concurrently. Microscopic road network simulations have the potential to be well-suited for parallelisation on GPUs due to a number of factors in their design. They are computationally demanding simulations, which perform fine-grained simulations of individuals within complex systems which may contain millions of individual vehicles in the case of national-scale simulations. Microscopic simulations can be implemented using an Agent Based Model (ABM) approach, which has been demonstrated as suitable for parallelisation [20]–[22]. Agent-based simulations of transport networks can potentially involve huge numbers of agents if large, complex road networks are being simulated. As such, microsimulation through an ABM approach potentially exposes the high level of parallelism required to take advance of modern many core processing hardware. However, GPGPU parallelisation is non trivial in a lot of cases, and care must be taken to both ensure that the adoption of parallel algorithms does not fundamentally change the result of simulation. Road network microsimulation software used within industry and in literature predominately leverages multi-core CPUs to improve simulation performance compared to serial implementations. Some research has been published into the application of many-core architectures such as GPUs for road network simulations [23]-[26], however, the adoption of fine-grained data-parallelism and GPUs has been limited, with little impact on the transport modelling sector or widespread adoption within literature thus far.

Macroscopic road network simulations are traditionally used in favour of finer-grained modelling approaches due to the reduced computational cost, provided by the higher level of abstraction. However, large scale macroscopic simulations can still have long run-times, even using state of the art approaches from research adopted by commercial multi-core CPU simulation packages. Time constraints can reduce the effectiveness of simulations and as a result modelling practitioners are restricted in the quantity, variety and therefore scale of simulations which can be completed within a reasonable period of time [14]. The approach to parallelisation within macroscopic road network simulations is less obvious than in the microsimulation case and will require the use of significantly different algorithms and data structures to access high levels of performance from many-core processor architectures, compared to those in use for the current state of the art macroscopic road network simulations for CPUs.

The choice of modelling approach used by practitioners is a compromise which is heavily influenced by the performance of simulations. Although GPUs are potentially suitable for parallelising both modelling approaches, the different approaches may see different levels of performance improvement compared to the current multi-core CPU implementations used within the transport modelling industry. This may influence the decision making process when modelling practitioners must decide which approach is the most suitable for use, providing the desired level of detail while also completing within a reasonable time-frame.

The research questions asked by this thesis are as follows:

- Can modern GPUs be used to provide efficient and scalable microscopic road network simulations which offer high levels of performance compared to more traditional CPUbased approaches?

- What are the essential models required for a road network simulation which can be used to evaluate the performance of microscopic simulations?

- How can simulator performance be evaluated for a range of simulation scales?

- What algorithms and data structures can be used to enable the desired levels of performance and scalability?

- Are modern GPUs suitable for the acceleration of macroscopic road network simulations, to reduce the time required to simulate large-scale road networks?

- Which parts of an Macroscopic model will benefit the most from many-core parallelisation?

- What algorithms and data structures must be used within a macroscopic model to access the high levels of performance offered by the GPU?

- What is the impact of GPUs on the choice of modelling approach, which currently favours high level macroscopic modelling approaches rather than fine-grained microscopic models due to computational cost and long application runtimes?

## 1.2 Contribution to Knowledge

This thesis makes the following contributions:

- C1 A minimal subset of agent-based road network simulation behaviours is defined for a microscopic road network model, with an associated scalable artificial benchmark road network which supports the evaluation of road network simulation performance at a range of simulation scales.

- C2 A general-purpose graph-based communication strategy is presented for high performance agent communication for fine-grained data-parallel agent based simulations, which enables high performance agent based simulations of transport networks on GPUs.

- C3 A benchmark ABM is proposed and used to evaluate the performance impact of the general-purpose graph-based communication strategy for GPU accelerated ABMs, without other complexities of road network simulation.

- C4 The proposed microscopic road network simulation model is implemented for execution on GPUs, and the performance is evaluated against an equivalent model in a commercial multi-core CPU software tool, demonstrating improvements to simulation performance and performance scalability.

- C5 A novel algorithm (Many Source Shortest Path (MSSP)) is presented for concurrently finding the shortest path between multiple origin and destination vertices within a transport network. The algorithm is able to extend the current state of the art in path finding within sparse transport networks by solving a number of shortest path calculations concurrently when using data parallel accelerators such as GPUs.

- C6 The proposed many-source-shortest-path algorithm (C5) is embedded within a macroscopic road network simulation tool, SATURN, to evaluate the impact of such an approach on macroscopic road network assignment and simulation models. Performance advances are demonstrated compared to the existing multi-core implementation, for large-scale real-world road networks.

- C7 The relative impact of GPU acceleration on microscopic and macroscopic road network simulations is compared and evaluated through the shared benchmarking model.

## 1.3 Publications

The work carried out during the completion of this thesis has resulted in the following publications:

- P. Heywood, S. Maddock, R. Bradley, D. Swain, I. Wright, M. Mawson, G. Fletcher, R. Guichard, R. Himlin, and P. Richmond, "A data-parallel many-source shortest-path algorithm to accelerate macroscopic transport network assignment", Transportation Research Part C: Emerging Technologies, 2019 [27]. This publication is related to Contributions C5 and C6.

- P. Heywood, S. Maddock, J. Casas, D. Garcia, M. Brackstone, and P. Richmond, "Dataparallel agent-based microscopic road network simulation using graphics processing units", Simulation Modelling Practice and Theory, 2017 [28]. This provides the basis of Contributions C1, C2, C3 and C4.

- P. Heywood, P. Richmond, and S. Maddock, "Road network simulation using FLAME GPU", Euro-Par 2015: Parallel Processing Workshops, Springer, 2015 [29]. This publication contains early work related to Contributions C1 and C3.

## 1.4 Thesis Structure

- Chapter 2 (Related Work) presents general background information related to road network simulation and the use of computer parallelism including GPGPU, with a more focussed review of microscopic and macroscopic road network simulations.

- Chapter 3 (GPU Accelerated Microscopic Simulation) describes the application of GPUs to microscopic road network simulations through ABM, by defining a set of models and associated scalable road network. The method by which the GPU ABM can be implemented is described, and a performance evaluation made against a state of the art, commercial microsimulation software tool.

- Chapter 4 (Network-Based Communication for Data-Parallel ABM) extends and improves the performance of the GPU accelerated ABM described in Chapter 3 through the use of a specialised communication pattern. The general purpose graph-based communication pattern for GPU accelerated ABMs improves the communication-efficiency of road network behavioural models within agent based models on many-core processors, leading to significant performance improvements and scaling behaviour. This is complemented by an abstract ABM model designed to benchmark the communication patterns presented in road network behavioural models.