#### UNIVERSITÀ DEGLI STUDI DI PADOVA Facoltà di Ingegneria

Corso di Laurea Magistrale in INGEGNERIA ELETTRONICA Indirizzo MICROELETTRONICA

## A 24GHz Synchronized Super-regenerative receiver in 65nm CMOS

Tesi di

Fabio Gini

Relatore Prof. Andrea Bevilacqua

Candidato Ing. Fabio Gini

> Sessione di Laurea Ottobre 2010 Anno Accademico 2009/2010

A nonna Maria, e alla mia famiglia.

"A ogni passo del suo cammino Siddharta imparava qualcosa di nuovo, poichè il mondo era trasformato e il suo cuore ammaliato. Vedeva il sole sorgere sopra i monti boscosi e tramontare oltre le lontane spiagge popolate di palme. Di notte vedeva ordinarsi in cielo le stelle, e la falce della luna galleggiare come una nave nell'azzurro. Vedeva alberi, stelle, animali, nuvole, arcobaleni, rocce, erbe, fiori, ruscelli e fiumi; vedeva la rugiada luccicare nei cespugli al mattino, alti monti azzurri e diafani nella lontananza; gli uccelli cantavano e le api ronzavano, il vento vibrava argentino nelle risaie. Tutto questo era sempre esistito nei suoi mille aspetti variopinti, sempre erano sorti il sole e la luna, sempre avevano scrosciato i torrenti e ronzato le api, ma nel passato tutto ciò non era stato per Siddharta che un veleno effimero e menzognero calato davanti ai suoi occhi, considerato con diffidenza e destinato a essere trapassato e dissolto dal pensiero, poichè non era realtà: la realtà era al di la delle cose visibili. [...] Bello e piacevole andar così per il mondo e sentirsi così bambino, così risvegliato, così aperto all'immediatezza delle cose, così fiducioso. [...]"

Hermann Hesse, Siddharta

#### Sommario

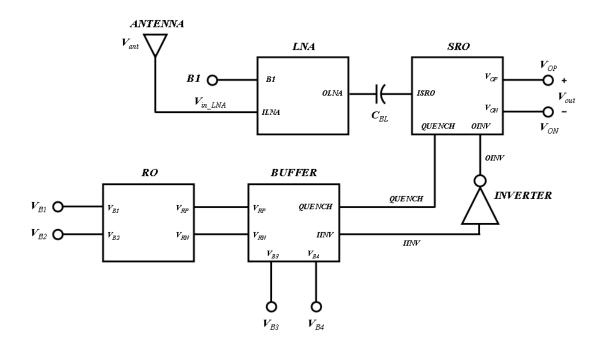

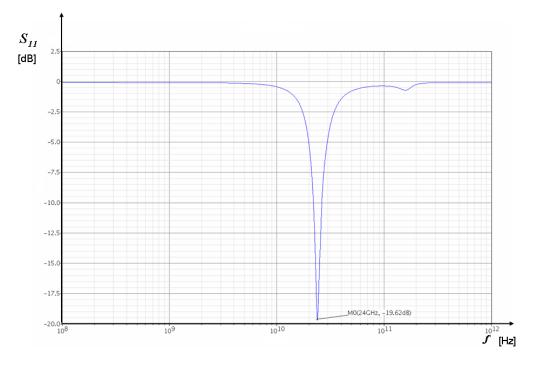

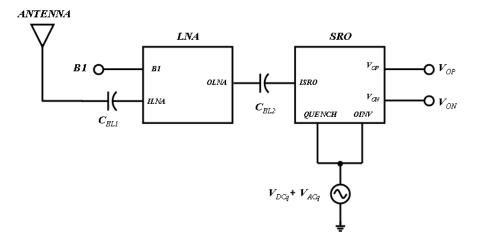

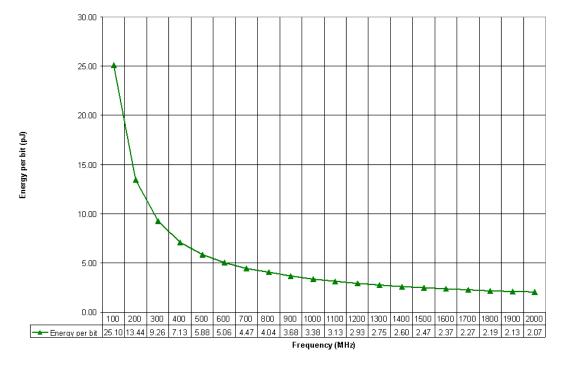

Questo lavoro presenta il progetto di un ricevitore super-rigenerativo sincronizzato, sviluppato in tecnologia CMOS 65 nm. Il ricevitore adotta una frequenza operativa di 24 GHz ed è progettato per raggiungere una velocità massima di 2 Gbps, a partire da un minimo di 100 Mbps. La tecnica super-rigenerativa viene impiegata per realizzare un ricevitore a bassa potenza, da utilizzare nella comunicazione a breve distanza (1 - 10 m), e la simulazione dimostra che, lavorando ad 1 Gbps, il ricevitore manifesta un rendimento energetico di 3.38 pJ/bit. Il diagramma a blocchi del circuito presenta tre blocchi principali: l'LNA (Low-Noise Amplifier), collegato all'antenna, che garantisce un S<sub>11</sub> di -19.62 dB a 24 GHz; l'oscillatore super-rigenerativo (SRO), che è il cuore del circuito; e l'oscillatore ad anello che viene utilizzato per generare il segnale di quench che deve pilotare l'SRO. Teoria, metodi di progettazione e risultati ottenuti sono ampliamente illustrati all'interno della Tesi.

#### Abstract

This work presents the design of a synchronized super-regenerative receiver developed in 65 nm CMOS technology. The receiver is working with an operating frequency of 24 GHz and it is projected to achieve a maximum data bit rate of 2 Gbps, starting from a minimum of 100 Mbps. The super-regenerative technique is used to realize a low power receiver for short-range distance (1-10 m), and the simulation shows that working at 1 Gbps the receiver has an energy efficiency of 3.38 pJ/bit. The block diagram of the circuit presents three main blocks: the LNA (Low-Noise Amplifier), connected to the antenna, which guarantees an  $S_{11}$  of -19.62 dB at 24 GHz; the Super-Regenerative Oscillator (SRO), which is the heart of the circuit; and the Ring Oscillator which is used to generate the quench signal that has to drive the SRO. Theory, design methods and final results are fully explained inside the Thesis.

## Contents

| 1        | Intr | roducti                    | ion                                                                                             | 1         |  |  |

|----------|------|----------------------------|-------------------------------------------------------------------------------------------------|-----------|--|--|

|          | 1.1  | Short-range wireless links |                                                                                                 |           |  |  |

|          | 1.2  | IBM1                       | DLP 65 nm CMOS Technology                                                                       | 4         |  |  |

|          |      | 1.2.1                      | MOSFET Small-Signal AC Model                                                                    | 7         |  |  |

|          |      | 1.2.2                      | Device characterization for the IBM10LP technology                                              | 12        |  |  |

| <b>2</b> | The  | eory ar                    | nd System Architecture Design                                                                   | 19        |  |  |

|          | 2.1  | Super-                     | -regenerative receiver (SRR)                                                                    | 19        |  |  |

|          | 2.2  | Low-N                      | Joise Amplifier (LNA)                                                                           | 23        |  |  |

|          |      | 2.2.1                      | Simplified analysis                                                                             | 23        |  |  |

|          |      | 2.2.2                      | Accurate analysis                                                                               | 26        |  |  |

|          | 2.3  | Super-                     | -regenerative oscillator (SRO)                                                                  | 28        |  |  |

|          |      | 2.3.1                      | Super-regenerative Modes                                                                        | 28        |  |  |

|          |      | 2.3.2                      | Analytical Model of the super-regenerative receiver for the Linear Mode $% \mathcal{L}^{(n)}$ . | 29        |  |  |

|          |      | 2.3.3                      | Synchronous Operation of the Receiver                                                           | 37        |  |  |

|          | 2.4  | Curren                     | nt-Reuse CMOS Differential LC-VCO                                                               | 38        |  |  |

|          |      | 2.4.1                      | Simplified Model of the Negative Resistance Oscillator                                          | 41        |  |  |

|          |      | 2.4.2                      | Accurate Model of the Negative Resistance Oscillator $\ldots \ldots \ldots \ldots$              | 44        |  |  |

|          | 2.5  | Tunab                      | ble Differential Ring Oscillator (RO)                                                           | 46        |  |  |

| 3        | Cire | cuit D                     | esign                                                                                           | <b>49</b> |  |  |

|          | 3.1  | Low-N                      | Joise Amplifier (LNA)                                                                           | 52        |  |  |

|          | 3.2  | Super-                     | -regenerative oscillator (SR0)                                                                  | 58        |  |  |

|          |      | 3.2.1                      | Design Methodology                                                                              | 61        |  |  |

|   |                | 3.2.2 Limits of this configuration and how to increase its performance $\ldots$ . | 63 |

|---|----------------|-----------------------------------------------------------------------------------|----|

|   | 3.3            | Ring Oscillator (RO)                                                              | 65 |

|   |                | 3.3.1 Buffer stage                                                                | 67 |

| 4 | $\mathbf{Sim}$ | nulation of the SRR and Discussion                                                | 71 |

|   | 4.1            | Receiver Sensitivity and SNR                                                      | 72 |

|   | 4.2            | Voltage Gain and Energy Efficiency                                                | 76 |

|   | 4.3            | Why synchronization is so important in the SRO                                    | 79 |

|   | 4.4            | Output waveforms of the SRR                                                       | 81 |

| 5 | Cor            | nclusions                                                                         | 85 |

# List of Figures

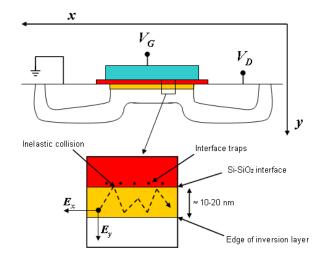

| 1.1  | Motion of an electron under the influence of lateral field $E_y$ and vertical field $E_x$ .             | 5  |

|------|---------------------------------------------------------------------------------------------------------|----|

| 1.2  | $I_D - V_G$ characteristics                                                                             | 6  |

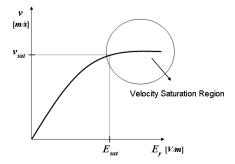

| 1.3  | Electron velocity vs. $E_y$                                                                             | 7  |

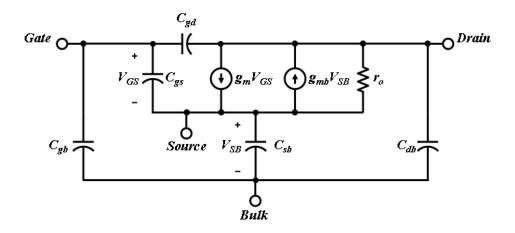

| 1.4  | MOSFET Small-Signal AC Model below $1 \ GHz$ operating frequency                                        | 8  |

| 1.5  | Unity Current Gain Frequency, $f_T$                                                                     | 9  |

| 1.6  | RF Model for MOSFET                                                                                     | 10 |

| 1.7  | MOSFET model in terms of $Y$ -Parameters                                                                | 11 |

| 1.8  | Circuit configuration to extrapolate the figures of merit. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 13 |

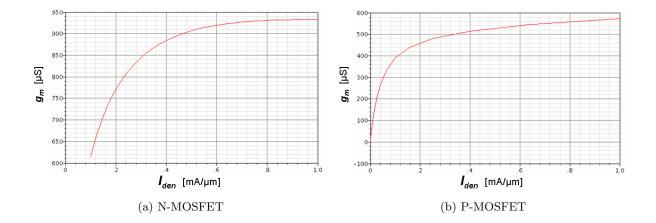

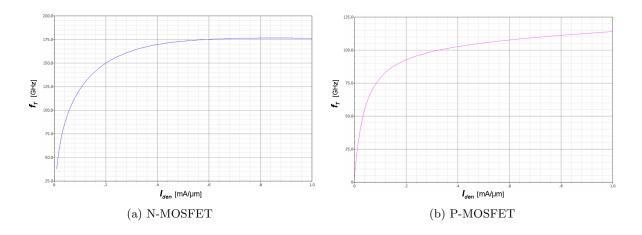

| 1.9  | $g_m$ vs. $I_{den}$                                                                                     | 14 |

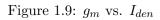

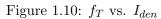

| 1.10 | $f_T$ vs. $I_{den}$                                                                                     | 14 |

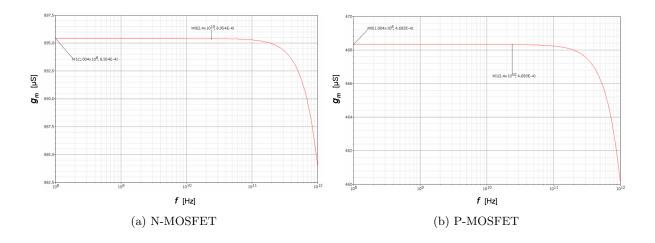

| 1.11 | $g_m$ vs. Frequency, $V_{GS} = V_{DS} = 1V$                                                             | 14 |

| 1.12 | N-MOSFET: a) $I_D$ vs. $V_{GS}$ with $V_{DS} \in [0.5V, 1V]$ step $0.1V$ ; b) $I_D$ vs. $V_{DS}$ with   |    |

|      | $V_{GS} \in [0.5V, 1V]$ step $0.1V.$                                                                    | 15 |

| 1.13 | P-MOSFET: a) $I_D$ vs. $V_{GS}$ with $V_{SD} \in [0.5V, 1V]$ step $0.1V$ ; b) $I_D$ vs. $V_{SD}$ with   |    |

|      | $V_{SG} \in [0.5V, 1V]$ step $0.1V.$                                                                    | 16 |

| 1.14 | $g_m$ vs. $I_{den}$ - zoom in                                                                           | 17 |

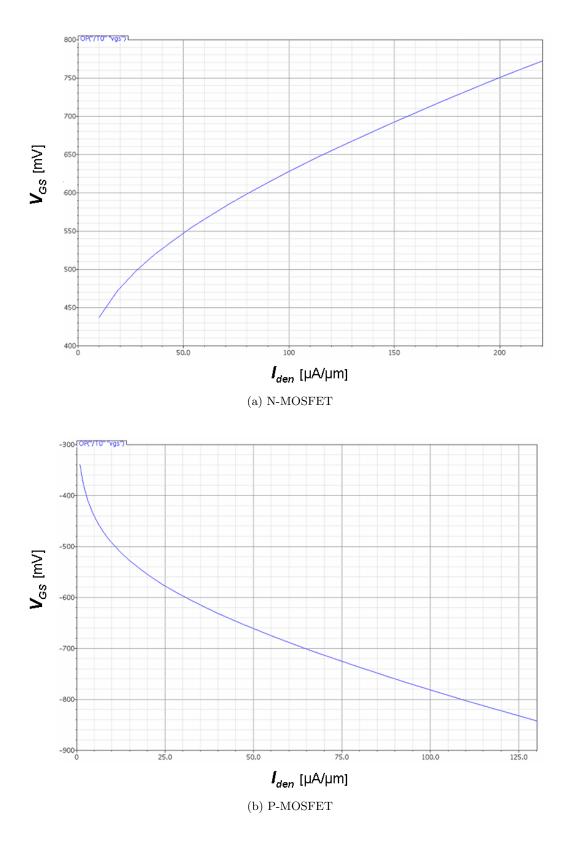

| 1.15 | $V_{gs}$ vs. $I_{den}$                                                                                  | 18 |

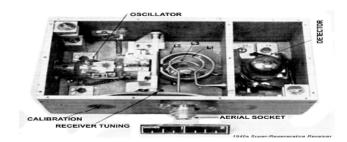

| 2.1  | A 1940's 500-MHz Super-regenerative receiver                                                            | 20 |

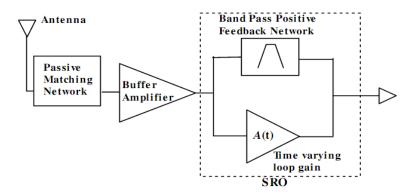

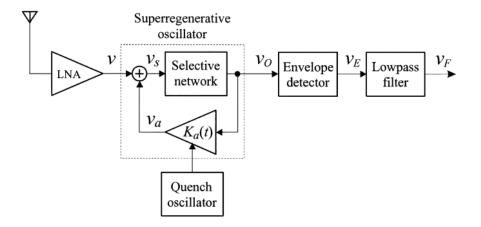

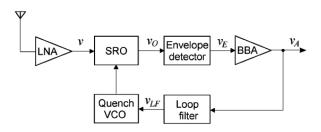

| 2.2  | A typical block diagram of super-regenerative receiver (SRR)                                            | 20 |

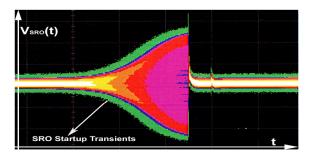

| 2.3  | A typical start-up transient of SRO circuit in presence of thermal noise                                | 21 |

| 2.4  | Detailed block diagram of the SRR                                                                       | 22 |

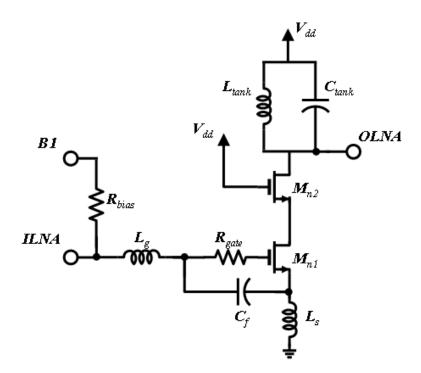

| 2.5  | Complete schematic of the 24-GHz LNA.                                                                   | 23 |

| 2.6  | Narrowband LNA with inductive source degeneration                                                       | 24 |

| 2.7  | Small-signal circuit for noise figure analysis of CS-LNA                                      | 26 |  |  |

|------|-----------------------------------------------------------------------------------------------|----|--|--|

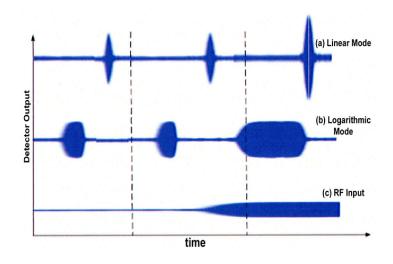

| 2.8  | Super-regenerative Modes                                                                      |    |  |  |

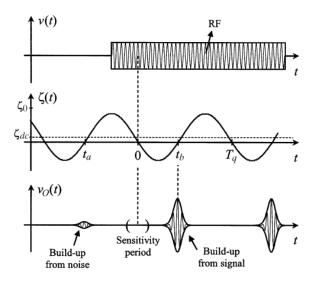

| 2.9  | RF input signal, damping function, and SRO output                                             |    |  |  |

| 2.10 | Damping function $\varsigma(t)$ , sensitive curves $s(t)$ , normalized envelope of the output |    |  |  |

|      | pulse $p(t)$ , and normalize envelope of the input signal $p_c(t)$                            | 31 |  |  |

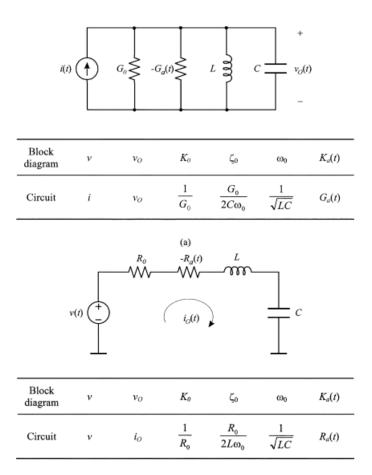

| 2.11 | Parallel and Series RLC circuits.                                                             | 32 |  |  |

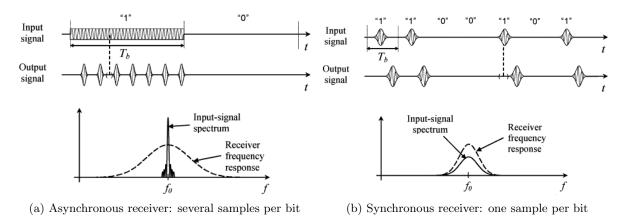

| 2.12 | SRO input and output signals with OOK modulation                                              | 38 |  |  |

| 2.13 | Block diagram of the synchronous super-regenerative receiver                                  | 38 |  |  |

| 2.14 | Normalized envelope of the input bit pulse $p_c(t)$ , shifted sensitivity curve of the        |    |  |  |

|      | SRO $s(t + \delta)$ , and normalized envelope of the SRO output oscillation                   | 39 |  |  |

| 2.15 | Differential LC-VCO: (a) conventional, (b) current-reuse.                                     | 40 |  |  |

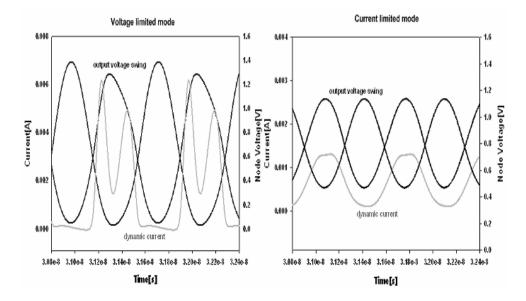

| 2.16 | Proposed VCO operations with $R_s = 0$ during each half period                                | 40 |  |  |

| 2.17 | Differential output voltage and dynamic current waveforms: voltage limited mode               |    |  |  |

|      | $(R_s = 0)$ and current limited mode $(R_s \neq 0)$                                           | 41 |  |  |

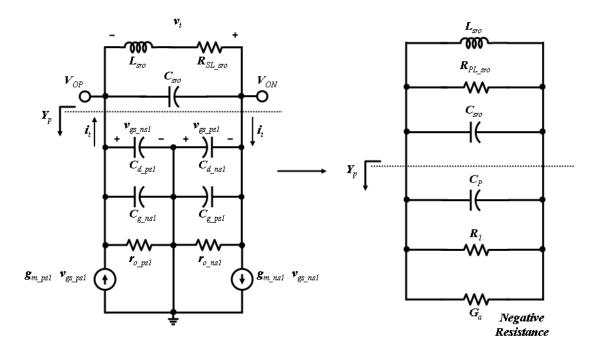

| 2.18 | Super-regenerative oscillator.                                                                | 42 |  |  |

| 2.19 | Total Network representation of the SRO                                                       | 43 |  |  |

| 2.20 | Tunable Differential Ring Oscillator.                                                         | 46 |  |  |

| 2.21 | Buffer Stage of the Differential Ring Oscillator.                                             | 46 |  |  |

| 3.1  | Global Circuit Design.                                                                        | 50 |  |  |

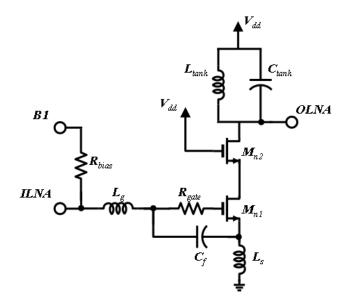

| 3.2  | Low-Noise Amplifier                                                                           | 52 |  |  |

| 3.3  | $S_{11}$ of LNA                                                                               | 56 |  |  |

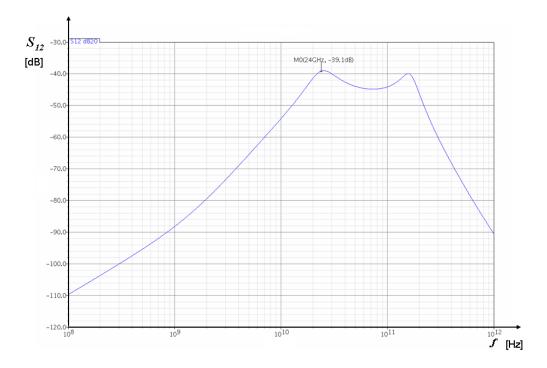

| 3.4  | $S_{12}$ of LNA                                                                               | 56 |  |  |

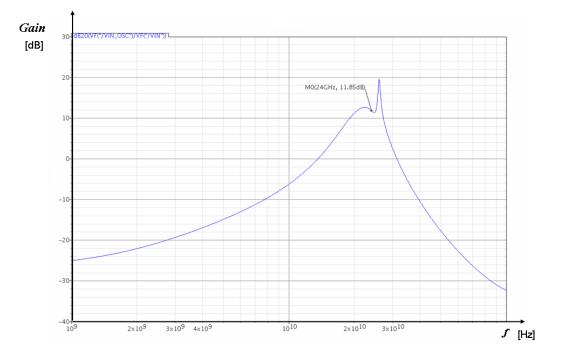

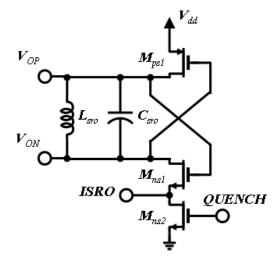

| 3.5  | Voltage Gain of LNA.                                                                          | 57 |  |  |

| 3.6  | Noise Figure of LNA                                                                           | 57 |  |  |

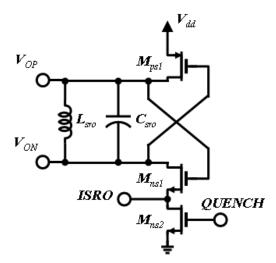

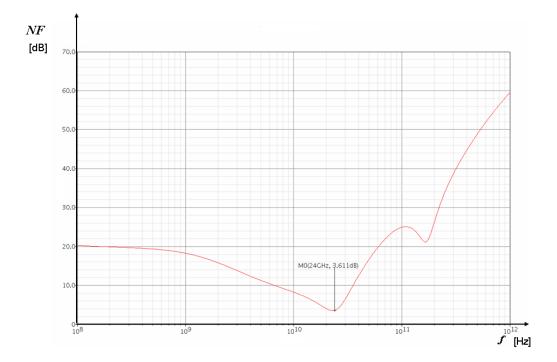

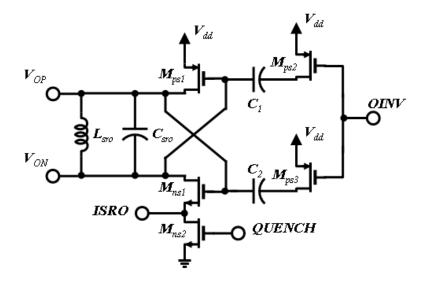

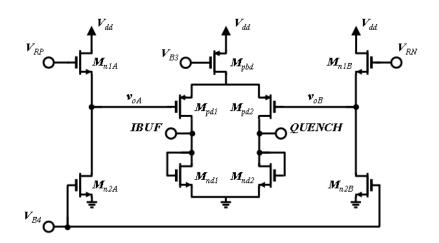

| 3.7  | Final Version of SRO.                                                                         | 58 |  |  |

| 3.8  | First version of the SRO.                                                                     | 59 |  |  |

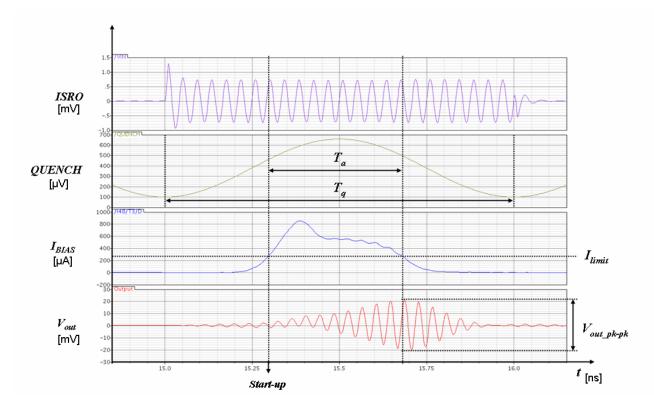

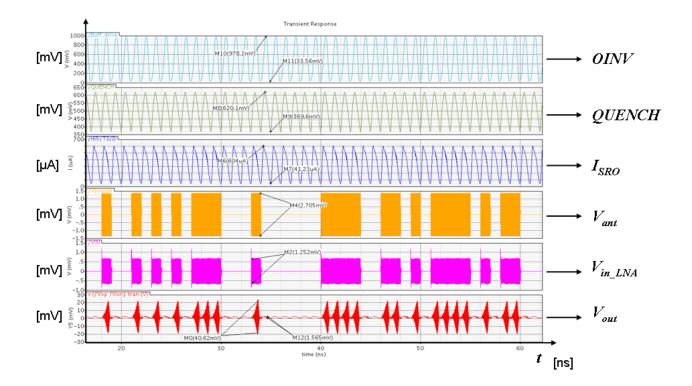

| 3.9  | Example in Cadence simulation with $f_q = 1 \ GHz$ : RF signal <i>ISRO</i> (it represents     |    |  |  |

|      | 1 bit), sinusoidal $QUENCH$ signal, bias current $I_{BIAS}$ , and differential SRO            |    |  |  |

|      | output $V_{out}$                                                                              | 60 |  |  |

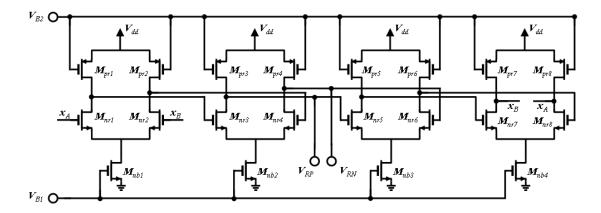

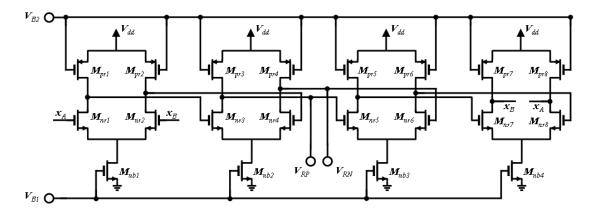

| 3.10 | Ring-Oscillator.                                                                              | 65 |  |  |

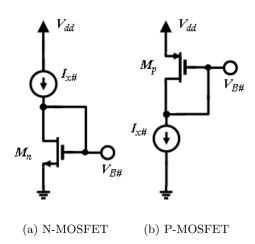

| 3.11 | Current Mirror configuration for N-MOSFET and P-MOSFET, respectively                          | 66 |  |  |

#### LIST OF FIGURES

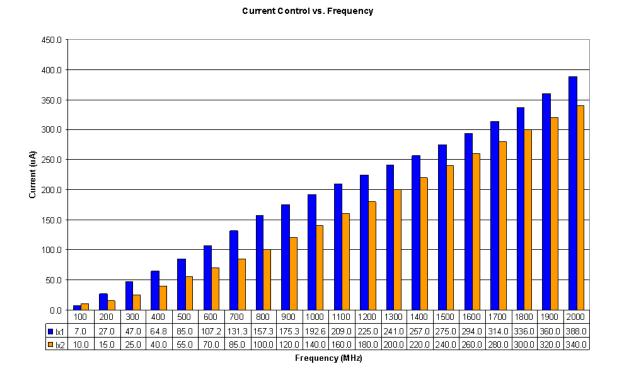

| 3.12 | Current Control in the Ring Oscillator                                              | 66 |

|------|-------------------------------------------------------------------------------------|----|

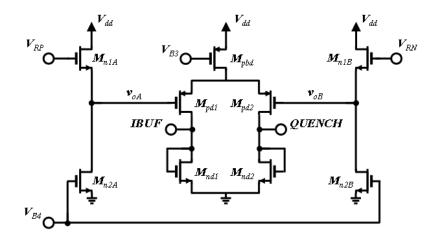

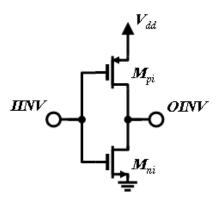

| 3.13 | RO Buffer.                                                                          | 68 |

| 3.14 | Inverter                                                                            | 68 |

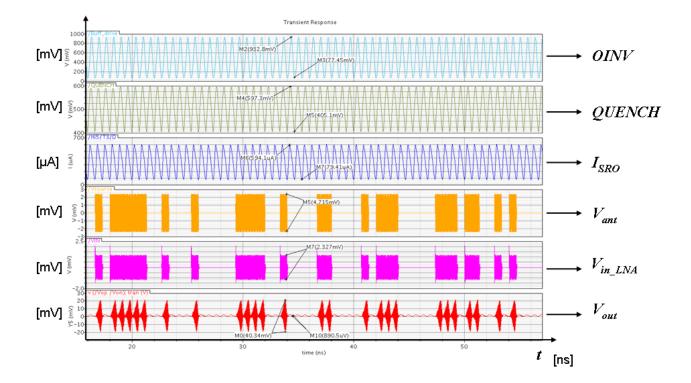

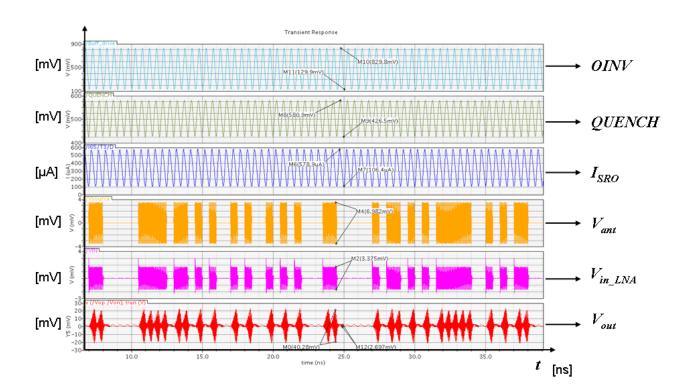

| 4.1  | Waveforms of the Final SRR at $1 GHz$                                               | 71 |

| 4.2  | Ideal circuit without Ring Oscillator                                               | 72 |

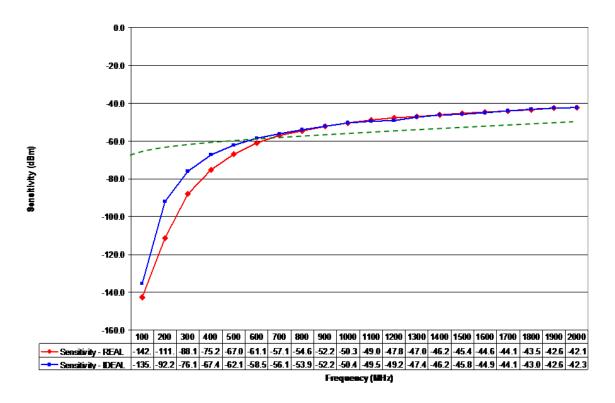

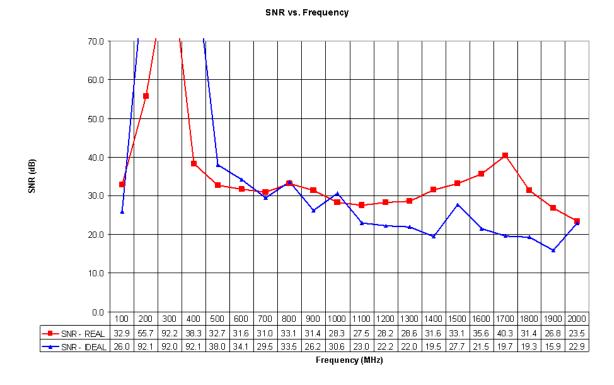

| 4.3  | Sensitivity vs. Frequency.                                                          | 74 |

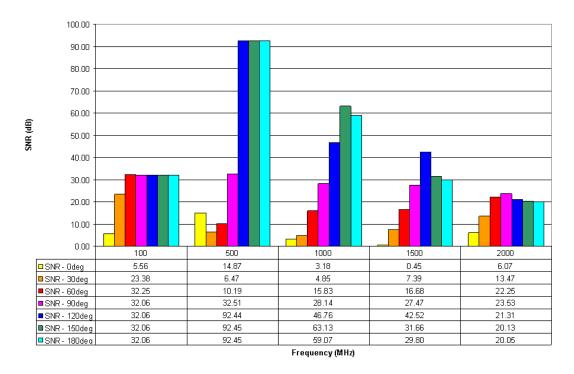

| 4.4  | $SNR_{out}$ vs. Frequency                                                           | 75 |

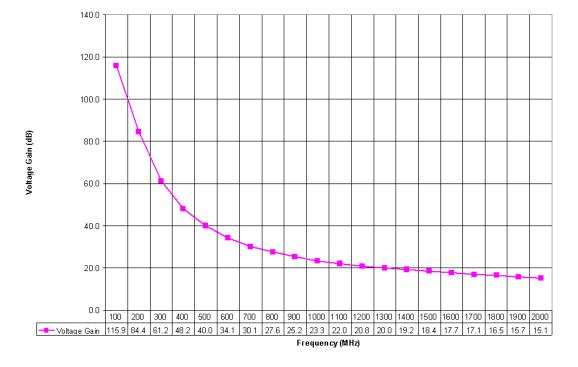

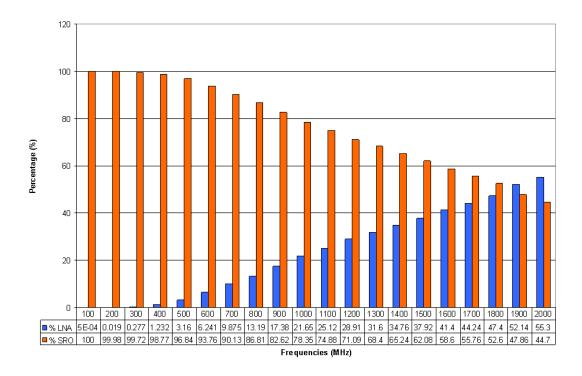

| 4.5  | Voltage Gain vs. Frequency                                                          | 77 |

| 4.6  | Percentage of Voltage Gain coming from the SRO and LNA vs. Frequency. $\ . \ . \ .$ | 77 |

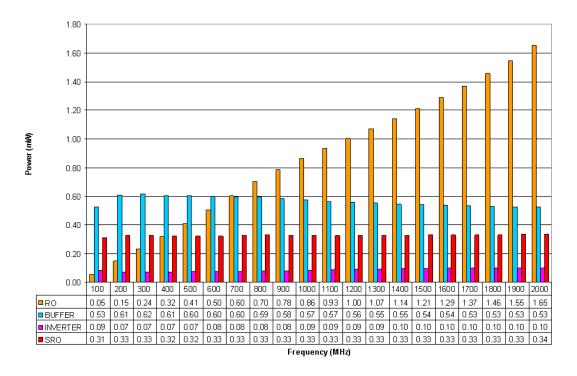

| 4.7  | Power of each block vs. Frequency                                                   | 78 |

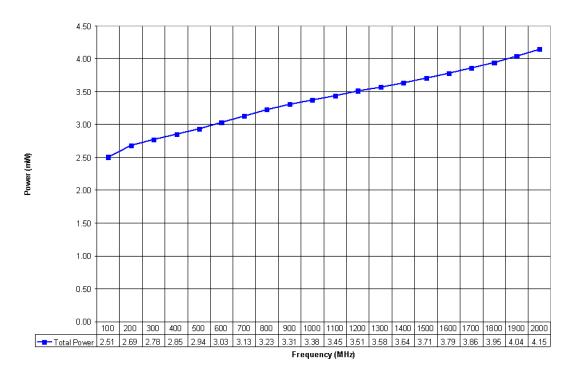

| 4.8  | Total Power vs. Frequency.                                                          | 78 |

| 4.9  | $E_{bit}$ vs. Frequency                                                             | 79 |

| 4.10 | Synchronization of the QUENCH                                                       | 79 |

| 4.11 | How change the SNR synchronizing the quench signal in different ways                | 80 |

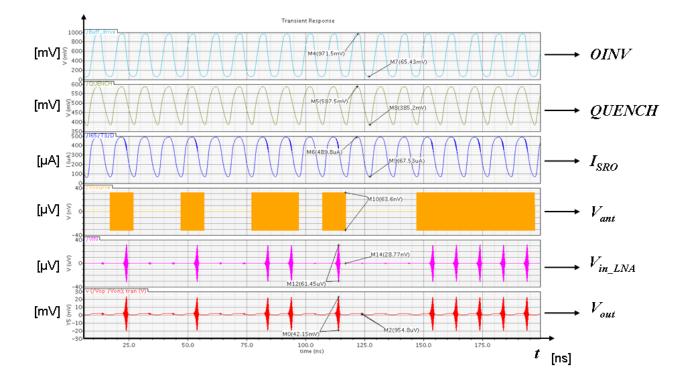

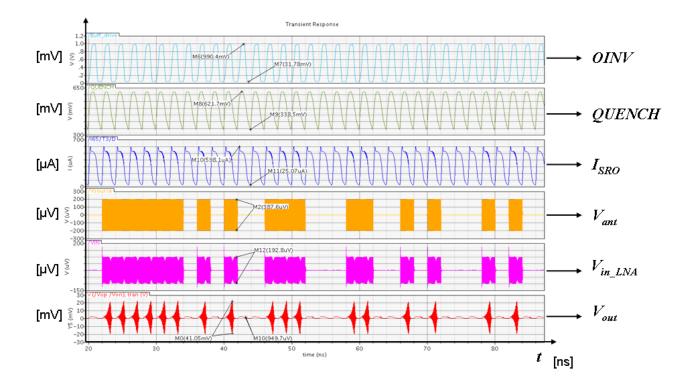

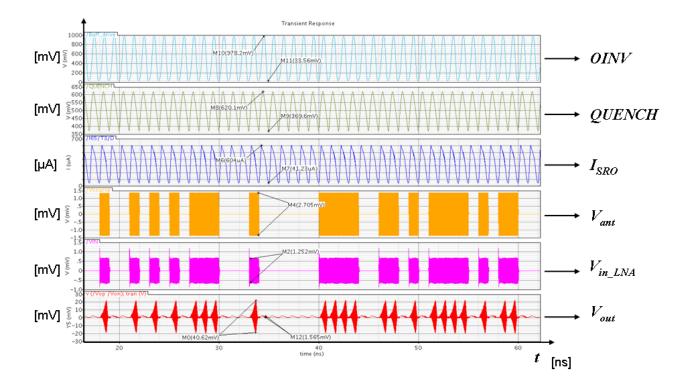

| 4.12 | Output waveforms of the SRR at 100 $MHz$                                            | 82 |

| 4.13 | Output waveforms of the SRR at 500 $MHz$                                            | 82 |

| 4.14 | Output waveforms of the SRR at $1 GHz$                                              | 83 |

| 4.15 | Output waveforms of the SRR at 1.5 $GHz$                                            | 83 |

| 4.16 | Output waveforms of the SRR at $2 GHz$                                              | 84 |

v

## List of Tables

| 1.1 | Circuit Parameters for MOSFET in terms of Y-Parameters                                                         | 11 |

|-----|----------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Circuit Parameters to include in Fig.1.7 for IBM10LP technology, at 24 $GHz~$                                  | 13 |

| 3.1 | Blocking Capacitors                                                                                            | 50 |

| 3.2 | Active devices (LNA)                                                                                           | 52 |

| 3.3 | Passive Components (LNA)                                                                                       | 52 |

| 3.4 | Active devices (SRO) $\ldots$ | 58 |

| 3.5 | Passive Components (SRO)                                                                                       | 58 |

| 3.6 | $M_{ns1}$ and $M_{ps1}$ in the SRO                                                                             | 62 |

| 3.7 | Active devices (RO)                                                                                            | 65 |

| 3.8 | Active devices (RO Buffer)                                                                                     | 68 |

| 3.9 | Active devices (Inverter)                                                                                      | 68 |

|     |                                                                                                                |    |

### Chapter 1

### Introduction

At the beginning of April 2010, during my Education Abroad Program at the University of Santa Barbara, in California, I started to work on my Master Thesis under the supervision of Prof. Patrick Yue, of the ECE Department. During my Master in Electrical Engineering I got really interested about RF design. The first class that I took it was in Italy, at my own University of Padova, with my official supervisor for this Master Thesis, Prof. Andrea Bevilacqua. The class was called Analog-Integrated Circuit Design. Then, during my experience in the United States, I had the possibility to follow two classes in Communication Electronics, and in one of these I met Prof. Yue, who became my American supervisor for this Master Thesis. He proposed to me to work on a particular kind of receiver, using the super-regenerative technique. We are talking about a receiver which is designed to work in the short-range wireless area (1 - 10 m). The super-regenerative technique is a really nice method to increase the data bit rate, that is the number of bits received per second, still maintaining a really low power consumption. Prof. Yue, in particular, gives to me the possibility to work on it using the IBM10LP technology, which employs the 65 nm CMOS process, working in the 24 GHzfrequency band. There was a belief that it would have been possible to realize a receiver capable to work at 1 Gbps, and dissipating less than 10 pJ per bit (the energy per bit is a fundamental concept in the Communication area). Before me, already another student, Kung-Hao Liang, in collaboration with Luis Chein, had worked on this project [16]. They used the 60 GHz frequency band, but the best obtained performance was around 200 Mbps, with an energy of 50 pJ/bit. Thus, for my work, I started considering their circuit configuration, adding then some changes. And, just to have a little anticipation in the introduction about my results, after five month of 2

work I was able to project a synchronized super-regenerative receiver with a maximum working frequency of 2 Gbps; and perfectly in agreement with the initial expectations, working at 1 Gbps, my circuit was dissipating just 3.4 pJ/bit.

The Thesis has been organized in this way:

- the introduction is dedicated to the description of possible marketing areas for this kind of receiver, and to focus the attention on some fundamental problems that are coming out using a short-channel device which works at really high frequency;

- in the second chapter I spent time to describe the theory that is important to read to comprehend:

- what is the super-regenerative technique;

- what is the difference between asynchronous and synchronous operating mode;

- what are the different boxes which form the block diagram of the receiver and how they work.

- in the third chapter I illustrated how, each block of the circuit, has been projected starting from the theory;

- in the forth chapter I wrote down the results I got, and in particular I tried to focus the attention on the main problems that I found building my circuit;

- in the last chapter there is the conclusion.

#### 1.1 Short-range wireless links

The kind of receiver that will be presented in this Master Thesis it is a low power receiver for short-range distance (1 - 10 m) which works in the 24 GHz frequency band. It has an energy efficiency of 3.38 pJ/bit, working with a bit-rate of 1 Gbps. It is a receiver able to capture and amplify a really fast AM (Amplitude-Modulated) signal that is coming from a pretty near source, that could be installed inside the same room or, if we talk about body area networks, on the human body. In these applications, where there is usually a device which is supplied by a battery, it is fundamental to dissipate a little power, increasing the battery lifetime.

For the marketing area, some important new application fields need to be cited, for example: WiGig short-range WiFi, wireless HDMI and, in the medical field, Wireless Body Area Network. [1][2][3]

In the WiGig area there are two associations that are working on the project: Wireless Gigabit Alliance and Wi-Fi Alliance; and there will be probably necessary at least a couple of years to have this technology available. WiGig will be able to become the new standard for the Wi-Fi connections, transferring data with a bit-rate in a range between 1 *Gbps* until a maximum of 7 *Gbps*. This means that it will be possible to transfer an high definition video in streaming from a computer to a television without HDMI cable. To make it possible, this two associations are working in a new transmission band of 60 *GHz*. Nowaday the typical Wi-Fi speed is around 150 *Mbps* using the standard 802.11*n*, so it means that with WiGig it will be possible to transmit the same data more than 6 times faster. The major companies that are working in this project are: Broadcom, Cisco, Dell, Intel, Microsoft, NEC, Nvidia, Nokia e Samsung.

Wireless HDMI (High Definition Multimedia Interface) technology is instead available since 2003. HDMI is a digital audio and video interface that is capable to transmit uncompressed streaming data. The wired counterpart connects two digital video and audio components, like DVD player and a High Definition television. Wireless HDMI is just the same thing but without wire. The transmitter is a little black box, the size of a laptop that will likely get smaller as the technology improves. Data are sent from the transmitter through the airwaves to the receiver where the video and audio are decompressed and then sent through the HDMI port to the displaying device. Wireless HDMI transmits data at 3 *Gbps*. The transmitter compresses data with an impression compression standard base on JPEG algorithm technology, which is used for compressing images for a wide variety of uses from medical images to personal pictures. The receiver and transmitter in the wireless HDMI system will not need a straight line of sight. In fact, they can be in different floors or different rooms and still capable of beaming data to each other. Both devices typically must be within 5 m. An UWB adapter can be used to widen that distance up to 31 m.

Finally, another important application for this kind or receiver could be the Wireless Body Area Network (WBAN). This is the application of wearable computing devices. A wireless communication between several miniaturized Body Sensor Units (BSU) and a single Body Central Unit (BCU) worn at the human body. The Body Area Network field is an interdisciplinary area which could allow inexpensive and continuous health monitoring with real-time updates of medical records via Internet. Implanting very small bio-sensors inside the human body in order to monitor the patients' health status no matter their location. Information are transmitted wirelessly to an external processing unit and this device will instantly transmit all information in real time to the doctors throughout the world. If an emergency is detected, the physicians will immediately inform the patient through the computer system by sending appropriate messages or alarms. The main applications of BANs are expected to appear primarily in the healthcare domain, especially for continuous monitoring and logging vital parameters of patients suffering from chronic diseases such as diabetes, asthma and heart attacks.

#### 1.2 IBM10LP 65 nm CMOS Technology

The technology that has been used to design the super-regenerative receiver is the IBM10LP 65 nm technology.

When a new technology has to be studied for the first time, you do not have a lot of information about its technological parameters, so, the first thing to do is to plot the figures of merit of the CMOS devices, which can give many useful information about the characterization of their performance. Usually, power consumption and band of an amplifier are the two most important items to take in account. Talking about CMOS devices that dissipate a little power and work at high speed, it is always related to the density current which is biasing them. The density current depends by the size of the device (and when the length L is constant, the width W becomes the parameter we need to consider) and by the bias current that is flowing through it. Because of the main task of a CMOS device is to amplify a signal, also what is its maximum transit frequency becomes fundamental.  $f_T$ , is the maximum operating frequency where the device can still amplify in current, and it is extrapolated putting the load shorted and finding the value of frequency where the current gain is one. Working at higher frequencies, in fact, the parasitic elements of the device, and in particular  $C_{gs}$  and  $C_{gd}$ , become relevant; their impedance goes down and this fact kills the gain of the transistor.

For the huge amount of problems that are coming out working at high frequency (24 GHz), and using device with a really short channel (65 nm), it is fundamental to write down a brief description of the equations which try to described these phenomena.

Two phenomena play a key role in the short-channel devices: mobility degradation and velocity saturation [4]. Fig.1.1 represents the motion of an electron inside the channel of a

transistor.

Figure 1.1: Motion of an electron under the influence of lateral field  $E_y$  and vertical field  $E_x$ .

#### Mobility Degradation

This effect affects also long-channel transistors, but it is a more serious limitation for shortchannel devices. It is related to the x-directed gate oxide fields (the electric field that is orthogonal to the gate,  $E_x$ ) which is higher in short-channel transistors because the power-supply voltage is not scaled as much as suggested by constant-field scaling when the gate-oxide thickness is reduced. The drain current in a MOSFET is carried by a mobile-charge density  $Q_n$  that is moving in a region near the surface under the influence of varying fields. The electrons are scattered by collision with the interface as well as with charged acceptor sites and thermal phonons. It is impossible to write down an exact theory to describe this phenomenon but some approximations have been done and the empirical equation that can represent the mobility degradation for the mosfet is

$$\mu_{eff} = \frac{\mu_0}{1 + (E_{eff}/E_0)^v} \tag{1.1}$$

where  $\mu_0$ ,  $E_0$ , and v are all fitting parameters.  $E_{eff}$  is, instead, the average x-directed field experienced by all the mobile carriers at the MOS surface. In Fig.1.2 there is the drain-current,  $I_D$ , due to the mobility degradation. The dotted line represents the ideal evolution of the current increasing  $V_G$ , while the thick line is the real one.

Figure 1.2:  $I_D - V_G$  characteristics.

#### **Velocity Saturation**

This phenomenon is related to the applied field in the direction of carrier drift (the y-direction for the MOSFET channel,  $E_y$ ). When high fields are applied, carrier velocities approach a limiting value. At lower fields, the velocity is fit by an equation of the form

$$v = \frac{\mu_{eff}E}{1 + E/E_{sat}} \qquad \qquad E < E_{sat} \tag{1.2}$$

while for fields greater than the saturation field  $E_{sat}$ , the velocity becomes constant

$$v = v_{sat} E > E_{sat} (1.3)$$

The parameter  $E_{sat}$  is determined by solving for the field at which  $v = v_{sat}$  and it becomes

$$E_{sat} = \frac{2v_{sat}}{\mu_{eff}} \tag{1.4}$$

E represents the y-direction field and and it can be also written as

$$E = \frac{V_{DS}}{L} = \frac{V_{GS} - V_T}{L} \tag{1.5}$$

So, taking  $\theta = 1/(E_{sat}L)$  for the velocity (1.2) there is the following equation:

$$v = \frac{\mu_{eff} \frac{V_{DS}}{L}}{1 + \theta V_{DS}} \tag{1.6}$$

And using this kind of equation inside the common equation of the drain current of a MOSFET, in velocity saturation conditions,  $I_D$  can be written as:

$$I_D = \frac{\mu_{eff}C_{ox}}{2} \frac{\frac{V_{GS} - V_T}{L}}{1 + \theta(V_{GS} - V_T)} W(V_{GS} - V_T) = \frac{\mu_{eff}C_{ox}}{2} \frac{1}{1 + \theta(V_{GS} - V_T)} \frac{W}{L} (V_{GS} - V_T)^2$$

(1.7)

And for the short-channel, where

$$\frac{V_{GS} - V_T}{L} \gg 1 \tag{1.8}$$

$I_D$  becomes, using eq.(1.4) and (1.7)

$$I_D = \frac{\mu_{eff} C_{ox} W}{2} (V_{GS} - V_T) E_{sat} = C_{ox} W (V_{GS} - V_T) v_{sat}$$

(1.9)

In velocity saturation, the output current is

- independent of L

- a linear function of  $(V_{GS} V_T)$

In silicon, typical values for the velocity saturation are:

$$\mu_{eff} \sim 0.07 \frac{m^2}{Vs} \qquad E_{sat} \sim 10^6 \frac{V}{m} \qquad v_{sat} \sim 10^5 \frac{m}{s}$$

(1.10)

Fig.1.3 illustrates how the velocity saturates increasing the  $E_y$ .

Figure 1.3: Electron velocity vs.  $E_y$ .

#### 1.2.1 MOSFET Small-Signal AC Model

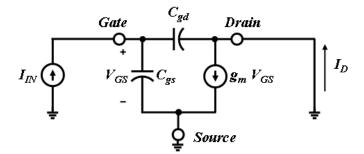

[5] To understand how complex a small-signal AC model for a MOSFET becomes, the operating frequency as to be increased, take a look to Fig.1.4. This model can be considered valid

for frequencies that are below 1 GHz; at 24 GHz the model should be even more complex. Comparing with the simplest small-signal AC model, where  $C_{gs}$  is the only considered parasitic capacitance, here there are many others that are playing an important role in the transistors performance, in particular:  $C_{gd}$ ,  $C_{sb}$ ,  $C_{gb}$ , and  $C_{db}$ . The last two, it is easy to see, can turn off the

Figure 1.4: MOSFET Small-Signal AC Model below 1 GHz operating frequency.

transistor, taken the gate-voltage and the drain-voltage to zero.  $C_{sb}$ , instead, is responsible for the body effect. When  $V_{SB} > 0$  the threshold voltage of the device increases and for the same applied  $V_{GS}$ , the transconductance  $g_m$  gets smaller. This fact is represented adding another transconductance  $g_{mb}$  which is opposite to  $g_m$ .  $C_{gd}$ , at the end, at high frequency, generates a feedback between the output and the input of the transistor. Because of the Miller effect, it can be represented in parallel with  $C_{gs}$  with a value equal to  $C_{gd}(1 - A_v)$ , where  $A_v$  in the inverting voltage gain of the transistor. Thus, it becomes responsible, at high frequency, of the increasing of the input capacitance of the transistor. Using the simplified model in Fig.1.5, we obtain for  $f_T$  the following expression:

$$f_T = \frac{g_m}{2\pi(C_{gs} + C_{gd})} \qquad when \qquad \left|\frac{I_D}{I_{IN}}\right| = 1 \tag{1.11}$$

Starting from eq.(1.9), we know that the transconductance  $g_m$  can be calculated as

$$g_m = \frac{dI_D}{dV_{DS}} = WC_{ox}v_{sat} \tag{1.12}$$

Thus, using eq.(1.4) and (1.11) the transit frequency  $f_T$ , can be rewritten as

Figure 1.5: Unity Current Gain Frequency,  $f_T$ .

$$f_T = \frac{g_m}{2\pi (C_{gs} + C_{gd})} \approx \frac{g_m}{2\pi C_{gs}} = \frac{WC_{ox}v_{sat}}{(2\pi)\left(\frac{2}{3}WLC_{ox}\right)} = \frac{1}{2\pi}\frac{3}{2}\frac{v_{sat}}{L} = \frac{1}{2\pi}\frac{3}{4}\frac{E_{sat}}{L}$$

(1.13)

Another important parameter to consider is  $f_{max}$  that, in presence of input and output matching for the device, represents the frequency at which the maximum power transfer,  $G_{max}$ , is equal to one. It can be shown in eq.(1.14) that:

$$|G_{max}| = 1 \longrightarrow f_{max} \approx \sqrt{\frac{f_T}{8\pi R_{gate}C_{gd}}}$$

(1.14)

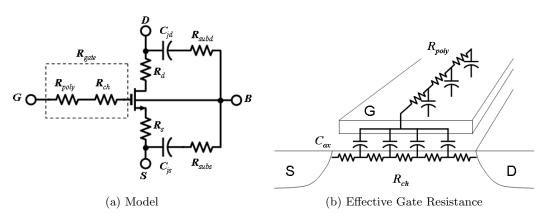

An important element appears inside eq.(1.14), the gate resistance  $R_{gate}$ . At low frequency it does not matter, because  $C_{gs}$  represents an open-circuit; but working in the RF design, where the parasitic capacitances start to have a fundamental role, also the parasitic resistances come out and have to be considered in the model. Thus, the RF model for the MOSFET becomes the one that is shown in Fig.1.6a.  $R_{gate}$  represents the effective gate resistance, and it can be split into two other parasitic resistances,  $R_{poly}$  and  $R_{ch}$ .

$$R_{gate} = R_{poly} + R_{ch} \tag{1.15}$$

Fig.1.6b shows where these two parasitic resistances come from.  $R_{poly}$  is the distributed gate electrode resistance and it can be estimated as

$$R_{poly} = \frac{1}{3}\rho_{poly}\frac{W}{n^2L} \tag{1.16}$$

where  $\rho_{poly}$  is the resistivity of the gate electrode, W and L the dimensions of the device, and n the number of fingers.  $R_{ch}$ , instead, is the channel induced gate resistance, and it can be

Figure 1.6: RF Model for MOSFET

calculated as

$$R_{ch} = \frac{1}{\delta} \left( \frac{V_{Dsat}}{I_{DS}} \parallel \frac{qL}{kT\mu_{eff}WC_{ox}} \right)$$

(1.17)

where  $\delta$  is a fitting parameter which takes in account for distributed effects and it swings between 12 and 15.  $V_{Dsat}$  is the drain saturation voltage and it is related to  $E_{sat}$  in the following way

$$V_{Dsat} = \frac{E_{sat}L(V_{GS} - V_T)}{E_{sat}L + (V_{GS} - V_T)}$$

(1.18)

and it converges to  $(V_{GS} - V_T)$  when  $E_{sat}$  becomes very large. q is the charge,  $1.602 \times 10^{-19} C$ ; k is the Boltzmann's constant,  $1.38 \times 10^{-23} J/K$ , and T is the temperature in Kelvin.

$R_s$  and  $R_d$  are, instead, the parasitic resistances of source and drain respectively. Finally,  $R_{subs}$  and  $R_{subd}$  represent the lumped substrate resistors.

Using the model to simulate the device in Cadence,  $R_s$ ,  $R_d$  and the two  $R_{sub}$  are already included. The standard values for this resistances, for this CMOS technology, are usually:  $R_s \sim 2 \Omega$  and  $R_{sub} \sim 100 \Omega$ . For the gate resistance instead, sometimes the model does not include it. For example in the IBM10LP technology  $R_g$  is not taken in account in the model, and in the simulation it is necessary to add an external resistance, of about  $2-3 \Omega$ , to consider it. A smart method to verify the presence or the absence of it in the model, is to plot  $G_{max}$ . As it is shown in eq.(1.14), if  $R_{gate} = 0$ ,  $f_{max}$  goes to infinity, so it means that  $G_{max}$  will be always above 1.

An important design rule, to minimize  $R_{gate}$  in RF MOSFETs, is to make a multi-finger layout, at the expense of more parasitic capacitance. Typical finger width for 0.25  $\mu m$  device is about 5  $\mu m$ , for 0.13  $\mu m$  device is 2.5  $\mu m$ ; so, in my project, for 65 nm device I used fingers  $1 \ \mu m$  wide. As it is shown in eq.(1.16),  $R_{poly}$  scales with  $1/n^2$ , instead,  $R_{ch}$  is independent on n.

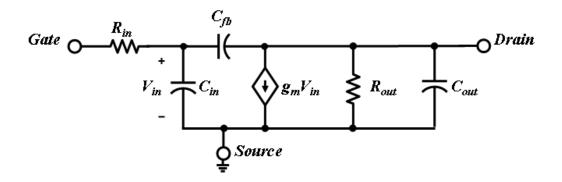

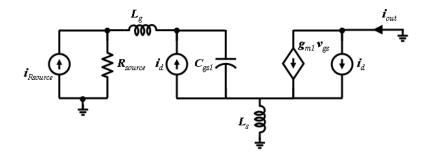

#### Equivalent Circuit Parameters for MOSFET in Terms of Y-Parameters

As, in the previous section, the device is considered when is working in saturation region. Consider the model in Fig.1.4, taking also in account the parasitic resistances, and using the Y-parameters, a new model for the RF MOSFET can be extrapolated, which is shown in Fig.1.7. In the Tab.1.1 there is the list of the 6 equations that can be plotted in Cadence to have an idea of how the 6 device parameters change in the frequency domain.

Input Resistance:

$$R_{in} = \Re\left\{\frac{1}{Y_{11}}\right\}$$

Input Capacitance:  $C_{in} = \frac{\partial}{\partial\omega}\left[\frac{1}{\Im\left(\frac{-1}{Y_{11}}\right)}\right]$ Output Resistance:  $R_{out} = \frac{1}{\Re(Y_{22})}$ Output Capacitance:  $C_{out} = \frac{\partial}{\partial\omega}[\Im(Y_{22})]$ Transconductance:  $g_m = \Re(Y_{21})$ Feedback Capacitance:  $C_{fb} = \frac{\partial}{\partial\omega}[\Im(-Y_{12})]$

Table 1.1: Circuit Parameters for MOSFET in terms of Y-Parameters

Figure 1.7: MOSFET model in terms of Y-Parameters.

#### 1.2.2 Device characterization for the IBM10LP technology

After this introduction, there is an idea of the huge amount of problems that come out designing a circuit in the radio-frequency domain. At low frequency, in the kHz range, all the parasitic elements are hidden inside the device. They do not play any role in the operating behaviour of the device and so there are a lot of pretty useful formula that can be used. Instead, when the frequency goes up, formula start to have a marginal role, because there are too many phenomena and parasitic elements that come up. At this point it is still important to have some easy formula to relate with, but the simulator becomes fundamental. This is why it is so important to test a device alone, plot some graphs, and do a first characterization of it, before starting the actual project. The same analysis should be done for both N- and P-MOSTFET.

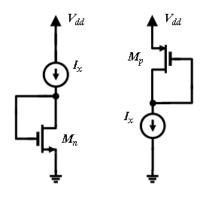

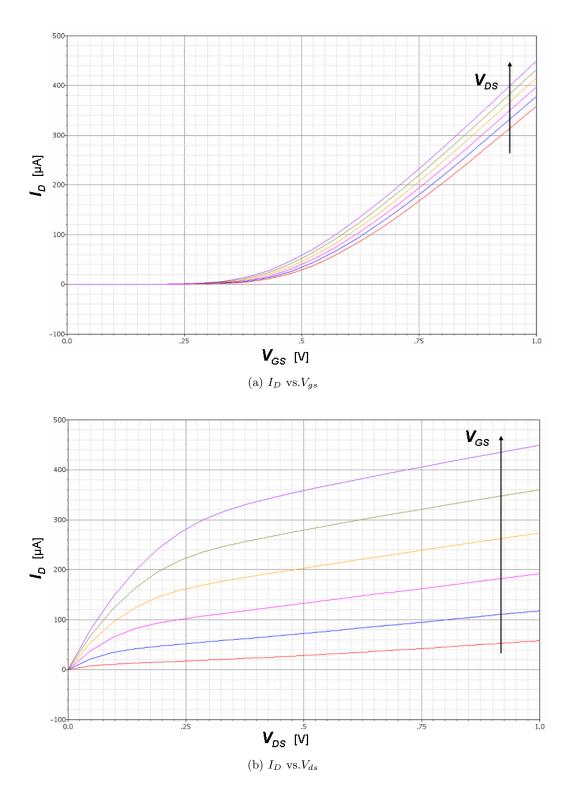

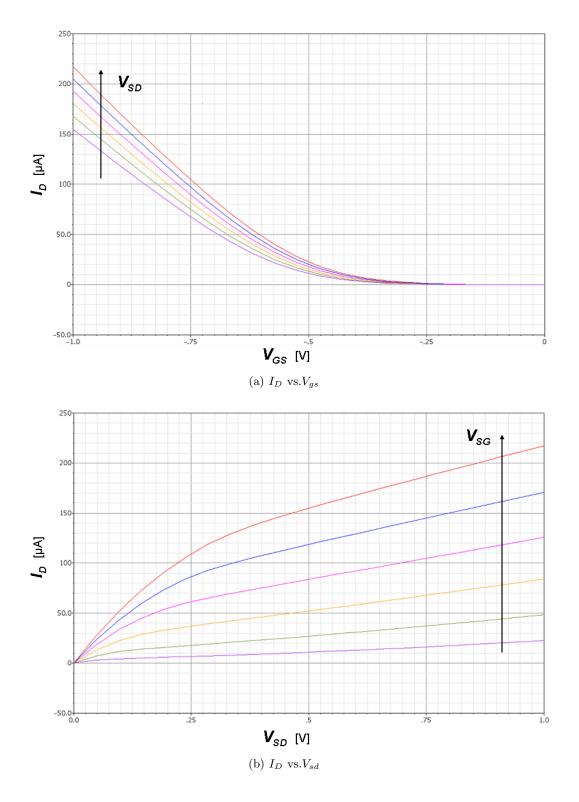

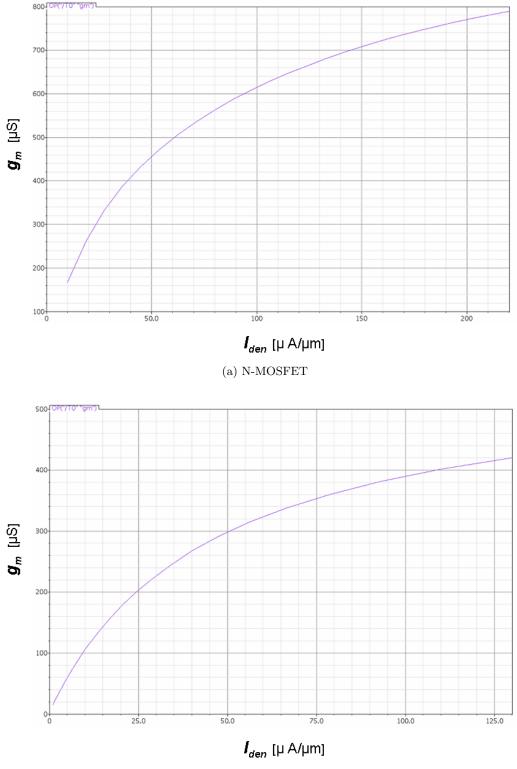

For all the plots that will be shown, a 1 finger device with  $W = 1 \, \mu m$  and  $L = 60 \, nm$  is used. With this technique, the current and the density current assume the same value, and so I could plot some important graphs in function of the density current which is the parameter which help to characterize a transistor, and not the current itself. The supply voltage for these testing simulation, and for the project in general it will be 1 V. The first plots to draw are  $I_D$  vs.  $V_{GS}$ , and  $I_D$  vs.  $V_{DS}$  (Fig.1.12 - 1.13). These plots can show the threshold voltage magnitude is about  $V_{th} = 350 \, mV$  for both the devices. Using then the circuit configuration in Fig.1.8, other plots are:  $g_m$  vs.  $I_{den}$  (Fig.1.9), and  $f_T$  vs.  $I_{den}$  (Fig.1.10), where the density current is  $I_{den} = I_x/W$ . These two plots help to understand what is the optimal bias current density to use. From Fig.1.9 it is possible to see that curves have a saturation point. There is a "limit" after that  $g_m$  becomes insensitive on the density current. It implies that the device is in velocity saturation, so, keeping increasing the drain current, maintaining W constant,  $g_m$  will remain constant the same and the device will dissipate more power for nothing (not power efficient). The goal is to work at an  $I_{den}$  where  $\partial g_m / \partial I_{den} > 1$ , and this happens when for the N-MOSFET  $I_{den} < 216 \ \mu A/\mu m$ , and for the P-MOSFET  $I_{den} < 123 \ \mu A/\mu m$ . In Fig.1.14, a zoom-in of  $g_m$ vs.  $I_{den}$  has been done in the interested region. These two plots has been the most useful for design of the circuit. They are fundamental to decide how much big devices have to be. The equation of  $g_m$  in Fig.1.14 can be simplified as

$$g_m = \sqrt{\frac{2\mu_{eff}C_{ox}W}{L}I_x} = W\sqrt{\frac{2\mu_{eff}C_{ox}W}{L}I_{den}}$$

(1.19)

i.e. if for a particular  $I_{den}$ ,  $W = 20 \ \mu m$ , just multiplying 20 times the value of  $g_m$  that is mapped

Figure 1.8: Circuit configuration to extrapolate the figures of merit.

in Fig.1.14 permits to obtain the new searched value.

From Fig.1.10, the transit frequency saturates at 175 GHz for the N.MOSFET, and to 125 GHz for the P-MOSFET.

Moreover, knowing  $I_{den}$  and  $g_m$ , from Fig.1.15, the value of  $V_{gs}$  to apply can be extrapolated.

Finally, taking the same devices, and putting  $V_{gs} = V_{ds} = 1 V$ , it can be calculated in Cadence the value of each equation, in Table 1.1, assumes at 24 GHz.  $R_{in}$  is 0 because, in the IBM10LP model, the gate resistance has not been included. In Table 1.2 there are the results.

| Device   | $R_{out}$      | $C_{in}$ | $C_{fb}$ | $C_{out}$ | $g_m$           |

|----------|----------------|----------|----------|-----------|-----------------|

| N-MOSFET | $5.94 K\Omega$ | 0.88 fF  | 0.22 fF  | 0.51 fF   | 895.4 $\mu S$   |

| P-MOSFET | $8.31 K\Omega$ | 0.84 fF  | 0.25 fF  | 0.56 fF   | $468.3 \ \mu S$ |

Table 1.2: Circuit Parameters to include in Fig.1.7 for IBM10LP technology, at 24 GHz

The last plot that is useful to see is plotted in Fig.1.11. It shows that when the frequency is smaller than 100 GHz, for both the devices,  $g_m$  maintains a constant value. So, during the design, the DC value for  $g_m$ , given by Cadence can be trusted, because it is pretty similar to the  $g_m$  value at 24 GHz.

Figure 1.11:  $g_m$  vs. Frequency,  $V_{GS} = V_{DS} = 1V$

Figure 1.12: N-MOSFET: a)  $I_D$  vs.  $V_{GS}$  with  $V_{DS} \in [0.5V, 1V]$  step 0.1V; b)  $I_D$  vs.  $V_{DS}$  with  $V_{GS} \in [0.5V, 1V]$  step 0.1V.

Figure 1.13: P-MOSFET: a)  $I_D$  vs.  $V_{GS}$  with  $V_{SD} \in [0.5V, 1V]$  step 0.1V; b)  $I_D$  vs.  $V_{SD}$  with  $V_{SG} \in [0.5V, 1V]$  step 0.1V.

(b) P-MOSFET

Figure 1.14:  $g_m$  vs.  $I_{den}$  - zoom in

Figure 1.15:  $V_{gs}$  vs.  $I_{den}$

### Chapter 2

# Theory and System Architecture Design

#### 2.1 Super-regenerative receiver (SRR)

[9][13] Integrated Circuits (IC) designers are favoured by the fact that the incremental cost of a transistor is essentially zero. This has given liberty with a large number of devices that are prevailing today. Not a long time ago when the economics of circuit design were fundamentally based on the number of device counts, often the designer was restricted by the relatively expensive active device to try to get blood from a stone. It is amazing that in the early 1920s, Edwin Armstrong devised a super-regenerative receiver circuit using few components that trade lot of gain for bandwidth, contrary to the conventional wisdom that gain and bandwidth should trade off more or less the directly. The number reduction of device components is not only cost-effective, but also improves reliability.

The characteristics of the super-regenerative receiver to generate large-signal gain at very low bias currents and the ability to operate above the cut-off frequency  $(f_T)$  of the RF device make it attractive and the preferred architecture for integrated ultra-low power wireless receiver.

Fig.2.1 depicts a 1940's 500 MHz SRR, which is bulky and require manual calibration, but the circuit operates above the device ft, which was an astonishing accomplishments in those days.

The phenomenon of the super-regenerative detection has been the main focus research, and it is still an open issue despite significant gains in practical experience and modern CAD tools

Figure 2.1: A 1940's 500-MHz Super-regenerative receiver

for design. The SRR circuits uses just a few components, and its basic design is simple, but detailed analysis is complex, due to the time varying and non-linear characteristics of the receiver circuit. Super-regenerative receivers have been used for many decades, and are still manufactured in large quantities for short-distance data exchange. Although an SRR has advantages of high gain, simplicity, low cost, low power consumption and constant demodulated output over a wide range of input signal levels, it has also drawbacks of inherent frequency instability.

Fig.2.2 shows the typical block diagram of a super-regenerative receiver, which consists of a matching network, an isolation amplifier, an amplifier with time varying loop gain and a bandpass feedback network forming a regenerative oscillator.

Figure 2.2: A typical block diagram of super-regenerative receiver (SRR).

The buffer amplifier between the antenna and the SRO (super-regenerative oscillator) performs the following functions: it reduces the RF leakage of the oscillation signal to the antenna, it provides an input match to the antenna via the passive matching network, and it injects the RF input signal current into the oscillator tank without adding significant loading to the SRO. The time varying nature of the loop gain is designed such that the SRO transconductance periodically exceeds the critical values of the transistor transconductance  $g_m$  necessary to induce instability. Consequently, the SRO periodically starts up and shuts off. The periodic shut down of the SRO is called "quenching".

The start-up time of a SRO (the time from enabling the oscillator until it reaches its saturation voltage Vsro) can be described by:

$$t_{rise} = \tau_{rise} \log \left[ \frac{V_{sro}}{\sqrt{v_n^2}} \right]$$

(2.1)

Where  $\tau$  is the time constant of the exponentially increasing oscillation envelope,  $V_{sro}$  is the zero-peak RF voltage of the saturated oscillator, and  $v_n$  is the thermal noise generated due to the resonator tank and active device.

From (2.1), the start-up time of the SRO is dependent on the instantaneous noise in the resonator, when the SRO loop gain is unity (at the onset oscillation).

Fig.2.3 exhibits the start up of the SRO in presence of thermal noise. Observing that the start up time is very sensitive to low-level signals in the SRO tank, it becomes obvious that this mechanism can be used to amplify any RF input signal.

Figure 2.3: A typical start-up transient of SRO circuit in presence of thermal noise.

Although the conceptual block diagram of the SRR is of a compact size, power efficient and uses small device counts, the design methodology is not well defined, which leads to a "cut and try" approach, based on results obtained from the simplified model. Moreover, the compact size of the SRR implies a small antenna, with poor efficiency that degrades the sensitivity of the receiver. To achieve reasonably good performance, a high sensitivity is required that conflicts with the circuit design requirements for low power consumption.

Fig.2.4 shows a typical SRR circuit that consists of the following basic modules: antenna, LNA (low noise amplifier), SRO (super-regenerative oscillator), QO (Quench oscillator), ED (envelope detector), and LPF (low-pass filter). The working principle is based on a repeated build up and decay of the self-oscillations in a SRO whose frequency is near or equal to the RF signal frequency intercepted by antenna. As illustrated, the RF signal is intercepted by

Figure 2.4: Detailed block diagram of the SRR.

the antenna and injected through the LNA into the SRO module. [10] The main objective of the LNA module is to facilitate the impedance matching with the antenna, guaranteeing the maximum power transfer into the SRO module. The LNA module optimize the noise figure, and in addiction, provides isolation, minimizing the power injected back into the antenna due to the building-up of the self-oscillations by SRO module. The gain of the SRO is periodically varied by QO signal ( $f_q$ ) for sampling the RF signal at the point of maximum sensitivity. The start-up time of the SRO's self-oscillations is proportional to the amplitude and frequency of the RF signal received through the antenna. The  $K_a(t)$  loop is used to stabilize the amplitude of the  $v_E$  by adjusting the bias current thereby enhancing the receiver's input dynamic range. Finally, the demodulation is performed by rectifying the self-oscillation voltage  $v_0$  and then filtering the envelope voltage  $v_E$  by the BPF.

## 2.2 Low-Noise Amplifier (LNA)

#### 2.2.1 Simplified analysis

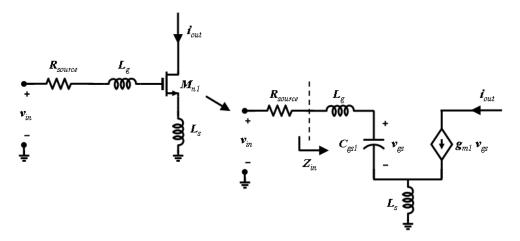

[5][11][12] The first stage of a receiver is typically a low-noise amplifier (LNA), whose main function is to provide enough gain to overcome the noise of subsequent stages. Hence, low noise figure and high gain are critical LNA performance parameters; in portable applications, low power dissipation is also essential. LNA design involves trade-off among linearity, input matching and power dissipation. The basic common-source LNA circuit is widely used in CMOS RF IC design and the CS-LNA configuration is currently popular because of its superior noise performance; i.e., the inductive degeneration is ideally noiseless and the RF input signal is preamplified by the input-matching series resonant network. The complete schematic of the 24-GHz LNA that I used in my project is depicted in Fig.2.5. The method employed here is the inductive

Figure 2.5: Complete schematic of the 24-GHz LNA.

source degeneration.  $L_g$ ,  $L_s$  and  $L_{tank}$  are implemented with an internal series resistance which takes in account losses in the component.  $R_{gate}$  instead is a resistance that has been added during the simulation in Cadence to take in account losses in the gate of the mosfet  $M_{n1}$ , whose were not considered in the IBM model. Adding  $C_f$  in shunt to the parasitic  $C_{gs}$  of  $M_{n1}$  gives more degrees of freedom to design the LNA input matching network.  $C_{tank}$ , at the same time, let me adjust the resonant frequency of the LNA without having to use a huge inductor  $L_{tank}$ .  $R_{bias}$  is a big resistance which has to make the output impedance of the bias circuit really high and neglectable in the LNA input matching network design. Cascoding  $M_{n2}$  is used to reduce the intersection of the tuned output with the tuned input, and to reduce the effect of the gatedrain capacitance of  $M_{n1}$ .  $L_g$ ,  $L_s$  and  $C_{gs}$  are chosen to provide the desired input resistance. Obviously at the input and at the output of the LNA two blocking capacitances,  $C_{BL1}$  and  $C_{BL2}$ , will be added. Their value will be the maximum value available for the technology that will be used. In this way they will not influence the input matching network in the operating frequency.

#### **Input Matching**

The simplified version of the LNA small-signal model is shown in Fig.2.6. It will help to extrapolate some basic and useful formulas for input matching and noise. To simplify the analysis,

Figure 2.6: Narrowband LNA with inductive source degeneration.

we can consider a device model that includes only a transconductance and a gate-source capacitance, and where  $L_g$  and  $L_s$  do not contain any parasitic resistance. In this case, it is not hard to show that the input impedance can be written as:

$$Z_{in} = s(L_s + L_g) + \frac{1}{sC_{gs1}} + \frac{g_{m1}}{C_{gs1}}L_s \approx s(L_s + L_g) + \frac{1}{sC_{gs1}} + \omega_T L_s$$

(2.2)

Hence, the input impedance is that of a series RLC network, with a resistive term that is directly proportional to the inductance value. And in the context of low-noise amplifiers, we actually seek to enhance this effect, creating a resistive input impedance without the noise of real resistors. However, this approach has the undesirable side effect of degrading high-frequency gain. Considering this model,  $Z_{in}$  is specified by choosing  $L_s$  and  $L_g$  to resonate with  $C_{gs1}$  at the operating frequency with  $(g_{m1}/C_{gs1})L_s$  set to 50 $\Omega$ . The associated quality factor is:

$$Q = \frac{1}{2\omega_0 C_{gs1} R_{source}} > 1 \tag{2.3}$$

#### Gain

The effective trasconductance of the LNA stage is:

$$G_m = g_{m1}Q = \frac{g_{m1}}{\omega_0 C_{gs1}(R_{source} + \omega_T L_s)} = \frac{\omega_T}{\omega_0 R_{source} \left(1 + \frac{\omega_T L_s}{R_s}\right)}$$

(2.4)

and when the input is matched to  $R_s$ , it becomes:

$$G_m = \frac{1}{2R_{source}} \left(\frac{\omega_T}{\omega_0}\right) = \frac{1}{2R_{source}} \left(\frac{f_T}{f_0}\right)$$

(2.5)

In RF systems  $R_{source}$  is usually equal to 50 $\Omega$ . Note the  $G_m$  depends only on the ratio of  $f_T$  to  $f_0$ and it is independent of the MOSFET small-signal trasconductance  $g_{m1}$ . The transit frequency  $f_T$  is usually 5 - 10 times bigger than the signal frequency  $f_0$ , therefore, the common-source LNA provides high gain.

The final gain for the LNA results:

$$A_v \approx g_{m1} Q R_{tank} \tag{2.6}$$

#### **Noise Figure**

The major advantage of the common-source amplifier with inductive degeneration is that the resistive input impedance is noiseless, unlike other topologies where a noisy resistor is added in the signal path to create a  $50\Omega$  terminating impedance. The noise factor of this topology is:

$$F = \frac{\overline{i_{n,out}^2}}{\overline{i_{R_{source}}^2}} = 1 + \frac{\gamma}{\alpha} \frac{1}{Q} \left(\frac{\omega_0}{\omega_T}\right) \left[1 + \frac{\delta\alpha^2}{5\gamma}(1+Q^2) + 2\left|c\right|\sqrt{\frac{\delta\alpha^2}{5\gamma}}\right]$$

(2.7)

With:

$$\overline{i_{R_{source}}^2} = \frac{4kT\Delta f}{R_{source}}$$

(2.8)

$$\overline{i_d^2} = 4kT\gamma g_{d0}\Delta f \tag{2.9}$$

$$\overline{i_g^2} = 4kT\delta g_g \Delta f \tag{2.10}$$

$$Q = \frac{1}{\omega_0 C_{gs1} R_{source}} \tag{2.11}$$

$$\overline{i_g i_d^*} = c \sqrt{\overline{i_g^2 i_d^2}} \tag{2.12}$$

where c = j0.395,  $\alpha$ ,  $\gamma$ , and  $\delta$  are bias-dependent parameters, and  $\omega_0$  and  $\omega_T$  are the operating and unity current gain frequencies, respectively. From (2.7), noise in the LNA is formed by

Figure 2.7: Small-signal circuit for noise figure analysis of CS-LNA.

three factors: channel noise, gate noise and correlated noise. Increasing Q of the input resonant circuit reduces the contribution of channel noise. In contrast, gate noise is enhanced by the Qfactor. Hence, there exists an optimum Q that minimizes the noise figure. For a given overdrive and  $f_T$ , the optimum values are:

$$F_{min} = 1 + \frac{\gamma}{\alpha} \left(\frac{\omega_0}{\omega_T}\right) \frac{2\delta\alpha^2}{5\gamma} Q_{opt}$$

(2.13)

$$Q_{opt} = \sqrt{1 + 2|c|} \sqrt{\frac{5\gamma}{\delta\alpha^2} + \frac{5\gamma}{\delta\alpha^2}}$$

(2.14)

To achieve a high  $f_T$ , minimum channel length is used. Knowing the optimum Q value for minimum noise figure, the optimum width of the device is then easily determined.

#### 2.2.2 Accurate analysis

If we consider Fig.2.5 and we also take in account the parasitic resistance of  $L_s$  and  $L_g$  the formula for the input matching becomes a little bit different. The following equation is the one

I used to design the LNA.

$$Z_{in} = s(L_s + L_g) + \frac{1}{s(C_{gs1} + C_f)}(1 + g_{m1}R_s) + \frac{g_{m1}}{C_{gs1} + C_f}L_s + R_s + R_g + R_{gate}$$

(2.15)

where  $R_s$  and  $R_g$  are the parasitic series resistances of  $L_s$  and  $L_g$  respectively.

## 2.3 Super-regenerative oscillator (SRO)

#### 2.3.1 Super-regenerative Modes

[13] Fig.2.8 shows the two typical operation modes for the SRR: detector output in the linear mode, detector output in the logarithmic mode and RF input signal. The linear mode is

Figure 2.8: Super-regenerative Modes.

described by a linear relationship between the amplitude of the RF input signal and the amplitude of the demodulated output. In this mode, SRO does not reach its steady state during the quench period, due to a high quench frequency and/or a low start-up current. However, the typical operation is made of a combination of the both modes; hence, it is difficult o predict an exact mode of SRO operation. In the linear mode, the oscillation amplitude is measured before the oscillator reaches saturation providing a high independent gain.

As depicted in the linear mode, the samples envelope is much larger in the presence of the RF input signal. Notice that, in this mode, the oscillator is disable after the amplitude is measured. Thus, in the linear mode, the oscillator never reaches saturation.

A logarithmic mode is described by a logarithmic relationship between the amplitude of the RF input signal and the amplitude of the demodulated output characterizes the logarithmic mode. In this mode the SRO reaches its steady state amplitude at each quench cycle, due to a low frequency and/or a high start-up current; therefore, a reduction in the dynamic range of the demodulated output is due to the logarithmic compression of the signal. In the logarithmic mode, however, the oscillator is allowed to saturate during each cycle. The detector circuitry

senses the area under the oscillation envelope, providing a signal dependent gain. As shown for the logarithmic mode, the area under the saturated oscillation envelope is increased in the presence of an RF input, resulting from the decrease oscillator start-up time in this condition.

So one important difference between the two modes is that the logarithmic mode provides an inherent automatic gain control.

## 2.3.2 Analytical Model of the super-regenerative receiver for the Linear Mode

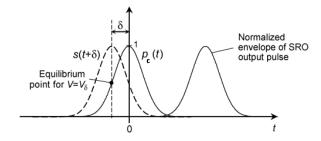

[9][10] Before starting with the detailed description of the theory, which will try to give a mathematical explanation of the super-regenerative phenomenon, it is convenient to anticipate the parameters that will be used (Fig.2.9 and 2.10 can help to visualize the shape of the functions that are going to be listed):

- 1. Feedforward Gain: Factor  $K_0$  is the gain provided by the selective network at the resonance frequency. It represents the open-loop gain of the super-regenerative oscillator, i.e., the one provided when the feedback amplifier remains inactive.

- 2. Sensitivity Curve: s(t) is a normalized function that, for t = 0, takes the maximum value of unity, and decreases toward zero as time separates from t = 0. The decrease of this curve is quite fast, due to its exponential dependence on t. In practical receivers, the value of this function becomes practically null in an environment relatively close to the origin, t = 0. The shape of s(t) is determined mainly by the environment of the zero-crossing of  $\varsigma(t)$ . A slow transition will provide a wide sensitivity curve, whereas a fast one will generate a narrow curve.

Both the regenerative gain and the frequency response depend on the product  $p_c(t)s(t)$ . In this way, the sensitivity curve acts as a function which weights the incoming envelope  $p_c(t)$ ; the values of  $p_c(t)$  near t = 0 will be taken into account, whereas those close to  $t_a t_b$  will be irrelevant. The instant t = 0 can be considered the instant of maximum sensitivity.

3. Regenerative Gain:  $K_r$  is also called the *slope* or *step factor* in the literature, depending on the type of quench applied. It takes in account the contribution of differential portions of the input signal envelope, each one weighted by the sensitivity curve. This gain depends on the product  $p_c(t)s(t)$ . If  $p_c(t)$  or s(t) is narrow, the regenerative gain will be small. Instead, if both of those are wide, the regenerative gain will be large.

- 4. Super-regenerative Gain:  $K_s$  is related with the exponential growth of the oscillation and is the most significant amplification factor. It is determined by the area enclosed by the negative portion of the damping function.

- 5. Frequency Response: It is the normalized Fourier transform of  $p_c(t)s(t)$  shifted toward the oscillation frequency  $\omega_0$ . If both,  $p_c(t)$  and s(t), are wide, the bandwidth of the selectivity curve of the receiver will be small; if  $p_c(t)$  or s(t) is narrow, the bandwidth will be large.

- 6. Normalized Oscillation Envelope: Finally, the normalized oscillation envelope p(t) is determined mainly by the evolution of the damping function close to  $t_b$ .

Figure 2.9: RF input signal, damping function, and SRO output.

The following analysis considers the block diagram previously presented in Fig.2.4. The feedback amplifier module shows a variable gain  $K_a(t)$ , which is controlled by the quench signal QO, that forces the system to be alternatively stable and unstable. The transfer function of the selective network (SN) can be described by

$$G(s) = K_0 \left[ \frac{2\zeta_0 \omega_0 s}{s^2 + 2\zeta_0 \omega_0 s + \omega_0^2} \right]$$

(2.16)

Figure 2.10: Damping function  $\varsigma(t)$ , sensitive curves s(t), normalized envelope of the output pulse p(t), and normalize envelope of the input signal  $p_c(t)$ .

From Equation (2.16), the characteristic differential equation of the SR can be given by

$$\frac{\partial^2 v_0(t)}{\partial t^2} + 2\varsigma_0 \omega_0 \frac{\partial v_0(t)}{\partial t} + \omega_0^2 v_0(t) = 2K_0 \varsigma_0 \omega_0 \frac{\partial v_s(t)}{\partial t}$$

(2.17)

where  $\varsigma_0$  is the quiescent damping factor and  $K_0$  is the maximum amplification. Fig.2.11 shows the typical parallel and series equivalent representation of the SRO. The feedback network can be described as  $v_s(t) = v(t)K_a(t)v_0(t)$ , which can be represented by the linear, time-variant, second-order differential equation

$$\frac{\partial^2 v_0(t)}{\partial t^2} + 2\varsigma_0 \omega_0 \frac{\partial v_0(t)}{\partial t} + \omega_0^2 v_0(t) = 2K_0 \varsigma_0 \omega_0 \left[ \frac{\partial v(t)}{\partial t} + K_a(t) \frac{\partial v_0(t)}{\partial t} + v_0(t) \frac{\partial K_a(t)}{\partial t} \right]$$

(2.18)

$$\frac{\partial^2 v_0(t)}{\partial t^2} + 2\varsigma_0 \omega_0 \frac{\partial v_0(t)}{\partial t} + \omega_0^2 v_0(t) = 2K_0 \varsigma_0 \omega_0 \frac{\partial v(t)}{\partial t} \quad for \quad \frac{\partial K_a(t)}{\partial t} \to 0$$

(2.19)

where  $\varsigma(t)$  is the instantaneous damping factor of the closed-loop system that can be characterized as

$$\varsigma(t) = \varsigma_0 \left[ 1 - K_0 K_a(t) \right] \tag{2.20}$$

Figure 2.11: Parallel and Series RLC circuits.

The instantaneous quality factor Q(t) is

$$Q(t) = \frac{1}{2\varsigma(t)} \tag{2.21}$$

The quench oscillator generates an instantaneous damping factor, or damping function,  $\varsigma(t)$ , that is periodic. This function is composed of successive quench cycles. A new quench cycle starts when the damping function changes to positive  $(t = t_a)$ , which extinguishes any oscillation present in the oscillator. After it changes to negative (t = 0), the oscillation builds up from the injected signal v(t) and achieves the maximum amplitude when  $\varsigma(t)$  once again changes to positive  $(t = t_b)$ . Citing results which have been obtained in the article [10], the receiver seems especially sensitive to the input signal in a certain environment at the instant t = 0. The behaviour of the receiver is mainly determined by the characteristics of the damping function (e.g., its shape, repetition frequency and mean value). Since  $\varsigma(t)$  gives global information about the system's performance, it is a better descriptor than just the feedback gain  $K_a(t)$ . In practice,  $K_a(t)$  is adjusted in order to obtain the desired  $\varsigma(t)$ .

The general solution of (2.18) can be broken down into the sum of the general solution of the homogeneous equation plus a particular solution of the complete equation, according to

$$v_o(t) = v_{oh}(t) + v_{op}(t)$$

(2.22)

where  $v_{oh}(t)$  is the free (or natural) response, which may exist even though no excitation is present, whereas  $v_{op}(t)$  represents the forced response generated by the excitation. Skipping the complex calculation and in order to obtain compact expressions that are easier to interpret, several parameters and functions that have been used in the literature to describe the

1. Super-regenerative gain:

operation of the receiver are introduced:

$$K_s(t) = e^{-\omega_0 \int_0^{t_b} \varsigma(\lambda) d\lambda}$$

(2.23)

2. Normalized envelope of the SRO output:

$$p(t) = e^{-\omega_0 \int_{t_b}^{t} \varsigma(\lambda) d\lambda}$$

(2.24)

3. Sensitivity curve:

$$s(t) = e^{\omega_0 \int_0^t \varsigma(\lambda) d\lambda}$$

(2.25)

All of these functions exhibit an exponential dependence on the damping function  $\varsigma(t)$ . The typical input signal v(t) of the SRO can be given in a single quench interval as

$$v(t) = V_m p_c(t) \cos \left[\omega_0 t + \phi\right] + n(t)$$

(2.26)

where  $V_m$  is the peak amplitude,  $p_c(t)$  is the normalized envelope of the SRO input signal, n(t) is the additive Gaussian noise generated by the active devices of the receiver circuit (described by the autocorrelation function  $R_n(\tau) = [\eta/2] \delta(t)$  with the power spectral density  $G_n(f) = \eta/2$ ). The SRO output can be described by: • the general solution of the homogeneous differential equation

$$v_{oh}(t) = V_h p_c(t) \cos(\omega_0 t + \phi_h) \tag{2.27}$$

where  $V_h$  and  $\phi_h$  are the magnitude and the phase, respectively;

• and the particular solution of the complete equation becomes

$$v_{op}(t) = 2\varsigma_0 K_0 K_s p_c(t) \int_{t_0}^t \dot{v}(\tau) s(\tau) \sin \omega_0 (t-\tau) d\tau$$

(2.28)

where  $\varsigma_0$  is the quiescent damping factor, s(t) is the sensitivity curve,  $K_0$  is the maximum amplification and  $K_s$  is the super-regenerative gain. The above expression apply to any value of t, but we are interested in the values of s(t) in the interval  $(t_a, t_b)$ . Note that the maximum value of expression (2.25) within this interval equals unity and that this value is achieved when t = 0. Considering, instead, p(t), expression (2.24) shows that the maximum value of unity is achieved when  $t = t_b$ . Fig.2.10 shows the typical shapes of s(t)and p(t) under sinusoidal quench.

The noise output  $n_0$  can be given by

$$n_0(t) = 2\varsigma_0 K_0 K_s p_c(t) \int_{t_0}^t n(\tau) s(\tau) \sin \omega_0(t-\tau) d\tau$$

(2.29)

From Equations (2.26) to (2.29) the signal to noise ratio (S/N) at the SRO output can be given as

$$[SNR]_{0} = \left[\frac{S}{N}\right]_{output} = \frac{E_{c}}{\eta} \frac{\left[\int_{t_{a}}^{t_{b}} p_{c}(\tau)s(\tau)d\tau\right]^{2}}{\int_{t_{a}}^{t_{b}} p_{c}^{2}(\tau)\int_{t_{a}}^{t_{b}} s^{2}(\tau)d\tau}$$

(2.30)

where  $E_c$  is the average chip energy.

From Equation (2.30) the SNR of the SRO can be optimized using Schwarz's inequality as

$$\frac{\left[\int_{t_a}^{t_b} p_c(\tau) s(\tau) d\tau\right]^2}{\int_{t_a}^{t_b} p_c^2(\tau) \int_{t_a}^{t_b} s^2(\tau) d\tau} \le 1$$

(2.31)

From Equation (2.30) and (2.31),  $[SNR]_{0,opt}$  can be given by

$$[SNR]_0 = \frac{E_c}{\eta} \quad for \quad p_c(t) = s(t) \tag{2.32}$$

#### Response to an RF Pulse

Next, the system response to a single RF pulse is going to be presented. For sake of simplicity, noise will be neglected in the study. Fig.2.10 helps to understand this section.

The RF pulse is applied within the limits of a single quench cycle, given by the interval  $(t_a, t_b)$ , and expressed as

$$v(t) = V p_c(t) \cos(\omega t + \phi) \tag{2.33}$$

where  $p_c$  is the normalized pulse envelope and V its peak amplitude.  $p_c$  is assumed to be zero beyond the cycle limits defined by  $t_a$  and  $t_b$ . Furthermore, there is no free response coming from previous quench cycles when the current cycle starts, and so  $v_{oh}(t) = 0$  and  $v_o(t) = v_{op}(t)$ , using expression (2.28), we obtain that the response  $v_{op}(t)$  is determined by the derivative of the excitation, whose expression is

$$\dot{v}(t) = V \left[ \dot{p}_c(t) \cos(\omega t + \phi) - p_c(t)\omega \sin(\omega t + \phi) \right]$$

(2.34)

This expression can be approximated by

$$\dot{v}(t) \approx -V p_c(t) \omega \sin(\omega t + \phi)$$

(2.35)

when  $p_c(t)$  varies slowly in comparison with the RF oscillation  $(|\dot{p}(t)| \ll p(t)\omega)$ . Taking  $v_{oh}(t) = 0$  and replacing (2.35) in (2.28) and making some consideration to simplify the expression, we can write that

$$v_o(t) \approx V K_0 K_s \varsigma_0 \omega p(t) \times \int_{t_a}^t p_c(\tau) s(\tau) \cos((\omega - \omega_0)\tau + \omega_0 t + \phi) d\tau$$

(2.36)

The sensitivity curves usually decreases rapidly as time separates from the origin, t = 0, reaching negligible values that fall outside the interval defined by  $(t_{sa}, t_{sb})$ , which can be defined as the sensitive period. This means that the influence of the input signal is small outside the specified interval. Assuming that s(t) is small at the end of the quench period, it has an effect on both the initial values of the envelope and the super-regenerative gain. In particular

$$s(t_a) = p(0) = e^{\omega_0 \int_0^{t_b} \varsigma(\lambda) d\lambda} = \frac{1}{K_s} \ll 1$$

(2.37)

Therefore, a small value for the sensitivity curve at the end of the quench cycle implies small values for the output envelope near the origin and large super-regenerative gains. Consider that the sensitive period ends for all practical purpose when the amplitude of the oscillation is still small, it is possible to replace t by  $t_b$  in the integration limits of (2.36), yielding

$$v_o(t) = V K_0 K_s \varsigma_0 \omega p(t) \int_{t_a}^{t_b} p_c(\tau) s(\tau) \cos((\omega - \omega_0)\tau + \omega_0 t + \phi) d\tau$$

(2.38)

And this equation is valid only after the practical end of the sensitivity period, when  $t > t_{sb}$ ; otherwise, t must be kept instead of  $t_b$ . Expression (2.38) shows that, in the linear mode, the output of the oscillator is proportional to the peak amplitude of the input signal, and that the forced response has the form of the free response after the end of the sensitivity period.

#### Response to a Pulse when the carrier is Tuned to the Resonance Frequency

When the receiver is tuned to the receiver frequency, then the solution becomes

$$v_o(t) = V K_0 K_s \varsigma_0 \omega_0 p(t) \left[ \int_{t_a}^{t_b} p_c(\tau) s(\tau) d\tau \right] \cos((\omega_0 t + \phi)$$

(2.39)

and it shows that in addiction to  $K_0$  and  $K_s$ , a new amplification factor appears. This factor is the regenerative gain

$$K_r = \varsigma_0 \omega_0 \int_{t_a}^{t_b} p_c(\tau) s(\tau) d\tau$$

(2.40)

This gain takes into account the area of the envelope of the received pulse weighted by the sensitivity curve. A pulse the concentrates its energy around the peak of the sensitivity curve will have a regenerative gain greater than that of a more spread pulse. Thus, the new expression for the tuned input is

$$v_o(t) = V K_0 K_r K_s p(t) \cos(\omega_0 t + \phi)$$

(2.41)

This expression allows the peak amplification K, defined as the ratio between the peak values of the input and the output oscillation, to be obtained. Thus

$$K = K_0 K_r K_s \tag{2.42}$$

The output is then reduced to the simple expression

$$v_o(t) = VKp(t)\cos(\omega_0 t + \phi) \tag{2.43}$$

#### 2.3.3 Synchronous Operation of the Receiver

[8] Taking always in account Fig.2.9 and keep working on equation (2.25), the sensitive curve s(t) can be also write as

$$s(t) = e^{\omega_0 \int_0^t \zeta(\lambda) d\lambda} \approx e^{-\frac{1}{2} \left(\frac{t}{\sigma_s}\right)^2}$$

(2.44)

Indeed, when the slope of  $\varsigma(t)$  is finite, s(t) can be approximated by a Gaussian function, whose standard deviation  $\sigma_s$  is considerably smaller than the quench period (sinusoidal quench). Consequently, from eq.(2.40) and (2.42), we can see that the receiver is more sensitive to the input signal at t = 0, which is called sensitivity period. This point confirms the behaviour of the SRO as a sampling device. The RF bandwidth of the receiver is proven to be inversely proportional to  $\sigma_s$ , and it can be expresses as

$$\Delta f_{-3dB} = \frac{\sqrt{\ln 2}}{\pi} \frac{1}{\sigma_s}.$$

(2.45)

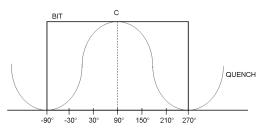

Fig.2.12a represents the conventional linear mode operation with a narrowband on-off keying (OOK) modulated input signal. This technique is adopted when the SRO is asynchronously quenched. Indeed, when input data and quench signal are not synchronized the quench samples several times during each bit period  $T_b$  to satisfy the Nyquist criterion so that the information can be retrieved by low-pass filtering the baseband bit samples. It means that if there is not any kind of synchronization between the received signal and the quench signal, we will need a quench able to detect more samples for each bit to observe the presence of a single bit. So, the quench frequency  $f_q$  should be more than 4 times bigger than the data-bit rate. In Fig.2.12a we can also observe that the sensitivity period is much shorter than the bit period, so the resulting RF bandwidth is much greater than the modulation bandwidth.

Another way to work is, instead, shown in Fig. 2.12b. When the SRO is quenched synchronously with the received signal, with a circuit configuration proposed in Fig. 2.13, we can get a single sample for each bit pulse. This means that the quench frequency equals the bit frequency. The duration of the sample bit is closer to that of the sensitivity period, and so the bandwidth of the modulated signal and that of the receiver become similar. The block diagram of the receiver in Fig. 2.13 incorporated a PLL that controls the quench voltage-controlled oscillator (VCO) to ensure bit sampling is properly carried out. The output of the envelope detector gives the error signal, which is passed through a baseband amplifier (BBA) and a loop filter. Fig.2.14 shows the normalized envelope of the received bit pulse and the sensitivity curve of

Figure 2.12: SRO input and output signals with OOK modulation.

Figure 2.13: Block diagram of the synchronous super-regenerative receiver.

the SRO under normal operation. After the acquisition of the bit, the loop goes to center the sensitive period of the SRO on the ascending flanks of the received bit pulses. Thus, the phase variation of the received pulse results in an amplitude variation at the loop-filter output that tends to correct the error  $\delta$ , that is shown in Fig.2.14.

### 2.4 Current-Reuse CMOS Differential LC-VCO

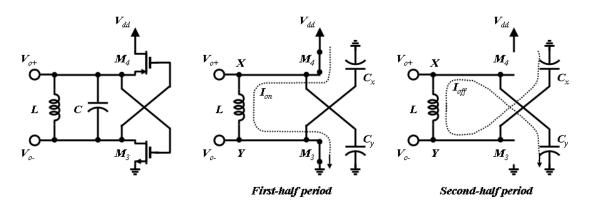

[6][16][17] Fig.2.15 shows a comparison between a conventional NMOS-based differential LC-VCO (2.15a) and the proposed current-reuse differential LC-VCO (2.15b). As compared to the complementary cross-coupled CMOS VCO, the circuit structure of the current-reused oscillator is asymmetrical. The negative conductances are provided by the cross connected pairs of

Figure 2.14: Normalized envelope of the input bit pulse  $p_c(t)$ , shifted sensitivity curve of the SRO  $s(t + \delta)$ , and normalized envelope of the SRO output oscillation.

transistors,  $M_1$  and  $M_2$  in the first case, and,  $M_3$  and  $M_4$  in the second case, to compensate the losses in the LC-tanks. In the conventional LC-VCO configuration, two N-MOSFETs or two P-MOSFETs can be used to form the cross-couple, and when the oscillation starts the two devices are alternatively ON and OFF. In the current-reuse oscillator, instead, the cross connected pair is formed by an N-MOSFET and P-MOSFET, and during the unstable phase they turn both ON and OFF at the same time. This configuration reduces power dissipation to half that of conventional topologies. In fact, in Fig.2.15a, for the whole oscillation period the bias current  $I_s$  is flowing alternatively in both branches; instead, Fig.2.16 shows that the bias current is going through the oscillator just in the first-half period. Thus, the series stacking of N- and P-MOSFET allows the supply current to be reduced by half compared to that of the conventional LC-VCO while providing the same negative conductance.