## Università degli Studi di Padova

DIPARTIMENTO DI INGEGNERIA DELL'INFORMAZIONE Corso di Laurea in Ingegneria Elettronica

## Statistical analysis of Total Ionizing Dose response in 25-nm NAND Flash memories

Laureanda: Federica Ferrarese Relatore: Prof. Alessandro Paccagnella

Correlatori: Dott. Marta Bagatin Dott. Simone Gerardin

# Abstract

Flash memory is one of the most widely used non-volatile information-storage device today, as portable store media in cellphones, cameras, music players and other portable devices. The floating-gate transistor cell, which is the base element on Flash memory, is being aggressively scaled, especially for NAND devices, to increase the memory capacity.

In addition, Flash memories are also interesting for space applications. Commercial devices are attractive for space, due to low cost per bit, but they are sensitive to radiation effects. The reason is that commercial Flash memories are characterized by higher performance than their rad-hard analogues, however it is necessary to study the radiation response to improve them against radiationinduced malfunctions. Ionizing particles, impinging on devices operating in space environment, cause a wide range of effects, from the function wear out to temporary effects or permanent ones, leading to unacceptable conditions for complex system, which have to work for long times without maintenance.

The purpose of this work is to analyze the bit error variability in response to Total Ionizing Dose (TID) in 25-nm SLC NAND Flash memories. A large number number of devices were exposed to gamma rays from Co-60 source and radiation induced Floating Gate errors, i.e. bit flips, were collected. The amount of errors were large enough to allow a statistical analysis of the results. Furthermore, radiation-induced effects were analyzed taking into account sources of statistical variability, related to scaling issue, since the nanometric size of the devices introduces several reliability problems, due to granularity of charge and matter.

For this reason more than 1 Terabit of cells were irradiated, from two different lots, analyzing cell-to-cell and lot-to-lot variability. In this work for the first time FG errors, due to TID effects, are statistically analyzed in Flash NAND samples. There are no previous studies with such a large amount of memories irradiated. The results of this thesis intend to produce a contribution in the study of Flash memory reliability, since this device is becoming more and more attractive for space market, as solid state driver for data storage.

# Sommario

Attualmente la memoria Flash è uno dei più diffusi dispositivi non volatili per l'immagazzinamento di informazioni, utilizzata in molte applicazioni di uso quotidiano come telefoni cellulari, fotocamere, lettori musicali ed alti dispositivi portatili. Il transistor a gate flottante, che costituisce l'elemento base della memoria Flash, ha subito un'aggressiva riduzione delle dimensioni, soprattutto nei dispositivi di tipo NAND, per aumentare la capacità della memoria.

Inoltre la memoria Flash è utilizzata anche in applicazioni spaziali, grazie al basso costo per bit, nonostante la sensibilità alle radiazioni. La ragione è che le memorie Flash commerciali sono caratterizzate da prestazioni superiori rispetto agli analoghi rad-hard, tuttavia è indispensabile studiarne la risposta alla radiazione, per prevenire eventuali malfunzionamenti. Le particelle ionizzanti, incidenti sui dispositivi che operano in ambiente spaziale, possono causare una vasta gamma di effetti, dall'usura ad effetti temporanei o permanenti, portando a una condizione inaccettabile in un sistema complesso, il cui funzionamento deve essere garantito per un lungo tempo, senza alcun intervento di manutenzione.

L'obiettivo di questo lavoro è di analizzare la variabilità dei bit errors dovuti alla dose totale ionizzante (TID) in memorie Flash SLC da 25 nm. Un gran numero di dispositivi è stato esposto a raggi gamma da Co-60 e sono stati misurati gli errori del Floating Gate, ovvero i bit flip, indotti dalla radiazione ionizzante. La quantità degli errori osservati è stata significativa, in modo da permettere un'analisi statistica dei risultati. Inoltre, gli effetti indotti dalla radiazione ionizzante sono stati considerati congiuntamente alle sorgenti di variabilità statistica relative allo scaling dei dispositivi, poiché le dimensioni nanometriche della cella introducono una serie di questioni affidabilistiche, dovute alla granularità della carica e della materia.

Per questo motivo è stato irraggiato più di un Terabit di celle, prelevate da due differenti lotti, ed è stata analizzata la variabilità tra lotti e tra dispositivi. Per la prima volta, irraggiando una così ampia popolazione di campioni, si sono analizzati statisticamente gli errori del Floating Gate dovuti a TID, in memorie Flash di tipo NAND. Con questa tesi si intende apportare un contributo nello studio dell'affidabilità delle memorie Flash in applicazioni per uso spaziale, dato che questi dispositivi si stanno largamente diffondendo sul mercato come unità a stato solido per l'immagazzinamento di informazioni.

# Contents

| A        | bstra | $\operatorname{ct}$                           | Ι        |

|----------|-------|-----------------------------------------------|----------|

| Sc       | omma  | ario                                          | III      |

| 1        | Intr  | oduction                                      | 1        |

|          | 1.1   | Non-volatile memory                           | 1        |

|          | 1.2   | Motivation                                    | 3        |

|          | 1.3   | Thesis Organization                           | 4        |

| <b>2</b> | The   | e Device                                      | <b>5</b> |

|          | 2.1   | Floating Gate Transistor                      | 5        |

|          |       | 2.1.1 The Reading Operation                   | 8        |

|          |       | 2.1.2 Charge Injection and Removal Mechanisms | 9        |

|          |       | 2.1.3 Threshold Voltage Distribution          | 13       |

|          | 2.2   | Array Organization                            | 16       |

|          |       | 2.2.1 NOR Architecture                        | 16       |

|          |       | 2.2.2 NAND Architecture                       | 18       |

|          | 2.3   | Reliability                                   | 20       |

|          |       | 2.3.1 Retention                               | 20       |

|          |       | 2.3.2 Endurance                               | 21       |

|          |       | 2.3.3 Statistical Effects                     | 22       |

|          | 2.4   | Scaling Issues                                | 30       |

|          | 2.5   | Conclusions                                   | 31       |

| 3        | Rad   | liation Effects                               | 33       |

|          | 3.1   | Space Radiation Environment                   | 33       |

|          | 3.2   | Basic Concepts                                | 37       |

|          |       | 3.2.1 Dosimetry                               | 38       |

|          |       | 3.2.2 Basic Radiation Effects in Device       | 39       |

|          | 3.3   | Total Ionizing Dose                           | 39       |

|          |       | 3.3.1 General Overview                        | 39       |

|          |       | 3.3.2 Charge Yield                            | 42       |

|          |       | 3.3.3 Oxide Traps Neutralization              | 43       |

|          | 3.4   | Radiation Induced Failure in Flash memory     | 44       |

|          |                  | 3.4.1 Floating Gate Cell                                                                                                                                              | 14        |

|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          |                  | 3.4.2 Peripheral Circuitry                                                                                                                                            | 18        |

|          | 3.5              | Conclusions                                                                                                                                                           | 50        |

| 4        | $\mathbf{Exp}$   | periment 5                                                                                                                                                            | <b>51</b> |

|          | 4.1              | Estec Co-60 Facility                                                                                                                                                  | 51        |

|          | 4.2              | Experimental Procedure                                                                                                                                                | 53        |

|          |                  | 4.2.1 Calibration $\ldots \ldots $                                  | 53        |

|          |                  | 4.2.2 TID test setup $\ldots \ldots \ldots$           | 59        |

|          | 4.3              | Conclusions                                                                                                                                                           | 35        |

| <b>5</b> | Var              | iability Analysis 6                                                                                                                                                   | 67        |

|          | 5.1              | Threshold Voltage Spread                                                                                                                                              | 67        |

|          |                  | 5.1.1 Lot-to-lot variability $\ldots \ldots $                                            | 71        |

|          |                  | 5.1.2 Chip-to-chip variability $\ldots \ldots \ldots$ | 75        |

|          | 5.2              | Errors Spatial Distribution into Pages                                                                                                                                | 32        |

|          |                  | 5.2.1 Device Decap $\ldots \ldots \ldots$             | 38        |

|          | 5.3              | Annealing                                                                                                                                                             | 38        |

|          | 5.4              | Current                                                                                                                                                               | 92        |

|          | 5.5              | Conclusions                                                                                                                                                           | 94        |

| 6        | Fina             | al Considerations 9                                                                                                                                                   | 97        |

| A        | Pro              | gram and Read Scripts 9                                                                                                                                               | 9         |

| в        | Erre             | ors distribution across pages 10                                                                                                                                      | )1        |

| Bi       | Bibliography 106 |                                                                                                                                                                       |           |

# List of Figures

| 1.1  | Non volatile memory market                                                                                                                                                        | 2 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1.2  | Flash applications                                                                                                                                                                | 3 |

| 2.1  | Schematic of a charge-based cell                                                                                                                                                  | 5 |

| 2.2  | Drain current as a function of gate voltage                                                                                                                                       | 6 |

| 2.3  | Schematic of capacitive coupling components in the FG cell. $\ . \ .$                                                                                                             | 7 |

| 2.4  | Energy band diagram                                                                                                                                                               | 9 |

| 2.5  | Energy band diagram for HEI                                                                                                                                                       | 1 |

| 2.6  | FN tunneling 1                                                                                                                                                                    | 2 |

| 2.7  | FN tunnel current versus electric field                                                                                                                                           | 3 |

| 2.8  | ISPP algorithm                                                                                                                                                                    | 5 |

| 2.9  | Threshold voltage distribution SLC and MLC $\ldots \ldots \ldots$ | 5 |

| 2.10 | NOR architecture                                                                                                                                                                  | 7 |

| 2.11 | Program and erase in NOR architecture                                                                                                                                             | 7 |

| 2.12 | NOR architecture                                                                                                                                                                  | 9 |

| 2.13 | Program and erase in NAND architecture                                                                                                                                            | 0 |

| 2.14 | Threshold voltage window closure                                                                                                                                                  | 2 |

| 2.15 | Over-erasing effect                                                                                                                                                               | 3 |

| 2.16 | Erratic bit                                                                                                                                                                       | 4 |

| 2.17 | Effects of cycling on SILC 2                                                                                                                                                      | 5 |

| 2.18 | SILC                                                                                                                                                                              | 5 |

| 2.19 | TAT 2                                                                                                                                                                             | 6 |

| 2.20 | Anode Hole Injection                                                                                                                                                              | 7 |

| 2.21 | TAT and 2-TAT                                                                                                                                                                     | 7 |

| 2.22 | EIS                                                                                                                                                                               | 8 |

| 2.23 | Random Telegraph Signal                                                                                                                                                           | 9 |

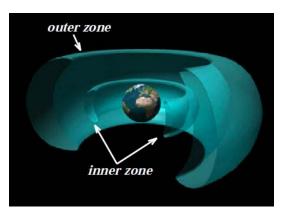

| 3.1  | Van Allen belts                                                                                                                                                                   | 4 |

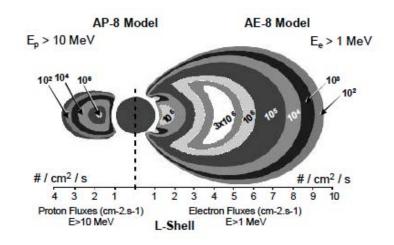

| 3.2  | Van Allen belts, AP-8 and AE-8                                                                                                                                                    | 5 |

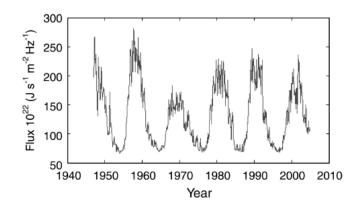

| 3.3  | Solar cycles                                                                                                                                                                      | 6 |

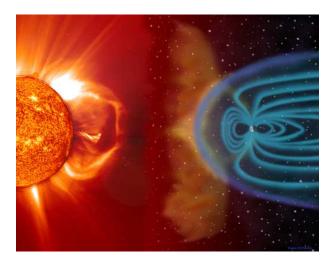

| 3.4  | Coronal mass ejection                                                                                                                                                             | 6 |

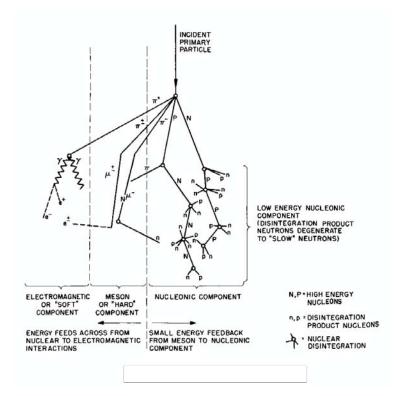

| 3.5  | Interaction of cosmic galactic rays rays with the atmosphere 3                                                                                                                    | 7 |

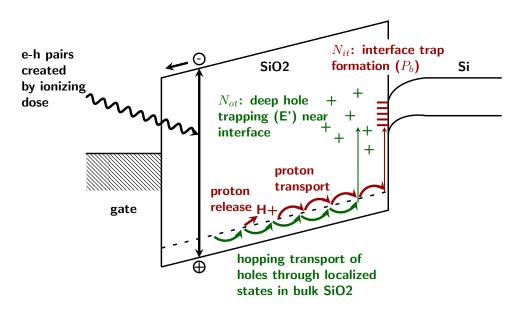

| 3.6  | TID damage                                                                                                 | 41 |

|------|------------------------------------------------------------------------------------------------------------|----|

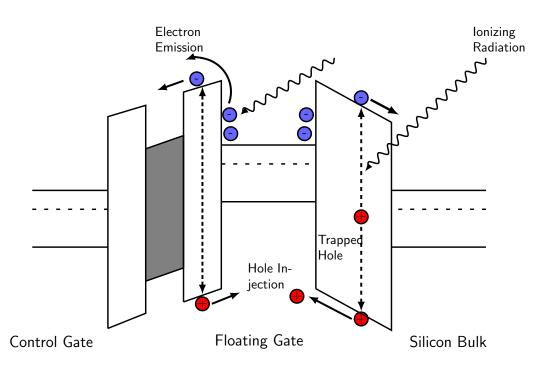

| 3.7  | Mechanisms of TID induced $V_T$ shift $\ldots \ldots \ldots \ldots \ldots \ldots$                          | 45 |

| 3.8  | Schematic representation of a FG memory cell                                                               | 46 |

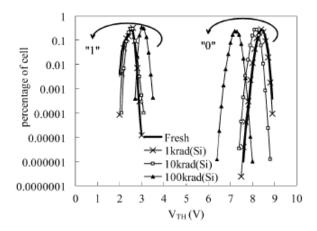

| 3.9  | TID effects on NOR                                                                                         | 47 |

| 3.10 | Sketch of the of $V_T$ distribution shift $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$               | 48 |

| 3.11 | Charge pump degradation                                                                                    | 50 |

| 4.1  | ESTEC Facility                                                                                             | 52 |

| 4.2  | Board and socket                                                                                           | 54 |

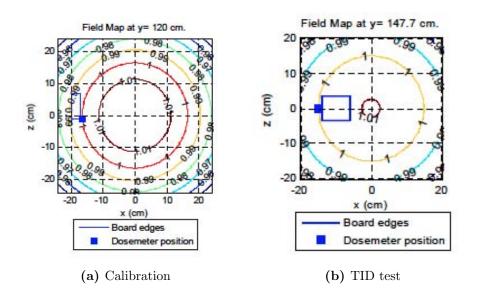

| 4.3  | Calibration setup                                                                                          | 56 |

| 4.4  | Dose rate distribution normalized to dosimeter readings                                                    | 56 |

| 4.5  | Calibration: errors build up                                                                               | 57 |

| 4.6  | Calibration: errors percentage build up                                                                    | 58 |

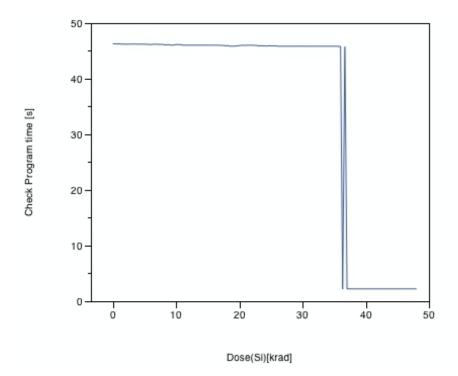

| 4.7  | Calibration: check program time                                                                            | 59 |

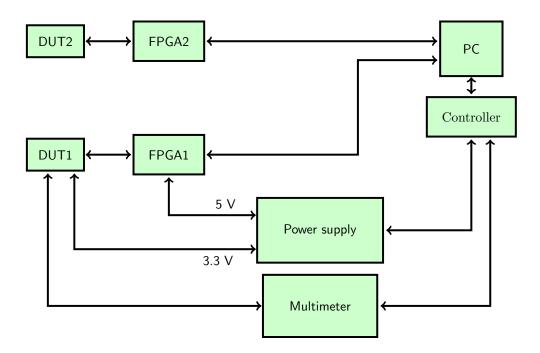

| 4.8  | TID test setup                                                                                             | 63 |

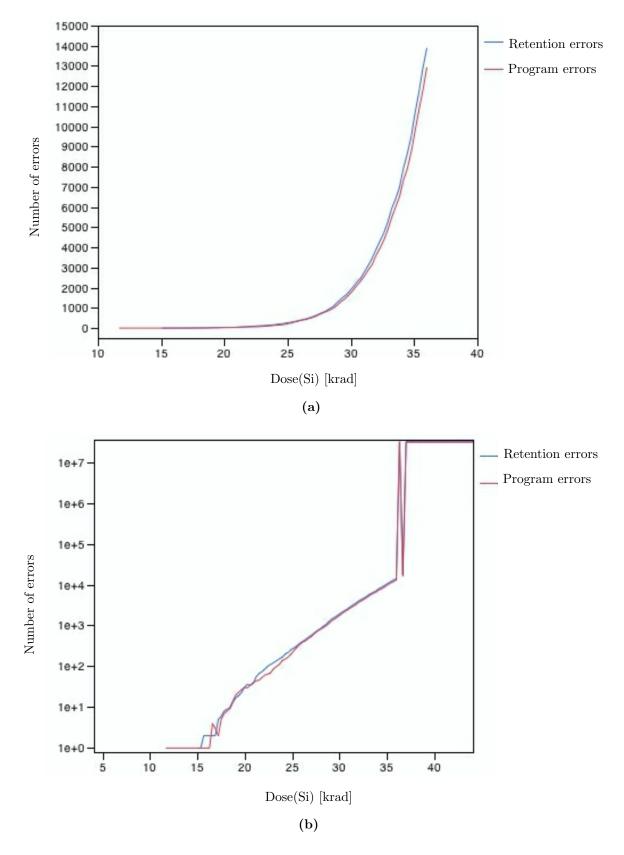

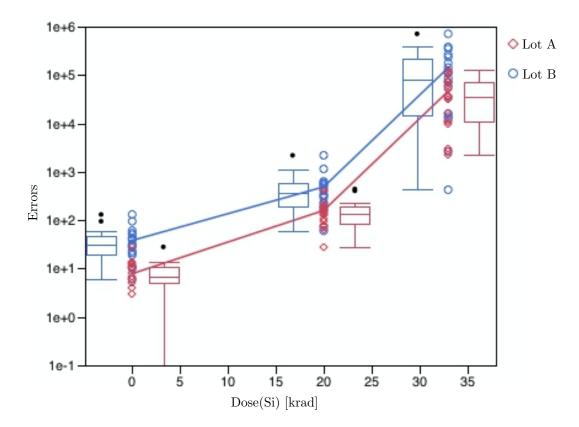

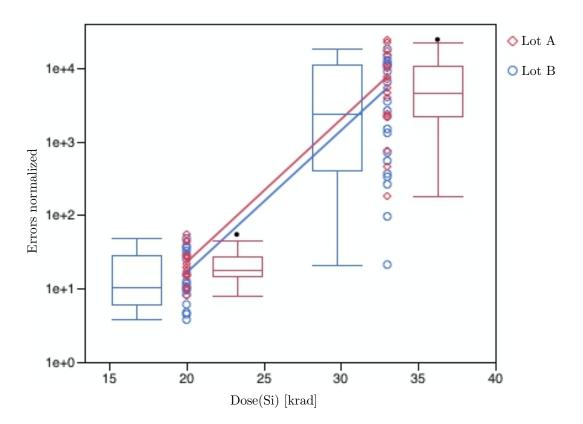

| 4.9  | Errors vs total dose                                                                                       | 65 |

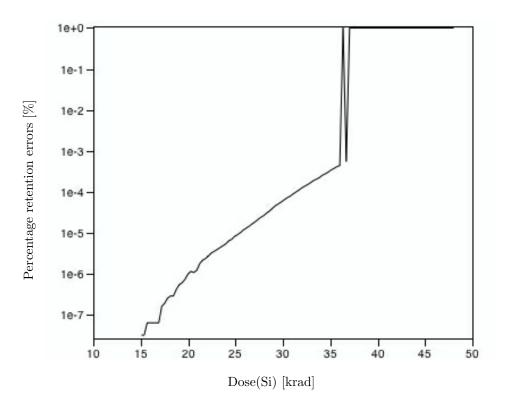

| 4.10 | Errors normalized vs total dose                                                                            | 66 |

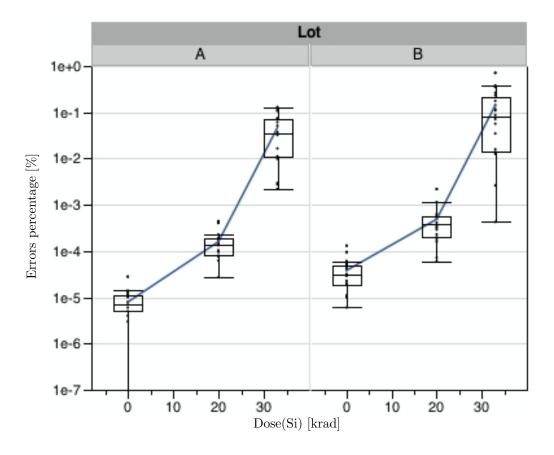

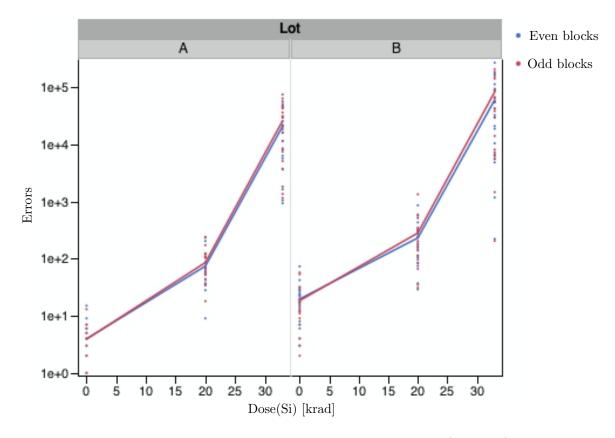

| 5.1  | Errors percentage versus total dose                                                                        | 68 |

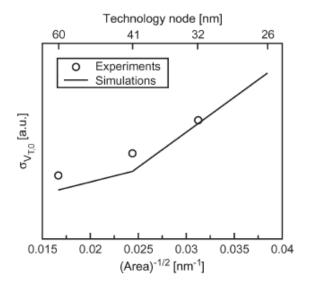

| 5.2  | $V_T$ spread vs technology node $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$           | 69 |

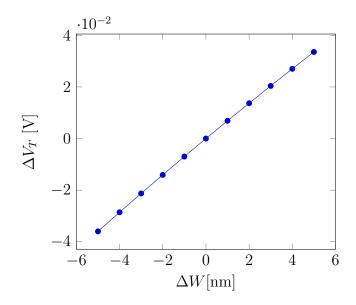

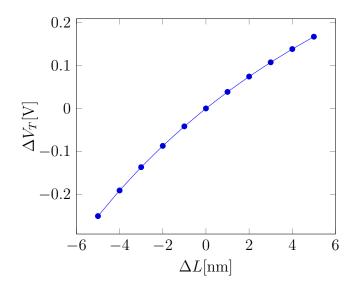

| 5.3  | $\Delta V_T$ vs $\Delta W$                                                                                 | 70 |

| 5.4  | $\Delta V_T$ vs $\Delta L$                                                                                 | 70 |

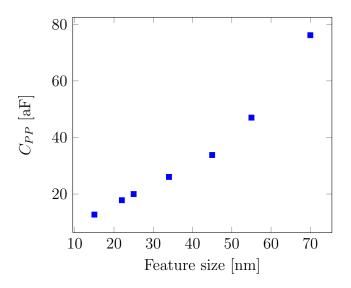

| 5.5  | $C_{PP}$ vs technology node $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 72 |

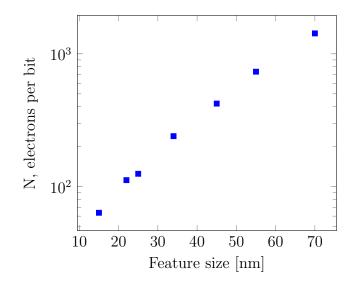

| 5.6  | Electrons per bit (N) vs technology node $\ldots \ldots \ldots \ldots \ldots \ldots$                       | 72 |

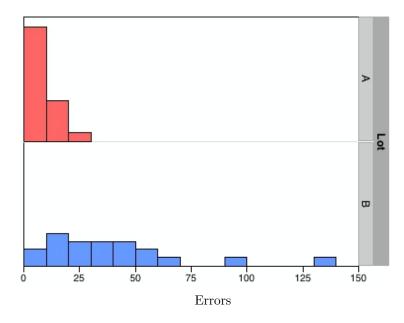

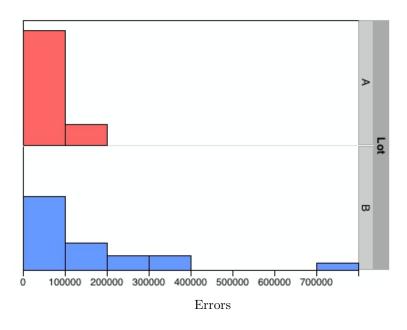

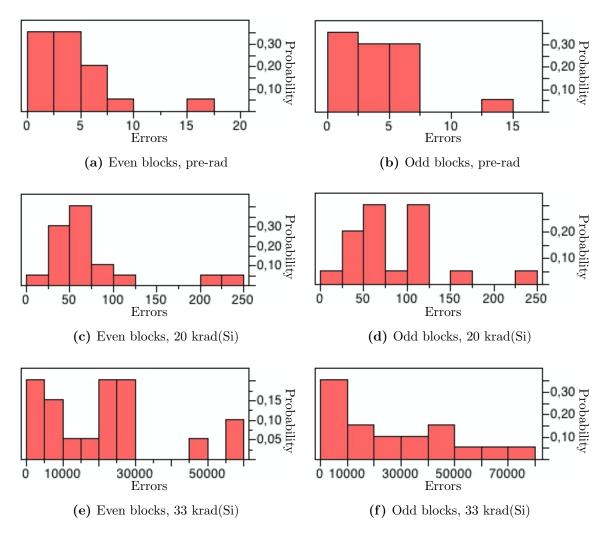

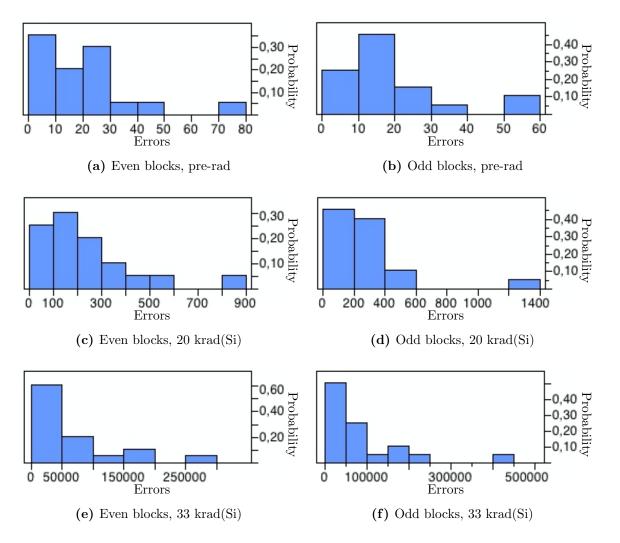

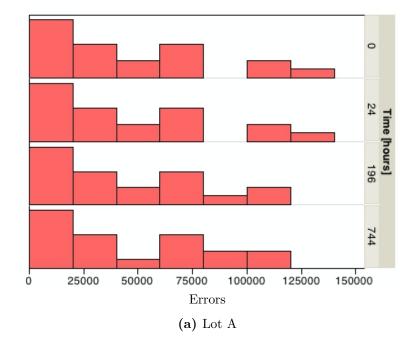

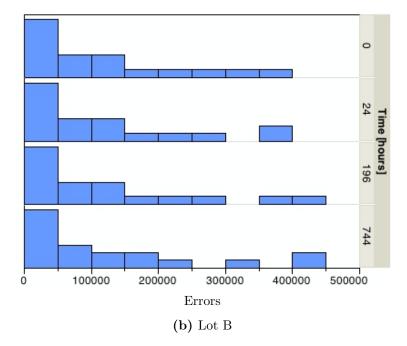

| 5.7  | Distribution of pre-rad errors                                                                             | 74 |

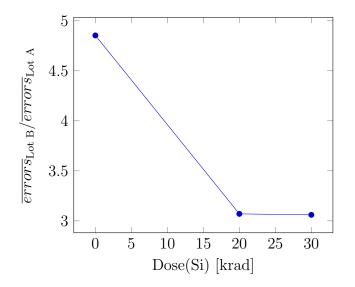

| 5.8  | Ratio of mean errors per chip                                                                              | 74 |

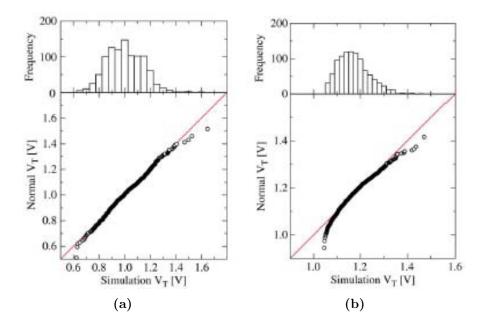

| 5.9  | Histogram and QQ of $V_T$ distribution with applied RDD and ITC.                                           | 77 |

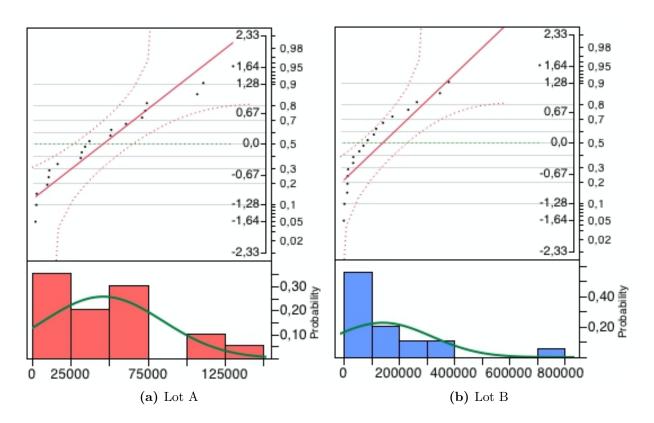

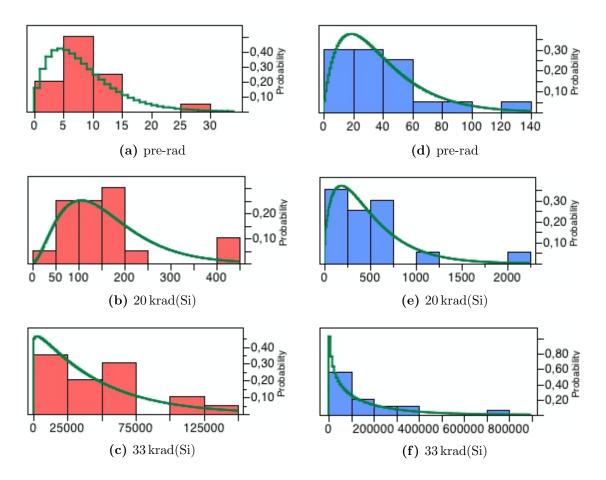

| 5.10 | Probability distribution                                                                                   | 79 |

| 5.11 | Probability distribution compared with Poisson distribution                                                | 80 |

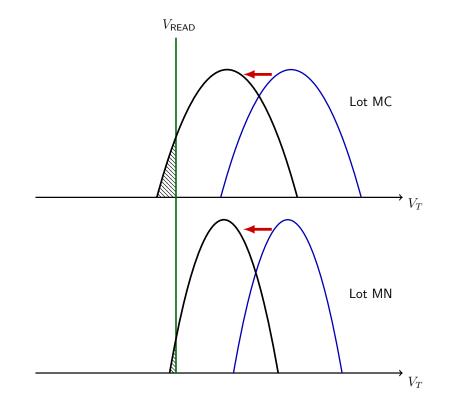

| 5.12 | Sketch of threshold voltage distribution shift                                                             | 81 |

| 5.13 | Errors distribution after a total dose of $33 \operatorname{krad}(Si)$                                     | 81 |

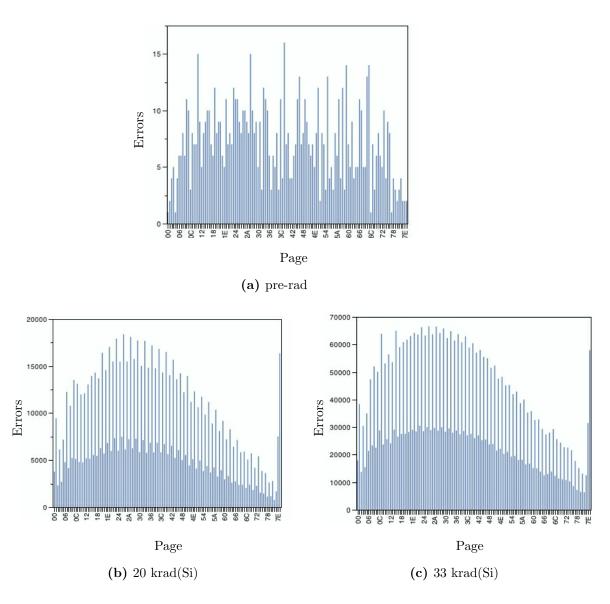

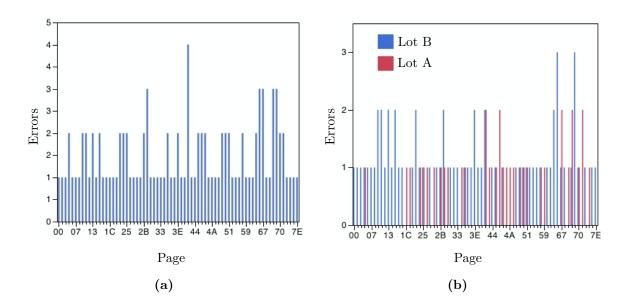

| 5.14 | Errors spatial distribution into pages                                                                     | 83 |

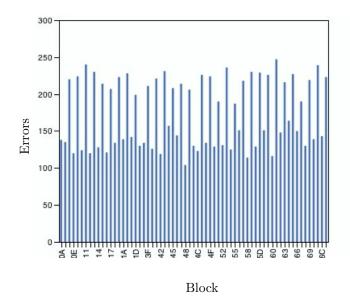

| 5.15 | Errors spatial distribution into blocks                                                                    | 84 |

| 5.16 | Even and odd blocks during calibration errors build up                                                     | 84 |

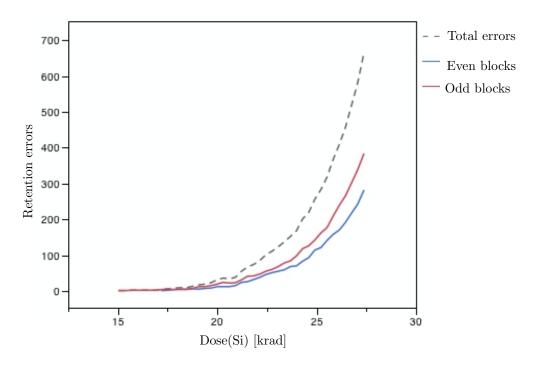

| 5.17 | Retention errors distinguishing even and odd blocks                                                        | 85 |

| 5.18 | Errors spatial distribution into pages, fresh devices                                                      | 85 |

| 5.19 | Probability distribution, even and odd blocks, Lot A                                                       | 86 |

| 5.20 | Probability distribution, even and odd blocks, Lot B                                                       | 87 |

| 5.21 | Decapped memory                                                                                            | 88 |

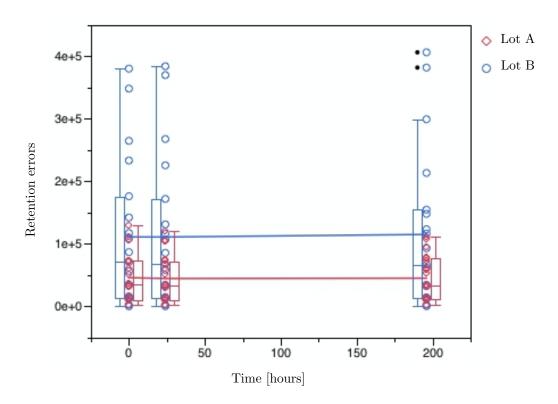

| 5.22 | Annealing errors                                   | 39             |

|------|----------------------------------------------------|----------------|

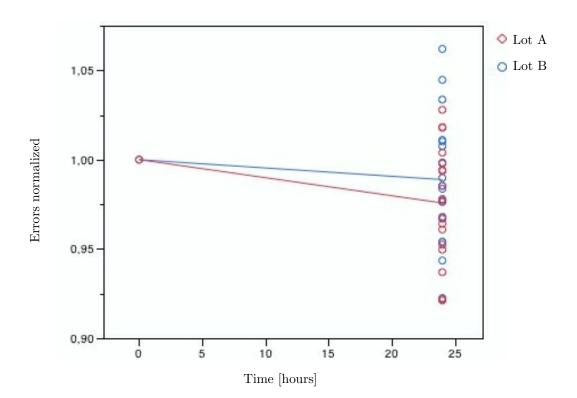

| 5.23 | Annealing, normalized errors, up to 24 hours       | 90             |

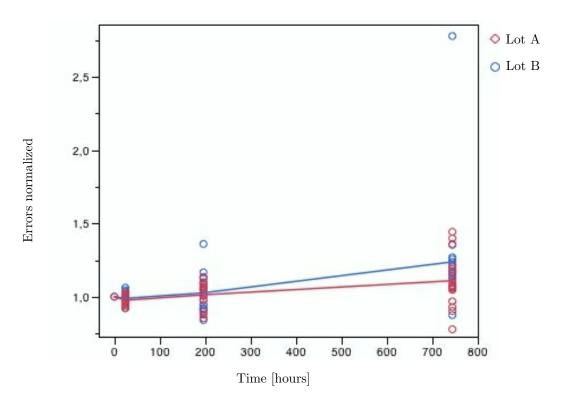

| 5.24 | Annealing, normalized errors                       | <del>)</del> 0 |

| 5.25 | Errors distribution over time                      | 93             |

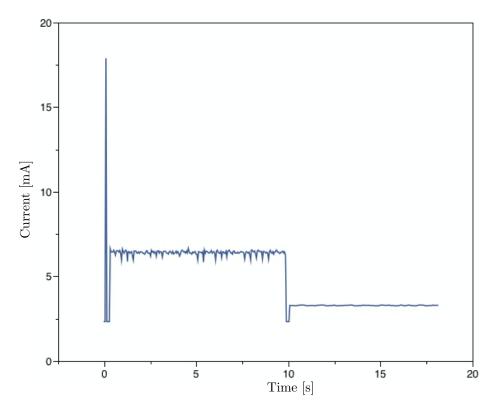

| 5.26 | Current during $E/P/R$ cycle                       | 94             |

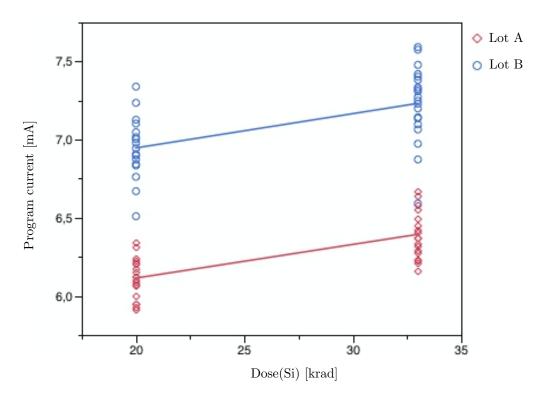

| 5.27 | Program current                                    | 95             |

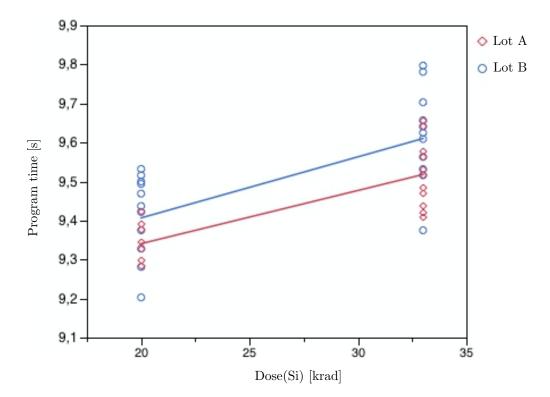

| 5.28 | Program time                                       | 95             |

|      |                                                    |                |

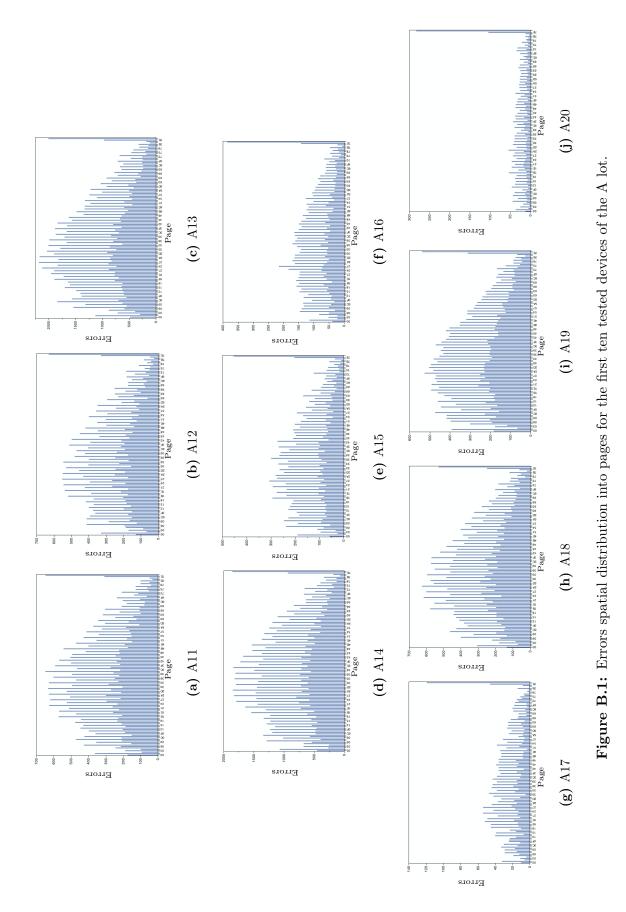

| B.1  | Errors spatial distribution into pages: A11-A20 10 | )2             |

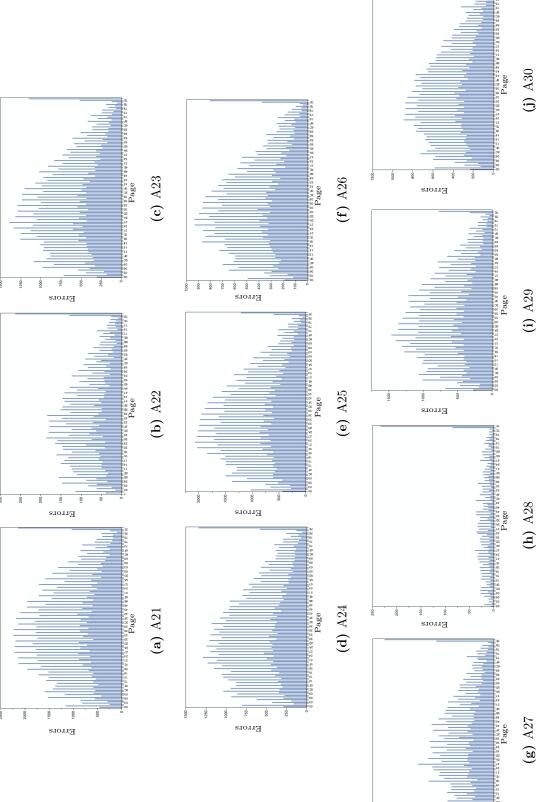

| B.2  | Errors spatial distribution into pages: A21-A30 10 | )3             |

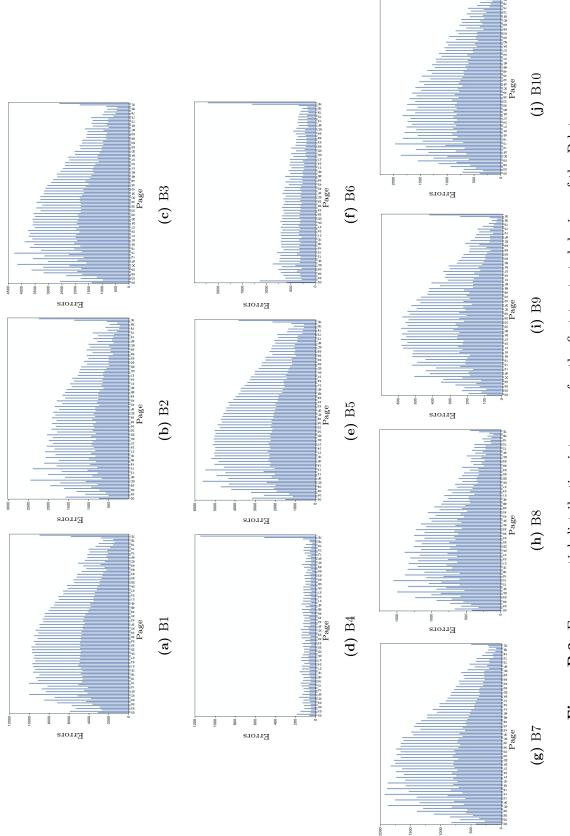

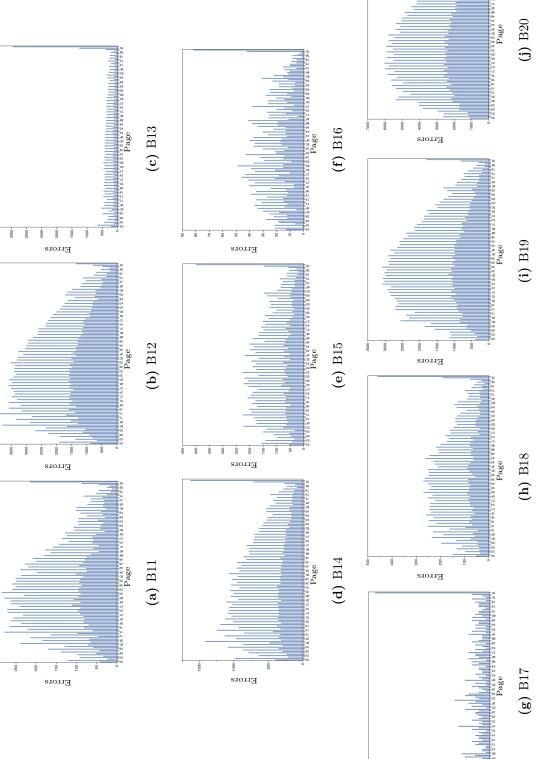

| B.3  | Errors spatial distribution into pages: B1-B10     | )4             |

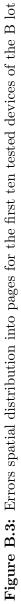

| B.4  | Errors spatial distribution into pages: B11-B20 10 | )5             |

# List of Tables

| 2.1 | Differences between NOR and NAND Flash memories | 17 |

|-----|-------------------------------------------------|----|

| 3.1 | Radiation effects in spacecraft electronics     | 40 |

| 4.1 | Details of the SLC NAND memories                | 54 |

| 4.2 | Gamma TID run on the calibration device         | 55 |

| 4.3 | Gamma TID runs during week 47 and 48            | 61 |

| 4.4 | Gamma TID runs during week 49 and 50            | 62 |

| 4.5 | Mean of errors per lot                          | 63 |

| 5.1 | QQ plot                                         | 78 |

# Chapter 1 Introduction

In this introductory chapter the main concepts and metrics of non volatile memory will be presented, just followed by a brief historical evolution of the previous technologic solutions which have lead to the Flash memory device, object of the thesis. Alternative solutions to the data storage mechanism used by floating gate devices and future technological trends will be presented.

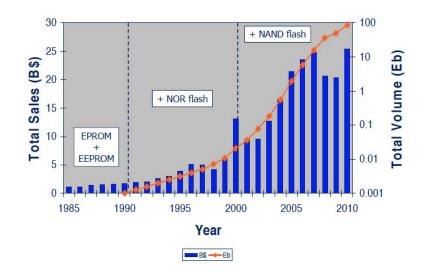

### 1.1 Non-volatile memory

A non volatile memory is a memory able to retain digital information without any power supply. This feature makes it an essential element of most systems, since critical information must be retrieved even if power is lost to the system. Non volatile memory market has been growing in the last two decades, because of the broad diffusion of portable electronic devices, such as smartphones, laptops, digital cameras and multimedia players. The huge success and market increase of Flash memories is due to their flexibility against the previous technology, read-only memory (ROM) and Programmable-ROM, but especially due to the remarkable scaling of these devices, which allowed a  $50 \times \text{cost-per-bit}$  reduction from  $1.5 \,\mu\text{m}$  (1987) to 20 nm (2012) technology nodes [1]. Flash memories combine the electrical erase from EEPROMs (electrically erasable and programmable read-only memory), which have the disadvantage to use a large area, and the high density from EPROMs, which are electrically programmable but erasable via ultraviolet exposure.

The most important connotative parameters for non-volatile memories are retention and endurance. They give the measure of how much strong is the NVMs, because this type of memory is more subject to wear-out than standard digital circuits.

**Retention** is the ability of the cell to keep the information for a long amount of time and it is measured in years. At this moment a typical value is ten years.

Endurance is the number of erase/program operations that can be executed

Figure 1.1: Non volatile memory market (Source: Micron [2])

without cell's properties degradation. It is measured in number of cycles (a typical value for floating gate memories is  $10^5$  cycles).

Other characteristics of interest for non-volatile memories are the following.

- 1. Density: the number of bits of information that may be stored on a single device.

- 2. Program or write time: the time necessary to write information into the memory.

- 3. Read time: the time necessary to read information from the memory.

- 4. Erase time: the time necessary to erase information from the memory. A peculiarity of non-volatile memories is that they must perform an erase operation before the program operation. This implies a complex peripheral circuitry and a speed penalty, because of the additional operation.

- 5. Operating power: the power necessary to perform the write, erase or read operation.

- 6. Standby power: the power consumed by the memory when no operations are being performed. In a non-volatile memory the power required to retain information is zero.

Various storage mechanisms differentiate various non volatile memories. The simplest one is the storage of a net amount of charge, whose presence or absence, different quantities or its sign represent the digital information. To this type of NVMs belong Floating Gate (FG), Charge Trap (CT), and Nanocrystal (nXTL)

memories. Phase change memories base the information storage on the phase (amorphous or crystalline structure) because of the very different behavior of these materials depending on the phase. Ferroelectrics materials use the direction of a remanent polarization (as a consequence of removal of an electric field) to make non-volatile memory bits. Instead ferromagnetic materials use the magnetoresistance, the property to change resistivity when immersed in a magnetic field. Other prototypes of storage mechanisms are under developing, but still immature to get commercialized, such as nanotube RAM, resistance RAM and Conductive-Bridging RAM [3].

### 1.2 Motivation

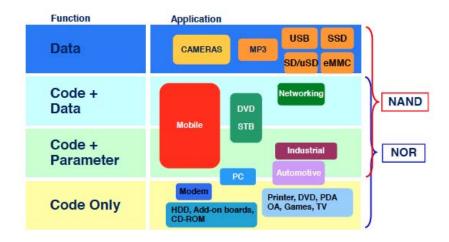

Flash memory is the most widely used non-volatile memory device today. As represented in Fig. 1.2, market application is very extended and the demand for increasing memory capacities, achieved by device scaling down, is in continuos increase. Nowadays in mainstream market are available 1 Gb NOR Flash memory manufactured in 45-nm technology, while NAND Flash memory has reached 32 Gb capacity in 25-nm, since NAND structure is characterized by highdensity array.

Figure 1.2: Applications of Flash memory device (source: Micron [2]).

Commercial NMVs are also used in space applications, since rad-hard market presently provides low capacity devices. In particular Flash memory devices are of great interest for space, because of the high-density storage and non-volatility. Obliviously, parts for space systems are subjected to reliability test, to study radiation induced effects on devices operation.

With the scaling down trends, many reliability issues have emerged, both intrinsic and radiation-related. Scaled devices have shown to be more prone to intrinsic charge loss mechanisms, such as stress induced leakage currents, erratic bits, etc. Also variability increases as cell size decreases. Several studies analyzed the variability effects on nanoscale Flash memories [4] [5] [6]. On the other hand, investigations on ionizing radiation effects have showed that in advanced Flash memory devices errors appear at lower radiation doses than in older devices.

However, the combined effect of radiation induced effects and intrinsic sources of variability is quite unexplored. This research field is very interesting in order to allow precise prediction of radiation-induced failure during space missions. The purpose of the work is to investigate the impact of variability on TID response of NAND floating gate cells. For this reason, a large number of FG cell has been tested (more than  $10^{12}$  cells), from two different lots. Statistical distribution of parameters has been analyzed, aiming at looking for variability response to TID, such as correlation between pre-rad and post-rad results.

### **1.3** Thesis Organization

The thesis is organized in 5 chapters, including the introductive chapter.

In chapter 2, a description of the floating gate memory cell and its operation principle are provided. The architecture types are presented and charge injection mechanisms are analyzed. Then, reliability issues, even related with the scaling down trend, are discussed.

Chapter 3 studies radiation effects on Flash memories. The first section introduces the basic concepts of the radiation environment. Subsequently, after an overview of the radiation effects on electronic devices, both Total Ionizing Dose and Single Event Effects on Flash memory device are explained.

In chapter 4 the experimental conditions of the TID test are provided, performed at ESTEC (Noordwijk, NL). The tested device characteristics and the test setup are described. The final section presents the results, which are analyzed in the following chapter.

Chapter 5 develops the statistical analysis of the results, providing explanation to both the cell-to-cell and lo-to-lot variability observed.

# Chapter 2 The Device

This chapter is devoted to the description of Flash memory cell. Fist of all, the operating principle of the FG cell will be exposed, thus the physic structure and the electric characteristics. Moreover two possible array organizations will be presented. Then the main reliability issues related to this data storage solution will be analyzed and discussed.

## 2.1 Floating Gate Transistor

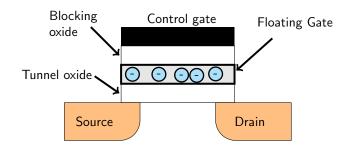

Figure 2.1: Schematic of a charge-based cell.

A Flash memory is a non-volatile memory that can be erased and reprogrammed. By the definition, a NMV cell doesn't need any power supply to retain digital values. The mechanism employed to retain the non-volatile digital information is the charge storage, for which it is necessary to create a potential well, where the charge can be confined. The basic element is the floating-gate transistor, represented in Fig. 2.1. It similar to a MOSFET, but there is an addition element, the charge storage element, placed between the silicon bulk and the gate, isolated from them by a tunnel oxide and a blocking oxide respectively. The charge storage element consists in a conductive polysilicon floating gate<sup>1</sup>, in which the charge is collected at the oxide interface or in discrete trapping sites.

<sup>&</sup>lt;sup>1</sup>For other charge-based memories, like Charge Trap (CT) and and Nanocrystal (nXTL) memories, the charge storage element is respectively a dielectric film, with high density of traps to capture charge carriers, and a layer of nanocrystals, each able to store charge.

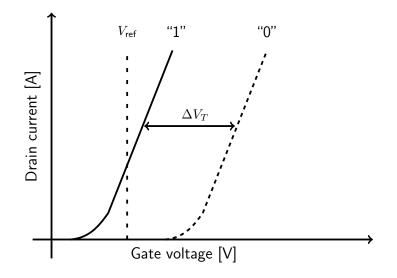

The amount of charge in the storage layer is responsible for the change of the threshold voltage of the transistor. Fig. 2.2 represents the drain current versus the gate voltage for a floating gate transistor. The left curve is obtained in the condition of a positive or no charge in the floating gate, which is called *erased*. The right curve is proper to a net negative charge in the storage element, that is the *programmed* state.

Figure 2.2: Drain current as a function of gate voltage for cell in *erase* ("1") and *program* ("0") state.

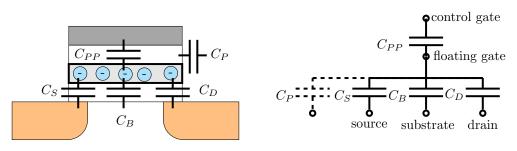

The model in Fig. 2.3 helps to understand the behavior of the FG device.  $C_{PP}$  is the capacitance between the FG and the control gate, while  $C_S$ ,  $C_B$  and  $C_D$  between the floating gate and respectively the source, the substrate and the drain<sup>2</sup>. In the condition of no charge stored in the FG:

$Q = 0 = C_{PP}(V_{FG} - V_{CG}) + C_S(V_{FG} - V_S) + C_B(V_{FG} - V_B) + C_D(V_{FG} - V_D)$  (2.1) where  $V_{FG}$  is the potential on the FG,  $V_{CG}$  is the potential on the control gate,  $V_S$ ,  $V_B$  and  $V_D$  are the potential on the source, the bulk, and the drain respectively. Defining  $C_{TOT} = C_{PP} + C_S + C_B + C_D$  as the sum of the capacitances and  $\alpha_J = C_J/C_{TOT}$  as the ratio between the capacitance on one of the four terminals and the total capacitance, it is possible to write the equation 2.1, carrying out the FG potential:

$$V_{FG} = \alpha_G \cdot V_{CG} + \alpha_S \cdot V_S + \alpha_B \cdot V_B + \alpha_D \cdot V_D \tag{2.2}$$

The floating gate results to be capacitively coupled to other terminals, therefore its potential is set not only by the control gate, but also by the other terminals and by the neighbor cells.

<sup>&</sup>lt;sup>2</sup>In this model it is not considered the capacitive coupling between neighbor cells  $C_P$

Figure 2.3: Schematic of capacitive coupling components in the FG cell.

If the source and the bulk are grounded, equation 2.2 can be rearranged:

$$V_{FG} = \alpha_G (V_{CG} + \frac{\alpha_D}{\alpha_G} \cdot V_D) = \alpha_G (V_{CG} + f \cdot V_D)$$

(2.3)

where

$$f = \frac{\alpha_D}{\alpha_G} = \frac{C_D}{C_{PP}} \tag{2.4}$$

The equations of the floating gate transistor can be obtained by substituting the MOS gate  $V_{GS}$  voltage with the  $V_{FG}$  potential and transforming the device parameters, threshold voltage  $V_T$  and conductivity factor  $\beta$  [7].

$$V_T^{FG} = \alpha_G \cdot V_T^{CG} \tag{2.5}$$

$$\beta^{FG} = \frac{1}{\alpha_G} \beta^{CG} \tag{2.6}$$

The I-V (current-voltage) characteristic equations for the floating gate transistor become:

• Triode region:  $|V_{DS}| < \alpha \cdot V_{GS} + f \cdot V_{DS} - V_T$

$$I_{DS} = \beta \left[ (V_{GS} - V_T) \cdot \left( f - \frac{1}{2 \cdot \alpha_G} \right) \cdot V_{DS}^2 \right]$$

(2.7)

• Saturation region:  $|V_{DS}| \ge \alpha \cdot V_{GS} + f \cdot V_{DS} - V_T$

$$I_{DS} = \frac{\beta}{2} \alpha_G (V_{GS} + f \cdot V_{DS} - V_T)^2$$

$$(2.8)$$

where  $\beta$  and  $V_T$  are measured with respect to the control gate.

These equations show the floating gate transistor behavior, different from a standard MOS transistor.

i) Looking at the voltage equation for triode region, the floating gate transistor can conduct current even when  $|V_{GS} < |V_T||$ , because the channel can be turned on raising the drain voltage  $(f \cdot V_{DS})$ . This is called the "drain turn-on".

- ii) While for a standard MOS in the saturation region, the  $I_{DS}$  is almost independent from the  $V_D$ , for the floating gate transistor the drain current continues to rise as drain voltage increases. The result is that no drain current saturation occurs for high drain voltage values.

- iii) The boundary between the two operation ragion is

$$V_{DS} = \alpha \cdot V_{GS} + f \cdot V_{DS} - V_T | \tag{2.9}$$

respect to

$$V_{DS} = V_{GS} - V_T \tag{2.10}$$

for the MOS transistor.

iv) The transconductance in saturation region is

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}} = \alpha_G \beta (V_{GS} + f V_{DS} - V_T)$$

(2.11)

and increases with  $V_{DS}$ , instead in conventional MOS transistors it is independent of the drain voltage.

v) The capacitive coupling ratio f depends on  $C_D$  and  $C_{PP}$  only ( $f = \alpha_D / \alpha_G = C_D / C_F G$ ), and its value in the saturation region is:

$$f = -\frac{\partial V_{GS}}{\partial V_{DS}}_{(I_{DS} = \text{constant})}$$

(2.12)

Many techniques have been proposed to extract the capacitive coupling ratio from simple dc measurements [7]. These methods require the measurement of the electrical parameters in both a memory cell and in a "dummy cell," i.e. a device identical to the memory cell, but with floating and control gates connected. By comparing the results, the coupling coefficient can be determined. Other methods have been proposed to extract coupling coefficients directly from the memory cell without using a "dummy" one, but they need a more complex extraction procedure.

#### 2.1.1 The Reading Operation

Before explaining the mechanisms that induce charge variations in the floating gate, let us show how equations 2.3, 2.5 and 2.7 become, considering a net charge  $Q \neq 0$  in the FG.

$$V_{FG} = \alpha_G V_{CG} + \alpha_D V_D + \frac{Q}{C_{TOT}}$$

(2.13)

$$V_T^{CG} = \frac{1}{\alpha_G} V_T^{FG} - \frac{Q}{C_{TOT}\alpha_G} = \frac{1}{\alpha_G} V_T^{FG} - \frac{Q}{C_{PP}}$$

(2.14)

$$I_{DS} = \beta \left[ \left( V_{GS} - V_T - \left( 1 - \frac{1}{\alpha_G} \right) \frac{Q}{C_{TOT}} \right) V_{DS} + \left( f - \frac{1}{2\alpha_G} \right) V_{DS}^2 \right]$$

(2.15)

Equation 2.14 demonstrates that the threshold voltage depends on the charge in the FG. The shift  $\Delta V_T$  is obtained subtracting to 2.14 the  $V_T$  value when Q = 0 (2.5):

$$\Delta V_T = V_T - V_{T0} = -Q/C_{PP} \tag{2.16}$$

represented in Fig. 2.2. The charge greatly affects the current level, which corresponds to the two different cell states, erased or programmed.

#### 2.1.2 Charge Injection and Removal Mechanisms

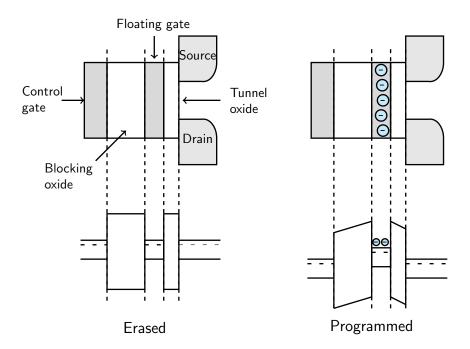

Fig. 2.4 shows the energy band diagram of the cell for the two states, erased and programmed. It is clear that the two oxide layers play a role of potential barriers, while the floating gate is a potential well. Without any charge in the storage element, the cell is in flat band condition. If the charge is stored in the floating gate, it creates a electrical field, that bends the oxide layer bands. The higher is the amount of the stored charge, the higher is the bands bend; as consequence, they become thinner.

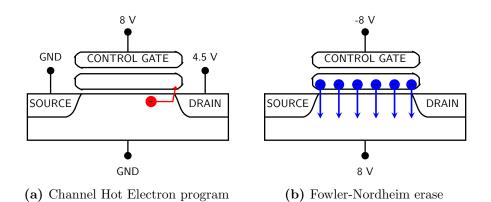

Figure 2.4: Energy band diagram for FG cell.

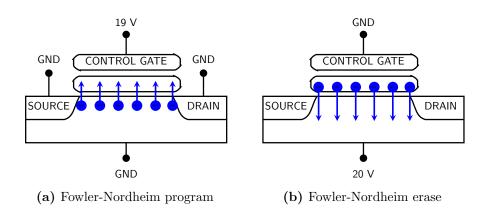

Two mechanisms perform injection (and/or removal) of the charge in the floating gate: the injection of electrons (or holes) over the potential barrier, called **Channel Hot Electron Injection** (HEI), and, through the barrier, **Fowler**- **Nordheim** (FN) tunneling. The blocking oxide, thicker than the tunnel oxide, allow us to confine the carriers in the storage element, reducing the leakage currents. It is formed by three-layer Oxide Nitride Oxide (ONO) structure, where a thin film of  $Si_3N_4$  is placed between two  $SiO_2$  layers. On the other hand, the tunnel oxide is made of high quality  $SiO_2$ .

#### **Channel Hot Electron**

When a carrier is traveling from source to drain, it is powered by the electric field and it interacts with the lattice, losing its energy throughout lattice vibrations. If the electric field is high enough<sup>3</sup>, electrons are not in dynamic equilibrium with the lattice as for low fields, and a fraction of them can gain enough energy to jump over the potential barrier and be injected into the floating gate. Three conditions are necessary for electrons to overcome the potential barrier:

- 1. the electron potential energy must be higher than the potential barrier;

- 2. it must be directed toward the barrier;

- 3. the field in the oxide must be directed to collect the charge.

To evaluate how many electrons could overcome the barrier, we must analyzed the energy distribution  $f_E(\varepsilon, x, y)$  as a function of the lateral field  $\varepsilon$ , the momentum distribution  $f_k(E, x, y)$  as a function on electron energy E, the shape and heigh of the barrier and the probability that an electron with energy E, wave vector k and distance from the Si/SiO<sub>2</sub> interface will overcome the barrier. Each function must be defined along the entire channel. The model becomes more complex considering the impact ionization, which is a second important energy loss mechanism.

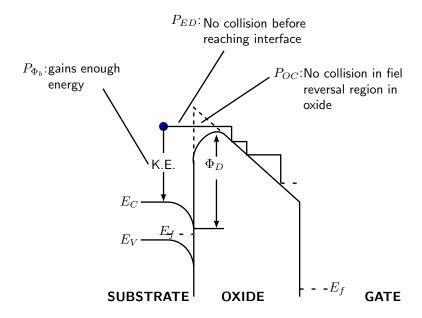

The HEI current can be explained introducing the "lucky electron" model. With this approach, the injection mechanism is attributed to the probability of an electron "lucky" enough not to be scattered during its travel in the electric field  $\varepsilon$ , gaining enough energy to jump over the barrier. The total probability of the event is the sum of three probabilities of the following events [7].

- 1. The carrier has to be "lucky" enough to acquire enough energy to jump over the barrier and to retain its energy after the collision that directs it toward the interface  $(P_{\Phi_b})$ .

- 2. The carrier traveling path from the direction point to the interface must be without collisions  $(P_{ED})$ .

<sup>&</sup>lt;sup>3</sup>For fields exceeding the value of  $100 \,\mathrm{kV/cm}$  [8].

3. The carrier can surmount the repulsive oxide field at the injection point, due to the Schottky barrier lowering effect, without collision in the oxide  $(P_{OC})$ .

This is a simple model that is in quite good agreement with simulation results, even if not very accurate.

Figure 2.5: Energy band diagram describing the three processes in involved HEI.

Another model to explain HEI, more rigorous than the previous, is based on the quasi-thermal equilibrium [9].

In both models the relation between the substrate current  $I_{sub}$  and the injection current  $I_G$  is

$$I_G/I_{ch} \sim I_{sub}/I_{ch}e^{-\Phi/\Phi_i} \tag{2.17}$$

where  $I_{ch}$  is the channel current,  $\Phi_i$  is the impact ionization energy and  $\Phi$  is the energy barrier seen by electrons to be injected in the oxide.

The substrate current is composed of holes generated by impact ionization close to the drain voltage. Holes are always generated since the energy ionization threshold  $\Phi_i$  (~1.6 V) is lower than the injection energy barrier  $\Phi$  (~3.2 V). Some holes can acquire enough energy from the lateral electric field to be injected in the oxide, degrading it. The ionization process generates a lot of carriers that can be injected in the oxide and be trapped at the interface, producing interface states, thus degrading the device performance.

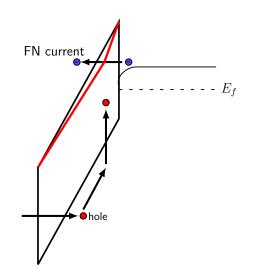

Figure 2.6: FN tunneling throught a potential barrier in a MOS structure.

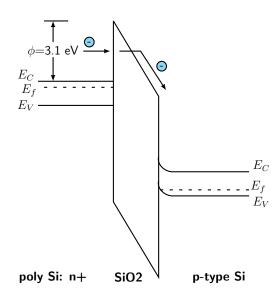

#### Fowler-Nordheim Tunneling

Fowler-Nordheim tunneling can be explained through the quantum mechanic, according to an electron is able to penetrate a potential barrier, and the probability that this could happen depends on the distribution of the occupied states in the injecting material and on the height, width, and shape of the barrier. The tunneling process in an MOS structure is represented in Fig. 2.6. A negative bias is applied to the metal electrode with respect to the p-type silicon substrate. The following equation describes the tunneling current density:

$$J = A \cdot E^2 \cdot exp\left(-\frac{B}{E}\right) \tag{2.18}$$

where E is the oxide electric field, A and B are constants related to the Si/SiO<sub>2</sub> barrier heigh:

$$A = \frac{q^3 \cdot m_0}{16\pi^2 \cdot \hbar \cdot m_{\text{ox}}\phi} \qquad B = \frac{4 \cdot \sqrt{2 \cdot m_{\text{ox}}} \cdot \phi^{3/2}}{3 \cdot \hbar \cdot q} \tag{2.19}$$

where  $m_0$  and  $m_{ox}$  are the electron effective mass in vacuum and in SiO<sub>2</sub> respectively,  $\phi$  is the Si/SiO<sub>2</sub> barrier height, q the elementary charge, and  $\hbar$  the reduced Planck's constant. It should be noted that the Fowler-Nordheim current is a function of the oxide field, and not of the applied gate voltage, but the mechanism can happen only if the oxide field is high enough, thus a gate voltage high enough is applied. In particular the following equation must be satisfied:

$$E \ge \frac{\phi}{q \cdot t_{\rm ox}} \tag{2.20}$$

being  $t_{\rm ox}$  the oxide thickness. An optimum tunnel oxide thickness of about 10 nm

is a tradeoff between performance requirements, such as programming speed and power consumption, and reliability constraints, which would require thick oxides, to avoid large tunnel current density. In fact, remembering that the oxide electric field is roughly equal to the applied voltage divided by  $t_{\rm ox}$ , since the tunnel current is exponentially dependent on the oxide electric filed (Fig. 2.7), an increase of few MV/cm leads the current density to rise some orders of magnitude [7]. This could be a critical problem concerning process control, because a very small variation in the tunnel oxide thickness among the cells belonging to the same array produces a great difference in programming and erasing current. For this reason, a very good process control is required. The result is the threshold voltage distribution spread. This mechanism is more efficient than CHE, but slower.

Figure 2.7: FN tunnel current as a function of the electric field [10].

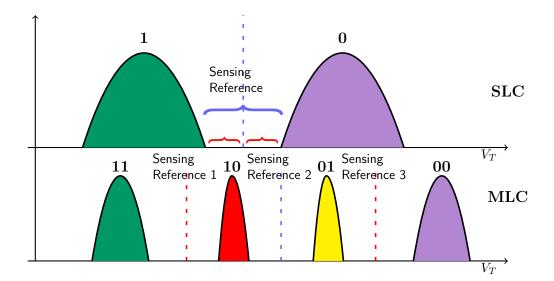

#### 2.1.3 Threshold Voltage Distribution

The large array organization of the cells leads to a wide distribution of the parameters. The threshold voltage distribution for each state, pictured in Fig. 2.9 should be as narrow as possible, but in general it has a Gaussian shape, even larger if no constraining algorithms are applied during program and erase operations. For this purpose, two reference levels are introduced, the program verify and the erase verify levels. The program/erase algorithms ensure the cell threshold voltage is beyond the erase verify level after an erase operation, and above the program verify level after programming.

Programming is obtained by applying pulses to the control gate and to the drain simultaneously, when the source is grounded. This operation can be performed selectively by applying the pulse to the word line (connected to gates) and biasing the bit line (connected to drain). The threshold voltage of the cell shifts to higher value because of the negative charge injected in the floating gate. The width of the programming pulse influences the amount of carriers injected, thus the threshold voltage shift [7]. Both temperature and drain voltage have an effect on threshold voltage shift: higher temperature reduces the number of electrons available for injection in the FG, increasing the programming time, and  $V_T$  depends linearly on the drain voltage.

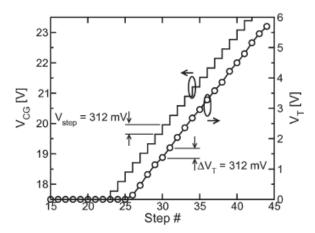

Accurate programming of Flash memories is usually obtained by the incremental step pulse programming algorithm (ISPP), consisting in the application to the cell control gate of short programming pulses of equal duration and increasing amplitude. The constant increase  $V_{\text{step}}$  of the control gate pulses drives to a very tight threshold voltage distribution, thus the  $V_T$  variation per step ( $\Delta V_{T,\text{step}}$ ) rapidly converges to  $V_{\text{step}}$ . After each program pulse, a verify operation is inserted:  $V_T$  is sensed and compared to a verify level. If it exceeds the program verify (PV) level, the algorithm stops and the program operation is concluded; otherwise another control gate step is applied to the memory cell. The purpose of the method is to induce small variations of the cell  $V_T$  by transferring small charge packets from the substrate to the floating gate. However, due to cell size scaling, the number of electrons controlling the cell state has critically decreased, so that a very low number of electrons are transferred during each voltage step. This is one of the new issues related to device scaling, introducing a spread in the final  $V_T$  distribution. To overcome this problem a double-verify (DV) algorithm has been introduced [11], able to get thinner  $V_T$  distribution in presence of electron injection statistic (EIS), which will be further presented.

The erase operation requires a high voltage pulse to be applied to the source, while control gates (connected to WL) are grounded and drains (connected to BL) floating. Before the operation, all the cell are programmed with the same threshold voltage value. After the erase pulse, the threshold voltage shift to lower values depends on the applied source voltage value: each volt reduction corresponds a one-order-of-magnitude increase in erasing time.  $V_T$  depends on the oxide thickness too. If two FG cells with the same oxide thickness have different threshold voltage values while programmed, after the erase they will have the same threshold voltage. Since, in large array, FG transistors can have little oxide thickness differences, after erasing there is a read operation to check if all the cells are erased or not. If not, another erase pulse and check operation are applied. The algorithm will de repeated until all the cells' threshold voltages are below the erase verify level. The final erased  $V_T$  has a Gaussian shape (Fig. 2.9).

Figure 2.8: Control-gate voltage waveform used to program a NAND cell and resulting VT transient on a 60-nm device. Note that only positive  $V_T$  values can be sensed in our NAND array [12].

Figure 2.9: Threshold voltage distribution for SLC (above) and MLC (below) memory.

Depending on the number of bits stored for each cell there are two possible architectures.

- Single Level Cell (SLC): is the simplest one, because each cell stores a single bit, "1" or "0".

- Multi-Level Cell (MLC): modulating the amount of charge in the FG, each cell can store multiple bits. The reading/erasing/programming operations are complex because of the threshold voltage distributions are thinner than in SLC devices. For this reason MLC memories are slower and less robust, but it is possible to double the memory density. The output levels must not be necessarily a power of 2, in fact it is possible to store 1.5 bit per cell, resulting 3 output levels. In the present market, memories with up to 4 bits per cell are available.

## 2.2 Array Organization

Flash memories take advantage of the electrical erase from EEPROMs and the high density from EPROMs, since the erase operation is performed in blocks and there is not the selection device (necessary in EEPROMs), achieving high density arrays. Furthermore Flash memories are very fast because of the intrinsic parallelism.

Depending on data access and data write organizations, there are mainly two types of architecture for Flash memories.

- **NOR**: the first in time to be developed, used in permanent data storage or rarely modified data; this architecture is convenient for code storage.

- **NAND**: different respect to NOR because of the array organized in serial chain of cells, convenient for data storage.

Tab. 2.1 resumes the differences between NOR and NAND-type Flash memories.

In this thesis, devices under investigation are NAND Flash memories, which are experiencing a dramatic increase in demand thanks to their high density storage. However also a NOR architecture description will be provided.

#### 2.2.1 NOR Architecture

The NOR array organization is shown in Fig. 2.10. Each cell has the source grounded through the source line and the drain shorted in the bit line, common to many cells.

| NOR Flash Memory               | NAND Flash Memory         |

|--------------------------------|---------------------------|

| Cell size = $10F^2$            | Cell size = $4F^2$        |

| Random access                  | Serial access             |

| Slower Program/Erase           | Faster Program/Erase      |

| CHE programming                | FN tunneling programming  |

| Byte/Word Program, Block Erase | Page Program, Block Erase |

| Lower density                  | Higher densiry            |

| Code storage applications      | Data storage applications |

Table 2.1: Main differences between NOR and NAND Flash memories.

Figure 2.10: Flash NOR architecture

Figure 2.11: Program (a) and erase (b) in NOR architecture

For the read operation, the cell address has to be provided to the row decoder and the column decoder. The row decoder selects the word line, raising its voltage. The bit line, selected by the column decoder, and its current, measured by a sense amplifier, will be significant if the cell is in the erased state, because the threshold voltage is under the read voltage. If no current is sensed, the cell is in the programmed state.

For programming and erasing operations, the word line selects the cell subject to the operation. Program is carried out by channel hot electron injection: the high current needed for this mechanism limits the parallelism of the operation. Supposing that "0" is the data to be written, the bit line will drive a high voltage, to allow the channel hot electron injection in the FG and consequently to increase the threshold voltage.

Erase is performed by FN tunneling. This operation is complex, first of all because it is applied on an entire section, secondly because the threshold voltage of some cells must be checked, to avoid too low values and, in case, to raise the threshold voltage to higher value. A high electric field must be applied between source and gate, to allow the carriers to flow out from the floating gate throughout FN tunneling.

The bit size is ~  $10 \text{ F}^2$ , where F is the feature size of the technology, therefore NOR cells can not be made smaller than ~  $10 \text{ F}^2$ . This limit is imposed by the difficulty of scaling the gate length, associate to the HEI mechanism for programming, and the array organization with a drain contact shared for each couple of cells. The consequence is a fast random access, about 100 nm, and a slow program operation, carried out at word level, about 5  $\mu$ s. The erase operation too is slow, performed at block level, typically 100 ms. With these time performances, NOR memory is use as read-mostly memory, with rare necessity of programming or erasing.

In NOR architecture the manufacturer guarantees that each single bit is functional and complies retention and endurance requirement. No ECC (Error Correction Code) must be implemented by the user. Typically there are different buses for code and data.

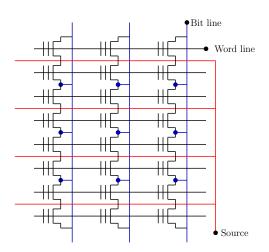

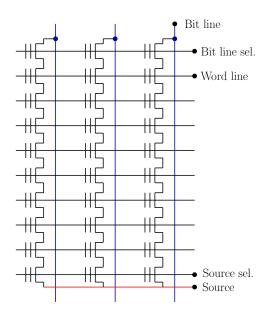

#### 2.2.2 NAND Architecture

The base element of the NAND architecture is not the single cell, but a serial chain of 16 or 32 floating gate transistor, each string connected to the Drain Selection line (DS) and to the Source Selection line (SS). Several strings are connected to the same bit line. The elimination of the shared drain contact between cells and the scaling of the channel length, because of the different injection mechanism (FN tunneling), allows to achieve a smaller area respect to NOR arrays. In

fact the bit size is  $4 F^2$ .

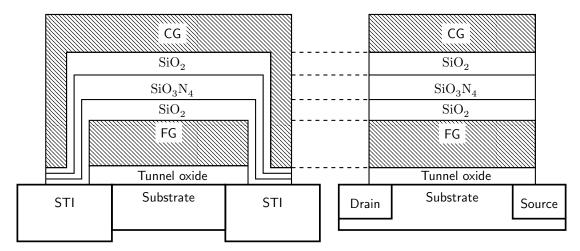

Figure 2.12: Flash NAND architecture

During reading operation, the selected cell has 0 V applied at the control gate, while other cells in series are biased at a voltage  $V_{PASS}$ , that is higher than the programming  $V_T^4$ , so that string current is determined only by the  $V_T$  of the selected cell. The sense amplifier, placed at the end of the bit line, will detect current only if the selected transistor has a negative threshold voltage, so it is in the erased state. An entire page is read at once in a single parallel operation.

Both program and erase operation use FN tunneling (with opposite polarity), that is more efficient than HEI, then currents are smaller and it is possible to reach a great level of parallelism. Program is performed at page level, applying positive voltage to the control gate, which capacitively couples to the FG and induces electrons to tunnel up from the channel. Erase operation is executed at block level, removing electrons by reversing the bias. Programming takes about 0.2 ms, erasing about 2 ms. This array organization makes NAND structure suitable for data storage, where random access is relatively important and latency is not critical.

An external ECC is indispensable because manufacturer does not guarantee each single bit and bad blocks are not infrequent in commercial devices. A block is defined bad block when it contains at least one page that has more bad bits that can be corrected by the minimum required ECC. The manufacturer specifies the minimum number of valid blocks (NVB) of the total available blocks, which will not fall below NVB during the endurance life of the memory. However, thanks

<sup>&</sup>lt;sup>4</sup>In case of MLC,  $V_{PASS}$  is higher than the highest programming  $V_T$  level.

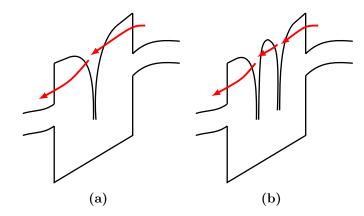

Figure 2.13: Program (a) and erase (b) in NAND architecture

to ECC, NAND Flash memory devices containing bad blocks, can be used quite reliably. ECC increase the latency, but allow to realize more scaled devices.

### 2.3 Reliability

Reliability of floating gate devices is a very complex problem, because of numerous factors that influence the two key parameters, endurance and retention, which give a measure of the quality of the device. Reliability aspects pose the most challenging questions for modeling, at both single-cell and array level.

There are two main categories of reliability mechanisms:

- intrinsic mechanisms, due to defects in the device structure, can affect all the cells in a uniform way and can be studied on single cell in test structures;

- single-bit mechanisms, due to extrinsic defects or to unfortunate configurations of intrinsic point defects, which occur in few cells.

In the following section will be summarized the most important factors responsible of reliability degradation in Flash memories, both intrinsic failure and statistical effect due to single-bit mechanisms.

#### 2.3.1 Retention

Retention is critical in any NVM device, since the ability of retain information without power supplied is the definition of non-volatile memory. Manufactures define data retention time, for which the device is assured to retain the stored charge. A typical benchmark for Flash memories is 10 year, thus the device should not lose more than a small fraction of its carriers for 10 years. The charge loss in the retention state is determined by tunneling leakage currents throughout dielectrics, which could be amplified if the dielectric contains defects. Fast program and erase operations require high voltages and current through thin oxides, which are easily degraded. Let illustrate three intrinsic mechanisms that lead to charge loss or charge gain.

The fiel-assisted electron emission consists of the move of one or more electrons from the floating gate to the oxide interface, and from there they can tunnel in the substrate, resulting a charge loss. If the cell is erased, the opposite injection can happen. The probability that the electron could tunnel from the floating gate to the substrate depends on the drop voltage between FG and substrate, and the FG potential depends on control gate potential, throughout the coupling coefficient between control gate and floating gate  $\alpha_G$ . Thus the leakage current produced depends on  $\alpha_G$  and on the stress level. The charge Q stored in the FG decreases as  $\alpha_G$  decreases, because the electron injection during programming is less efficient, or as level stress increases, because this causes more negative charge trapped in the oxide. The leakage current depends exponentially on the electric field<sup>5</sup> around the FG, which is proportionally to the charge Q:

$$E = \frac{Q}{2\epsilon_{\rm ox}\sigma} \tag{2.21}$$

where  $\sigma$  is the floating gate area.

The **thermodynamic emission** is a mechanism of carriers emission from the FG, above the potential barrier. This phenomenon is negligible at room temperature, while become relevant at high temperature.

The last is the **electron detrapping** in the gate oxide, producing charge loss, thus threshold voltage reduction.

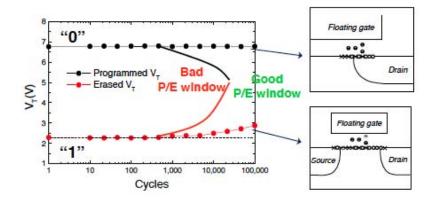

#### 2.3.2 Endurance

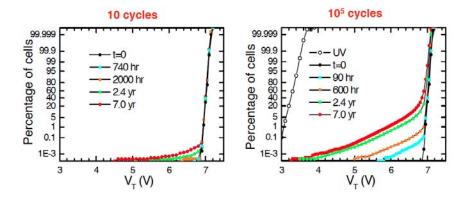

Flash memory is required to retain its properties on being subjected to repeated program/erase cycles. However when oxides are repeatedly stressed at high fields, interface and bulk traps develop in the dielectric. Program/erase cycles cause uniform degradation of the cell performance and limit the Flash memory endurance. Fig. 2.14 shows the result of an endurance test on a single cell. The variations of program and erase threshold voltage give a measure of the oxide aging.

The increase of erase  $V_T$  over cycles is due to the generation of negative traps, whole the reduction of the program  $V_T$  is attributed to oxide traps and interface

<sup>&</sup>lt;sup>5</sup>Because in a tunneling mechanisms, the current density is  $J = AE_{ox}^2 exp(\frac{-B}{E_{ox}})$

states generation. The variation of the threshold program/erase voltage level, thus the "window" closure is the result of three effects:

- variation of the transistor  $V_T$ , measured at the floating gate;

- oxide conduction variation;

- transconductance degradation, leading to higher  $V_G$  for the same  $I_D$ .

To prevent program/erase window closure is indispensable the optimized cell design. Flash memories are typically expected to least 100,000 program/erase cycles without wearing out. However, multi-level cells have lower endurance benchmarks, because of a stringent threshold voltage window.

Figure 2.14: Threshold voltage window closure as a function of program/erase cycles on a single cell, showing endurance characteristic [2].

#### 2.3.3 Statistical Effects

Multiple sources of statistical variability affect the FG cell threshold voltage, thus the array reliability during program, erase and data retention, which are associated with the discreteness of the charge. These variability sources increase their impact on  $V_T$  variability as technology scaling proceeds.

First of all, the statistical distribution of defects in the cell tunnel oxide leads to RTS, SILC and erratic bits. In addition, the cell-to-cell parameter variation, due to a more critical process control, introduces a great variability. Finally, the miniaturization of the area leads to a reduction of the dopants and of the electrons transferred to/from the floating gate to change the cell state, making the discreteness of the matter a fundamental source of statistical variability.

This paragraph is devoted to the brief description of sources of statistical variability.

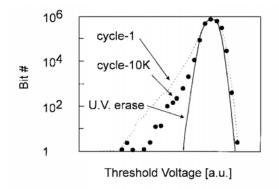

#### **Over-erasing**

In Flash memory each erasing is actually formed by a series of elementary erase operation. After the first erase pulse, an algorithm checks if the operation is completed, controlling the threshold voltage. The verification of the complete erasure of all the cell belonging to the same block, which can be very large, is one of the biggest issues in Flash technology. The threshold voltage distribution of the erased state spreads around an average voltage, with a shape like Gaussian, but it is not symmetrical toward lower values (Fig. 2.15). A very small percentage of the cells has a very large threshold voltage variation, and these few cells have an high relevance. The erasing speed of these cells is too high respect to the other cells. Since all the cells are erased simultaneously, the time required to erase the slowest may be long enough to over-erase the fastest cell. If the over-erased cells exhibit a negative or zero threshold voltage, all the cells connected to the same bit line would be read as "1" independently of they actual content. The population

Figure 2.15: Threshold voltage distribution after different erase procedures: UV erase, after the first cycle and after 10 K cycles [7].

related to faster cells is too large to be attributed to extrinsic defects, and it is supposed to be due to statistical fluctuations of oxide charge and to the structure of the injecting electrode [13]. Positive charges in the tunnel oxide and irregular polycrystal grains may induce a local increase of the electric field, making some cells to be erased faster than average. This physical explanation is consistent with the tail behavior after programming/erasing cycles.

#### Erratic Bits

A relevant mechanism of single bit failure during programming/erasing cycles is the occurrence of an "erratic bit". Such bits show an unstable and unpredictable behavior in erasing, since its erase threshold voltage changes randomly from cycle to cycle, from the center of the Gaussian shape distribution to the lower part of

Figure 2.16: Erratic bit due to hole trapping.

the tail. This behavior is ascribed to an hole trapping/detrapping in the tunnel oxide. It has been demonstrated [14] that the statistical distribution of hole traps give a low but finite probability of having clusters of two or more positive charges whose combined electric field effect induces a huge increase in the tunnel current. Trapping/detrapping of a single positive charge cause a detectable change in the erase speed, leading to over-erase failures. Since this behavior is due to statistical fluctuations of intrinsic oxide defects, erratic bit events can be reduced by process optimization, but not completely eliminated. They are menaged by internal algorithm and ECC.

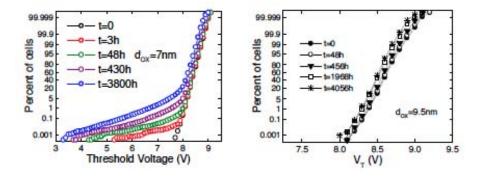

#### Stress Induced Leakage Current

One of the effect of trap generation in the oxide is the Stress Induced Leakage Current (SILC), that appears as a gradual and continuos increase of the leakage current. It is characterized by an uniform conduction across the whole oxide area, due to neutral trap generation inside the insulating layer caused by electrical stress. Different components contribute to SILC, that were classified by K. Sakakibara *et al.* [15] [16] [17]. The *DC* component is the predominant for 10 nm-oxide, such as tunnel oxide in FG memories. This component is modeled by a trap-assisted tunneling (TAT), pictured in Fig. 2.19. The electrical stress generates neutral defects uniformly distributed across the whole oxide area. These defects allow the trap assisted tunneling of electrons. SILC is proportional to the defects concentration and the trap-assisted tunneling probability. The strong dependence of SILC on the number of program/erase cycles is pictured in Fig. 2.17. The reduction of the oxide thickness reduces the distance between the neutral defects and the oxide interface, raising the probability that traps could capture

or emit electrons. In Fig. 2.18 it is show the threshold voltage distribution of two samples of the same lot, but with different oxide thickness. During retention the  $V_T$  shift is higher for the sample with the thinner oxide.

Figure 2.17: Effects of cycling on SILC. Data retention test at room temperature [2].

Figure 2.18: Effects of tunnel oxide thickness on SILC.  $V_T$  distribution of two sales from the same lot, but with different tunnel oxide thickness [2].

There are various theories on the origin of the neutral traps responsible of the SILC.

- Hydrogen-induced defects: an hydrogen atom is captured in an oxygen vacancy, this compound forms a hydrogen bridge<sup>6</sup> for electrons.

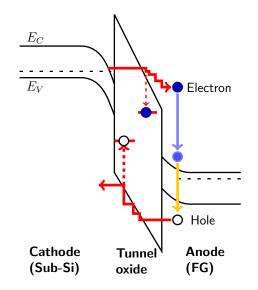

- Anode Hole Injection (AHI): electrons with high kinetic energy injected into the floating gate cause anode hole generation in the floating gate (Fig. 2.20), which leads to degradation of the cell, such as threshold voltage shift and, ultimately, the breakdown [18].

- The third model [19] includes both holes and hydrogenous species. Holes, generated and injected into the oxide, can be trapped or react with Si-H

<sup>&</sup>lt;sup>6</sup>The hydrogen bridge is a complex of a hydrogen atom and an oxygen vacancy: the hydrogen replaces an oxygen atom and the structure can be positively, negatively or neutrally charged depending on the electrons trapped (none, two or one respectively).

Figure 2.19: Trapped-assisted tunneling.

bonds in the dioxide layer, producing hydrogen release, according to the following reaction:

$$Si-H + h^+ \rightarrow Si + H^+$$

$Si-H + h^+ \rightarrow Si^+ + H$

The first forces will lead to the release of positive hydrogen ions, while the second the release of neutral hydrogen atoms. The mobile hydrogen can then drift or diffuse towards the interface, where it can break a Si-H bond and create an interface trap, according to one of the following reactions:

$$\begin{split} \mathrm{Si-H+H^++e^-} &\rightarrow \mathrm{Si+H_2} \\ \mathrm{Si-H+H} &\rightarrow \mathrm{Si+H_2} \end{split}$$

Hydrogen and hydrogen-related compounds are present in the silicon dioxide, because the oxide is grown in  $H_2O$  ambient and because H is used to passivate the silicon dangling bonds at the interfaces. All these mechanisms well explain the defect generation and they may all contribute simultaneously to produce traps involved in SILC.

Anomalous SILC than can not be explained with the trap assisted tunneling (TAT) mechanism have been attributed to two trap assisted tunneling (2TAT) (Fig. 2.21).

#### **Electron Injection Spread**

The discrete nature of the electric flow charging the floating gate determines the accuracy of the program algorithm in nanoscale cell. As illustrated before, in order to obtain tight  $V_T$  distribution after program, the control gate voltage is not kept constant during the programming transient, but s increased as a staircase

Figure 2.20: Diagram of anode hole injection in Flash memory cell.

Figure 2.21: Trap-assisted tunneling (a) and tunneling assisted by 2 traps (b).

with fixed step amplitude. After each step,  $V_T$  is sensed and compared to a verify level. Small variation of  $V_T$  are obtained transferring small charge packets from the substrate to the floating gate. Due to memory cell miniaturization, the number of electrons for each packet is very low. The statistic of the electron injection introduces a spread in the final  $V_T$  distribution.

Compagnoni *et all.* [12] have presented a model for the EIS. The spread of  $\Delta V_T$  is related to the spread of the number of injected electron n by the following equation:

$$\sigma_{\Delta V_T} = \frac{q}{C_{PP}} \sqrt{\sigma_n^2} \tag{2.22}$$

where q is the electronic charge. By assuming that n is ruled by a Poisson statistic, its variance  $\sigma_n^2$  is equal to its mean  $\overline{n}$  and equation 2.22 become:

$$\sigma_{\Delta V_T} = \frac{q}{C_{PP}} \sqrt{\overline{n}} = \sqrt{\frac{q}{C_{PP} \overline{\Delta V_T}}}$$

(2.23)

since  $\Delta V_T = qn/C_{PP}$ .

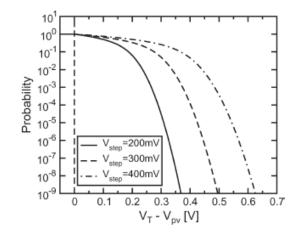

The effect of the injection spread on the  $V_T$  distribution respect to the programverify level  $V_{pv}$  is shown in Fig. 2.22. While neglecting the injection spread, the maximum value reached by  $V_T$  is  $V_{pv} + V_{step}$ , considering the EIS, larger values can be obtained, allowing the cell to move farther away from the verify level. The

Figure 2.22: Cumulative probability for  $V_T - V_{pv}$  assuming constantcurrent NAND programming with different  $V_{step}$  values (60nm technology)[12].

Poissonian behavior should be carefully considered for evaluating the impact of EIS on the programming algorithm accuracy. Furthermore the miniaturization of cell leads to a reduction of  $C_{PP}$ , which according to equation 2.23, determine an increase of  $\sigma_{\Delta V_T}$ .

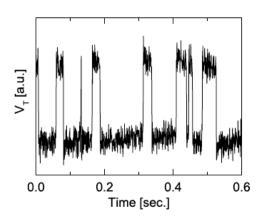

#### Random Telegraph Signal

Random Telegraph Signal (RTS) is a stochastic fluctuation between two levels of the device threshold voltage, induced by the capture or emission of a single electron in a gate oxide trap. Fig. 2.23 is an example of RTS fluctuation detected in a Flash memory cell. Random variations of cell  $V_T$  may give rise to erroneous data reads or erroneous program operation, since also program algorithm includes verification steps. This is particularly critical for MLC application, whose threshold voltage cell control is more critical.

Adopting a simple electrostatic approach and assuming trap located at the substrate/tunnel oxide interface, the following equation estimates the threshold voltage shift caused by the capture/release of a single electron [20]:

$$\Delta V_T^{st} = \frac{qt_{\rm ox}}{LW\epsilon_{\rm ox}\alpha_G} \tag{2.24}$$

where q is the electron charge,  $t_{\rm ox}$  the tunnel oxide thickness, L and W the channel length and width respectively, and  $\alpha_G$  the capacitive coupling coefficient between control gate and floating gate. Equation 2.24 is a simple electrostatic approach: in the case of W = L = 45 nm,  $t_{\rm ox} = 7$  nm and  $\alpha_G = 0.65$ ,  $\Delta V_T^{\rm st}$  result 25 mV, a quite low value.

Figure 2.23: Example of RTS measured in the time domain for a single Flash memory[20].

However it has been reported that NVMs feature RTS with magnitude much larger than the value predictable by equation 2.24, calling this phenomenon "Giant RTS" [20].

The amplitude of RTS  $V_T$  fluctuations has been shown increase upon channel size downscaling. This size dependence is explained by percolation effects, through non-uniform  $V_T$  landscape in the random doped channel and by confinement effects of the current at the channel edges, due to local field enhancement.

#### **Other Variability Sources**

The first and the most relevant source of statistical variability in nanoscale devices is the **random discrete dopants (RDD)**. Statistical variability simulations [5] demonstrate that RDD causes the reduction of the average threshold voltage. The reason is that RDD induces current percolation path in the channel, which leads to early turn on of the FG cell.

The second most important source of variability in Flash memory cell is **in-terface trapped charge (ITC)**. The average threshold voltage increase because of charge trapped at the surface of the device. As for RDD, the distribution of the trapped charges is governed by Poisson distribution.

Line edge roughness (LGR) of gate induce a smaller variability respect to RDD and it is due to the short channel effects around the nominal channel length. Line edge roughness affects also shallow trench isolation (STI), resulting in random STI roughness (LSR). In this case the induced variability (half the value of LGR) is due to the channel width dependence of the threshold voltage, which is weaker compared to the channel length dependance.

Oxide thickness fluctuation (OTF) has a small impact on statistical variability considering the relative thick (8-nm) oxide in Flash memory cells.

Finally **polysilicon granularity (PSG)** causes an increase of the average threshold voltage because of the increased potential at grain boundaries, but he variation is small due to the thick tunnel oxide.

# 2.4 Scaling Issues

The effort of semiconductor memory technology is constantly focused on accommodate more cells per unit of wafer area. The main purpose is the cost-per-bit reduction, obtained by cell size scaling. However downscaling must be supported by redesign in new technology, considering that high density require high performance dielectrics and high voltage architectures.

While the cell basic structure has not changed throughout different generation, scaling down has been carried out on the cell area, through active area and passive elements scaling. The reduction of the channel length not only allows increasing of density, but also speeds up the program operation, because carrier injection into the FG is more efficient. However decreasing L, the capacitive coupling between FG and drain increases, enhancing the probability of punch-through and drain turn on. The fair channel length comes from a tradeoff between performance and disturb.

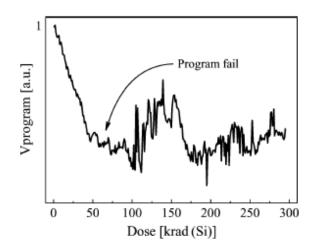

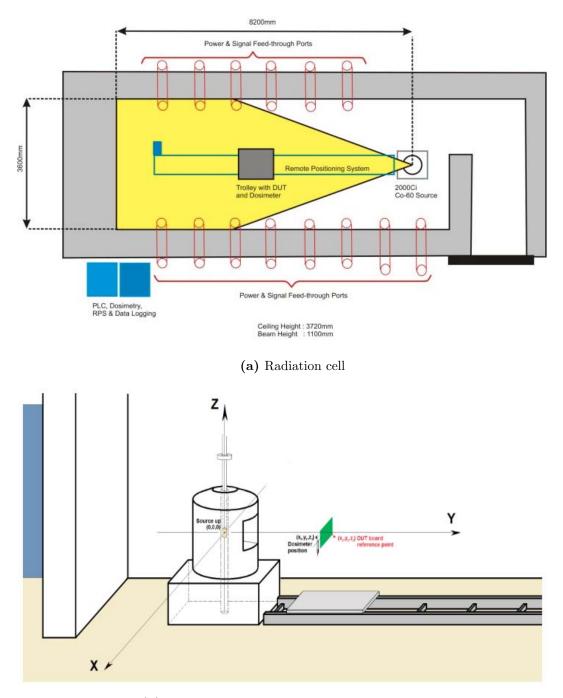

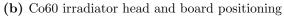

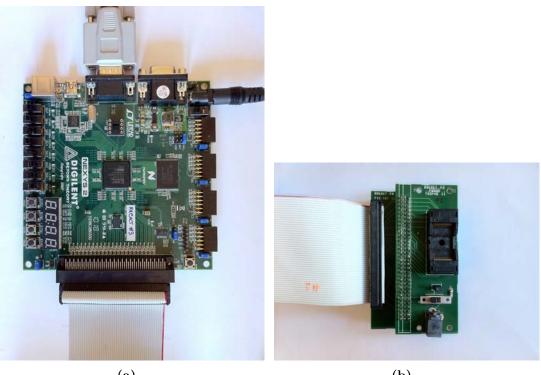

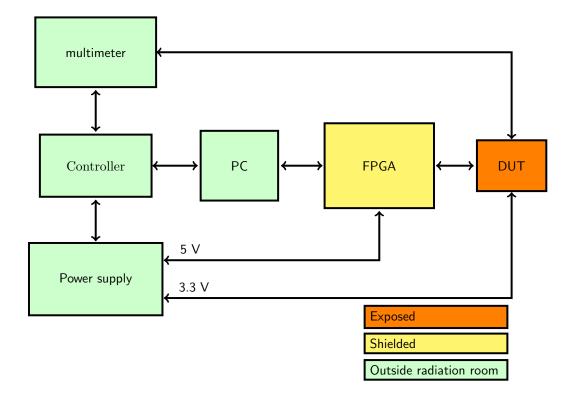

Another relevant issue in Flash memory is the relatively high voltage needed to programming and erasing, operations based on physical mechanisms (FN and HEI) whose parameters do not scale. Concerning the tunnel oxide thickness, it is limited at 7-8 nm, in order to comply data retention requirement of at least 10 years<sup>7</sup>. In fact, thinner oxide facilitates trap assisted tunneling process caused by oxide aging. As consequence, amplitude of RTN  $V_T$  fluctuations increases. The interpolydielectric too is limited to about 12-13 nm by the coupling coefficient  $\alpha_G$ . Furthermore, reducing the cell-to-cell distance causes parasitic coupling cross talk, which contribute to  $V_T$  distribution width. This issue is especially relevant for NAND Flash memory, because of its high density: since cells are very close to each other, scaling of NAND Flash memory is limited by parasitic interferences between adjacent cells. This is especially critic for multi-level cells.