#### UNIVERSITY OF PADOVA

# FACULTY OF ENGINEERING DEPARTMENT OF INFORMATION ENGINEERING MASTER OF SCIENCE IN ELECTRONIC ENGINEERING

MASTER'S THESIS

## 94 GHz Monolithic Transmitter for Weather Radar Application

UNIVERSITY SUPERVISOR: **Prof. Andrea Neviani**

COMPANY SUPERVISOR: **Ph.D. Marc Tiebout**

GRADUAND: Claudio Puliero

**ACADEMIC YEAR 2010/2011**

#### Abstract

This thesis was written for concluding my studies at the University of Padua. The main topic is the design of a monolithic transmitter in SiGe bipolar technology, for weather radar application at an operating frequency around 94GHz. At such a high frequency parasitic elements have to be taken into account very carefully. Appropriate matching networks become important to allow the signals to pass across the different sections of the transmitter, without reflections or attenuations. To this aim, transmission lines were used instead of inductors, in order to save size and to have a more reliable modelling of device parameters and parasitic elements. The structure of the transmitter includes a transformer (which acts as Balun), a frequency quadrupler and a buffer. The transmitter input receives a single-ended reference signal at 23.5GHz, with a power of OdBm on a single-ended input impedance of  $50\Omega$ . The output has been designed for a differential load of  $100\Omega$  and to operate in the temperature range of  $0^{\circ}\text{C}$  -  $100^{\circ}\text{C}$ , with a typical output power above 10dBm and spurious harmonic below -25dBc.

### Acknowledgment

First of all, I would like to thank Infineon Austria (site of Villach), the Industrial & Multimarket (IMM) and the RF power groups, which gave me the opportunity to make my thesis through an internship into their company. I'm very grateful to Marc Tiebout for his availability, his teachings and his big patience during my questions and my errors. A thanks also to all the colleague that I met during this experience into Infineon, whom helped me to spend seven pleasant months in Austria and that aided me during the hard times.

A special thanks to my high school (ITIS Severi), which has let me discover the electronic, in particular to Prof. Daniele Consolaro who encouraged me to inscribe at the university.

A great thanks to the University of Padua which formed and trained me on the way of electronic engineer. My sincere gratitude to all the group of IC design at my university and to Professor Andrea Neviani who sponsored my thesis in Infineon Austria and also helped me to draft it.

Most of all, I must to acknowledge my parents and my sister, that supported me during all my student's career, helping me during the worst of times and rejoicing with me over the best one. Thanks very much to my parents for have grown me up and for have paid my studies.

Last but not least a great thanks to all my friends, starting from my childhood friends up to the last Austrians ones, through my basket team and my LAN party crew. A fervent thought at that mates who chose a different way and now live far from me, I wish you a wonderful life!!

A last thanks to all people that I have forgotten, but who had a significant role into my academic studies and also in my life.

## Table of Contents

Abstract Acknowledgment Table of contents

| 1. Introduc | tion                                           | 1  |

|-------------|------------------------------------------------|----|

|             | ther Radars system                             |    |

| 1.1.1.      | Clouds studies                                 | 5  |

| 1.1.2.      | Brief story of weather radars                  | 6  |

| 1.1.3.      | Weather radar functioning                      | 8  |

| 1.2. Othe   | er transmitter bandwidth possible applications | 10 |

| 1.3. Trans  | smitter overview                               | 11 |

| 1.3.1.      | Target structure diagram                       | 13 |

| 1.3.2.      | Target specifications                          | 14 |

| 1.3.3.      | Transmitter for imaging in body scanner        | 17 |

| 2. Technolo | ogy overview                                   | 19 |

| 2.1. Infin  | eon's B7HF200                                  | 21 |

| 2.2. Bipo   | lar characteristics                            | 24 |

| 2.3. Chip   | packaging and measure problems                 | 27 |

| 2.4. Use    | of transmission lines                          | 28 |

| 3. Input ne | twork                                          | 31 |

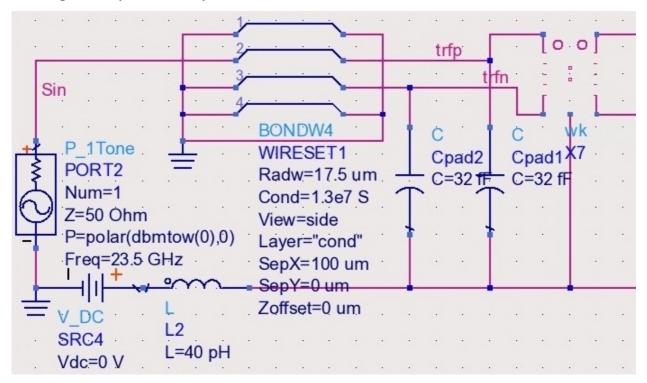

| 3.1. Bond   | ding and pads                                  | 31 |

| 3.2. Trans  | sformer                                        | 33 |

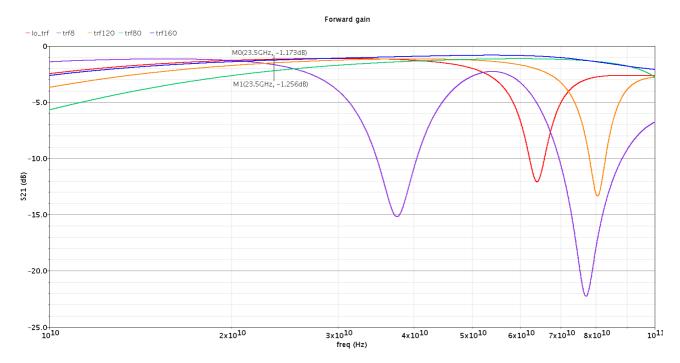

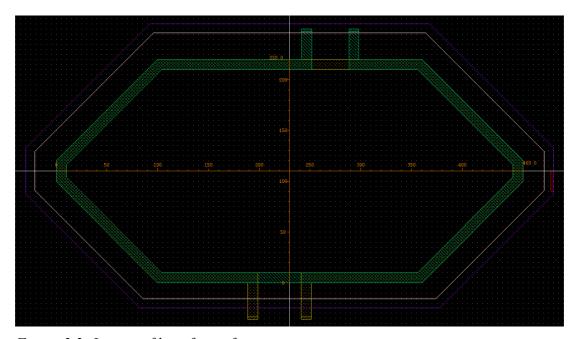

| 3.2.1.      | Choice of transformer                          | 33 |

| 3.2.2.      | Lumped model fitting                           | 35 |

| 4. Quadrup  | ler                                            | 37 |

|             | uit operation                                  |    |

| 4.1.1.      | Gilbert cell as frequency doubler              | 39 |

| 4.1.2.      | Bias circuit                                   | 42 |

| 4.2. Desi   | gn to 94GHz                                    | 44 |

| 4.2.1.      | Gain stage                                     | 45 |

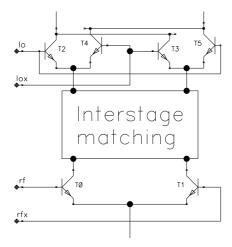

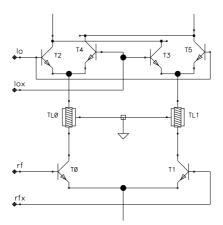

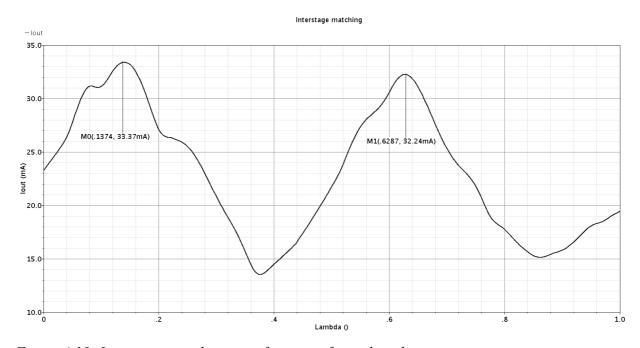

| 4.2.2.      | Interstage matching and quadrature phase       | 47 |

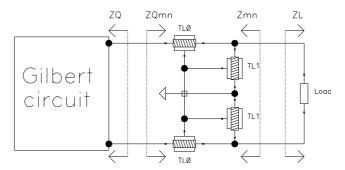

| 4.2.3.      | Matching networks                              | 50 |

| 4.2.4.      | Stability                                      | 52 |

| 4.2.5.      | Design result                                  | 54 |

| 4.3. L                                                                 | ayout                                                                                                                                                                                                          | 55                                                              |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 4.3.                                                                   | 1. Post-layout issues                                                                                                                                                                                          | 56                                                              |

| 4.4. F                                                                 | nal circuit and simulation results                                                                                                                                                                             | 57                                                              |

| 5. Buffeı                                                              |                                                                                                                                                                                                                | 63                                                              |

| 5.1. C                                                                 | ircuit operation                                                                                                                                                                                               | 64                                                              |

| 5.1.                                                                   | 1. Cascode configuration                                                                                                                                                                                       | 65                                                              |

| 5.1.                                                                   | 2. Bias circuit                                                                                                                                                                                                | 66                                                              |

| 5.2. D                                                                 | esign to 94GHz                                                                                                                                                                                                 | 67                                                              |

| 5.2.                                                                   | 1. Gain stage                                                                                                                                                                                                  | 68                                                              |

| 5.2.                                                                   | 2. Interstage matching                                                                                                                                                                                         | 70                                                              |

|                                                                        | 3. Matching networks                                                                                                                                                                                           |                                                                 |

| 5.2.                                                                   | 4. Stability                                                                                                                                                                                                   | 73                                                              |

| 5.2.                                                                   | 5. Design result                                                                                                                                                                                               | 74                                                              |

|                                                                        | ayout                                                                                                                                                                                                          |                                                                 |

|                                                                        | 1. Post-layout issues                                                                                                                                                                                          |                                                                 |

| 5.4. F                                                                 | nal circuit and simulation results                                                                                                                                                                             | 76                                                              |

|                                                                        |                                                                                                                                                                                                                |                                                                 |

| 6. Powe                                                                | amplifier                                                                                                                                                                                                      | 81                                                              |

|                                                                        | amplifierossible configurations and functioning                                                                                                                                                                |                                                                 |

| 6.1. P                                                                 |                                                                                                                                                                                                                | 81                                                              |

| 6.1. P<br>6.2. E                                                       | ossible configurations and functioning                                                                                                                                                                         | 81<br>83                                                        |

| 6.1. P<br>6.2. E<br>6.2.                                               | ossible configurations and functioning<br>mitter follower plus cascode                                                                                                                                         | 81<br>83<br>85                                                  |

| 6.1. P<br>6.2. E<br>6.2.<br>6.2.                                       | ossible configurations and functioning<br>mitter follower plus cascode                                                                                                                                         | 81<br>83<br>85<br>85                                            |

| 6.1. P<br>6.2. E<br>6.2.<br>6.2.<br>6.3. C                             | ossible configurations and functioning                                                                                                                                                                         | 81<br>83<br>85<br>85<br>86                                      |

| 6.1. P<br>6.2. E<br>6.2.<br>6.2.<br>6.3. C                             | nitter follower plus cascode  1. Design  2. Simulation results  ascode  1. Design                                                                                                                              | 81<br>83<br>85<br>85<br>86<br>87                                |

| 6.1. P<br>6.2. E<br>6.2.<br>6.2.<br>6.3. C<br>6.3.<br>6.3.             | nitter follower plus cascode  1. Design  2. Simulation results  ascode  1. Design                                                                                                                              | 81<br>83<br>85<br>85<br>86<br>87<br>88                          |

| 6.1. Po<br>6.2. E<br>6.2.<br>6.3. C<br>6.3.<br>6.3.<br>6.3.            | mitter follower plus cascode  1. Design  2. Simulation results  1. Design  2. Simulation results  3. Simulation results                                                                                        | 81<br>83<br>85<br>85<br>86<br>87<br>88                          |

| 6.1. Po<br>6.2. E<br>6.2.<br>6.3. C<br>6.3.<br>6.3.<br>6.3.<br>6.4. R  | mitter follower plus cascode  1. Design  2. Simulation results  ascode  1. Design  3. Low output power due to layout parasitic elements  emoval of power amplifier                                             | 81<br>83<br>85<br>86<br>87<br>88<br>89                          |

| 6.1. Po<br>6.2. E<br>6.2.<br>6.3. C<br>6.3.<br>6.3.<br>6.4. R          | mitter follower plus cascode  1. Design  2. Simulation results  ascode  1. Design  3. Low output power due to layout parasitic elements                                                                        | 81<br>83<br>85<br>86<br>87<br>88<br>89<br>89                    |

| 6.1. Policies 6.2. 6.2. 6.3. 6.3. 6.3. 6.4. R 7. Top le 7.1. S         | mitter follower plus cascode  1. Design  2. Simulation results  ascode  1. Design  2. Simulation results  ascode  3. Low output power due to layout parasitic elements  emoval of power amplifier  vel circuit | 81<br>83<br>85<br>86<br>87<br>88<br>89<br>89                    |

| 6.1. Policies 6.2. 6.2. 6.3. 6.3. 6.3. 6.4. R 7. Top le 7.1. S 7.2. Le | mitter follower plus cascode                                                                                                                                                                                   | 81<br>83<br>85<br>86<br>87<br>88<br>89<br>89<br><b>91</b><br>93 |

Bibliography

## Chapter 1: Introduction

The main goal of RADARs is to scan the open space, or an object, and then reconstruct its image through the electromagnetic energy reflected back, from the object to the radar station. The optical image is created by mapping the electromagnetic scattering coefficient onto a two-dimensional plane. Objects with a higher coefficient are assigned to a higher optical reflective index.

Transmitter structure is basically the same for most of the RADARs; the main parameter is the frequency, which depends on the field of use. To choose the right operative frequency for the RADAR, it depends principally on the dimension of the object that have to be scanned. An increase of the operating frequency means to be able to recognize smaller objects and to have a higher resolution. It is also helpful for decreasing the dimension of the RADAR antenna, which enables to put these devices into portable or mobile structures like cars or planes. On the other hand at higher frequency we have much more construction costs for the transmitter and in the most case also more power consumption and lower efficiency.

With a lower size of the transmitter it is also possible to construct phased array antennas, which are more performant. They are also more reliable because they are without the mechanical structure, which moves the antenna into the right direction for scanning all the space. In these kind of antennas, the relative phases of the respective signals feeding the antennas, are varied in such a way that the effective radiation pattern, of the array, is reinforced in a desired direction and suppressed in undesired directions.

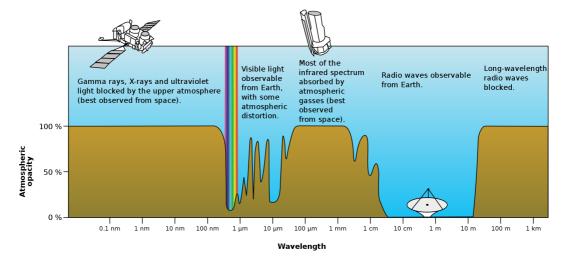

Figure 1.1: Atmospheric opacity vs. wavelength

Another issue to take into account for long distance and high frequency RADAR application (into the free-space), is the absorption of electromagnetic radiation due to the Earth's atmosphere. The combined absorption spectra of the gases in the atmosphere leave "windows" of low opacity, allowing the transmission only into certain frequency bands. One of these small windows is also present around the 94GHz working frequency of this transmitter, which is one of the reasons why this frequency has been chosen.

Also the free-space path loss has to be considered. It is proportional to the square of the distance between the transmitter and receiver, and also proportional to the square of the frequency of the radio signal. Higher frequency means higher attenuation for the same distance.

From these considerations weather radars will be the main target for the 94GHz monolithic transmitter design treated in these pages. Despite that some other possible applications could be found and they will be shown in a following section.

#### 1.1 Weather Radars system

Since the beginning of human history, the weather has played a large and sometimes direct part in our behaviour for a lot of daily activities. Some examples can be timely evacuations for protect life and property, or to plan activities and agriculture; they are also used by commodity traders for stock markets and by people to determine what to wear on a given day. For these reasons humans have attempted to predict the weather informally for millennia, and formally since at least the nineteenth century. [Int:1]

Figure 1.2: Europe seen from satellite

The weather forecasts are made by collecting quantitative data about the current state of the atmosphere and using scientific understanding of atmospheric processes to project how the atmosphere will evolve. The basic idea of numerical weather prediction is to sample the state of the fluid at a given time and use the equations of fluid dynamics and thermodynamics to estimate the state of the fluid at some time in the future.

The main inputs from country-based weather services are surface observations, from automated weather stations at ground level, over land, and from weather buoys at sea. The World Meteorological Organization acts to standardize the instrumentation, observing practices and timing of these observations worldwide. Stations either report hourly in METAR reports or every six hours in SYNOP reports. Sites launch radiosondes, which rise through the depth of the troposphere and well into the stratosphere. Data from weather satellites are used in areas of where traditional data sources are not available. Compared with similar data from radiosondes, the satellite data has the advantage of global coverage, however at a lower accuracy and resolution.

Some commercial planes provide reports along their aircraft routes and also the ships report information along their shipping route. Research flights using reconnaissance aircraft fly in and around weather systems of interest such as tropical cyclones. Reconnaissance aircraft are also flown over the open oceans during the cold season into systems which cause significant uncertainty in forecast guidance, or are expected to be of high impact 3-7 days into the future over the downstream continent.

Weather radar systems (typically Arinc 708 on commercial aircraft) and lightning detectors, are important also for aircraft flying at night, or in instrument meteorological conditions, where it is not possible for pilots to see the weather ahead. Theirs main goal is to improve the daily weather report and to make flying safer by providing pilots with real-time heavy precipitation, icing conditions (sensed by radar) or turbulence (sensed by lightning activity). These are both indications of strong convective activity and severe turbulence, weather systems allow pilots to deviate around these dangerous areas.

Weather radars are both transmitters and receivers (R.A.D.A.R. is an acronym that stands for "RAdio Detection And Ranging"). They transmit a microwave beam and then "listen" for echoes that bounce back from precipitation-sized particles (or "targets") within or falling from clouds. Just as a beam of light from a flashlight

shows objects in the dark, weather radar detects and locates precipitation, but it does so both in daylight and darkness, through thick clouds, and at greater distances than can a flashlight beam. Both the flashlight and weather radar work on the same principle: a small part of the transmitted energy is reflected back towards the source after striking an object.

Into each weather station there is a meteorological radar, which provides information on precipitation location and intensity, that can be used to estimate precipitation accumulations over time. So weather radar are a versatile tool for atmospheric assessment, with uses that include:

- Rainfall estimates

- · Real-time cloud detection

- Speed and direction of cell motion

- Identifying precipitation location and intensity

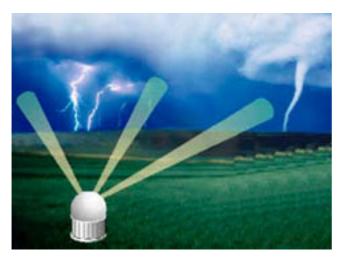

Figure 1.3: Typical weather antennas

In addition modern weather radars are mostly pulse-Doppler radars, which are capable of measuring if whether precipitation echoes are moving toward or away from the radar antenna, and can therefore measure rotation within storms which may precede severe storms. Generally a "Pulse Doppler" weather radar is also used to determine the wind speed and direction.

Meteorologists use weather radar to detect, locate, and measure the amount of precipitation within or falling from clouds. From weather forecast studies derive the importance of a good weather radars, with a high resolution, that means high operative frequency. This is the reason why it will be presented a suggestion of a monolithic transmitter cell at 94 GHz, for potential weather uses.

#### 1.1.1 Clouds studies

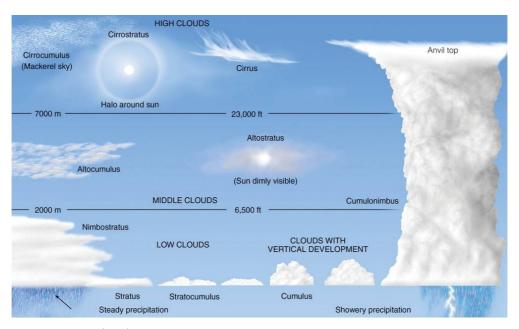

A cloud is a visible mass of water droplets or frozen ice crystals suspended in the Earth's atmosphere above the surface of the Earth or other planetary body. Two processes, possibly acting together, can lead to air becoming saturated: cooling the air or adding water vapour to the air. Generally, precipitation will fall to the surface; an exception is virga which evaporates before reaching the surface. [Int:1]

Clouds can show convective development like cumulus, be in the form layered sheets such as stratus, or appear in thin fibrous wisps as with cirrus. Whether or not a cloud is low, middle, or high level depends on how far above the ground its base forms. Some cloud types can form in the low or middle ranges depending on the moisture content of the air. While a majority of clouds form in the Earth's troposphere, there are occasions where clouds in the stratosphere and mesosphere are observed. All weather-related cloud types form in the troposphere, the lowest major layer of the Earth's atmosphere. Clouds have been observed on other planets and moons within the Solar System, but due to their different temperature characteristics, they are composed of other substances such as methane, ammonia, or sulphuric acid.

Figure 1.4: Clouds types

Clouds are a key element in the global hydrological cycle, and they have a significant role in the Earth's energy budget through its influence on radiation budgets. Climate model simulations have demonstrated the importance of clouds in moderating and forcing the global energy. An improved understanding of the

radioactive impact of clouds on the climate system requires a comprehensive view of clouds that includes their physical dimensions, vertical and horizontal spatial distribution, detailed micro-physical properties, and the dynamical processes producing them.

For this purpose millimetre-wave cloud radars at W-band were designed. They are radar system designed to monitor cloud structure with a wavelengths about ten times shorter than those used in conventional storm surveillance radars such as NEXRAD. These radars provide fine scale cloud information and offer significant advantages over LIDAR and lower frequency radars. The high scattering efficiency and short wavelengths at millimetre-wave frequencies provide high sensitivity for cloud detection, and enable construction of compact, low-power consumption radars for use in airborne applications.

The National Oceanic and Atmospheric Administration designed MMCR to monitor clouds overhead at various testing sites of the U.S. Department of Energy's atmospheric radiation measurement program. The MMCR is a vertically pointing Doppler weather radar that operates at a frequency of 35GHz. The main purpose of this radar is to determine cloud boundaries (e.g., cloud bottoms and tops). The shorter wavelength of the radar helps detect tiny water and ice droplets that conventional radars are unable to "see". The radar also helps to estimate microphysical properties of clouds, such as particle size and mass content, which aids in understanding how clouds reflect, absorb and transform radiant energy passing though the atmosphere. MMCR also reports radar reflectivity (dBZ) of the atmosphere up to 20km and possesses the capability to measure vertical velocities of cloud constituents.

#### 1.1.2 Brief story of weather radars

During World War II, military radar operators noticed noise in returned echoes due to weather elements like rain, snow, and sleet. [Int:1] Just after the war, military scientists returned to civilian life or continued in the Armed Forces and pursued their work in developing a use for those echoes. In the United States, David Atlas developed the first operational weather radars. In Canada, J.S. Marshall and R.H. Douglas formed the "Stormy Weather Group" in Montreal. Marshall and his doctoral student Walter Palmer are well known for their work on the drop size distribution in mid-latitude rain that led to understanding of the Z-R relation, which correlates a given radar reflectivity with the rate at which water is falling on the ground. In the

United Kingdom, research continued to study the radar echo patterns and weather elements such as stratiform rain and convective clouds, and experiments were done to evaluate the potential of different wavelengths from 1 to 10 centimetres.

In 1953, Donald Staggs, an electrical engineer working for the Illinois State Water Survey, made the first recorded radar observation of a "hook echo" associated with a tornadic thunderstorm.

Between 1950 and 1980, reflectivity radars, which measure position and intensity of precipitation, were built by weather services around the world. The early meteorologists had to watch a cathode ray tube. During the 1970s, radars began to be standardized and organized into networks. The first devices to capture radar images were developed. The number of scanned angles was increased to get a three-dimensional view of the precipitation, so that horizontal cross-sections (CAPPI) and vertical ones could be performed

The National Severe Storms Laboratory, created in 1964, began experimentation on dual polarization signals and on Doppler effect uses. In May 1973, a tornado devastated Union City, Oklahoma, just west of Oklahoma City. For the first time, a Dopplerized 10cm wavelength radar from NSSL documented the entire life cycle of the tornado. The researchers discovered a mesoscale rotation in the cloud aloft before the tornado touched the ground: the tornadic vortex signature. NSSL's research helped convince the National Weather Service that Doppler radar was a crucial forecasting tool.

Between 1980 and 2000, weather radar networks became the norm in North America, Europe, Japan and other developed countries. Conventional radars were replaced by Doppler radars, which in addition to position and intensity of could track the relative velocity of the particles in the air. In the United States, the construction of a network consisting of 10cm wavelength radars, called NEXRAD or WSR-88D (Weather Service Radar 1988 Doppler), was started in 1988 following NSSL's research. In Canada, Environment Canada constructed the King City station, with a five centimetre research Doppler radar, by 1985; McGill University dopplerized its radar (J. S. Marshall Radar Observatory) in 1993. This led to a complete Canadian Doppler network between 1998 and 2004. France and other European countries switched to Doppler network by the end of the 1990s to early 2000s. Meanwhile, rapid advances in computer technology led to algorithms to detect signs of severe weather and a plethora of "products" for media outlets and researchers.

After 2000, research on dual polarization technology has moved into operational use, increasing the amount of information available on precipitation type (e.g. rain vs. snow). "Dual polarization" means that microwave radiation which is polarized both horizontally and vertically (with respect to the ground) is emitted. Wide-scale deployment is expected by the end of the decade in some countries such as the United States, France, and Canada.

Since 2003, the U.S. National Oceanic and Atmospheric Administration has been experimenting with phased-array radar as a replacement for conventional parabolic antenna to provide more time resolution in atmospheric sounding. This would be very important in severe thunderstorms as their evolution can be better evaluated with more timely data.

#### 1.1.3 Weather radar functioning

Weather radars send directional pulses of microwave radiation on the order of a microsecond long, or triangular frequencies modulation signal (FMCW), by using a cavity magnetron, a klystron tube or a solid-state electronics, connected by a waveguide to a parabolic antenna. The wavelengths from 1 to 10 cm are approximately ten times the diameter of the droplets or ice particles of interest, because Rayleigh scattering occurs at these frequencies. This means that part of the energy of each pulse will bounce off these small particles, back in the direction of the radar station.

Shorter wavelengths are useful for smaller particles, but the signal is more quickly attenuated. Thus 10cm (S-band) radar is preferred but is more expensive than a 5cm C-band system. 3cm X-band radar is used only for very short distance purposes, and 1cm Ka-band weather radar is used only for research on small-particle phenomena such as drizzle and fog.

Radar signals spread out as they move away from the radar station. This means that the air region of any given pulse is moving through, it is larger for areas farther away from the station, and smaller for nearby areas, decreasing resolution at far distances. At the end of a 150-200 km sounding range, the volume of air scanned by a single pulse might be on the order of a cubic kilometre. This is called the pulse volume.

For the pulsed radar, between each pulse, the radar station serves as a receiver and listens for return signals from particles in the air. The duration of the "listen" cycle is on the order of a millisecond, which is a thousand times longer than the pulse

duration. The length of this phase is determined by the need for the microwave radiation (which travels at the speed of light) to propagate from the detector, to the weather target, and back again, for distances which could be several hundred kilometres.

The horizontal distance from station to target is calculated simply from the amount of time that lapses from the initiation of the pulse to the detection of the return signal. (The time is converted into distance by multiplying by the speed of light). If pulses are emitted too frequently, the returns from one pulse will be confused with the returns from previous pulses, resulting in incorrect distance calculations. In order to determine the height we can assume that the Earth is round. With knowledge of the variation of the index of refraction through air and the distance to the target, it can be calculated the height above ground of the target.

FMCW radars, instead, are systems where a known stable frequency continuous wave radio energy is modulated by a triangular modulation signal, so that it varies gradually. This transmit signal is then mixed with the reflected from a target object to produce the information signal. The received waveform is almost a delayed replica of the transmitted waveform and the time delay is a measure of the distance.

Each weather radar network uses a series of typical angles that will be set according to the needs. After each scanning rotation, the antenna elevation is changed for the next sounding. This scenario will be repeated on many angles to scan all the volume of air around the radar within the maximum range. Usually, this scanning strategy is completed within 5 to 10 minutes to have data within 15km above ground and 250km distance of the radar.

Due to the Earth curvature and change of index of refraction with height, the radar cannot "see" below the height above ground of the minimal angle or closer to the radar than the maximal one.

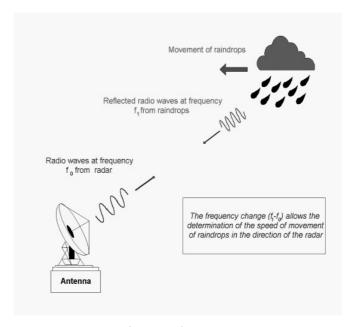

Doppler weather radar has become increasingly popular in recent years. It is capable of measuring the approach (or departing) speed of raindrops. The Doppler principle can be explained by noting the change in pitch of an ambulance siren. The pitch heightens as the ambulance approaches and lowers as it departs. In other words, the faster the ambulance approaches, the higher will be the pitch. For the case of a Doppler radar, the faster the raindrops move towards the radar, the higher will be the frequency (i.e. pitch) of the microwave reflected from raindrops. The

raindrops approach speed is determined by the frequency shift, and provides a good estimation of the winds, which carry the raindrops.

Figure 1.5: Doppler weather RADAR

#### 1.2 Other transmitter bandwidth possible applications

Some other 94GHz transmitter possible applications were studied during last years, they could be found on internet, but most of them are for military use and poor information are shown. [Appleby:04] [Int:1]

One example is a real-time 94GHz passive millimetre-wave imager for helicopter operations, that can penetrate poor weather far better than infrared or visible systems. Imaging in this band offers the opportunity for passive surveillance and navigation allowing military operations in poor weather. This 94GHz imager has diffraction limited performance over the central two thirds of the 30  $\times$  60 degrees field of view with and a 25Hz frame update rate.

Another military use is the Active Denial System (ADS) that is a non-lethal, directed-energy weapon developed by the U.S. military. It is a strong millimetre-wave transmitter primarily used for crowd control (the "goodbye effect"). Some ADS such as HPEM ADS are also used to disable vehicles. Informally, the weapon is also called heat ray.

The ADS works by firing a high-powered beam of electromagnetic radiation in the form of high-frequency millimetre waves at 95 GHz (a wavelength of 3.2 mm). Similar to the same way that a microwave oven heats food, the millimetre waves excite the water and fat molecules in the body, instantly heating it and causing

intense pain. Note that while microwaves will penetrate human tissue and remove the water to "cook" the flesh, the millimetre waves used in ADS are blocked by cell density and only penetrate the top layers of skin, so it will not damage human flesh.

Such is the nature of dielectric heating that the temperature of a target will continue to rise so long as the beam is applied, at a rate dictated by the target's material and distance, along with the beam's frequency and power level set by the operator. Like all focused energy, the beam will irradiate all matter in the targeted area, including everything beyond/behind it that is not shielded, with no possible discrimination between individuals, objects or materials, although highly conductive materials such as aluminium cooking foil should reflect this radiation and could be used to make clothing that would be protective against this radiation. All living things in the target area receive a similar dosage of radiation.

In addition some passive millimetre-wave cameras for concealed weapons detection operate at 94 GHz. Atmospheric radio window at 94 GHz is used for imaging millimetre-wave radar applications in astronomy, defence, and security applications. Also some notes on a 94GHz automobile collision-avoidance radar was found, but in automotive the typical used frequency is around 77GHz. [Moldovan:04]

The designed transmitter is not suitable for transceiver uses for data signals. As we will see, this is due to the presence of a fundamental tone frequency doubler, which produces a considerable intermodulation distortion for signals in a potential data bandwidth.

#### 1.3 Transmitter overview

In electronics and telecommunications a transmitter or radio transmitter is an electronic device which, with the aid of an antenna, produces radio waves. The transmitter itself generates a radio frequency alternating current (or voltage), which is applied to the antenna. When excited by this alternating current, the antenna radiates radio waves.

Depending on the specific application, the peak powers generated by the radar transmitter can range from milliwatts to gigawatts. Both thermionic tube-type transmitters and solid-state transmitters are used. If the transmitter is specified to generate high average power, than typically an amplifier based on vacuum tube technology will be required. [Book:6]

The transition from high-power klystrons, traveling wave tubes (TWTs), crossed-

field amplifiers (CFAs), and magnetrons, to solid-state electronics has actually been very gradual because the power output of individual solid-state devices is quite limited compared to typical radar requirements. Nevertheless, transmitter designers have learned that the required higher power levels, for radar transmitters, can be achieved also with a solid-state technology, because transistors and transistor amplifier modules can be readily combined in parallel, to achieve a composite higher equivalent output power. Anyway both vacuum tubes and solid-state devices will be appealing in high performance radars for many years to come.

For this project it has been used a solid-state configuration thanks to the availability of a silicon technology, and also because we point to a target market of planes and phased-array antennas. In these fields low sizes are required, besides some other characteristics become relevant, compared to tube-type transmitters, like lower supply voltages and an higher meantime between failures (MTBF). [Book:5]

Another distinction that can be made for transmitters is between broadcasting transmitters and RADAR transmitters. Ordinarily the first ones are the most complicated, because, in order to broadcast information, a modulation process is needed for the data signal. Recent and most used frequency modulation requires more exacting specifications for the harmonic distortion and intermodulation in the data signal bandwidth, and also adequate rejection of noise. For these reasons, in these cases more complex circuits are implemented.

The transmitters for RADARs, instead, are used for sending a signal with a desired power at one single frequency or quasi-static frequency modulated signal (in case of FMCW radar), for then watching which is the reflected power that returns back to the antenna, or the frequency variation due to Doppler effect. More relaxed circuits can be used at this purpose.

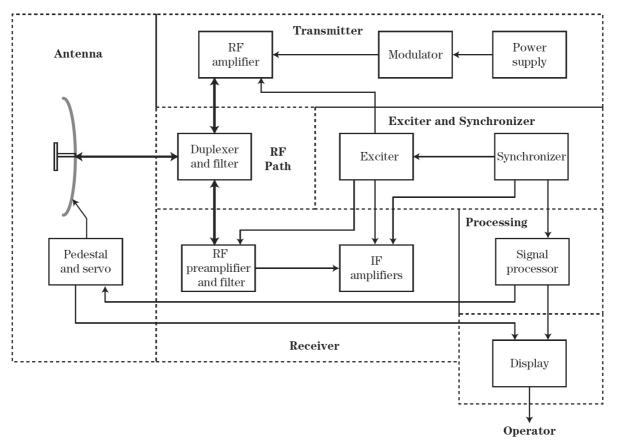

Generally around the transmitter there are also some other circuits, that all together form the RADAR system. These are the RF path, the receiver, the signal processing circuits and the devices that act to control and synchronize all the functional blocks. Even the transmitter can be divided into some small blocks: the signal generator (usually a voltage oscillator), the signal modulator (not always present) and an amplification stage. This is also the structure of our transmitter, which will be analysed with more detail in the next sections.

Figure 1.6: Block diagram of a typical pulsed radar [Book:5]

#### 1.3.1 Target structure diagram

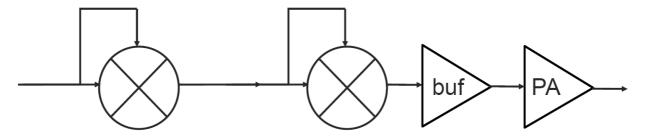

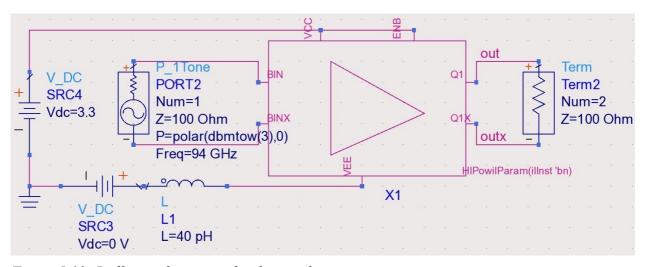

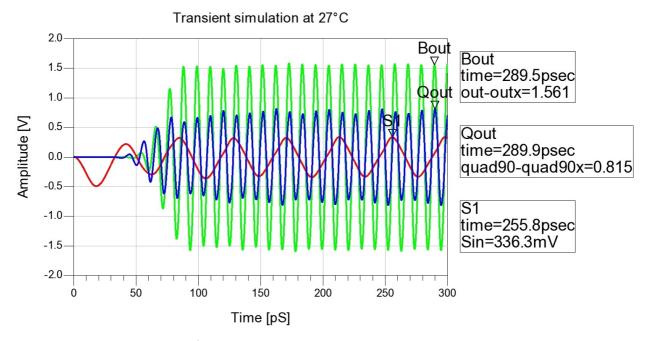

The goal of this thesis project is to produce a RADAR transmitter. To do this, it is needed to produce an appropriate power signal to the following antenna, starting from a local oscillator signal at 23.5GHz. It has been specified to start from this lower frequency signal, and than to modulate it at 94GHz (with a frequency quadrupler), because it is too difficult produce an electronic harmonic oscillator at such high frequency, instead of locally multiply a lower frequency signal.

This oscillator signal has been considered as an external input, produced by a further circuit that will be a voltage controlled oscillator or more probably a PLL. This device has a specified  $50\Omega$  single-ended output impedance.

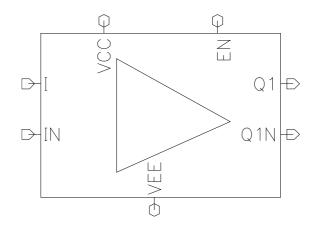

Figure 1.7: Transmitter target structure

Therefore the transmitter has an input and an output. Due to the single-ended output of the input, it is also required an unbalance to balance convention (Balun), given that the transmitter circuit will be differential. This task is made by an high frequency integrated circuit transformer, on chip. After the transformer there is a cascade of two frequency doublers, so a quadrupler, whose output goes to the amplification stage, which is composed by a buffer and a power amplifier. Amplification is divided into two blocks, for a gradual increase of signal amplitude (7-10dB per stage), as at this high frequencies not more gain is possible.

The output of the transmitter is directly connected to an RF path, with a differential load of  $100\Omega$ .

Since a frequency doubler is present into the structure of my transmitter, it is very difficult to use it for broadcasting data signals. Multiplying these kind of signals (with two or more very close component in frequency) by itself, it generates a folding of some multiplied component, like the intermodulation behaviour, which degrades the information signal.

#### 1.3.2 Target specifications

Due to the research purpose of this thesis design, specifications are given as target specifications, which are negotiable according to simulations results.

#### Source signal

The source signal is assumed as a sinusoidal wave at 23.5GHz, very stable with the temperature variation, both in output frequency that in output power. Temperature is considered variable between 0 and  $100^{\circ}$ C. As already said the source signal is given as a single-ended output on a  $50\Omega$  impedance.

| Source signal device |     |      |     |                         |

|----------------------|-----|------|-----|-------------------------|

| Specs                | min | nom  | max | Comment                 |

| Output frequency     | 23  | 23.5 | 24  | GHz                     |

| Output power         | 0   |      |     | dBm                     |

| Output impedance     |     | 50   |     | $[\Omega]$ Single-ended |

| Temperature          | 0   | 27   | 100 | °C                      |

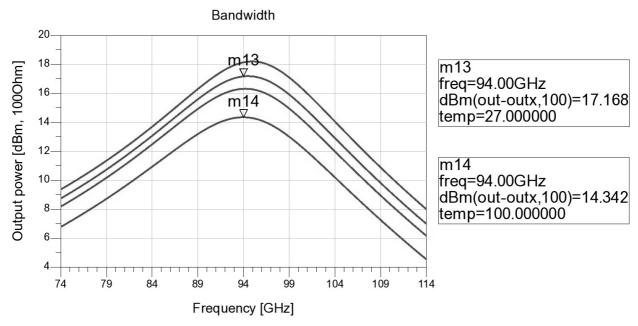

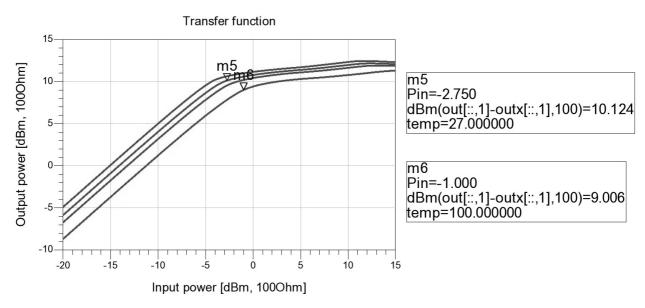

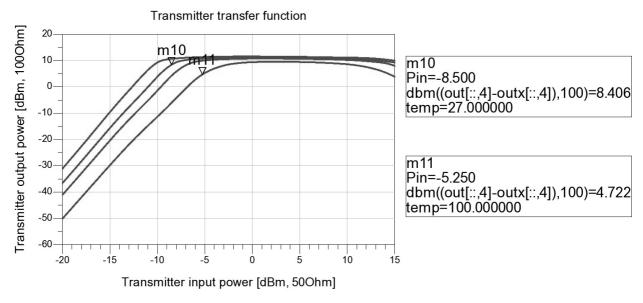

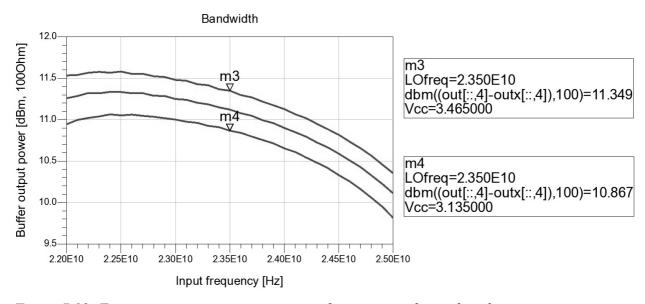

#### Top level circuit

The top level circuit, at the end, have to produce an output at 94GHz, with at least a bandwidth of 2GHz around the central frequency (like a bandpass filter). The output power should be as high as possible, taking into account also the power consumption of the circuit. Anyway the output signal power can be estimated in

roughly 15dBm on a  $100\Omega$  differential load.

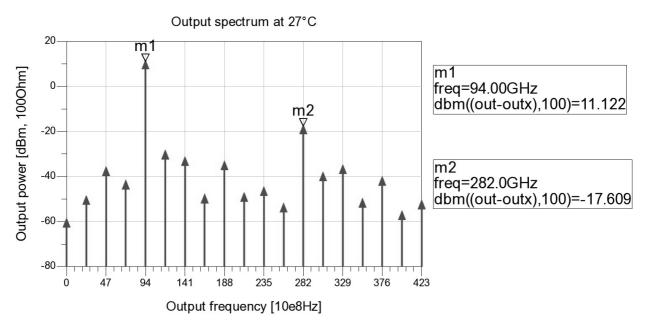

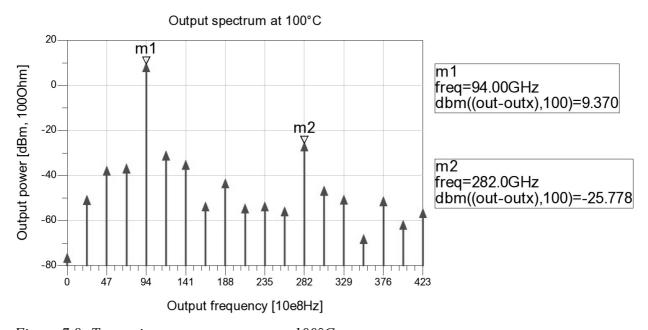

The output signal should be a sinusoidal wave, like at the input, so a maximum harmonic distortion of -20dBc was decided. This is valid for all the output harmonics referred to carrier frequency, which is 94GHz at the output.

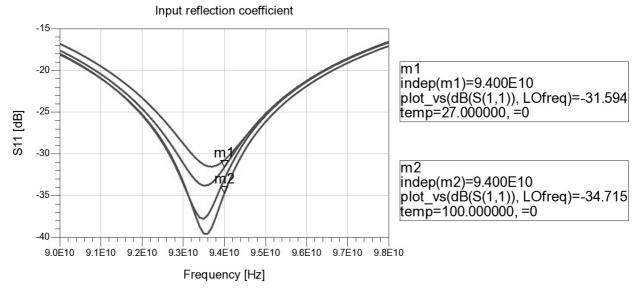

Matching networks are needed both at the input and at the output. This because reflection coefficients lower than -10dB are required: on the  $50\Omega$  single-ended load at the input and  $100\Omega$  differential at the output. Instead, a prearranged matching is not required between the internal blocks that compose the transmitter. Here matching networks are also needed, but the goal is a little bit different and it will be analysed during the design process.

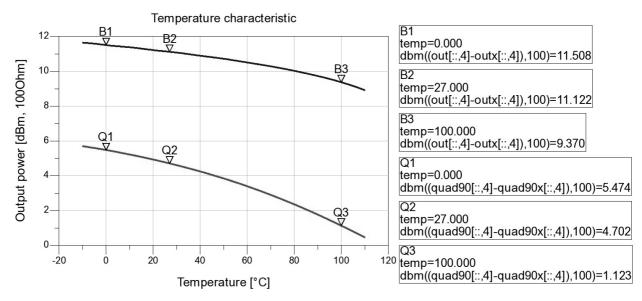

Temperature is also taken into account, it has to be able to vary from 0 to 100°C. In this range all the specifications have to be guaranteed: reflection coefficients, harmonics distortion, bandwidth and minimal output power.

Voltage supply is fixed by B7HF200 Infineon technology: 3.3V. The total power consumption is rather uncritical, since it isn't a battery supplied device, so it has been set lower than 1W.

| Top level circuit                                |     |      |     |                           |  |

|--------------------------------------------------|-----|------|-----|---------------------------|--|

| Specs                                            | min | nom  | max | Comment                   |  |

| Input frequency                                  | 23  | 23.5 | 24  | GHz                       |  |

| Output frequency                                 | 92  | 94   | 96  | GHz                       |  |

| Bandwidth                                        | 2   |      |     | [GHz] -3dB                |  |

| Input power                                      | 0   |      |     | dBm                       |  |

| Output power                                     | 10  | 20   |     | [dBm] As much as possible |  |

| Harmonics distortion                             |     |      | -20 | dBc                       |  |

| Input impedance                                  |     | 50   |     | [Ω] Single-ended          |  |

| Output impedance                                 |     | 100  |     | $[\Omega]$ Differential   |  |

| Input reflection coefficient (S <sub>11</sub> )  |     |      | -10 | dB                        |  |

| Output reflection coefficient (S <sub>22</sub> ) |     |      | -10 | dB                        |  |

| Temperature                                      | 0   | 27   | 100 | °C                        |  |

| Voltage supply                                   |     | 3.3  |     | V                         |  |

| Power consumption                                |     |      | 1   | W                         |  |

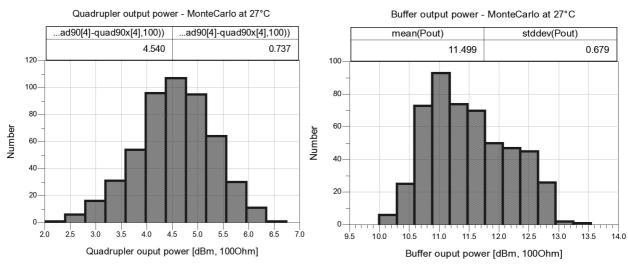

#### Quadrupler

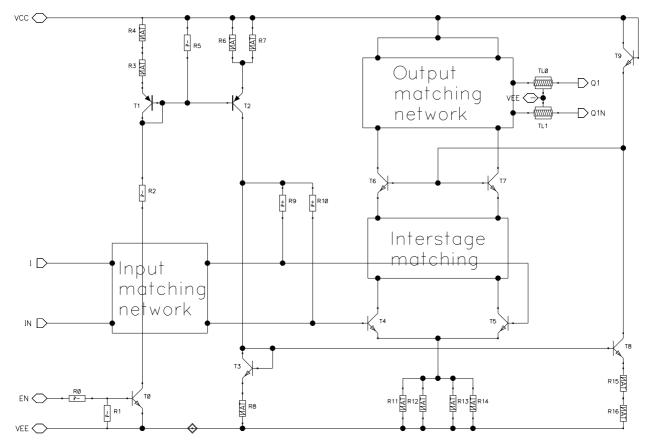

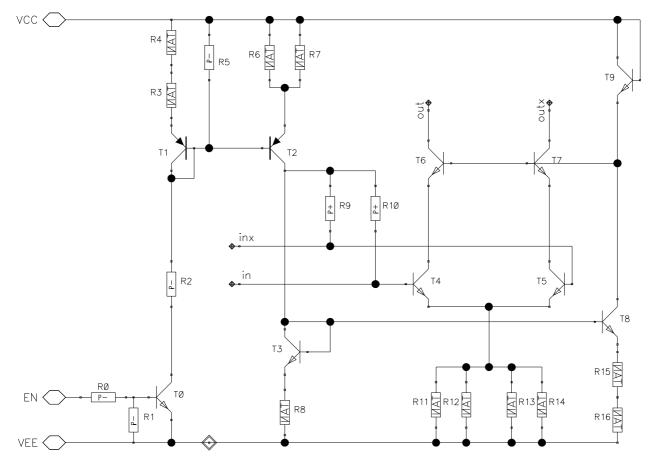

The quadrupler is the circuit that multiplies by four the input signal. This modulation is made of a cascade of two Gilbert mixer cells [Gilbert:68]. The input of the circuit is directly connected to the transformer. Between it and the first

doubler a matching network has to be placed, its purpose is to guarantee the matching at the input of the transmitter.

Quadrupler should gain power to cover the transformer losses. Output power should be at least 0dBm at 100°C and normally roughly 3dBm.

Seeing that the modulation process is the highest generator of spurious harmonics, also here the harmonic distortion has to be considered, even if it can be considered not really strict, since the following amplification blocks will decrease it, through their band-pass nature.

| <u>Quadrupler</u>    |     |      |     |            |

|----------------------|-----|------|-----|------------|

| Specs                | min | nom  | max | Comment    |

| Input frequency      | 23  | 23.5 | 24  | GHz        |

| Output frequency     | 92  | 94   | 96  | GHz        |

| Bandwidth            | 2   |      |     | [GHz] -3dB |

| Input power          | 0   |      |     | dBm        |

| Output power         | 0   | 3    |     | dBm        |

| Harmonics distortion |     |      | -20 | dBc        |

| Temperature          | 0   | 27   | 100 | °C         |

#### Buffer

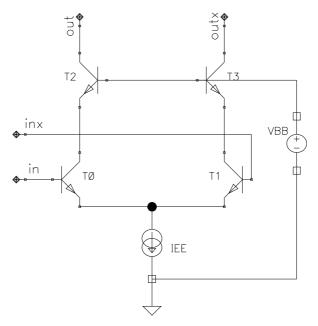

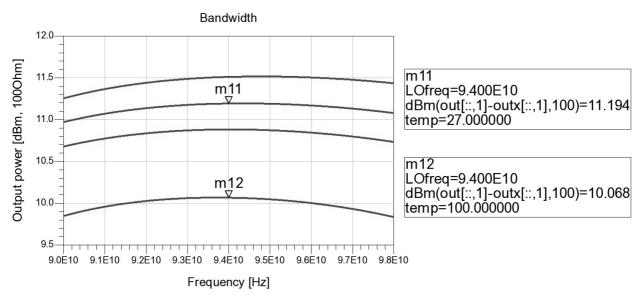

The buffer isn't only the fist amplification block, but it separates the multiplication from the amplification. At this high frequency the interconnections between blocks are made with transmission lines, so if the impedances are not matched we could have high reflection or impedance variation. These behaviours can decrease the amplification or the true output voltage. For these reasons I decided to set both the input and the output impedance of the buffer to  $100\Omega$  differential, and than to do the matching on this value.

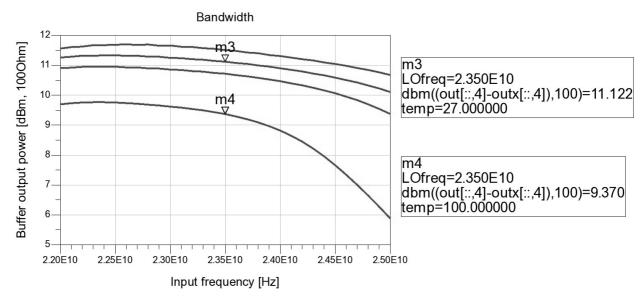

At the output of the buffer it should be available at least a power of 8dBm at 100°C and a normal power of roughly 11dBm. Also the harmonic distortion has to be lower than -20dBc, respect to the carrier frequency.

| <u>Buffer</u>    |     |     |     |            |

|------------------|-----|-----|-----|------------|

| Specs            | min | nom | max | Comment    |

| Input frequency  | 92  | 94  | 96  | GHz        |

| Output frequency | 92  | 94  | 96  | GHz        |

| Bandwidth        | 2   |     |     | [GHz] -3dB |

| Input power      | 0   | 3   |     | dBm        |

| <u>Buffer</u>                                    |     |     |     |                         |

|--------------------------------------------------|-----|-----|-----|-------------------------|

| Specs                                            | min | nom | max | Comment                 |

| Output power                                     | 8   | 11  |     | dBm                     |

| Harmonics distortion                             |     |     | -20 | dBc                     |

| Input impedance                                  |     | 100 |     | $[\Omega]$ Differential |

| Output impedance                                 |     | 100 |     | $[\Omega]$ Differential |

| Input reflection coefficient (S <sub>11</sub> )  |     |     | -10 | dB                      |

| Output reflection coefficient (S <sub>22</sub> ) |     |     | -10 | dB                      |

| Temperature                                      | 0   | 27  | 100 | °C                      |

#### Power amplifier

The power amplifier is the final block of the transmitter, which should produce an output power as high as possible. Important for this device is the output impedance and corresponding matching, because it will be the transmitter output.

At the output of this block all the top level target specifications have to be respected: bandwidth, harmonic distortion and reflection coefficient; whole in the temperature range of 0 - 100°C.

| Power amplifier                                  |     |     |     |                  |

|--------------------------------------------------|-----|-----|-----|------------------|

| Specs                                            | min | nom | max | Comment          |

| Input frequency                                  | 92  | 94  | 96  | GHz              |

| Output frequency                                 | 92  | 94  | 96  | GHz              |

| Bandwidth                                        | 2   |     |     | [GHz] -3dB       |

| Input power                                      | 8   | 11  |     | dBm              |

| Output power                                     | 15  | 20  |     | dBm              |

| Harmonics distortion                             |     |     | -20 | dBc              |

| Output impedance                                 |     | 100 |     | [Ω] Differential |

| Output reflection coefficient (S <sub>22</sub> ) |     |     | -10 | dB               |

| Temperature                                      | 0   | 27  | 100 | °C               |

Phase noise is not specified explicitly, due to the frequency multiplication, it is simply the phase noise of the input signal plus 12dBc/Hz.

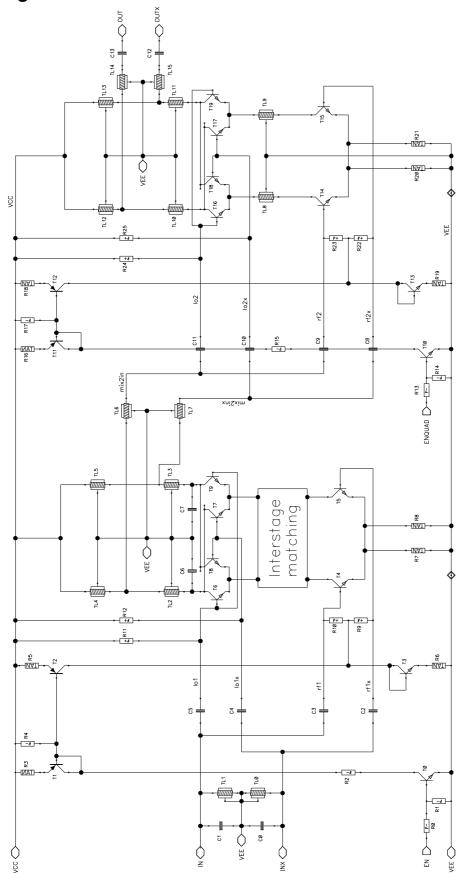

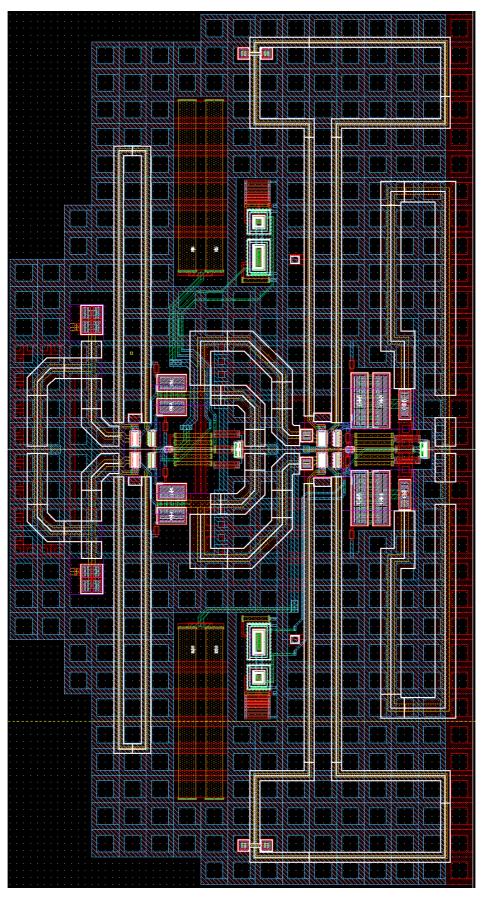

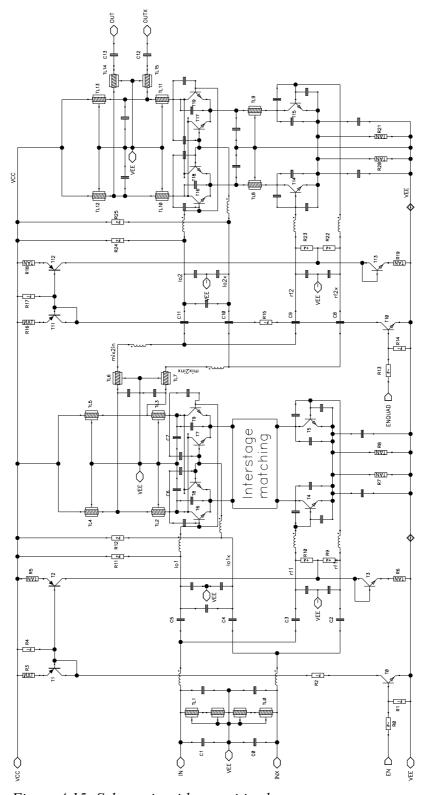

#### <u>1.3.3</u> Transmitter for imaging in body scanner

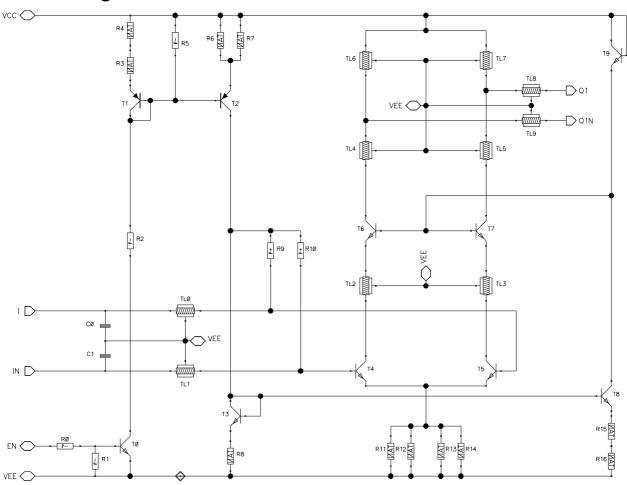

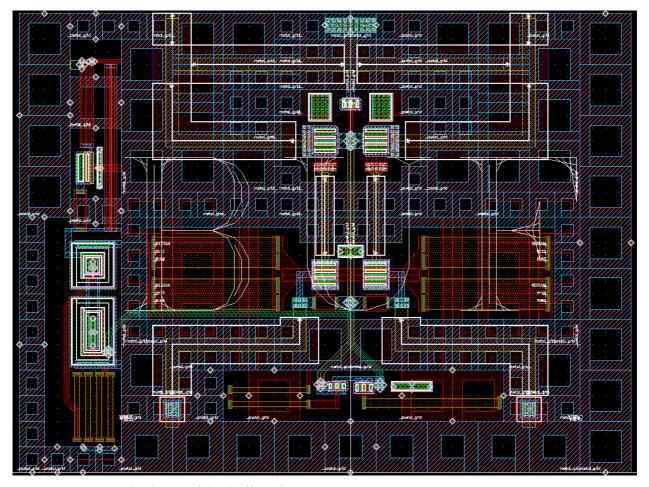

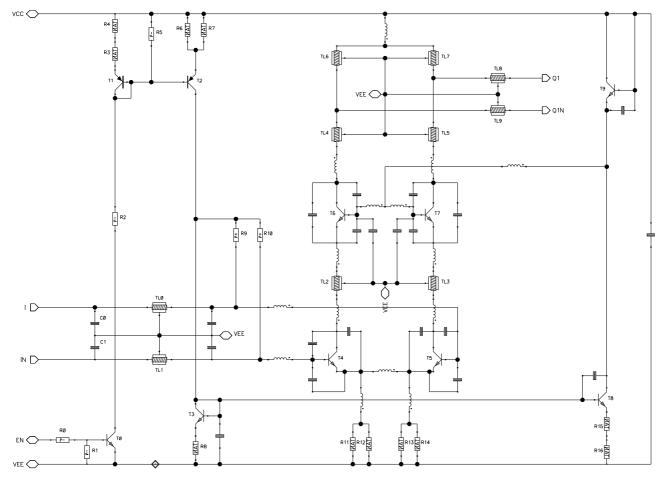

The design work for this thesis didn't start from white space, but a schematic of a transmitter for imaging in body scanner was given as starting point [Tiebout:11]. The structure of thesis transmitter is quite similar to that one of body scanner, only an input buffer was removed. Performances of the transmitter for imaging in body scanner have been verified and compared with measurement on the real chip. This

can let us trust in simulations results.

The working frequency the body scanner applications is roughly 78GHz, and the used technology is the same Infineon B7HF200, so the distance of this transmitter from the goal of the thesis is not so great. For these reasons the circuits suggestion was seriously taken into account, and the schematics of the starting transmitter have been analysed and than tuned to the goal frequency of the new transmitter.

## Chapter 2: Technology overview

In the integrated circuit technologies, BiCMOS (also called BiMOS) refers to the integration of bipolar junction transistors and CMOS technology into a single integrated circuit device. Also a pure bipolar integrated circuit technology, as B7HF200, exists as manufacturing process. These kind of planar processes let to produce bipolar transistors with very high cut-off frequency (around some hundreds of GHz), by using some particular construction technique like isolation regions between adjacent components separated by oxide spacer, emitter and extrinsic base regions, or self-aligned processing techniques. All these innovative construction techniques have made these type of products more expensive respect to CMOS wafers, but also more well performing.

Historically, fabricating both bipolar and metal-oxide-semiconductor (MOS) transistors in a single integrated circuit proved difficult and expensive. Therefore, until recently, most of integrated circuits have used one or the other, according to application requirements [Int:1]. This "all one or the other" choice necessarily entailed an engineering compromise in many cases, particularly for mixed-signal integrated circuits. If compared to the ideal case, where the type of each transistor could be freely and independently chosen according to the function and purpose of that particular transistor in the circuit (as it can be in circuits built of discrete components, albeit at much higher cost and size than an integrated circuit design) it appears as an unpleasant situation.

Bipolar transistors offer high speed, high gain, and low output resistance, which are excellent properties for high-frequency analog amplifiers, whereas CMOS technology offers high input resistance and it is excellent for constructing simple, low-power logic gates.

For as long as the two types of transistors have existed in production, designers of circuits utilizing discrete components have realized the advantages of integrating the two technologies. However, lacking an implementation into integrated circuits, the application of this free-form design was restricted to fairly simple circuits. Discrete circuits of hundreds or thousands of transistors quickly expand to occupy hundreds or thousands of square centimetres of circuit board area, and for very high-speed circuits, such as those used in modern digital computers, the distance

between transistors (and the minimum capacitance of the connections between them) also makes the desired speeds grossly unattainable, so that if these designs cannot be built as integrated circuits, then they simply cannot be built.

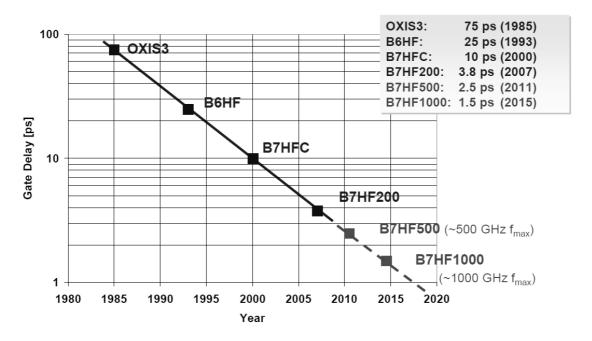

Figure 2.1: Moorse's law for SiGe HF technology [Lachner:07]

In the 1990s, modern integrated circuit (IC) fabrication technologies began to make BiCMOS a reality. This technology rapidly found application in amplifiers and analog power management circuits, and it has also some advantages in digital logic. BiCMOS circuits use the characteristics of each type of transistor most appropriately. Generally this means that high current circuits use metal-oxide-semiconductor field-effect transistor (MOSFETs) for efficient control, and portions of specialized very high performance circuits use bipolar devices.

In recent years, improved technology has made possible to combine complimentary MOS transistors and bipolar devices in a single process at a reasonable cost.

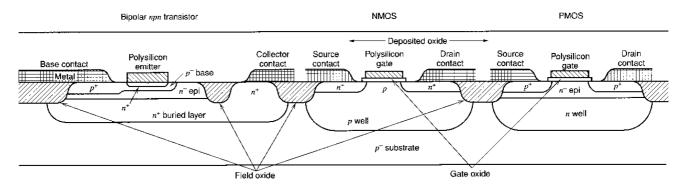

A cross section of a typical BiCMOS process is shown in figure 2.2. A single nepitaxial layer is used to implement both the PMOS transistors and bipolar npn transistors. Its resistivity is chosen so that it can support both devices. An n<sup>+</sup> buried layer is deposited below the epitaxial layer to reduce the collector resistance of the bipolar device, which simultaneously increases the immunity to latchup. The p<sup>-</sup> buried layer (or oxide) between transistors, improves the packing density, because the collector-collector spacing of the bipolar devices can be reduced. It comes at the expense of an increased collector-substrate capacitance.

Figure 2.2: Cross section of a high-performance BiCMOS process [Book:1]

Actually in a typical high-frequency, low voltage, oxide-isolated BiCMOS process, the bipolar devices can also be isolated by using the same local-oxidation technique used for CMOS. This approach has the advantage of greatly reducing the bipolar transistor collector-substrate parasitic capacitance, because the heavily doped high-capacitance regions, near the surface, are now replaced by low-capacitance oxide isolation. The device can also be packed much more densely on the chip. [Book:1] Afterwards this technology opens a wealth of new opportunities, because it is now possible to combine the high-density integration of CMOS with the current-driving capabilities and high cut-off frequency of these bipolar transistors.

#### 2.1 Infineon's B7HF200

Infineon's B7HF200 is a high performance SiGe bipolar technology with automotive qualification for ultra high frequency applications. They have developed this high-performance SiGe bipolar technology mainly for automotive radar applications: it is optimized for a balanced compromise between the most important transistor parameters to achieve good circuit performance at 77GHz. Special care has been taken on manufacturability and reliability, to achieve the high quality requirements needed for automotive applications. [Boeck:04]

The SiGe bipolar is also the technology of choice for many high frequency applications like mobile communications, optical data communications at 10 and 40 Gbit/s, or microwave radio links. Recent advances in technology development enabled impressive transistor parameters like maximum oscillation frequencies and transit frequencies in excess of 300GHz and even gate delay times down to 2ps. Therefore, even very high frequency applications like wireless LANs at 60GHz and radar systems around 77GHz, which could only be realized in expensive III-V technologies up to few years ago, seem now to become feasible in a low cost silicon

based technology in a highly integrated manner. Especially radar systems for the automotive industry could become a new mass market, if the system costs can be reduced sufficiently.

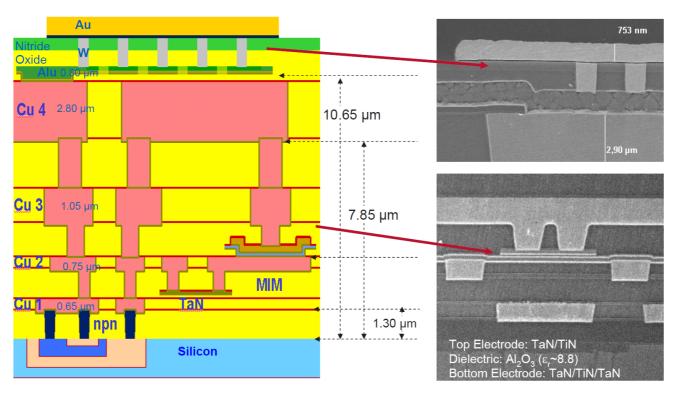

The B7HF200 technology provides several additional devices to the high speed npn transistors. Three types of npn devices with different  $f_T$  - BV<sub>CE0</sub> trade-offs are offered by modifying the collector implant dose, and one vertical pnp. Two poly resistors with sheet resistances of 150 and  $1000\Omega/\text{sq}$ . and a TaN thin film resistor with  $20\Omega/\text{sq}$ . are available. A MIM capacitor with an  $Al_2O_3$  dielectric and a specific capacitance of 1.4 fF/ $\mu$ m<sup>2</sup> is integrated in a Cu metallization consisting of 4 layers with thicknesses of 600, 600, 1200, and 2500 nm, respectively.

Figure 2.3: Metallization cross section of B7HF200 SiGe process [Lachner:07]

The technology has a 0.35µm lithography, a transit frequency of 200 GHz, a maximum oscillation frequency of 275 GHz and a ring oscillator gate delay of 3.5ps. Further public informations are available from [Infineon:06].

| <u>B7HF200</u>                   |                      |  |  |  |

|----------------------------------|----------------------|--|--|--|

| Process type                     | 200 GHz SiGe bipolar |  |  |  |

| Lithography node                 | 0.35μm               |  |  |  |

| Substrate material               | p-Silicon 20 Ωcm     |  |  |  |

| Wafer diameter                   | 8" (200 mm)          |  |  |  |

| f <sub>T</sub> /f <sub>max</sub> | 200/250 GHz          |  |  |  |

| <u>B7HF200</u>                             |                                                                        |  |  |  |

|--------------------------------------------|------------------------------------------------------------------------|--|--|--|

| Min. gate delay                            | 3.7 ps                                                                 |  |  |  |

| Effective emitter width                    | 0.18μm                                                                 |  |  |  |

| Base layer                                 | SiGe:C                                                                 |  |  |  |

| Current drive capability of NPN transistor | up to 6.5 mA/μm <sup>2</sup>                                           |  |  |  |

| Isolation                                  | Deep & shallow trench                                                  |  |  |  |

| Devices                                    | UHS / HS / MS / HV NPN, Poly-<br>R, Met- R, MIM-Cap, Varactor,<br>VPNP |  |  |  |

| Metallization                              | 4 layers of Cu (Dual Damascene)<br>metal + 1 top layer of Al metal     |  |  |  |

| Thick last metal                           | 2.8 μm Cu                                                              |  |  |  |

| Bonding pads                               | Au lift off                                                            |  |  |  |

| Supply voltage                             | 2.7 to 5.75 V                                                          |  |  |  |

| Tungsten filled contacts                   |                                                                        |  |  |  |

| Bipolar transistors |                                                                                                                                                                                      |                                          |  |  |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|--|--|--|

| UHS NPN             | $BV_{CE0}$<br>$BV_{CES}$<br>$f_T$ (@ $j_C$ = 6.5 mA/ $\mu$ m <sup>2</sup> )<br>$f_{max}$                                                                                             | ≥ 1.2 V<br>≥ 4.8 V<br>200 GHz<br>250 GHz |  |  |  |  |

| HS NPN              | $BV_{CE0}$<br>$BV_{CES}$<br>$f_T$ (@ $j_C$ = 5.0 mA/ $\mu$ m <sup>2</sup> )<br>$f_{max}$                                                                                             | ≥ 1.4 V<br>≥ 5.8 V<br>170 GHz<br>250 GHz |  |  |  |  |

| HV NPN              | $\begin{array}{l} \text{BV}_{\text{CE0}} \\ \text{BV}_{\text{CES}} \\ \text{f}_{\text{T}} \ (@ \ j_{\text{C}} = 0.5 \ \text{mA/}\mu\text{m}^2) \\ \text{f}_{\text{max}} \end{array}$ | ≥ 3.3 V<br>≥ 11.5 V<br>35 GHz<br>120 GHz |  |  |  |  |

| VPNP                | BV <sub>CE0</sub><br>BV <sub>CES</sub><br>f <sub>T</sub><br>V <sub>early</sub>                                                                                                       | ≤ -6.5 V<br>≤ -10 V<br>3.5 GHz<br>35 V   |  |  |  |  |

| Passive devices                                                                   |                                                                                                                 |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Poly Resistor 1 p <sup>+</sup> - Poly                                             | $R_s = 150 \Omega/sq \pm 10\%$                                                                                  |

| Poly Resistor 2 p <sup>-</sup> - Poly                                             | $R_s = 1000 \Omega/sq \pm 10\%$                                                                                 |

| Low Tolerance Metal Resistor TaN                                                  | $R_s = 20 \Omega/\text{sq} \pm 5\%$                                                                             |

| Varactor<br>Spec. Capacitance<br>Capacitance Ratio 0.0 V/-5.0 V<br>Quality Factor | $BV_{CA} > 5 V$<br>$C_{VAR} = 2.3 \text{ fF/}\mu\text{m}^2 @ V_{PN} = 0 V$<br>(DC/C) V = 2.2<br>Q @ 77  GHz > 8 |

| Passive devices                                               |                                                                                                        |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Linear Capacitor (MIM)                                        | -5.5 V < V < +5.5 V<br>C <sub>area</sub> = 1.4 fF/μm <sup>2</sup><br>Q @ 2 GHz > 50<br>Q @ 24 GHz > 25 |

| Inductors<br>Coil dia 135 μm 1.7 nH<br>Coil dia 60 μm 0.25 nH | Q @ 2 GHz > 15<br>Q @ 24 GHz > 20                                                                      |

#### 2.2 Bipolar characteristics

In the technology used for this transmitter different type of bipolar transistors are present: high speed npn, high voltage npn and high voltage pnp too. The basic physical phenomena of these devices are left to specialized theory books, but I will try to do a short introduction to them, with some graphs of the characteristics.

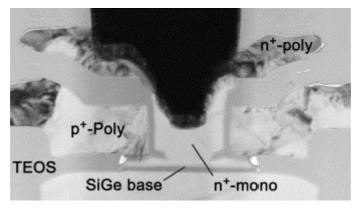

Regarding the physical structure of a BiCMOS npn, we have briefly discussed it in a previous section, but I would like to add some other information on the B7HF200 high speed npn. These transistors have a double-polysilicon self-aligned emitter-base configuration, with an effective emitter width of  $0.18\mu m$ , which also achieves small device parasitics. The collector doping level determines trade-off between breakdown voltage and cut-off frequency  $f_T$ , and typically it is used for increase the frequency.

Figure 2.4: TEM cross section of the emitter-base complex of a transistor [Forstner:08]

The SiGe:C base of the transistors is implemented by selective epitaxial growth; SiGe:C is used to reduce the base resistance and, at the same time, improves gain and frequency response by reducing the base doping. Moreover the transistors have a mono-crystalline emitter contact in the active transistor region, without any interface native oxide, to guarantee a small emitter resistance and a reproducible interface between emitter contact and active silicon area. The emitter-base isolation

is improved to increase the base current and the manufacturability of technology.

Given some other information on the structure of SiGe devices, now it will be shown some measured characteristic about these transistors, which have been got from some papers. [Boeck:04] [Lachner:07] [Forstner:08]

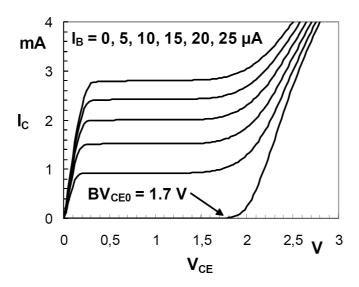

Figure 2.5 gives the output characteristics of the transistors with an area of  $A_E = 0.14 \times 2.6 \,\mu\,m^2$  . The collector-emitter breakdown voltage BV<sub>CEO</sub> is 1.7V.

Figure 2.5: Output characteristics [Boeck:04]

In the figure 2.6, instead it can be seen the measure of the common-emitter current gain, generally represented by  $\beta_F$  or  $h_{fe}$ . It is the ratio of the collector current to the base current in forward-active region.

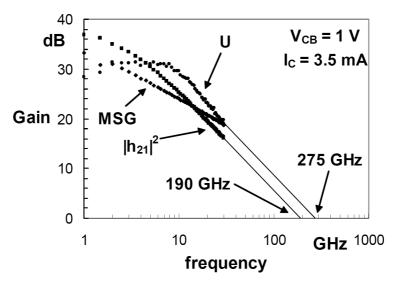

Figure 2.6: Measured gains vs. frequency [Boeck:04]

The transistor has been measured with a bias where the maximum oscillation frequency has its optimum, and an area  $A_E = 0.14 \times 2.6 \,\mu\,m^2$ . The graph show a

decrease of current gain already at 1GHz, with an expected transient frequency around the 190GHz.

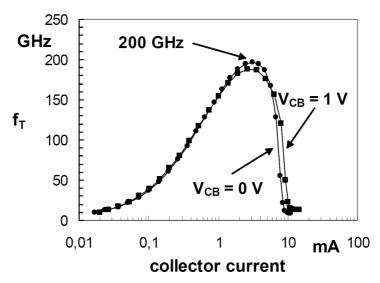

The highest transient frequency can be reached only by an optimum emitter current density, as can be seen in figure 2.7 for the same transistor of the previous measures.

Figure 2.7: Cut-off frequency  $f_T$  vs. collector current [Boeck:04]

In our differential circuits we will not use the bipolar transistors with a current input signal, but with a voltage signal. For this reason it is also important to have a look on how the collector current changes with the variation of the emitter-base voltage.

Its expression in the active region is  $I_C = I_S e^{\frac{V_{BE}}{V_T}}$

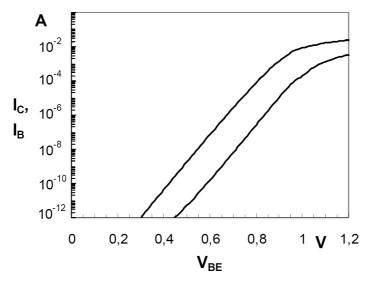

Figure 2.8: Gummel characteristics of the transistor [Boeck:04]

The typical Gummel characteristics of transistors is shown in figure 2.8, it has been measured always for an emitter area of  $A_E = 0.14 \times 2.6 \,\mu\,m^2$ . The devices have ideal transfer characteristics down to the pA regime and the typical current gain is 250.

A more explicit value that is often used in radio frequency circuit design is the transconductance gain, that can be calculated by the formula:

$$g_{m} = \frac{\partial I_{C}}{\partial V_{BE}} = \frac{I_{C}}{V_{T}}$$

The transconductance is direct proportional to the collector current, so for increase the gain of the transistor it is necessary to increase the collector current. Increase the current means to increase the emitter length, due to optimum current density requested to reach the higher cut-off frequency.

Working at frequency near to 100GHz, like for the amplification stage of the transmitter, we have to expect a quite high decrease of the transconductance value due to the characteristic of the bipolar transistor, which is near to the transient frequency. Higher current will be needed for the same amplification.

Concerning the pnp transistors, these have a vertical structure and they are typically used only into biasing or auxiliary circuits, due to their not high transient frequency (compared to npn).

#### 2.3 Chip packaging and measure problems

To build an integrated circuit, the individual devices formed by the planar process must be interconnected by a conducting path. This procedure is usually called interconnection or metallization.

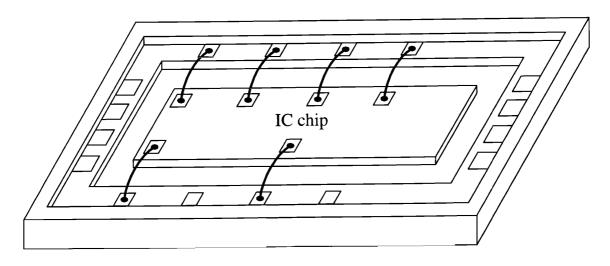

Figure 2.9: Wire bonding packaging

As the performances of individual transistors improves the overall circuit, performances can be limited by the interconnections between the transistors, rather than by the transistors themselves. Moreover other performance limits can be introduced by the packaging and the wire bonding.

After that the wafer fabrication process is completed, it is diced into individual circuits or chips, often by fracturing the silicon along weak crystallographic planes after scribing the surface with a sharp, diamond-tipped instrument. Afterwards in the most straightforward packaging approach, the back of each chip is soldered to a package, and wires are connected or bonded from the leads on the package to the metal pads on the face of the semiconductor chip. Finally, the package is sealed with a protective ceramic, a metal cover or with plastic, and then the circuit undergoes to electrical testing and measurement.

By working at such high frequency for try to have some fine measurement results, almost comparable to the simulation, a lots of parasitic elements have to be taken into account, especially that ones introduced by the bonding process.

Concerning the internal connection, these metal wires are, in practice, a series of a resistor and an inductor. Their values depend on the length of the wire: as longer will be the path, higher will be the resistance and the inductance. However the main parasitic effect is due to the inductance, because at high frequency its impedance becomes relevant. This issues is also present in wires that connect the chip to the packaging. They are longer than internal connections, so their effect is bigger. Also an external capacitive parasitic element has to be added: this is due to the metal bonding PADs, which creates a capacitive effect with the ground reference plane and with substrate (also connected to ground).

In the end I can say that to prevent not-wanted attenuations, impedance changes or other strange behaviours, all the most relevant parasitic elements have to be taken into account, by adding them into the circuit schematic.

#### 2.4 Use of transmission lines

Circuits operating at high frequencies, for which the circuit dimensions are not small relative to the wavelength, may not be treated as an interconnection of lumped passive or active components with unique voltages and currents, defined at any point in the circuit. In this situation the circuit dimensions aren't small enough so that there is negligible phase change from one point in the circuit to another. [Book:2]

From the electromagnetic and transmission line theories we know that in some situations we can have a signal reflection due to a load mismatch. Besides, in order to deliver the maximum power to the load we must have an impedance matching, which means that the impedance seen from the load, toward the circuits, has to be complex conjugate of the load  $Z_m = Z_l^*$ .

Typical matching networks used at high frequency are the "lumped elements matching network", which are made of reactive elements as capacitors and inductors (L-network,  $\Pi$ -network, T-network) [Book:3]. Passing the 10 or 20 GHz the sizes of lumped elements become comparable to the use of transmission line as matching networks. In particular the inductors construction is the main problem, because with the increasing of the frequency we have more electromagnetic interferences and less component's quality factor, due to parasitic element, tolerance or mismatch increasing.

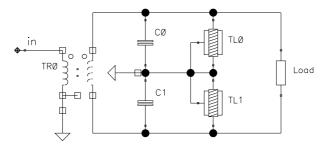

Afterwards in the EHF and in the last part of SHF bandwidths, the matching networks are made with planar transmission lines for integrate circuits. Typically this networks are single-stub shunt tuning, double-stub tuning or other similar configurations, whose theory and designing rules can be found on the theory books [Book:2].

Integrated circuits transmission lines are also used to connect different device on the same wafer, where possible. This happen because at high frequency the behaviour of a transmission line is much more comprehensible and reliable than a simple wire of metal, whose electrical characteristic (usually inductive) can be influenced by electromagnetic coupling or other parasitic effects due to the components around it.

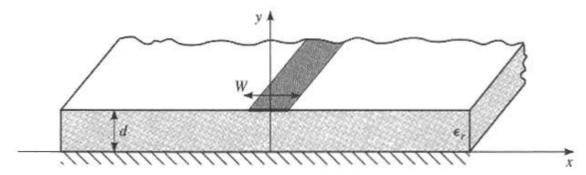

Figure 2.10: Microstrip transmission line

Microstrip transmission lines are one of the most popular type of planar transmission lines, primarily because it can be fabricated by photolithographic

processes and it is easily integrated with other passive and active microwave devices. The geometry of a microstrip line is shown in Figure 2.10. A conductor of width W is printed on a thin, grounded dielectric substrate of thickness d and relative permittivity  $\epsilon_r$ .

The characteristic impedance of this kind of transmission lines is quite difficult to calculate by hands, for this reason it is typically simulated with 3D electromagnetic simulation software. Anyway the characteristic impedance depends on the width of the line (W), the substrate thickness (d) and its relative permittivity (that slowly changes with the signal carrier frequency). These transmission lines have also an attenuation due to both dielectric and conductor losses: their value depends on conductor and dielectric electrical characteristics.

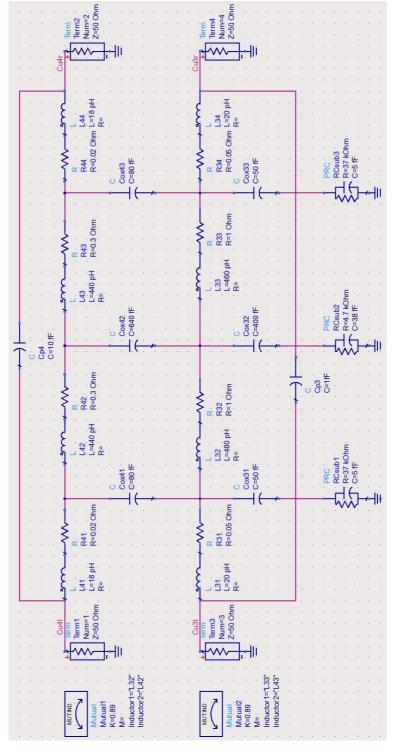

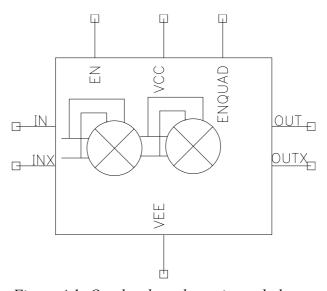

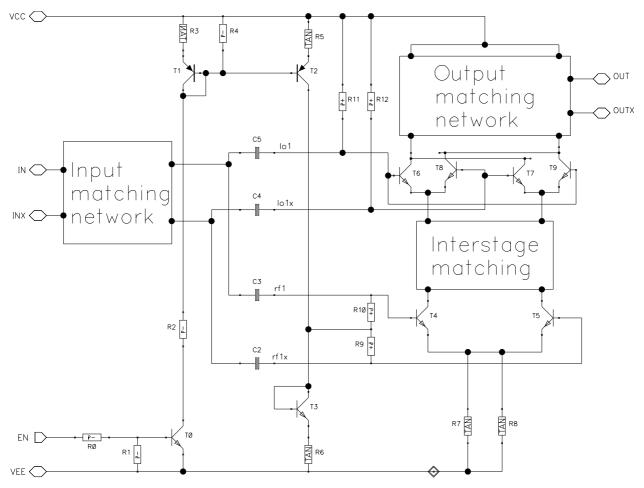

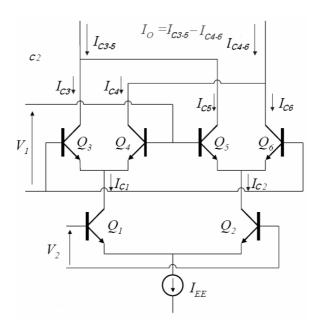

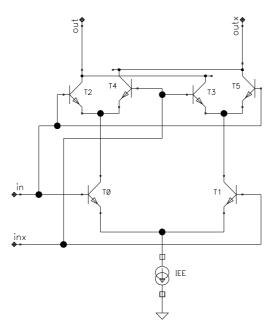

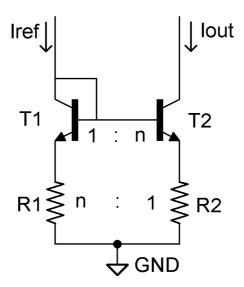

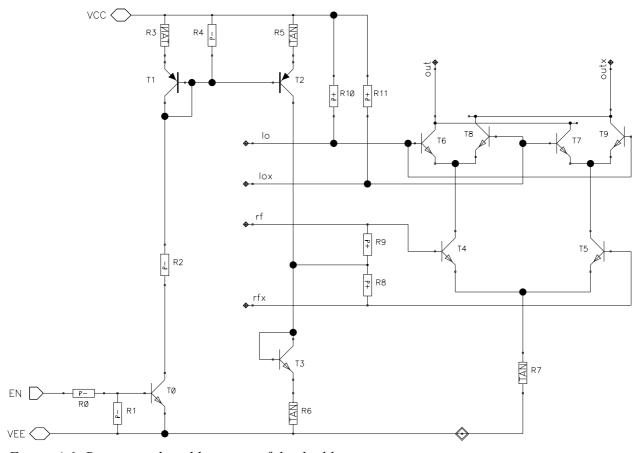

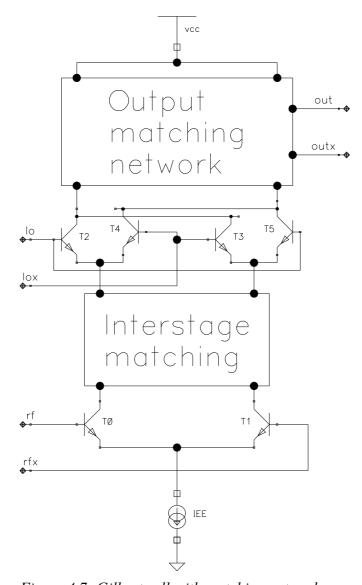

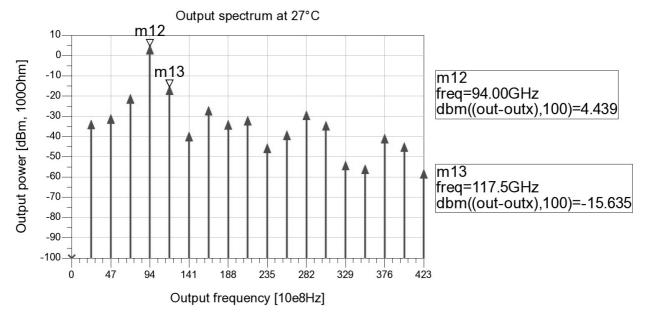

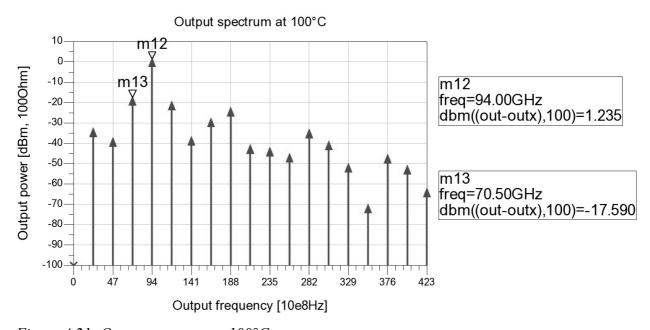

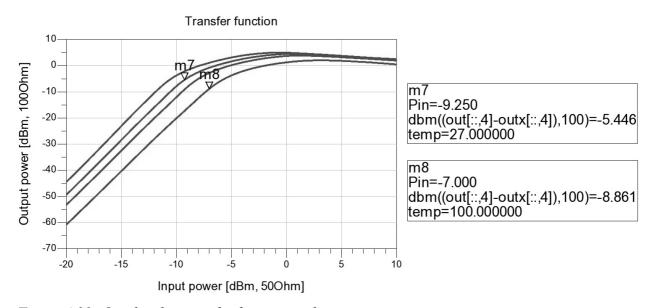

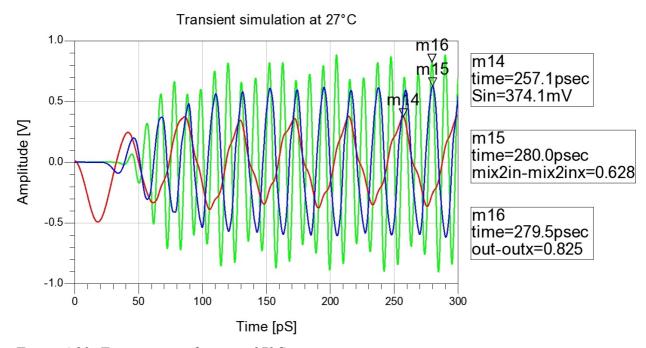

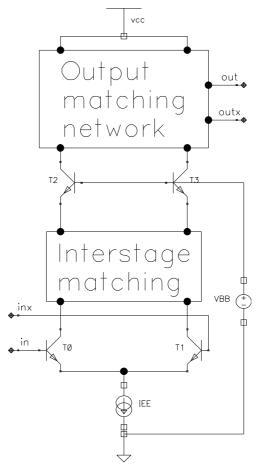

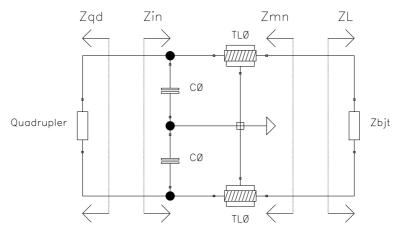

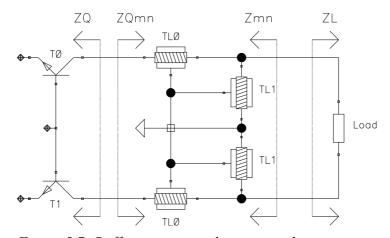

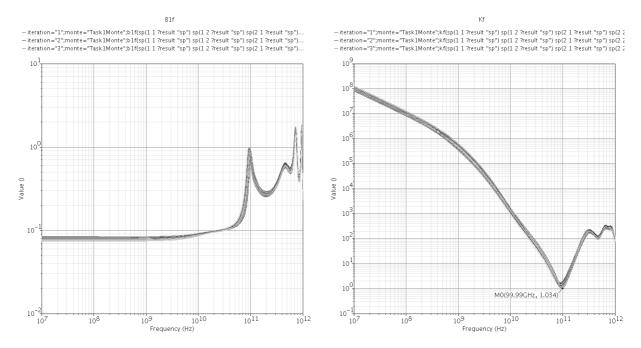

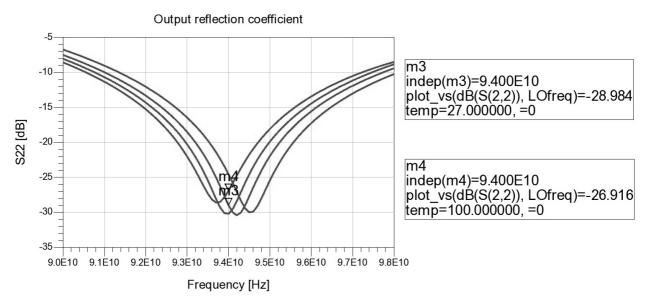

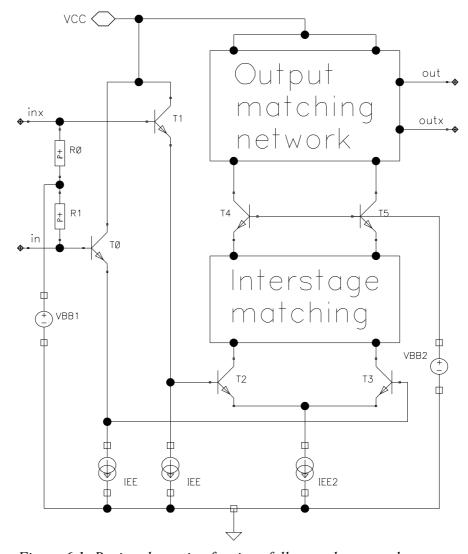

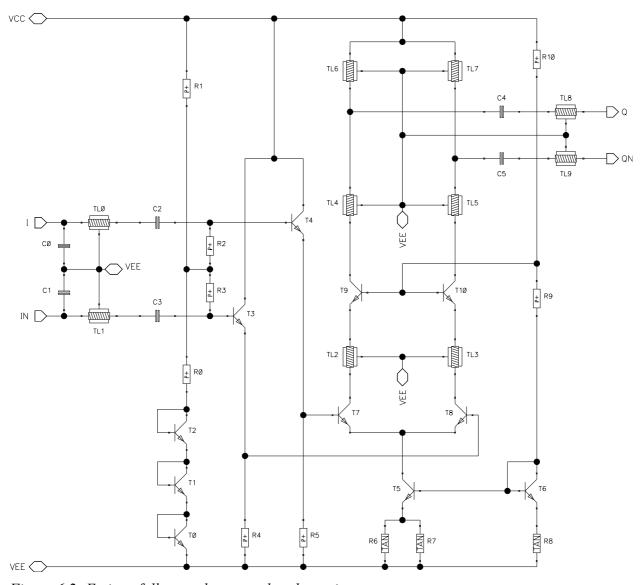

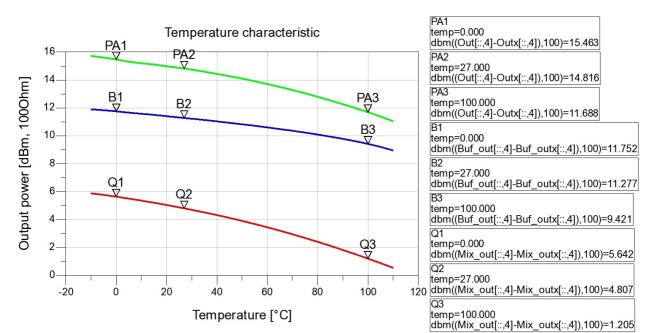

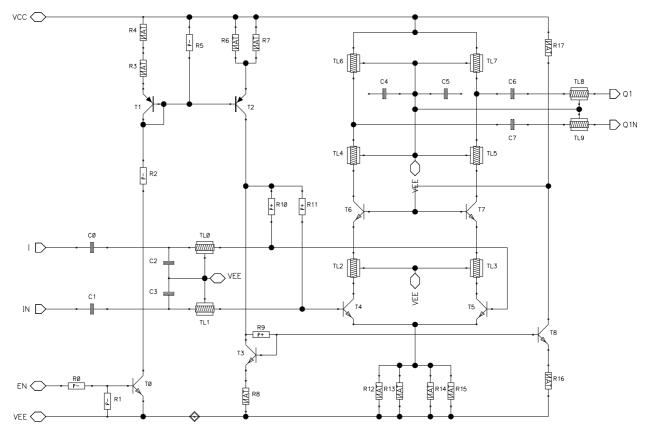

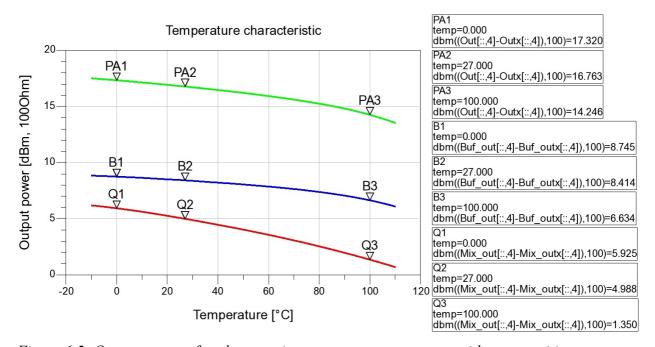

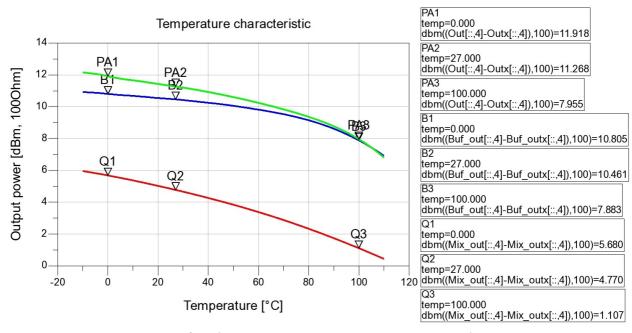

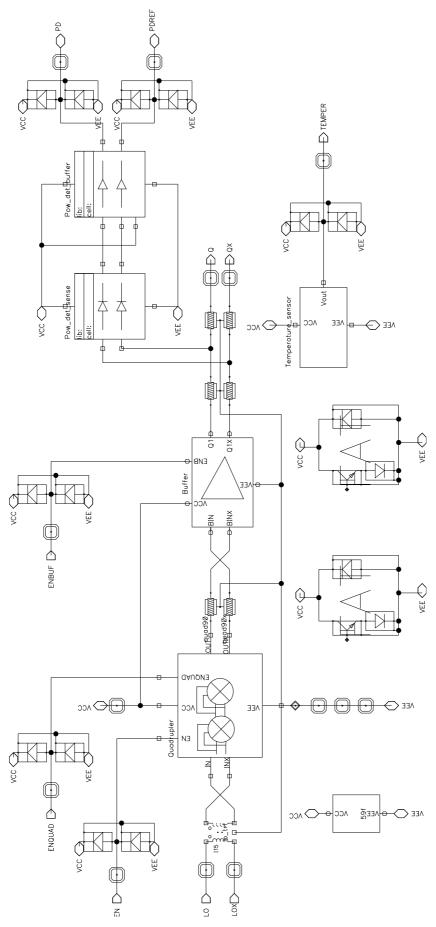

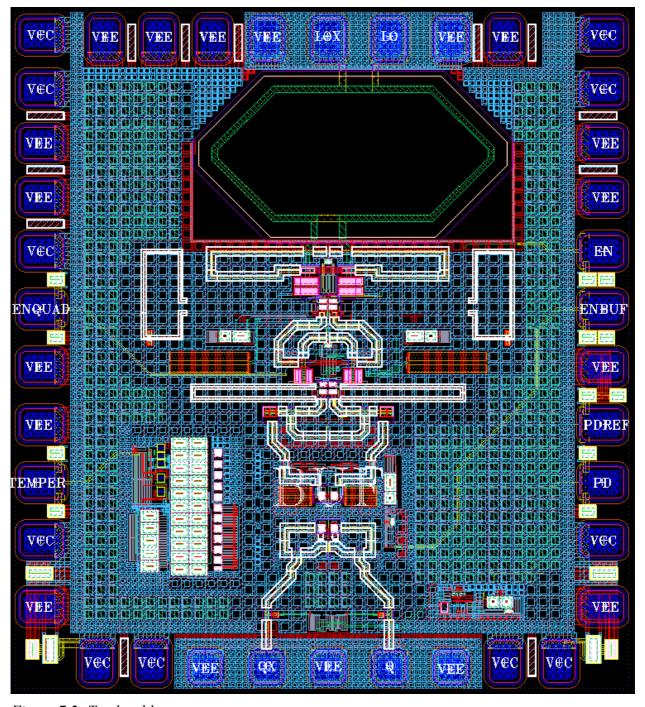

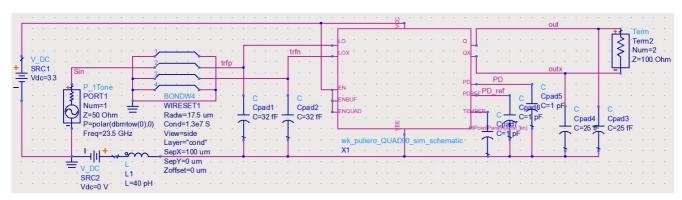

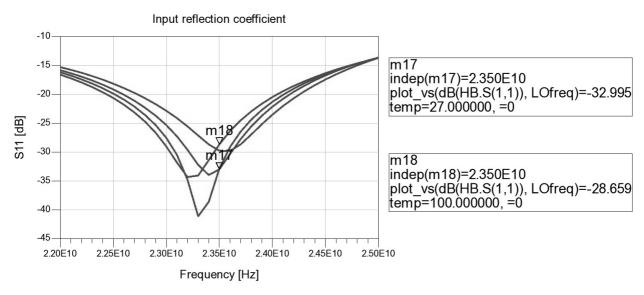

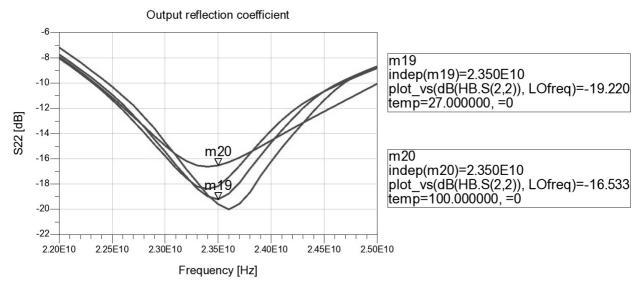

Into Infineon's B7HF200 technology, the four-layer metallization provides low-loss passive components, such as spiral inductors and transmission lines (compared to the much more complex metal stack required for advanced CMOS processes). In particular the lower metal layers can serve as low-loss ground planes for microstrip lines. Therefore a metal layer M4 over a metal layer M2 is used for the design of the transmission lines.