### UNIVERSITÀ DEGLI STUDI DI PADOVA

Facoltà di ingegneria industriale

**NTNU – Trondheim** Norwegian University of Science and Technology

Corso di Laurea Magistrale in Ingegneria Elettrica Electrical Engineering Master Degree

STUDY AND DESIGN OF AN INVERTERS SERIES CONFIGURATION COMPOSED BY THREE-PHASE AND SINGLE-PHASE MULTILEVEL UNITS FOR HIGH POWER APPLICATIONS

(STUDIO E PROGETTAZIONE DI UNA CONFIGURAZIONE DI INVERTER IN SERIE COMPOSTA DA UNITÀ MULTILIVELLO TRIFASE E MONOFASE PER APPLICAZIONI A ELEVATA POTENZA)

Laureando - Graduating student

Mattia Filippini

Relatore - Supervisor **Prof. Nicola Bianchi** Co-relatore - Co-supervisor

Prof. Marta Molinas

ANNO ACCADEMICO 2014/2015

# Contents

| 1        | Intr              | Introduction                      |                                                 |    |  |  |

|----------|-------------------|-----------------------------------|-------------------------------------------------|----|--|--|

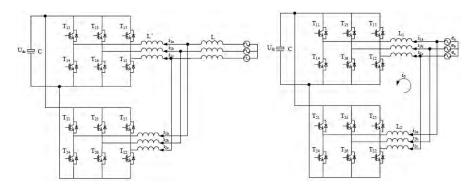

| <b>2</b> | er topologies     | 13                                |                                                 |    |  |  |

|          | 2.1               | rters paralleling                 | 13                                              |    |  |  |

|          |                   | 2.1.1                             | Parallel concept                                | 13 |  |  |

|          |                   | 2.1.2                             | Interleaving                                    | 14 |  |  |

|          |                   | 2.1.3                             | Circulating current                             | 16 |  |  |

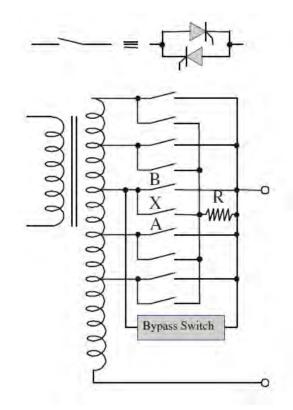

|          |                   | 2.1.4                             | Zero Sequence Blocking Transformer (ZSBT)       | 18 |  |  |

|          | 2.2               | 2.2 Classic multilevel topologies |                                                 | 19 |  |  |

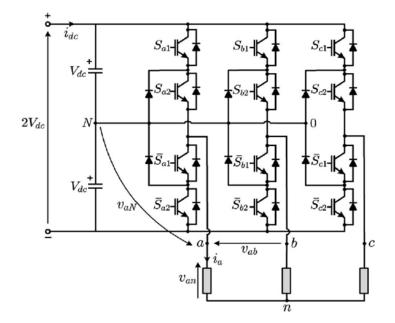

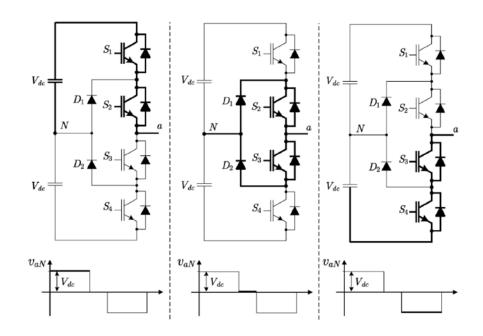

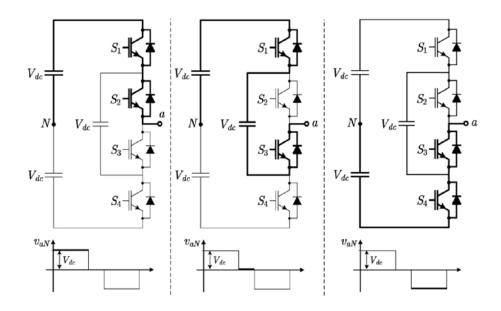

|          |                   | 2.2.1                             | 3L-NPC: neutral point clamped                   |    |  |  |

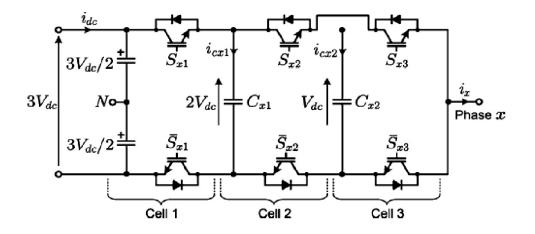

|          |                   | 2.2.2                             | 3L-FC: Flying capacitor                         |    |  |  |

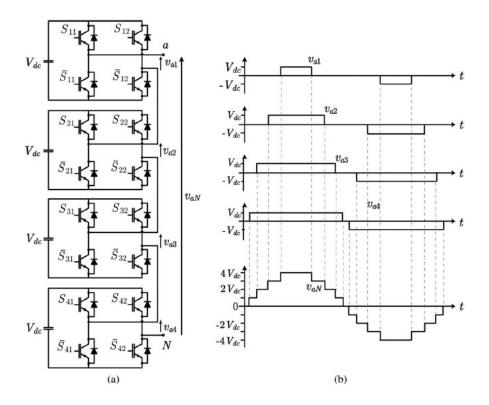

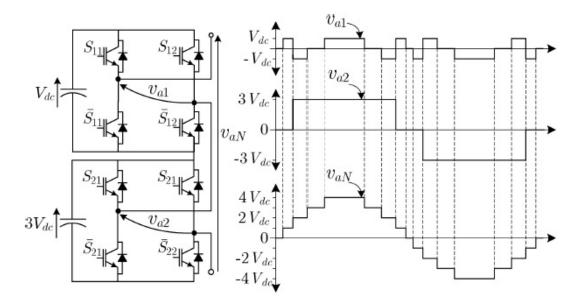

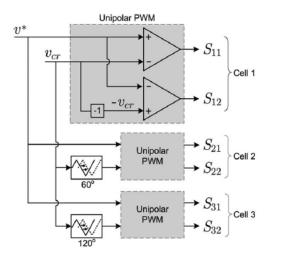

|          |                   | 2.2.3                             | CHB: Cascaded H-bridge                          | 25 |  |  |

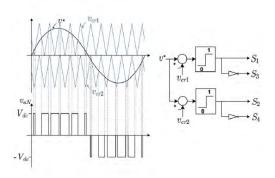

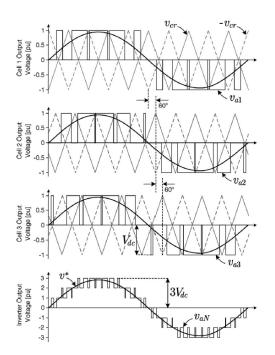

|          |                   | 2.2.4                             | Modulation strategies for multilevel converters |    |  |  |

|          | 2.3               | Hybrid                            | l and other series configurations               |    |  |  |

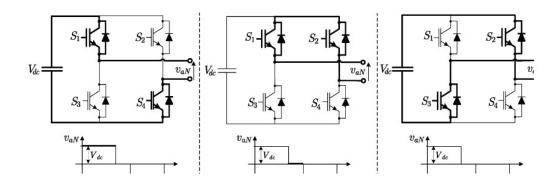

|          |                   | 2.3.1                             | ANPC structure                                  |    |  |  |

|          |                   | 2.3.2                             | MMC structure                                   | 31 |  |  |

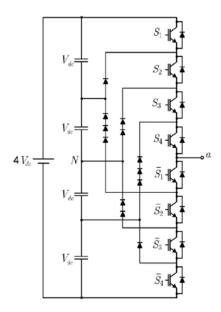

|          |                   | 2.3.3                             | Asymmetrical CHB and FC                         | 31 |  |  |

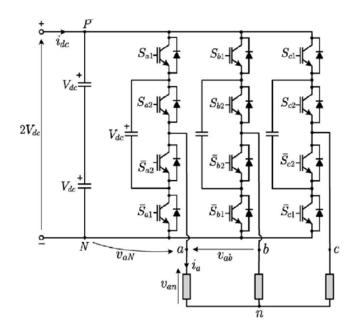

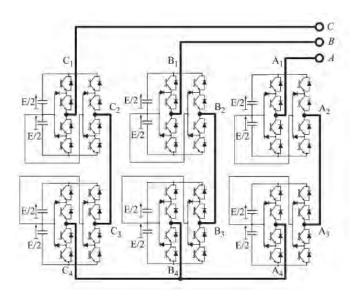

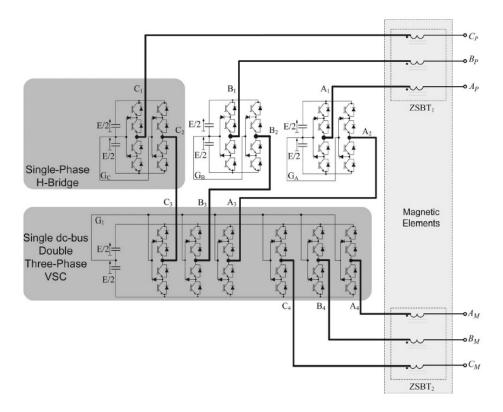

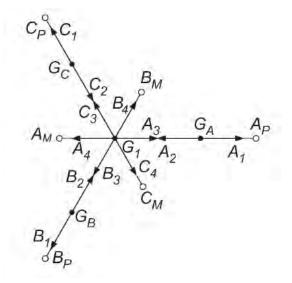

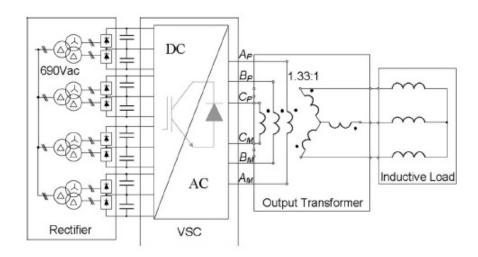

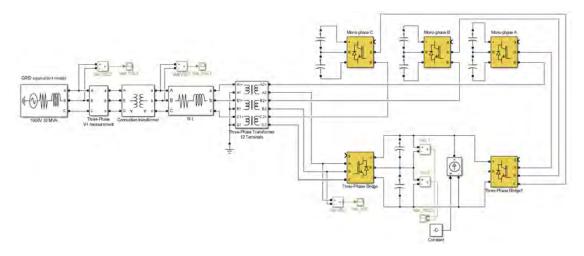

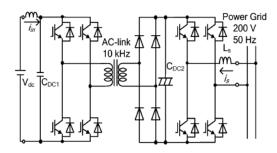

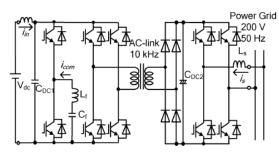

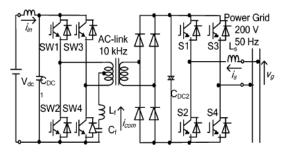

| 3        | Selected topology |                                   |                                                 |    |  |  |

|          | 3.1               |                                   | uction $\ldots$                                 | 33 |  |  |

|          | 3.2               | Proper                            | ties of this configuration                      | 36 |  |  |

|          |                   | 3.2.1                             | Voltage level                                   |    |  |  |

|          |                   | 3.2.2                             | Power plant                                     |    |  |  |

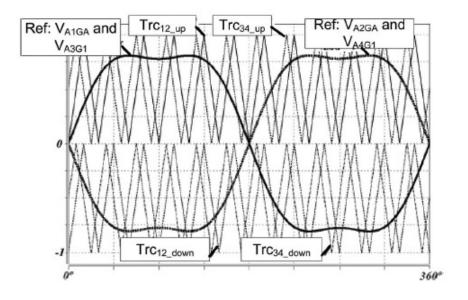

|          |                   | 3.2.3                             | Interleaving                                    | 40 |  |  |

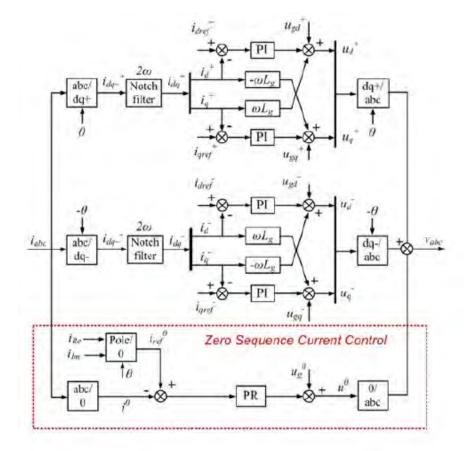

|          |                   | 3.2.4                             | Unbalanced grid                                 | 40 |  |  |

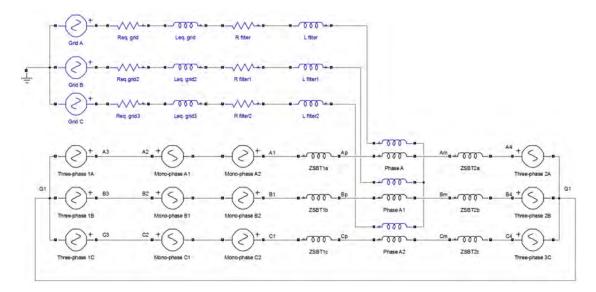

|          | 3.3               | Genera                            | al control problem                              | 43 |  |  |

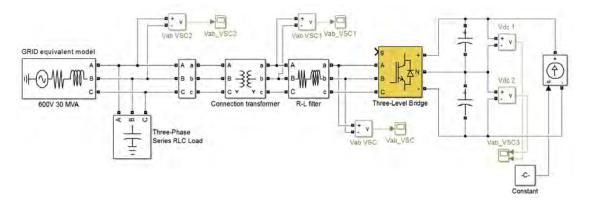

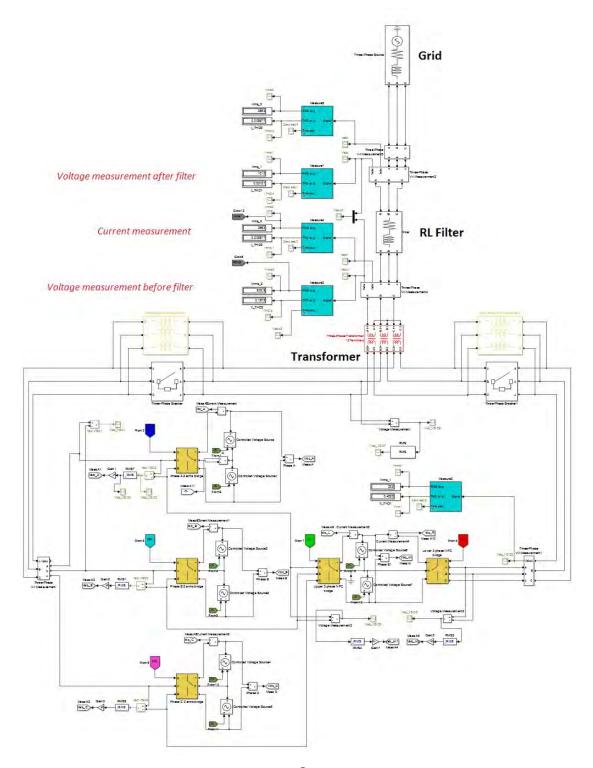

|          |                   | 3.3.1                             | System configuration                            | 43 |  |  |

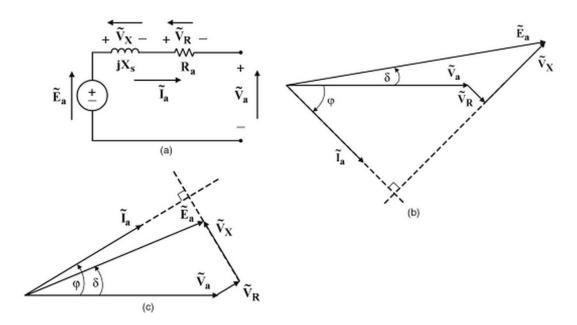

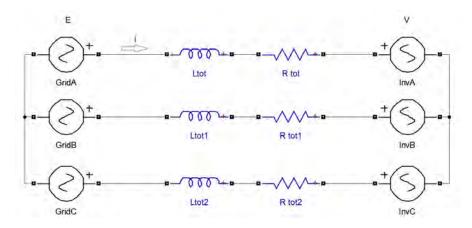

|          |                   | 3.3.2                             | Theoric control                                 | 45 |  |  |

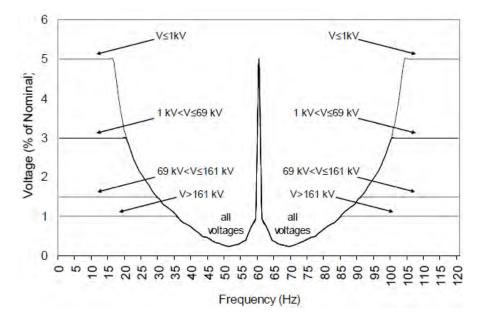

| 4        | Grid              | d mode                            | el and filter impedance                         | 51 |  |  |

| •        | 4.1               |                                   | it system                                       |    |  |  |

|          | 4.2               |                                   | nodel                                           |    |  |  |

|          | 4.3               |                                   | impedance                                       |    |  |  |

|          |                   |                                   |                                                 |    |  |  |

| 5.3       Results       60         5.3.1       Pgenerated <plim< td="">       60         5.3.2       Pgenerated<plim< td="">       63         6       Control structure       69         6.1       Internal loops       69         6.2       Current loop P1 tuning       73         6.2.1       Results       74         6.3       PQ loops       76         6.3.1       Results       77         6.4       Soft starter       78         6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         8       Sources models       107         8.1.1       DC voltage sources       107         8.1.2       Power and current waveforms       109      <tr< th=""><th><b>5</b></th><th>Opt</th><th>imizat</th><th>ion</th><th>57</th></tr<></plim<></plim<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>5</b> | Opt                | imizat               | ion                                         | 57  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|----------------------|---------------------------------------------|-----|--|--|--|--|--|--|--|--|

| 5.3       Results       60         5.3.1       Pgenerated <plim< td="">       60         5.3.2       Pgenerated&gt;Plim       63         6       Control structure       69         6.1       Internal loops       69         6.2       Current loop P1 tuning       73         6.2.1       Results       74         6.3       PQ loops       76         6.3.1       Results       77         6.4       Soft starter       78         6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         8       Sources models       107         8.1.1       DC voltage sources       107         8.1.2       Power and current waveforms       109         8.2.1       Capacitors       129</plim<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | 5.1                | Proble               | em definition                               | 58  |  |  |  |  |  |  |  |  |

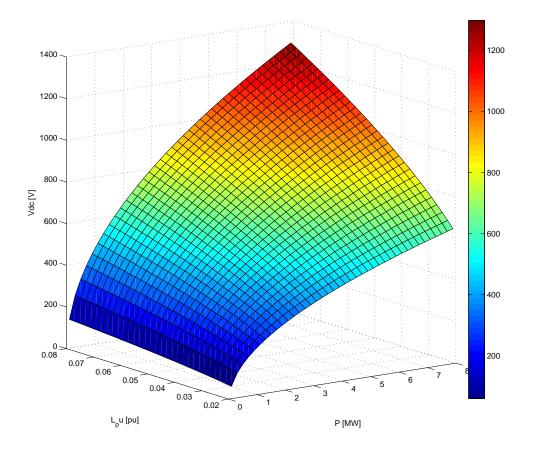

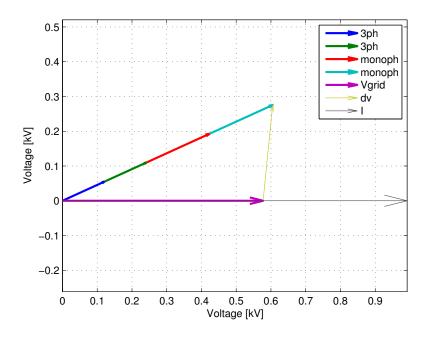

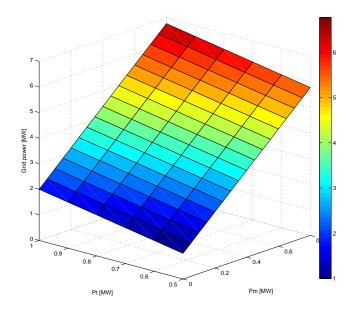

| 5.3.1       Pgenerated <plim< td="">       60         5.3.2       Pgenerated&gt;Plim       63         6       Control structure       69         6.1       Internal loops       69         6.2       Current loop PI tuning       73         6.2.1       Results       74         6.3       PQ loops       76         6.3.1       Results       77         6.4       Soft starter       78         6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage reference       107         8.1.1       DC voltage reference       107</plim<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | 5.2                | Looku                | p table concept                             | 60  |  |  |  |  |  |  |  |  |

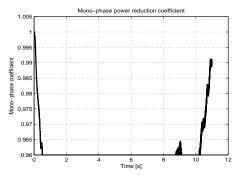

| 5.3.2       Pgenerated>Plim       63         6       Control structure       69         6.1       Internal loops       69         6.2       Current loop PI tuning       73         6.2.1       Results       74         6.3       PQ loops       76         6.3.1       Results       77         6.4       Soft starter       78         6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage reference       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2.0       Capacitors       124 </td <td></td> <td>5.3</td> <td>Result</td> <td>S</td> <td>60</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | 5.3                | Result               | S                                           | 60  |  |  |  |  |  |  |  |  |

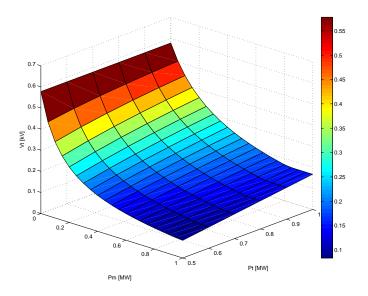

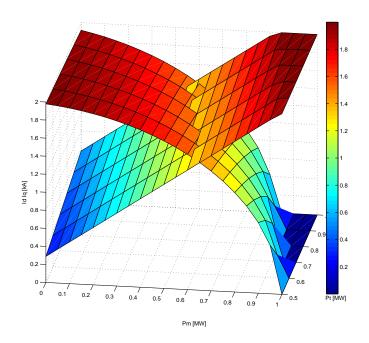

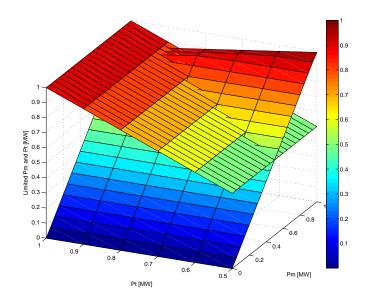

| 6       Control structure       69         6.1       Internal loops       69         6.2       Current loop P1 tuning       73         6.2.1       Results       74         6.3       PQ loops       76         6.3.1       Results       77         6.4       Soft starter       78         6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.1       Theory       93         7.1       Theory       93         7.2       Without interleaving       93         7.3       With interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.1       DC voltage reference       107         8.1.2 <td></td> <td></td> <td>5.3.1</td> <td>Pgenerated<plim< td=""><td>60</td></plim<></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                    | 5.3.1                | Pgenerated <plim< td=""><td>60</td></plim<> | 60  |  |  |  |  |  |  |  |  |

| 6.1       Internal loops       69         6.2       Current loop PI tuning       73         6.2.1       Results       74         6.3       PQ loops       76         6.3.1       Results       77         6.4       Soft starter       78         6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2.0       Co sources dynamic model       126         8.2.3       Balancing issues <td< td=""><td></td><td></td><td>5.3.2</td><td>Pgenerated&gt;Plim</td><td>63</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                    | 5.3.2                | Pgenerated>Plim                             | 63  |  |  |  |  |  |  |  |  |

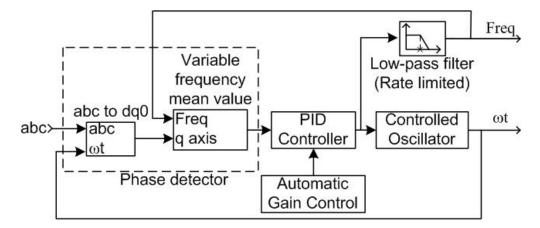

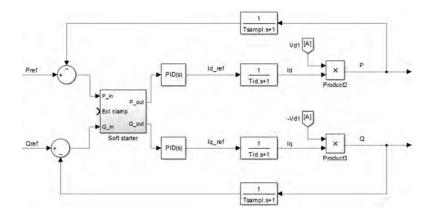

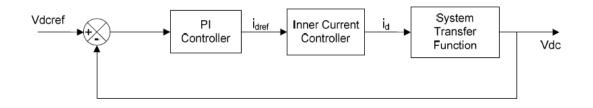

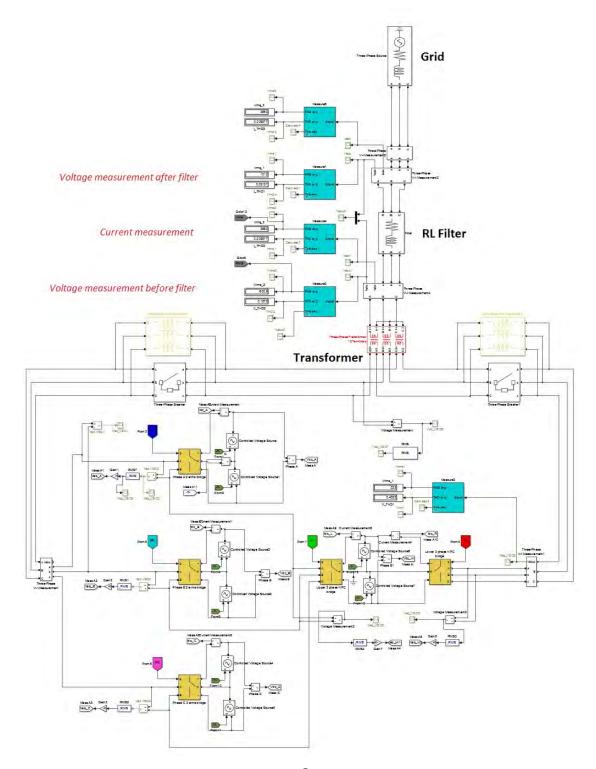

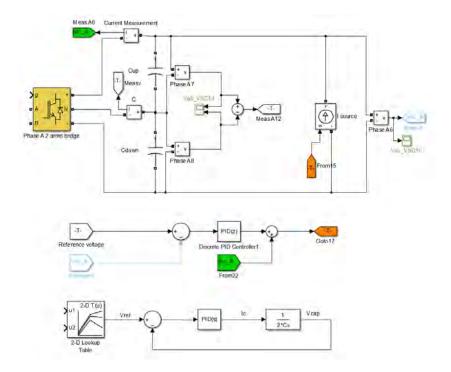

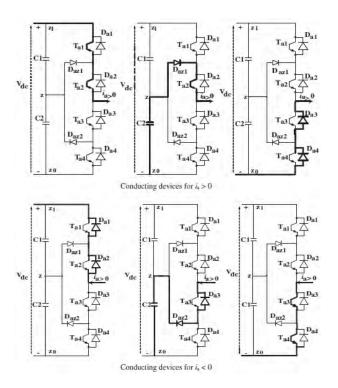

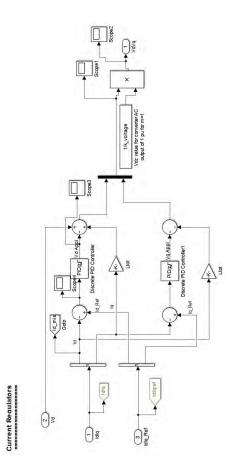

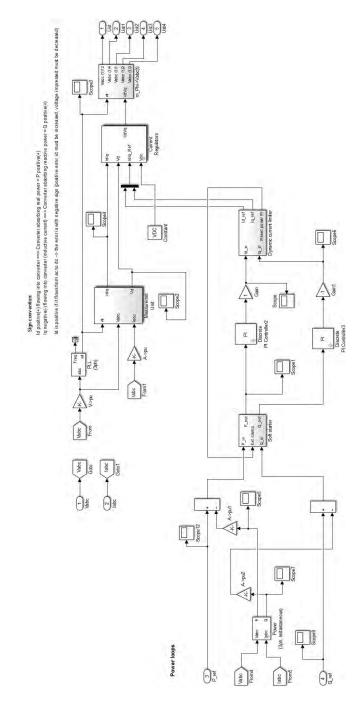

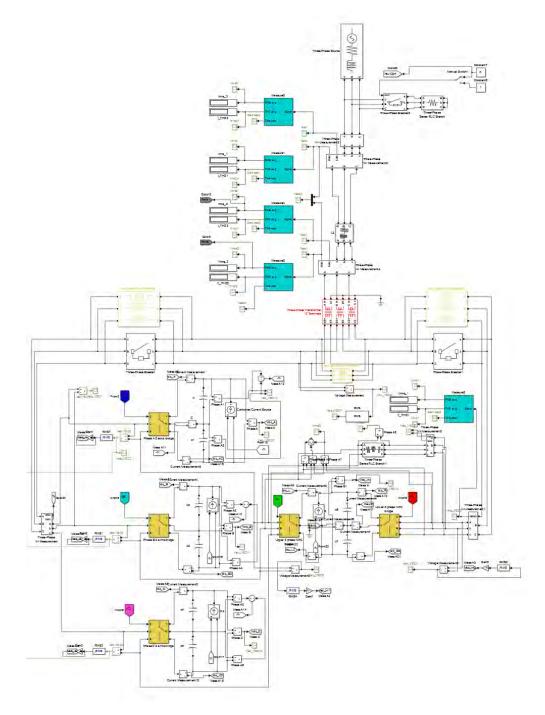

| 6.2       Current loo P I tuning       73         6.2.1       Results       74         6.3       PQ loops       76         6.3.1       Results       77         6.4       Soft starter       78         6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       93         7.3       With interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         8       Sources models       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2.1       Capacitors       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system <td>6</td> <td>Cor</td> <td colspan="11">Control structure 69</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6        | Cor                | Control structure 69 |                                             |     |  |  |  |  |  |  |  |  |

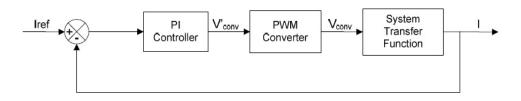

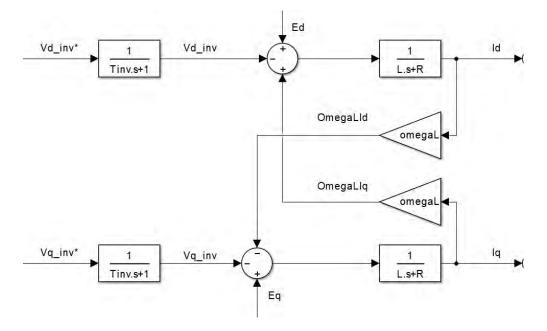

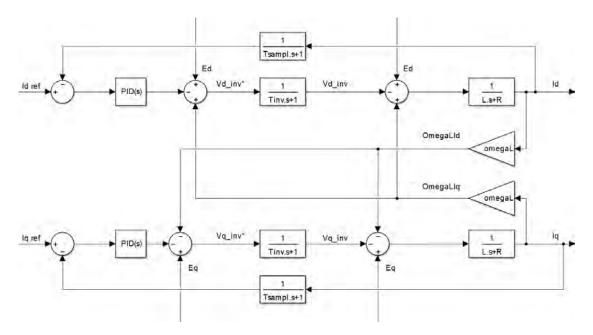

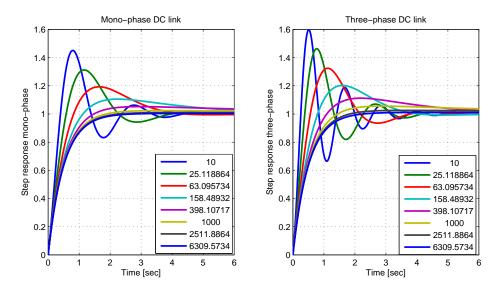

| 6.2       Current loop PI tuning       73         6.2.1       Results       74         6.3       PQ loops       76         6.3.1       Results       77         6.4       Soft starter       78         6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       93         7.3       With interleaving       99         7.4       THD vs power       99         8       Sources models       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2.1       Capacitors       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 6.1                | Intern               | al loops                                    | 69  |  |  |  |  |  |  |  |  |

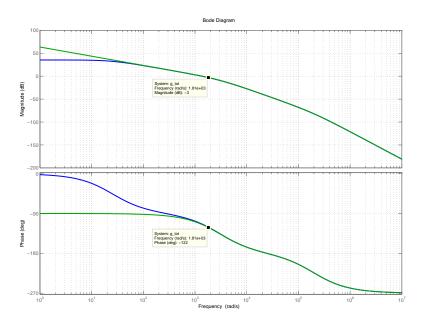

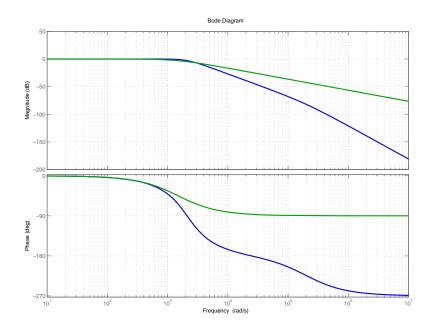

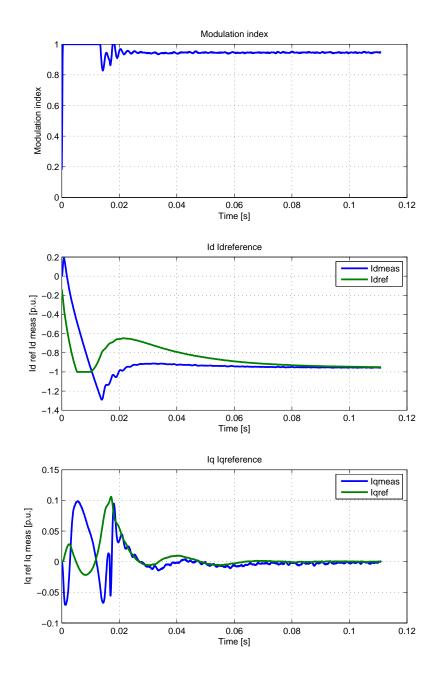

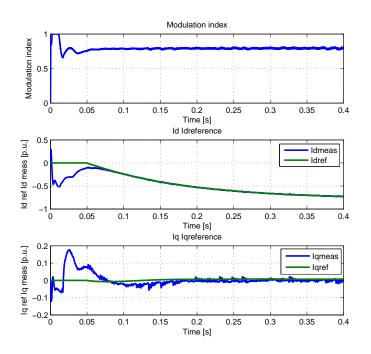

| 6.2.1 Results       74         6.3 PQ loops       76         6.3.1 Results       77         6.4 Soft starter       78         6.4.1 Start-up transient and solution       78         6.4.2 Results       79         6.5 Dynamic current limiting       85         6.5.1 Fault operation       85         6.5.2 Implementation and results       87         7 Interleaving       93         7.1 Theory       93         7.2 Without interleaving       93         7.3 With interleaving       94         7.3 With interleaving       94         7.3 With interleaving       99         8 Sources models       107         8.1 DC voltage sources       107         8.1.2 Power and current waveforms       109         8.2 DC capacitors       124         8.2.1 Capacitors design       124         8.2.2 DC sources dynamic model       126         8.2.3 Balancing issues       129         8.2.4 Single-phase balancing system       136         8.2.5 Three-phase balancing system       141         8.3 Variable sources       154         8.4 Power electronics efficiency estimation       159         9 Magnetic components sizing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 6.2                |                      | •                                           | 73  |  |  |  |  |  |  |  |  |

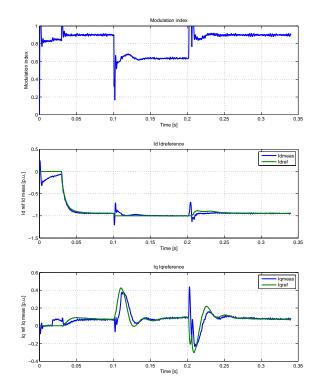

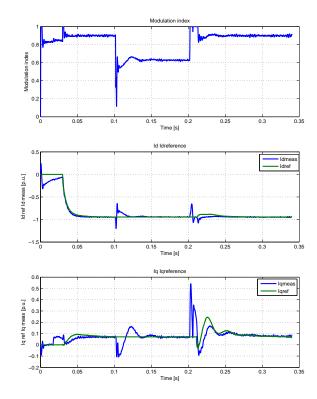

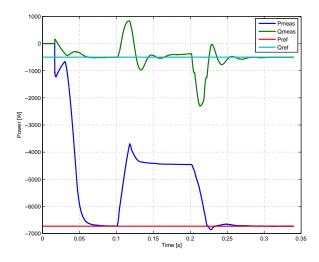

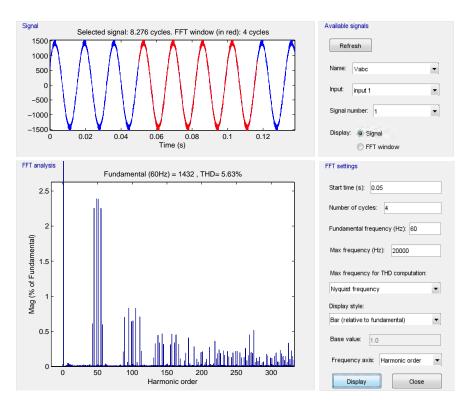

| 6.3       PQ loops       76         6.3.1       Results       77         6.4       Soft starter       78         6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         7.4       THD vs power       99         8       Sources models       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                    |                      |                                             | 74  |  |  |  |  |  |  |  |  |

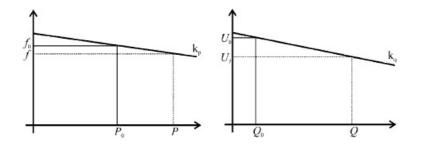

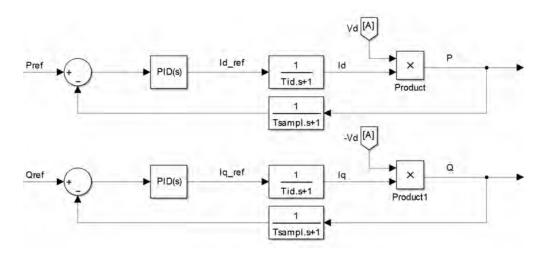

| 6.3.1 Results       77         6.4 Soft starter       78         6.4.1 Start-up transient and solution       78         6.4.2 Results       79         6.5 Dynamic current limiting       85         6.5.1 Fault operation       85         6.5.2 Implementation and results       87         7 Interleaving       93         7.1 Theory       93         7.2 Without interleaving       93         7.3 Theory       93         7.4 THD vs power       99         7.4 THD vs power       99         8 Sources models       107         8.1.1 DC voltage reference       107         8.1.2 Power and current waveforms       109         8.2 DC capacitors       124         8.2.1 Capacitors design       124         8.2.2 DC sources dynamic model       126         8.2.3 Balancing issues       129         8.2.4 Single-phase balancing system       136         8.2.5 Three-phase balancing system       141         8.3 Variable sources       154         8.4 Power electronics efficiency estimation       159         9 Magnetic components sizing       165         9.1 Power transformer       165         9.1.2 Additional losses <td></td> <td>6.3</td> <td>PQ lo</td> <td></td> <td>76</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 6.3                | PQ lo                |                                             | 76  |  |  |  |  |  |  |  |  |

| 6.4       Soft starter       78         6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       136         8.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                    | •                    | *                                           | 77  |  |  |  |  |  |  |  |  |

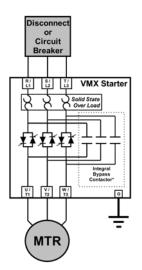

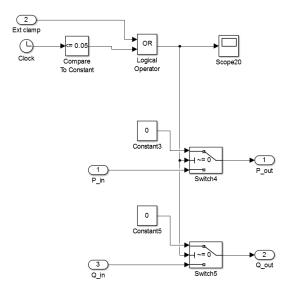

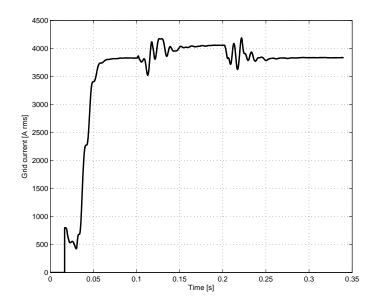

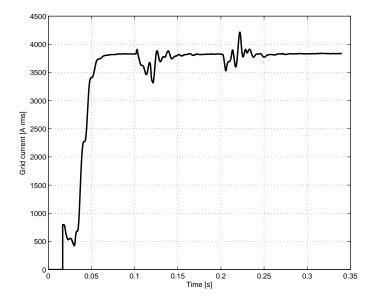

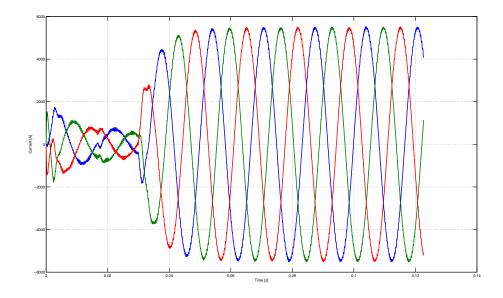

| 6.4.1       Start-up transient and solution       78         6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165 <td></td> <td>6.4</td> <td>Soft st</td> <td></td> <td>78</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | 6.4                | Soft st              |                                             | 78  |  |  |  |  |  |  |  |  |

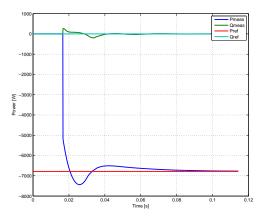

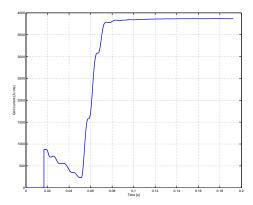

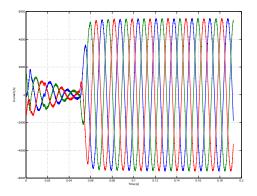

| 6.4.2       Results       79         6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors design       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | -                  |                      |                                             |     |  |  |  |  |  |  |  |  |

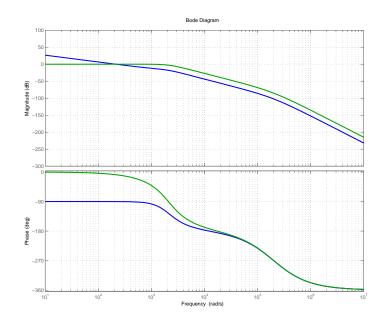

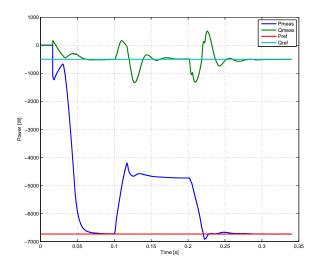

| 6.5       Dynamic current limiting       85         6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       136         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1.1       Design       165         9.1.2       Additional losses       171 <td></td> <td></td> <td>6.4.2</td> <td>•</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                    | 6.4.2                | •                                           |     |  |  |  |  |  |  |  |  |

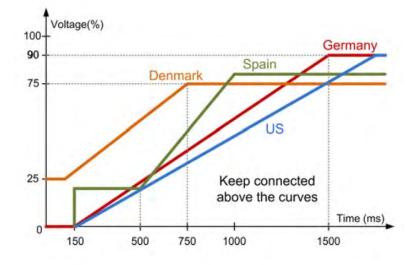

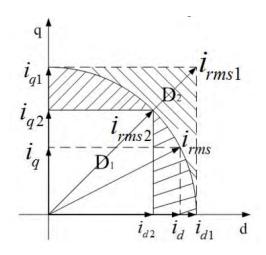

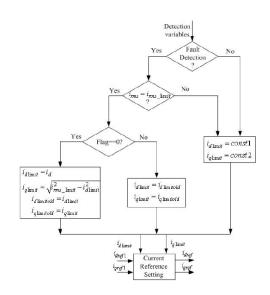

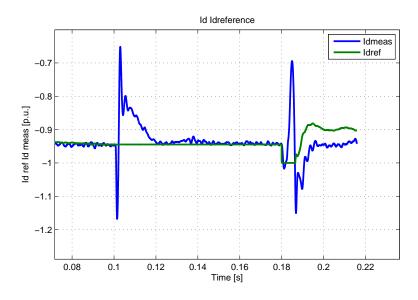

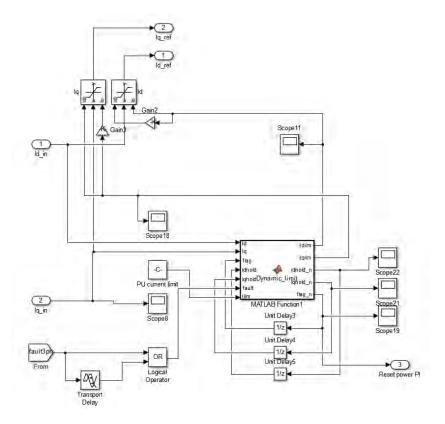

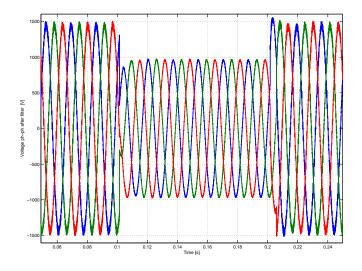

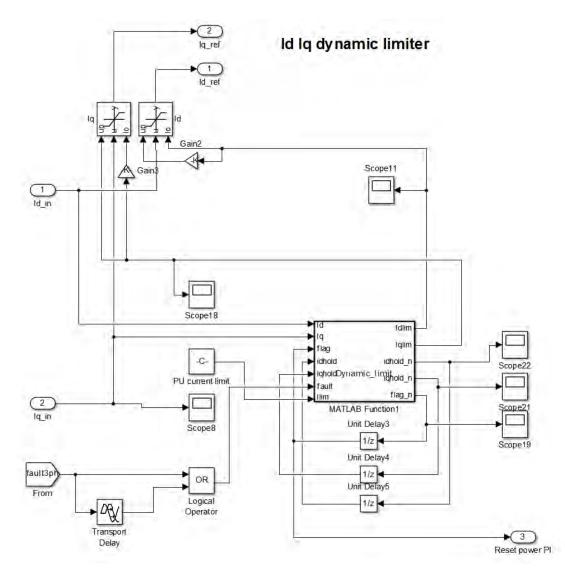

| 6.5.1       Fault operation       85         6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1       Power transformer       165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 6.5                | Dvnar                |                                             |     |  |  |  |  |  |  |  |  |

| 6.5.2       Implementation and results       87         7       Interleaving       93         7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                    | -                    |                                             |     |  |  |  |  |  |  |  |  |

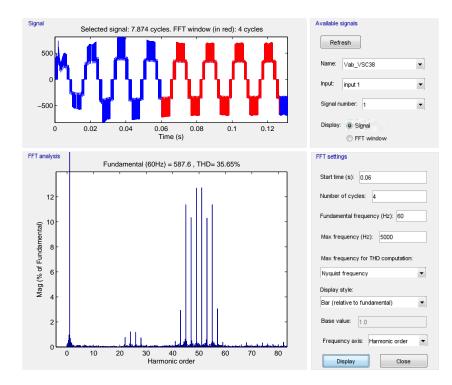

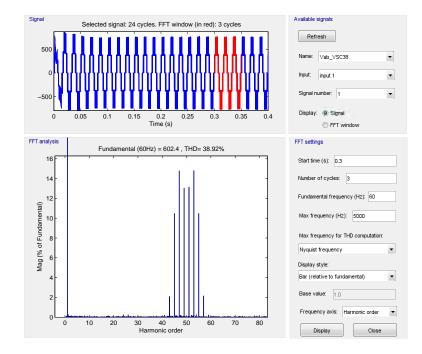

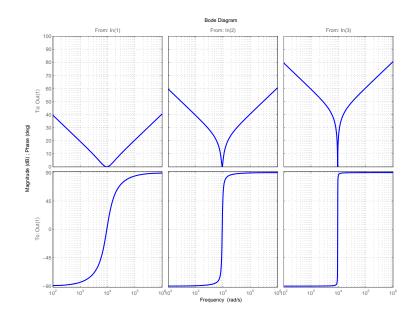

| 7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                    |                      | *                                           |     |  |  |  |  |  |  |  |  |

| 7.1       Theory       93         7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _        | <b>.</b>           |                      |                                             | ~ ~ |  |  |  |  |  |  |  |  |

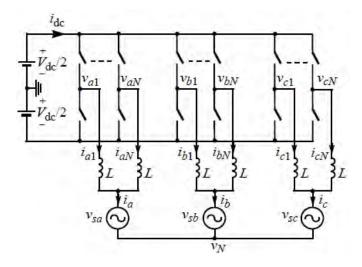

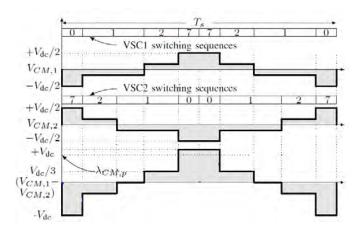

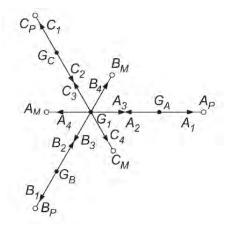

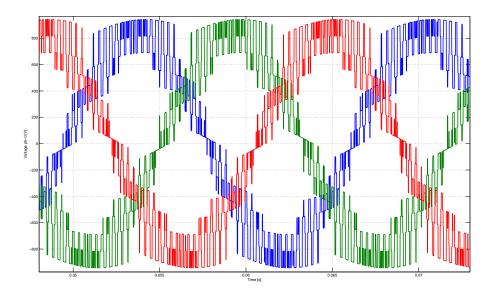

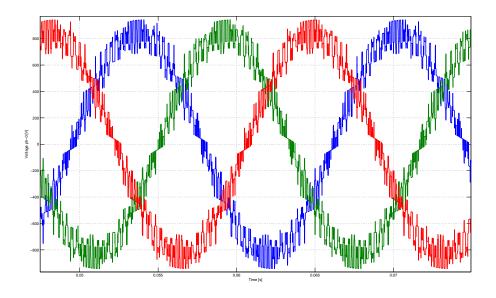

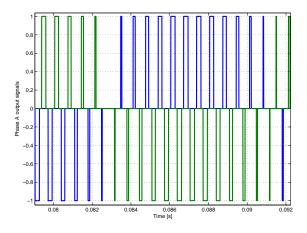

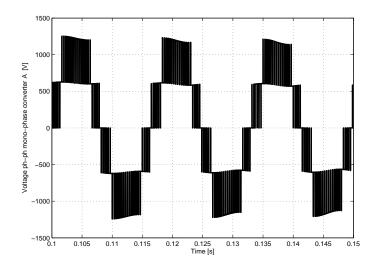

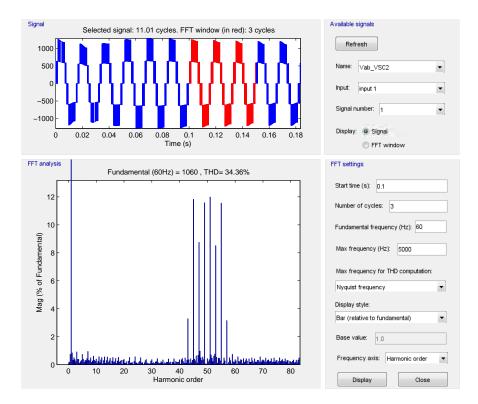

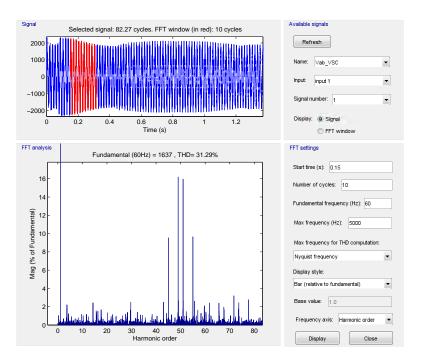

| 7.2       Without interleaving       94         7.3       With interleaving       99         7.4       THD vs power       99         7.4       THD vs power       99         8       Sources models       107         8.1       DC voltage sources       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       104         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7        |                    |                      | 0                                           |     |  |  |  |  |  |  |  |  |

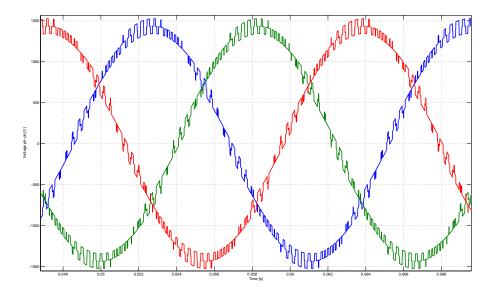

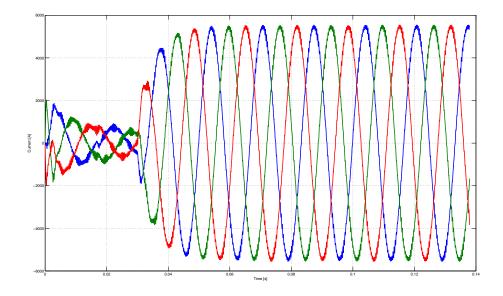

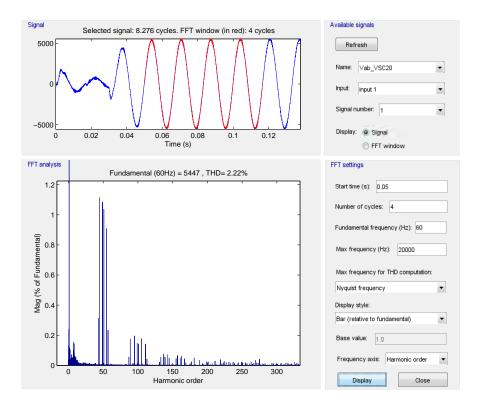

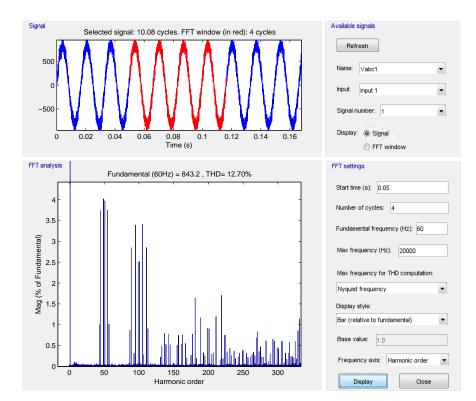

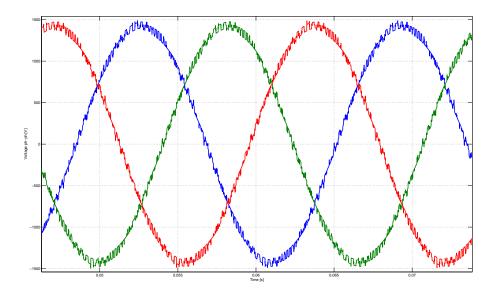

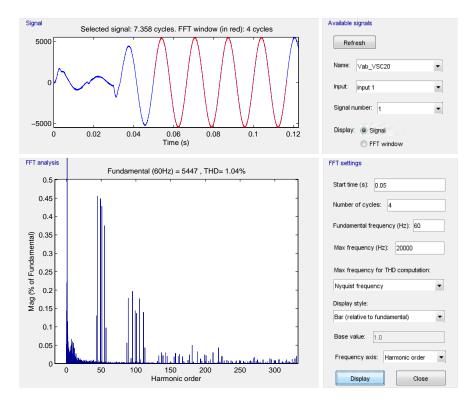

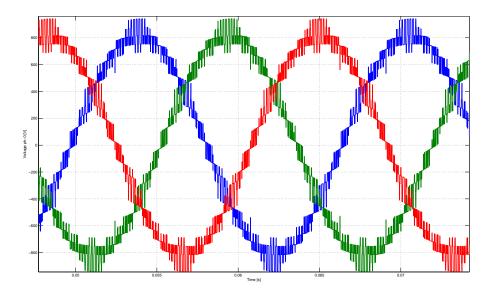

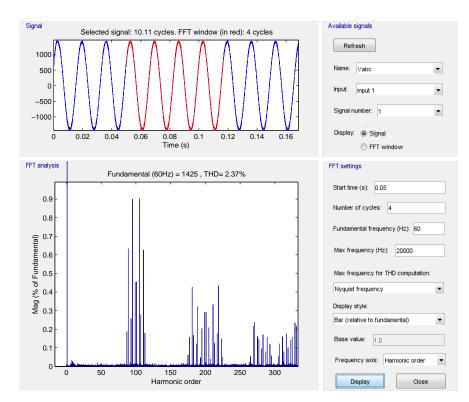

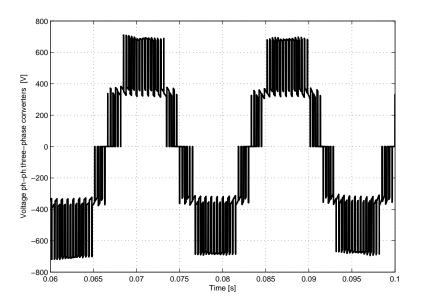

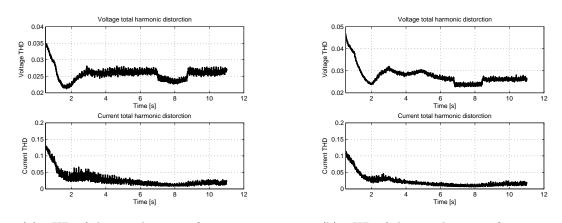

| 7.3       With interleaving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                    |                      |                                             |     |  |  |  |  |  |  |  |  |

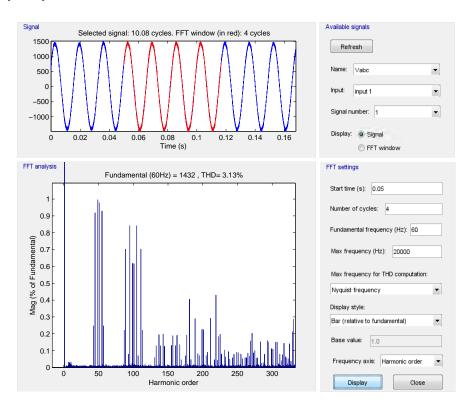

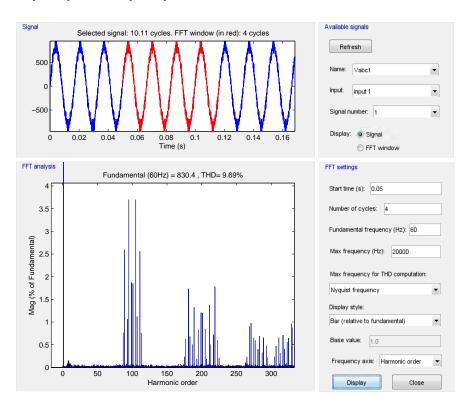

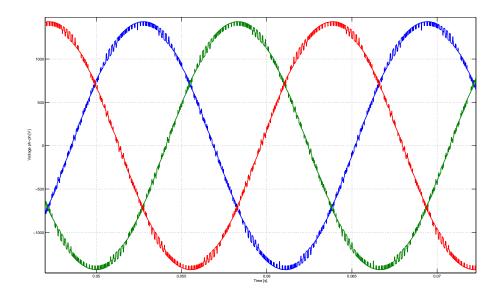

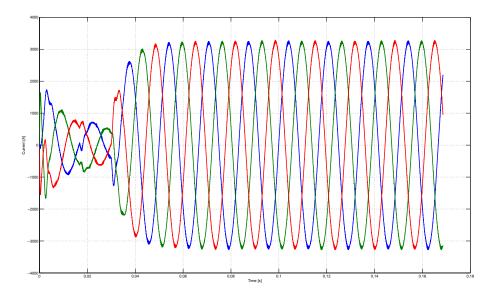

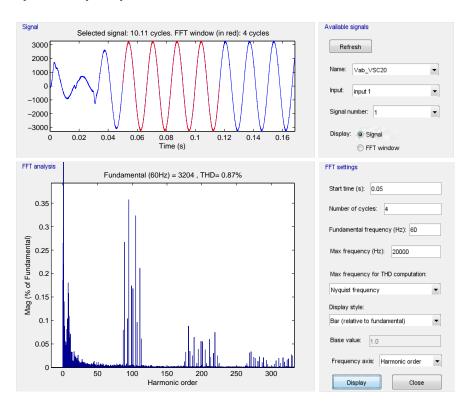

| 7.4 THD vs power       99         8 Sources models       107         8.1 DC voltage sources       107         8.1.1 DC voltage reference       107         8.1.2 Power and current waveforms       109         8.2 DC capacitors       124         8.2.1 Capacitors design       124         8.2.2 DC sources dynamic model       126         8.2.3 Balancing issues       129         8.2.4 Single-phase balancing system       136         8.2.5 Three-phase balancing system       141         8.3 Variable sources       154         8.4 Power electronics efficiency estimation       159         9 Magnetic components sizing       165         9.1 Power transformer       165         9.1.1 Design       165         9.1.2 Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                    |                      | 9                                           | -   |  |  |  |  |  |  |  |  |

| 8       Sources models       107         8.1       DC voltage sources       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                    |                      |                                             |     |  |  |  |  |  |  |  |  |

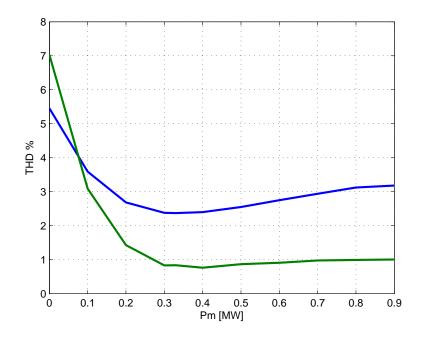

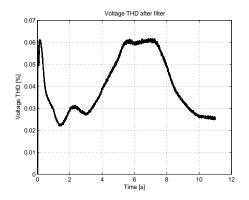

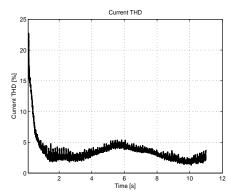

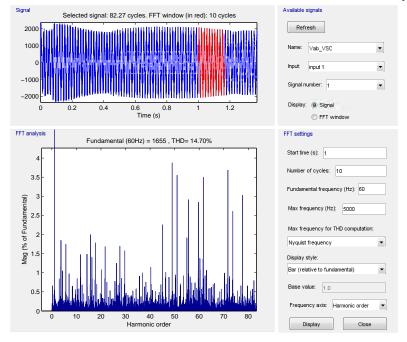

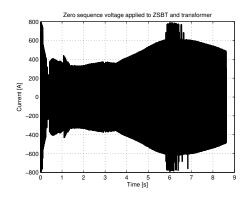

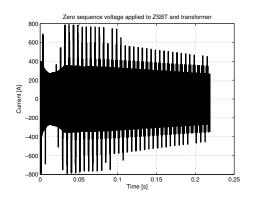

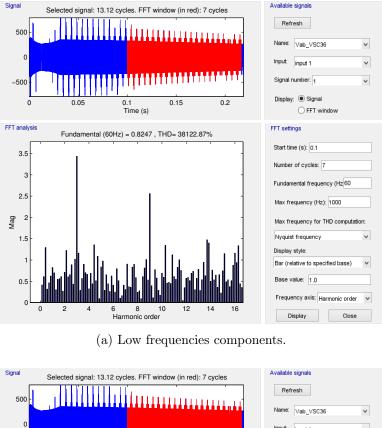

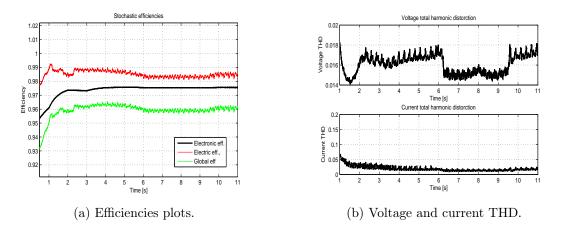

| 8.1       DC voltage sources       107         8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 7.4                | THD                  | vs power                                    | 99  |  |  |  |  |  |  |  |  |

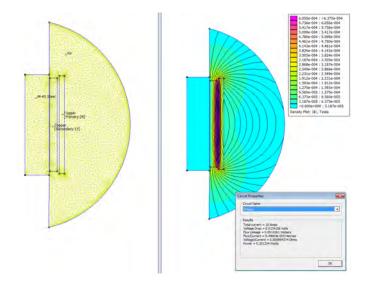

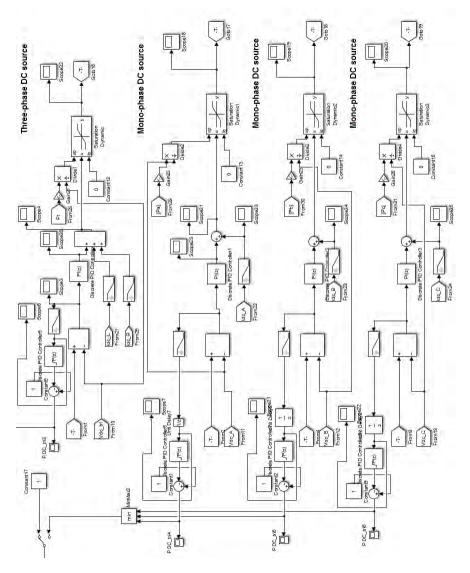

| 8.1.1       DC voltage reference       107         8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8        | Sources models 107 |                      |                                             |     |  |  |  |  |  |  |  |  |

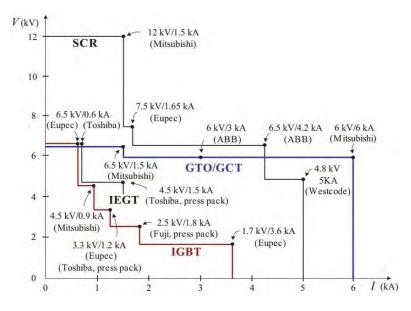

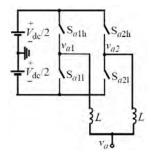

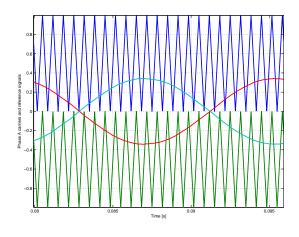

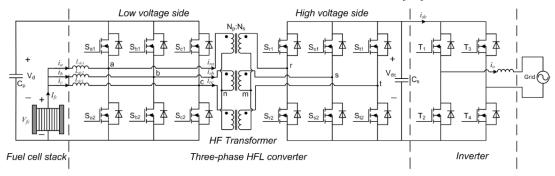

| 8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       124         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 8.1                | DC vo                | ltage sources                               | .07 |  |  |  |  |  |  |  |  |

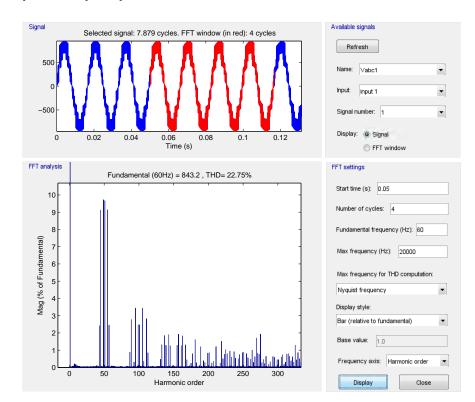

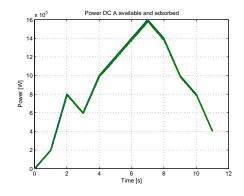

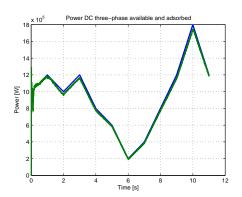

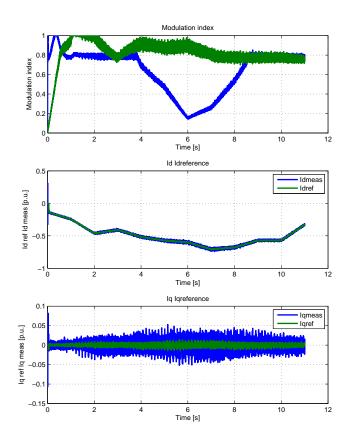

| 8.1.2       Power and current waveforms       109         8.2       DC capacitors       124         8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       124         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                    | 8.1.1                | DC voltage reference                        | .07 |  |  |  |  |  |  |  |  |

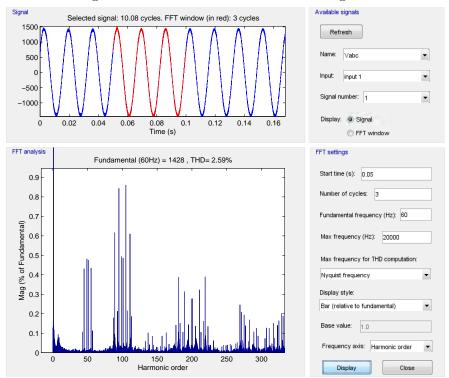

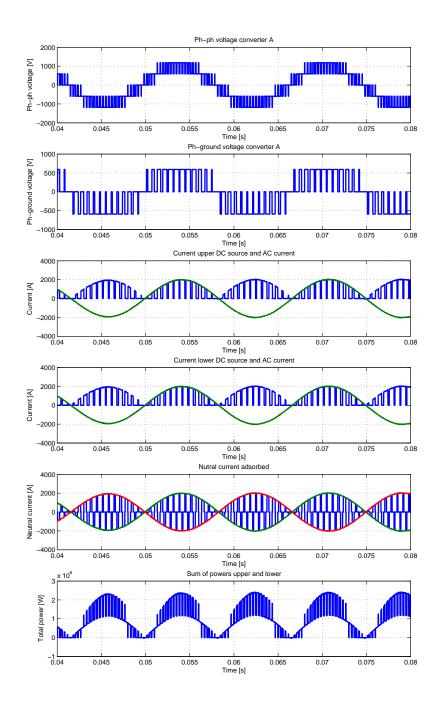

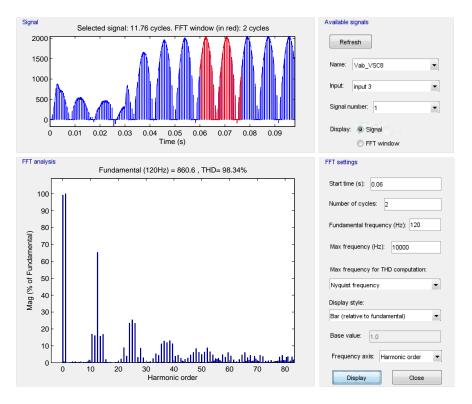

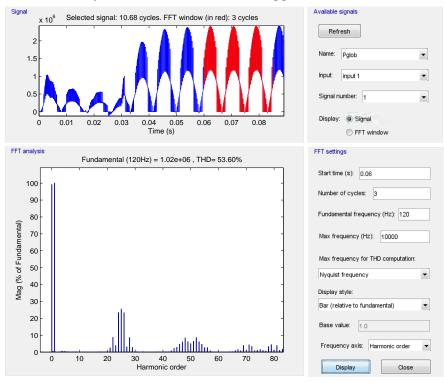

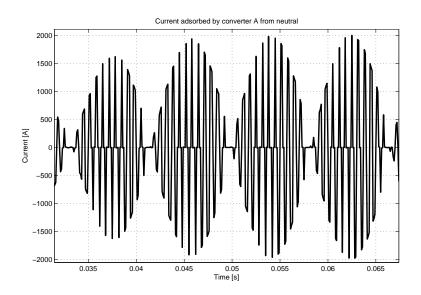

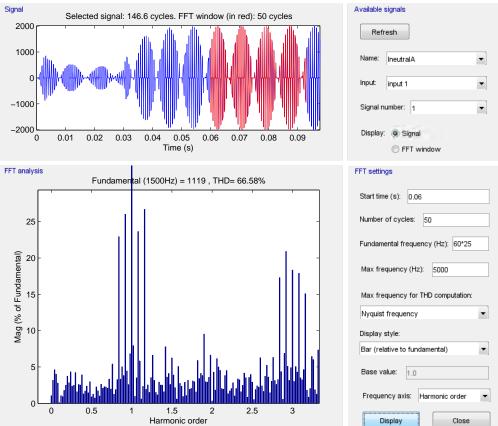

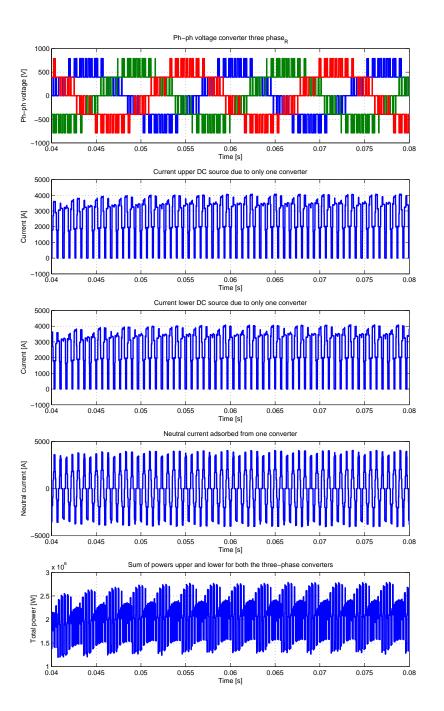

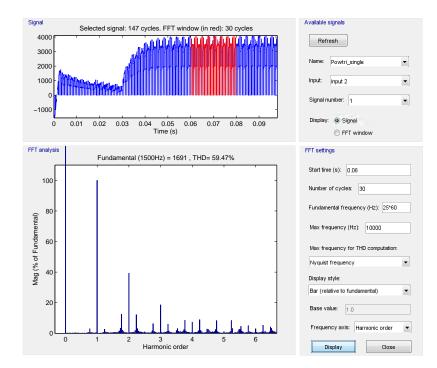

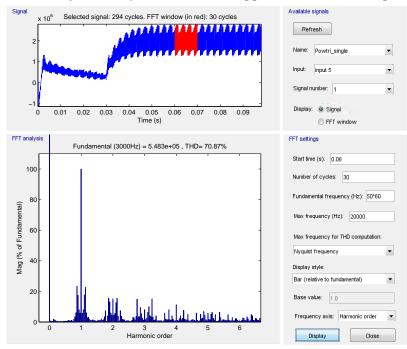

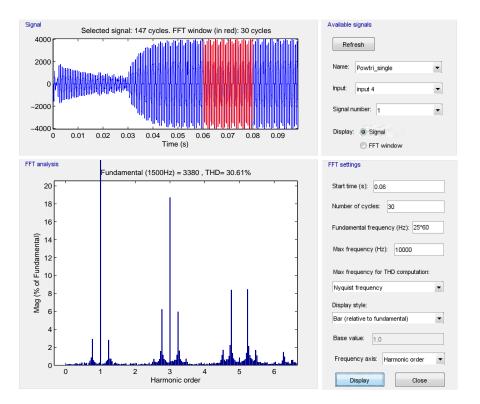

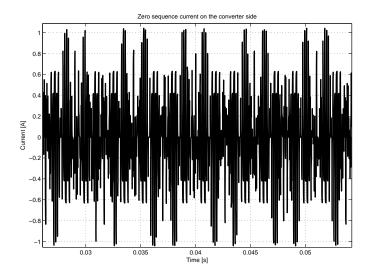

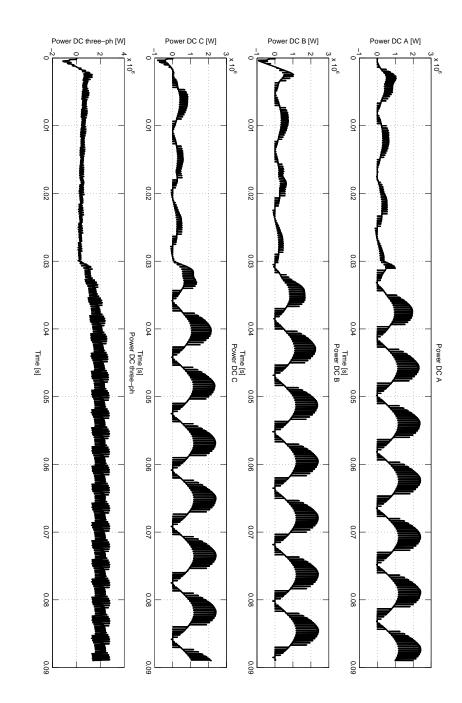

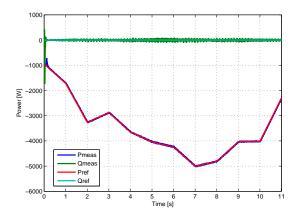

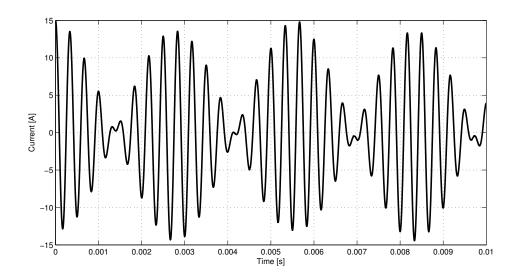

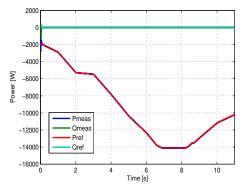

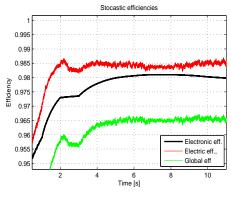

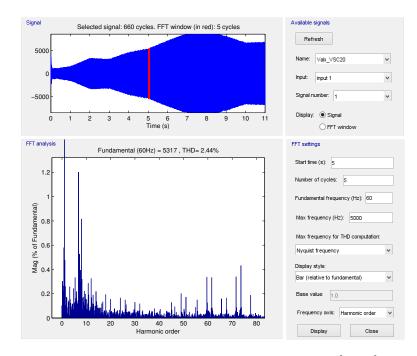

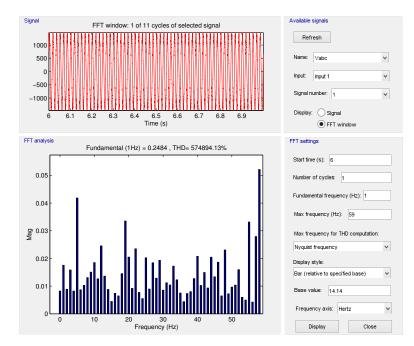

| 8.2.1       Capacitors design       124         8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                    | 8.1.2                | Power and current waveforms                 | .09 |  |  |  |  |  |  |  |  |

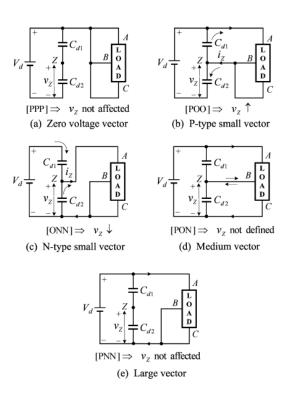

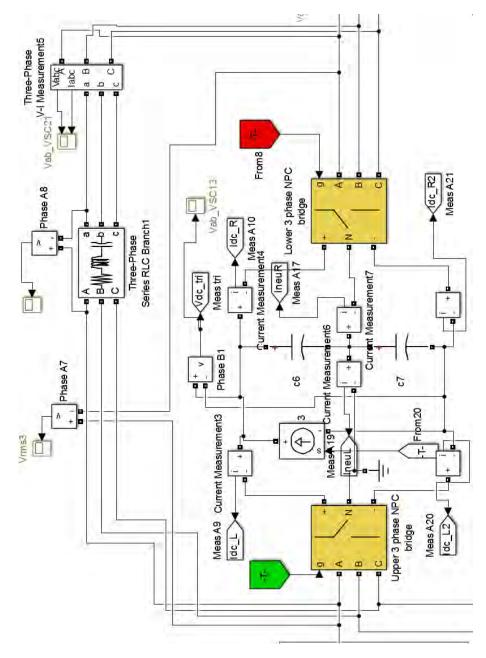

| 8.2.2       DC sources dynamic model       126         8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | 8.2                | DC ca                | pacitors                                    | 24  |  |  |  |  |  |  |  |  |

| 8.2.3       Balancing issues       129         8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       141         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                    | 8.2.1                | Capacitors design                           | 24  |  |  |  |  |  |  |  |  |

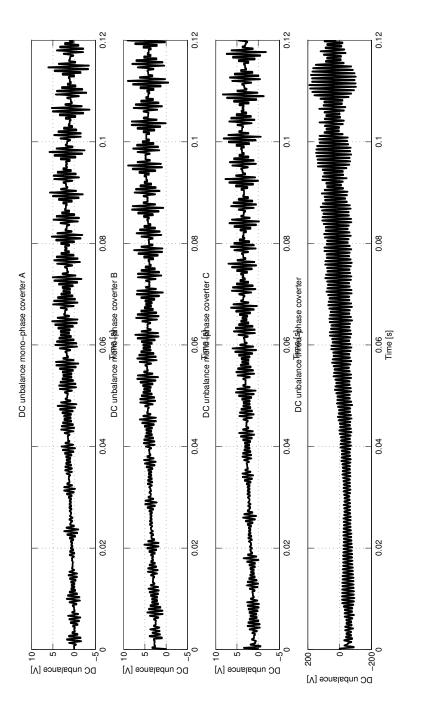

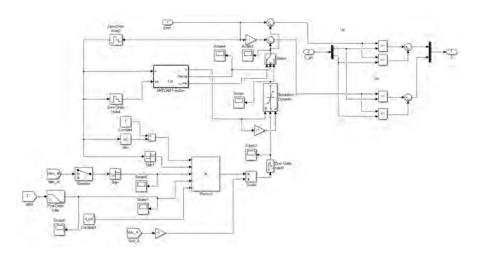

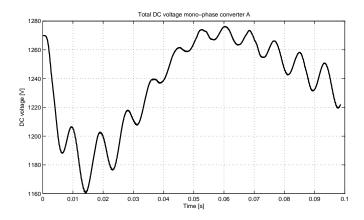

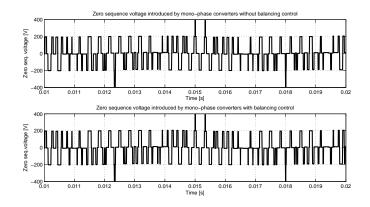

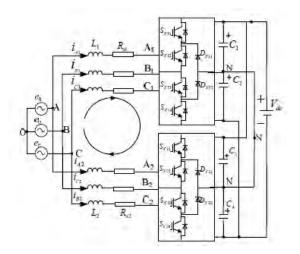

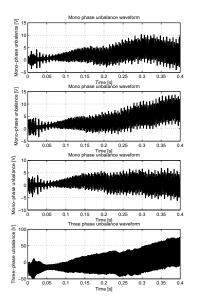

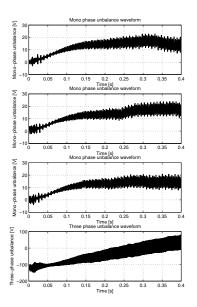

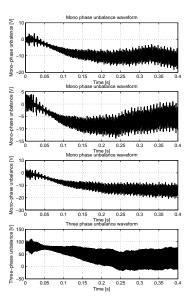

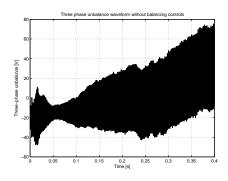

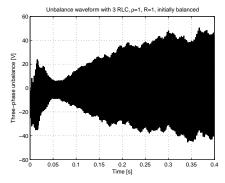

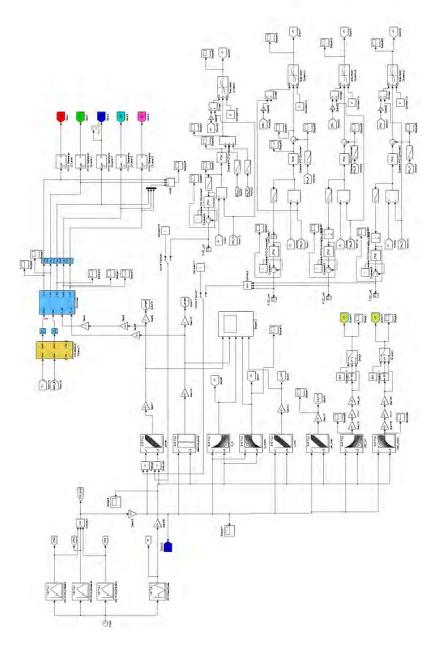

| 8.2.4       Single-phase balancing system       136         8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                    | 8.2.2                | DC sources dynamic model                    | 26  |  |  |  |  |  |  |  |  |

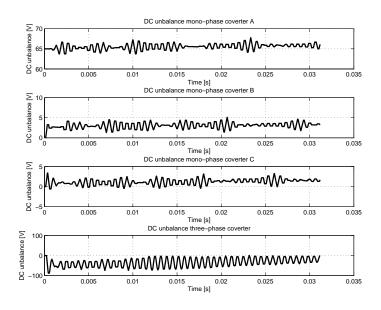

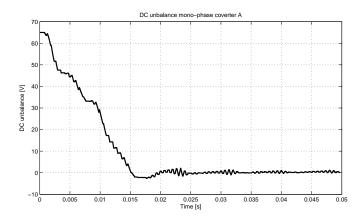

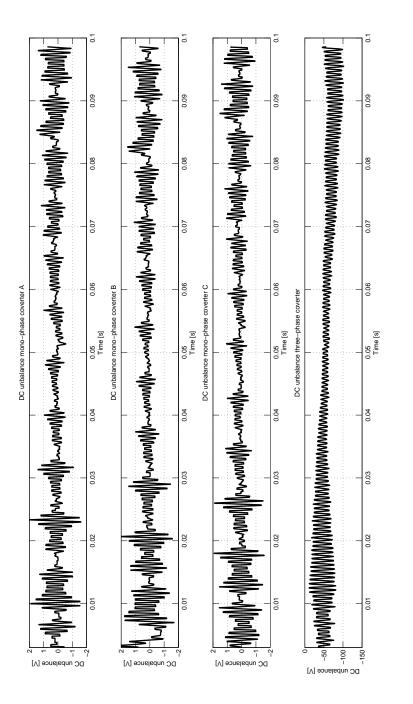

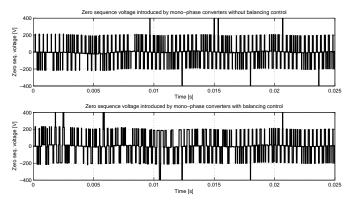

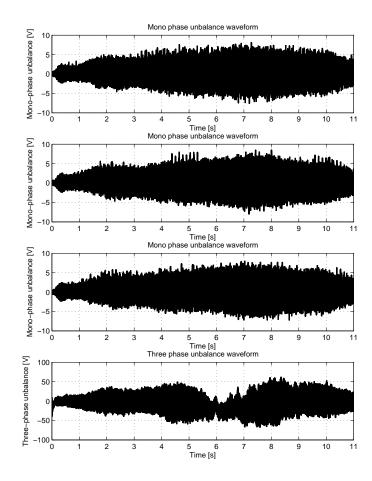

| 8.2.5       Three-phase balancing system       141         8.3       Variable sources       154         8.4       Power electronics efficiency estimation       159         9       Magnetic components sizing       165         9.1       Power transformer       165         9.1.1       Design       165         9.1.2       Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                    | 8.2.3                | Balancing issues                            | .29 |  |  |  |  |  |  |  |  |

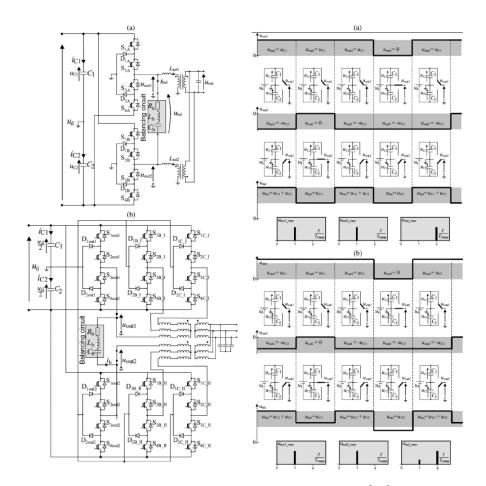

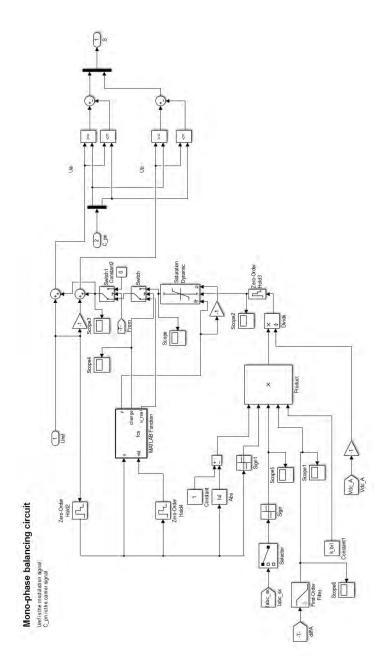

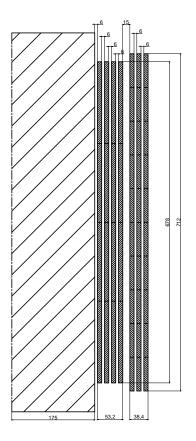

| 8.3 Variable sources       154         8.4 Power electronics efficiency estimation       159         9 Magnetic components sizing       165         9.1 Power transformer       165         9.1.1 Design       165         9.1.2 Additional losses       171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                    | 8.2.4                |                                             |     |  |  |  |  |  |  |  |  |