# Università degli Studi di Padova

SCUOLA DI INGEGNERIA Corso di Laurea Magistrale in Ingegneria Elettronica

Tesi di laurea magistrale

# Design of Programmable Phase Shifters and Attenuators in 130nm CMOS Technology

Relatore: **Prof. Andrea Bevilacqua** Correlatore: **Dr. Ing. Michele Caruso**  Laureando: Stefan Kokorović

To my family

iv

#### Abstract

This thesis proposes the analysis and design of two important circuits, often used in radio frequency (RF) systems: the phase shifter and the programmable attenuator.

The control of phase and amplitude of signals is important in many applications. Phased arrays, an example of adaptive antenna systems, base their operation on phase shifters to electronically steer the beam and obtain an overall antenna with a programmable radiation pattern. Another example is the Doherty Power Amplifier (DPA), an architecture often used in nowadays cellular base-stations. Phase and amplitude control circuits are used in DPA systems to optimize its efficiency.

The thesis starts with an introduction chapter which presents more in detail phased array and DPA systems and explains how they can take benefit from circuits like phase shifters and attenuators.

The core of the work is represented by the second and the third chapters which present the analysis and design of, respectively, a phase shifter and an attenuator for DPA application, using the Infineon 130nm CMOS technology. The respective chapters start with an overview of the possible solutions and continue with a detailed analysis of the differential  $\pi$ -network topology, which has been chosen for both phase shifter and attenuator. The final parts describe the design procedure.

After a brief description of the full-custom layout, the thesis concludes with the presentation of the simulation results, including parasitic extraction. In particular the two blocks are realized using only passive elements and cover the frequency band from 1GHz to 3GHz. The phase shifter shows an insertion loss of 1.8dB and a delay range of 76.5ps ( $52^{\circ}$ ) at 2GHz. This result is obtained with an average step of  $4.8ps(3.25^{\circ})$ . The attenuator shows an Insertion Loss (IL) of 1.3dB and an attenuation range of 15.2dB at 2GHz. This result is obtained with an average step of 0.49dB.

vi

# Contents

| A             | bstra | ict      |                                        | v   |

|---------------|-------|----------|----------------------------------------|-----|

| Co            | onter | nts      |                                        | vii |

| $\mathbf{Li}$ | st of | Figur    | es                                     | xi  |

| $\mathbf{Li}$ | st of | Table    | 5                                      | xv  |

| 1             | Intr  | oducti   | ion                                    | 1   |

|               | 1.1   | Applie   | cations                                | 1   |

|               |       | 1.1.1    | Phased Array                           | 2   |

|               |       | 1.1.2    | Doherty Power Amplifier (DPA)          | 5   |

|               | 1.2   | Target   | t Specifications                       | 9   |

|               | 1.3   | Netwo    | ork Analysis Basics                    | 10  |

|               |       | 1.3.1    | The Scattering Matrix                  | 11  |

|               |       | 1.3.2    | The ABCD Matrix                        | 12  |

|               |       | 1.3.3    | Mutual Inductors                       | 13  |

|               |       | 1.3.4    | Linearity - P1dB                       | 15  |

| <b>2</b>      | Ana   | alysis a | and Design of a Phase Shifter          | 17  |

|               | 2.1   | Introd   | uction to Phase Shifters               | 17  |

|               |       | 2.1.1    | Phase Shifter vs True Time Delay (TTD) | 21  |

|               |       | 2.1.2    | Specifications in the Time Domain      | 22  |

|               | 2.2   | Tunab    | ble Delay Line                         | 23  |

|               | 2.3   |          | Design                                 | 30  |

|               |       | 2.3.1    | Inductors Design                       | 30  |

| 6 | Sun        | iiiiai y                           | •••      |

|---|------------|------------------------------------|----------|

|   | Sun        | nmary                              | 77       |

|   |            | 5.2.4 Monte-Carlo Simulations      | 74       |

|   |            | 5.2.3 Temperature Variations       | 73       |

|   |            | 5.2.2 Power Supply Variations      | 72       |

|   |            | 5.2.1 Nominal Simulations          | 70       |

|   | 5.2        | Attenuator                         | 70       |

|   |            |                                    | 68       |

|   |            | -                                  | 67       |

|   |            |                                    | 66       |

|   |            |                                    | 65       |

|   | 0.1        | •                                  | 62<br>62 |

| 9 | 5.1        |                                    | 62       |

| 5 | Sim        | aulation Results                   | 61       |

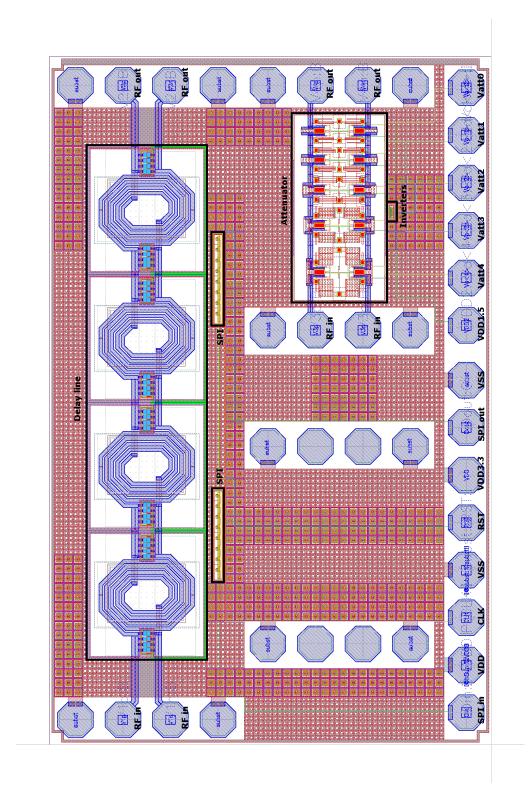

|   | 4.3        | Test Chip                          | 59       |

|   | 4.2        |                                    | 59       |

|   | 4.1        | Delay Line                         | 58       |

| 4 | Lay        | out                                | 57       |

|   | 3.4        | Summary                            | 55       |

|   | 3.3        | 0                                  | 53       |

|   |            |                                    | 52       |

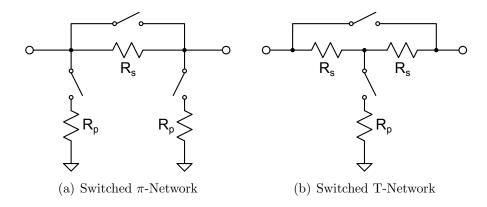

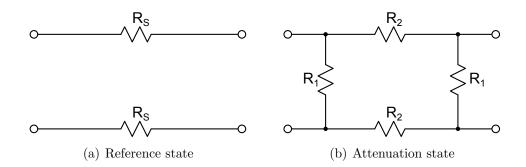

|   | 3.2        |                                    | 47       |

|   | 3.1        | 0                                  | 43       |

| 3 | Ana        | alysis and Design of an Attenuator | 43       |

|   | 2.0        | Summary                            | 42       |

|   | 2.5<br>2.6 | 1 1 00                             | 40<br>42 |

|   | 2.4        | 0                                  | 39<br>40 |

|   | 0.4        |                                    | 38       |

|   |            | 0                                  | 34       |

|   |            | 0.20 V $1.1$ $1.1$ $1.1$           | 0 /      |

| CONTENTS                                           | ix |

|----------------------------------------------------|----|

| <b>B</b> Effective Inductance in Coupling Presence | 81 |

| C Alpha is a Function of the Channel Length Only   | 83 |

| Bibliography                                       | 85 |

CONTENTS

Х

# List of Figures

| 1.1 | Adaptive antenna concept. Beam steered from $-50^{\circ}$ to $50^{\circ}$                                                                   | 3  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Phased array receiver                                                                                                                       | 4  |

| 1.3 | Dohery amplifier versus standard class AB amplifier efficiency                                                                              |    |

|     | $(dashed line)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                            | 7  |

| 1.4 | Active load-pull concept used in the DPA architecture                                                                                       | 7  |

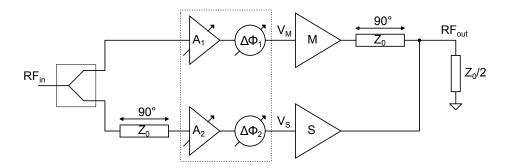

| 1.5 | Doherty power amplifier                                                                                                                     | 8  |

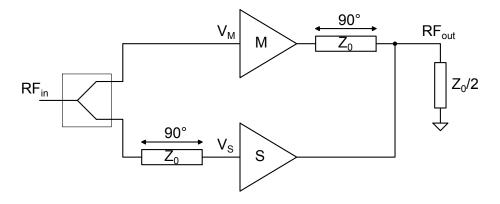

| 1.6 | Doherty Power amplifier with the amplitude/phase control cir-                                                                               |    |

|     | cuit                                                                                                                                        | 9  |

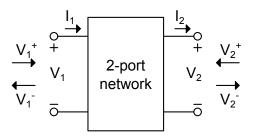

| 1.7 | 2-port network                                                                                                                              | 11 |

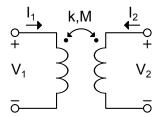

| 1.8 | A transformer representation                                                                                                                | 14 |

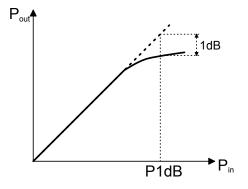

| 1.9 | 1-dB compression-point                                                                                                                      | 16 |

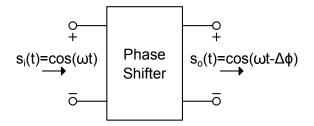

| 2.1 | 2-port phase shifter                                                                                                                        | 18 |

| 2.2 | Operation of a reflective-type phase shifter $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                            | 19 |

| 2.3 | Switched-line phase shifter                                                                                                                 | 20 |

| 2.4 | Loaded-line phase shifter                                                                                                                   | 21 |

| 2.5 | Ideal phase response of a Phase Shifter and a True Time Delay                                                                               |    |

|     | for different phase shift configurations                                                                                                    | 21 |

| 2.6 | Lumped delay line, topology also called $\pi - network$                                                                                     | 23 |

| 2.7 | Tunable delay element concept. In figure are reported graphics                                                                              |    |

|     | for the $C_{MAX}$ and $C_{min}$ (dashed line) cases                                                                                         | 28 |

| 2.8 | Comparison between infinite quality factor of the components                                                                                |    |

|     | (grey lines) and finite quality factor. Dashed lines represent                                                                              |    |

|     | the $C_{min}$ case $\ldots \ldots \ldots$ | 29 |

| 2.9 | Possible inductor shapes                                                                                                                    | 31 |

| 2.10 | Interleaved transformer                                                                                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.11 | Designed transformer                                                                                                                                                                          |

| 2.12 | Sonnet simulations results                                                                                                                                                                    |

| 2.13 | Differential MOS-varactor                                                                                                                                                                     |

| 2.14 | $C_{mos}$ as a function of $\frac{V_c}{V_{DD}}$                                                                                                                                               |

| 2.15 | $\alpha$ in function of $\frac{L_c}{L_{min}}$                                                                                                                                                 |

| 2.16 | Final cell                                                                                                                                                                                    |

| 2.17 | Delay extension with an optimal delay control solution $\ldots$ 40                                                                                                                            |

| 2.18 | Fine - Coarse tuning concept                                                                                                                                                                  |

| 3.1  | 2-port attenuator                                                                                                                                                                             |

| 3.2  | Switched-path topology                                                                                                                                                                        |

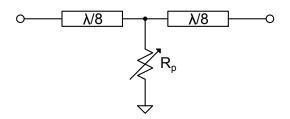

| 3.3  | Distributed attenuator                                                                                                                                                                        |

| 3.4  | Switched $\pi/T$ networks                                                                                                                                                                     |

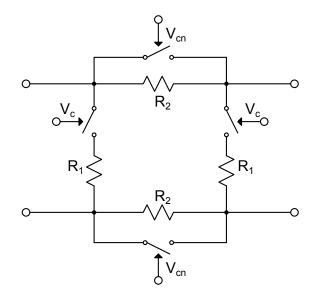

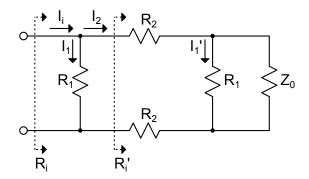

| 3.5  | Designed cell. $V_{cn}$ is the inverted $V_c$ signal $\ldots \ldots \ldots 47$                                                                                                                |

| 3.6  | The 2 possible topologies                                                                                                                                                                     |

| 3.7  | Attenuator current limits analysis                                                                                                                                                            |

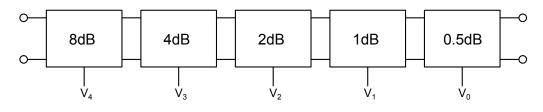

| 3.8  | Overall attenuator                                                                                                                                                                            |

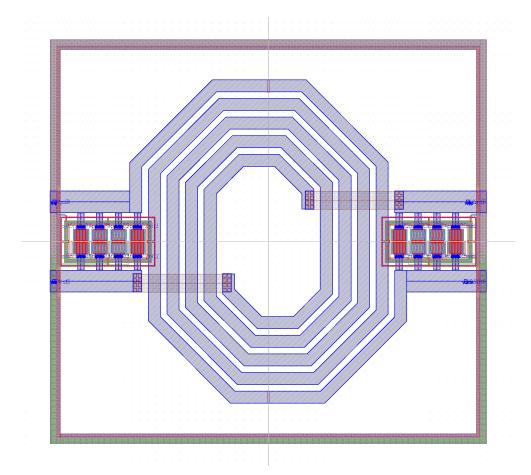

| 4.1  | Delay line cell layout                                                                                                                                                                        |

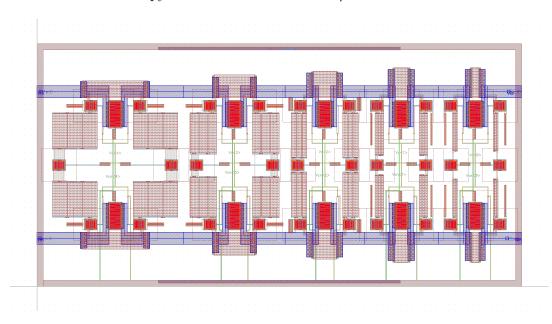

| 4.2  | Attenuator layout                                                                                                                                                                             |

| 4.3  | Test chip layout                                                                                                                                                                              |

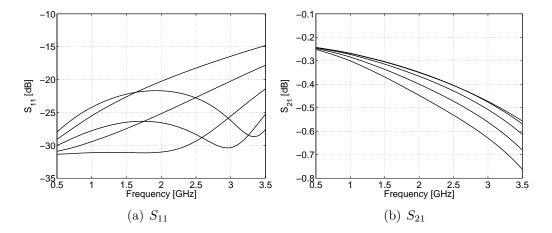

| 5.1  | $S_{11}$ (a) and $S_{21}$ (b) for the single cell $\ldots \ldots $            |

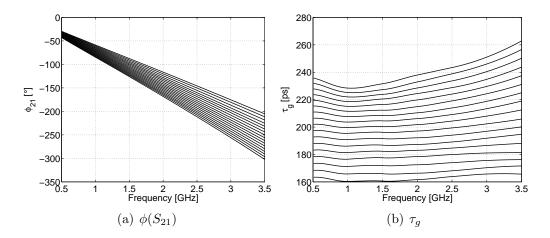

| 5.2  | $\phi(S_{21})$ (a) and $\tau_g$ (b) for the single cell $\ldots \ldots $      |

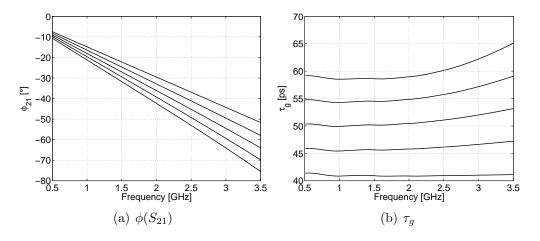

| 5.3  | Input matching (a) and transmission coefficient (b) of the de-                                                                                                                                |

|      | lay line                                                                                                                                                                                      |

| 5.4  | Transmission coefficient phase (a) and group delay (b) of the                                                                                                                                 |

|      | $delay line \dots \dots$                                                                |

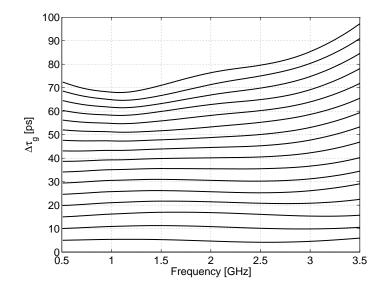

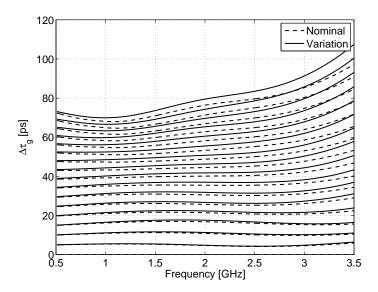

| 5.5  | Group delay difference $\Delta \tau_g$ of the delay line $\ldots \ldots \ldots \ldots 64$                                                                                                     |

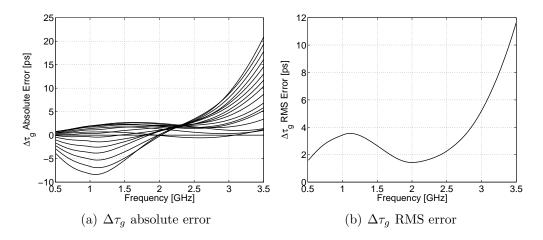

| 5.6  | $\Delta \tau_g$ absolute error (a) and $\Delta \tau_g$ RMS error (b)                                                                                                                          |

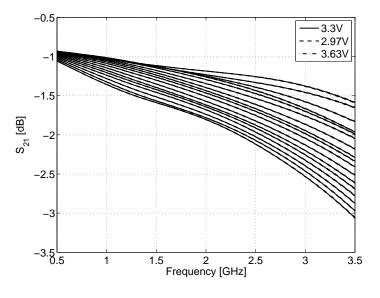

| 5.7  | $S_{21}$ sensibility to power supply variations $\ldots \ldots \ldots$        |

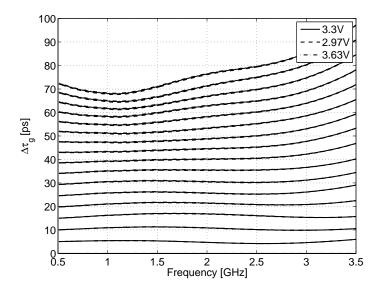

| 5.8  | $\Delta \tau_g$ sensibility to power supply variations $\ldots \ldots \ldots$ |

| 5.9  | $S_{21}$ sensibility to temperature variations $\ldots \ldots \ldots$         |

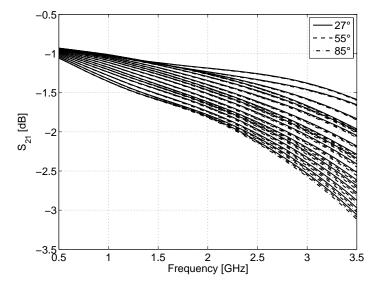

| 5.10 | $\Delta \tau_g$ sensibility to temperature variations $\ldots \ldots \ldots \ldots$                         | 66 |

|------|-------------------------------------------------------------------------------------------------------------|----|

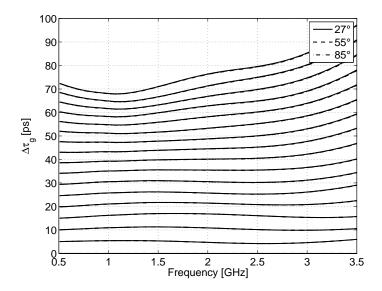

| 5.11 | $S_{21}$ variation due to transformers interaction                                                          | 67 |

| 5.12 | $\Delta \tau_g$ variation due to transformers interaction                                                   | 67 |

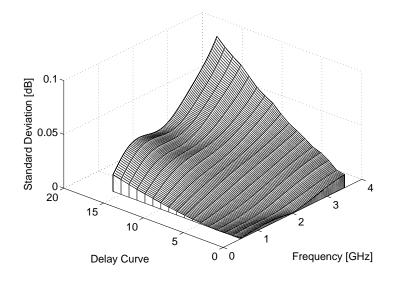

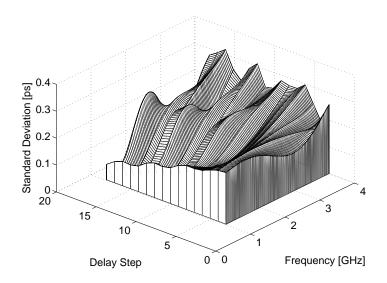

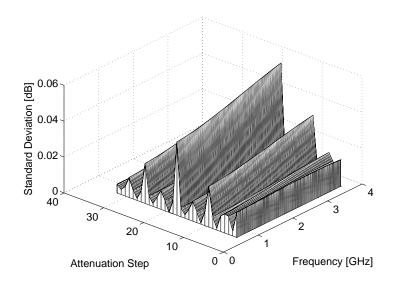

| 5.13 | $S_{21}$ standard deviation                                                                                 | 68 |

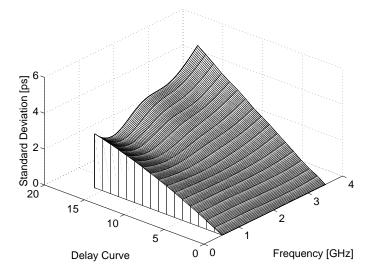

| 5.14 | $\Delta \tau_g$ standard deviation                                                                          | 68 |

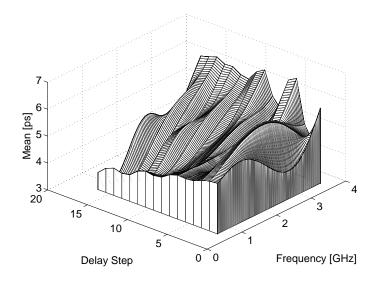

| 5.15 | Mean of the distance between adjacent delay curves                                                          | 69 |

| 5.16 | Standard deviation of the distance between adjacent delay curves $% \left( {{{\rm{D}}_{{\rm{D}}}} \right)$  | 69 |

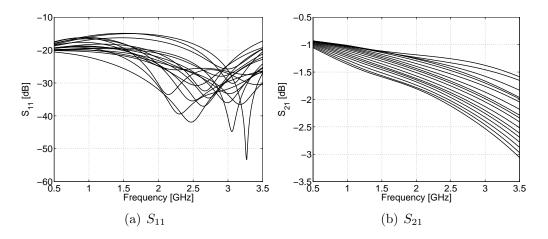

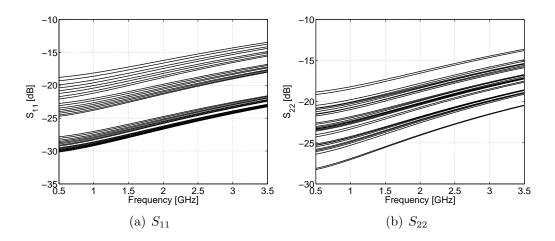

| 5.17 | Input matching (a) and output matching (b) of the attenuator                                                | 70 |

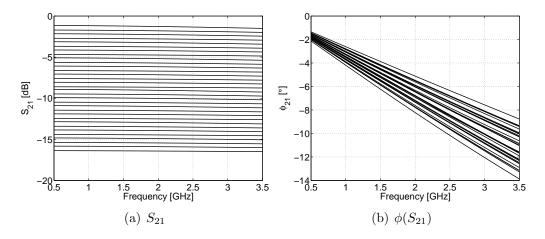

| 5.18 | Transmission coefficient (a) and transmission coefficient phase                                             |    |

|      | (b) of the attenuator $\ldots \ldots \ldots$ | 70 |

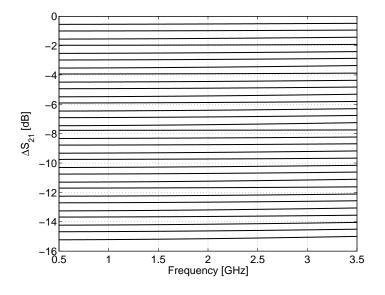

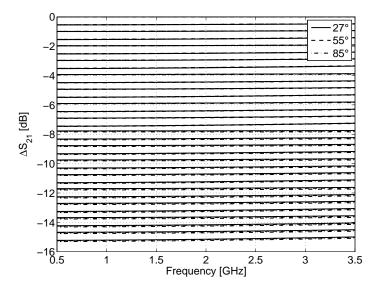

| 5.19 | Transmission coefficient difference $\Delta S_{21}$                                                         | 71 |

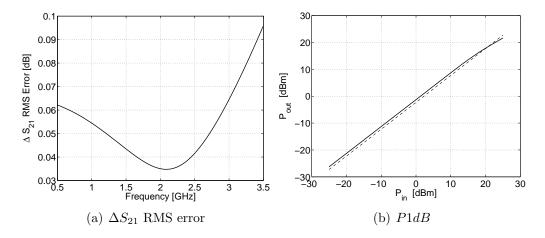

| 5.20 | $\Delta S_{21}$ RMS error (a) and 1-dB compression point (b)                                                | 71 |

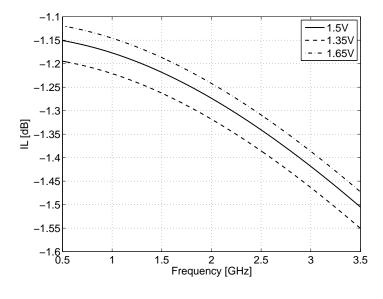

| 5.21 | Insertion loss $IL$ sensibility to power supply variations $\ldots$ .                                       | 72 |

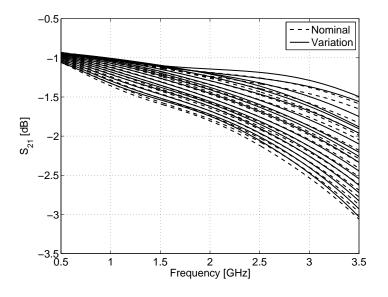

| 5.22 | $\Delta S_{21}$ sensibility to power supply variations                                                      | 72 |

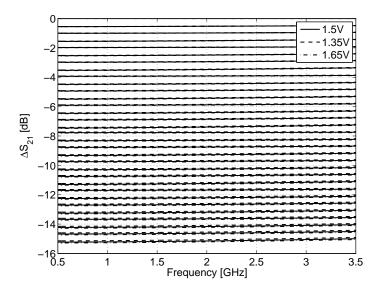

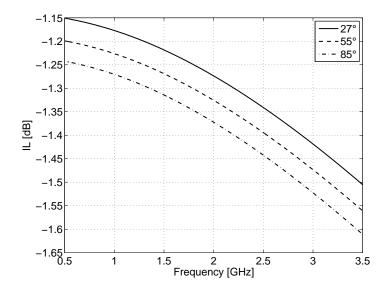

| 5.23 | Insertion loss $IL$ sensibility to temperature variations                                                   | 73 |

| 5.24 | $\Delta S_{21}$ sensibility to power supply variations                                                      | 73 |

| 5.25 | Insertion loss standard deviation                                                                           | 74 |

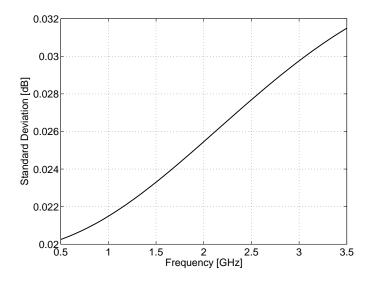

| 5.26 | $\Delta S_{21}$ standard deviation                                                                          | 74 |

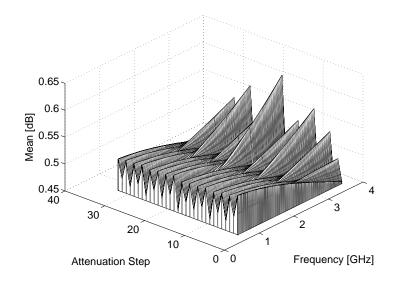

| 5.27 | Mean of the distance between adjacent attenuation steps $\ . \ . \ .$                                       | 75 |

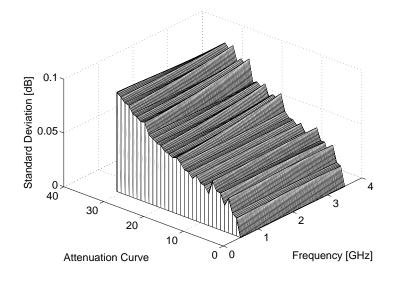

| 5.28 | Standard deviation of the distance between adjacent attenua-                                                |    |

|      | tion steps                                                                                                  | 75 |

| A.1  | Generic $\pi$ -network                                                                                      | 79 |

### LIST OF FIGURES

$\operatorname{xiv}$

# List of Tables

| 1.1 | Phase shifter target specifications                          | 10 |

|-----|--------------------------------------------------------------|----|

| 1.2 | Attenuator target specifications                             | 10 |

| 2.1 | Phase shifter TTD target specifications                      | 22 |

| 2.2 | Designed transformer characteristics at $2GHz$               | 34 |

| 2.3 | Characteristics of the nMOSFETs used to realize the varactor | 38 |

| 3.1 | Attenuator target specifications                             | 53 |

| 3.2 | Design resistances values for each stage                     | 54 |

xvi

# Chapter 1

# Introduction

Phase shifters and attenuators are important RF building blocks used in different kind of systems. The aim of this chapter is to explain their usefulness through some practical applications.

Afterwards, the goal of this work is presented, that is the target specifications for the design of the two circuits.

The chapter concludes with the recall of some basic concepts which will be often used in the rest of the thesis for the network analysis.

## 1.1 Applications

Phase shifters are circuits able to introduce a controllable phase shift in a signal path. Probably its major use is in adaptive antenna systems where they allow to control the phase of each path and change the radiation pattern of the overall antenna system([9]).

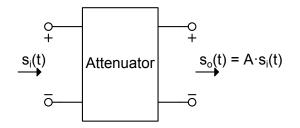

Programmable attenuators, instead, are circuits which permit to control the amplitude of a signal lowering its amplitude. They are required in a variety of applications such as the automatic gain control of transmitter/receiver systems, amplitude weighting in phased-array radars and temperature compensation of power amplifiers ([41]).

To get more insight about these blocks two applications are presented in this section, that is phased array and Doherty Power Amplifier systems. In the former they are used to electronically steer the beam of the multiple antenna system, increasing hence the overall antenna gain. In the latter, instead, they are used to calibrate the amplifier, allowing hence an efficiency optimization.

### 1.1.1 Phased Array

Antennas are key components of any wireless communication system. In the transmitting process, these devices permit the transmission of an electrical signal in the form of electromagnetic radiation. This radiation propagates through space and can be received by other antennas which in this case do the reciprocal process, that is turning an electromagnetic wave into an electrical signal which can then be elaborated by the processing circuits.

The dipole antenna is the simplest and probably the most used type of antenna. It consists of two identical conductive elements which are usually bilaterally symmetrical. However, its simplicity results also in limited performances. For example, once the length of the antenna has been set, also the current distribution on it is set, which results in a fixed radiation pattern that cannot be changed any more [7].

To overcome this limit and enhance system performance a solution, which is often used in practice, is the multiple antenna system. These systems are often made of different dipole antennas, arranged in a determined manner and fed by independent currents. By a proper choice of the number of these elements, the geometry and the excitations, it is possible to obtain a variety of radiation patterns.

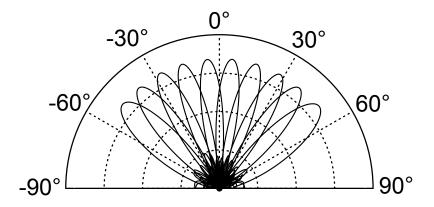

A special case of such systems is the adaptive antenna([9]). In a receiver, for example, the primary function of any adaptive antenna system is to maximize the received power from one particular direction while suppressing undesired signals coming from other directions. From the transmitter side, instead, the task is to focus almost all the irradiated energy in a determined direction. This concept can be represented by the radiation patterns shown in figure 1.1. Here it can be seen that an adaptive antenna is able to change its radiation pattern and hence to steer the beam in the desired direction. The steer of the beam can be realized both mechanically and electronically.

Figure 1.1: Adaptive antenna concept. Beam steered from  $-50^{\circ}$  to  $50^{\circ}$

An example of an adaptive antenna system, where the beam steering is done electronically, is the phased array configuration. Basically, the phased array antenna is composed of a group of individual elements, which are distributed and oriented in a linear one(or two)-dimensional spatial configuration. The amplitude and phase excitations of each element can be individually controlled to form the desired radiation pattern. The beam steering is controlled electronically by adjusting the phase of the excitation signals at the individual elements. This task is accomplished with the antenna aperture remaining fixed in space without the involvement of mechanical motion.

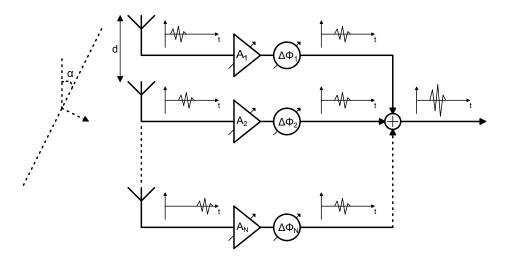

To get more insight about these systems, a complete block diagram of a phased array receiver is reported in figure 1.2. For a deeper analysis see [8]. It is worth to notice that all the considerations which will be hereafter made are also valid for the transmitter. In this example, the system is made by a linear antenna array composed by N equally spaced antennas. For simplicity, it is supposed that every antenna is followed by a programmable attenuator and a phase shifter; in practical applications also a low noise amplifying stage is typically present. The attenuator is usually used to correct the amplitude errors between the various paths, which are inevitably present due to manufacturing variations and design techniques. The phase shifter is used instead to realign the signals from the various paths, considering that the electromagnetic wave arrives in different time instants on each antenna. The output signal is finally obtained summing together the contributions of each

Figure 1.2: Phased array receiver

path.

When a plane electromagnetic wave arrives at the antenna array at an angle  $\alpha$  between the wave front and the array, the received signals by the various antennas experience a phase shift difference due to the difference in the propagation paths length. If d is the distance between adjacent antennas, v the propagation speed of the electromagnetic wave in the medium and  $\omega$  the angular frequency of the signal, the phase difference  $\Delta \phi$  between the signals in two adjacent antennas is

$$\Delta \phi = \frac{d \sin(\alpha)}{v} \omega \tag{1.1}$$

Considering that the array is made of N antennas, the total phase shift  $\Delta \phi_{tot}$  experienced by the signal in the last antenna compared to the one received from the first antenna is

$$\Delta\phi_{tot} = (N-1)\frac{d\sin(\alpha)}{v}\omega \tag{1.2}$$

Adjusting the phase shift introduced by each path in a proper way, a phase realignment of the various signals can be obtained. With sufficient antenna spacing, the noise of each antenna is uncorrelated to the noise of the other antennas in the array. Hence, the noise in each signal path before summation are independent. As a result, the shifted signals from the various antennas sum coherently while the noise sums incoherently. This results in an improvement of  $10 \log(N)[dB]$  in the SNR at the output of the N-element phased array receiver ([23]).

From another point of view, a phased array architecture can be seen as a system which permits to change the radiation pattern of the antenna array. With a certain phase setting for each path the system can be programmed to accept signals coming from one direction while rejecting signals coming from other directions.

Phased arrays have been traditionally used for military RADAR (RAdio Detection And Ranging) applications for many decades. The electronic beam steering of the phased array radar is orders of magnitude faster than the traditional radars based on mechanical rotation, which results in higher scanning speeds and lower profile for the system.

Although the first use of phased array RADARs was for military applications, nowadays its use is extended beyond this context. Other important applications can be easily find in the automotive. In this context driving-aid functions such as collision avoidance radar, automatic cruise control technology, parking aid and side collision warning can make safer and easier the driving experience ([10]).

Phased arrays are also used in wireless communication systems and in particular in cellular base-stations to enhance the signal coverage in the area of interest.

Biomedical applications are among the emerging applications that can take advantage of phased-array systems. For instance, phased array can be used in microwave imaging to detect early stage breast cancer ([8]).

### 1.1.2 Doherty Power Amplifier (DPA)

The market of wireless communication increased dramatically in the last 20 years, and the high demand in the network access has led many service providers to investigate digital technology to satisfy all the users ([6]).

These investigations brought to the development of complex digital modulation schemes such as Orthogonal Frequency-Division Multiplexing (OFDM), used in several 4G networks. These modulation schemes use amplitude modulated (AM) signals with high peak-to-average ratio (PAR), making more challenging the design of the electronic circuits and in particular power amplifiers ([11]).

The power amplification of amplitude modulated RF signals has mainly two problems. The first is that the envelope, and hence the modulating signal, will be distorted if the amplifier is used at its full nominal power level. The second is that conventional power amplifier designs only give maximum efficiency at a single power level, which is dependent on the circuit design but it is usually near the maximum nominal power for the device. As the input power is backed off from this point, the efficiency drops quickly and the heat dissipation can increase. The overall effect is therefore that the mean efficiency, which is much lower than the efficiency at the maximum power level, must be considered ([5]).

Several efficiency enhancement techniques were invented over the years and among them three classical techniques are worth to be mentioned: the Envelope Elimination and Restoration (EER), the Envelope Tracking(ET) and the Doherty Amplifier. In this example the Doherty PA technique is presented.

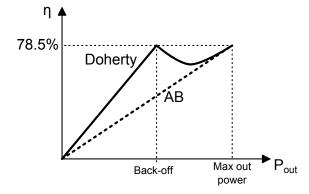

The Doherty amplifier configuration is realized using two power amplifiers, called the main (M) and the peak (P) amplifiers. This technique allows to realize an amplification process with higher efficiency over a wide range of output power with respect to a classic linear amplifier configuration. The peak amplifier is turned off for low power levels, while the main amplifier alone provides the power to the load. The peak amplifier starts to conduct only when the output power exceeds a certain amount, defined as the output power back-off, and together with the main amplifier provides the necessary power to the load. The main amplifier is often biased in class AB while the peak amplifier in class C. The typical DPA efficiency in function of the output power is reported in figure 1.3. The curve of an AB class amplifier is also reported in the figure and as it can be seen the efficiency of the Doherty

Figure 1.3: Dohery amplifier versus standard class AB amplifier efficiency (dashed line)

Figure 1.4: Active load-pull concept used in the DPA architecture

amplifier is clearly better ([13]).

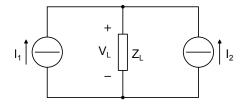

The DPA configuration makes use of the active load-pull technique, i.e. the concept that the impedance of an RF load can be modified by applying a current from another phase coherent source ([5]). To fully understand the DPA behaviour it is then useful to introduce first this concept(Fig. 1.4). Considering that the load voltage is  $V_L = Z_L(I_1 + I_2)$  it is than easy to calculate the load impedance  $Z_1$  seen from the current generator  $I_1$ , that is

$$Z_1 = Z_L \left( 1 + \frac{I_2}{I_1} \right) \tag{1.3}$$

A similar expression can be found for the load impedance seen from the generator  $I_2$ . From equation 1.3 in can be seen that the impedance seen from one generator can be modulated by the current of the other generator. In particular, the impedance  $Z_1$  can be increased if  $I_2$  is in phase with  $I_1$ , while it can be decreased if  $I_2$  and  $I_1$  are in anti-phase.

The Doherty amplifier uses this concept with some small modifications and

Figure 1.5: Doherty power amplifier

a practical implementation diagram is usually similar to the one reported in figure 1.5. As it can be seen it is made of two amplifiers which contribute is combined through an impedance inverting network.

For small input power levels the DPA acts as a typical PA, since the main device is conducting while the auxiliary is turned off due to its Class C bias condition. Assuming that the auxiliary PA's output is an open-circuit in this case, it is straightforward to deduce that the output impedance  $Z_M$  of the main amplifier is  $2Z_0$ .

Increasing the input power level, the current supplied by the main amplifier to the load increases reaching the device saturation, hence the maximum efficiency condition. The key action of the Doherty amplifier occurs in this moment; in fact, for higher input power level the auxiliary device automatically turns on, injecting current into the output load. This current increases the output voltage and modulates the impedance  $Z_M$  seen by the main device which, thanks to the impedance inverting network, becomes lower than  $2Z_0$ . In this way the main device is maintained in a constant maximum output voltage, and thus maximum efficiency condition. When both amplifiers contribute their maximum power, each device sees a load impedance of  $Z_0$ and contributes equally to the overall output power.

It is worth to notice that another inverting network is present on the signal path of the auxiliary amplifier. It is, in fact, necessary to compensate the presence of the inverting network at the output of the main device and allow

Figure 1.6: Doherty Power amplifier with the amplitude/phase control circuit

the in phase sum of the signals on the load impedance.

In practical implementations of the Doherty amplifier some important considerations must be made. A key design constraint in any DPA is to match the amplitude and phase of the signals at the input of the main  $V_M$  and peaking  $V_P$  amplifiers such that the desired load modulation is achieved and the output signals are combined as expected at the summing node. Independent variations in amplitude and/or phase of these signals, which may arise for example from small variations in the manufacturing of the packaged transistor, PCB tolerances and tolerances in surface mounted capacitors can result in large performance differences for the Doherty amplifier. Phase and amplitude control of the incident signals enables significant performance improvement of the DPAs [14].

This is why phase shifters and attenuators are important in this system. In fact, putting a cascade of an attenuator and a phase shifter in each of the two paths of the Doherty configuration enables the control over the amplitude and phase imbalances optimizing hence the signals combining at the output node (fig.1.6). This results in an optimization of the amplifier efficiency.

## **1.2** Target Specifications

In the previous section two examples where phase shifters and attenuators are used have been given. In particular, the aim of this thesis is the design of these two blocks for the Doherty power amplifier application ([15]) using the Infineon 130nm CMOS technology with a high resistive substrate [16]. The tentative target specifications for the phase shifter are reported in table 1.1, while those for the programmable attenuator are reported in table 1.2. The target specifications listed in the two tables are intended in the

| f[GHz] | S11[dB] | IL[dB] | $\Delta \phi [^{\circ}]$ | $Step[^{\circ}]$ | P1dB[dBm] |

|--------|---------|--------|--------------------------|------------------|-----------|

| 2      | < -10   | < 3    | > 45                     | < 6              | > 20      |

Table 1.1: Phase shifter target specifications

| f[GHz] | S11[dB] | IL[dB] | $\Delta S_{21}[dB]$ | Step[dB] | P1dB[dBm] |

|--------|---------|--------|---------------------|----------|-----------|

| 2      | < -10   | < 1.5  | > 15                | 0.5      | > 20      |

Table 1.2: Attenuator target specifications

frequency range from 1GHz to 3GHz. This means that the unitary fractional bandwidth is required. The two blocks must handle and have linear behaviour for high input powers; the 1-dB compression-point P1dB should be higher than 20dBm. Moreover, they have to be realized with only passive components, and hence they should not consume power.

From table 1.1 it can be seen that the phase shifter should have an Insertion Loss (IL) lower than 3dB and a phase shift range of at least  $45^{\circ}$  with steps of  $6^{\circ}$ . Moreover it should achieve this task with an as low as possible insertion loss variation over different phase shift configurations.

From table 1.2, instead, it can be seen that the attenuator should have an attenuation range  $\Delta S_{21}$  of at least 15dB with steps of 0.5dB. Furthermore the attenuator should show a phase variation  $\Delta \phi$  over different attenuation settings less than 3°.

### **1.3** Network Analysis Basics

The aim of this section is to recall some basic tools for network analysis which have been often used in this work and which can be useful to more

Figure 1.7: 2-port network

easily understand all the presented concepts. For a deeper discussion refer to [1], [2].

#### **1.3.1** The Scattering Matrix

Almost all circuits analysed in this thesis can be seen as passive linear two port networks (Fig. 1.7). This kind of circuits can be characterized in various ways. To simplify the analysis and also emphasize important design criteria, it is often useful to use higher-level descriptions which mainly focus on the input-output behaviour but neglect details of the internal circuit structure. At lower frequencies the most common representations are the *impedance* and *admittance matrices*, or a mixture of them.

A different way to describe a network, especially useful when dealing with circuits at radio frequencies, is the *scattering matrix*. This matrix relates the voltage waves incident on each ports to the voltage waves reflected from each port. If  $V_i^+$  is the amplitude of the voltage wave incident on port *i* and  $V_i^-$  is the amplitude of the voltage wave reflected from port *i*, the scattering matrix [S] of a 2-port network is defined as:

$$\begin{bmatrix} V_1^- \\ V_2^- \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} V_1^+ \\ V_2^+ \end{bmatrix}$$

(1.4)

where each specific element  $S_{ij}$  is defined as:

$$S_{ij} = \frac{V_i^-}{V_j^+} \Big|_{V_k = 0 \text{ for } k \neq j}$$

(1.5)

In words, the last equation says that  $S_{ij}$  is found by driving the port j with an incident wave of voltage  $V_j^+$  and measuring the reflected wave amplitude  $V_i^-$  coming out of the port i while all the other ports are terminated in matched loads to avoid reflections.

The use of S-parameters is mainly due to practical measurement reasons. In fact, at radio frequencies it is difficult to provide adequate short- or opencircuits which would be necessary to measure impedance ad admittance parameters. To measure S-parameters, instead, it is necessary to provide an adequate matching condition at ports and this is much easier to do.

An interesting property of the scattering matrix, which will be used subsequently, is worth to be reminded. It regards reciprocal networks and states that the scattering matrix in this cases is symmetric, i.e.:

$$S = S^T \tag{1.6}$$

where T stands for transpose of the matrix.

### 1.3.2 The ABCD Matrix

Another convenient network description used to represent (only) two port networks is the *transmission*, or *ABCD*, *matrix*. The input port voltage and current are related to the output port voltage and current through the next equations:

$$\begin{bmatrix} V_1 \\ I_1 \end{bmatrix} = \begin{bmatrix} A & B \\ C & D \end{bmatrix} \begin{bmatrix} V_2 \\ I_2 \end{bmatrix}$$

(1.7)

where the A, B, C and D parameters made the transmission matrix. These coefficients can be found short-circuiting or open-circuiting the output port, obtaining:

$$A = \frac{V_1}{V_2}\Big|_{I_2=0} \qquad B = \frac{V_1}{I_2}\Big|_{V_2=0} \qquad C = \frac{I_1}{V_2}\Big|_{I_2=0} \qquad D = \frac{I_1}{I_2}\Big|_{V_2=0}$$

(1.8)

This model is particularly useful when dealing with the cascade of two or more 2-port networks. In fact the ABCD matrix of this kind of system can be found by multiplying the ABCD matrices of the individual 2-port networks. This is the reason why the sign convention of  $I_2$  has been chosen to flow out of port 2 (see Fig. 1.7). In fact putting two stages in cascade the current flowing out from the first stage goes inside the second stage and the sign conventions agree.

#### **Relation to S-Matrix**

Even though the ABCD-parameters are difficult to measure in practice, they are extremely useful for network analysis. Moreover, once the ABCD-matrix coefficients are known, the S-parameters can be easily calculated from them through the next expressions:

$$S_{11} = \frac{A + B/Z_0 - CZ_0 - D}{A + B/Z_0 + CZ_0 + D}$$

(1.9)

$$S_{12} = \frac{2(AD - BC)}{A + B/Z_0 + CZ_0 + D}$$

(1.10)

$$S_{21} = \frac{2}{A + B/Z_0 + CZ_0 + D} \tag{1.11}$$

$$S_{22} = \frac{-A + B/Z_0 - CZ_0 + D}{A + B/Z_0 + CZ_0 + D}$$

(1.12)

It is important to underline that these expressions are valid as soon as the characteristic impedances are the same on all the ports (equal to  $Z_0$ ). Otherwise different equations must be used (see [1]).

### **1.3.3** Mutual Inductors

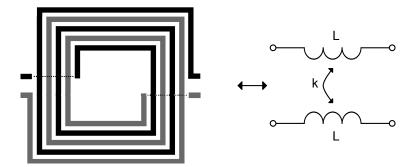

Another element which is widely used in this work and which is worth to be recalled is the transformer. As an anticipation the transformer will be used instead of two uncoupled inductors exploiting the mutual inductance to increase the effective inductance. In the appendix B it is shown how this fact can be achieved.

A transformer, which electrical representation is reported in figure 1.8, can be mathematically described through the following equations:

Figure 1.8: A transformer representation

$$\begin{cases} V_1 = i\omega L_1 I_1 + i\omega M I_2 \\ V_2 = i\omega M I_1 + i\omega L_2 I_2 \end{cases}$$

(1.13)

The coefficient M is called *mutual induction coefficient* and it takes into account the interaction between inductors and it can be both positive and negative. The mutual induction coefficient is positive (M > 0) if the magnetic field lines generated from the coils have the same direction when concatenated to each other; the mutual induction coefficient is negative (M < 0)otherwise. Moreover, higher M coefficient means that higher is the quantity of the magnetic field lines generated from one inductor that are concatenated with the other.

Another parameter often used and closely related to M is the *coupling coef*ficient k, defined as:

$$k = \frac{M}{\sqrt{L_1 L_2}}, \qquad |k| \leqslant 1 \tag{1.14}$$

The coupling coefficient is null (k = 0) when no interaction between inductors is present; instead, its magnitude is unitary (|k| = 1) when all the magnetic field lines generated from one inductor are concatenated with the other. Moreover, it is worth to observe that the mutual induction and the coupling coefficients have the same sign, hence the considerations made for M are valid also for k.

#### 1.3.4 Linearity - P1dB

The distortion is a phenomenon related to the fact that real devices (transistors, diodes etc..) are non linear, and this origins spurious frequency contributions. Any difference in the shape of the input and the output waveforms versus time, not considering scaling factor and time translation, is called distortion. For example, MOSFETs are often used as switches and when they are in the closed state they can be represented with a series resistance, which is due to the channel resistance of the MOS. For small signals this resistance can be assumed linear and the overall system is not affected. However, when the signal amplitude increases, the channel resistance starts to deviate from the linear behaviour and the overall system linearity is affected.

For a memoryless non-linear system the input/output characteristic can be approximated with a polynomial ([4]):

$$y(t) = a_0 + a_1 x(t) + a_2 x^2(t) + a_3 x^3(t) + \cdots$$

(1.15)

where x(t) and y(t) are, respectively, the input and output signals while  $a_i$  coefficients represent the response of the system. The coefficient  $a_0$  represents the dc component of the output signal,  $a_1$  is the linear gain of the system, whereas  $a_2$ ,  $a_3$ , ..., describe the distortion of the system.

Assuming that the input signal is a pure sinusoid  $x(t) = A\cos(\omega t)$ , and remembering the trigonometric relations  $\cos^2(x) = (1+\cos(2x))/2$  and  $\cos^3(x) = (3\cos(x) + \cos(3x))/4$ , the output signal of equation 1.15, truncated at the third order, can be expressed as:

$$y(t) = a_0 + a_1 A \cos(\omega t) + a_2 A^2 \cos^2(\omega t) + a_3 A^3 \cos^3(\omega t)$$

=  $\left(a_0 + \frac{a_2 A^2}{2}\right) + \left(a_1 A + \frac{3a_3 A^3}{4}\right) \cos(\omega t) +$

+  $\frac{a_2 A^2}{2} \cos(2\omega t) + \frac{a_3 A^3}{4} \cos(3\omega t)$  (1.16)

It can be seen that due to non-linearities in the system, even if at the input a single-tone signal is applied, higher order harmonics are present at the output. Moreover, the second order distortion causes a DC offset, while the

Figure 1.9: 1-dB compression-point

third order distortion produces a gain variation.

Different figures of merit exist to quantify the harmonic distortion of a system ([4]). In this work the 1-dB compression-point (P1dB) will be prevalently used. Looking at the fundamental tone term in Eq. 1.16

$$y(t) = \dots + \left(a_1 A + \frac{3a_3 A^3}{4}\right) \cos(\omega t) + \dots$$

(1.17)

it can be seen that it depends on the third order distortion. Often  $a_3 < 0$  which leads to a gain reduction (or compression). This gain compression affects the system for higher amplitudes A of the input signal. The 1-dB compression-point is defined as the input amplitude (or power) value which causes the gain to drop by 1dB compared to the ideal case. This concept is represented in figure 1.9.

It is worth to notice that here, for simplicity, it has been assumed a maximum 3rd order distortion. In general higher order distortions can be present in the system and they also influence the gain variation, as well as the DC signal value.

# Chapter 2

# Analysis and Design of a Phase Shifter

In the previous chapter some of the applications where phase shifters can be used have been presented. In phased arrays, for example, they are used to change the pattern of a multiple-antenna system while in the Doherty Power Amplifiers they are used to compensate the parasitics effect and hence optimize the power amplifiers efficiency.

In this chapter, phase shifters will be discussed more in detail. Different possible ways in which they can be realized are presented and among them the  $\pi$ -network topology is chosen for a deep analysis and a successive design of a phase shifter for DPA application.

Finally, an alternative topology, which has been explored trying to obtain better circuit performance mainly in terms of insertion loss, is presented.

## 2.1 Introduction to Phase Shifters

A phase shifter is a two port network which permits the control of the phase difference between the output and the input signals by means of a control signal (DC voltage). In other words, considering the notation reported in figure 2.1, it is possible to control the parameter  $\Delta\phi$ . Ideally this phase shift should be achieved without losses.

Figure 2.1: 2-port phase shifter

Different phase shifter types have been presented over the years and the choice of which one to implement depends on the available technology and the application. One first distinction that can be made is between analog and digital phase shifters. In *analog* phase shifters the phase difference can be varied in a continuous manner by means of a continuous variation of the control signal. On the other hand, in *digital* phase shifters, the phase difference can be changed only within a finite set of values; in many applications, however, it is enough.

From the technology point of view, semiconductor phase shifters are here considered. They can be made in mainly two different ways: the first one is based on the use of Micro Electro-Mechanical Systems (MEMS) ([18]) while the second on semiconductor devices(pin diodes, MOSFETs) ([24] -[31]). The former technology basically makes available less lossy switches compared to the latter one, however it is not always available. With regard to the latter one, the choice is often between gallium arsenide (GaAs) and silicon (Si) technologies and it is based on the compromise between performances and costs. The goal of this work was to design a state of the art circuit, using a CMOS process.

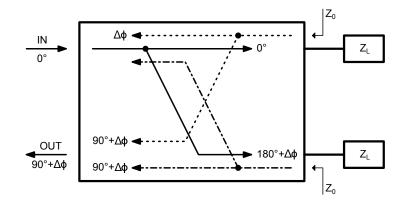

Phase shifters using semiconductor devices can be mainly of the reflection or transmission type. A reflection-type phase shifter (RTPS) consists of a hybrid 90° coupler combined with two reflective loads [31]. Its operation is reported in figure 2.2. The input signal is split in two equal parts which reach the loads with a 90° phase difference between them. Each part is then reflected again by a load with an input impedance  $(Z_L)$  which is different from the characteristic impedance of the coupler  $(Z_0)$ . This impedance difference

Figure 2.2: Operation of a reflective-type phase shifter

introduces a phase shift  $(\Delta \phi)$  which is equal to the phase of the reflection coefficient  $\rho$ :

$$\rho = \frac{Z_L - Z_0}{Z_L + Z_0} \tag{2.1}$$

The reflected signals are then split and phase shifted again by the coupler, obtaining that signals arriving at the input are in opposition of phase and they cancel each other, while the signals arriving at the output are in phase and sum constructively with a total phase shift (compared to the input) of  $90^{\circ} + \Delta \phi$ . Changing hence the load impedances it is possible to change the phase difference between output and input. This can be done, for example, by varying the load capacitance with a simple varactor. The choice of the reflective load depends on the required phase shift and allowable losses. In fact, the use of a complex load can give a high phase shift from one side, but from the other it gives also high losses. Hence a compromise for a specific application should be found.

The other type of phase shifters, *transmission-type*, can be further divided into two groups: switched-line and loaded-line phase shifters. The *switchedline* phase shifter is, conceptually, the simplest one. The basic configuration for a 1-bit phase shifter is shown in figure 2.3. As it can be seen, two signal paths for the signal are possible and the two Single-Pole-Double-Throw (SPDT) switches are used to chose one of them. The two paths are usually realized with transmission lines having a different length. When the signal passes through the longest path it experiences an additional phase delay

Figure 2.3: Switched-line phase shifter

compared to the other path of:

$$\Delta \phi = \frac{2\pi f}{v_p} \Delta l \tag{2.2}$$

where  $v_p$  is the phase velocity. In this type of phase shifter the insertion loss is mainly due to the switches, hence the use of this solution is legitimate only if a technology with good switches is available.

An interesting thing which can be observed in switched-line phase shifters is that the phase shift  $\Delta \phi$  is proportional to the frequency. This is actually obvious, since transmission lines introduce a constant time delay. Hence the time delay difference between the two paths can be expressed as:

$$\Delta \tau = \frac{\Delta l}{v_p} \tag{2.3}$$

Because of this feature, switched-line phase shifters are also called *switched delay lines*. This concept is presented in detail in the next subsection, where the difference between constant phase shift and constant time delay will be explained.

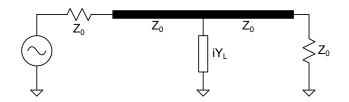

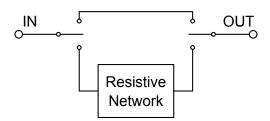

The other type of phase shifters is the *loaded-line* phase shifters. It is mainly based on a uniform transmission line which is periodically loaded with small reactive impedances. A simple example, to better explain this concept, is shown in figure 2.4. It can be shown ([3]) that if  $Y_L$  is the susceptance of the loaded impedance and  $Z_0$  is the characteristic impedance of the transmission line, then the phase shift introduced by the phase shifter can be expressed

Figure 2.4: Loaded-line phase shifter

Figure 2.5: Ideal phase response of a Phase Shifter and a True Time Delay for different phase shift configurations

as:

$$\Delta \phi = \tan^{-1} \left( \frac{Y_L Z_0}{2} \right) \tag{2.4}$$

This topology is the basic idea of this work, hence it will be deeply analysed in this chapter.

### 2.1.1 Phase Shifter vs True Time Delay (TTD)

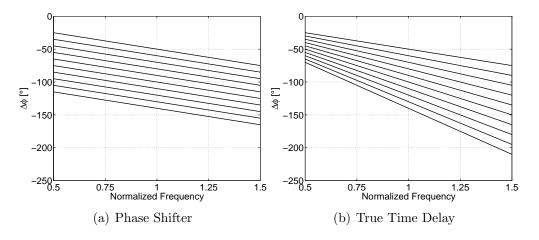

In section 2.1 it has been seen that switching between two transmission lines introduces a constant time delay difference instead of a constant phase shift difference. Actually this type of circuits should be rather called delay lines, or also *True Time Delay (TTD)* phase shifters.

To better explain this concept the ideal phase shift response for both phase shifter and TTD is reported in figure 2.5. From the figure it can be seen that, for both of these elements, it is possible to change the desired phase shift. However, the various shifting configurations are different between them in the two cases. In the phase shifter different configurations have the same slope and hence the phase difference between two different configurations is constant over frequency. In the TTD, instead, different configurations have different slope and the phase difference between two different configurations is not constant over frequency. What is constant in this case is the group delay difference between various configurations, which is defined as:

$$\tau_g = -\frac{d\phi}{d\omega} \tag{2.5}$$

The choice of which of the two types to use depends mainly on the application. In narrow band systems the two solutions usually have similar behaviour. In wide band systems, for example timed arrays, the TTD should be used otherwise the presence of signal dispersion could worsen degrades the system performances ([23]).

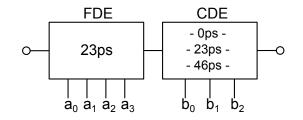

### 2.1.2 Specifications in the Time Domain

The initial specifications have been set considering the phase of the signal and hence the desired phase shift. As it has been shown previously a TTD phase shifter has a constant time delay instead of the phase shift. In this work, after an accurate analysis of the system, it has been decided to implement a TTD phase shifter. Therefore, the specifications have been translated in the time domain and are reported in table 2.1, for convenience. The targets

| f[GHz] | S11[dB] | IL[dB] | $\Delta \tau_g [ps]$ | Step[ps] | P1dB[dBm] |

|--------|---------|--------|----------------------|----------|-----------|

| 2      | < -10   | < 3    | > 65                 | < 8      | > 20      |

Table 2.1: Phase shifter TTD target specifications

reported in table 2.1 are intended for a frequency range of  $1 \div 3GHz$ . They have been obtained expressing in time the specifications presented in the table 1.1. The conversion phase-time has been made considering a frequency

Figure 2.6: Lumped delay line, topology also called  $\pi$  – *network*

of 2GHz. For example the specification on the step comes from the fact that  $6^{\circ}$  corresponds to  $6/360 \cdot 1/(2GHz) \simeq 8ps$ .

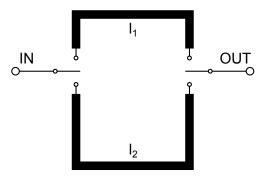

## 2.2 Tunable Delay Line

Phase shifter topologies presented so far mainly use transmission lines. Considering that the center frequency of the phase shifter designed in this work is 2GHz, the use of one of these solutions would probably complicate the design. In fact, a signal at this frequency has a wavelength  $\lambda$  of about 4cmin the used CMOS technology and a phase shift  $\Delta\phi$  of  $45^{\circ}$  would require a transmission line of at least 0.05cm length for the switched line topology. Implementing a line of this length in the CMOS technology would mean to accept a circuit with high losses; this is unacceptable considering that one of the requirement is to minimize the losses as much as possible.

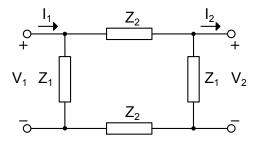

Even though transmission lines offer wide bandwidth, for applications under 4-5GHz an often used concept is *lumped delay lines*. Considering the network in figure 2.6, it is made using lumped elements and it can be seen as an approximation of a transmission line with characteristic impedance  $Z_0$  over a finite bandwidth, that is for frequencies lower than the *cut-off frequency*  $f_c$ ; these parameters, as will be shown soon, are related to the circuit elements through the following expressions:

$$Z_0 = \sqrt{\frac{L}{C}}, \qquad f_c = \frac{1}{2\pi\sqrt{LC}} = \frac{\omega_c}{2\pi}$$

(2.6)

Moreover, a signal which goes through this circuit undergoes a group delay of:

$$\tau_g = 2\sqrt{LC} \tag{2.7}$$

Even though this solution has a finite bandwidth, it allows to have a greater control over the line parameters. In fact, for example, varying the inductance or the capacitance value it is possible to vary the delay. It is true that also the characteristic impedance and the cut-off frequency vary but this is not necessarily a problem, as will be seen soon.

The equations just presented are valid for frequencies much smaller than the cut-off frequency; a deeper analysis of the  $\pi$ -network of figure 2.6 is now made with the aim to extract the equations which completely describes the circuit behaviour, even for frequencies higher than the cut-off frequency. Exploiting the calculus reported in the appendix A for the generic  $\pi$ -network, the ABCD-matrix of the lumped delay line results:

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} 1 - \omega^2 2LC & i\omega 2L \\ i\omega 2(1 - \omega^2 LC^2) & 1 - \omega^2 2LC \end{bmatrix}$$

(2.8)

Remembering the equations 1.9 and 1.11, reported in the introduction, which relates the ABCD parameters to the S-parameters, it is possible to calculate the reflection coefficient  $S_{11}$  and the transmission coefficient  $S_{21}$  as:

$$S_{11} = \frac{A + B/Z_0 - CZ_0 - D}{A + B/Z_0 + CZ_0 + D}$$

(2.9)

$$S_{21} = \frac{2}{A + B/Z_0 + CZ_0 + D} \tag{2.10}$$

The coefficients  $S_{22}$  and  $S_{12}$  are not reported since the network is symmetric and they are equal to  $S_{11}$  and  $S_{21}$ , respectively.

Let's consider for a moment the first expression. When a generator with internal impedance  $Z_g$  drives a transmission line, the latter has to have a characteristic impedance  $Z_0 = Z_g$  to satisfy the matching condition. This matching consideration derives from the condition that no reflections occur at the input port, that is  $S_{11} = 0$ . Applying the same condition to the first equation allows to extract the characteristic impedance associated to the  $\pi$ -network (which will be called *cell* in this context):

$$S_{11} = 0 \quad \Rightarrow \quad Z_{0c}(\omega) = \sqrt{\frac{L}{C} \left[1 - \left(\frac{\omega}{\omega_c}\right)^2\right]^{-1}}$$

(2.11)

where  $\omega_c = 1/\sqrt{LC}$  is the cut-off angular frequency and represents the frequency at which the characteristic impedance becomes imaginary. Notice that in the last expression  $Z_{0c}$  notation has been used instead of  $Z_0$  with the aim to emphasize the fact that the characteristic impedance of the cell is considered.

Focusing now on the equation 2.10 and substituting the ABCD parameters, the transmission coefficient  $S_{21}$  is obtained:

$$S_{21}(i\omega) = \frac{1}{(1 - 2\omega^2/\omega_c^2) + i[\omega(L/Z_0 + CZ_0) - \omega^3 CZ_0/\omega_c^2]}$$

(2.12)

Note that  $S_{21}$  mostly influences the insertion loss of the cell. However, in these expression only the finite bandwidth is taken into account since the inductor and capacitor are assumed to be ideal (infinite quality factor Q). The introduction of parasitics would heavily complicate the discussion and increase the risk to ignore more important things for the design. This task is left to the simulators.

The phase difference introduced by the cell can be calculated now, looking at the phase of the transmission coefficient  $S_{21}$

$$\phi_{21}(\omega) = -\arctan\left[\frac{\omega(L/Z_0 + CZ_0) - \omega^3 CZ_0/\omega_c^2}{1 - 2\omega^2/\omega_c^2}\right]$$

(2.13)

Finally, the group delay of the cell, defined as the derivative of the phase with respect to frequency, can be calculated from the last equation and results:

$$\tau_g(\omega) = -\frac{d}{d\omega} [\phi_{21}(\omega)] = \frac{(L/Z_0 + CZ_0)(1 + 2\omega^2/\omega_c^2) - \omega^2 CZ_0(3 - 2\omega^2/\omega_c^2)/\omega_c^2}{(1 - 2\omega^2/\omega_c^2)^2 + \omega^2 (L/Z_0 + CZ_0 - \omega^2 CZ_0/\omega_c^2)^2}$$

(2.14)

Supposing now that the matching condition is satisfied, i.e.  $Z_{0c} = Z_0$ , the last equation can be written in a simple way for frequencies much smaller than the cut-off frequency as:

$$\tau_{g,DC} = \tau_g(0) = 2\sqrt{LC} \tag{2.15}$$

As expected this equation coincides with the equation 2.7 introduced at the beginning of this section, when the lumped delay network has been introduced. It gives a rule of thumb on the selection of the component values. Note also that from the last equation it can be seen that:

$$\tau_{g,DC} = 2\sqrt{LC} = \frac{2}{\omega_c} \tag{2.16}$$

which means that there is a limit on the maximum delay which can be introduced from a single cell for a specific bandwidth. In fact, as it will be seen later, higher delays can be obtained by the cascade of more cells.

A variable delay element is able to change the group delay depending on the value of the control signal. The last equation suggests that this can be done by simply changing the capacitance or the inductance value. In passive circuits a variable capacitance is much easily done, for example with varactors. Hence, replacing the capacitors in the schematic of figure 2.6 with varactors, a variable delay element can be obtained. However, the change of the capacitance values leads to a change of the characteristic impedance of the cell  $Z_{0c}$ . Since the source and load impedances are fixed and equal to  $Z_0$ , the cell cannot be perfectly matched both when the capacitance is minimum  $C_{min}$  and maximum  $C_{MAX}$ . Therefore the group delay difference  $\Delta \tau_g$  between maximum and minimum capacitance configurations must be derived from the general  $\tau_q(\omega)$  equation:

$$\Delta \tau_{g,DC} = \tau_{g,DC}|_{C=C_{MAX}} - \tau_{g,DC}|_{C=C_{min}} = (\alpha - 1)C_{min}Z_0$$

(2.17)

where  $\alpha = C_{MAX}/C_{min}$ . Considering that a capacitance variation results in a characteristic impedance variation, a good matching condition for both the maximum and minimum capacitance cases is when the source/load impedance

### 2.2. TUNABLE DELAY LINE

$Z_0$  is equal to the geometrical mean of the minimum  $Z_{0c,min}$  and maximum  $Z_{0c,MAX}$  characteristic impedance of the cell ([8]), i.e.:

$$Z_{0c,opt} = \sqrt{Z_{0c,min} Z_{0c,MAX}} \tag{2.18}$$

In this condition the group delay difference of the cell can be expressed as:

$$\Delta \tau_{g,DC} = \frac{(\alpha - 1)}{\sqrt[4]{\alpha}} \sqrt{LC_{min}}$$

(2.19)

From the last equation it can be seen that the  $\alpha$  coefficient results in a larger delay variation per cell. However, as it has just been shown, the change of the capacitance leads to a change of the characteristic impedance of the cell. As a result, a higher  $\alpha$  causes a higher  $Z_{0c}$  variation and hence a lower input matching which is associated with a higher insertion loss.

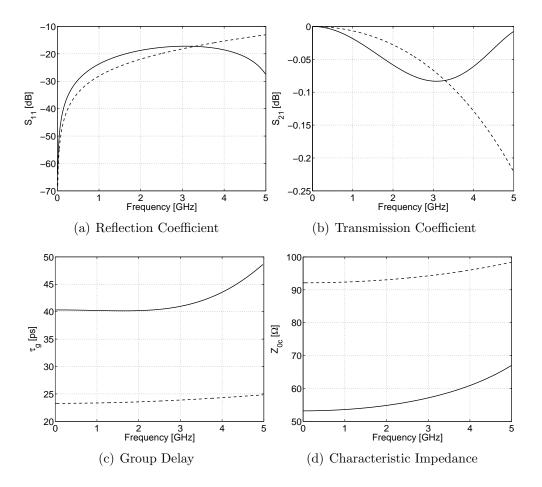

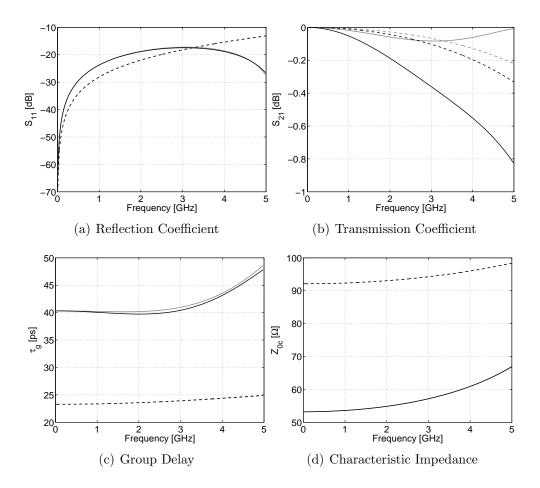

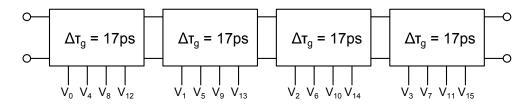

To better explain the concept on which is based this delay element, an example of design is reported in figure 2.7. Some of the parameters, introduced in the previous discussion, are shown in this figure with two curves per plot which represents the maximum and minimum capacitance cases. The cell has been designed to have a group delay difference  $\Delta \tau_g$  of 17ps and characteristic impedance  $Z_{0c}$  is 70 $\Omega$ . These values are similar to the values of the finally designed delay line and they can already give some clues on its behaviour.

The figure 2.7(a) shows that the reflection coefficient  $S_{11}$  is lower than -17dBover all the band. A rule of thumb usually used is  $S_{11} < -10dB$ , which means that less than 10% of the power is reflected from the cell. Hence, in this case, even if the characteristic impedance of the cell (Fig. 2.7(d)) is not constant, this is not a problem. It could become important if the delay difference asked to the cell is substantially higher than 17ps; however in this case even the finite bandwidth would become a problem. In fact, as it can be seen from the figure 2.7(c), the maximum capacitance case curve starts to increase around 3.5 - 4GHz and this is due to the finite bandwidth. This increase introduces delay error in the cell which, for low bandwidth values, can become important. Observe that, as it can be seen easily from the formulas previously derived, higher capacitance C means higher group delay  $\tau_g$  but also

Figure 2.7: Tunable delay element concept. In figure are reported graphics for the  $C_{MAX}$  and  $C_{min}$  (dashed line) cases

Figure 2.8: Comparison between infinite quality factor of the components (grey lines) and finite quality factor. Dashed lines represent the  $C_{min}$  case

lower characteristic impedance  $Z_{0c}$  and cut-off frequency  $f_c$ . This fact sets the limit on the maximum delay variation obtainable from a single cell.

In this example ideal components have been assumed, that is infinite quality factor for both capacitor and inductor. If parasitics are introduced, which means to consider the finite quality factor of the reactive elements, the cell behaves slightly different. Figure 2.8 shows the comparison between the ideal case (dashed line) and a more realistic case where the inductor and the capacitor have finite quality factors of, respectively,  $Q_L = 10$  and  $Q_C = 20$ . It can be observed that the most remarkable changes concern the transmission coefficient and the group delay difference, while the other two parameters do not change significantly.

## 2.3 Cell Design

The  $\pi$ -network topology previously introduced and used to realize the phase shifter is a passive network and it is basically made of inductors and capacitors. As it has been seen from the last examples these elements have a finite quality factor Q, which means that some parasitic series resistances are present in the circuit. The main effect of these resistances, as it can be seen from the figure 2.8(b) is to introduce additional losses and they should be made as low as possible with an accurate design of the reactive elements. In this section some guidelines for the optimal design of these components are presented, starting from the inductor.

### 2.3.1 Inductors Design

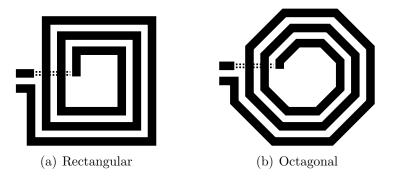

An often used method to realize on-chip inductors is the planar spiral. Figure 2.9 shows some possible shapes. In terms of the inductance and the quality factor values, different shapes have different characteristics. A circular shape is usually better than the square one in terms of the quality factor Q and the choice of which one to implement mainly depends on the available technology. On the other hand, the characteristics of the inductor like the area, number of turns, width of the strips etc. are usually influenced by the application. For a detailed discussion about IC inductors see [2],[19].

Another possibility to realize on-chip inductors is to use active circuits to synthesize the equivalent of an inductor. These circuits, however, introduce more distortion and power consumption than a passive implementation and considering that in this work it is required no power consumption, the passive solution has been chosen.

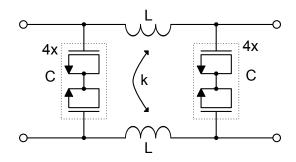

When more than one inductor is required from the circuit topology, as it is the case in the  $\pi$ -network presented previously, another possibility is to use a transformer instead of uncoupled inductors. An example of a possible implementation as a planar spirals is shown in figure 2.10 for the case of two

Figure 2.9: Possible inductor shapes

Figure 2.10: Interleaved transformer

inductors. In fact, exploiting the coupling between inductors, it is possible to obtain higher effective inductances value for the same on-chip area. Or, from the other point of view, the same inductances value can be implemented in a smaller area. It is important to notice that this is not a general rule; in this case the higher inductance is obtained because of the differential driving signals. This concepts are better explained in the appendix B. Furthermore it is shown that the increase is closely related to the coupling coefficient k. Higher k means also higher increase in the effective inductance. The transformer in figure 2.10, usually called interleaved transformer, is well suited for four-port applications that demand symmetry. For this reason it is a good solution to be used in the  $\pi$ -network topology.

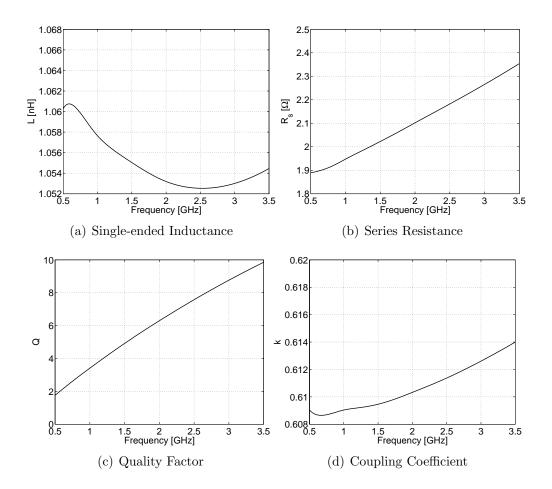

The inductors are mainly described by two parameters, that is the inductance

value L and the quality factor Q. The quality factor is defined as:

$$Q(\omega) = \frac{\omega L(\omega)}{R_s(\omega)} \tag{2.20}$$

where  $R_s$  is the series parasitic resistance. It is worth to notice that all the parameters are frequency dependent. However focusing on a sufficiently finite bandwidth they can be considered almost constant. Usually the inductance and the quality factor values are specified at a determined frequency.

Another important parameter to be considered are the parasitic capacitances. In an inductor they mainly account for the existing capacitance between the coils and the substrate. In the transformer also a capacitance between different coils is present. Considering that in the differential  $\pi$  topology used in this work this parasitic capacitance goes in parallel to the external capacitor, it should be taken into account in the design. Its presence results in a lower overall  $\alpha$  coefficient and hence lower delay, which should be compensated with a proper design of varactors.

From all these considerations it is clear that an accurate design of the inductors is important to achieve better performance. Some important guidelines which have been taken into account for this purpose are here reported:

- The strip width (spiral width) leverages the series resistance and parasitic capacitance towards substrate. Lower width means lower capacitance but higher resistance. On the other side, however, higher width means higher capacitance but lower resistance only if the skin effect is negligible. Considering that this effect depends on the frequency, increasing the width to reduce the series resistance, hence increasing the quality factor, brings benefits up to a certain point.

- The inductor should not be filled up to the center. In fact, the most inner turns would give a high resistive but a limited inductive contribution which results in an inductance reduction, and hence a quality factor reduction.

- The distance between coils leverages the parasitic capacitances between coils. Higher distance means lower capacitance but also lower coupling

Figure 2.11: Designed transformer

coefficient. On the other side lower distance results in an increasing of both k and capacitances. Considering that this parasitic capacitance goes in parallel with the external one, it should be minimized in order to improve the delay tuning capacity of the cell.

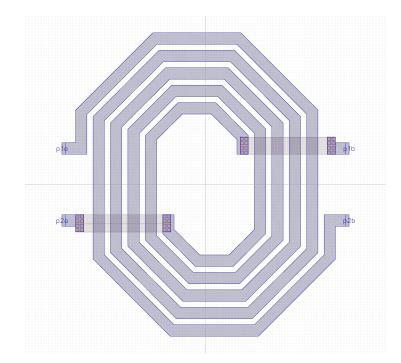

Taking into account the last observations and the design specifications, the transformer has been fully designed on the higher metal layer to maximize the quality factor (lowest sheet resistance). Considering that the technology allows 45° strips it has been designed having an octagonal shape; the oval form has been used to save some horizontal space. The optimal value of the strips width has been found to be  $7.5\mu m$ . Moreover, the optimal distance between strips, which has permitted to keep low parasitic capacitances while maintaining a good coupling coefficient, has found to be  $4\mu m$ . With an area of  $160 \times 200\mu m^2$  and 2.5 turns the resulting transformer layout is reported in figure 2.11. The transformer presents an effective inductance value of 1.7nH and a quality factor of 10 at the frequency of 2GHz. This is achieved through a 0.61 coupling coefficient. For convenience, some of the transformer

| $A[\mu m^2]$     | Coilturns | $L_{eff}[nH]$ | $R_s[\Omega]$ | k    | Q    | $C_p[fF]$ |

|------------------|-----------|---------------|---------------|------|------|-----------|

| $160 \times 200$ | 2.5       | 1.7           | 2.1           | 0.61 | 10.1 | 83        |

Table 2.2: Designed transformer characteristics at 2GHz

characteristics are reported in table 2.2. The capacitance  $C_p$  considers the parasitic capacitance between the inductors and toward substrate. Its effect is to increase the overall cell capacitance C.

A different solution which could come in mind to save some area is to put the coils on different metal layers. In this case, however, a substantially higher sheet resistance of the lower metal layer would lead to an asymmetric transformer which in this case is an unwanted effect.

It is important to underline that the transformer has been accurately simulated with an EM simulator. In fact all the parameters here reported have been extracted from this simulation results, which are reported in figure 2.12. An important thing to observe is that the figures 2.12(a) and (c) do not take into account the coupling. So they represent the inductance and quality factor values of one inductor while the other is an open-circuit. The effective values are increased by the (1 + k) factor.

### 2.3.2 Varactors Design

In the previous section the transformer has been analysed. The other important elements are the variable capacitors, which will be analysed here.

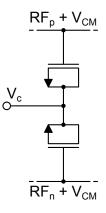

As anticipated, a variable delay element is able to change its delay configuration and this can be done replacing the capacitors with varactors. A varactor is a component which offers a variable capacitance depending on the voltage of the control signal (DC bias). Different possible configurations exist to obtain a varactor in CMOS technology (see [20, 21]). The configuration used in this work is the differential nMOSFET varactor reported in figure 2.13. As it can be seen the signal in this case is applied to the gates terminal while the control signal is applied to the drain/source terminals (the bulk terminal is grounded). The common mode voltage is put to  $V_{DD}$  in order to have a

Figure 2.12: Sonnet simulations results

Figure 2.13: Differential MOS-varactor

Figure 2.14:  $C_{mos}$  as a function of  $\frac{V_c}{V_{DD}}$

positive control signal voltage  $V_c \in \{0, V_{DD}\}$ .

When the control voltage is 0 the gate-source voltage is greater than the threshold voltage of the MOS and the channel is formed; the varactor is in the maximum capacitance configuration

$$C_{MAX} = \frac{1}{2} (C_{gc} + C_{ol(s)} + C_{ol(d)})$$

(2.21)

Note that the 1/2 factor is present because the differential capacitance is considered.

On the other hand, when the control voltage is  $V_{DD}$  the gate-source voltage is lower than the threshold voltage; the varactor is in the minimum capacitance configuration

$$C_{min} = \frac{1}{2} (C_{gb} + C_{ol(s)} + C_{ol(d)})$$

(2.22)

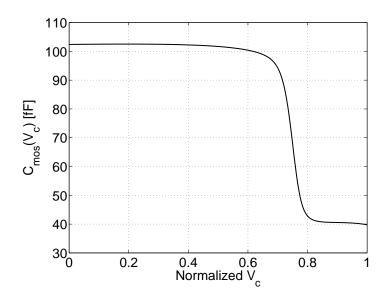

The resulting differential varactor capacitance is reported in figure 2.14, in function of the control signal. The asymmetry (the transition from the maximum to the minimum capacitance value is around  $0.8V_{DD}$  and not  $0.5V_{DD}$ ) comes from the fact that the common mode voltage is set to  $V_{DD}$ . It can be made symmetric lowering the common mode, however this is not necessary

Figure 2.15:  $\alpha$  in function of  $\frac{L_c}{L_{min}}$

in this case. Furthermore, a voltage reference would be needed in this case. From the design point of view, as it has already been seen, the ratio between the maximum and minimum capacitance is also important:

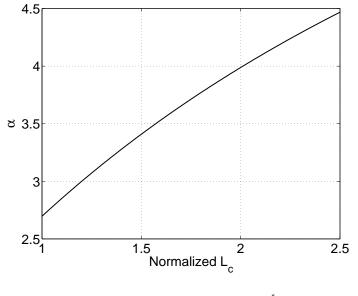

$$\alpha = \frac{C_{MAX}}{C_{min}} \tag{2.23}$$

In fact, the delay difference depends directly on it. It can be shown that this coefficient depends only on the channel length, at least as soon as the channel width W is much higher than the channel length  $L_c$ . This fact is shown in the appendix C. In figure 2.15 the  $\alpha$  coefficient is plotted in function of  $L_c$  and this plot is very useful for the design. Note that this curve does not take into account the parasitic capacitances due to the layout, which are inevitably present. Their presence results in an  $\alpha$  coefficient reduction which depends on the transistors dimensions and should be taken into account during the design.

Another important parameter is the quality factor of the varactor and it

| $W[\mu m]$     | $L_c[\mu m]$  | nf | $C_{min}[fF]$ | $C_{MAX}[fF]$ | α   | $R_g[\Omega]$ | Q(2GHz) |

|----------------|---------------|----|---------------|---------------|-----|---------------|---------|

| $116.3L_{min}$ | $1.22L_{min}$ | 9  | 40            | 104           | 2.6 | 10.2          | 48      |

Table 2.3: Characteristics of the nMOSFETs used to realize the varactor

basically depends on the parasitic gate resistance  $R_g$ . It is defined as:

$$Q = \frac{1}{\omega C R_g} \tag{2.24}$$