# Università degli studi di Padova

MASTER THESIS

# A Machine Learning-based Test Program Quality Tool for Automotive Microcontrollers

Author: Asma KHEDRI Supervisors: Prof. Gian Antonio Susto Ing. Angelo De Poli Dr.Ing. Giambattista Carnevale

A thesis submitted in fulfillment of the requirements for the degree of Master

in ICT for Internet and Multimedia

Infineon Technologies Department of Information Engineering

November 26, 2019

"In god we trust, all others bring data"

— W. Edwards Deming

### UNIVERSITÀ DEGLI STUDI DI PADOVA

# Abstract

#### Department of Information Engineering

### A Machine Learning-based Test Program Quality Tool for Automotive Microcontrollers

by Asma KHEDRI

In the semiconductor industry where large amounts of data are generated, data driven quality control technologies are gaining increasing importance. In Infineon, production testing is an important aspect in the automotive microcontroller manufacturing, during which thousands of data are stored, the purpose of this thesis is to make use of these data to build a quality gate tool based on machine learning techniques in order to improve testing quality and facilitate better usage of test information for yield improving. In fact, tests in the production flow involves a large number of sequential steps, mainly two important phases, the front-end testing, i.e before packaging, and the back end-testing, after packaging. In this thesis, we study the possibility of predicting the final state of the packaged chips based on the tests done before packaging.

**Keywords**: Automotive, Semiconductors, Machine-Learning (ML), Production Test, Yield, etc.

# Acknowledgements

I would like to take this opportunity to express my heartfelt gratitude to a number of people whose I was blessed to know and work with.

First, to Professor Gian Antonio Susto, my thesis advisor, the one I turn to whenever I run into a trouble spot, you were an incredible mentor to me, your motivational words and insightful suggestions were the reasons behind the success of this thesis.

To Giambattista, Pierre and Andrea, the best team someone could ever work with, thank you for the continuous support, patience, motivation, and immense knowledge. To Pierre, thank you for being optimistic when I first thought my results are not good enough, you always made it easier for me and taught me not to give up. To Andrea, thank you for your enthusiasm for Machine Learning, your brilliance inspired me. To Giambattista, thank you for trusting my skills, for being there every time I needed help, you boosted my confidence and encouraged me to move forward. I have learnt a lot from you all during these months, and for that I am deeply grateful.

To Angelo DePoli, thank you for welcoming me in the MC team in Padua, my experience in Infineon Technologies was a milestone in my career, thank you for offering me the chance to be part of such an interesting thesis work.

To Ms. Roberta Pellizzaro, without you this graduation wouldn't be happening today, thank you.

To my cousin Nadia, words are not enough to thank you, you supported me in every step since I set a foot in Padua.

To my family, far from the eyes but close to the heart, thank you for being patient and strong, for supporting my choices, for being there for me in all my achievements, you taught me to be the person I am today, thank you.

To Amen, the one I always annoyed when I felt anxious and stressed, the one who was there through my ups and downs, thank you.

To my dear friend Mouna, the reason I applied for the University of Padova in the first place, thank you for being my partner in this rest journey.

To anyone who ever offered me a smile and a word of motivation while I was writing this thesis, it meant a lot to me, thank you.

Asma Khedri

# Contents

| Abstract |      |                                            | iii |  |

|----------|------|--------------------------------------------|-----|--|

| Ac       | knov | vledgements                                | v   |  |

| 1        | Intr | oduction                                   | 1   |  |

|          | 1.1  | Introduction                               | 1   |  |

|          | 1.2  | Infineon Technologies                      | 1   |  |

|          |      | 1.2.1 Automotive MC team in Padua          | 3   |  |

|          | 1.3  | Motivation and Related Work                | 4   |  |

|          | 1.4  | Problem Statement                          | 6   |  |

|          | 1.5  | Thesis Overview                            | 7   |  |

| 2        | Proc | luction Test Flows for Non-Volatile-Memory | 9   |  |

|          | 2.1  | Introduction                               | 9   |  |

|          | 2.2  | Device Under Test (DUT)                    | 9   |  |

|          |      | 2.2.1 Flash Memory                         | 10  |  |

|          | 2.3  | Non-Volatile-Memory Production Test Flow   | 13  |  |

|          |      | 2.3.1 Front End Insertions                 | 13  |  |

|          |      | 2.3.2 Assembly and Packaging               | 13  |  |

|          |      | 2.3.3 Back End                             | 14  |  |

|          |      | 2.3.4 Test Binning                         | 14  |  |

|          | 2.4  | Test Results                               | 15  |  |

|          | 2.5  | Data Source For ML                         | 16  |  |

| 3        | Met  | hodological background                     | 19  |  |

|          | 3.1  | Introduction                               | 19  |  |

|          | 3.2  | Feature Engineering                        | 19  |  |

|          |      | 3.2.1 Density Estimation                   | 19  |  |

|          |      | 3.2.2 Kolmogorov–Smirnov Test              | 20  |  |

|          |      | 3.2.3 Correlation Analysis                 | 21  |  |

|          |      | 3.2.4 Data Normalization                   | 22  |  |

|          | 3.3  | Dimensionality Reduction                   | 24  |  |

|          | 3.4  | Machine Learning Techniques                | 25  |  |

|          |      | 3.4.1 Imbalanced Classification            | 25  |  |

|          |      | 3.4.2 ML Classifiers                       | 28  |  |

|          | 3.5  | Performance Metrics                        | 33  |  |

|          | 3.6  | Data Split                                 | 38  |  |

| 4  | Data                      | a preparation                                               | 41        |  |

|----|---------------------------|-------------------------------------------------------------|-----------|--|

|    | 4.1                       | Introduction                                                | 41        |  |

|    | 4.2                       | Data Extraction                                             | 41        |  |

|    |                           | 4.2.1 Esquare Tool                                          | 41        |  |

|    |                           | Job Definition                                              | 41        |  |

|    |                           | 4.2.2 Extraction Specifications                             | 42        |  |

|    |                           | 4.2.3 EFF File Structure                                    | 42        |  |

|    | 4.3                       | Data Cleaning and Pre-processing                            | 45        |  |

|    |                           | 4.3.1 Data Description                                      | 46        |  |

|    |                           | Data Correlation Analysis                                   | 47        |  |

|    |                           | Density Distribution                                        | 48        |  |

|    |                           | 4.3.2 Filtering decisions                                   | 50        |  |

|    | 4.4                       | Final dataset                                               | 51        |  |

| _  | <b>a</b> 1                |                                                             |           |  |

| 5  |                           | Development and Results                                     | 53        |  |

|    | 5.1                       | Introduction                                                | 53        |  |

|    | 5.2                       | Model Selection                                             | 53        |  |

|    | 5.3                       | Balanced Random Forest Results                              | 56        |  |

|    |                           | 5.3.1 Performance metrics                                   | 56        |  |

|    | - 1                       | 5.3.2 Decision Threshold Adjustment                         | 57        |  |

|    | 5.4                       | Feature Selection                                           | 59        |  |

|    | 5.5                       | Quality gate tool                                           | 61        |  |

|    | 5.6                       | Distance of Chip from The Center of Wafer                   | 63        |  |

| 6  | Con                       | clusion and Future Work                                     | 67        |  |

|    | 6.1                       | Summary and Contributions                                   | 67        |  |

|    | 6.2                       | Future Work                                                 | 68        |  |

| •  | <b>A</b>                  | <b>1</b>                                                    | (0)       |  |

| Α  |                           | pendix<br>CDDJ                                              | <b>69</b> |  |

|    | A.1                       | SBIN analysis                                               | 69<br>70  |  |

|    | A.2                       | Data Statistics                                             | 70        |  |

|    | A.3                       | Performance metrics of SVM with under-sampled balanced data |           |  |

|    | A.4                       | List of Features                                            | 72        |  |

|    | A.5 Snapshot of Real Data |                                                             |           |  |

| Bi | bliog                     | raphy                                                       | 75        |  |

# **List of Figures**

| 1.1<br>1.2<br>1.3 | Infineon's logo                                                                                                                                                                                 | 1<br>7<br>8 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2.1               | AURIX TC39x Feature Table [39]                                                                                                                                                                  | 10          |

| 2.2<br>2.3        | TestFlow                                                                                                                                                                                        | 14<br>15    |

| 3.1               | Illustration of the two-sample Kolmogorov–Smirnov statistic.<br>Red and blue lines each correspond to an empirical distribu-<br>tion function, and the black arrow is the two-sample KS statis- |             |

| 2.0               | tic [2]                                                                                                                                                                                         | 21          |

| 3.2<br>3.3        | Feature selection Vs feature reduction                                                                                                                                                          | 25<br>26    |

| 3.4               | Machine learning workflow                                                                                                                                                                       | 20<br>29    |

| 3.5               | Decision Tree Example                                                                                                                                                                           | 31          |

| 3.6               | Random Forest overview                                                                                                                                                                          | 31          |

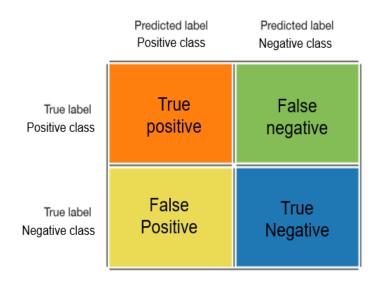

| 3.7               | Confusion matrix and terminology for a binary classification                                                                                                                                    | 01          |

|                   | problem                                                                                                                                                                                         | 34          |

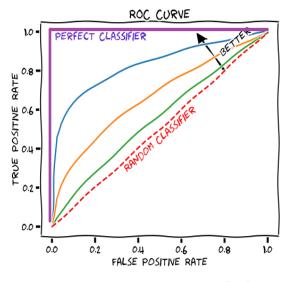

| 3.8               | ROC curves [23]                                                                                                                                                                                 | 36          |

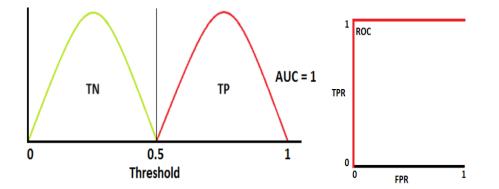

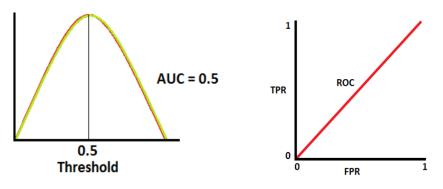

| 3.9               | distribution of predicted probabilities to fail in ideal case [25]                                                                                                                              | 36          |

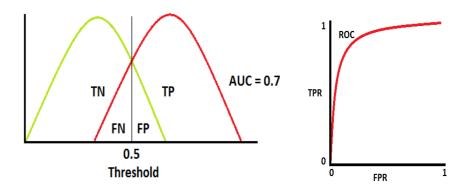

| 3.10              | distribution of predicted probabilities to fail in practical case [25]                                                                                                                          | 37          |

| 3.11              | distribution of predicted probabilities to fail in worst case [25]                                                                                                                              | 37          |

| 3.12              | overfitting explained in case of oversampling [11]                                                                                                                                              | 39          |

| 4.1               | EFF file structure                                                                                                                                                                              | 44          |

| 4.2               | EFF header                                                                                                                                                                                      | 45          |

| 4.3               | Dataframe with values of FE tests for each extracted chip. In                                                                                                                                   | 10          |

| 1.0               | columns we have chip position, FE tests and label.                                                                                                                                              | 45          |

| 4.4               | Possible types of test results                                                                                                                                                                  | 47          |

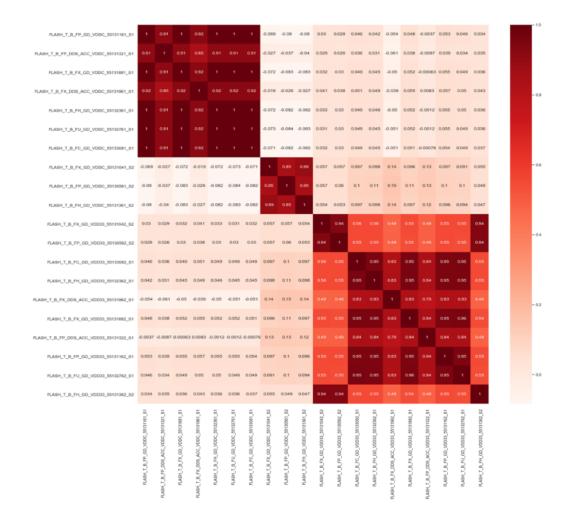

| 4.5               | correlation matrix of subset of features                                                                                                                                                        | 49          |

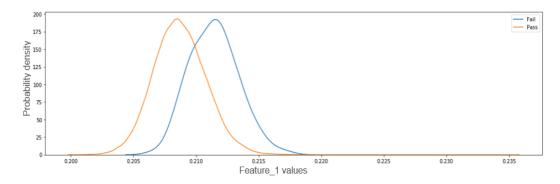

| 4.6               | Density distribution of feature1 values                                                                                                                                                         | 50          |

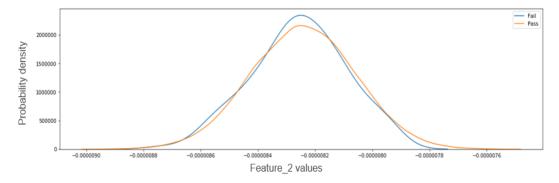

| 4.7               | Density distribution of feature2 values                                                                                                                                                         | 50          |

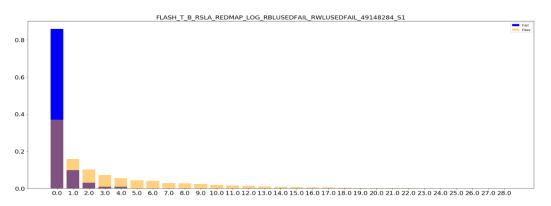

| 4.8               | probability distribution of discrete values feature                                                                                                                                             | 50          |

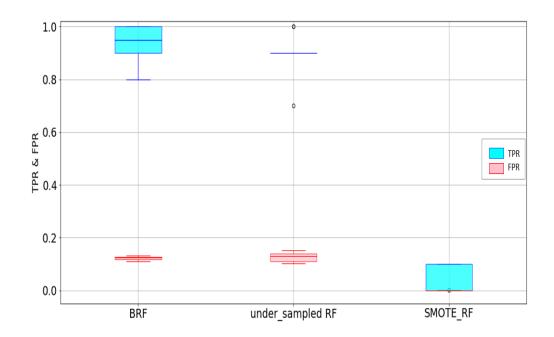

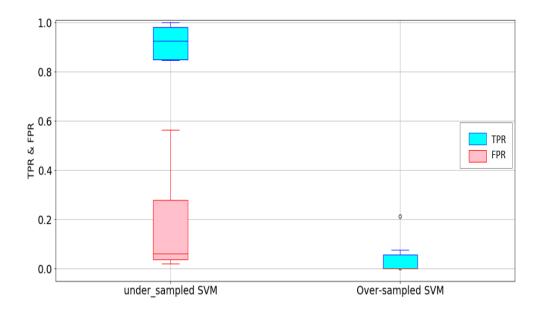

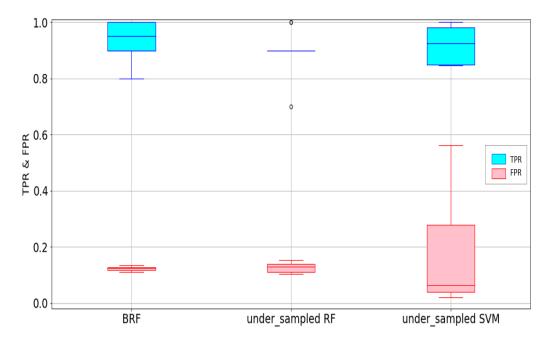

| 5.1<br>5.2        | TPR and FPR of RF models evaluated over cross-validation<br>TPR and FPR of SVM models evaluated over cross-validation                                                                           | 54<br>55    |

|                   |                                                                                                                                                                                                 |             |

| 5.3  | TPR and FPR of ML models evaluated over cross-validation .         | 56 |

|------|--------------------------------------------------------------------|----|

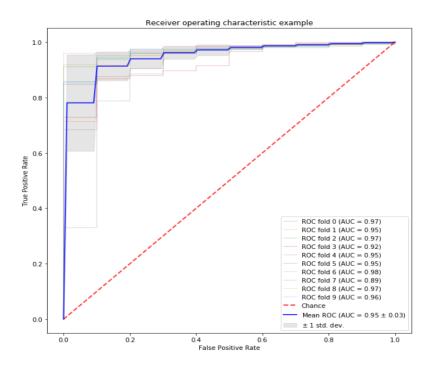

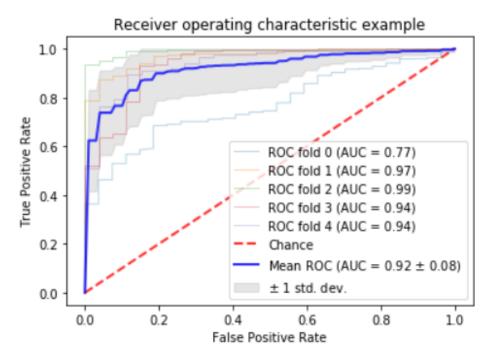

| 5.4  | BRF with cross-validated ROC curve                                 | 57 |

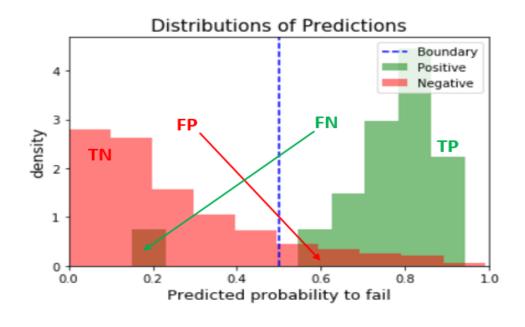

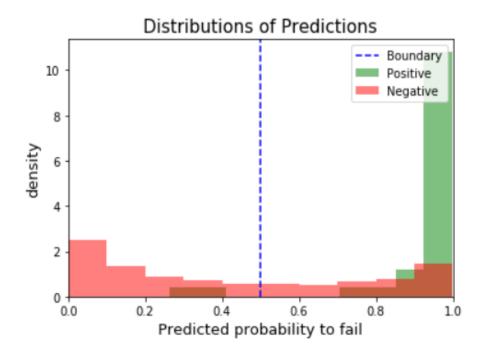

| 5.5  | distribution of predicted probabilities to fail with BRF           | 58 |

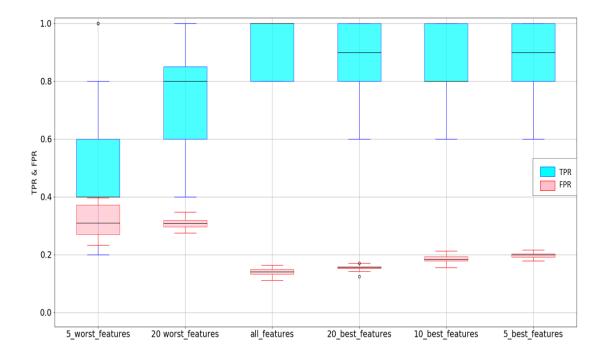

| 5.6  | TPR & FPR with different number of features by BRF over 10-        |    |

|      | fold cross validation                                              | 61 |

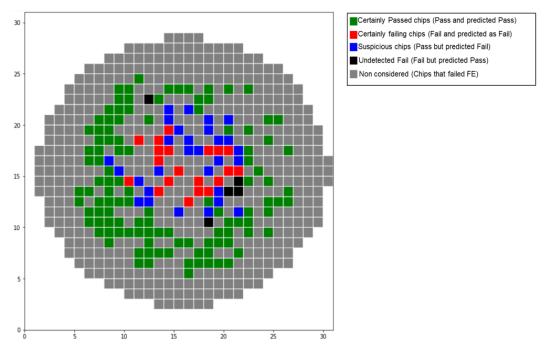

| 5.7  | Quality gate tool on a certain wafer                               | 63 |

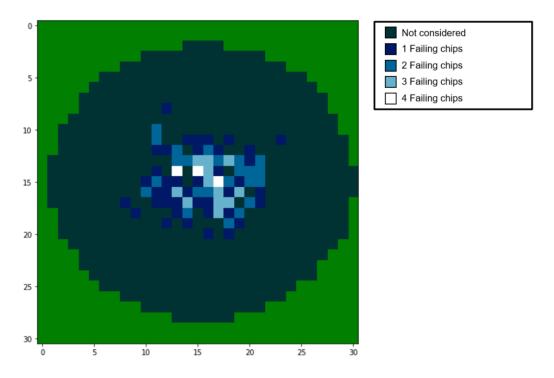

| 5.8  | Number of total failing chips in a specific XY position among      |    |

|      | 134 failing chips                                                  | 64 |

| 5.9  | Density distribution of distances of FE passing chips from cen-    |    |

|      | ter                                                                | 64 |

| 5.10 | TPR & FPR with BRF with and without using the feature <i>Dis</i> - |    |

|      | <i>tance</i> over 10-fold cross-validation                         | 65 |

| A.1  | Density distribution of two features with different SBINs          | 69 |

| A.2  | TPR of BRF when detecting different SBINS from Pass                | 70 |

| A.3  | Table of different statistics for a subset of features             | 70 |

| A.4  | ROC curves over 5-fold cross validation with SVM using under-      |    |

|      | sampling technique                                                 | 71 |

| A.5  | Distribution of predicted probabilities to fail with SVM           | 72 |

| A.6  | Snapshot of the Dataset used in the thesis                         | 74 |

|      |                                                                    |    |

# List of Tables

| 2.1 | Example of Result tables of Program, Erase, and verify com-<br>mands | 16 |

|-----|----------------------------------------------------------------------|----|

| 4.1 | Extraction criteria                                                  | 43 |

| 5.1 | Confusion matrix using BRF with threshold 0.5                        | 57 |

| 5.2 | Confusion matrix using BRF with threshold 0.6                        | 59 |

| 5.3 | Confusion matrix using BRF with threshold 0.65                       | 59 |

| 5.4 | Confusion matrix using BRF with threshold 0.7                        | 59 |

| 5.5 | Confusion matrix using BRF with threshold 0.8                        | 59 |

| A.1 | Confusion matrix using SVM with threshold 0.5                        | 71 |

# **List of Abbreviations**

- MC Micro Controller

- ML Machine Learning

- FE Front End

- BE Back End

- **NVM** Non Volatile Memory

- PdM Predictive Maintenance

- VM Virtual Metrology

- FDC Fault Detection

- NN Neural Network

- SVM Support Vector Machine

- IC Integrated Circuit

- ATE Automatic Test Equipment

- **DUT** Device Under Test

- HBIN Hard Bin

- SBIN Soft Bin

- TN Test Number

- KDE Kernel Density Estimation

- KS Kolmogorov Smirnov

- PCA Principal Component Analysis

- BRF Balanced Random Forest

- **TP True Positive**

- **FP** False Positive

- TN True Negative

- FN False Negative

- **TPR** True Positive Rate

- **FPR** False Positive Rate

- **ROC** Receiver Operating Characteristic

- CV Cross Validation

- **QG Quality Gate**

For those who answer the call in the middle of the day or night. For those who answer the call from near and from far. For those who answer the call for help with no expectation of personal gain. This work is dedicated to you all ...

# **Chapter 1**

# Introduction

## 1.1 Introduction

This thesis was entirely realized during an internship at the Padua Development Center of the company Infineon Technologies, working as a member of the Microcontroller team. The aim of this chapter is to introduce the framework this thesis was conceived in: the company and its philosophy as well as the team itself. It then explains the motivation behind starting this thesis, as well as a review of some related work. Finally, it discusses the overall goal and structure of the thesis.

## 1.2 Infineon Technologies

Infineon Technologies is a leading innovator in the international semiconductor industry founded in April 1999. It is head quartered in Munich, Germany but, it has 17 Production sites and 35 Research and Development ones scattered all over Europe, the Americas and the Pacific Regions, and more than 40k employees worldwide.

Today the company is working on 4 business areas. Here follows the official presentation given by the company for these 4 areas [38]:

• Automotive (ATV): In the ATV segment, Infineon develops products and solutions for conventional drivetrains while also actively shaping

FIGURE 1.1: Infineon's logo

the keystone trends that define the industry. Demand for our power semiconductors is on an upward path, fueled by the rising number of electronic applications in cars -a trend further accentuated by the growing popularity of electromobility. We are the undisputed market leader in silicon-based IGBTs and IGBTmodules. Our expertise in silicon carbide is also increasingly relevant for automotive power semiconductors. We are paving the way for self-driving cars with our radar sensors and microcontrollers. Positioned as number two in the radar sensor market, we are already noting strong momentum from the proliferation of driver assistance systems. In the long term, radar systems will be fused with other sensor technologies. We are laying the ground work for this by developing products such as LIDAR solutions. With our AURIX<sup>TM</sup> family, we are also benefiting from the trend towards increased automation. Our products here control electronic systems such as steering and braking, also acting as host controllers to provide functional safety and data security for central computing platforms.

- Industrial Power Control (IPC): The IPC segment specializes in the efficient conversion of electric energy along the entire supply chain from generation and transmission right through to consumption. Applications here include wind turbines, high-voltage DC transmission systems, energy storage systems, charging infrastructures for electric vehicles, and household appliances. Infineon is the world leader in IGBT-based discrete power semiconductors and power semiconductor modules. To further strengthen this core IPC business, we are aiming for technology leadership in silicon carbide. Complementary product areas are also becoming increasingly important for us, in particular Intelligent Power Modules (IPMs) integrating controllers, drivers and switches to enable digital control capabilities.

- Power Management and Multimarket (PMM): Our PMM segment focuses on power semiconductors for energy management as well as components for wireless infrastructures and mobile devices. PMM also specializes inultrareliable components for applications in industries such as aerospace. Infineon is the clear leader in the global MOSFET market. Our *CoolMOS<sup>TM</sup>* and *OptiMOS<sup>TM</sup>* families deliver excellent levels of

energy efficiency. We also offer leading-edge solutions based on gallium nitride. In parallel to this product group, we are continuing to expand our portfolio of complementary drivers and controllers. Batteryoperated devices are one of the fastest-growing applications for power semiconductors. In the high-frequency and sensor space, we have established a strong technology footprint with MEMS microphones (silicon in particular),time-of-flight sensors for 3D cameras and radar applications. We have already established very successful positions in the respective markets. At the same time, we can apply our expertise in these areas to more and more use cases that are set to gain momentum over the coming years. Key examples here include human-machine interaction (HMI) and facial recognition.

Digital and Security Solutioms (DSS): The Digital Security Solutions (DSS) segment has over thirty years' experience delivering some of the world's most challenging and large-scale digital security projects. Our success here is built on our wealth of expertise in conventional smart card applications. We are transferring our core skills in payment cards and government documents to the fast-growing field of embedded security applications. As digitalization shapes more and more areas of everyday life, security is becoming a key success factor for applications across industries as diverse as computing, automotive, Industry 4.0 and smart homes. Parallel to its role as an independent business segment, DSS acts as a competence center for our other three segments, supporting their efforts to hardwire security functionality into the irrespective system solutions.

### 1.2.1 Automotive MC team in Padua

Located in the Development Center of Padova, the Microcontroller (MC) team is part of the product and testing engineering organization of ATV, focusing on embedded Flash of automotive and industrial microcontrollers. The team has different responsibilities:

- To contribute to Non-Volatile Memory (NVM) testing concept, analyzability and manufacturability, validation and analysis planning.

- To provide NVM analysis tools to improve automation.

- To provide embedded firmware and test patterns for productive testing on NVM.

- To perform NVM test-chip analysis for design and technology learning.

- To execute NVM validation and characterization.

- To perform enhanced In-System tests on application conditions.

- To provide Design Validation Reports for Customer presentations.

- To support NVM qualification (product and technology).

- To review test program contents of test package releases (production, qualification, characterization).

To better respond to these tasks, Padua MC team is divided into two subteams:

- **Test Engineering**: this group develops embedded software for analysis and testing. In particular this group is responsible for development of the Firmware and of test program used for performing Flash memory tests.

- **Product Engineering**: this group characterizes Embedded Flash and it validates robustness of non volatile memories. Its purpose is ensuring the quality of memory by validating the requirements of customers, also considering statistical aspect, extending validation to many samples. It does the analysis, it searches the causes that generate the problem to solve, and therefore it offers solutions for the designers and technology experts. The characterization activity tries to push parameters, like temperature, power and system frequencies, to the limits.

This thesis was entirely realized during an internship with the MC team, working as member of the Test engineering team.

## **1.3 Motivation and Related Work**

Semiconductor manufacturing is a complex and lengthy process, during which, voluminous data are generated and collected. This data has received considerable attention from researchers to transfer this complex engineering data into valuable information and knowledge for process improvement and yield enhancement [8]. With the rapid progress in artificial intelligence, machine learning and statistical techniques are widely applied in predicting the outcomes of manufacturing process and measurement tests. In literature, the

large amounts of data generated by electrical tests, measurement of physical parameters, and collection of equipment and process parameters were used for different purposes such as:

- Virtual Metrology (VM) systems

- Predictive Maintenance (PdM) systems

- Fault Detection (FDC) systems

### Virtual Metrology

A VM system consists of a mathematical model that estimates a process results based on previous metrology measurements, instead of measuring it practically. In other words, the purpose is to be able to predict these "costly to measure" quantities from readily available fabrication parameters or sensor data that can be used without further costs [37]. There are many advantages to virtual metrology including [3]:

- **Reducing wafer scraps:** process inspection can be performed through VM for every wafer to sustain yield performance

- **Tighter process control:** VM provides a basis to overcome the metrology delay problem for run-to-run control

- **Increasing throughput:** wafer handling from process tool to metrology tool can be reduced and, thus, production cycle time can be shorted.

VM has been approached by using different techniques, both Linear, such as Ordinary Least Square (OLS) and Partial Least Squares (PLS) [19], [20], and Non-Linear, such as Artificial Neural Networks (NNs) [46].

### **Predictive Maintenance**

PdM is a new approach to maintenance management where actions are performed only when necessary, given the fact that PdM systems can statistically assess the health status of a piece of equipment allowing advance detection of pending failures, enabling timely pre-failure interventions, thanks generally to prediction tools based on historical data and statistical inference methods [36].

Different machine learning techniques were applied in literature for PdM systems, such as NNs in [45], the Kalman predictor in [34] and Support Vector Machines in [1] [36].

### **Fault Detection**

FDC system does not predict the future behavior of the tool/process, but aims to detects and classifies different faults in it. FDC systems identify the root cause of the abnormal behavior. This is of particular interest in the everyday work of a semiconductor plant: the root causes of faults in a complex process may be dozens, sometimes hundreds, and even expert process engineers have difficulty understanding the pathology and, therefore, how to properly cope with the faulty process/tool [37]. The FDC systems employ classification techniques, for example K-NearestNeighbour (kNN) in [16], Principal Component-based kNN in [17] and Support Vector Machines (SVMs) in [28]

In following, we describe how ML techniques are used in this thesis, the goal we want to reach and the challenges faced.

### **1.4 Problem Statement**

The semiconductor manufacturing process, from the first stage up to final product shipping, is interleaved with the testing of the product itself. There are mainly two phases:

- The front-end process (FE): in this step the chips (IC) are patterned and projected on the silicon wafer. In this stage, chips are referred to as silicon chips or dies, that will be later inside a final package/chip. However, before the wafer is sent to chip preparation, it goes through FE testing, where every single die on the wafer is tested, and is accessed through specialized prober machines (Automatic Test Equipment (ATE)).

- The back-end process (BE): is mainly cutting and packaging of the wafer to single protected chips. Once packaged the chip goes through other tests before final shipping, which we refer to as **BE testing**, in this stage the chip is accessed trough its standard I/O lines (pads or pins), the same ones which will be used during its working life.

Throughout the entire process, a microcontroller goes from being a circuit integrated on a wafer, i.e. die, to a packaged chip, as seen in Figure 1.2. Each chip has specific (X,Y) coordinates on a wafer, and every wafer has a unique ID. Usually wafers are organized in groups of 25 or 50, called lots, and each

FIGURE 1.2: From wafer to chip: The process start with a wafer with hundreds of ICs, that goes through FE testing, the dies who pass the FE are packaged and sent to BE testing, the passing packaged chips are ready to be shipped

lot has a unique ID as well.

In the automotive MC team in Padua, test engineers are responsible of developing the Test Program that Infineon's chips have to go through. Thus, the quality of the testing algorithms is crucial in order to detect all possible faulty dies. The aim of this thesis is to build a quality gate tool to our Test Program, using machine learning techniques as explained in the following section.

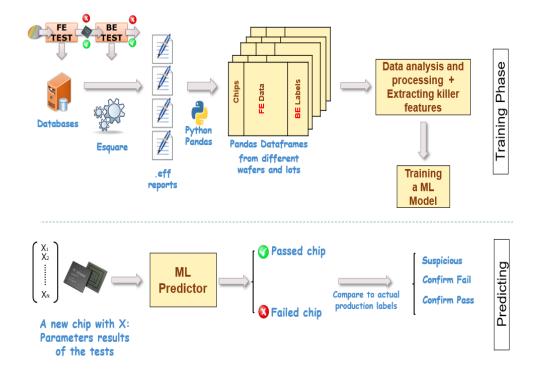

## 1.5 Thesis Overview

As seen aforementioned, the chip goes through FE then BE testing phases during which all tests results are stored. Dies that passed the FE testing are sent to assembly and BE testing. However, some faulty dies may be undetected during the FE tests, yet they will ultimately fail in BE tests. The first task of our tool is to take into consideration all dies that passed the FE, the results of each test, and predict whether these dies will pass or fail the BE test phase. This is done by first extracting chips who passed FE, their FE tests results, and their corresponding labels (i.e. Fail or Pass) after BE testing, data extraction is described in Section 4.2. In the context of machine learning, the test results are the features, and the BE labels present the target. The second step is to study whom of these features are the ones that are more contributing in the failure of the chip, also known in this thesis as killer parameters. We refer to this step as data processing which is detailed in both Section 3.2 and Section 4.3. Once the dataset is ready, it is used to train a ML model. The model will then, given the FE tests results of new chips, predict the final state of the chip after the BE. It is important to note that in this step, the dataset is

FIGURE 1.3: Qaulity Gate tool big picture

imbalanced, indeed the number of BE failing chips is usually very low compared to the passing ones, which highlight the need of carefully training and choosing the model for correct classification, details regarding this challenge is mentioned in Section 3.4.1. The second task of the Quality Gate tool, is to compare these predictions, to the real labels given to these chips after going through BE. In case of an accurate model, we expect the labels assigned after BE testing to be similar to the ones predicted, thus we confirm the reliability of our test program in detecting failures. The QG tool will either confirm the results of the BE testing or raise a warning in case of suspicious behavior, that is a chip is predicted to fail when it actually passed and vice-versa. Details about the selected ML model and the output of the quality gate tool are presented in Chapter 5.

Fig 1.3 is a simplified representation of the big picture of the entire thesis, starting from data extraction to final comparison.

# Chapter 2

# Production Test Flows for Non-Volatile-Memory

## 2.1 Introduction

Infineon Technologies AG is a leading player and pioneer in automotive electronics. Thanks to its testing quality, Infineon's microcontrollers are wellsuited for safety-critical applications to support clean, autonomous and connected cars. This chapter is dedicated to explain the entire testing process within Infineon, starting by an overview on the tested devices, then a description of the testflow, and finally the test results and binning. In the end of this chapter, we describe the thesis outlook in the context of the testing process explained.

## 2.2 Device Under Test (DUT)

The production data analyzed during this thesis are related to the *AURIX*<sup>TM</sup> 2G microcontroller family produced by Infineon, more specifically the product line TC39x. In fact, *AURIX*<sup>TM</sup>, standing for Automotive Realtime Integrated NeXt Generation Architecture, is Infineon's current family of microcontrollers that serve the precise needs of the automotive industry in terms of performance and safety. With the second generation being a further enormous increase in performance, *AURIX*<sup>TM</sup> TC39x were specifically designed for electric and/or autonomous vehicles. They are equipped with [39] :

- up to 16 Mbytes of embedded Flash memory

- more than 6 Mbytes of RAM

- up to six 32-bit *TriCore*<sup>TM</sup> processor cores.

AURIX<sup>TM</sup> TC39x characteristics are summed up in Figure 2.1. Each of these modules in the microcontroller is tested in order to deliver reliable chips. However, as mentioned in Section 1.2.1 ,Flash memory testing is MC Padua team's core business. In fact, embedded Flash (eFlash) memories represent a large percentage of the area of modern automotive microcontrollers, thus significantly contribute to the overall product quality and yield. In this context, our main focus in this thesis will be regarding the tests done on Flash, and in predicting failure caused by flash related tests.

| Feature Set | 9x Series<br>eXtension<br>(16MB)     |                    |

|-------------|--------------------------------------|--------------------|

| TriCore     | # Cores / Checker                    | 6/4                |

| 1.6         | Frequency                            | 300MHz             |

| Accelerator | Signal processing Unit (SPU)         | 2xSPU              |

| Flash       | Program Flash                        | 16MB               |

| FIdSN       | Data Flash (physical/logical)        | 1024kB             |

| SRAM        | Total (DMI , PMI, LMU, AMU)          | 6912KB             |

| DMA         | Channels                             | 128                |

| ADC         | Modules Primary / Sec / FC / DS      | 8/4/8/14           |

| ADC         | Channels Primary / Sec / FC /DS      | 64/64/8/14         |

|             | GTM TIM / (A)TOM / MCS               | 64 / 192 / 10      |

| Timer       | CCU / GPT modules / bit<br>streaming | 2/1/1              |

|             | FlexRay (#/ch.)                      | 2 /4               |

|             | CAN-FD / TT                          | 12/1               |

|             | QSPI / ASCLIN / I2C                  | 6 /12/2            |

|             | SENT / PSI5 / PSI5S                  | 25/4/1             |

| Interfaces  | HSSL / MSC / EBU                     | 2/4/1              |

|             | Ethernet 100Mbps/1Gbps               | 1/1                |

|             | eMMC/SDIO                            | 1/1                |

|             | Radar /ext. ADC IF (RIF)             | 12x400Mbps<br>LVDS |

|             | Camera IF (CIF)                      | -                  |

| ecurity HSM |                                      | HSM+ECC256         |

| Safety      | SIL Level                            | ASIL D             |

| Power       | EVR                                  | Yes (3.3V/5V)      |

| rowei       | Standby Control Unit                 | yes                |

FIGURE 2.1: AURIX TC39x Feature Table [39]

### 2.2.1 Flash Memory

The embedded flash memory, is a non volatile memory, that comprises the following components:

- Flash Standard Interface (FSI) : a programmable finite state machine that handles sequences to perform erase, program and verify (see following section) operations on all Flash memories.

- **ProgramFlash(PFLASH**): Divided into one or more banks <sup>1</sup> each connected to a CPU. It is used by the application to store program code and data constants. In addition to the Flash arrays <sup>2</sup>, it also contains an analog block with pumps and regulators.

- Data Flash (DFLASH): The Data Flash Module is divided in banks and used to emulate an EEPROM (Electrically Erasable Programmable Read-Only Memory <sup>3</sup>) to store data for user and security applications. DFLASH read accesses are relatively slow compared to PFLASH accesses. Data Flash Module also contains regions to store configuration data in User Configuration Blocks (UCBs), and Configuration Sector (CFS). This last region is not accessible by user and stores system set-up data needed for the correct working configuration of the chip. In addition to the Flash Arrays, there is an analog block containing pumps and regulators.

An Aurix<sup>TM</sup> TC39x contains a total of 16 MB of Program Flash memory. Each Program Flash memory consists of 5 memory banks with a size of 3 MB and 1 with the size of 1 MB. Each bank can be subdivided into physical sectors of 1 MB, so every Program Flash bank consists of 3 physical sectors, with the exception of the 1 MB size one, that has only one physical sector [24].

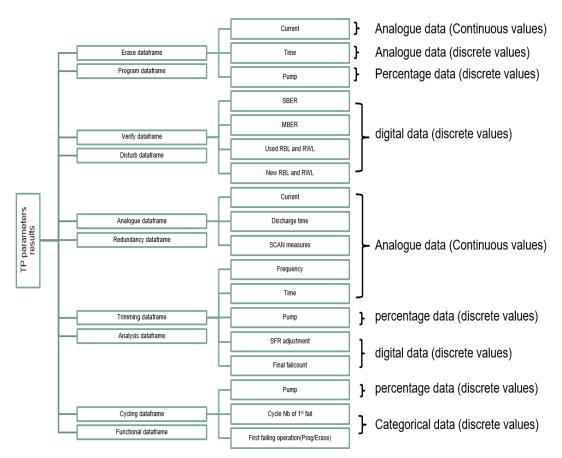

In this thesis, all tests done on all Flash components, banks and sectors are considered. In fact, for flash testing, an approach, based on a software solution for embedded memories testing called Flash Software Implemented Self-Test (FSIST), is followed. This technique consists of using the computing resources of the Device Under Test (DUT) to test its eFlash memory itself. The FSISTs are portions of software executed by the DUT's CPU, and could perform the following tests [10]

• Erase Command: performs erase operation on the flash array and measures the erase time, pump voltage used, number of erased sectors, etc.

<sup>&</sup>lt;sup>1</sup>a Flash module (e.g PFLASH) is divided in separate banks. The banks support concurrent operations with some limitations due to common logic

<sup>&</sup>lt;sup>2</sup>Flash array is the physical memory used to store information.

<sup>&</sup>lt;sup>3</sup>EEPROM is a type of non-volatile memory, used in electronic devices to store small amounts of data that must be maintained when power is off.

According to the module design specification, it is possible to erase different cluster of cells.

- **Program Command:** performs a program operation with some particular patterns, and measure program time and pump load used. Possible patterns could be solid patterns (Program all zeros, Program all ones) and checkerboard patterns (alternated zeros and ones).

- Verify Command: the verify test reads all the Flash memory and compares the read content (*actual content*) with the one previously injected during the programming/erasing step (*expected content*). it is possible to verify all kind of patterns, verify all zeros, verify all ones, verify checkerboard patterns.

- Disturb and Stress Command: executes disturb and stress on the flash array to stimulate the appearance of faults. Different patterns of disturb and stress are performed, such as Gate Disturb, Drain disturb, side wall stress, Burn-In all, etc.

- Redundancy Command: This command handle the repair of the flash by computing how to allocate the redundancy resources in order to repair the failed Flash cells detected during the verify.

- Analogue Command: performs analogue measurements such as current, voltage and frequencies, in order to perform analogue tuning.

- Trimming Command: is used to trigger tuning tests on eFlash. every time an erase and verify are performed, trimming is performed to adjust the parameters to get the minimum bit erros. Trimming is done on the following parameters: Voltages done chip to chip (aka CTCT Chip To Chip Trimming), and Flash Oscillator trimming.

- **Cycling Command:** cycling is a combination of erase and program operations done to disturb the flash.

- Functional Command: contains several test objects that cannot be linked to any other FSIST command but belong to functional testing.

Each of these commands have a set of failing criteria, i.e. specifications, if a test does not meet these specifications it fails and the chip is binned. Indeed, during FE testing some chips are failing during the aforementioned flash tests if specifications aren't met. The following section describe in details the entire test flow, and the binning of chips.

### 2.3 Non-Volatile-Memory Production Test Flow

### 2.3.1 Front End Insertions

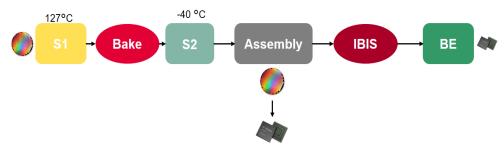

The FE test stages can be divided into sub-phases which differ in the testing temperature (from  $-40^{\circ}$  to  $125^{\circ}$  Celsius), and usually referred to respectively as S1 and S2. Each test phase is composed of a multiple single tests which are identified by a unique number called test number (TN). For each insertion, we define a test suite, which is a sequence of test routines that are usually composed of the following steps: Stress, Disturb, Program/Erase, Verify, Repair, Flash scan, Analogue measurement and trimming. Note that, this sequence is not strictly followed, it may happen that after a single Erase, several kinds of verify are executed and not all of them are followed by a repair. However, it is possible to differentiate these single tests by their unique TN.

As mentioned before in Section 2.2.1, when describing FSIST commands, each of these tests produce a set of measurements, that according to certain specifications, it is decided whether a die should pass or fail that test. For example, given an erase command, a test can be declared **FAIL** based on the following criteria: Erase time too long or Pump load limits exceeded. For a verify command, a test will fail if the number of SBER detected exceed SBER\_LIMIT, i.e. accepted limit on Single Bit Error found, on overall selected banks.

Now for each test, if a die failed a test not meeting the criteria, it is filtered out and it does not undergo the rest of the test-flow. By the end of the FE test, bad dies are separated from good dies when cutting the wafer, and only dies that passed all the S1 and S2 insertions remain and will be packaged.

### 2.3.2 Assembly and Packaging

As a first step, the wafer is cut into singular dies. These dies are actually functional but are impossible to use without an external protective package, indeed any scratch would impact the reliability of the chip, and any shock would cause its failure. Therefore, as a second step, the individual chips are placed in a package and terminals are attached. The result is a finished semiconductor device, that should go through several other tests, i.e. BE testing, in order to be shipped to the customer in the highest quality.

### 2.3.3 Back End

Similar to FE testing, Back End tests can also be divided into sub-phases with different testing temperatures. However, the first step in BE testing is IBIS, IBIS testing is the crucial part of BE testing, as it is the step where most stress is applied on packaged chips, the following insertions usually do not bring any additional test coverage <sup>4</sup> with respect to NVM operations. For that reason, in this thesis we consider the labels assigned right after IBIS testing as a final label of the packaged chip, yet we will refer to it as BE. Figure 2.2 is a representation of the entire test process.

FIGURE 2.2: TestFlow

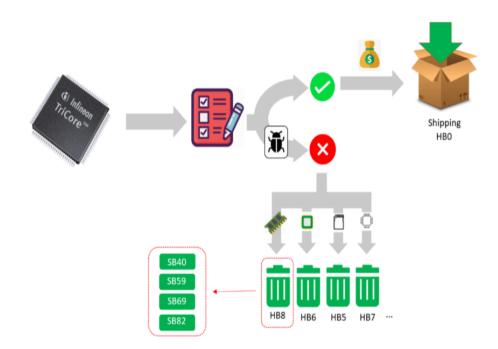

### 2.3.4 Test Binning

When a chip fail the testing it is discarded into specific bins according to the type of the failing part of the chip, or the failing test. There are two types of BINS: Hard-Bins and Soft-Bins.

- **HBIN**: a HBIN is defined by a single-digit number indicating the container index for failing devices depending on the filing module. For example, the HBIN1 is the bin that contains all the passing devices. HBIN8 is the BIN that contains all the chips that have failed because of flash related reasons. As we are interested in this thesis in the Flash binning, only these failing chips of this bin are considered.

- **SBIN**: a soft bin could be seen as a *sub-bin* of the HBIN where the failing devices are binned based on particular module tests, e.g. for flash testing, a chip exceeded the number of SBER tolerated in a verify test is binned in HB8 and a certain SBIN. SBIN is defined by a three-digit number which more precisely identifies the faults causing the rejection.

<sup>&</sup>lt;sup>4</sup>Test Coverage: the ability of the test to detect a given set of faults that may occur on the DUT. It is the ratio of detected failures over the total failures

FIGURE 2.3: Passing and failing chips distributed into Bins [32]

In our case, we will consider only the chips that passed the FE testing, so chips in HBIN1 after FE tests, among these chips we consider only the ones that either failed or passed IBIS testing for flash related issues, therefore we are considering passing chips, and chips binned in HBIN8 after IBIS tests. Further details about the dataset are provided in Chapter 4.

## 2.4 Test Results

All the test algorithms produce some results, which contain the results of the test and some other additional information. According to the specific test algorithm, we have two kind of results:

- **Bitmaps**: are special output of a verify and a repair test. As its name indicate, a bitmap is a topographical map of bit error position. This kind of results is not used in this thesis, and therefore is not detailed in this section and it will not be again referenced in the following chapters.

- **Parametric results**: are the results returned by FSIST tests and that can be expressed in numeric format via two parametric tables , the *result table* and the *debug table*. These data are stored into reserved RAM portions during the tests execution and are then downloaded by the ATE which save them in an Infineon's shared database for data analysis purpose.

## **Result Table**

The result table is the main output of a test algorithm, it comprises up to 6 parametric results. Each FSIST fills the result table with different information, depending on the relevance it has for that specific test. In table 2.1 the result table of the Program, Erase and Verify algorithms is reported [10].

| Parametrs | Program                | Erase                | Verify                                                                                                                 |

|-----------|------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------|

| PARAM1    | Program Time [s]       | Erase time [s]       | Number of SBER                                                                                                         |

| PARAM2    | Pump Max Load<br>[%]   | Pump Max Load<br>[%] | Number of MBER                                                                                                         |

| PARAM3    | Pump Avg Load<br>[%]   | Pump Avg Load<br>[%] | Number of failing zeros                                                                                                |

| PARAM4    | Pump Sigma<br>Load [%] |                      | Number of failing ones                                                                                                 |

| PARAM5    |                        |                      | Number of RED BL (i.e<br>Redundancy bit line)<br>used.<br>Number of RED<br>MNSEC (i.e Redun-<br>dancy word line) used. |

| PARAM6    |                        |                      | Number of new RED BL<br>used.<br>Number of new RED<br>MNSEC used.                                                      |

TABLE 2.1: Example of Result tables of Program, Erase, and verify commands

## Debug Table

The debug table is a much larger results table. It collects all the other information that may be useful to know about the executed test algorithm. It is optional and it is actually dumped only when expressively required for debug purposes. For example the program test reports in the debug table: Number of programmed pages, Mean page program time, Max page program time, etc.

# 2.5 Data Source For ML

In this thesis, as explained in chapter 1, we aim to predict the final state i.e. Pass/Fail of the packaged chip based on the passed FE tests that it went

through, that is given a new chip that passed FE, depending on the results of these test, we predict whether it will fail or pass the BE. However, as explained aforementioned, each testing algorithm produce two tables of 4 to 6 parameters. Therefore, for each chip, each parameter of each test in FE is a feature in our ML problem, lot and wafer ID are excluded, and the final label assigned after IBIS, will be our target. The final label assigned is either HBIN1 indicating pass or HBIN8 indicating flash related fail. However, in HBIN8, we have different possible failures indicated by soft bins as explained previously, some of these soft bins only have less than 10 instances, some occurs more than others in the dataset, and some are easier differentiated it from pass than others. For that reason, we will focus on this thesis, as a first step, on predicting one of the most occurring SBIN, SBIN555 (analysis regarding the choice of SBIN are provided in appendix). Therefore, the dataset is re-labeled as following, only samples with the selected SBIN are designated by a binary "0" indicating fail and all others (even samples that had a different fail mode, i.e different SBIN) are designated by a binary "1" indicating pass. This model thus uses a binary classifier, however in next step, other SBINs could be considered, or as well as a multi-classifier predicting different SBINs. Further details regarding the data are explained in Chapter 4

# **Chapter 3**

# Methodological background

## 3.1 Introduction

This chapter is dedicated to explain the theory behind the techniques used in this thesis work. According to usual workflow of Machine Learning [22] [9], the work is divided in four steps: data extraction, data processing, model selection and performance evaluation. The following chapter is structured as following, we first describe the statistics done on data and feature engineering <sup>1</sup> techniques used, we then introduce the challenge of data imbalance and present the proposed solutions, finally we define the possible classifiers we are using, the data used to train and test them, and how to evaluate them.

## 3.2 Feature Engineering

This section is dedicated to explain the theory behind the techniques adopted for feature filtering and processing.

### 3.2.1 Density Estimation

When the distribution of the data is unknown, it is rather useful to be estimated in order to understand the behavior of the data. There are two main density estimation techniques we use in order to visualize our data:

• Kernel Density Estimation (KDE) : Kernel density estimation (KDE) is a non-parametric way to model the probability distribution that generated a dataset. A basic example is the histogram, an histogram divides the data into discrete bins, counts the number of points that fall in each bin, and then visualizes the results in an intuitive manner. Kernel

<sup>&</sup>lt;sup>1</sup>feature engineering field contains a variety of issues and tasks. The most representative issues and tasks are feature transformation, feature generation and extraction, feature selection, automatic feature engineering, and feature analysis and evaluation

density estimates are closely related to histograms, but can be enriched with properties such as smoothness or continuity by using a suitable kernel [30]. In this thesis, we use the python function *kdeplot*, with a typical kernel that is the Gaussian kernel, to plot the density distribution of our data [31].

• **Probability barplot**: Another way to visualize the distribution of data, is to measure the probability of occurrence of each possible values in the data. This is usually done when dealing with data with discrete values.

These techniques provide an accessible way to see and understand trends, outliers, and patterns in data. Indeed these techniques were used in this thesis to analyze the features. In fact, in case of features with continuous values, KDE was used to present the distribution of the measurements, meanwhile for features with discrete values, it was more reasonable to use histograms and barplots.

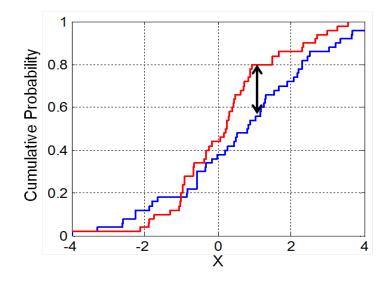

#### 3.2.2 Kolmogorov–Smirnov Test

The Kolmogorov–Smirnov **K-S** test [21], is a non-parametric test that compare continuous or discontinuous probability distributions. It could be used to compare a representative sample of data with a reference probability distribution, which is usually referred to as **one-sample K–S test**, or to compare two samples, usually referred to as **two-sample K–S test**. In this thesis, we are interested in the two-sample K–S test.

The K-S test is actually constructed as a statistical hypothesis test. We determine a null hypothesis, that the two samples we are testing come from the same distribution. Then we search for evidence that this hypothesis should be rejected. This is done by computing the K-S statistic D, if D exceeds a certain confidence level, we reject the null hypothesis that the samples are from the same distribution. On the other hand if the K-S statistic D is very small we cannot reject the hypothesis that the distributions of the two samples are the same.

The Kolmogorov–Smirnov statistic is defined as:

$$\mathcal{D}_{n,m} = \sup_{x} |(F_{1,n}(x) - F_{2,m}(x))|$$

(3.1)

Where where  $F_{1,n}$  and  $F_{2,m}$  are the empirical distribution functions of the first and the second sample respectively, *sup* the supremum function, and

FIGURE 3.1: Illustration of the two-sample Kolmogorov–Smirnov statistic. Red and blue lines each correspond to an empirical distribution function, and the black arrow is the two-sample KS statistic [2]

*n*, *m* are the sizes of first and second sample respectively. It could also be seen as the maximum vertical distance between the empirical cumulative distribution functions of the two samples [41], as in figure 3.1.

During this thesis, K-S test was a very efficient way to study the significance of the features. In fact, K-S test was used to determine if for a certain feature, the failing instances and the passing ones were different from each other. In other words, if we take one feature, and consider a sample of only passing chips and a sample of only failing chips, we can make use of K-S statistics to know whether these two samples are different or similar, in case of a very small K-S statistic the failing chips sample is similar to the passing chips sample and this feature is not actually bringing any information on how to separate these two classes. These results are better described in Chapter 4.

#### 3.2.3 Correlation Analysis

One of the most common approaches to dimensionality reduction is correlation analysis [35] [7], the purpose of this analysis is to identify the correlations between each pair of features, or between a feature and the target, to understand which features are the most relevant to the model.

The correlation between two variables is defined as:

$$\rho_{x,y} = \frac{cov(X,Y)}{\sigma_X \sigma_Y} = \frac{E[(X - \mu_X)(Y - \mu_Y)]}{\sigma_X \sigma_Y}$$

(3.2)

where *X* and *Y* are two vectors, with mean values  $\mu_X$  and  $\mu_Y$  and standard deviations  $\sigma_X$  and  $\sigma_Y$ . *E*[.] is the expected value operator, and *cov* denotes covariance. The correlation coefficient  $\rho_{X,Y}$  cannot exceed 1 in absolute value, and is a measure of the degree of linear relationship between two random variables.

The closer the correlation coefficient in absolute value to 1 the more closely the two variables are related. In case of correlation between a feature and the target, a high correlation shows that the feature is strongly related to the target, and therefore an interesting feature to keep. However, in case of two features, a high correlation means these two features are related, therefore bringing the same information to the model, and it is rather more reasonable to keep only one of them. Note that,  $\rho_{X,Y}$  is a measure of linear correlation, thus it does not take into consideration non linear correlations.

In order to exploit linear relationships between all pair of features, we compute the correlation matrix, given the matrix  $X = [X_1, ..., X_n]$ :

$$X = \begin{pmatrix} x_{11} & x_{12} & x_{13} & \dots & x_{1n} \\ x_{21} & x_{22} & x_{23} & \dots & x_{2n} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ x_{d1} & x_{d2} & x_{d3} & \dots & x_{dn} \end{pmatrix}$$

Where  $X_1, X_2, ..., X_n$  vectors are the n features of our dataset, *d* is the size of instances in our dataset. The correlation matrix  $R_X$  could be defined as following:

$$R_{X} = \begin{bmatrix} \rho_{X_{1},X_{1}} & \rho_{X_{1},X_{2}} & \rho_{X_{1},X_{3}} & \dots & \rho_{X_{1},X_{n}} \\ \rho_{X_{2},X_{1}} & \rho_{X_{2},X_{2}} & \rho_{X_{2},X_{3}} & \dots & \rho_{X_{2},X_{n}} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ \rho_{X_{n},X_{1}} & \rho_{X_{n},X_{2}} & \rho_{X_{n},X_{3}} & \dots & \rho_{X_{n},X_{n}} \end{bmatrix}$$

$R_X$  is a symmetric matrix with the correlation measures,  $\rho_{X_i,X_j}$  is the correlation coefficient between the  $i^{th}$  and  $j^{th}$  features, where  $i, j = \{1, ..., n\}$ , and n is the number of features. The correlation matrix for our features is computed and analyzed in Chapter 4.

### 3.2.4 Data Normalization

To better describe the data normalization, some definitions of the related statistics are firstly given:

• Mean: the statistical mean refers to the mean or average that is used to derive the central value of a discrete set of numbers, it is determined by

adding all the data points in a variable X and then dividing the total by the number of points:

$$\mu_X = \frac{\sum_i x_i}{n} \tag{3.3}$$

Where  $\mu_X$  is the mean value of the variable *X*, *n* is the size of *X*, and  $x_i$  is the *i*<sup>th</sup> point of *X*.

Standard deviation: often represented by *σ*, is a statistical parameter that measures the dispersion of a dataset relative to its mean. It is calculated as the square root of variance by determining the variation between each data point relative to the mean, for a variable X= [x<sub>1</sub>,..., x<sub>n</sub>], *σ* is calculated as following:

$$\sigma = \sqrt{\frac{\sum_{i} (x_i - \mu_X)}{n}}$$

(3.4)

If the data points are further from the mean, there is a higher deviation within the data set; thus, the more spread out the data, the higher the standard deviation. A low standard deviation means that most of the numbers are close to the average. Note that, this statistic is also useful to get an idea about the range of values of our features in this work.

In the context of machine learning, while training the model, when features have different range of values, data normalization is rather important to change the values of features to a common scale without changing its behavior or nature, thus no feature has more importance than another due to having larger values. The common feature normalization technique we adopting in this thesis is **Z Normalization (Standardization)** [43], that is computed as following:

$$X_{i,scaled} = \frac{X_i - \mu_i}{\sigma_X} \tag{3.5}$$

Note that in case of variable where all observations have the exact same value,  $\sigma_X$  will be equal to zero, and hence data normalization cannot be computed for such variable. However, a feature with  $\sigma = 0$  is actually not affecting the final target, as it is completely uncorrelated to the class, so it can be dropped anyway.

The importance of data normalization actually depends on the choice of the ML model. Some models exploit "Distance" or "Similarities" between data samples, such as SVM, in this case, if the data is not scaled, some features may be given higher priority than others. On the other hand, other graph-based models, such as Random forest and Naive Bayes, are invariant to data scaling. Some other models like Neural Network may not necessarily need data scaling, but that could help speed up the learning and lead to faster convergence. Further details about the ML algorithms are presented in Section 3.4.2.

# 3.3 Dimensionality Reduction

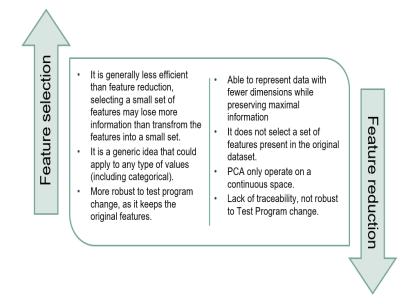

As we are dealing with a lot of possible features, it is important to consider dimensionality reduction techniques. In this thesis we give priority to filtering techniques, that is, choosing features based on their correlations and properties as explained above, however, feature selection and reduction techniques were studied. In literature there are two ways to reduce the dimensions and granularity of features:

- Feature Selection: is selecting the most informative features and excluding the least informative ones without changing them. Example of feature selection techniques is to consider random forest algorithm to rank features by importance, and take the top ones. [27]

- Feature Reduction: is transforming features into a lower dimension, creating new features that are a combination of the original features. The most known and effective technique for feature reduction is PCA (Principal Component Analysis) [44].

However, these two techniques have their pros and cons, Fig 3.2 is a summary of the difference between these two techniques. In fact, reduction technique are rather efficient yet such methods do not select a set of features present in the original dataset, and thus cannot be used to know the killer features in the testflow, in other words, we will not be able to know which feature, i.e FE test is influencing the chip failure in IBIS. On the other hand, feature reduction techniques are not robust to feature set variation. In fact, test program may slightly change in terms of test time, number of tests and flow tests, hence a variation in the features set. Therefore we want to keep track of the exact name of the killer test, to extend the same ML model to other test programs in the future.

FIGURE 3.2: Feature selection Vs feature reduction

# 3.4 Machine Learning Techniques

### 3.4.1 Imbalanced Classification

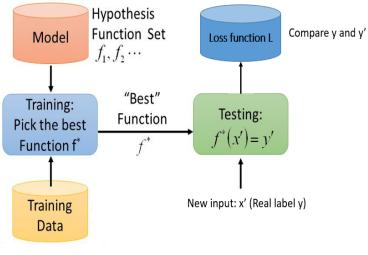

The imbalanced data is characterized by having many more instances of certain classes than others [33]. In our case, fail instances are rare compared to pass instances, therefore respectively the minority and majority class. The fundamental issue with the imbalanced learning problem is the ability of imbalanced data to significantly compromise the performance of most standard learning algorithms [15]. In fact, most learning techniques are designed to maximize the expected accuracy by empirical risk minimization. That is to say, looking for the method that minimizes the loss as follows :

$$\min_{f} \sum_{i} L(f(x_i), y_i) \tag{3.6}$$

where *x* is the input, f(x) is the predicted output, and  $y \in 1,0$  is the real label, as also seen in Fig. 3.3. However, when the data is imbalanced, as in our case, the majority class is Pass instances, labeled as y = 1, the minimum value of (3.6) may be achieved by setting *f* to be as simple as  $f(x) \equiv 1, \forall x$ . In other words, a "*high accuracy*" classifier may be achieved simply by declaring or classifying all samples as being in the majority class [6]. A model who always predict pass is actually useless, for that, different techniques were suggested in literature to deal with the imbalance challenge, whether techniques to re-balance the dataset, or techniques to bias the model in order to

take into consideration the imbalance issue of dataset. In the following section we summarize the techniques we tried in this thesis:

- Data level:

- undersampling

- oversampling

- Algorithm level:

- Cost-Sensitive Learning (CSL)

- Balanced Random Forest

However various other techniques are available based on different ML problems, the interested reader may refer to [15].

(x1,y1)(x2,y2)(x3,y3)..

FIGURE 3.3: Machine learning workflow

#### **Balancing Data:**

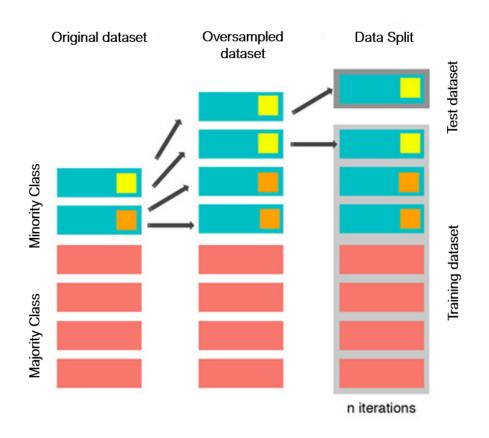

Without any changes in the learning algorithm, we need to modify the dataset itself to provide a balanced training set for the classifier. There are two ways to balance the dataset, augmenting the minority class to be equal to the majority or reducing the number of majority class instances to be equal to the minority class, these techniques are called respectively **Oversampling** and **Undersampling**.

- Oversampling: consist of augmenting the minority class, by adding replicates of failing samples. Although this solves the imbalance issue, it may lead to an increase in computation time and to overfit due to a large number of identical minority training instances. However, another recommended oversampling technique is to create new synthetic instances of the minority class, instead of only replications, this technique is known as SMOTE oversampling (Synthetic Minority Oversampling) and it creates entries that are interpolations of the minority class [4], which is one of the techniques adopted in this work, the results are presented in Chapter 5.

- Undersampling: consist of randomly picking samples from the majority class, thus removes data from the original data set. Although this may reduce the number of the training instances, but will not append any new data to the original dataset. Results of this technique are also presented in Chapter 5.

#### ML Algorithms For Imbalanced Data:

Instead of creating a balanced data set for the model to train, other approach consist of changing the ML algorithm to handle the imbalance of data. Two approaches are suggested in this thesis:

- **Cost-Sensitive algorithms** : consists in using models which take into consideration the unbalancing of the data by weighting the training samples differently, depending on the class they belong to [13]. Intuitively, we want to give higher weight to minority class and lower weight to majority class. A possible way to set weights is to consider the ratio between the minority and majority class.

- **Balanced Random Forest (BRF)**: inspired by Random Forest to ensemble trees induced from balanced down-sampled data. The BRF algorithm does the following [5]:

- For each iteration in random forest, draw a bootstrap sample from the minority class. Randomly draw the same number of cases, with replacement, from the majority class.

- Induce a classification tree from the data to maximum size, without pruning. The tree is induced with the CART algorithm (Classification And Regression Tree algorithm) [29], with the following

modification: at each node, instead of searching through all features for the optimal split, only search through a set of randomly selected features.

Repeat the two steps above for the number of times desired. Aggregate the predictions of the ensemble and make the final prediction.

### 3.4.2 ML Classifiers

Several machine learning classifiers could be used to predict whether a chip is among the Pass class or the Fail class based on data measured on FE test, in this section we provide an overview of the classifiers studied in this thesis work. We use three different approaches:

- **Support Vector Machine (SVM)**: as a techniques based on similarity between data samples.

- Random Forest (RF): as graph-based technique.

- Neural network (NN): as a deep learning approach.

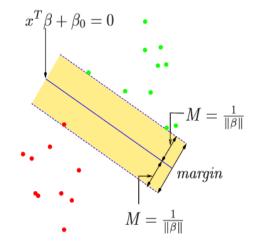

#### **Support Vector Machine:**

In a nutshell, SVM is a supervised machine learning algorithm that is based on the idea of finding an hyperplane that best divides a dataset into two classes, as shown in the Figure 3.4. In fact, in case of linearly separated, We suppose that a training dataset S is available

$$S = \{x_i \in \mathbb{R}^{1 \times d}, y_i \in \{0, 1\}\}, i = 1, \dots n.$$

(3.7)

the values -1,1 are assigned to the two classes which the data belong to, could be referred to as class A and class B, for example  $y_i = -1$  if the sample  $\in$  class A, and  $y_i = 1$  if the sample  $\in$  class B.

The hyperplane  $F_0$  in the  $\mathbb{R}^d$  space is defined as:

$$F_0 = \{x | f(x) = x\beta + \beta_0 = 0\}$$

(3.8)

where  $\beta \in \mathbb{R}^d$  with  $\|\beta\|_{\cdot} = 1$ . The classification is then based on the choice of f(x) (and consequently of  $F_0$ ):

FIGURE 3.4: linearly separable SVM classification problem [36]

for a new sample  $x^{new} \notin S$ , we classify

$$\begin{cases} 1 \quad y^{new} = -1 \text{ if } f(x^{new}) > 0\\ 2 \quad y^{new} = 1 \text{ if } f(x^{new}) < 0 \end{cases}$$

(3.9)

Since, by assumption, the two classes are separable, then it is possible to find a function f(x) s.t.

$$y_i f(x) > 0 \ \forall i \tag{3.10}$$

We choose the hyperplane yielding the largest margin M between the two classes as seen in Fig 3.4.

This can be rephrased in terms of the maximization problem:

$$\max_{\beta,\beta_0,\|\beta\|} M \text{ subject to } y_i f(x) > 1, i = 1, \dots, n$$

(3.11)

that can be further translated into a more convenient minimization problem:

$$\min_{\beta,\beta_0} \|\beta\|. \text{ subject to } y_i f(x) > 1, i = 1, \dots, n$$

(3.12)

The best hyperplane is found by optimum  $\beta$  that maximizes the margin. The boundaries of the defined margin, are called the support vectors [36].

However, in case of non linearly separable data, SVM is employed in combination with Kernel Methods. To put it briefly, the idea of kernel methods is to map the non-linear separable dataset into a higher dimensional space where it is possible to find an hyperplane that can separate the samples. The kernel function defines inner product of the mapping function [36]. Popular choices for the kernel function K are:

- **Polynomial:**  $K(x_i, x_j) = (1 + \langle x_i, x_j \rangle)^d$

- **Radial Basis (RBF):**  $K(x_i, x_j) = \exp(-\frac{||x_i x_j||}{\sigma^2})$

- Neural network:  $K(x_i, x_j) = tanh(\langle x_i, x_j \rangle + b)$

Radial Basis kernels are the most widely used and the ones considered in this thesis.

#### **Random Forest:**

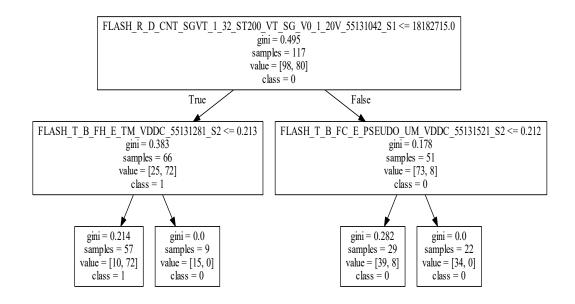

**Decision Tree Model:** Decision tree models are a non-parametric supervised learning method used for classification and regression. The goal is to create a model that predicts the value of a target variable by learning simple decision rules inferred from the data features [29]. In a decision tree, each internal node represents a "question" on an attribute (e.g. whether the number of SBER of a verify test is above a certain value or no, see Section 2.3.1 and Section 2.4 ), each branch represents the outcome of the question, and each leaf node represents a class label. Each branch can generate other branches until a a final predicted labels are reached, which correspond to the leaves of the tree. Figure 3.5 , is an example of a simple decision tree, using *Gini inpurity* as splitting quality metric, and a maximum depth set to 3 [29]

**Random Forest** Random forest classifiers are among the widely known and the most robust classifiers [12]. A random forest is a meta estimator that fits a number of decision tree classifiers on various sub-samples of the dataset and uses averaging to improve the predictive accuracy and control overfitting. In random forests, each tree in the ensemble is built from a sample drawn with replacement (i.e., a bootstrap sample) from the training set, see Fig. 3.6. In addition, when splitting a node during the construction of the tree, the chosen split is no longer the best split among all features. Instead, the split that is picked is the best split among a random subset of the features. As a result of this randomness, the bias of the forest usually slightly increases(with respect to the bias of a single non-random tree) but,due to averaging, its variance also decreases, usually more than compensating for the increase in bias, hence yielding an overall better model, less prone to overfitting.

FIGURE 3.5: Decision Tree Example

FIGURE 3.6: Random Forest overview

#### Neural network

In this thesis, we are using a feedforward artificial neural network, sometimes referred to as multi-layer perceptron. It consists of, at least, three layers of nodes: an input layer, a hidden layer and an output layer. Except for the input nodes, each node is a neuron that uses a nonlinear activation function. It utilizes a supervised learning technique called backpropagation for training and is able to distinguish data that is not linearly separable [14]. The model uses a ReLU activation function for the hidden layers:

$$ReLU: f(x) = max(0, x)$$

(3.13)

and a sigmoid function for its output single neuron

$$sigmoid: f(x) = \frac{1}{1 + \exp^{-x}}$$

(3.14)

The usage of a sigmoid activation function in the output node enables to predict a probability, thus the the predictor does not produce a label, but rather a probability of belonging to one or the other class. The predicted label is then the one corresponding to the most likely class. In this thesis, the implemented neural network is constituted of<sup>2</sup>

- 3 hidden layers.

- 512 nodes with 0.5 dropout

- optimizer: Adamax

- L2 Regularizer <sup>3</sup> of the neurons weights of  $10^{-3}$

- batch size: 64

- epochs: 40

Note that the results obtained by the NN were not as promising as the other models, thus we will not present its results in this thesis. However, further study of these model will be among the next steps of this thesis.

These three models are able to predict a probability, i.e. to predict how likely it is for a new instance to belong to a certain class. Given a new chip,

<sup>&</sup>lt;sup>2</sup>These hyperparameters were chosen based on a grid search for the model's optimization

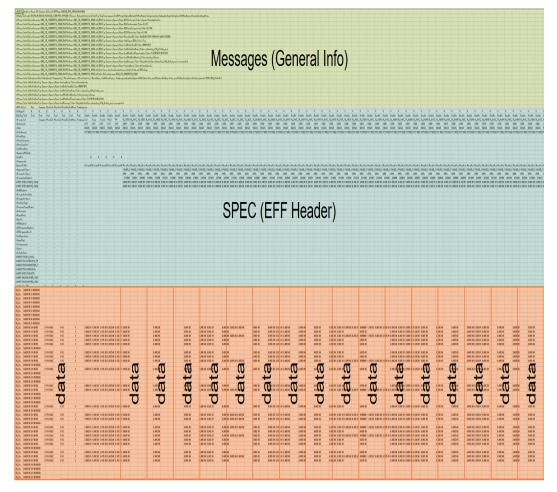

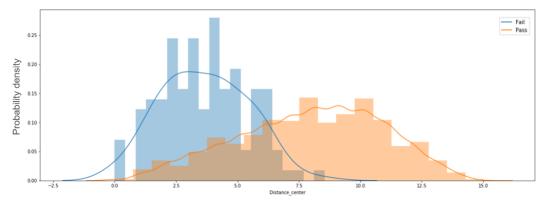

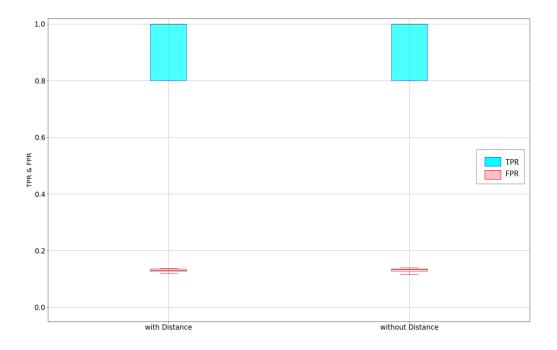

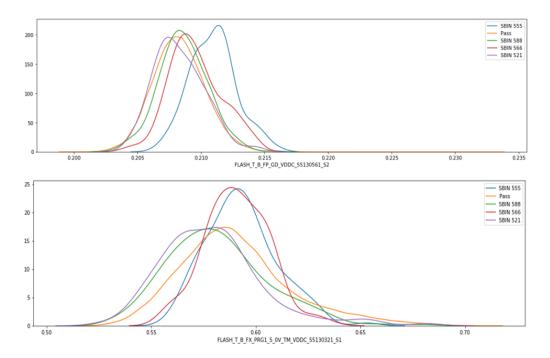

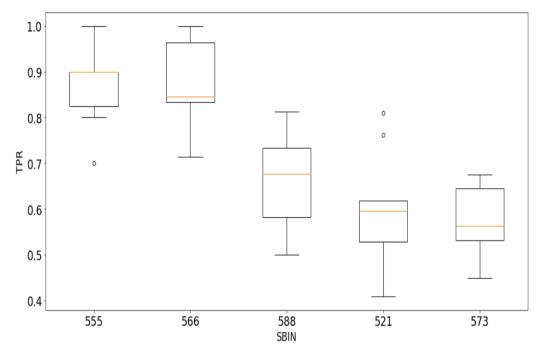

<sup>&</sup>lt;sup>3</sup>The regularization is a technique to discourage the increasing of the complexity of a model during its training.