# TESI DI LAUREA

# ELECTRICAL CHARACTERIZATION OF THIN FILM PASSIVATION LAYERS FOR P-TYPE SILICON SOLAR CELLS

Caratterizzazione elettrica di strati di passivazione a film sottile per celle solari in Silicio di tipo-p

Laureando: Morato Alessandro Relatore: Meneghesso Gaudenzio

Corso di laurea Magistrale in Ingegneria Elettronica

Padova, 17 Luglio 2012

Anno Accademico 2011/2012

## Abstract

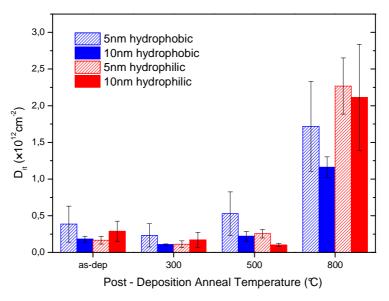

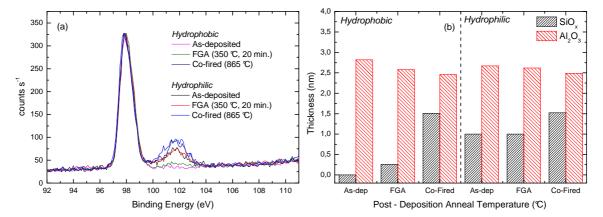

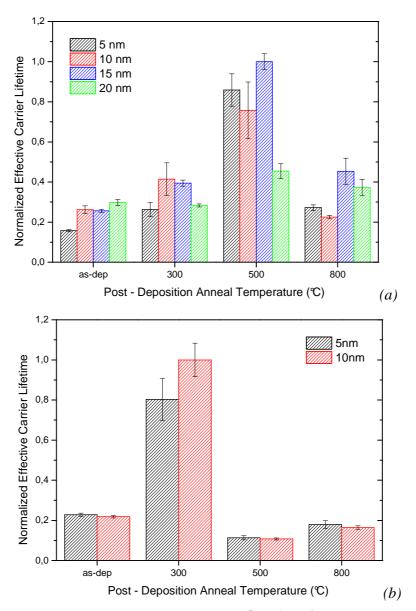

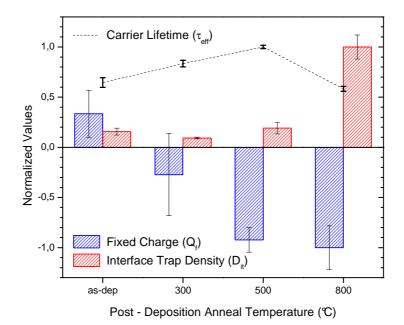

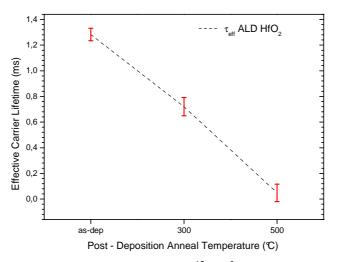

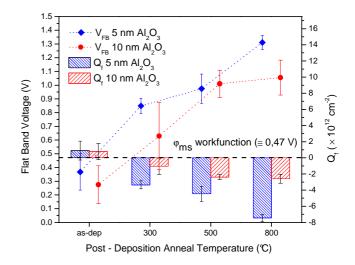

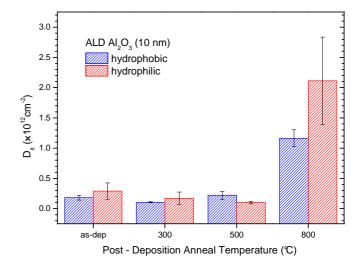

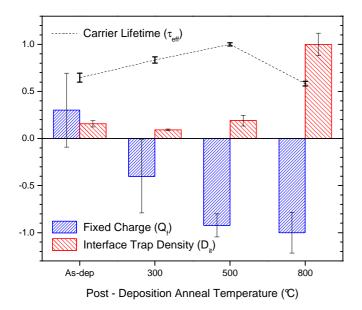

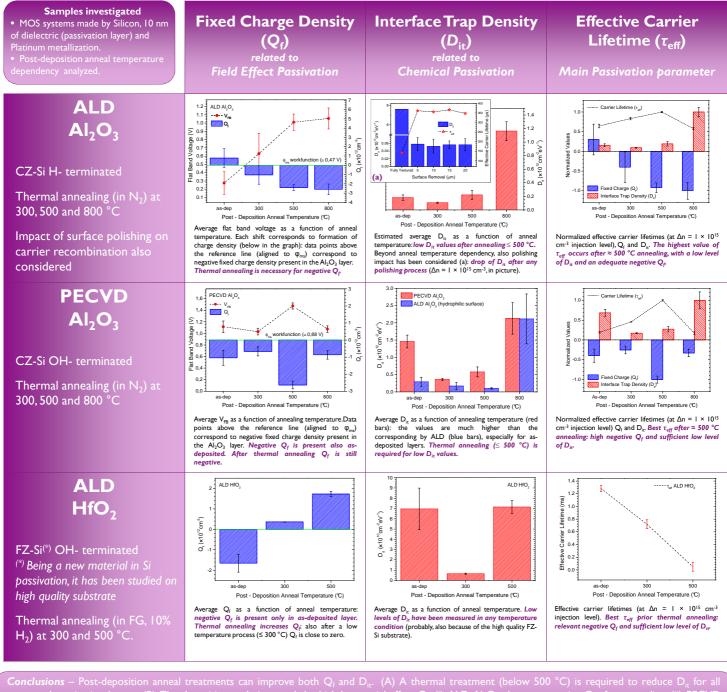

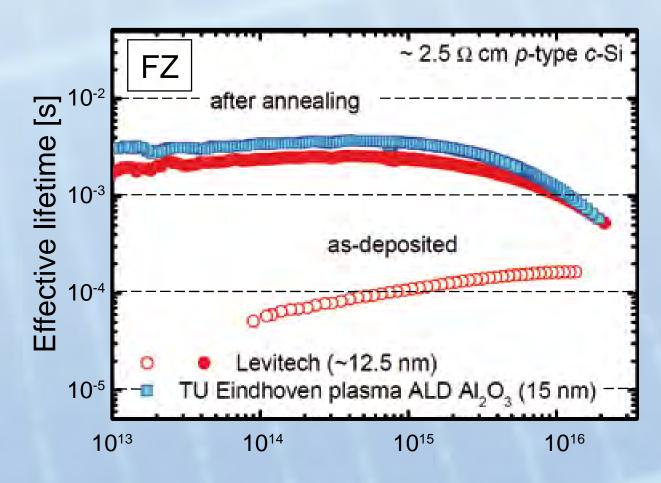

This work characterizes p-type Silicon surface passivation using a high-k material (Al<sub>2</sub>O<sub>3</sub> or HfO<sub>2</sub>) combining capacitance voltage (CV) and lifetime measurements. For Al<sub>2</sub>O<sub>3</sub> samples, the Silicon substrate bulk and surface quality is equivalent to CZ Silicon used in industrial solar cell processing. While Al<sub>2</sub>O<sub>3</sub> has been proven to provide high quality surface passivation on p-type doped Silicon surfaces, the influence of the growth conditions and the post-deposition annealing is not yet completely understood. The dielectric thin film has been deposited by common techniques (ALD, PECVD) on H-/OH- terminated Silicon surfaces (hydrophobic and hydrophilic, respectively). The impact of the roughness of the surface prior to the deposition has been also considered. Then, the passivation of each layer has been investigated as a function of different Al<sub>2</sub>O<sub>3</sub> thicknesses (5 to 30 nm) and postdeposition annealing temperatures (300 to 800 °C). CV measurements have been used to characterize *chemical passivation* (= interface trap density,  $D_{it}$ ) and *field effect passivation* (= fixed charge density,  $Q_f$ ). Lifetime measurements have been used to assess the effective surface passivation. The results of both types of electrical characterization fit well together. (i) Prior post-deposition anneal, only either chemical passivation (ALD) or field effect passivation (PECVD) is adequate, resulting in lower effective lifetimes. (ii) At higher annealing temperatures, a negative net charge in the  $Al_2O_3$  and a low  $D_{it}$  at the interface are measured, ideal for p-type CZ Silicon passivation and causing maximal effective lifetimes. (iii) At too high annealing temperatures, chemical passivation is destroyed resulting in decreasing effective lifetimes even though negative field effect remains in many cases. Another candidate as passivation layer on Silicon is HfO<sub>2</sub>. Being a new material in photovoltaics, it has been studied on high quality substrates (FZ Silicon) and its electrical characterization has demonstrated interesting passivation properties at low anneal temperatures, also as-deposited.

# Sommario

Questo lavoro tratta la caratterizzazione della passivazione superficiale del Silicio di tipo-p ottenuta tramite materiali ad elevata costante dielettrica (Al<sub>2</sub>O<sub>3</sub> e HfO<sub>2</sub>), combinando misure di capacità-tensione (CV) e di tempo di vita. Per quanto riguarda i campioni di Al<sub>2</sub>O<sub>3</sub>, la qualità del substrato di Silicio e della superficie è equivalente al Silicio CZ utilizzato nella produzione industriale di celle solari. Se da un lato è stato dimostrato come Al<sub>2</sub>O<sub>3</sub> possa fornire una passivazione superficiale di alta qualità su superfici di Silicio di tipo-p, l'influenza delle condizioni di crescita del materiale dielettrico e il contributo dell'annealing dopo la deposizione, non sono ancora stati del tutto compresi. Il sottile strato di dielettrico è stato depositato tramite tecniche comuni (ALD, PECVD) su superfici di Silicio con terminazioni H-/OH- (rispettivamente, idrofobiche ed idrofile). Anche l'influenza della rugosità della superficie, prima della deposizione del dielettrico, è stata considerata. La passivazione di ciascuno strato è stata analizzata in funzione di differenti spessori di Al<sub>2</sub>O<sub>3</sub> (da 5 a 30 nm) e delle temperature degli annealing successivi alla deposizione (da 300 a 800 °C). Le misure CV sono state impiegate per caratterizzare la cosiddetta passivazione chimica (correlata alla densità di trappole all'interfaccia,  $D_{it}$ ) e la passivazione per effetto di campo (legata alla densità di carica fissa,  $Q_i$ ). Le misure di tempo di vita sono state utilizzate per valutare l'effettiva passivazione di superficie. I risultati di entrambi i tipi di caratterizzazione elettrica concordano fra loro. (i) Prima dell'annealing, soltanto la passivazione chimica (ALD) o la passivazione per effetto di campo (PECVD) è adeguata, comportando bassi tempi di vita per i portatori. (ii) A temperature di annealing maggiori, la presenza di una carica netta negativa all'interno di  $Al_2O_3$  ed un basso livello di  $D_{it}$  all'interfaccia sono misurati, ideali per la passivazione del Silicio CZ di tipo-p, fornendo i maggiori tempi di vita. (iii) A temperature di annealing

troppo elevate, la passivazione chimica viene compromessa comportando una diminuzione dei tempi di vita, nonostante in molti casi un opportuno effetto di campo rimanga presente. Un altro candidato come strato di passivazione su Silicio è HfO<sub>2</sub>. Trattandosi di un materiale nuovo nell'ambito del fotovoltaico, è stato studiato su substrati di alta qualità (Silicio FZ) e la sua caratterizzazione elettrica ha dimostrato interessanti proprietà di passivazione a basse temperature di annealing, anche solo una volta depositato.

# Preface

The present thesis is submitted as fulfillment of the prerequisites for obtaining the M.Sc. in Electrical Engineering at the University of Padova, Italy (Università degli Studi di Padova). The duration of this 21 ECTS credits project is a 8 months internship from September 2011 to May 2012. The work has been carried out at IMEC (Interuniversity Microelectronics Centre), Leuven (Belgium) in the "PV-Platform" group headed by Dr. Joachim John and with the supervision of Prof. Gaudenzio Meneghesso, professor of Microelectronics at the Department of Electrical Engineering at the University of Padova. From this work an article has been presented at last "IEEE – Photovoltaic Specialists Conference" in Austin (TX, USA) and the results obtained have been also used in other publications (Appendix A). I wish to thank Prof. Meneghesso and Dr. John to give me the opportunity to prepare this thesis abroad, permitting me to work in a real high-technology research group . I wish to thank everyone who helped me during this amazing experience, in particular my daily supervisor Dr. Bart Vermang. I also want to acknowledge Hans Goverde, Dennis Lin and Anne Lorenz for their precious help answering my questions.

# **Table of Contents**

| Abs  | iii                                      |                                       |    |  |

|------|------------------------------------------|---------------------------------------|----|--|

| Som  | v                                        |                                       |    |  |

| Pref | vii                                      |                                       |    |  |

| 1    | Intro                                    | duction                               | 1  |  |

| 1.1  | Energ                                    | y Market                              | 1  |  |

| 1.2  | Photo                                    | 3                                     |    |  |

| 1.3  | Silicon                                  | 4                                     |    |  |

| 1.4  | Silicon Surface Passivation              |                                       |    |  |

| 1.5  | Outlin                                   | 5                                     |    |  |

| Refe | rences                                   |                                       | 7  |  |

| 2    | Recor                                    | nbination in Crystalline Silicon      | 9  |  |

| 2.1  | Recon                                    | 10                                    |    |  |

|      | 2.1.1                                    | Radiative Recombination               | 11 |  |

|      | 2.1.2                                    | Auger Recombination                   | 12 |  |

|      | 2.1.3                                    | Bulk Recombination Through Defects    | 13 |  |

|      | 2.1.4                                    | Surface Recombination Through Defects | 15 |  |

|      | 2.1.5                                    | Emitter Recombination                 | 17 |  |

| 2.2  | The Effective Lifetime $(\tau_{eff})$ 18 |                                       |    |  |

| 2.3  | Measuring the Effective Lifetime         |                                       |    |  |

|      | 2.3.1                                    | Lifetime Measurement                  | 19 |  |

|      | 2.3.2                       | Quasi-St                         | teady-State Photoconductance Technique (QSSPC)    | 22 |  |  |

|------|-----------------------------|----------------------------------|---------------------------------------------------|----|--|--|

| Refe | rences                      |                                  |                                                   | 26 |  |  |

| •    |                             |                                  |                                                   | 29 |  |  |

| 3    | -                           | k Material Deposition Techniques |                                                   |    |  |  |

| 3.1  | Wafer                       | Wafer Cleaning                   |                                                   |    |  |  |

| 3.2  | Drying Techniques           |                                  |                                                   |    |  |  |

| 3.3  | Deposition Techniques       |                                  |                                                   |    |  |  |

|      | 3.3.1                       | Thermal                          | ALD                                               | 33 |  |  |

|      |                             | 3.3.1.1                          | ALD Reactor                                       | 34 |  |  |

|      |                             | 3.3.1.2                          | Temperature and Pressure Choice                   | 39 |  |  |

|      | 3.3.2                       | PEALD                            |                                                   | 40 |  |  |

|      | 3.3.3                       | CVD                              |                                                   | 42 |  |  |

|      | 3.3.4                       | PECVD                            |                                                   | 44 |  |  |

| Refe | rences                      |                                  |                                                   | 46 |  |  |

| 4    | Silicor                     | 1 Surface                        | Passivation by ALD Al <sub>2</sub> O <sub>3</sub> | 49 |  |  |

| 4.1  | Electrical Characterization |                                  |                                                   |    |  |  |

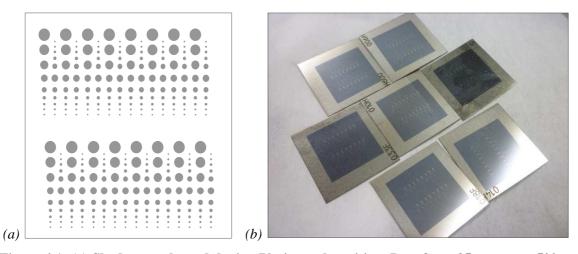

|      | 4.1.1                       | 1.1 Samples Preparation          |                                                   |    |  |  |

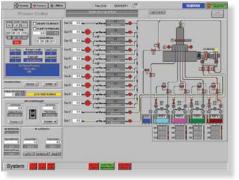

|      | 4.1.2                       | Electrical Measurement Setup     |                                                   |    |  |  |

|      | 4.1.3                       | Solar Gr                         | 53                                                |    |  |  |

|      |                             | 4.1.3.1                          | Scattering Properties                             | 53 |  |  |

|      |                             | 4.1.3.2                          | Loss Angle                                        | 55 |  |  |

| 4.2  | Field H                     | 56                               |                                                   |    |  |  |

|      | 4.2.1                       | Distribu                         | 56                                                |    |  |  |

|      | 4.2.2                       | Fixed Cl                         | 58                                                |    |  |  |

|      |                             | 4.2.2.1                          | Extraction of the Necessary Parameters            | 58 |  |  |

|      |                             | 4.2.2.2                          | Fixed Charge Density Calculation                  | 61 |  |  |

|      |                             | 4.2.2.3                          | Mobile Charge Density Calculation                 | 66 |  |  |

| 4.3  | Chemical Passivation        |                                  |                                                   |    |  |  |

|      | 4.3.1                       | D <sub>it</sub> Theo             | 68                                                |    |  |  |

|      | 4.3.2 Features and Disadvantages of Conductance Method                          | 70       |  |  |  |

|------|---------------------------------------------------------------------------------|----------|--|--|--|

|      |                                                                                 |          |  |  |  |

|      | 4.3.3 One Frequency Conductance Method                                          | 73       |  |  |  |

|      | 4.3.4 Interface Trap Density Investigation                                      | 75       |  |  |  |

|      | 4.3.4.1 Impact of Surface Finishing on Chemical Passiva                         | ition 76 |  |  |  |

|      | 4.4 Relating Electrical Results to Effective Carrier Lifetime                   | 79       |  |  |  |

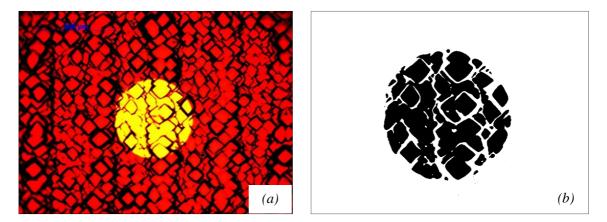

|      | 4.5 Silicon Surface Texturing Influence                                         | 83       |  |  |  |

| Refe | erences                                                                         | 87       |  |  |  |

| 5    | Silicon Surface Passivation by PECVD Al <sub>2</sub> O <sub>3</sub>             | 93       |  |  |  |

| 5.1  | Electrical Characterization                                                     |          |  |  |  |

|      | 5.1.1 Fixed Charge Density Investigation                                        | 93       |  |  |  |

|      | 5.1.2 Interface Trap Density Investigation                                      | 100      |  |  |  |

| 5.2  | Relating Electrical Results to Effective Carrier Lifetime                       | 105      |  |  |  |

| Refe | erences                                                                         | 108      |  |  |  |

| 6    | Silicon Surface Passivation by HfO <sub>2</sub>                                 | 111      |  |  |  |

| Refe | erences                                                                         | 116      |  |  |  |

| 7    | Conclusions                                                                     | 117      |  |  |  |

| #    | Appendix                                                                        | 119      |  |  |  |

| А    | Manuscript and poster presented at 38 <sup>th</sup> IEEE-PVSC, Austin (TX, USA) |          |  |  |  |

| В    | WCT-120, Silicon wafer lifetime tester, Sinton Consulting Inc.                  |          |  |  |  |

| С    | Accudry, IPA vapor dryers, IMTEC                                                |          |  |  |  |

| D    | Savannah Series, ALD systems, Cambridge NanoTech                                |          |  |  |  |

| E    | Levitrack Tool, Spatial ALD system, Levitech                                    |          |  |  |  |

| F    | FlexAl, PEALD systems, Oxford Instruments                                       |          |  |  |  |

| G    | <i>DEP<sub>x</sub> 2000</i> , PECVD system, Roth&Rau                            |          |  |  |  |

| Н    | PA300PS, semi-automatic probing system, Cascade Microtech Inc.                  |          |  |  |  |

| Ι    | Agilent 4284A (ex HP4284A), precision LCR meter, Agilent Tech.                  |          |  |  |  |

# Chapter 1 Introduction

### **1.1 Energy Market:**

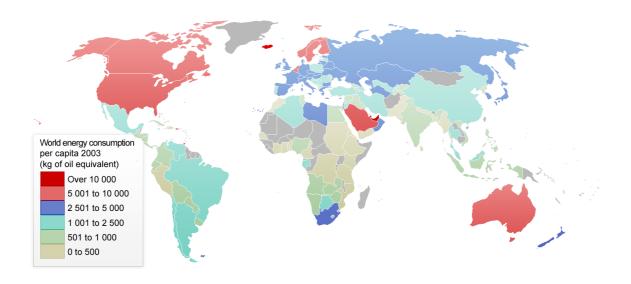

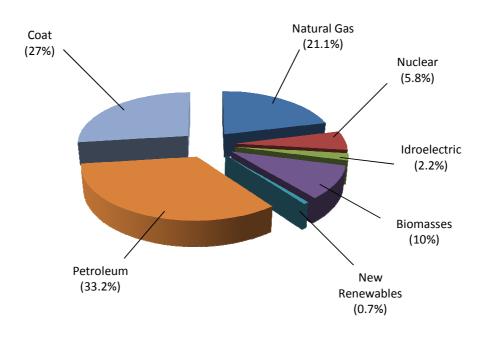

In the beginning of the twenty-first century, our society is faced with an energy challenge: as highly populous, developing countries (Brazil, Russia, India and China over all) become more affluent and as the developed nations continue to increase their energy consumption (Fig. 1.1) [1], the energy demand in the entire world has reached levels that cannot be sustained in the future. At the same time, fossil fuels, which are currently providing more than 80% of the total global energy supply (Fig. 1.2) [1], are limited (according the most pessimistic previsions we have already reached the petroleum extraction peak [2]) and, in addition, their widespread use has significant adverse environmental consequences. The combustion of fossil fuels produces carbon dioxide, which is one of the causes of global warming as well as of other environmental effects, such as acid rain, higher ozone concentration in urban areas, particulates and aerosols that are detrimental to air quality. The limited supply of the fossil fuels and their effects on the global environment indicate the only long term solution of the energy challenge: a significant increase in the use of renewable energy sources for the production of electricity as well as for meeting other energy needs of the industrial and post-industrial human society.

### 2 Chapter 1 - Introduction

Figure 1.1: Map depicting world energy consumption per capita based on 2003 data [1]

Figure 1.2: Primary energies in the world [1]

## 1.2 Photovoltaic Technologies

In 1839 Becquerel discovered the photovoltaic (PV) effect by demonstrating that electrons could interact with electromagnetic radiation with an electrolytic cell made from a Platinum electrode coated by Silver [4]. One century later (1954), Gerald Pearson, Daryl Chapin and Calvin Fuller were the first ones to build a PV device based on mono-crystalline Silicon with an energy conversion efficiency of ~ 6 % and an estimated cost of 200 \$/W [5]. Nowadays, great strides have been made, leading to more and more efficient devices: the current record for commercial monocrystalline-Silicon based solar cell is  $\approx 25\%$  [6].

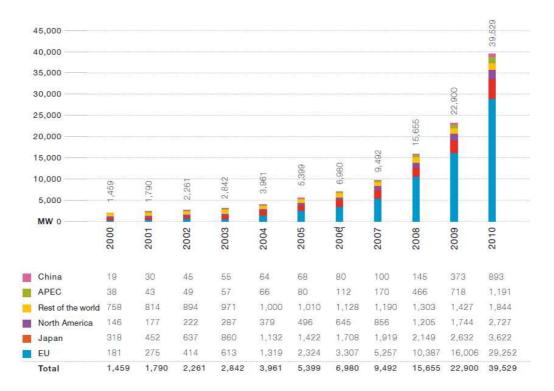

Figure 1.3: Evolution of global cumulative installed PV capacity (2000-2010) [3]

Photovoltaics, among other forms of renewable energies (e.g. wind, hydro, biomass, and geothermal) can be considered a credible candidate to face the global climate change and energy crisis. Compared to conventional energy production by burning fossil fuels, PV has

#### 4 Chapter 1 - Introduction

several advantages ranging from offsetting greenhouse gas emissions, to meeting government renewable energy targets, to providing a cost-competitive and self-sufficient energy option for rural and remote communities. However, in order for PV to be widely accepted as an economically viable means of electricity generation and to be used on a larger scale across the world, the levelized cost of PV electricity must be reduced to values that are competitive with conventional electricity.

The progress of PV market over the last 10 years has been impressive: the total installed PV capacity in the world has multiplied by a factor of 27, from 1.5 GW in 2000 to 39.5 GW in 2010 with a yearly growth rate of 40% (Fig. 1.3) [3]. That growth has proved to be sustainable, allowing the industry to develop at a stable rate and governments to finance further research.

### **1.3 Silicon Solar Cells**

PV market is expected to be dominated by crystalline Silicon solar cells for at least the next decade [3]: Silicon dominance will last at least until 2020. In order to maintain this market share of Silicon in PV technology and obtain grid parity, production costs require a significant reduction. At present, the Silicon wafer cost constitutes about 70% of the cell cost [7], driving the PV industry to ever thinner wafers.

PV industry uses solar grade Czochalski (CZ) Silicon (less pure and less expensive) for the production of solar cell. The typical thickness of a mono-crystalline solar cell is 200  $\mu$ m: Silicon solar cells costs can be reduced by decreasing the Silicon substrate thickness. The continuous decrease of the substrate thickness yields an increased surface-to-volume ratio that makes *surface passivation* a crucial point. Passivation means the deposition on the Silicon substrate of a *passivating surface layer* such as Silicon nitride, Silicon dioxide or

Titanium dioxide, which can reduce surface recombination and increase the efficiency of the solar cell.

### **1.4 Silicon Surface Passivation**

As described in the above paragraph, the passivation of the Silicon surface is one of the most relevant technological challenges to reduce thickness of the Silicon substrate. The effective recombination can be used to express the level of surface passivation. As it will be widely explained in Chap. 2, the surface is an abrupt interrupt of the Silicon crystal lattice resulting in a high density of dangling bonds on top of the wafer. The dangling bonds create interface traps, which are active recombination centers of excited electron/hole pairs. The interface trap density can be reduced by synthesizing a thin functional film (passivation layer) on the Silicon surface to reduce the effects of dangling Silicon bonds. Furthermore, an electrical field can be created at the Silicon/deposited film interface, by forming a fixed charge density with the adequate polarity within the passivation layer. When this electrical field has the right polarity, it can repel the free electrons at the surface reducing the carrier concentration at the surface. Both effects lead to reduction of the effective surface recombination velocity and therefore to an increase of conversion efficiency. They are indicated as "chemical passivation" and "field effect passivation" respectively. They are considered the most common passivation techniques and this work provides a characterization of the Silicon surface passivation by analyzing these two aspects.

### **1.5 Outline of the Thesis**

This thesis wants to provide a description of the Silicon surface passivation (in terms of chemical passivation and field effect passivation) by electrical measurements. Various passivation layers have been investigated (varying the material used, the deposition

### 6 Chapter 1 - Introduction

technique, the post-deposition annealing temperature). The work is developed in the following chapters:

- *Chap.2* provides an exhaustive dissertation about the carrier recombination theory. The main recombination mechanisms are discussed.

- *Chap. 3* illustrates the most common techniques to deposit passivation layers. Also the followed steps to prepare the samples investigated are here explained.

- *Chap.4* provides a theoretical explanation of the electrical measurement techniques used to characterize the passivation properties. The results of the first passivation layer (ALD Al<sub>2</sub>O<sub>3</sub>) are here collected.

- *Chap.5* presents a different deposition technique for Al<sub>2</sub>O<sub>3</sub>: PECVD.

- *Chap.6* discusses the characterization of a novel material for Silicon surface passivation: HfO<sub>2</sub>.

# **Chapter 1 References**

- [1] <u>www.iea.org</u>, last access date 25/06/2012.

- [2] Alexandra Witze, "Energy: That's oil, folks...", Nature 445, 14-17 (4 January 2007).

- [3] <u>http://www.epia.org</u>, EPIA (European Photovoltaic Industry Association), "Global Market Outlook For Photovoltaics Until 2015", last access date 26/06/2012.

- [4] Richard Williams, "*Becquerel Photovoltaic Effect in Binary Compounds*", Journal of Chemical Physics, Vol. 32, pp.1505-1514 (May 1960).

- [5] John Perlin, "*From Space to Earth: The Story of Solar Electricity*", Harvard University Press (2002).

- [6] ARC Photovoltaics Centre of Excellence, "Annual Report 2008", pp. 26-28, University of New South Wales, Australia (2008).

- [7] <u>http://pvinsights.com/</u>, last access date 22/06/2012.

8 Chapter 1 - Introduction

# Chapter 2 Recombination in Crystalline Silicon

This chapter explains in detail the theory of generation and recombination in Silicon: the theoretical approach is mostly based on [1, 2]. Generation in semiconductors is the process whereby electron-hole pairs are created and recombination is its opposite: a loss of electron-hole pairs, with the excess energy released as either *photons* or *phonons*. Recombination therefore reduces the performance of solar cells, particularly the open circuit voltage ( $V_{oc}$ ). Experimentally, it is the recombination lifetime that is measured. The recombination lifetime ( $\tau$ ) of a material can be defined as the average time for an electron – hole pair to recombine following generation. It can be determined from the recombination rate (U) as shown in Equation 2.1:

$$\tau = \frac{\Delta n}{U} \tag{2.1}$$

where  $\Delta n$  ( $\Delta p$ ) is the excess carrier density of electrons (holes) and  $\Delta n = \Delta p$  in the absence of trapping effects. Interpreting this recombination lifetime can be difficult, as it represents a number of specific recombination mechanisms occurring simultaneously within the bulk and at the surfaces. For this reason, the recombination lifetime is sometimes referred to as an *effective lifetime*.

### 2.1 **Recombination Mechanisms**

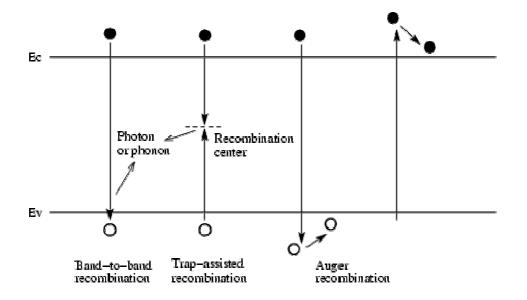

Three fundamental recombination mechanisms that occur in semiconductors are (i) *radiative recombination*, (ii) *Auger recombination*, and (iii) recombination through defects in the bandgap (as known as *Shockley – Hall – Read recombination*). Other recombination processes within solar cells can generally be viewed as a combination of these three fundamental mechanisms: (a) The surface of a semiconductor represents an abrupt discontinuity in its otherwise uniform crystal structure. The high number of dangling bonds creates a large density of defects throughout the bandgap. Therefore, *surface recombination* is a particular case of process (iii) above. (b) Similarly, in the heavily doped emitter regions of a solar cell, the high doping results in Auger recombination limiting the lifetime within the emitter, in conjunction with surface recombination at the emitter surface. *Emitter recombination* is therefore a particular case of processes (ii) and (iii) above.

Figure 2.1: The main recombination mechanisms are depicted: (a) radiative recombination, (b) recombination through defects in the bandgap, (c) Auger recombination with the excess energy transferred to a valence band hole or to a conduction band electron.

### 2.1.1 Radiative Recombination

Radiative recombination is simply the direct destruction of an electron - hole pair as depicted in Figure 2.1 (a): it is the inverse process to optical generation, the excess energy being released mainly as a photon with an energy close to that of the bandgap. It involves a conduction band electron falling from an allowed conduction band state into a vacant valence band state (a hole). Therefore, as seen in Equation 2.2, the radiative recombination rate ( $U_{rad}$ ) depends on the concentration of free electrons (n) and free holes (p), while B is the coefficient of radiative recombination.

$$U_{rad} = Bnp \tag{2.2}$$

From Equation 2.2, the common relationships for the radiative lifetime in n-type and p-type material under low injection ( $\tau_{rad,li}$ ) and high injection conditions ( $\tau_{rad,hi}$ ) can be determined as shown in Equation 2.3, where  $N_{dop}$  is respectively the density of donor ( $N_D$ ) or acceptor atoms ( $N_A$ ). It can be seen that the radiative lifetime depends on the inverse of the majority carrier density ( $\tau_{rad} \propto 1/n$ ). Therefore,  $\tau_{rad}$  is constant at low injection, but then decreases and continues to decrease as the injection level increases. In general, the rate of radiative recombination in Silicon is considered negligible compared to other recombination processes, since Silicon is an *indirect-bandgap* semiconductor and must simultaneously emit a photon and a phonon to conserve both energy and momentum (improbable, according to quantum mechanics).

$$\tau_{rad,li} = \frac{1}{BN_{dop}}$$

and  $\tau_{rad,hi} = \frac{1}{B\Delta_n}$  (2.3)

### 2.1.2 Auger Recombination

Traditionally, Auger recombination is viewed as a three-particle interaction where a conduction band electron and a valence band hole recombine, with the excess energy being transferred to a third free electron or hole, as depicted in Figure 2.1 (c). The charge carriers involved are assumed to be non-interacting quasi-free particles. Therefore, the *eeh* process denotes when the excess energy is transferred to another electron, with the recombination rate given by  $U_{eeh} = C_n n^2 p$ . Similarly, the *ehh* process denotes when the excess energy is transferred to another hole, with recombination rate  $U_{ehh} = C_p n p^2$ , where  $C_n$  and  $C_p$  are Auger coefficients. The total Auger recombination rate ( $U_{Auger}$ ) is then given by Equation 2.4, from which the common relationships for the Auger lifetime in n-type and p-type material under low injection ( $\tau_{Auger,li}$ ) and high injection conditions ( $\tau_{Auger,hi}$ ) can be determined. Both are shown for p-type Silicon in Equation 2.5, where  $C_a = C_n + C_p$  is the ambipolar Auger coefficient.

$$U_{Auger} = C_n n^2 p + C_p n p^2 \tag{2.4}$$

$$\tau_{Auger,li} = \frac{1}{C_p N_A^2}$$

and  $\tau_{Auger,hi} = \frac{1}{(C_n + C_p)\Delta n^2}$  (2.5)

From Equation 2.5, it can be seen that the Auger lifetime ideally depends on the inverse of the carrier density squared ( $\tau_{Auger} \propto 1/n^2$ ). It shows a stronger dependence with the injection level than  $\tau_{rad}$ , and therefore, Auger recombination will become the dominant mode of recombination in Silicon for high injection levels, as might occur in concentrator solar cells, or for high doping densities, as occurs in heavily doped emitter regions. However, Auger recombination is more complicated. Band-to-band Auger processes can occur with phonon participation (*phonon-assisted Auger recombination - PAAR*) and without phonon participation (*direct Auger recombination - DAR*) to conserve momentum. Furthermore, a third Auger recombination mechanism, *termed trap-assisted Auger recombination* (*TAAR*)

has been also proposed. Finally, additional processes that have not yet been accounted for may impact the Auger lifetime. One such possibility is the Coulombic interactions between mobile charged carriers and fixed charges (ionized dopant atoms). A general parameterization of Auger recombination has been proposed by Kerr and can be found in Equation 2.6 [1]. The parameterization is intended to provide the simplest functional form for the experimental observations of Auger recombination in Silicon and demonstrates that Auger recombination is increased above the ideal rate, and that the increase is a function of both the doping density and the injection level.

$$U_{Auger} = np(1.8 \times 10^{-24} n_o^{0.65} + 6 \times 10^{-25} p_o^{0.65} + 3 \times 10^{-27} \Delta n^{0.8})$$

(2.6)

### 2.1.3 Bulk Recombination Through Defects

The presence of defects within a semiconductor crystal, coming from impurities or crystallographic imperfections such as dislocations, produces discrete energy levels within the bandgap. As shown in Figure 2.1 (b), these defect levels, also known as *traps*, greatly facilitate recombination through a two step process : a free electron from the conduction band first relaxes to the defect level and then relaxes to the valence band where it annihilates a hole. The dynamics of this recombination process were first analyzed by Shockley and Read [3] and Hall [4], with the recombination rate ( $U_{SRH}$ ) for a single defect level given by Equation 2.7. Where  $n_i$  is the intrinsic carrier concentration and  $\tau_{p0}$  and  $\tau_{n0}$  are the fundamental hole and electron lifetimes which are related to the thermal velocity of charge carriers ( $v_{th}$ ). The density of recombination defects ( $N_t$ ), and the capture crosssections ( $\sigma_p$  and  $\sigma_n$ ) for the specific defect as shown in Equation 2.8.  $n_1$  and  $p_1$  are statistical factors defined as in Equation 2.9, where  $N_C$  and  $N_V$  are the effective density of states at the conduction and valence band edges,  $E_C$  and  $E_G$  are the conduction band and bandgap energies and  $E_t$  is the energy level of the defect. k is the Boltzmann's constant.

14 Chapter 2 - Recombination in Crystalline Silicon

$$U_{SRH} = \frac{np - n_i^2}{\tau_{p0}(n + n_1) + \tau_{n0}(p + p_1)}$$

(2.7)

$$\tau_{p0} = \frac{1}{\sigma_p v_{th} N_t} \qquad and \qquad \tau_{n0} = \frac{1}{\sigma_n v_{th} N_t}$$

(2.8)

$$n_1 = N_C \exp \frac{E_t - E_C}{kT}$$

and  $p_1 = N_V \exp \frac{E_C - E_G - E_t}{kT}$  (2.9)

It follows from Equation 2.1 that the SRH lifetime ( $\tau_{SRH}$ ) can be expressed as in Equation 2.10. It can be seen that the SRH lifetime is a function of the carrier injection level and the dopant density (through  $n_0$  and  $p_0$ ), as well as defect specific properties such as the concentration of traps, their energy level and their capture cross-sections. An important result that follows is that traps with energies close to the centre of the bandgap (deep defects) are the most effective recombination centers. Furthermore, for such deep defects in p-type Silicon, the SRH lifetime can be simplified for low injection ( $\tau_{SRH,li}$ ) and high injection ( $\tau_{SRH,li}$ ) conditions as in Equation 2.11.

$$\tau_{SRH} = \frac{\tau_{n0}(p_0 + p_1 + \Delta_n) + \tau_{p0}(n_0 + n_1 + \Delta_n)}{n_0 + p_0 + \Delta n}$$

(2.10)

$$\tau_{SRH,li} = \tau_{n0} \qquad and \qquad \tau_{SRH,hi} = \tau_{n0} + \tau_{p0} \tag{2.11}$$

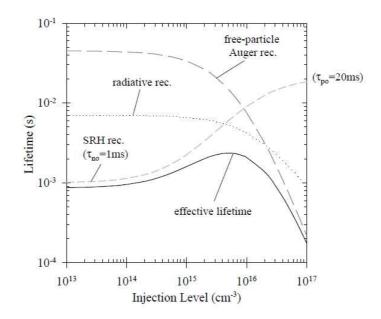

Figure 2.2 shows lifetime curves for a 1  $\Omega$ ·cm p-type Silicon wafer for SRH recombination (deep defect,  $\tau_{n0} = 1$  ms and  $\tau_{p0} = 20$  ms), radiative recombination and free-particle Auger recombination. It can be seen that recombination through deep defects results in a distinctly different injection level dependence than the intrinsic recombination processes (radiative and Auger), and that SRH recombination normally dominates at low injection levels, eventually being surpassed by the rate of Auger recombination at sufficiently high injection levels.

Figure 2.2: Lifetime curves for a 1  $\Omega$ ·cm p-type Silicon wafer for *SRH recombination* (deep defect,  $\tau_{n0} = 1$  ms and  $\tau_{p0} = 20$  ms), *radiative recombination* and *free-particle Auger recombination*, taken from [1].

### 2.1.4 Surface Recombination Through Defects

Since the surfaces or interfaces of a Silicon substrate represent an abrupt discontinuity in its crystalline structure, the SRH bulk recombination discussion above serves as a useful starting point for the analysis of defects originating at the surfaces of semiconductors. The large numbers of partially bonded Silicon atoms give rise to many *dangling bonds*, and therefore a large density of defect levels are found within the bandgap near the semiconductor surface. Even if the Silicon surface is not bare (due to a native oxide on top) the presence of Silicon-oxygen bonds can stress the crystal structure at the surface, which again introduces many defect states. The SRH analysis of Section 2.1.3 can be again applied, although it has to be reformulated in terms of recombination events per unit surface area, rather than per unit volume. For a single defect at the surface, the rate of surface recombination ( $U_{surface}$ ) is given by Equation 2.12, where  $n_s$  and  $p_s$  are the

#### 16 Chapter 2 - Recombination in Crystalline Silicon

concentrations of electrons and holes at the surface, and  $S_{no}$  and  $S_{po}$  are related to the density of surface states per unit area ( $N_{ts}$ ), and the capture cross-sections ( $\sigma_p$  and  $\sigma_n$ ) for the specific defect as shown in Equation 2.13.

$$U_{surface} = \frac{n_s p_s - n_i^2}{\frac{n_s + n_1}{S_{p0}} + \frac{p_s + p_1}{S_{n0}}}$$

(2.12)

$$S_{n0} = \sigma_n v_{th} N_{ts} \qquad and \qquad S_{p0} = \sigma_p v_{th} N_{ts} \tag{2.13}$$

In reality, defect levels are so numerous that they can be considered to be continuously distributed throughout the bandgap, and both their density and capture cross-sections will be dependent on their energy level. Using  $D_{it}(E)$  for the density of interface traps at a given energy (rather than  $N_{ts}$  for a specific energy level) and integrating over the entire bandgap (from valence band energy  $E_V$  to conduction band energy  $E_C$ ), Equation 2.14 follows for a continuum of noninteracting surface states  $E_{it}$ . Similar to the definition of the recombination lifetime, the effective surface recombination velocity ( $S_{eff}$ ) is defined as in Equation 2.15 and so the surface recombination velocity can be related to the fundamental properties of the surface defects through Equations 2.12 and 2.14.

$$U_{surface} = \int_{E_V}^{E_C} \frac{v_{th}(n_s p_s - n_i^2)}{\frac{n_s + n_1}{\sigma_p(E_{it})} + \frac{p_s + p_1}{\sigma_n(E_{it})}} D_{it}(E_{it}) dE_{it}$$

(2.14)

$$U_{surface} = S_{eff} \Delta n \tag{2.15}$$

What can be concluded from Equation 2.14 is that there are two fundamental mechanisms for reducing the surface recombination rate at a semiconductor surface. (1) Reducing the density of the interface states and the magnitude of the capture cross-sections. By growing an appropriate dielectric layer such as Silicon oxide, many of the dangling Silicon bonds

are passivated with oxygen or hydrogen atoms and the  $D_{it}$  is reduced. (2) Minimizing the concentration of minority carriers also reduces the surface recombination rate. (2a) This can be achieved by doping the semiconductor surface to repel the minority carries such as in an emitter region or a BSF. (2b) Alternatively, fixed charges in an overlying dielectric layer can be used to either repel the minority carriers (for a p-type wafer one would use negative charges to repel the free electrons), or in the extreme case invert the surface (large amounts of fixed positive charges would invert the surface of a p-type Silicon wafer). This is also known as *field effect passivation*, as an electric field is essentially established near the surface.

### 2.1.5 Emitter Recombination

Modeling the recombination occurring within an emitter region from first principles is relatively complicated. Doping profiles are not normally uniform and so the spatial variation in the dopant concentration needs to be considered, as does the possibility of a dead layer from the diffusion process. Heavy doping effects including the degeneracy of the semiconductor, bandgap narrowing and free-carrier absorption need to be included, along with intrinsic recombination processes and the normal SRH recombination processes related to defects, both within the emitter and at the emitter's surface.

Because the emitter regions are heavily doped, two simplifications follow. Firstly, the minority carrier concentration in the emitter region normally remains low and secondly, Auger recombination is likely to be the dominant bulk recombination mechanism. It follows that the recombination lifetime in the emitter region is constant with injection level, and the recombination current into the emitter ( $J_{rec}$ ) can be expressed as in Equation 2.16, where  $J_{0E}$  is defined to be the emitter saturation current density, and *n* and *p* refer to the electron and hole concentrations on the base side of the space-charge region.

18 Chapter 2 - Recombination in Crystalline Silicon

$$J_{rec} = J_{0E} \, \frac{np}{n_i^2} \tag{2.16}$$

Emitter recombination can be viewed as a special case of surface recombination. A virtual surface can be defined just at the base side of the space-charge region. Hence, combining Equations 2.15 and 2.16 reduces for p-type Silicon to the quasistatic emitter approximation (Equation 2.17), with q the elementary charge. It is important to differentiate such a virtual surface from the actual surface of an emitter. The  $S_{eff}$  at the virtual surface is merely another way of representing the  $J_{0E}$ .

$$S_{eff} = J_{0E} \frac{N_A + \Delta n}{q n_i^2} \tag{2.17}$$

## **2.2** The Effective Lifetime $(\tau_{eff})$

The five recombination mechanisms discussed in Section 2.1 may occur simultaneously within a semiconductor. In many situations, some of the recombination processes will contribute negligibly to the overall recombination rate (e.g. radiative recombination in Silicon). Indeed, in many experimental situations the aim is to minimize the other recombination mechanisms to facilitate the exploration of one particular recombination process. In the study of surface recombination processes for example, high quality float-zone (FZ) Silicon wafers can be used to minimize bulk recombination. In other situations, the contributions from different recombination processes will be unknown or even unavoidable. It is therefore necessary to consider how the different recombination mechanisms combine to give an overall effective recombination rate or an effective lifetime. In general, the recombination processes can be considered to occur independently and the effective recombination rate ( $U_{eff}$ ) is simply the sum of the individual rates, as expressed in Equation 2.18, where the first three terms refer to bulk recombination processes and are often grouped as in Equation 2.19.

$$U_{eff} = U_{rad} + U_{Auger} + U_{SHR} + U_{surface} + U_{emitter}$$

(2.18)

$$U_{bulk} = U_{rad} + U_{Auger} + U_{SHR}$$

(2.19)

Test structures used for examining recombination at the interface of Silicon and a passivating film are briefly discussed.

The test structure is a Silicon wafer which has been passivated on both sides with an identical dielectric film. The recombination rate can be expressed as in Equation 2.20 and simplifies to Equation 2.21 if the carrier profiles are relatively uniform throughout the wafer with a thickness W.

$$U_{eff} = U_{bulk} + 2U_{surface} \tag{2.20}$$

$$\frac{1}{\tau_{eff}} = \frac{1}{\tau_{bulk}} + \frac{2S_{eff}}{W}$$

(2.21)

## 2.3 Measuring the Effective Lifetime

### 2.3.1 Lifetime Measurement

As an accurate determination of recombination lifetime is a fundamental prerequisite for lifetime spectroscopy. The measurement of carrier lifetimes is based on the recombination dynamics of excess carriers which are normally generated optically. The different techniques may be classified in terms of the time dependence of the illumination and the technique used to measure the excess carrier density. Concerning the time dependence of

the illumination, three operating regimes can be distinguished. (i) The first regime involves a sharp pulse of illumination that is rapidly turned off and a subsequent determination of the excess carrier density without illumination. This is the traditional *transient technique*, used especially to measure high carrier lifetimes. (ii) The second regime is the *steady-state illumination*, which is of minor importance due to the problem that the samples will quickly suffer from heating and a changing lifetime in true steady state. (iii) Such effects are avoided in the third regime, where the illumination intensity is slowly reduced to zero over several milliseconds, the decay being long enough to ensure that the sample remains in steady state in terms of the recombination processes. This is the basis of the *quasi-steady-state method* first introduced by Sinton and Cuevas [7].

The major advantage of a slowly decaying illumination is that a large range of operating points can be conveniently explored. Note that the covered range of carrier densities is typically about one order of magnitude (in this work typically ~  $10^{14}$  -  $10^{15}$ ). Obviously the first two regimes are special cases of the third, which therefore represents the general case.

The detailed analysis of the recombination dynamics in all three cases is based on the continuity equation for the excess minority carriers (Equation 2.22).

$$\frac{\partial \Delta n}{\partial t} = G_{bulk}(t,x) - U_{bulk}(t,x) + \frac{1}{q} \frac{dJ_n}{dx}$$

(2.22)

where  $G_{bulk}$  and  $U_{bulk}$  are the photogeneration rate and the recombination rate in the bulk,  $\Delta n$  the excess minority carrier density (usually  $\approx 10^{15}$  cm<sup>-3</sup> in this work) and  $J_n$  the electron current density. The transport term reduces to surface recombination terms when Equation 2.22 is integrated over the sample width, because the sample is in open-circuit conditions. A generalized analysis procedure has been proposed by Nagel et al. [8]. In order to define an effective lifetime regardless of the decay time of the illumination source, they combined the bulk and surface recombination rates into an effective recombination rate *Ueff* and found, considering all the terms in Equation 2.22, the following Equation 2.23 for the effective carrier lifetime.

$$\tau_{eff} = \frac{\Delta n_{av}}{G_{av}(t) - \frac{\partial \Delta n_{av}(t)}{\partial t}} \qquad (general \ case) \tag{2.23}$$

where  $n_{av}$  is the average excess carrier density and  $G_{av}$  the average generation rate, both calculated over the whole wafer thickness. In the extreme operating regimes, simplified  $\tau eff$  expressions follow directly from Equation 2.23.

In the first regime with G = 0:

$$\tau_{eff} = \frac{\Delta n_{av}}{\frac{\partial \Delta n_{av}(t)}{\partial t}} \qquad (quasi - transient \ case) \tag{2.24}$$

which is only valid when carrier lifetime is significantly higher than the decay time of the illumination source.

In the second regime with  $\partial \Delta n / \partial t = 0$ :

$$\tau_{eff} = \frac{\Delta n_{av}}{G_{av}(t)} \qquad (quasi - steady - state \ case) \tag{2.25}$$

which is only valid when the carrier lifetime is significantly lower than the decay time of the illumination source.

Thus, to determine the effective lifetime it is necessary to measure the time dependence of the excess carrier density and the generation rate within the test samples (except for the transient case). The excess carrier density can be directly monitored via the photoconductance, which can be measured inductively (*Quasi-Steady-State*)

#### 22 Chapter 2 - Recombination in Crystalline Silicon

*Photoconductance technique, QSSPC)* or by means of the reflectivity of microwaves (*Microwave-Detected Photoconductance Decay technique, MW-PCD*). Only the first one has been used in this work and it will be widely described.

A common feature of both techniques is that they are non-contacting, which makes them ideally suited for lifetime spectroscopic purposes, as partially finished devices that are free of metal contacts can be investigated, including the starting material itself, as in the present work.

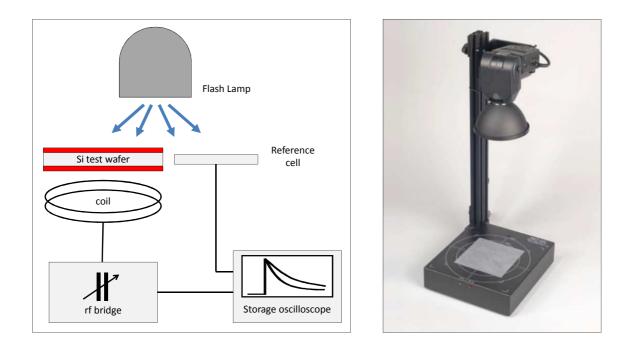

### 2.3.2 Quasi-Steady-State Photoconductance Technique (QSSPC)

The experimental apparatus used in the present work for QSSPC measurements was fabricated by *Sinton Consulting* [9] and is shown in Fig. 2.3a(Appendix B). A photographic flash lamp (Fig. 2.3b) is used as the generation source. The sample is inductively coupled by a coil to a radio-frequency bridge, which senses changes in the permeability of the sample and therefore its conductance. A reference solar cell and an oscilloscope are used to determine the time dependence of both the excess photoconductance of the test sample  $\Delta \sigma(t)$  and its illumination I(t) by using appropriate calibration functions. The average excess carrier density  $\Delta n_{av} = \Delta p_{av}$  in the test sample can be determined by Equation 2.26.

$$\Delta n_{av}(t) = \frac{\Delta \sigma(t)}{q(\mu_n + \mu_p)W}$$

(2.26)

where *W* is the sample thickness and  $\mu_n$  and  $\mu_p$  are the electron and hole mobilities. As  $\mu_n$  and  $\mu_p$  are themselves functions of the carrier density, the determination of  $\Delta n_{av}$  requires an iterative procedure on the basis of a carrier-density-dependent mobility model [10].

The illumination intensity  $I_{av}$ , measured from the calibrated reference solar cell and normally quoted in suns (1 sun = 1000 W/m<sup>2</sup>), is a measure of the number of photons

incident on the sample surface. As any real sample will only absorb a fraction  $f_{abs}$  of these available photons, the remainder being lost by reflection and transmission, the generation rate within the sample can be determined as Equation 2.27.

$$G_{av}(t) = \frac{I_{av}(t) f_{abs} N_{ph}^{1sun}}{W}$$

(2.27)

where  $N_{ph}^{1sun}$  is the flux of photons in solar light with an irradiance of 1 sun, which generate electron-hole pairs in the sample. As the required quantities in the general Equation 2.23 can thus be experimentally measured, a determination of the effective lifetime is possible.

Figure 2.3: (a) Schematic of the inductively coupled photoconductance apparatus used for measuring the effective lifetime. The picture also illustrate the particular sample under test: the Silicon wafer investigated has been coated on both sides with an identical dielectric film. (b) The Xenon photo flash lamp WCT-120 here used for QSSPC, fabricated by *Sinton Consulting* [9].

As the decay time of the flash lamp may be varied by two orders of magnitude, the QSSPC setup allows measurements in the *transient mode* (PCD) and in the *quasi-steady-state mode* (QSSPC). The typical PCD and QSSPC traces are displayed in Fig. 2.4a and 2.4b, respectively. In conjunction with the simplified analyses given in Equations 2.24 and 2.25, both modes are restricted to certain lifetime ranges. Being well suited for high lifetimes, the PCD mode is less accurate for low lifetimes (< 200  $\mu$ s) due to the poor cutoff time of the flash lamp. The QSSPC mode, on the contrary, is well suited for low lifetimes, but becomes increasingly invalid for high lifetimes (> 200  $\mu$ s), as the steady-state assumption starts to break down.

Figure 2.4: Typical traces measured by means of the inductively-coupled QSSPC system. (a) Traces in the transient mode showing the sharp illumination peak (*solid line*) and the ensuing photoconductance decay (*dashed line*). (b) Traces in the quasi-steady-state mode, showing the uniform decay of both signals.

However, using the QSSPC mode in conjunction with the generalized analysis given in Equation 2.23, it constitutes an excellent method for measuring a large range of carrier lifetimes (from 0.1  $\mu$ s to several ms) over a large range of carrier densities ( $10^{12}$ – $10^{17}$  cm<sup>-3</sup>, depending on the lifetime level). Thus, this technique is ideally suited for injection-

dependent lifetime measurements and has been used throughout this work. Details about the calibration of the coil and the reference solar cell may be found in [11].

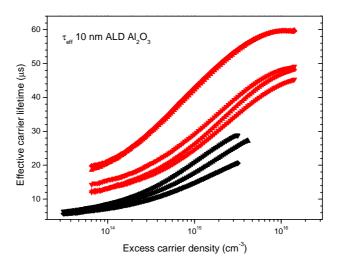

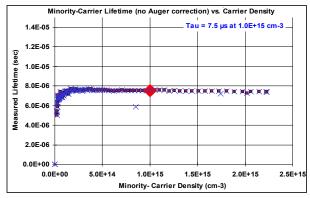

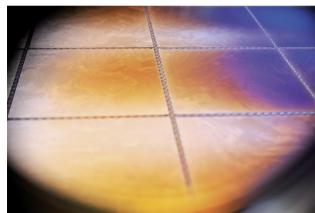

An example of one lifetime QSSPC measurement as a function of carrier density can be founded in Fig. 2.5. As mentioned in the presentation of this work, all the investigated samples have been made of solar grade material (CZ Silicon): this point is widely developed in Chap. 4. This means that the investigated samples may have a low level of uniformity: this can be seen in Fig. 2.5. Different curves (red dots) have been obtained only changing the stimulated area of the sample, indicating not uniform properties on the investigated area because of the low quality material used. Fig. 2.5 also indicates a clear lifetime degradation over time: the back dots correspond to measurements done ~ 2 months later than the red dots.

Figure 2.5: Example of injection-level-dependent effective lifetime measurements using QSSPC technique. The Silicon substrate was coated by 10 nm ALD  $Al_2O_3$ . (i) Red dots have been measured stimulating different points on the passivated surface: the dispersion indicate the not perfect uniformity of the sample. (ii) The black dots have been measured on the same saple after ~ 2 months: the degradation is evident.

# **Chapter 2 References**

- M. J. Kerr, "Surface, Emitter and Bulk Recombination in Silicon and Development of Silicon Nitride Passivated Solar Cells", PhD thesis, The Australian National University (June 2002).

- [2] Richard S. Muller and Theodore I. Kamins, "Device Electronics for Integrated Circuits" (Third Edition), Wiley (2003), pp. 228-238.

- [3] W. Shockley and W.T. Read, "Statistics of the recombinations of holes and electrons", Physical Review, 87:835–842 (1952).

- [4] R.N. Hall, "*Electron-hole recombination in germanium*", Physical Review, 87:387 (1952).

- [5] E. Cornagliotti, "Analysis and Modelling of Recombination Sources in Crystalline Silicon Solar Cells with Rear Side Local Contacts", PhD thesis, University of Leuven (September 2011).

- [6] T. Roth, "Analysis of Electrically Active Defects in Silicon for Solar Cells", PhD thesis, University of Konstanz, October, 2008.

- [7] R.A. Sinton and A. Cuevas, "Contactless determination of current-voltage characteristics and minority-carrier lifetimes in semiconductors from quasi-steadystate photoconductance data", Appl. Phys. Lett. 69 (17), 2510–2 (1996).

- [8] H. Nagel, C. Berge, and A.G. Aberle, "Generalized analysis of quasi-steadystate and quasi-transient measurements of carrier lifetimes in semiconductors", J. Appl. Phys. 86 (11), 6218–21 (1999).

- [9] <u>http://www.sintoninstruments.com/</u>, last access date 10/06/2012.

- [10] F. Dannhäuser, "The dependence of carrier mobility in Si on the concentration of free charge carriers", Solid-State Electron. 15 (12), 1371–5 (1972).

- [11] R. Mühlhaupt, "Messung der Ladungsträgerlebensdauer in Silizium für die Prozessoptimierung bei der Herstellung von Solarzellen", Diplomarbeit, Fachhochschule Furtwangen (2004).

28 | Chapter 2 - Recombination in Crystalline Silicon

# Chapter 3 High-k Material Deposition Techniques

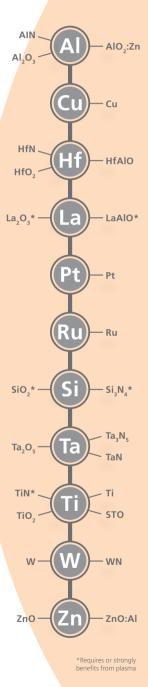

In this work, high-k materials are characterized as negatively charged passivation layer for p-type Silicon. Therefore, in this chapter some relevant deposition techniques are discussed first. (i) *Atomic Layer Deposition* (ALD) presents (a) excellent uniformity and growth control, and (b) high trimethylaluminum (TMA, Al(CH<sub>3</sub>)<sub>3</sub>) efficiency. Other deposition techniques here discussed are (ii) *Plasma-Enhanced* (PE) *or Plasma-Assisted* (PA) *ALD*, (iii) *Chemical Vapor Deposition* (CVD) and (iv) *Plasma Enhanced Chemical Vapor Deposition* (PECVD).

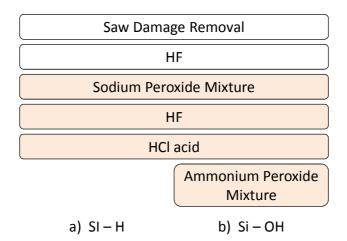

## 3.1 Wafer Cleaning

Prior to starting with any deposition of the passivation layer, advanced cleaning treatment of Silicon surface is required in order to decrease the level of impurities and obtain a sufficient cleanliness of the surface. This chemical process can leave an oxidized Silicon OH- surface (*Hydrophilic surface*) or an HF last Silicon H- surface (*Hydrophobic surface*). The wafer investigated have been cleaned using a technique similar to the *RCA clean standard*, the procedure developed in 1965 by Werner Kern while working for *Radio Corporation of America* [1, 2].

### 30 Chapter 3 - High-k Material Deposition Techniques

Passivation layers investigated have been deposited on p-type Czochralski (CZ) Silicon substrates with a resistivity of 1 - 1.5  $\Omega$ ·cm and a thickness of 180 µm. They first endure a Saw Damage Removal (SDR) to reduce damages after the sawing of an ingot. This etching process has two steps: (i) a dip in NaOH : H<sub>2</sub>O (5 minutes at 85 °C) and (ii) neutralization in HCl : H<sub>2</sub>O (10 minutes at 85 °C). Between SDR and cleaning, the wafers are then dipped into a Hydrofluoric acid (HF) and water solution for 10 seconds (the HF concentration is about 2%) to remove mostly the organic impurities on the surface. This HF dip is a characteristic step of IMEC process and is not mentioned in the standard procedure (RCA). Afterwards, the samples are soaked in a Sulfuric Peroxide Mixture (SPM), H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>SO<sub>4</sub> 1:4, for 10 minutes at 85°C. This treatment results in the formation of a thin Silicon dioxide layer on the Silicon surface that traps metallic contaminants on the wafers' surface. Finally, this dioxide layer is removed with a final dip in HF water solution (2%) and HCl water solution (5%). Now the surface of each wafer is H- terminated and presents a lower level of roughness and contamination. OH- terminations on the surface require an additional step: Ammonium Peroxide Mixture (APM, NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O 1:1:5) allows the formation of these OH groups on the wafer.

Figure 3.1: Surface cleaning sequences of p-Silicon wafers. Prior the as-known *standard cleaning* (red cells), a polishing process and an additional HF dip have been done (white cells). After the last dip in Hydrochloric acid, the surface is H- terminated (a). An additional cleaning step (APM) is required to have OH- terminations on the surface (b).

# **3.2 Drying Techniques**

After the cleaning, a drying process of the surface is needed. There are several techniques available: the samples here investigated have been dried using a *Marangoni dryer*. This is an expensive and time consuming technique (compared to others, e.g. *hot-air*) but it has been used since a low level of impurities on the surface is required.

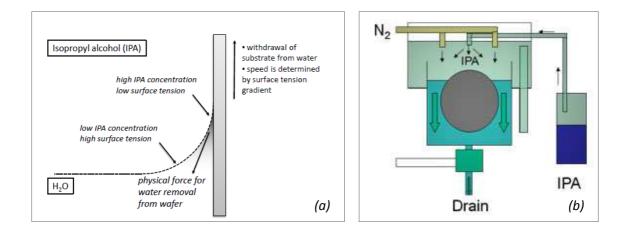

The substrates are introduced in a tank filled with water. An alcohol vapor (*Isopropyl alcohol*, IPA) is vaporized using heated  $H_2$  through nozzles over the wet wafer surface. The Marangoni effect is introduced by a surface-tension gradient in the wetting film (IPA:H<sub>2</sub>O) on the substrate, causing the water film quickly drain backwards into the rinse bath. As a result, a completely dry substrate emerges from the bath [3]. For a schematic representation, see Figure 3.2.

Figure 3.2: The Marangoni Effect as drying technique (a): It is based on surface tension gradient forces after the deposition of IPA on the wet surface. (b) Cross section of a dryer tool (*Accudry* by IMTEC, [4] and Appendix C). All the mentioned parts are well visible: IPA tank and the noozles to create the  $N_2$  - alcoholic vapor inside the chamber, the water tank containing the wafers and the drain system to decrease the water level. The tension gradient forces make the surface out of water dry: the process ends when the water tank is empty.

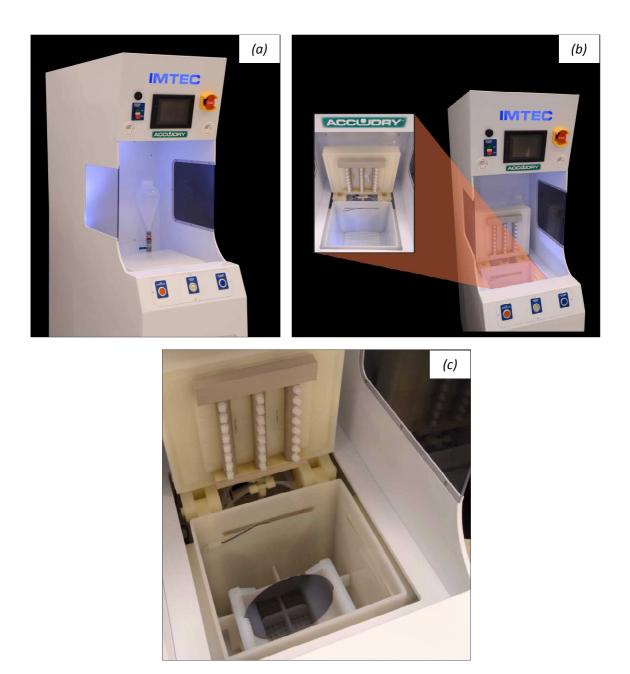

Figure 3.3: *Accudry*, dryer tool based on Marangoni effect, by *IMTEC* [4] (a). This tool can rapidly displace water from the wafer surface (inside the process chamber, (b)) until it is completely dry. This yields substrates that are watermark-free with extremely lowparticle counts and zero feature damage. The drying process is controlled by the level of water in the tank (c): it signifies no moving parts or mechanical stress on the wafers, meaning no costly breakage or damage.

# 3.3 Deposition Techniques

The deposition of dielectric layer is a crucial point: the quality of the material deposited and the interface region on the wafer play a fundamental role. Some of the most common deposition techniques are discussed below, focusing on the ones used in the samples preparation (Thermal ALD and PECVD).

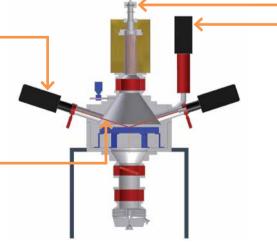

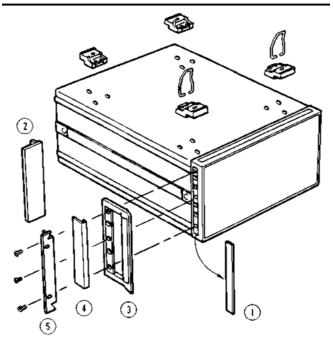

Figure 3.4: Cross section of a typical ALD reactor. The picture illustrates and distinguishes the main components of this deposition tool.

## 3.3.1 Thermal ALD

Thermal ALD is an accurate technique, because of its excellent uniformity and growth control allowing conformal films to be deposited on very high aspect ratio structures. ALD is based on sequential, self-limiting surface chemical reactions involving two vapor phase reactive chemical species, typically a metal-organic precursor and a co-reactant.

### 34 Chapter 3 - High-k Material Deposition Techniques

During the process, the wafer to coat is inside a high-vacuum chamber, where the reactants are injected continuously at pressure and temperature controlled. The film grows at a rate determined by the velocity of the reactions involved and by the time needed to bring reactants at the surface: both these parameters are linked to the pressure and the temperature. This means the desired thickness depends mostly on the velocity and on the time of the deposition. However, controlling the velocity of the reactions is not easy and limitations in resolution of the thickness can occur.

Very thin layers can be grown by Thermal ALD, depositing one single atomic layer per time: this signifies the thickness of the film can be determined by the number of cycles performed.

### 3.3.1.1 ALD Reactor

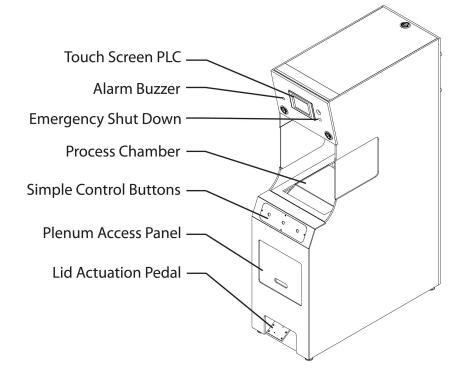

Fig. 3.4 depicts the typical cross section of an ALD reactor:

- a) Two separated chambers contain liquid state precursors at controlled temperature.

- b) Both chambers are separated from the reaction chamber by high pressure valves. The valves have also to guarantee high velocity opening/closing and they are controlled electronically.

- *c)* The wafer to coat is set at the center of the deposition chamber on a support sometimes heated. The volume of the chamber is as small as possible in order to reduce the time to make the vacuum and the gas quantity needed.

- *d)* Gases are injected and expelled through a pump system to maximize the velocity and the efficiency of the process. To maintain a steady pressure during the process it is necessary that the pumps injecting gases and pumps expelling this work at the same rate: an automatic control system is needed to keep constant the gas flow.

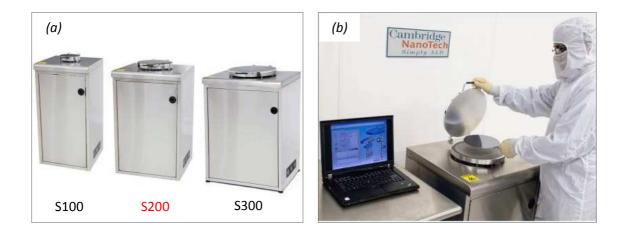

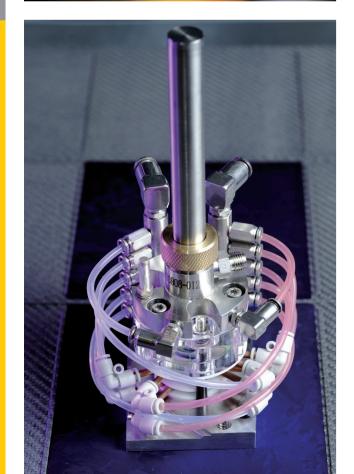

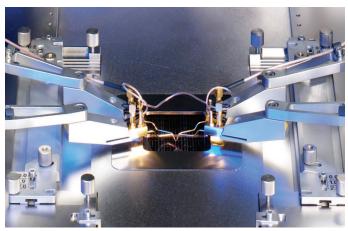

The samples investigated in this work have been built from wafers coated by *Savannah S200*, ALD reactor of Nanotech Cambridge ([5], Appendix D), Fig. 3.5.

Figure 3.5: *Cambridge NanoTech* is considered one of the leading providers of ALD solutions for research and industry worldwide [5]. The tool used comes from the *Savannah Series* (a): S200 allows the deposition on wafers with a a diameter up to 200 mm. The tool is compact (b) and the complete control of all key system parameters is easily achievable through the dedicated Graphical User Interface (c).

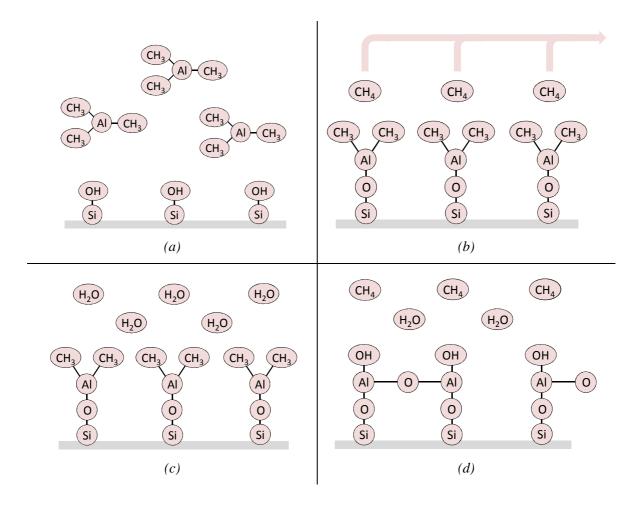

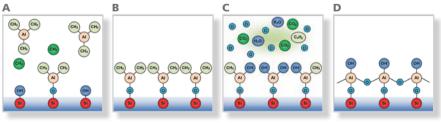

After describing the ALD reactor, the chemical reactions involved during the deposition of Aluminum Oxide ( $Al_2O_3$ ) are here illustrated. The process takes place over a p-type Silicon substrate, with OH- groups on its surface after the cleaning process (*Hydrophilic* surface). Each deposition cycle can be divided into four different steps (Fig. 3.6) [6].

Figure 3.6: (a) to (d) Schematic diagram of one cycle of atomic layer deposition of  $Al_2O_3$  using sequential saturation exposures of TMA and  $H_2O$ , separated by inert gas purging steps. After the full cycle, the starting hydroxylated surface is reproduced, allowing the cycle to be repeated to build up a coating with near monolayer precision.

- *a)* Injection of TrimethylAluminum, Al(CH<sub>3</sub>)<sub>3</sub>, in the reaction chamber.

- b) A reaction involving TrimethylAluminum and the surface of the wafer takes place: the precursor chemically reacts and bonds to the surface without fully decomposing. The precursor also changes the dominant surface termination, leaving the surface ready to react with the co-reactant.

AlOH + Al(CH<sub>3</sub>)<sub>3</sub>

$$\rightarrow$$

AlOAl(CH<sub>3</sub>)<sub>2</sub> + CH<sub>4</sub>

The reaction is self-limited by the disponibility of free OH- groups on the surface: when all the OH- groups have been saturated, the reaction stops, also if there is still exceeding gas inside the chamber. The remaining vapor products are pumped or pushed out of the deposition zone using inert gas flow.

c) Water vapor  $(H_2O)$  is injected in the reactor. A reaction with  $CH_3$ -groups starts:

$$2Al(CH_3)_3 + 3H_2O \rightarrow Al_2O_3 + 6CH_4$$

Also in this step the reaction is self limited by the presence of CH<sub>3</sub>-groups.

*d)* The vapor products are flushed out. The starting hydroxylated surface is reproduced and the "ALD cycle" can start over again.

The characteristic feature of an ALD process is that the half-reactions are self-limiting. Once the precursor has reacted with sites prepared during the previous co-reactant exposure, the surface reaction stops: that is, the surface sites prepared by the precursor reaction are reactive to the co-reactant, but not the precursor itself. This means that during steady-state growth, the precursor will typically deposit at most only one monolayer during each half-reaction cycle, even when the surface is exposed to the reactant species for long periods of time. One must ensure that enough precursor is delivered to achieve full

### 38 Chapter 3 - High-k Material Deposition Techniques

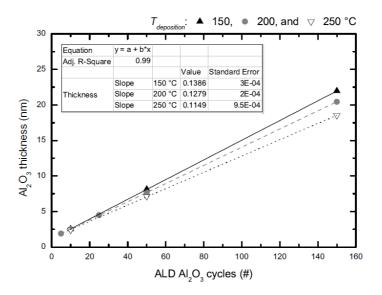

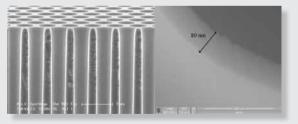

saturation, otherwise, growth will be non-ideal and non-uniform [7]. Therefore, each reaction  $Al_2O_3$  cycle adds a given amount of material to the surface, referred to as the growth per cycle (GPC), which depends on the deposition temperature. Figure 3.7 shows the  $Al_2O_3$  layer thickness on hydroxylated Silicon as a function of the amount of ALD cycles for deposition temperatures of 150, 200 or 250 °C. This graph clearly shows the self-limiting facet of ALD: for hydroxylated Silicon samples a GPC of 1.1 to 1.4 Å per cycle, depending on the deposition temperature, is calculated. In this work, ALD  $Al_2O_3$  films have been deposited at 200 °C.

Figure 3.7: Thickness of  $Al_2O_3$  layers deposited as described above on hydroxylated Silicon wafers as a function of the number of ALD cycles for deposition temperatures of 150, 200 or 250 °C. Also the linear fits are shown. From its slope the growth per cycle can be calculated.

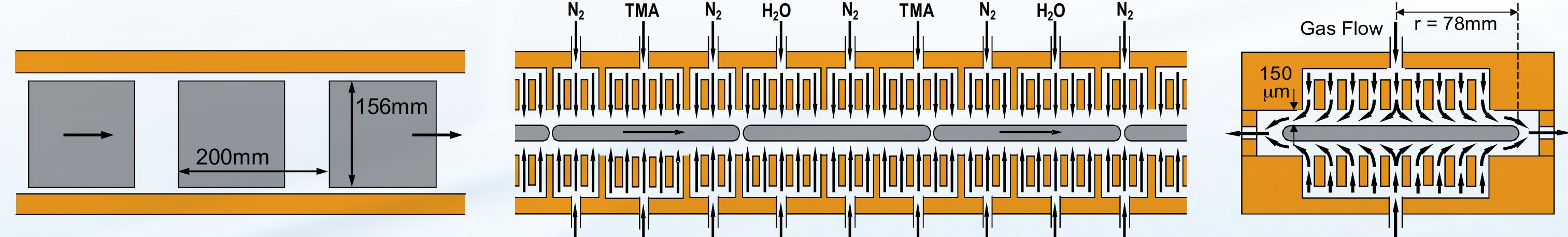

The process described above is a typical temporal ALD cycle since the samples are placed in a reaction chamber and the half cycles are separated by purge steps. Uniform ultrathin layers can be manufactured using temporal ALD, however, conventional time-resolved ALD is limited by a low deposition rate (~  $0.2 \text{ nm min}^{-1}$ ).

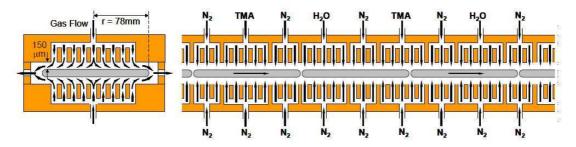

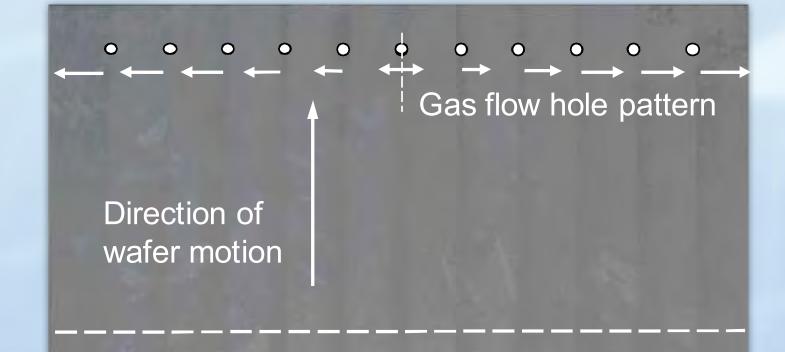

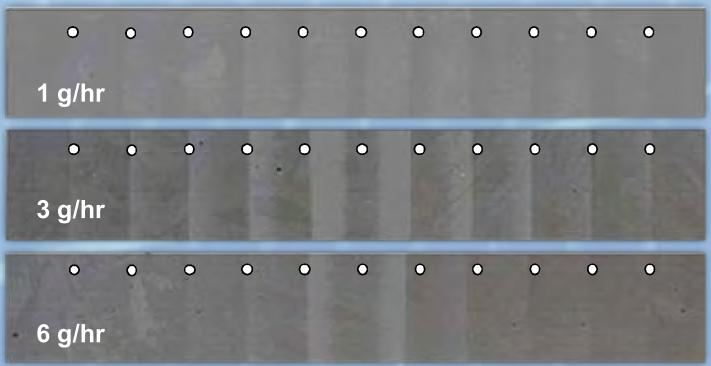

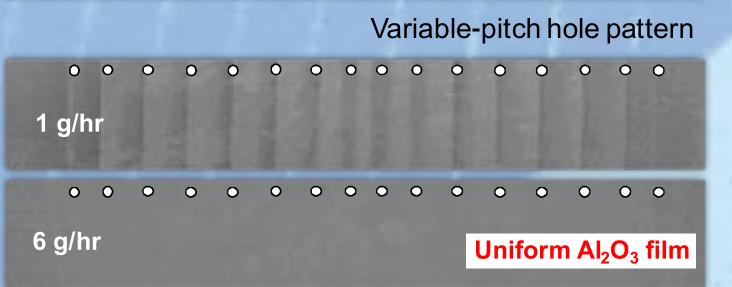

Instead of temporal separation, the ultra-fast ALD concept is based on the spatial separation of the half-reaction: such reactor has separate zones exposing the precursor one by one to a

substrate that floats underneath the reactor [8]. Fig. 3.8 displays a schematic overview of a reactor for the spatial resolved ALD deposition of  $Al_2O_3$  [9].

Figure 3.8: Schematic overview of the Levitrack<sup>®</sup> ALD system [10] for ultra-fast deposition of Al<sub>2</sub>O<sub>3</sub> passivation layers (Appendix E).

It can be seen that the wafers pass regions in which the front of the wafer surface is successively exposed to  $Al(CH_3)_3$  (TMA), N<sub>2</sub>, H<sub>2</sub>O and N<sub>2</sub>. In this arrangement the flow of precursors is constant in time, being the wafer the only object in the track that moves. In this way very high deposition rates are achieved, while maintaining the required high film quality. This concept allows (i) single side, (ii) in-line, and (iii) atmospheric pressure deposition, and (iv) a deposition speed well above 1 nm/s. Commercial ultra-fast setups with a throughput of 1 wafer min<sup>-1</sup> (10 nm) are available, meeting the cost-efficiency and throughput demands of the PV market [10, 11].

### 3.3.1.2 Temperature and Pressure choice

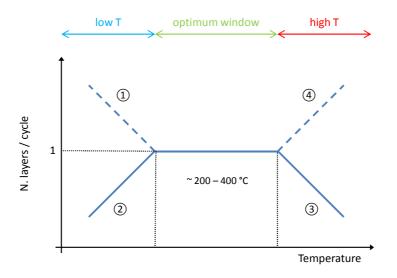

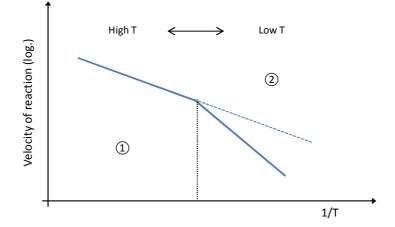

The pressure inside the reactor has to be chose carefully in order to keep the precursors steady and volatile at the deposition temperature. To achieve ALD growth, the temperature must be held within 200-400 °C: out of this *ALD window* the reaction doesn't work properly (Fig. 3.9).

a) If the temperature is too low (< 200 °C), condensation of the gas on the substrate could be observed, and more than one layer per cycle will be grown (1). In this

temperature condition it is also possible an incomplete reaction, because of its slowness (2): less than one layer per cycle will be obtained in this way.

b) If the temperature is too high (> 400 °C), it is possible that the bonding ready formed will be broken: this means the evaporation of the deposed layer. In this way (3), the grown layer looks uncompleted (less than 1 layer per cycle). Another unexpected effect can occur at too high temperatures (4): the gas molecules are broken starting off undesirable reactions with the substrate (more than one layer grown per cycle).

Figure 3.9: Schematic representation of the *ALD window*. To achieve ALD growth, the temperature must be held low enough so that the precursor does not decompose during surface adsorption, but the temperature must be high enough to thermally activate the reaction and/or avoid surface condensation.

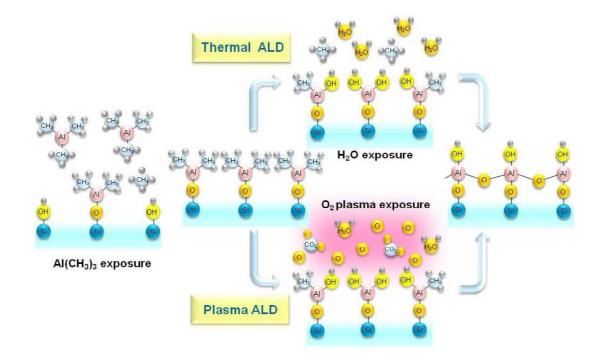

### 3.3.2 PEALD

In the Plasma-Enhanced ALD (PEALD) process, an oxygen plasma is ignited above the substrate, generating oxygen radicals which effectively react with the methyl groups and

the Aluminium at the surface, as illustrated in Fig. 3.9. All the considerations below have been obtained by a *remote* approach: an inductively coupled plasma (ICP) source is used, which means that the oxygen plasma is not in direct contact with the Silicon wafer during  $Al_2O_3$  deposition. This type of remote-plasma deposition technique is known to create almost no plasma damage at the surface, and is hence well suited for an excellent Silicon surface passivation [12].

Figure 3.10: Schematic of one cycle of a thermal and a plasma-assisted ALD process. Each cycle consists of two half-steps: first, the TrimethylAluminum (TMA) molecules attach to the hydroxyl groups attached to the Silicon surface; second, the molecules are oxidized by  $H_2O$  (thermal ALD) or an  $O_2$  plasma (plasma ALD).

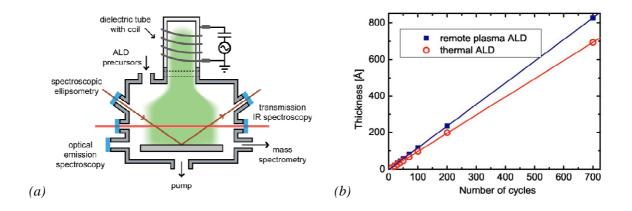

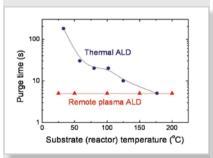

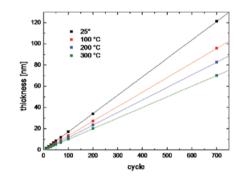

As expected, the thickness increases linearly with the number of completed cycles also for the remote plasma ALD process. J. L. Hemmel et al. have observed (using the *Oxford Instruments FlexAL* reactor, Fig. 3.11.a and Appendix F) from in situ thickness measurements, that the growth per cycle is higher for remote plasma ALD than for thermal

### 42 Chapter 3 - High-k Material Deposition Techniques

ALD (in the same Pressure/Temperature conditions): i.e., 1.2 Å/cycle for remote plasma ALD and 1.0 Å/cycle for thermal ALD (Fig. 3.11.b) [13]. Thus, the mass densities of the remote plasma ALD films are slightly higher than those of the thermally deposited films. Also, plasma ALD yields fair material properties at low deposition temperatures (substrate heated at a temperature below 100°C) at a relatively high growth per cycle and short cycle times [13].

Figure 3.11: (a) Schematic cross section of a (remote) Plasma Enhanced ALD reactor (*Oxford Instruments FlexAL* reactor) [14]. The picture also depicts the different diagnostics implemented in situ (ellipsometer, spectroscopy) to obtain fundamental understanding of the reaction mechanism of plasma-assisted ALD. (b) Al<sub>2</sub>O<sub>3</sub> film thickness as a function of the number of cycles for both remote plasma ALD and thermal ALD [13]. The thickness has been determined by in situ spectroscopic ellipsometry and the growth per cycle was obtained from the linear fits shown in the figure. The substrate temperature was 200°C.

### 3.3.3 CVD

Chemical Vapor Deposition (CVD) is a deposition technique allowing the formation of a high quality/purity film through the reaction on one or more gas species on the surface of a substrate. Usually the material to coat is kept on a base inside the deposition chamber and it is exposed to one or more gases containing the material to deposit. Precursors react with the

surface forming a solid layer and some volatile products later on are expelled from the chamber. Depending on the material grown and the reactions involved, typical process temperatures are within 300-900 °C.

Figure 3.12: Cross section of a typical CVD tool. The picture depicts the most relevant phases during the deposition process.

CVD follows three main steps (Fig 3.11):

- The material to be deposited is put inside the reactor throw one or two gaseous compounds.

- Precursors react with the surface forming a thin and uniform film, plus eventual volatile residuals.

- Residual materials are expelled out from the reactor, otherwise a residual layer would form blocking the reaction.

The growth rate depends on two factors: the *velocity of the reaction* and the *concentration of precursor gases* near the surface. Optimizing the process, the temperature is a fundamental parameter. In general it can be observed (Fig. 3.13) that increasing this parameter (1), an higher level of thermal agitation of the molecules is obtained and the transport of the reactants is improved. However, if the temperature is too low (2), a new limitation linked to the reaction efficiency occurs. In general, depending on the

### 44 Chapter 3 - High-k Material Deposition Techniques

temperature, the bottle neck will be the slowest process: the deposition takes place at high temperatures, a good draining system for unreacted products is required.

Figure 3.13: The graph illustrates the limit of the velocity of reaction (logarithmic scale) as function of the temperature. The growth process depends on two factors: (1) the transport of the reactants, more relevant at high temperatures and (2) the surface velocity of reaction, significant at low temperatures.

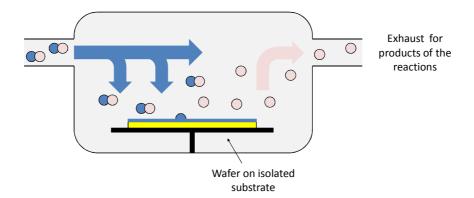

### 3.3.4 PECVD

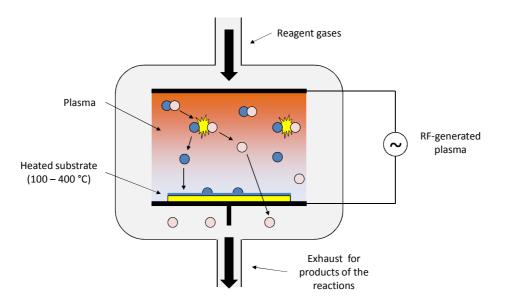

Plasma Enhanced CVD is a variant of CVD using a ionized gas (plasma) in order to improve the reactivity of the precursors and then the efficiency of the process. The plasma is typically generated with a RF electromagnetic field (order of MHz) between two plan electrodes. The substrate (typically OH- terminated) is set on the lower electrode and heated at relatively low temperatures (100-400  $^{\circ}$ C).

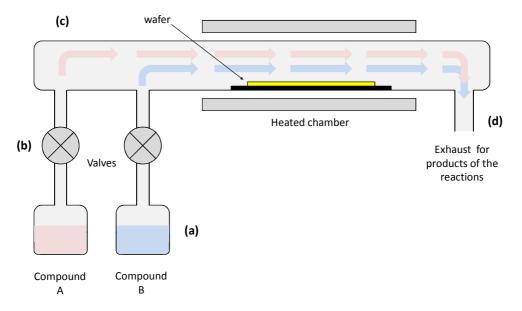

The reagent gases are injected from the top and the reagent species are activated by the plasma between the electrodes. The residual gases and the products of the reactions are removed from the bottom. The pressure in the chamber can vary from few microbar up to few millibar (Fig. 3.13).

Since the electric field is orthogonal to the wafer, the surface of the substrate is subjected to an intense ionic bombardment. Ions can be either *reactive* (interacting with the substrate forming the film) or *inert*. If the second case occurs, the bombardment with inert ions will increase the temperature at the surface making the reaction more efficient. In both cases, the growth of the film occurs mostly on the horizontal surfaces of the wafer, rather than on the vertical ones.

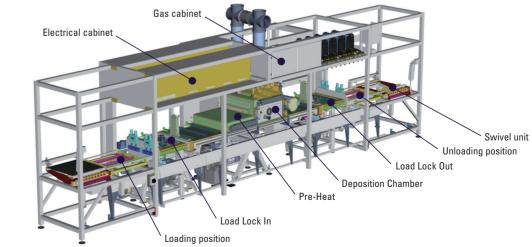

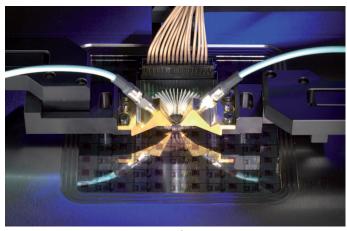

PECVD is already frequently used in industrial Silicon PV to deposit a front surface antireflection coating of PECVD hydrogenated amorphous Silicon Nitride (a-SiNx:H). Hence, PECVD has already been demonstrated as a low-cost and industrially relevant technique. The most frequently used in-line PECVD  $Al_2O_3$  layer has been developed by *Roth&Rau* (Appendix G). The microwave-remote plasma is created by 2.45 GHz microwave pulses, which are introduced to the reaction chamber via a linear antenna. The chamber pressure and deposition temperature are in the range of respectively 0.15 mbar and 300 °C. As reactants, a mixture of nitrous oxide (N<sub>2</sub>O), TMA and argon (Ar) is applied [15, 16].

Figure 3.13: Cross section of a typical PECVD tool. The picture depicts the most relevant phases during the deposition process.

46 Chapter 3 - High-k Material Deposition Techniques

# **Chapter 3 References**

- [1] W. Kern and D. Puotinen, "*Cleaning solutions based on hydrogen peroxide for use in silicon semiconductor technology*", RCA Rev. **31**:187-206 (1970).

- Werner Kern, "The *Evolution of Silicon Wafer Cleaning Technology*", Lam

Research Corporation, Advanced Research Center, San Diego, California 92126.

- [3] A.F.M. Leenaars, J.A.M. Huethorst and J.J. van Oekel, "Marangoni drying: a new extremely clean drying process", Langmuir, **6**:1701–1703 (1990).

- [4] <u>http://www.imtecacculine.com</u>, last access date 21/06/2012.

- [5] <u>http://www.cambridgenanotech.com</u>, last access date 20/06/2012.

- [6] G. Agostinelli, A. Delabie, P. Vitanov, Z. Alexiev, H.F.W. Dekkers, S. De Wolf and G. Beaucarn, "Very low surface recombination velocities on p-type silicon wafers passivated with a dielectric with fixed negative charge", Solar Energy Materials & Solar Cells, pp. 903438–3443 (2006).

- [7] G.N. Parsons, S.M. George and M. Knez, "Progress and future directions for atomic layer deposition and ALD-based chemistry", MRS Bulletin, 36:865–871 (2011).

- [8] P.Poodt, A. Lankhorst, F. Roozeboom, F. Spee, K. Maas and D. Vermeer, "Ulter fast atomic layer deposition of aluminum oxide layers for solar cell passivation", Advanced Materials, Vol. 22, pp. 3564-3567 (2010).

- K. Vanormelingen, P. Vermont, V. Kuznetsov, M. Ernst and B. Vermang,

*"Industrial PERC cells with efficiencies up to 18.5% using a spatial ALD Al2O3 passivation layer"*, proceedings of the 27<sup>th</sup> EUPVSEC, Frankfurt (Germany), 24-28 September 2012.

- [10] <u>http://www.levitech.nl</u>, last access date 16/06/2012.

- [11] <u>http://www.solaytec.org</u>, last access date 18/06/2012.

- [12] J. Schmidt, F. Werner, B. Veith, D. Zielke, R. Bock, V. Tiba, P. Poodt, F. Roozeboom, A. Li, A. Cuevas and R. Brendel, "Industrially Relevant Al<sub>2</sub>O<sub>3</sub> Deposition Techniques for The Surface Passivation of Si Solar Cells", 25<sup>th</sup> European Photovoltaic Solar Energy Conference, Valencia, Spain, 6-10 September 2009.

- J. L. van Hemmen, S. B. S. Heil, J. H. Klootwijk, F. Roozeboom, C. J. Hodson,

M. C. M. van de Sanden and W. M. M. Kessels, "*Plasma and Thermal ALD of Al<sub>2</sub>O<sub>3</sub> in a Commercial 200 mm ALD Reactor*", Journal of The Electrochemical Society, **154**, 7, G165-G169 (2007).

- [14] http://<u>www.oxfordplasma.de</u>, last access date 20/06/2012.

- [15] P. Saint-Cast, D. Kania, M. Hofmann, J. Benick, J. Rentsch, and R. Preu, "Very low surface recombination velocity on p-type c-Si by high-rate plasma-deposited aluminum oxide", Applied Physics Letters, 95:151502 (2009).

- 48 Chapter 3 High-k Material Deposition Techniques

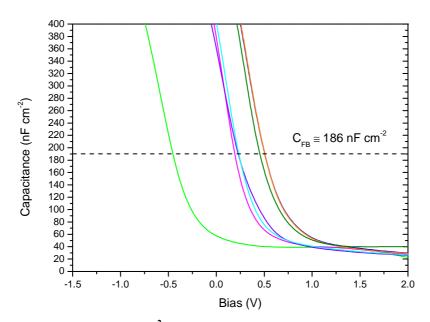

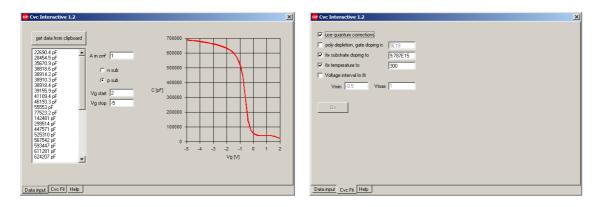

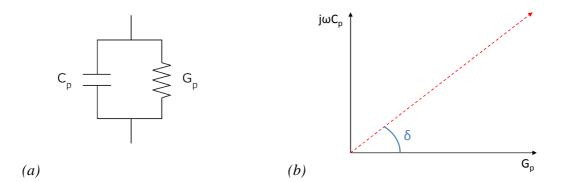

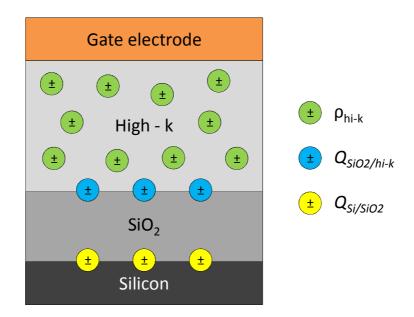

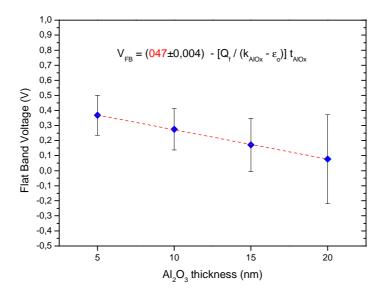

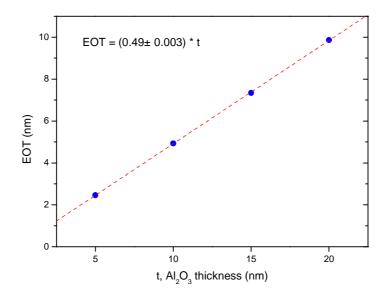

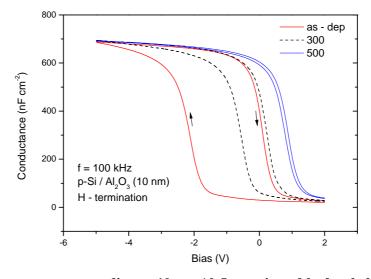

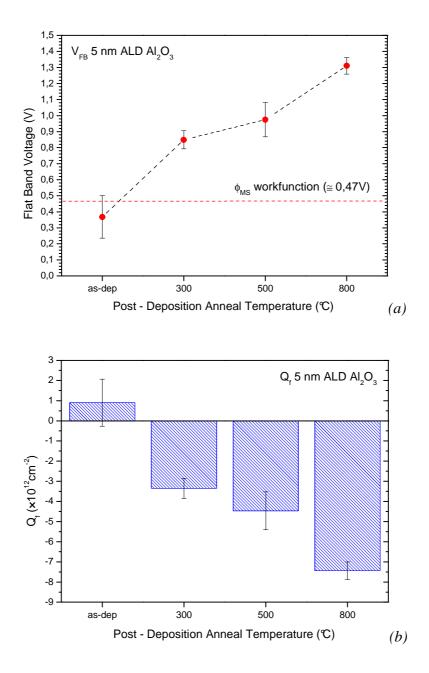

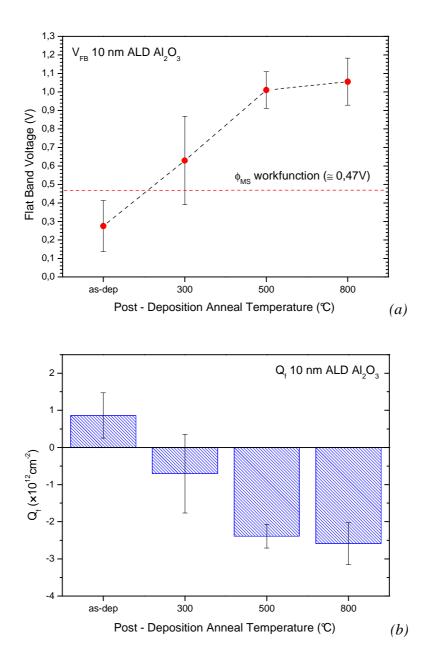

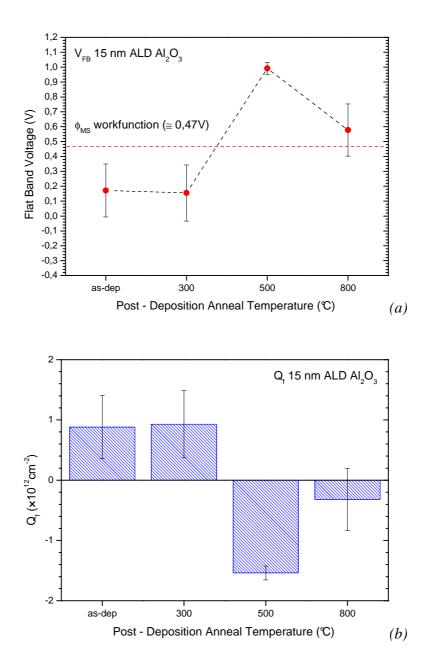

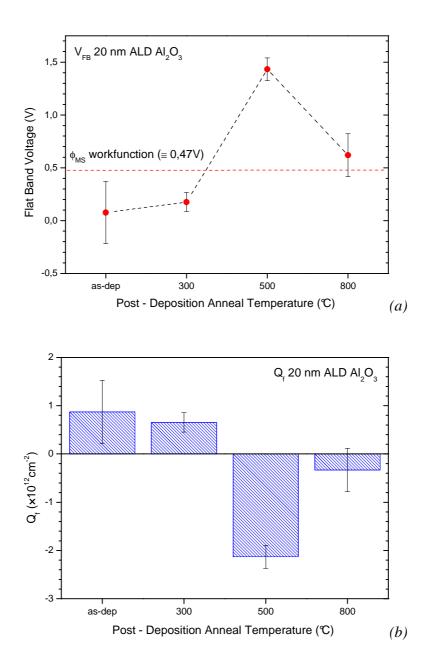

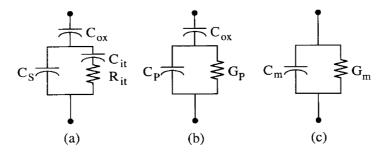

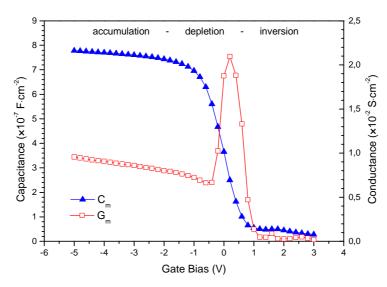

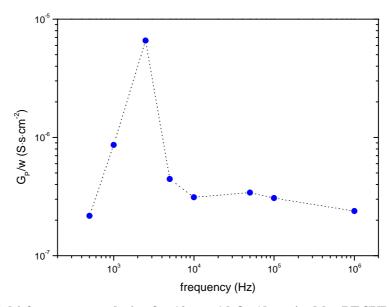

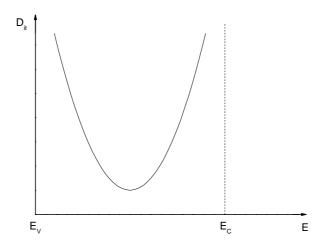

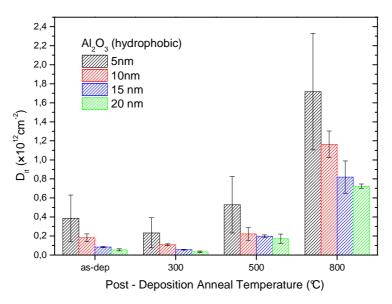

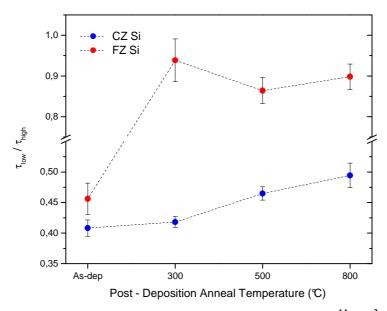

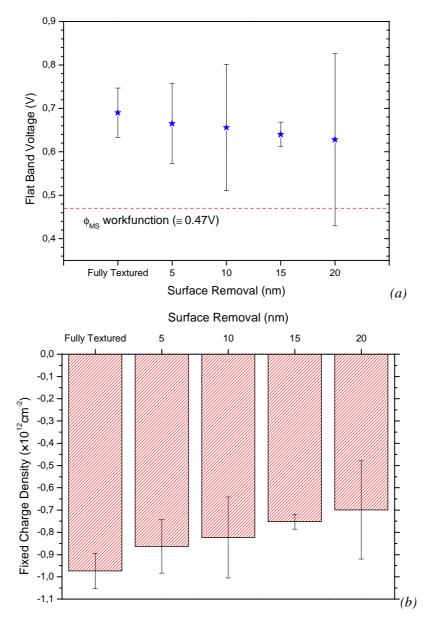

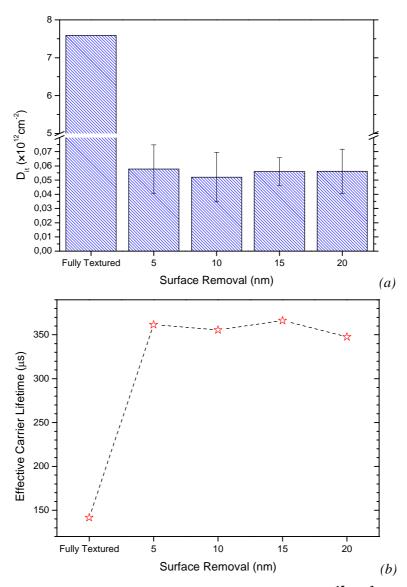

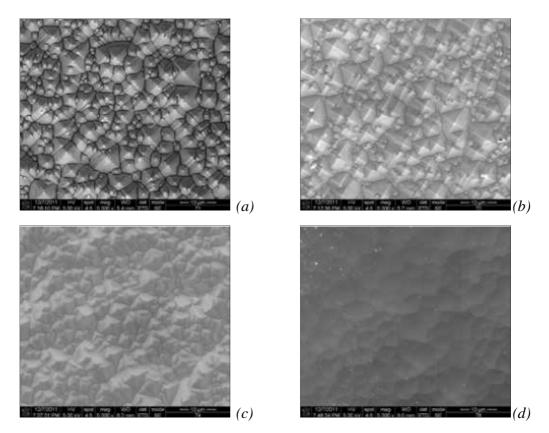

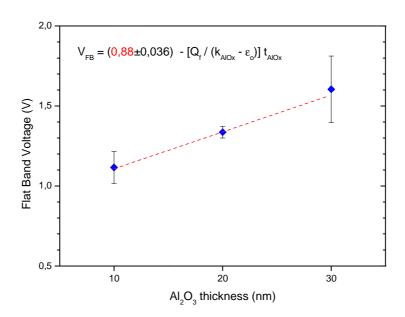

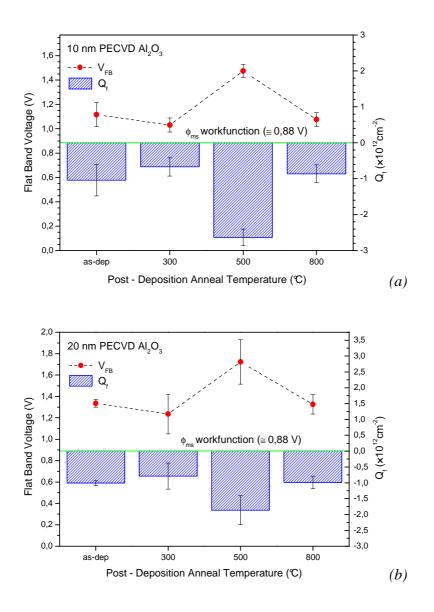

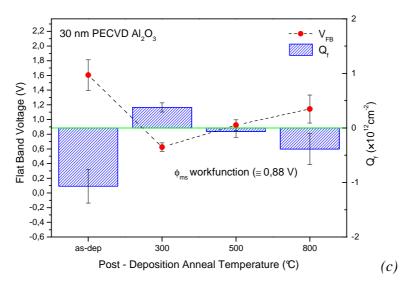

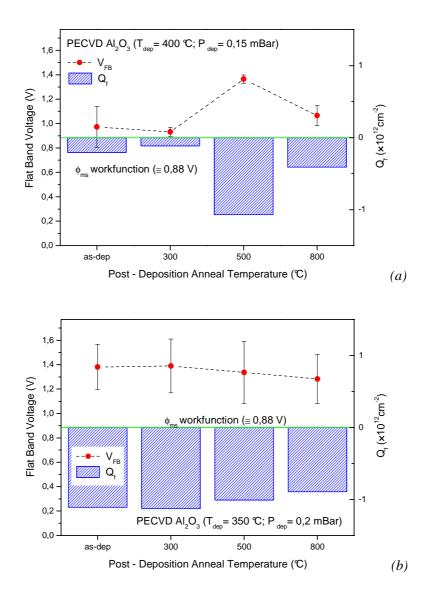

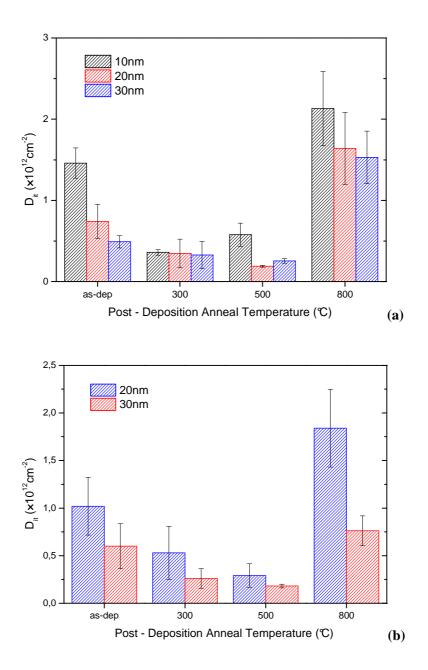

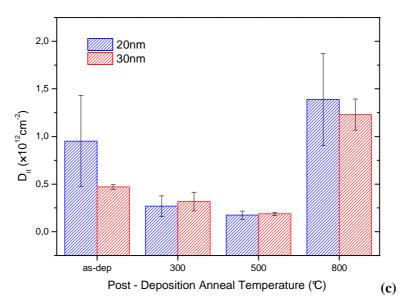

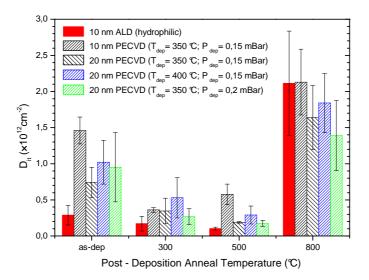

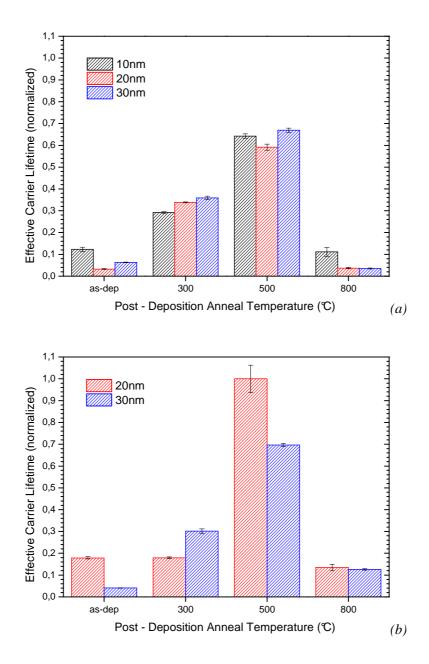

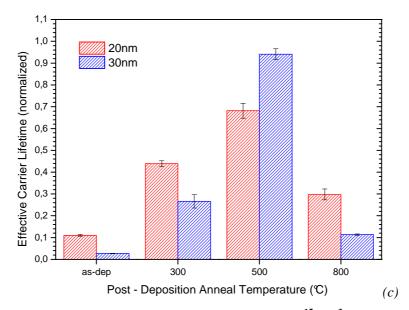

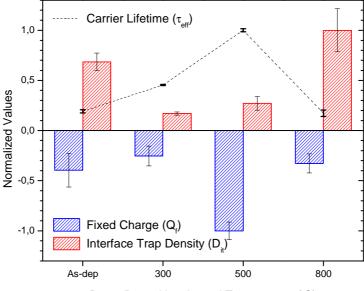

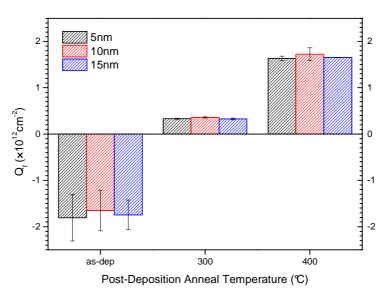

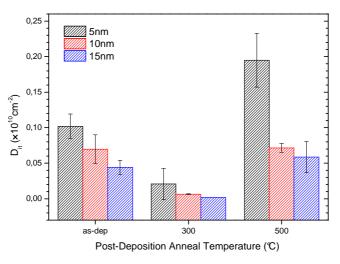

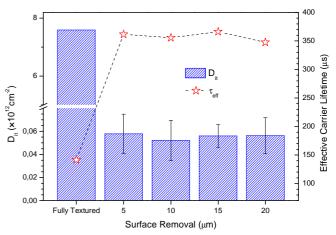

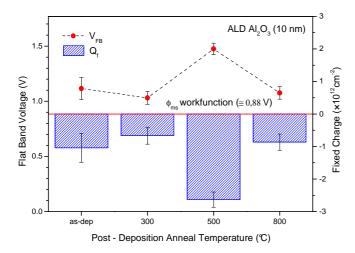

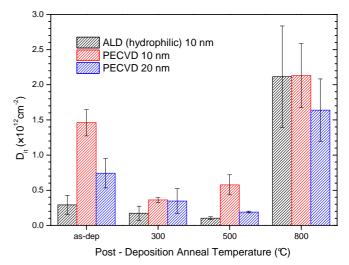

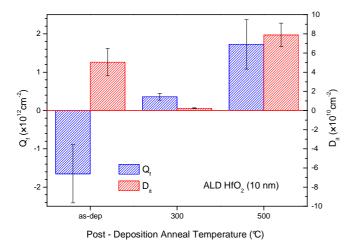

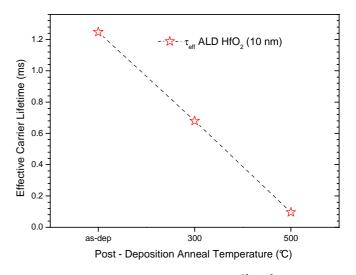

- [16] W.M.M. Kessels, B. Hoex and M.C.M. van de Sanden, "Atomic layer deposition prospects for solar cell manufacturing", 33<sup>rd</sup> IEEE Photovoltaic Specialists Conference, San Diego, California, USA, 11-16 May 2008.