### Universitá degli Studi di Padova

Corso di laurea in Ingegneria Elettronica

#### Master Thesis

# Design of a Monostable for the controller of an innovative Buck regulator

Relatore:

Ch.mo Prof. Andrea BEVILACQUA (Universitá degli studi di Padova)

Co-relatori:

Dr. Ralf Brederlow (Texas Instruments Deutschland GmbH)

Prof. Dr. Doris SCHMITT-LANDSIEDEL (Technische Universität München)

Laureando: Nicola RASERA

# Declaration of Authorship

I, Nicola Rasera, declare that this thesis titled, 'Design of a Monostable for the controller of an innovative Buck regulator' and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

May 4th 2014, Nicola Rasera

"As far as the laws of mathematics refer to reality, they are not certain, as far as they are certain, they do not refer to reality."

Albert Einstein

### Abstract

In the last decades the spread of portable devices has carried electronic circuits to a higher level of challenges. In fact these products are continuously demanding for higher performances together with the longest possible battery life, that results in a low power consumption.

Texas Instruments MSP430 is a 32-bit micro controller capable of assuring a very low power consumption concurrently with high performances and for these qualities is one of the most used MCU. Its power management module (PMM) is very important for assuring these characteristics, since it needs to achieve the highest energy conversion efficiency possible. One or more low drop-out voltage linear regulators (LDO) are usually employed in PMM but their efficiency degrades as the difference between their input and output voltages increases. Unfortunately battery voltages has not scaled as much as the ICs internal supply, therefore LDOs yield poor efficiency.

Texas Instruments is developing a switched mode power supply and a controller for operating it with a Pulse Frequency Modulation in order to improve the MSP430 power management efficiency. The controller uses two monostable for generating the correct time pulses. These devices consume  $25\mu A$  each.

The aim of this thesis is to improve their current consumption up to the lowest possible achievable. The new power management concept is described and the monostable consumption is analysed in order to understand how it can be optimized. Afterwards the various devices composing the monostables are analysed investigating various solutions. The final circuit has been design with a TI's 90nm CMOS process, and it shows the same characteristics of the previous design with a current consumption improved up to  $5\mu A$ .

# Acknowledgements

I would like to thank the many people who made this thesis possible. I would like to express my gratitude to my supervisors, Prof. Andrea Bevilacqua, Dr. Ralf Brederlow and Prof. Dr. Doris Schmitt Landsiedel that together allowed me to live this experience. I am grateful to Prof. Andrea Bevilacqua and Dr. Ralf Brederlow for the precious advices and the continuous support they gave me. I am indebted to Rüdiger Kuhn of TI MSP430 analog team that with his experience and patience helped me during this 6 months. I want to thank Ph.D. Francesco Santoro of TUM for his friendship and his advices. I am deeply grateful to Texas Instruments Deutschland, Technische Universität München and Universitá degli Studi di Padova.

Finally special thanks goes to my girlfriend, my parents, my sister, my relatives and my friends that continuously believe in me and support me either in the happy and sad moments.

# Contents

| $\mathbf{D}$ | Declaration of Authorship |             |                                                  |     |

|--------------|---------------------------|-------------|--------------------------------------------------|-----|

| C            | onter                     | $_{ m nts}$ |                                                  | v   |

| Li           | st of                     | Figure      | es                                               | vii |

| Li           | st of                     | Tables      | S                                                | X   |

| 1            | Intr                      | oducti      | ion                                              | 1   |

| 2            | App                       | olicatio    | on description                                   | 3   |

|              | 2.1                       | MSP4        | 30 power management                              | 3   |

|              | 2.2                       | Switch      | ned Mode Power Supply (SMPS) fundamentals        | 4   |

|              | 2.3                       | Buck        | Converter for the power management               | 7   |

|              | 2.4                       | Monos       | stable                                           | 10  |

| 3            | Cor                       | nparat      | or                                               | 13  |

|              | 3.1                       | _           | arator fundamentals                              | 13  |

|              | 3.2                       |             | arator requirements and simulation set-up        | 19  |

|              | 3.3                       | Analy       | sis and results of comparator topologies         | 21  |

|              |                           | 3.3.1       | Differential input pair with current mirror load | 21  |

|              |                           | 3.3.2       | Differential input pair with cross coupled load  | 28  |

|              |                           | 3.3.3       | Self-biased comparator                           | 34  |

|              |                           | 3.3.4       | Preamplifier with CSDA second stage              | 38  |

| 4            | Cur                       | rent g      | enerator                                         | 51  |

|              | 4.1                       | Curre       | nt generator requirements                        | 51  |

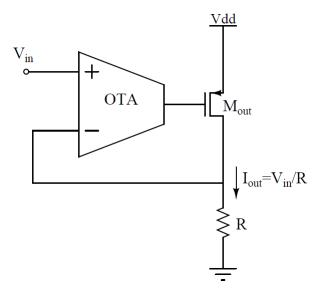

|              | 4.2                       | ОТА а       | as voltage regulator                             | 51  |

|              |                           | 4.2.1       | OTA voltage regulator design                     | 52  |

|              | 4.3                       | Voltag      | ge buffer                                        | 59  |

|              |                           | 4.3.1       | Subthreshold operation                           | 60  |

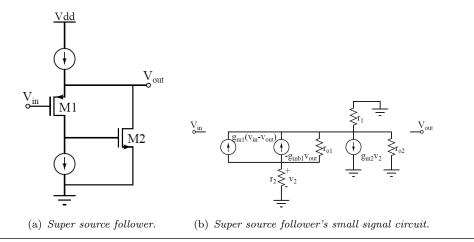

|              |                           | 4.3.2       | Super source follower                            | 62  |

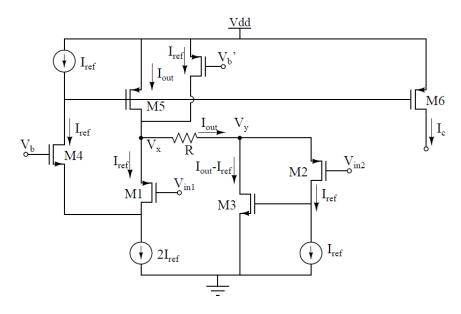

|              |                           | 4.3.3       | Super source follower current generator          | 65  |

| 5            | Mo                        | nostab      | le implementation                                | 69  |

|              | 5.1                       | Voltag      | re ramp signal generation                        | 60  |

|            | ·  |

|------------|----|

| Contents   | VI |

| 0010001003 | VI |

|    | 5.2<br>5.3<br>5.4 | Digital reset                                              | 78              |

|----|-------------------|------------------------------------------------------------|-----------------|

| 6  | Summary           |                                                            | 85              |

| A  |                   | iability and mismatch  Accuracy analysis simulation method | <b>88</b><br>91 |

| Bi | Bibliography      |                                                            |                 |

# List of Figures

| 2.1  | LDO                                                                                   | 4  |

|------|---------------------------------------------------------------------------------------|----|

| 2.2  | Basic SMPS DC/DC converters                                                           | 5  |

| 2.3  | Buck time characteristics                                                             | 6  |

| 2.4  | PWM                                                                                   | 7  |

| 2.5  | Fixed $T_{on}$ and $T_{off}$ controller concept                                       | 8  |

| 2.6  | Charge transferred                                                                    | 8  |

| 2.7  | Output voltage ripple                                                                 | 9  |

| 2.8  | Buck controller for Texas Instruments power management                                | 10 |

| 2.9  | Basic monostable                                                                      | 10 |

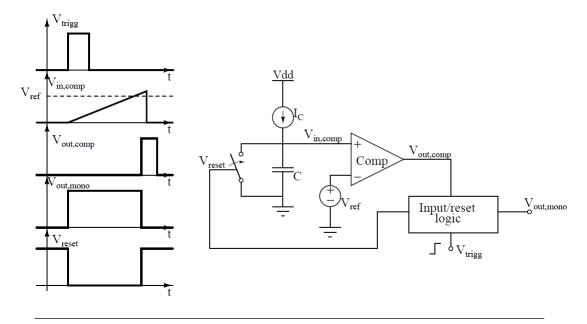

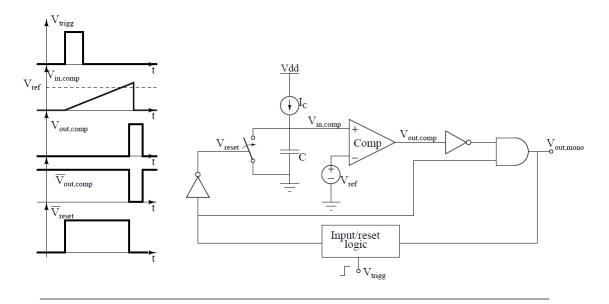

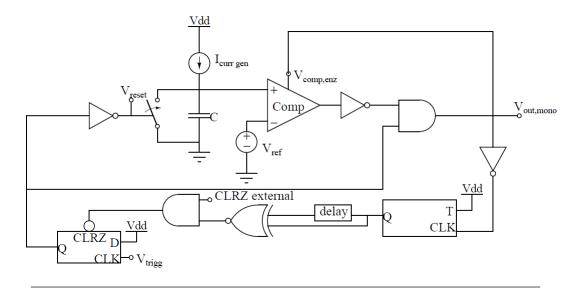

| 2.10 | Concept of the designed monostable                                                    | 11 |

| 2.11 | First monostable realization                                                          | 12 |

| 3.1  | Comparator's ideal characteristic                                                     | 14 |

| 3.2  | Comparator's finite gain                                                              | 14 |

| 3.3  | Comparator's real characteristic                                                      | 15 |

| 3.4  | Comparator's time response                                                            | 16 |

| 3.5  | Dynamic comparator                                                                    | 19 |

| 3.6  | Comparator simulation test bench                                                      | 21 |

| 3.7  | OTA transfer function                                                                 | 22 |

| 3.8  | Differential pair with mirror load comparator                                         | 23 |

| 3.9  | Current mirror load comparator frequency transfer function                            | 24 |

| 3.10 | Current mirror load comparator: transient results                                     | 26 |

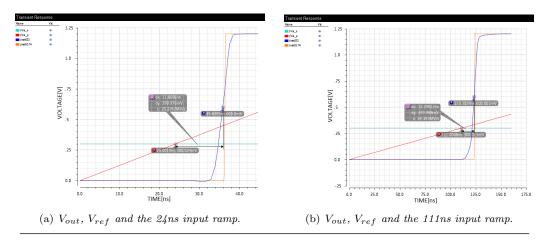

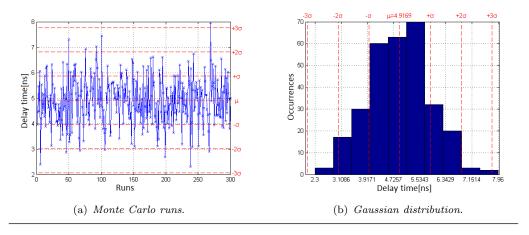

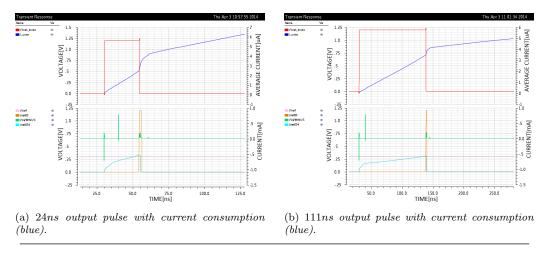

| 3.11 | Current mirror load comparator:<br>Monte Carlo, $24ns$ period                         | 27 |

| 3.12 | Current mirror load comparator:<br>Monte Carlo, $111ns$ period                        | 27 |

| 3.13 | Cross coupled load comparator                                                         | 29 |

| 3.14 | Cross coupled load comparator: transient results                                      | 30 |

|      | Cross coupled load comparator with push-pull second stage $\dots \dots$ .             | 31 |

| 3.16 | Cross coupled load comparator with push-pull second stage: transient results          | 32 |

| 3.17 | Cross coupled load comparator with push-pull second stage: Monte Carlo, $24ns$ period | 32 |

| 9 10 | Cross coupled load comparator with push-pull second stage: Monte Carlo,               | 32 |

| 3.10 | 111ns period                                                                          | 32 |

| 3.19 | Cross coupled load comparator with push-pull second stage: $V_{os}$                   | 33 |

| 3.20 | Cross coupled load comparator with push-pull second stage: Monte Carlo,               |    |

|      | $V_{os}$                                                                              | 34 |

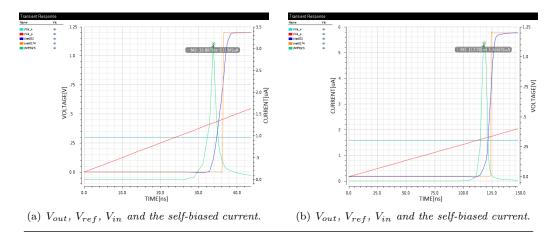

|      | Self-biased comparator                                                                | 36 |

| 3.22 | Self-biased comparator: transient results                                             | 36 |

List of Figures viii

| 3.23         | Self-biased comparator: 24ns period transient                               | 37       |

|--------------|-----------------------------------------------------------------------------|----------|

| 3.24         | Self-biased comparator: adaptive current                                    | 38       |

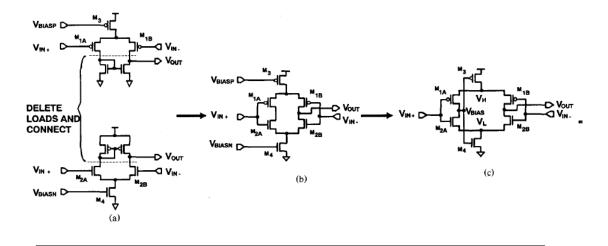

| 3.25         | CSDA derivation                                                             | 39       |

| 3.26         | CSDA operation                                                              | 40       |

| 3.27         | CSDA small signal circuit                                                   | 40       |

| 3.28         | Allen-Holberg [4] comparator                                                | 42       |

| 3.29         | Diode load comparator with CSDA second stage                                | 43       |

| 3.30         | Diode load comparator with CSDA second stage: transient result              | 43       |

| 3.31         | Resistor load with CSDA second stage                                        | 45       |

| 3.32         | Final comparator current consumption                                        | 46       |

| 3.33         | Final comparator: transient results                                         | 46       |

| 3.34         | Final comparator: Monte Carlo, $24ns$ results                               | 48       |

| 3.35         | Final comparator: Monte Carlo, $111ns$ results                              | 48       |

| 3.36         | Final comparator: Monte Carlo $-40^{\circ}$ results, $24ns$ period          | 48       |

| 3.37         | Final comparator: Monte Carlo $95^o$ results, $24ns$ period                 | 49       |

| 3.38         | Final comparator: Monte Carlo $-40^o$ results, $111ns$ period               | 49       |

| 3.39         | Final comparator: Monte Carlo $95^o$ results, $24ns$ period                 | 49       |

| 4.1          |                                                                             | -0       |

| 4.1          | Circuit for the generation of the $V_{in}-V_{out}$ proportional current     |          |

| 4.2          | Linear voltage regulator                                                    |          |

| 4.3<br>4.4   | Linear voltage regulator block diagram                                      | 53       |

|              |                                                                             | 55<br>55 |

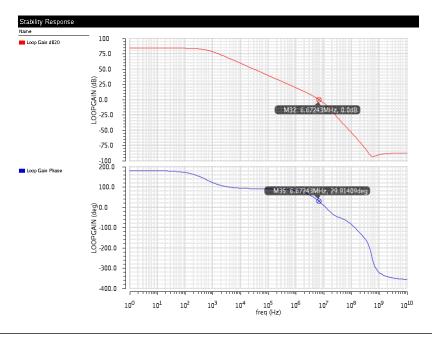

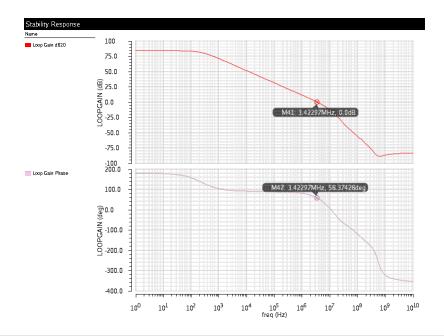

| $4.5 \\ 4.6$ | Linear voltage regulator: step response                                     | 56       |

| 4.0          | Linear voltage regulator: loop gain Bode diagram                            | 57       |

| 4.7          | Linear voltage regulator: compensated step response                         | 57       |

| 4.9          | Old current generator                                                       |          |

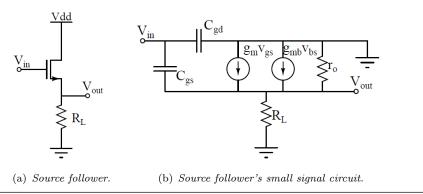

|              | Source follower                                                             | 59       |

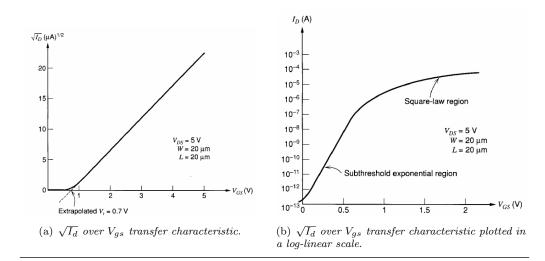

|              | MOS weak inversion transfer characteristic                                  |          |

|              | Super source follower                                                       |          |

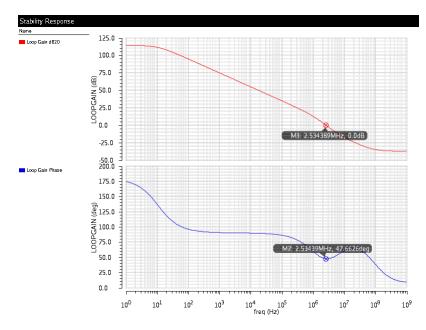

|              | Super source follower: loop gain Bode diagram                               |          |

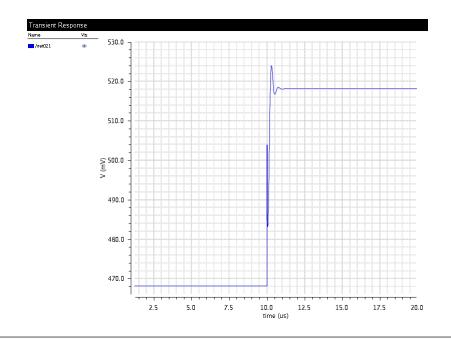

|              | Super source follower: step response                                        |          |

|              | Super source follower circuit for the $V_{in} - V_{out}$ current generation |          |

|              | Super source follower current generator with biasing circuitry              |          |

|              | Super source follower current generator: Monte Carlo results                | 68       |

| 4.11         | Super source follower current generator. Monte Carlo results                | UC       |

| 5.1          | Ideal ramp input voltage                                                    | 70       |

| 5.2          | Ramp input signal generated by the super source follower current generator  | 72       |

| 5.3          | Ramp input signal generated by the super source follower current gener-     |          |

|              | ator with a real switch                                                     | 73       |

| 5.4          | Ramp input signal generated by the super source follower current gener-     |          |

|              | ator with the comparator input capacitance                                  | 74       |

| 5.5          | Real ramp input signal with $220fF$ adding capacitor                        | 75       |

| 5.6          | Real ramp input signal                                                      | 75       |

| 5.7          | Capacitance digital reset signals                                           | 76       |

| 5.8          | ·                                                                           | 77       |

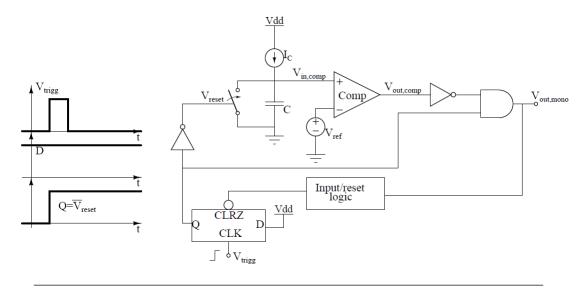

| 5.9          | Digital reset derivation: D flip-flop                                       | 77       |

List of Figures ix

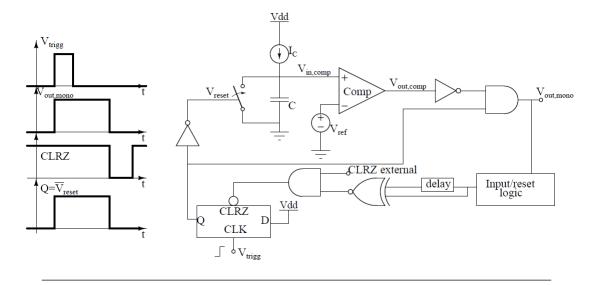

| 5.10 | Digital reset derivation: monostable introduction                        | 78 |

|------|--------------------------------------------------------------------------|----|

| 5.11 | Final digital reset circuit                                              | 79 |

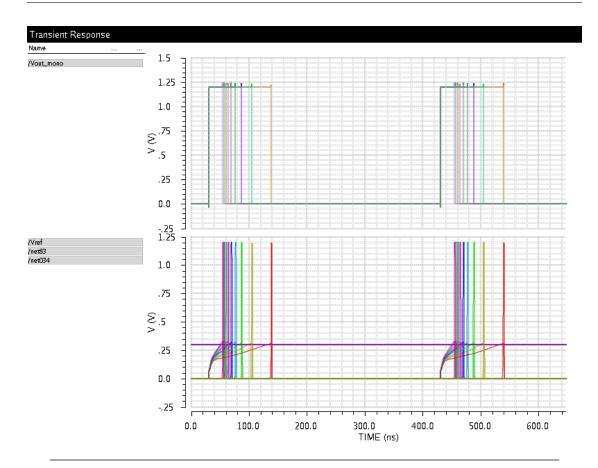

| 5.12 | Monostable pulses                                                        | 80 |

| 5.13 | Variable monostable pulses                                               | 81 |

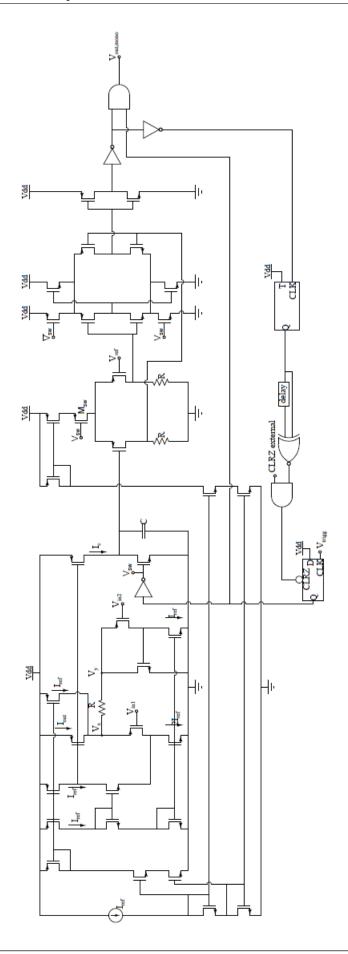

| 5.14 | Monostable complete circuit                                              | 84 |

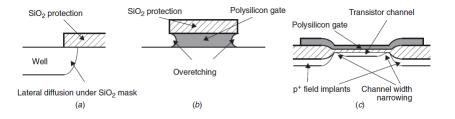

| A.1  | Effects that determine systematic variations                             | 89 |

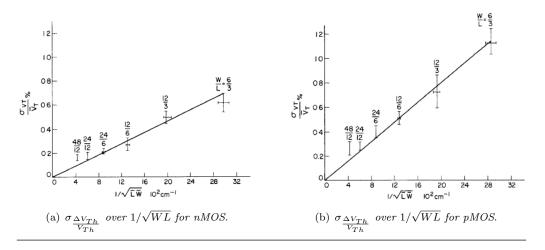

| A.2  | $1/\sqrt{WL}$ proportionality of $\sigma_{\frac{\Delta V_{Th}}{V_{Th}}}$ | 90 |

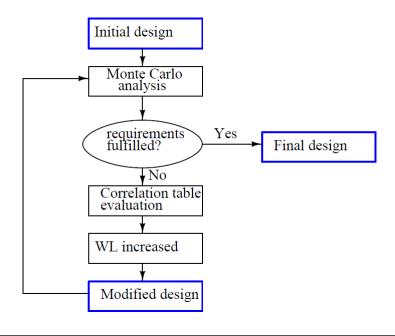

| A.3  | Monte Carlo design procedure                                             | 92 |

# List of Tables

| 3.1 | Current mirror load comparator: Monte Carlo results' summary              | 28 |

|-----|---------------------------------------------------------------------------|----|

| 3.2 | Cross coupled load comparator with push-pull second stage: Monte Carlo    |    |

|     | results' summary                                                          | 33 |

| 3.3 | Self-biased comparator: Monte Carlo results' summary                      | 37 |

| 3.4 | Diode load comparator with CSDA second stage: Monte Carlo design          |    |

|     | process                                                                   | 44 |

| 3.5 | Final comparator: Monte Carlo design process                              | 47 |

| 3.6 | Final comparator: Monte Carlo temperature results' summary, $24ns$ period | 50 |

| 3.7 | Final comparator: Monte Carlo temperature results' summary, $111ns$       |    |

|     | period                                                                    | 50 |

| 4.1 | Super source follower current generator: Monte Carlo design process $$    | 67 |

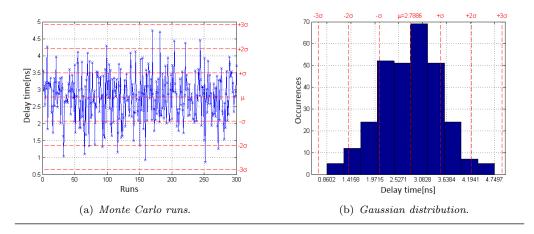

| 5.1 | Monostable: Monte Carlo temperature results, 24ns period                  | 80 |

| 5.2 | Monostable: Monte Carlo temperature results, $111ns$ period               |    |

| 6.1 | Summary table                                                             | 87 |

To whom believes always in me

## Chapter 1

## Introduction

In the last two decades we have faced an exponential increase of electronic applications in every field, from the automotive to everyday products like microwaves or washing machines.

A micro-controller is always hidden inside all these products. These circuits are small computers that control various applications and interaction of the users with the tool. In the last decades also the number of portable devices arose significantly. These devices increased continuously their computational power and applications. The most famous example is the smartphone. However, the increase of their complexity determined the increase of their power consumption. Therefore battery-powered devices need highly efficient circuits in order not to compromise their battery life time. Thus, micro-controllers capable of providing the desired functions together with a low consumption are highly desirable.

MSP430 is continuously decreasing its power consumption in order to allow portable devices to achieve higher performances. A solution for the optimization of this microcontroller is described (chapter 2). This involves the use of a switched-mode power supply regulator instead of a linear regulator for the power management of the device. In fact it can increase significantly the efficiency of the energy conversion circuit. Obviously it needs a controller that itself has to achieve a low power consumption so as not to affect the overall efficiency. The controller uses two monostables to fix the period in which the energy is transferred from the battery to the load. These are the most significant devices of the controller, both for their role and their current consumption. In this thesis the one-shot circuit will be analysed and its current consumption will be lowered.

In chapter 2 the premises and the motivations of the project will be explained.

In chapter 3 a comparator will be realized and both its performances and its current consumption will be optimized for the monostable.

In chapter 4 a circuit for the extrapolation of a current proportional to the difference between two voltages will be analysed and realized.

Finally in chapter 5 the monostable is designed using the devices obtained in the other chapters. Afterwards the circuit will be tested and the final results will be reported.

## Chapter 2

# Application description

In this chapter the application of the monostable realized will be explained. A brief introduction in the difference between an LDO and a SMPS circuit for ultra-low power MCUs will take place. Finally the requirements for the monostable will be set.

#### 2.1 MSP430 power management

The MSP430 is a Texas Intruments 16 bit Micro Controller Unit. A microcontroller is a small computer integrated on a single chip that contains a CPU, memories and I/O peripherals. MCUs are usually employed on embedded systems for special purpose digital control.

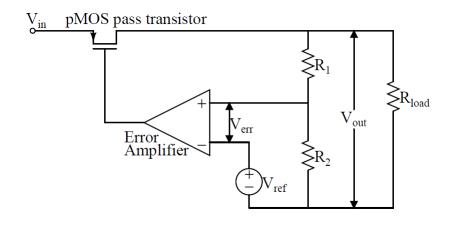

Texas Intruments 4 bit TMS1000 (1972) was the first programmable system on chip employed in application such as calculators and oven. Towards the decades MCUs developed their processing power, thanks to higher levels of integration, while they reduced their power consumption. MSP430 main advantages are the low cost and the low power consumption. It can draw less than  $1\mu A$  in idle mode, while it has 6 different low power modes, useful for a lot of low power applications. It requires, as every electronic device, an external supply voltage that usually is an external battery. Therefore the MSP needs a power management module, PMM, able to provide an internal supply voltage for the integrated circuit from the external battery. The present power management is realised by a Low Dropout voltage regulator (LDO). This device is mainly a constant voltage source that provides a constant voltage at its output varying its internal resistance to the variations that occurs in the load resistance. A circuit that does this simple task is reported in figure 2.1.

The key device is the error amplifier that compares a scale-down version of the output voltage to a reference (usually a bandgap type) and adjust its output voltage in order

Figure 2.1: Basic linear voltage regulator.

to set its differential input voltage as close as possible to zero. Therefore it drives a pass transistor and varies its drain current so as to keep  $V_{err}$  close to zero through a negative feedback. The pass transistor is usually a pMOS since the gate source voltage that controls it is usually negative.

Many are the advantages provided by an LDO, such as its fast response to input and output transients, low output noise, small area; however its main drawback is its maximum theoretical efficiency that is

$$\eta_{LDO} = \frac{V_{out}}{V_{in}} \tag{2.1}$$

In fact as the difference between the output voltage and the input voltage increases,  $\eta_{LDO}$  drastically decreases. While the integrate circuit internal supply voltage has scaled through the decades, the battery supply voltage has remained constant. Therefore today LDOs present low cost, low complexity, but poor efficiency. Therefore switched mode power supply circuits become advisable since nowadays battery powered devices need high efficiency power regulators in order not to compromise the battery life.

### 2.2 Switched Mode Power Supply (SMPS) fundamentals

Switched mode power supply circuits are electronic devices used as regulators and for providing the necessary power to electronic circuits. Differently from linear regulators where there is an element (the pass transistor) that always conduct, SMPS devices continuously switches from on and off stage, remaining the lowest time possible (ideally zero) in high dissipation. For this reason the maximum ideal efficiency of such a circuit is 100%.

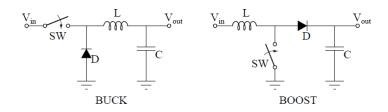

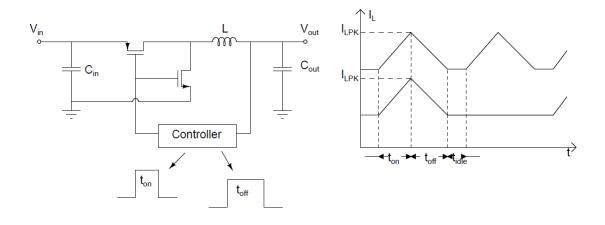

The basic DC/DC converters are the Buck converter and the Boost (figure 2.2). The first one is a step-down converter since  $V_{out} < V_{in}$  while the second a step-up since  $V_{out} > V_{in}$ . The converter used to substitute the LDO is a Buck, therefore the analysis will focus on this circuit.

FIGURE 2.2: Basic Switched mode power supply DC/DC converters.

#### **Buck operation fundamentals**

A Buck converter is reported in the above figure. Assuming ideal switches and a current  $i_L$  always higher than zero, it is possible to evaluate the circuit operation in 2 phases:

• Powering phase: at the instant t = 0 the MOS is turned on while the diode is turned off. The voltage across the inductance is  $v_L = V_{in} - V_{out}$  and its current increases linearly as

$$i_L(t) = i_L(0) + \frac{V_{in} - V_{out}}{L}t$$

(2.2)

• Freewheeling phase: the MOS is turned off while the diode turns on. During this period the energy stored in the inductor is transferred to the output capacitor and to the load. The inductor voltage is  $v_L = -V_{out}$ , therefore its current linearly decreases as

$$i_L(t) = I_{LPK} - \frac{V_{out}}{L}t \tag{2.3}$$

The steady-state condition states that the inductor current variation during each phase has to be equivalent, thus

$$\Delta I_L = \frac{V_{in} - V_{out}}{L} t_{on} = \frac{V_{out}}{L} t_{off} \Rightarrow V_{out} = \frac{t_{on}}{t_{on} + t_{off}} V_{in} = \delta V_{in} \quad \text{with } \delta = \text{duty-cycle}$$

(2.4)

This way of operating is called Continuous Current Mode (CCM). Equation 2.4 shows the step down characteristic of the Buck converter. The Buck time characteristics are reported in figure 2.3.

FIGURE 2.3: CCM and DCM Buck time characteristics.

The Buck behaviour varies with output current variations. As the load decreases, the inductor current becomes zero for a period and the Buck enters in Discontinuous current mode (DCM). In fact the diode does not allow  $i_L$  to become less than zero when the MOS is off. The way of operating is the same as for the CCM but there is a third phase called **idling phase** in which  $i_L = 0A$  and the capacitor provides the output current. The output voltage is thus given by

$$V_{out} = MV_{in} = \frac{\delta^2}{\delta^2 + \frac{2f_s L I_0}{V_{in}}} = \frac{\delta^2}{\delta^2 + I_{oN}}$$

(2.5)

where  $f_s$  is the switching frequency of the system and  $I_{oN} = \frac{2Lf_s\overline{I_{out}}}{V_{in}}$ .

#### Output voltage control modulations

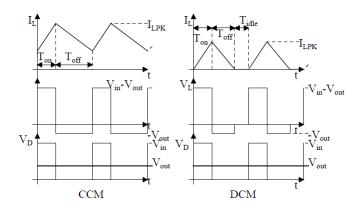

The output voltage has to be regulated and therefore an active controller is needed. In CCM the output voltage can be regulated varying the duty-cycle. Therefore a pulse width modulation (PWM) is employed; this utilizes a fixed switching frequency and varies the width of the on and off time in order to keep the output voltage regulated. The pulse width modulator is usually a comparator that compares a triangular waveform with a modulation signal proportional to the output voltage, in order to obtain a variable pulse square waveform used to control the switch (figure 2.4).

However CCM, and so PWM, is usually used for high load current since the Buck efficiency is higher in this mode of operation. In the case of light loads, other modulations

FIGURE 2.4: Pulse Width Modulation.

are used, like Pulse Frequency Modulation (PFM). Differently form PWM, in PFM the on and off times are fixed and what varies is their repetition frequency. Therefore when the output voltage is lower than the reference, the energy transferred to the load is increased enhancing the frequency.

#### 2.3 Buck Converter for the power management

A DC-DC switching converter as a Buck has a higher efficiency than a LDO when the difference between input and output voltage is considerable. They are usually designed for showing a high efficiency at a set peak power level, while when operated in lighter load conditions their efficiency degrades. This is mainly related to the switching power losses. These losses can be reduced operating at a lower frequency, when a pulse width modulation (PWM) is employed, but results in higher peak inductor currents that determines an increased cost. The use of a discontinuous current mode (DCM) converter controlled by a frequency pulse modulation (PFM) results in a high efficiency for medium to light load conditions[1].

The converter that Texas Instruments is developing for the new MSP430 power management uses this concept[2]. A fast and stable control loop is needed. The solution proposed by Ph.D. Francesco Santoro is a power supply capable of providing the necessary energy when the digital core needs it and enter in an idle mode when the system absorbs only the leakage current[2]. For this reason a fast start up is desirable. Therefore he has designed a synchronous DCM Buck converter employing a predictive peak current controller (figure 2.5).

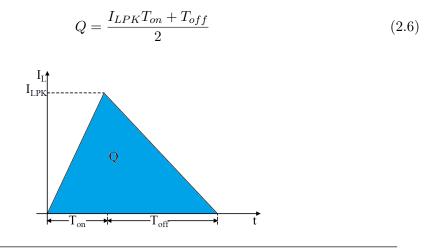

The inductor peak current is constant, thus the charge Q transferred every period to the load is fixed

FIGURE 2.5: Buck converter with the controller that sets the variable on and off times.

FIGURE 2.6: Quantity of charge transferred to the load every period.

Since this charge is known, it is possible to minimize the output capacitor and therefore obtain a fast start up.

The controller senses the input and output voltages of the converter,  $V_{in,Buck}$  and  $V_{out,Buck}$ , to set the on and off time  $T_{on}$ ,  $T_{off}$ . The on and off time of a Buck are given by:

$$T_{on} = \frac{I_{LPK}L}{V_{in,Buck} - V_{out,Buck}}$$

$$T_{off} = \frac{I_{LPK}L}{V_{out,Buck}}$$

$$\Rightarrow I_{LPK}L = \alpha = const \Rightarrow \begin{cases} T_{on} & \propto \frac{\alpha}{V_{in,Buck} - V_{out,Buck}} \\ T_{off} & \propto \frac{\alpha}{V_{out,Buck}} \end{cases}$$

$$(2.7)$$

Therefore the controller sets the correct on time depending on the difference between the input and output voltages. The maximum inductor peak current  $I_{LPK}$  depends on the maximum DC load. The inductor dimension depends on the maximum load current, the maximum frequency of the digital circuit and the maximum output ripple voltage allowed (equation 2.8).

$$\overline{I_L} = \frac{I_{LPK} \left( T_{on} + T_{off} \right)}{2 \left( T_{on} + T_{off} + T_{idle} \right)}$$

$$\overline{I_{out}} = I_{load,max}$$

$$\Rightarrow \overline{I_{out}} = I_L \Rightarrow I_{LPK} = 2I_{load,max} \frac{T_{on} + T_{off} + T_{idle}}{T_{on} + T_{off}}$$

$$\Delta V_{out} = \overline{\frac{I_{out}}{Cf_s}} \left( 1 - \frac{1}{2} \sqrt{\frac{I_{oN}}{M(1 - M)}} \right)$$

(2.8)

FIGURE 2.7: Output ripple voltage is function of the inductor peak current  $I_{LPK}$ .

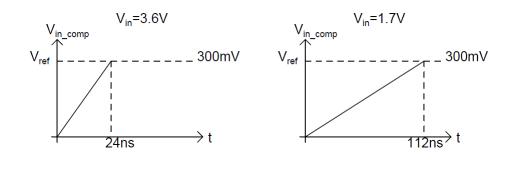

Since  $\overline{I_{out}}=2.65mA$  and  $I_{LPK}=7.5mA$ , the inductor has been set to  $L=7.4\mu H$ . For this circuit the input voltages can vary from 1.7V to 3.6V (it is a battery) while the output voltage is fixed at 1.2V. Therefore the on time varies from  $T_{on}=\frac{7.5mA\cdot7.4\mu H}{3.6V-1.2V}\simeq 23.2ns$  and has been chosen equal to 24ns for simplicity, to  $T_{on}=\frac{7.5mA\cdot7.4\mu H}{1.7V-1.2V}\simeq 111ns$ . The off time is instead fixed to  $T_{off}=\frac{7.5mA\cdot7.4\mu H}{1.2V}\simeq 46.3ns\approx 48ns$ . The controller is reported in figure 2.8.

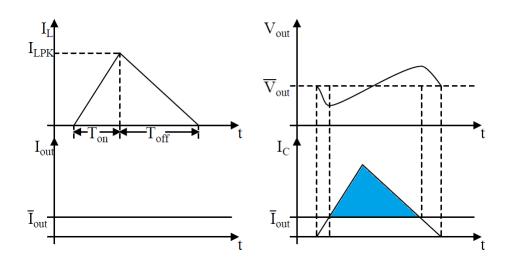

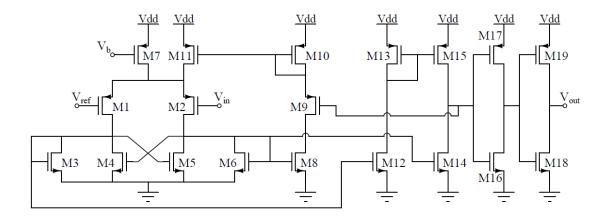

A comparator senses the output voltage  $V_{out,Buck}$  and compares it with a reference  $V_{ref}$ . When the output voltage goes under the reference, the comparator output goes to a digital control logic that wakes up the switching converter and triggers a monostable that fixes the on time. The on time monostable then triggers an off time monostable after a small delay so as to avoid cross conduction, since the two pulses drive the power stage. The signal is then sent to the control logic after a minimum delay time in order to assure that the converter does never enter in continuous current mode (CCM). Finally

FIGURE 2.8: Controller realized for the DCM Buck converter.

the control logic allows the system to start again until the output voltage is higher than the reference voltage and the comparator switches again putting the converter in idle mode. In this way the resulting Buck period (considering the maximum current load) results to be  $T_{Buck} = T_{on} + T_{off} + T_{idle} = 24ns + 48ns + 28ns = 100ns$  (for a 3.6V input voltage) and  $T_{Buck} = T_{on} + T_{off} + T_{idle} = 111ns + 48ns + 91ns = 250ns$  (for the 1.7V input voltage).

#### 2.4 Monostable

The key devices in the whole controller are the monostable circuits. In fact they have the important role of driving the Buck's power stage, therefore they regulate the amount of energy transferred to the load every period.

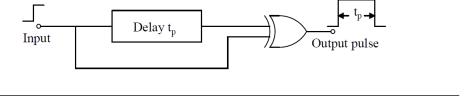

A monostable is a circuit that generates a pulse of a pre-defined time width in response to an external trigger input signal. The name of this device derives from its unique stable state, during its rest period. The external impulse causes the circuit to its quasi stable state for a period of time that is determined by the circuit internal parameters. Usually a one-shot circuit uses a device able to provide a delay that sets the pulse width. The simplest monostable is realized using the circuit in figure 2.9.

FIGURE 2.9: Simplest monostable design.

In the stable state the output is zero since the inputs are both at zero. When an impulse is applied, the output goes to 1 until the two XOR inputs return equal, time that is exactly the delay  $t_p$  introduced. In this way a pulse of width  $t_p$  has been generated.

A common mode to produce a delay cell is to introduce a RC time constant or use a cascade of elementary digital ports.

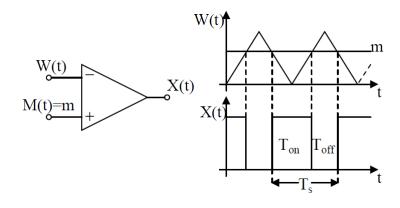

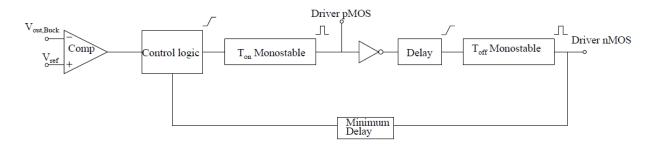

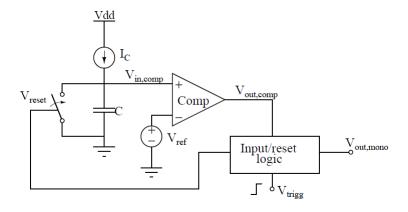

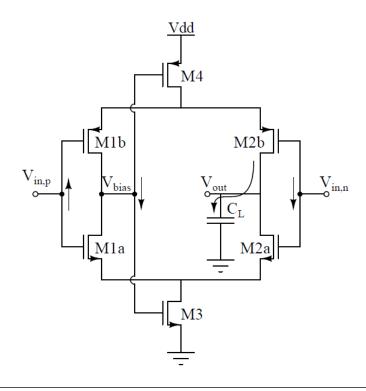

Another common way of design a monostable is that reported in [3] and [1]. The common concept is reported in figure 2.10.

Figure 2.10: Monostable concept.

A triggering signal determines the input of the monostable pulse and turns off the switch that keeps the capacitor discharged. A constant current is therefore able to charge the capacitor and generate a ramp input voltage signal since

$$I(t) = C\frac{dV(t)}{dt} \Longrightarrow V(t) = V(t_0) + \frac{1}{C}I_C(t - t_0)$$

(2.9)

This ramp input voltage has a constant slope and the monostable's time width can be set as the time took by the ramp to reach a defined voltage. Therefore a comparator is used to detect this event. It compares the ramp voltage signal with a voltage reference and its output goes from 0 to 1 when the input signal crosses the reference. A suitable digital circuitry uses this signal to determine the end of the pulse.

The Buck controller needs a monostable able to vary its pulse width depending on the input and output voltage of the regulator and obtain always the same  $I_{LPK}$ . The previous concept can be used for the realization of this device, but it has to be modified in order to be able to provide different pulses. The parameter that can be easily varied is the current that charges the capacitor. In fact it varies the slope of the ramp voltage, allowing it to cross the reference at different times. If this current varies proportionally to the input output voltage difference  $V_{in,Buck} - V_{out,Buck}$ , then the monostable varies its width proportionally to this parameter.

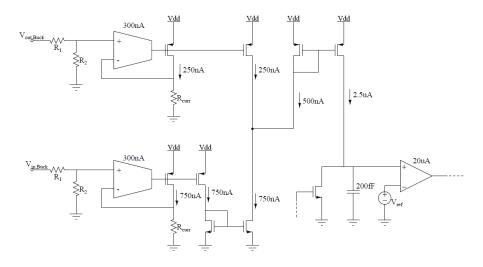

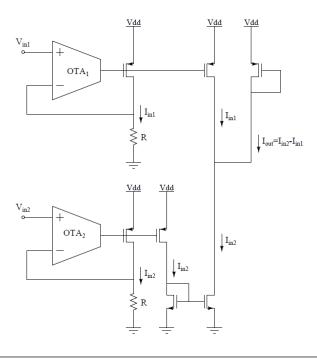

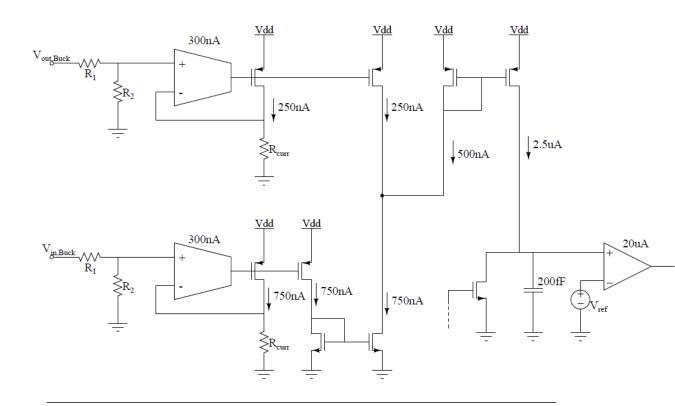

This concept has been developed by Ph.D. Francesco Santoro. The circuit that he realized is reported in figure 2.11. Two voltage regulators for the generation of the currents proportional to  $V_{in,Buck}$  and  $V_{out,Buck}$  are used. The two currents are then

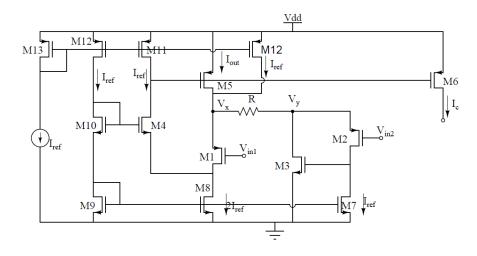

subtracted using a current mirror. The current resulting from this operation is then used to charge a capacitor. Finally a comparator is used to detect the reference crossing. The current consumption of every device is reported in the figure. The resulting overall current consumption of the fist version of the monostable is

$$I_{cons} = 2 \cdot I_{cons,OTA} + I_{V_{in}} + I_{V_{in},copy} + I_{V_{out}} + I_{V_{in}-V_{out}} + I_C + I_{cons,comp}$$

$$\approx 2 \cdot 300nA + 2 \cdot 750nA + 250nA + 750nA + 2.5\mu A + 20\mu A = 25.6\mu A$$

(2.10)

The purpose of this thesis is therefore to reduce as much as possible the consumption of this monostable.

the requirements set for this circuits are:

- average current consumption in a period  $\overline{I_{cons}} \leq 10 \mu A$  as a fist goal

- ullet input Buck voltage that varies from 1.7V to 3.6V

- variable pulse width  $T_{on}$  from 24ns to 111ns

- maximum allowable pulse jitter related to process variations and random mismatches  $\sigma_{T_{on}} \leq 2.5\%$  of  $T_{on}$

The comparator is the circuit that consumes more current since it has to be fast. Thus the optimization starts from this circuit.

FIGURE 2.11: Francesco Santoro monostable design concept.

# Chapter 3

# Comparator

As explained in the previous chapter, the optimization began from the comparator, since it has to match very strictly requirements and it is the most current hungry device. In the first monostable version, the comparator was an open loop 2-stage OTA with an average current consumption of  $20\mu A$ .

This chapter will begin with the comparator fundamentals. After that, all the different suitable solutions will be described, each one with its pros and cons. The fundamentals and the relative considerations are based on [4].

#### 3.1 Comparator fundamentals

#### Static characteristics

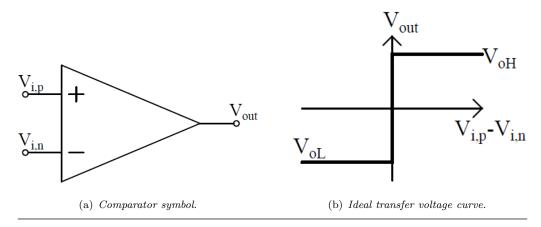

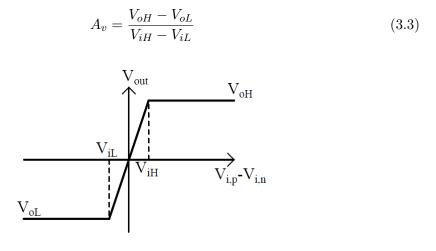

The comparator is a widely used circuit and it relates analog signals to digital ones; in fact it can be considered a 1-bit analog to digital converter.

This circuit, as the name suggests, compares its two input voltages, giving a binary output (0 or 1) depending on the result of the comparison. Therefore  $V_{out}$  equals a defined high voltage  $V_{oH}$  when the positive input  $V_{i,p}$  is greater than the negative input voltage  $V_{i,n}$ , otherwise it is set to a defined low voltage  $V_{oL}$ . The behaviour of the ideal comparator is mathematically described in 3.1.

$$V_{out} = \begin{cases} V_{oH} & if \ V_{i,p} - V_{i,n} > 0 \\ V_{oL} & if \ V_{i,p} - V_{i,n} < 0 \end{cases}$$

(3.1)

The output of the comparator changes its state(from  $V_{oL}$  to  $V_{oH}$ ) when there is a variation of  $\Delta V = V_{i,p} - V_{i,n}$  (figure 3.1). The gain of the ideal comparator is

FIGURE 3.1: Comparator symbol and ideal transfer voltage curve.

$$A_v = \lim_{\Delta V \to 0} \frac{V_{oH} - V_{oL}}{\Delta V} = \infty \tag{3.2}$$

In figure 3.2 it is shown a more realistic transfer function of a comparator. In fact the gain is not infinite any more and there is a finite transition region. The gain is better defined as

Figure 3.2: Tranfer voltage curve of a more realistic comparator.

Now it is also possible to introduce a parameter, the *resolution*, that shows what is the minimum input change needed for the saturation of the output voltage. Of course the greatest gain possible is pursued in order to obtain the smallest transition region and the lowest resolution.

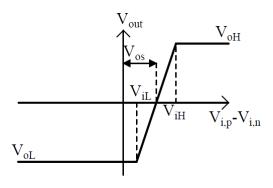

The input offset voltage  $V_{os}$  is another very important non-ideality of comparators. In figure 3.2, the output of the comparator changes state when the differential input crosses the zero voltage. However, the change of state happens at a defined voltage  $V_{os}$  (figure

3.3). This non ideal behavior should not be a problem if this voltage could be predicted. Unfortunately the offset voltage depends from the structure of the circuit, process variations and random mismatches that changes from die to die. These variations are related to the mismatches between every device that arise in the fabrication process.

FIGURE 3.3: Transfer voltage curve with input offset voltage  $V_{os}$ .

The ICMR, input common mode range is another parameter that has to be taken into account when designing a comparator. This parameter describes the range of common mode voltage in which the comparator works properly. Usually this ICMR is the range in which the transistors works in saturation region.

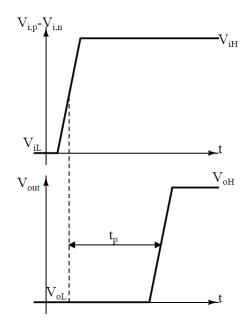

#### Dynamic characteristics

The static characteristics and the comparator's non idealities have been explained. The other very important and interesting parameters of this circuit are its dynamic characteristics, that include both large and small signal behavior.

The propagation delay is the most important dynamic characteristic of a comparator. This is the time that it takes to make a change in  $V_{out}$  signal in response to a  $V_{in}$  impulse. This delay is a really important and constraining parameter since it is often the speed limitation of an A/D converter. As it is possible to see from figure 3.10 the propagation delay is defined as the time elapsed from when the input signal in the positive (or negative) input becomes larger (or lower) than the negative one, to when the output reaches a defined threshold  $V_{thr} = \frac{V_{oH} + V_{oL}}{2}$ .

Usually the propagation delay varies in dependence of the input signal swing; a small delay time is obtained with a large input swing. This fact is simply understandable since, as it will be shown, the comparator input is usually a differential input pair; a large and fast change in its differential voltage determines a large and fast change in its drain current. This behaviour has a limit, otherwise every comparator would have

FIGURE 3.4: Output response to an input response with the delay time.

a zero time delay and this one would not be an important dynamic parameter. This upper limit is the *slew rate*, as it will be described.

Therefore when the input has a large voltage swing, and so a large change in the overdrive  $(V_{ov} = V_{gs} - V_T)$ , we have a delay time that is mainly determined by the large-signal behaviour of the comparator. Differently, when a small differential input signal is applied (hence a small  $V_{ov}$ ), the delay time is mainly determined by the small-signal behaviour of the comparator.

In this case the frequency response of the comparator relates the small-signal dynamics and the most simple model is a single pole response:

$$A_v(s) = \frac{A_{v0}}{1 + \frac{s}{\omega_p}} = \frac{A_{v0}}{1 + s\tau_p}$$

(3.4)

where  $A_{v0}$  is the DC gain and  $\omega_p$  is the pulse of the pole, hence the -3dB frequency( $\omega_p = 2\pi f_p$ ) of the comparator. This equation represents the variation of  $V_{out}$  in response of a small variation in the differential input. The time relation between these two variations is really important for this analysis. Then from  $A_v(s) = \frac{\Delta V_{out}}{\Delta V_{in}}$  we obtain a first order exponential response:

$$\Delta V_{out} = A_{v0} (1 - e^{-t/\tau_p}) \Delta V_{in} \tag{3.5}$$

The propagation delay is the time that passes from the input variations to when the output voltage crosses the threshold previously defined. Let us assume that the minimum input voltage capable of moving the output is applied. This minimum input voltage is:

$$V_{in,min} = \frac{V_{oH} + V_{oL}}{A_{v0}} \tag{3.6}$$

From 3.5 and 3.6 we obtain

$$\frac{V_{oH} + V_{oL}}{2} = A_{v0} (1 - e^{-t_d/\tau_p}) \left(\frac{V_{oH} + V_{oL}}{A_{v0}}\right)$$

(3.7)

Solving this simple equation it is possible to find a simple relation for the delay time

$$t_d = \tau_p \cdot \ln(2) \simeq 0.69\tau_p \tag{3.8}$$

From the general hypothesis, this equation is valid for both positive and negative input variations. Moreover it is possible to relate the delay for input variations k times bigger than the minimum one.

$$t_d = \tau_p \cdot \ln\left(\frac{2k}{2k-1}\right) \tag{3.9}$$

As it is possible to see from equation 3.9, the bigger is the input voltage (and obviously the overdrive), the smaller is the propagation delay.

Obviously there is an upper limit to this behaviour. In fact, increasing the input overdrive voltage, leads the comparator to a large-signal mode of operation in which the maximum current for charging and discharging the capacitances is limited by the slewrate. In this case the delay is

$$t_d = \frac{\Delta V}{SR} = \frac{V_{oH} - V_{oL}}{2 \cdot SR} \tag{3.10}$$

Sometimes it is useful to understand whether the delay is dominated by a small-signal or a large-signal dynamic and the overdrive at which occurs the change from small-signal to large-signal dynamics.

This change theoretically happens when the delay time is limited both by equations 3.9 and 3.10

$$\tau_{p} \cdot \ln\left(\frac{2k}{2k-1}\right) \doteq \frac{V_{oH} - V_{oL}}{2 \cdot SR}

\Rightarrow k_{lim} = \frac{e^{\frac{V_{oH} - V_{oL}}{2 \cdot \tau_{p} \cdot SR}}}{2\left(e^{\frac{V_{oH} - V_{oL}}{2 \cdot \tau_{p} \cdot SR}} - 1\right)}$$

(3.11)

As an example we can suppose a comparator with  $A_{v0}=60dB$ ,  $V_{oH}-V_{oL}=1.2V$ , a dominant pole at  $2\pi f_p=\frac{1}{\tau_p}=10^4 rad/s$  and a  $SR=300mV/\mu s$ . We obtain that

$$k_{lim} = \frac{e^{\frac{1.2}{2 \cdot 100 \mu s \cdot 300 mV/\mu s}}}{2\left(e^{\frac{1.2}{2 \cdot 100 \mu s \cdot 300 mV/\mu s}} - 1\right)} \simeq 25$$

Since  $V_{in,min} = 1.2mV$ , we have that for an input smaller than 30mV the delay propagation is dominated by the small-signal dynamic, while after this value it is dominated by the large-signal dynamic.

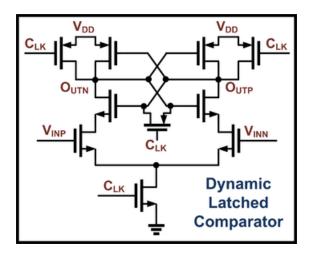

#### The two families of comparators

Comparators are one of the most important and used circuit in ICs. They can be classified into two main families: time-continuous and time-discrete comparators.

The former, as the name suggests, compares the two inputs continuously in the time. The latter, instead, does the comparison in two different phases, each one decided by a clock signal. Hence there is a first phase of *evaluation*, and a second phase of *comparison*. This type of comparators are widely used for AD-converters and can guarantee a high speed and a low power consumption(in figure 3.5 there is an example of time-discrete comparator).

In general the DCDC comparator used to turn on the controller can be time-discrete since it can use the "clock" that results from the on and off time monostables. Instead the time continuous nature of these devices force the use of time-continuous comparators into them.

For this reason the comparators that will be considered in the following analysis will be only time-continuous.

Figure 3.5: Time-discrete comparator.

#### 3.2 Comparator requirements and simulation set-up

The monostable requirements have been defined in chapter 1. This circuit has to provide a pulse with a variable time width that varies from 24ns to 111ns depending on the Buck's input and output voltages. These pulses have then to show a low variability to process variations and random mismatches. Therefore a requirement concerning the statistical behaviour has been set:  $\sigma_{T_{on}} \leq 2.5\%$  of  $\mu_{T_{on}}$ . The other important requirement is the average current consumption in a period of operation, that has to be the lowest possible. Initially the consumption set as a first goal is  $\overline{I_{cons}} \leq 10\mu A$ . Afterwards this requirement will be lowered in order to obtain a circuit with the lowest possible current consumption.

#### Comparator requirements

The comparator is the most important device in the monostable. In fact it has to be very fast and produce the lowest possible delay time. For this reason the assigned power budget is the highest of the whole monostable. However the current consumption is not the only important requirement of the comparator; in fact it has even to show the lowest delay together with the lowest mismatch and processing variability. Being very precise and careful, even the comparator's offset is important, especially because its variations affect the delay and its precision. Luckily (as explained in A) its value decreases when bigger devices are used, as the use of bigger devices decreases the variation of the delay time.

The requirements set for the comparator are:

- maximum delay time  $t_d$  equal to 10 15% of the total period. This means that  $t_{d_{max}} = 2.4 3.3ns$  if  $T_{on} = 24ns$  and  $t_{d_{max}} = 11 16.6ns$  if  $T_{on} = 111ns$ ;

- maximum standard deviation  $\sigma_{t_d}$  equal to the 10% of the propagation delay. It has to be noted that this 10% of  $t_p$  represents only the 1% of  $T_{on}$ ;

- average current consumption in a period  $\overline{I_{cons}} \leq 7\mu A$  (first goal).

#### Simulation set-up

In the following sections various comparator's topologies will be analysed in order to find the most suitable circuit that fulfils all the requirements described above. Firstly a theoretical analysis of them will be done and then the circuits will be simulated with Cadence, in order to check their behaviour. In order to obtain a simulation that is the closest possible to the real behaviour of the circuit, it is important to use a correct test bench.

For its realization it is essential to have a clear knowledge of the task of the circuit, the comparator in this case, and its actual inputs. A bad test bench design may lead to errors and a bad functioning of the designed circuit.

In chapter 1 it is shown the idea that stands behind the operation of the monostable. A current proportional to the difference of two voltages is driven into a capacitance, generating a ramp voltage that is compared to a steady reference voltage: the time from the beginning of the ramp to the instant in which it crosses the reference represents the pulse of the monostable.

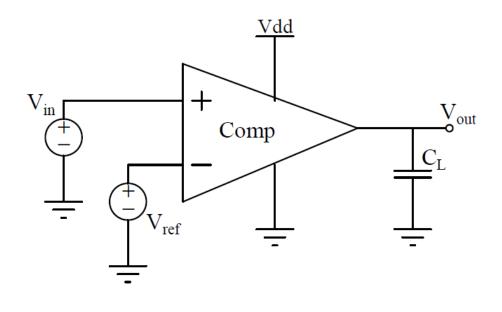

Therefore the comparator has a single supply voltage of 1.2V, a constant reference voltage  $V_{ref} = 300mV$  connected to the negative input pin, and a ramp input signal. In the final circuit the load of the comparator is a digital port, then it is the input capacitance of this port. The comparator has even a bias current that is provided by a current mirror from a reference of 100nA. The test bench is shown in figure 3.6; the current reference and the supply voltage are realized by an ideal current generator and an ideal voltage generator, respectively. For some realizations some ideal pulse generators will be used in order to switch on and off the comparator every period, and achieve a smaller current consumption.

The simulations used are:

- transient analysis in order to check the propagation delay and the current consumed

- dc sweep analysis for the measurement of  $V_{os}$

• Monte Carlo analysis is used to check the fulfilment of statistical requirements.

The number of runs for every Monte Carlo is set to 300 (appendix A).

FIGURE 3.6: Test-bench used for the simulations.

### 3.3 Analysis and results of comparator topologies

In this section all the different analysed and simulated comparator topologies are examined. The work starts with the simple circuit and then the topologies evolve depending on the problems faced during the development of the solution.

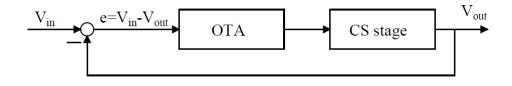

#### 3.3.1 Differential input pair with current mirror load

The comparator is mainly an amplifier with a differential input and a single-ended output. It is capable of amplifying the input differential voltage, saturating the output to  $V_{oH}$  or  $V_{oL}$  depending on the magnitude of  $V_{id} = V_{in,p} - V_{in,n}$ . The mode of operation of an OTA(figure 3.7) shows a transconductance region and a saturation region. While OTA are forced to operate on the former, a comparator has the simple task of saturating the output voltage to his maximum or minimum voltage. Therefore a comparator is usually an open-loop OTA. The advantage of this way of operation is that the comparator has a wider band and it does not show stability problems; as a consequence, it is not necessary a compensation path when a multi stage OTA is used as comparator[4].

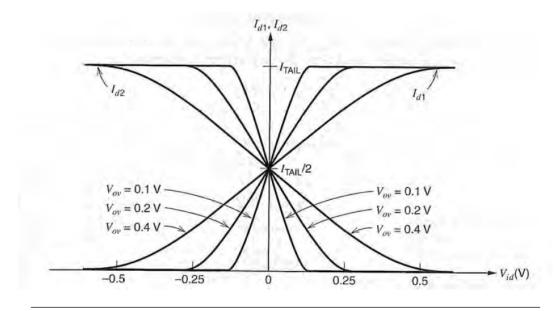

FIGURE 3.7: OTA transfer function[5].

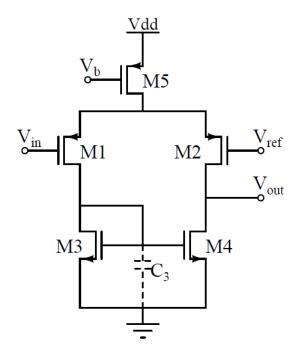

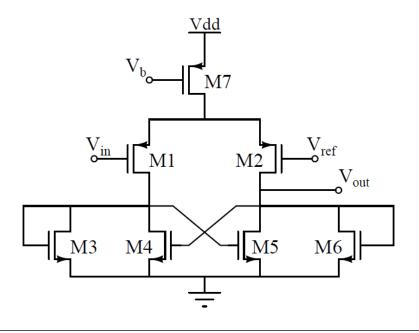

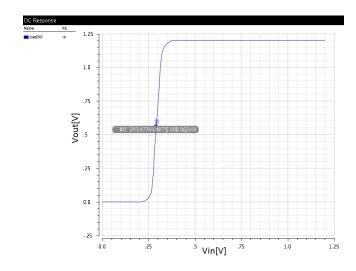

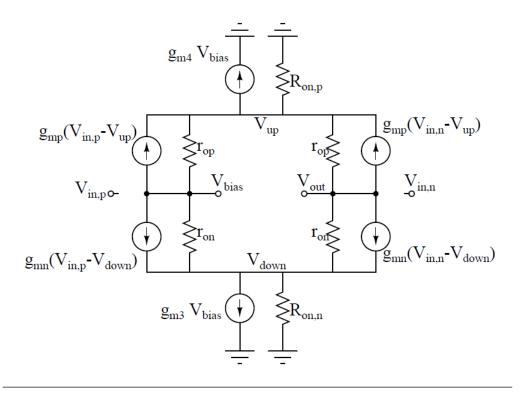

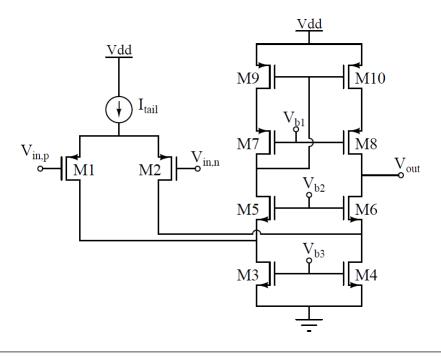

The most simple OTA to implement is a differential input pair loaded by a two MOS in a mirror configuration (figure 3.8), in order to match the single-ended topology. The input common mode is closer to ground than to  $V_{dd}$  since the inputs are  $V_{in,n} = V_{ref} = 300mV$  and  $V_{in,p}$  is a ramp voltage starting from 0V. This thing suggests the use of a pMOS input differential pair. For  $V_{in} = 0V < 300mV = V_{ref}$  almost the entire tail current flows in transistor M1, with the consequence of a zero current flowing in the branch of M2 and M4. This means that M2 is turned off and M4 is in triode region, with zero drain-source voltage; therefore the output voltage in this case is zero, following correctly the comparator definition. As  $V_{in}$  approaches  $V_{ref}$  the tail current begins to steer from the branch of M1 to that of M2. When  $V_{in} > V_{ref}$  the most of the current flows in M2 while little current is mirrored by the load since the current flowing through M1 is small. Therefore the output voltage is forced to raise from 0V to  $V_{dd}$  since the current charges the output capacitance.

In [4], [5] and [6], the frequency response of this circuit is given by a dominant pole and a couple zero-pole coming from the current mirror load. Therefore it is

Figure 3.8: Differential pair with current mirror load comparator circuit. The parasitic capacitance  $C_3$  responsible for the zero-pole couple is reported.

$$A_{v}(s) = \frac{V_{out}(s)}{V_{id}(s)} = A_{v0} \frac{1 + \frac{s}{\omega_{z}}}{\left(1 + \frac{s}{\omega_{p,D}}\right) \left(1 + \frac{s}{\omega_{p,ND}}\right)}$$

$$with \quad A_{v0} = g_{m1,2}(r_{o2} \parallel r_{o4})$$

$$\omega_{p,D} \simeq \frac{1}{(r_{o2} \parallel r_{o4}) C_{out}}$$

$$\omega_{p,ND} \simeq \frac{g_{m3}}{C_{3}}$$

$$\omega_{z} \simeq \frac{2g_{m3}}{C_{3}}$$

$$(3.12)$$

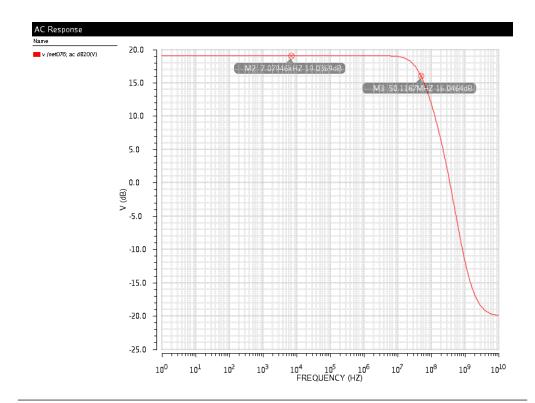

The output capacitance  $C_{out} \approx C_L$  and  $C_3 \approx 2C_{gs,n}$ , if the parasitic gate drain capacitances are considered negligible compared to  $C_{gs}$  and  $C_L$ . Therefore it is possible to assume that the 5-MOS OTA has a dominant pole frequency response, since the  $C_L$  is several times bigger than  $C_3$ . In fact the literature shows that  $\omega_{p,ND}$  and  $\omega_z$  come several decades after  $\omega_{p,D}$ . The frequency response Bode diagram of the comparator is reported in figure 3.9 demonstrating that it is a correct approximation. A single-ended OTA has even a pole and a zero that comes from the current mirrored by the active load; this pole-zero couple is usually at higher frequencies than the dominant pole and can be omitted in this basic analysis. The effect of pole-zero couple presence is that of slightly slowing the transient response.

FIGURE 3.9: Transfer function of the comparator with the current mirror load.

Having made these premises, the transfer function is:

$$H(s) = \frac{A_{v0}}{1 + s\tau_c} \tag{3.13}$$

The step response of a first order transfer function is well-known and equal to:

$$V_{out}(t) = A_{v0}V_{step}(1 - e^{-t/\tau_c})$$

(3.14)

However in this case the input is not a step but a ramp signal  $V_{in}(t) = mt$  where  $m = \frac{V_{ref}}{\Delta T}$  is the slope of the ramp. The Laplace-transform of the ramp is  $\mathcal{L}^{-1}\{mt\} = \frac{m}{s^2}$ . It is known from the signal theory that the transient response to a ramp input signal is simply the time integral of the step transient response, that is:

$$V_{out}(t) = \int_0^t A_{v0} m(1 - e^{-\tau/\tau_c}) d\tau = A_{v0} m(t + \tau_c e^{-t/\tau_c})$$

(3.15)

Once the time behaviour of the output voltage is obtained, it is possible to relate the propagation delay to the dominant pole of the comparator. In this way a relationship useful to find all the comparator's parameters can be obtained. However equation 3.15 is non-linear and not easy to solve; for this reason it is necessary to make an approximation,

substituting the exponential with its Taylor power series expression, interrupted at its second-order term.

$$V_{out}(t_p) = V_{THR} = A_{v0} m (t_p + \tau_c e^{-t_p/\tau_c})$$

$$\frac{V_{oH} - V_{oL}}{2} = V_{THR} = A_{v0} m \left( t_p + \tau_c \cdot \left( 1 - \frac{t_p}{\tau_c} + \frac{t_p^2}{2\tau_c^2} \right) \right)$$

(3.16)

Considering  $M = \frac{V_{THR}}{A_{v0}m}$  we obtain

$$2\tau_c^2 - 2M\tau_c + t_p^2 = 0 (3.17)$$

Once the desired delay  $t_p$  is fixed, equation 3.17 gives two time constants as solution (with a condition on the maximum DC gain). The relation between time constants and poles is simple:

$$\omega_c = 1/\tau_c \tag{3.18}$$

As it will be shown in equation 3.20, the tail current directly depends on the pole frequency, therefore the lowest pole has been chosen in order to obtain the lowest current consumption.

The dominant pole is given by  $\omega_c = \omega_{p,D} = \frac{1}{(r_{o2}|r_{o4})C_L}$  (equation 3.12). Moreover it is known from MOSFETs' model that its output resistance can be expressed by  $r_{o2,4} = \frac{1}{\lambda_{n,p}I_{d2,4}}$ . Sometimes it is referred as  $r_o = \frac{\eta_{n,p}L}{I_d}$  but there are no differences since in both cases the channel length L is a choice of the designer. The resistances' parallel is

$$r_{o2} \| r_{o4} = \frac{1}{(\lambda_n + \lambda_p) I_{d2,4}}$$

(3.19)

Combining equation 3.18 with 3.19 it is possible to find the tail current for the comparator, that is

$$I_{M1,2} = \frac{I_{M5}}{2} = \frac{\omega_c C_L}{\lambda_n + \lambda_p} \tag{3.20}$$

Afterwards, it is possible to find the transconductance of the differential pair and then  $(W/L)_1 = (W/L)_2$

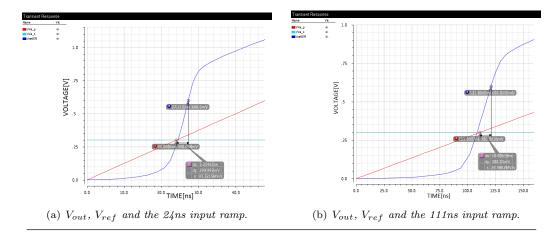

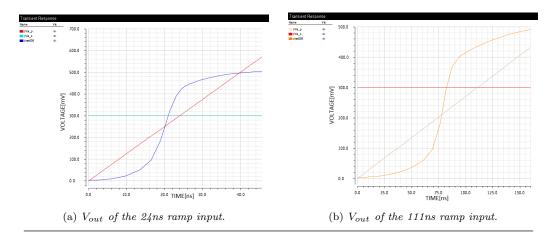

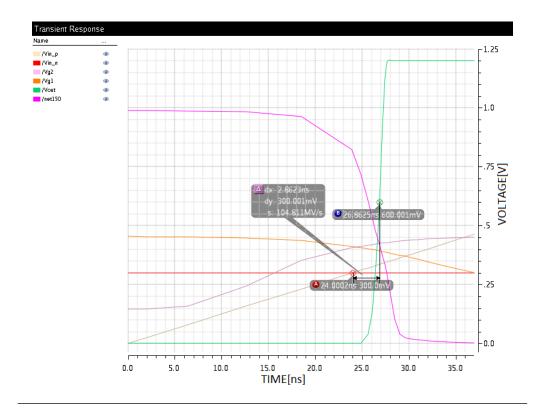

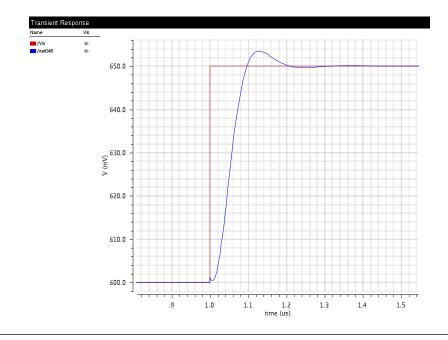

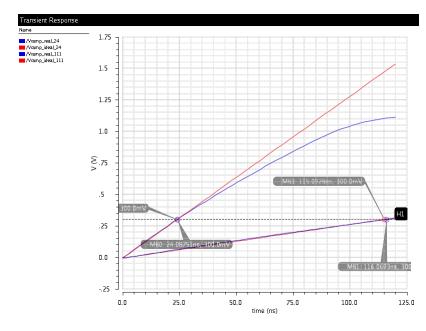

FIGURE 3.10: Output voltage and delay time with 24ns and 111ns input ramp.

$$g_{m1,2} = \frac{A_{v0}}{r_{o2} \| r_{o4}} \Rightarrow \left(\frac{W}{L}\right)_1 = \left(\frac{W}{L}\right)_2 = \frac{g_{m1,2}^2}{2\mu_p C_{ox} I_{d1,2}}$$

(3.21)

where the last equality has been derived from the well-known  $g_m = \sqrt{2I_d\mu_{n,p}C_{ox}W/L}$ . The dimensions of the load MOS M3 and M4 are the last parameters that has to be decided. Since  $g_{m3,4} = \mu_{n,p}C_{ox}W/L(V_{gs3,4} - V_{Tn}) = \frac{2I_{d3,4}}{V_{gs3,4} - V_{Tn}}$  then we find

$$\left(\frac{W}{L}\right)_{3} = \left(\frac{W}{L}\right)_{4} = \frac{2I_{d3,4}}{\mu_{n}C_{ox}(V_{gs3,4} - V_{Tn})}$$

(3.22)

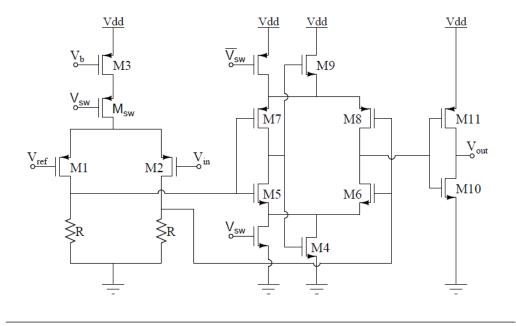

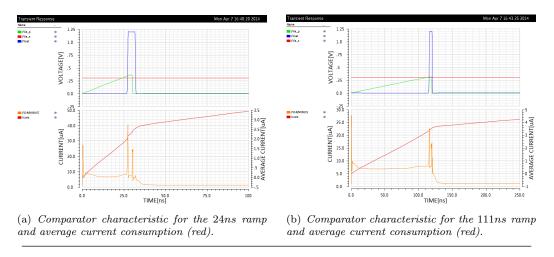

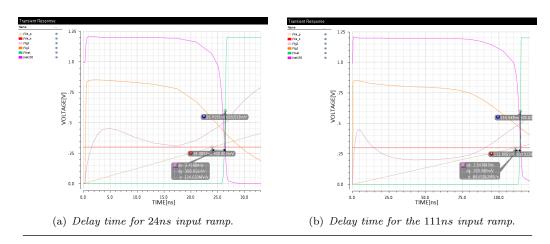

### Results

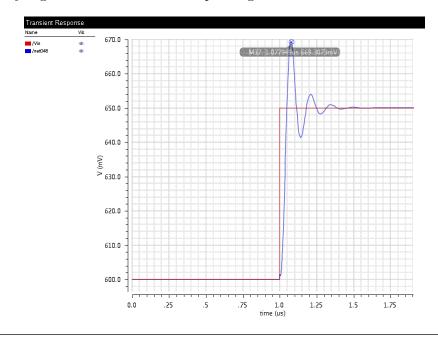

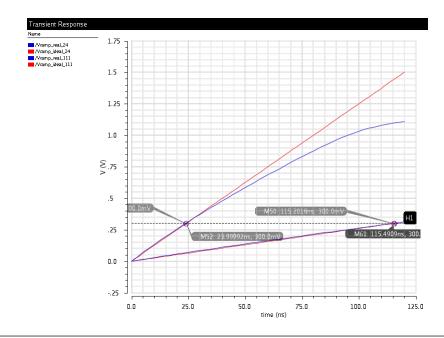

The comparator realized from the analysis above, shows a nominal delay  $t_p=3.21ns$  for the 24ns ramp and  $t_p=10ns$  for the 111ns ramp, with a tail current of  $I_{tail}=10\mu A$ . In figure 3.10 the results are shown. It is possible to see the input ramp (for simplicity it stops raising at 400mV), the voltage reference and the output voltage. This voltage is full-swing but it has not a fast change in the logic state since it is not possible to obtain a high gain from the OTA we are using. This gain can be increased using two cascaded inverters as output stage. In this way a full-swing digital output signal can be obtained. These two inverters form a digital buffer with the capability of increasing the output current and driving faster the output capacitance. However it is necessary to design the first inverter with a W/L capable of sinking the output capacitance without loading the output node of the comparator. As more than one inverter is cascaded, it is important to increase the W/L of a 2.72 factor, so as not to load the previous stage and to obtain the lowest delay[4],[7].

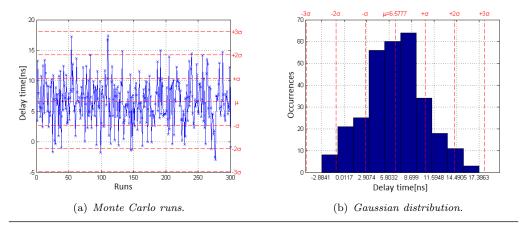

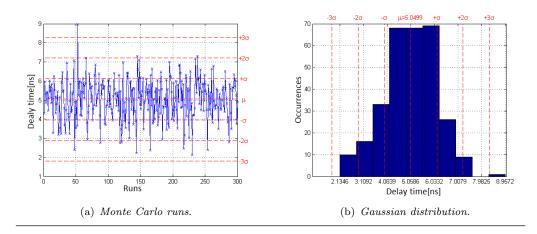

FIGURE 3.11: Statistical results for the 24ns period.

Figure 3.12: Statistical results for the 111ns period.

The requirements are nearly satisfied since the  $t_p$  is respectively the 14.04% for the 24ns and 9.46% for the 111ns. The most difficult task is the satisfaction of the requirement regarding the smaller period delay. The other difficult point regards the current consumption. In this circuit it is equal to the  $10\mu A$  of the tail current, plus the  $1\mu A$  of biasing current mirror, therefore  $I_{cons}=11\mu A$ ; the consumption requirement is not fulfilled. However we will not focus much on the consumption, since it is possible to reduce the average consumption per period switching off the comparator during the time when it is not needed and switching it on when the ramp voltage begins. In this way it is however necessary to ensure that the comparator is able to turn on completely in 24ns

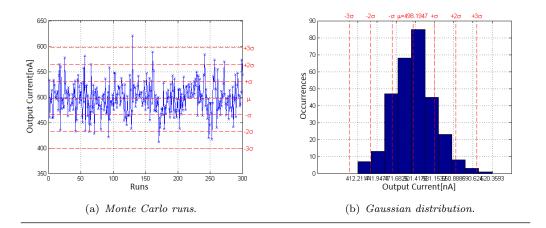

The last requirements that need to be checked are the ones regarding random mismatches and processing variations. Therefore a Monte Carlo analysis is done obtaining the results in figure 3.11 for the 24ns period, and in figure 3.12 for the 111ns period.

In table 3.1the results are reported, showing that the circuit is not fulfilling the requirements

| $\mathbf{T_{on}}$  | $\mu_{\mathbf{t_p}}$ | $\sigma_{\mathbf{t_p}}$ | $\sigma_{\mathbf{t_p}}$ | in | %   | of | $\mathbf{t_p}$ | $I_{cons}$ |

|--------------------|----------------------|-------------------------|-------------------------|----|-----|----|----------------|------------|

| $\overline{24ns}$  | 3.36ns               | $6.51 \cdot 10^{-10}$   |                         |    | 20% |    |                | $11\mu A$  |

| $\overline{111ns}$ | 10.69ns              | $3.42 \cdot 10^{-10}$   |                         |    | 30% |    |                | $11\mu A$  |

Table 3.1: Mirror load comparator Monte-Carlo results

In order to understand how it is possible to improve these values, it is important to check the correlation table. This table shows the parameters responsible for the statistical distribution, together with their correlation factor. Therefore it is necessary to reduce the influence of the factors with the highest correlation in order to reduce the value of  $\sigma$ . In this case the random mismatches of the differential input pair transistors are the responsible for the high standard deviation. This result is easy to understand since the input devices are responsible for the steering of the current, and for the input offset voltage (in this case  $V_{os} = 5mV$ ); therefore the variations in the current factor and input offset determine the variations in the propagation delay.

In order to reduce the standard deviation it is necessary to increase the gate area  $(W \cdot L)$  of the input devices (appendix A). Unfortunately increasing the gate area keeping the same W/L (and so the same  $g_m$ ) slows the transistors and so the steering of the current in response to the differential input voltage. This has the consequence of increasing the delay. A way to overcome this problem is to increase the tail current.

This set the designer in front of a strong trade-off between speed (and its mismatch and processing variations) and current consumption.

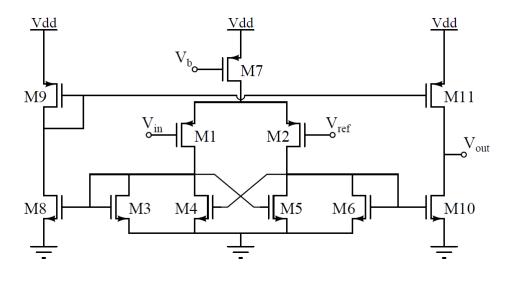

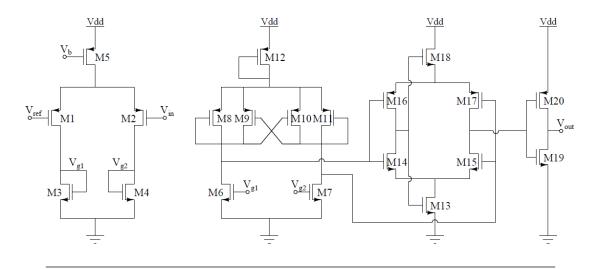

### 3.3.2 Differential input pair with cross coupled load

In the previous solution it is clear how the delay was fulfilling the basic requirements. However some problems arise when the circuit has to be optimized in order to reduce the mismatches and processes variability. Therefore a way to cope with this problem is to design a faster comparator, so that its delay can be increased when the statistical requirements have to be fulfilled.

A possible solution could be the use of a cross coupled configuration (Figure 3.13). In fact the cross couple introduces a positive feedback in the circuit, that provides a reduced propagation delay. Moreover this type of load can even present an hysteresis that comes from the positive feedback. However this function will not be used since the introduction of the hysteresis does not let achieve the lowest delay [4].

Inside this circuit there are two path of feedback: a negative feedback path, a currentseries feedback through the common source node of M1 and M2, and a positive feedback,

Figure 3.13: Cross coupled comparator circuit.

a voltage-shunt that takes place through the gate of M4 and the drain of M5 and vice versa[4].

The positive feedback can be easily understood looking at the small signal variations in the output voltage node. Assuming a small signal decrease of  $\Delta V_{out}$ , it means a decrease of M4 gate voltage. This fact leads to a decreasing of  $I_{d4}$  (through  $g_{m4}$ ). The drop of  $I_{d4}$  forces an increasing of  $I_{d3}$  with the result of enhancing the gate voltage of transistor M5, that leads to an increasing of  $I_{d5}$ . Therefore this enhanced current discharges the output capacitance and contributes to a further decrease in the output voltage. If the opposite initial assumption is made (small signal increase of  $\Delta V_{out}$ ) the effect and the analysis are analogous.

The same deductive reasoning is applied for the negative feedback path; assuming a small signal drop of  $\Delta V_{out}$ , this leads to a decreasing of  $I_{d4}$  and therefore of  $I_{d1}$ . However the current biasing the input differential pair is constant and a  $I_{d1}$  drop forces an increase of  $I_{d2}$ . This current charges the output capacitance, working against the discharge carried out by the positive feedback.

If the positive feedback dominates over the negative feedback, then the circuit shows an hysteretic transfer function, while when the negative feedback dominates over the positive one the circuit shows no hysteresis. The circuit shows hysteresis when the W/L of M4 and M5 is bigger than that of M3 and M6.

An histeretic behaviour is not required in the comparator, therefore the cross couple

FIGURE 3.14:  $V_{out}$ ,  $V_{ref}$  and  $V_{in}$  for the 24ns and 111ns ramp input.

load has transistor M4 and M5 smaller then M3 and M6.

The amplifier uses the negative resistance of the cross coupled to compensate the positive resistance of the diode load and achieve a higher gain [8]. The output resistance is

$$R_{out} \simeq \frac{1}{q_{m6} - q_{m5}} \tag{3.23}$$

The output transconductances of the transistor  $g_{o2}$ ,  $g_{o6}$  and  $g_{o5}$  have been neglected since they are negligible compared to  $g_{m6}$  and  $g_{m5}$ .

Assuming  $g_{m1} = g_{m2}$ ,  $g_{m4} = g_{m5}$  and  $g_{m3} = g_{m6}$ , the dc gain is therefore

$$A_{v0} \simeq -\frac{g_{m1,2}}{g_{m3,6} - g_{m4,5}} = -\frac{g_{m1,2}}{g_{m3,6}} \frac{1}{1 - g_{m4,5}/g_{m3,6}}$$

(3.24)

From the equation above it can be seen that if  $g_{m4,5}/g_{m3,6} = 1$  the gain could be infinite[8].

An important disadvantage of this amplifier is the limited output swing. In fact the diode-connected transistors clamp the voltage. Therefore, as it is possible to see from figure 3.14, the lower voltage  $V_{oL}$  is zero but the higher voltage  $V_{oH}$  is only a diode forward voltage over 0V. Clearly this is not the way of operation expected from a comparator; it is necessary to add a second stage able to provide a higher gain and a full-swing output.

The simplest solution is to use a push-pull second stage (figure 3.15). This is mainly an inverter stage whose current is given using the diode load as a mirror and therefore uses the mirrors to perform a differntial to single-ended conversion. The gain will be higher than in the previous circuit and it is given by:

$$\frac{\Delta V_1}{\Delta V_{in}} = -\frac{g_{m1,2}}{g_{m3,6}} \frac{1}{1 - R} \quad \text{with } R = \frac{g_{m4,5}}{g_{m3,6}}$$

$$\frac{\Delta V_{out}}{\Delta V_1} = -g_{m10}(r_{o10} || r_{o11})$$

$$\Rightarrow A_{v0} = g_{m10}(r_{o10} || r_{o11}) \frac{g_{m1,2}}{g_{m3,6}} \frac{1}{1 - R}$$

(3.25)

The transistor are chosen so as not to show an hysteretic behaviour, as it has been done in the previous case.

FIGURE 3.15: Cross coupled with push-pull output stage comparator circuit.

### Results

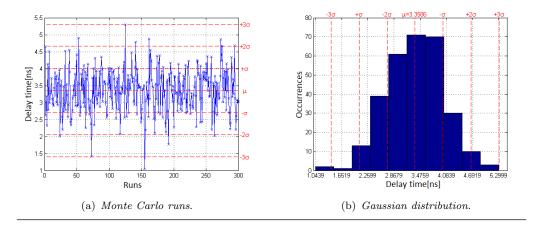

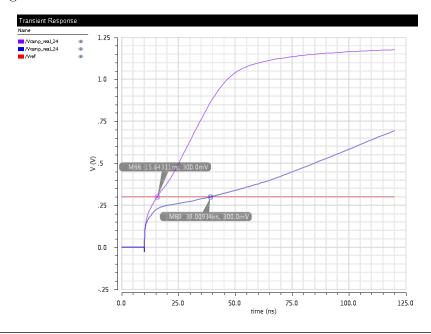

The comparator realized with this topology shows a nominal delay time of  $t_p = 2.87ns$  for the 24ns input ramp and  $t_p = 6.76ns$  for the 111ns input ramp. These results have been accomplished using the same tail current of the previous circuit,  $I_{tail} = 10\mu A$ . Comparing the two results, it is possible to see how the choice of using a cross-couple load in order to decrease the time delay was correct. In figure 3.16 the output of the comparator for the two ramps is shown. Since the comparator has low gain, two output inverters have been added in order to give the correct output. It is possible to notice that they do not add a considerable delay time. Moreover the gain of the comparator is increased since they can sink a lot of current for a small period of time.

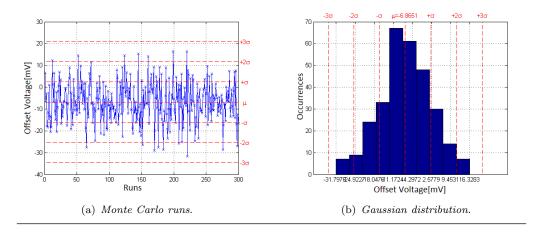

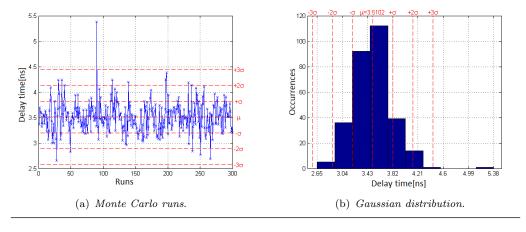

Figures 3.17 and 3.18 are obtained from a Monte Carlo analysis.

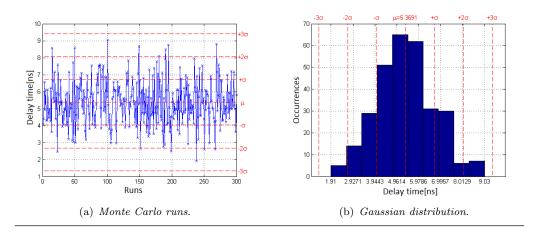

The results obtained are summarized in table 3.2.

FIGURE 3.16:  $V_{out}$ ,  $V_{ref}$ ,  $V_{in}$ , delay time and the inverter output for the 24ns and 111ns ramp input.

Figure 3.17: Statistical results for the 24ns period.

Figure 3.18: Statistical results for the 111ns period.

| $\mathbf{T_{on}}$  | $\mu_{\mathbf{t_p}}$ | $\sigma_{\mathbf{t_p}}$ | $\sigma_{\mathbf{t_p}}$ | in | %   | of | $\mathbf{t_p}$ | $I_{cons}$ |

|--------------------|----------------------|-------------------------|-------------------------|----|-----|----|----------------|------------|

| 24ns               | 2.79ns               | $7.1 \cdot 10^{-10}$    |                         |    | 25% |    |                | $13\mu A$  |

| $\overline{111ns}$ | 6.58ns               | $3.83 \cdot 10^{-9}$    |                         |    | 58% |    |                | $13\mu A$  |

Table 3.2: Cross-couple push-pull comparator Monte-Carlo results

It has been found from the correlation table that in this case the devices responsible for the unsuitable standard deviation are the transistors that form the load (M3, M4, M5, M6). This is mainly related to the small dimensions of transistors M4 and M5. In fact small devices have been used in order to obtain a fast comparison and avoid the hysteretic behaviour. Unfortunately small devices have by definition a small gate area  $(W \cdot L)$  and therefore they are more susceptible to random mismatches. As a consequence the delay time has a high variation that is related to the current factor and offset voltage mismatches. In fact an input DC sweep simulation reveals a relevant  $V_{os} = 6.5 mV$  (figure 3.19), and a Monte Carlo shows how its statistical variations are very important (figure 3.20).

Figure 3.19: Input  $V_{os}$  of the push-pull cross-coupled comparator.

A way to improve these results is that of increasing the area of the cross-coupled transistors. Increasing the area of these devices leads to a higher delay. For example quadrupling the gate area of transistors M3, M4, M5 and M6 gives a delay time of 4.9ns, but improves the statistical behaviour of the circuit giving a  $\sigma_{t_p} = 0.6 \cdot 10^{-9}$ .

Unfortunately the requirements lead to pursue a low delay time together with a limited statistical variation that this circuit is not able to provide. In fact the cross-couple gives the advantage of a fast comparison, but has many disadvantages. Again the limited output swing requires the use of a second stage, adding more delay time and current consumption; secondly the statistical variations are high when small delay time is needed.

FIGURE 3.20: Statistical results of the input  $V_{os}$ .

The increase of the tail current could be a solution, but it is not possible since the fulfilment of the current requirement could not be satisfied.

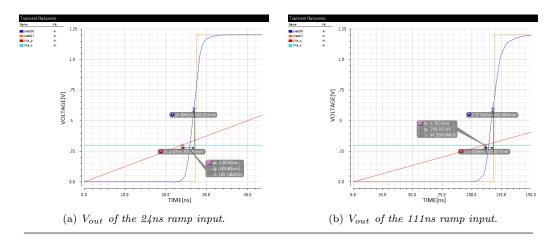

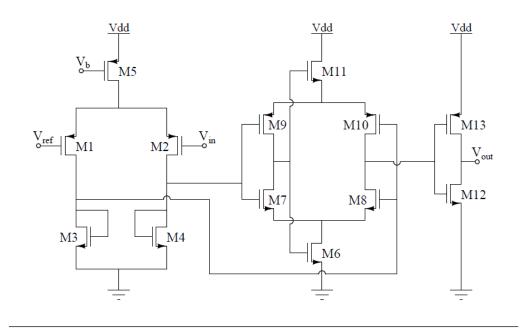

### 3.3.3 Self-biased comparator

In the last two sections two different comparators have been analysed. In these two solutions high attention was given to the fulfilment of the delay time requirement, and very little to the consumption requirement.

Both circuits used a tail current of  $10\mu A$  that itself exceeds the consumption requirement defined in section 3.2. In addition to the tail current even the current used by the push-pull stage has to be accounted in the average current consumption in a period.

It is therefore necessary to investigate on a way to reduce the current consumption. In the solutions seen, a tail current that continuously flows in the differential pair is used. This sets the minimum current consumption to the value of this current. Obviously it is not a good and efficient solution, since the comparator does not need to operate for most of the period. What really matters is that the comparator can be ready to sense the change of  $V_{id}$  sign and so to switch the output from 0V to  $V_{dd}$  or vice versa. The current that flows when the comparator has already switched and before it switches, can be accounted as a loss current. For this reason it is necessary to pursue an ideal solution able to provide a zero current consumption before and after the switch instant, while it is allowed to have an arbitrary high current in the few nanoseconds in which the comparator switches. In this way the average current consumption in a period can be really low since the circuit is biased only for a negligible time compared to the whole period. Clearly it is not possible to have a comparator that is completely off for the whole period except for the instant of the switch; such a solution implies the knowledge of the switching moment, fact that makes the comparator useless. Let us consider as an example the 24ns period; we are looking for a comparator that is switched off with

zero biasing current for 20ns and then in 4ns must be able to turn on and compare the two inputs, switching the output from  $V_{oL}$  to  $V_{oH}$ . A similar way of operation would require a suitable digital signal to turn on the biasing current and so the circuit just a few nanoseconds before the end of the period; of course this is quite impossible because we are designing a monostable to give a similar signal, otherwise the entire circuit would be useless. For this reason a good compromise would be to accept a low constant current biasing the comparator and then find a way to enhance this current only a few nanoseconds before the comparison event.

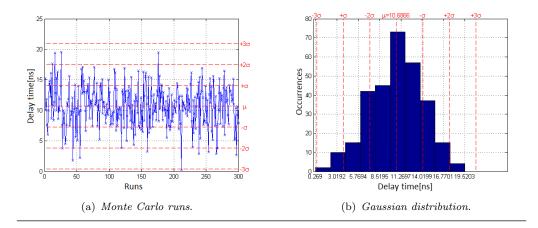

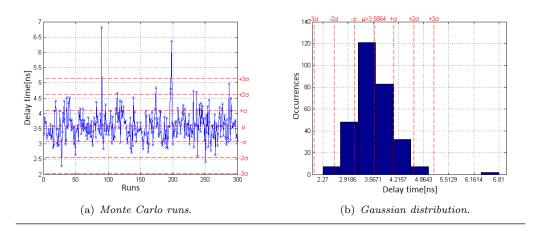

In order to achieve this result, a concept similar to how the push-pull second stage works was used, together with [9]. In fact the push-pull stage operates mirroring the current that flows in the load and uses it to obtain a full-swing voltage output signal. As the input ramp voltage increases, the current steers from M2 to M1, and so the current flowing in the diode load transistor increases. Unfortunately the diode load does not represent a high impedance node, and so a low current determines a low swing of the output node, such small that it does not ensure the saturation of the push-pull second stage output to  $V_{dd}$ . On the other hand a high current it is not available since low current consumption has to be pursued. A solution is to use a small biasing current and introduce a self biasing branch that is able to increase the tail current only when the comparator has to switch, which is exactly the moment when most of the current steers from M2 to M1. This self biasing branch mirrors the current of the diode load M6 and adds it as a tail current. In this way it is possible to obtain a current that increases itself as the circuit is approaching the switching point. Unfortunately once the comparator switches to  $V_{dd}$ , the self biasing branch continues to bias the circuit with a high tail current, which means a high and useless current consumption, since the comparison has already been done. If a switch is put in series to this branch (e.g. a pMOS), it can disable the self-biasing branch once the output node reaches  $V_{dd}$ . The gate of this transistor is then biased by the output voltage of the push-pull stage: when the output is low the self biasing is enabled while it is disabled when the comparator switches and the output goes to  $V_{dd}$ . The  $R_{on}$  of this switch does not represent a great problem so its W/L can be small. In figure 3.21 there is the entire circuit schematic.

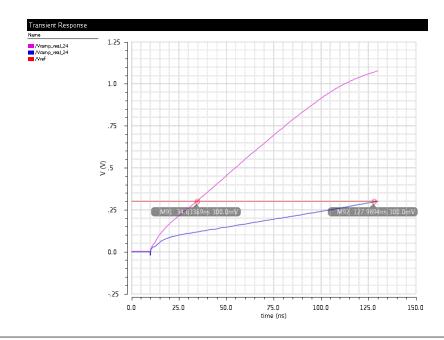

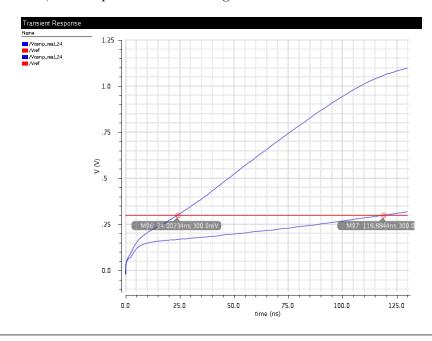

The circuit is exactly the same of the previous section, with the only difference of the adaptive bias branch. Therefore the theoretical analysis is the same as the one done previously, but the calculus are more difficult since the current flowing in the circuit changes during the time of operation. The design process has been developed from the previous circuit. Since the target is to reduce the current consumption, the tail current is reduced from  $10\mu A$  to  $3\mu A$ . The self biasing branch was designed as follows. As it is possible to see from the circuit the load current is mirrored two times, one with a K mirror factor and the other with a K' mirror factor. These two values are chosen such

Figure 3.21: Auto-bias comparator circuit.

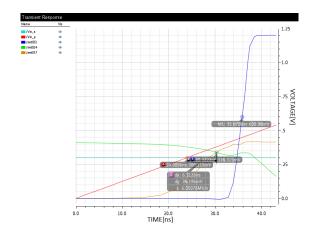

FIGURE 3.22: Output voltage and delay time with 24ns and 111ns input ramp.

that the total tail current (the continuous one and the auto-biasing one) is doubled, so as to keep the average current consumption really low. In figure 3.22 the simulation results are shown for the adaptive biasing current.