# University of Padova

# Department of Information Engineering

# **DEGREE THESIS**

# Amplifier Design for a Pipeline ADC in 90nm Technology

SUPERVISOR: Prof. Andrea Gerosa

**CANDIDATE:** Alessandro Michielin

| and the nSilition staff; in partic | Ferosa for the guidance throughou<br>cular Thierry and Laurent for their<br>c support on my internship period | r |

|------------------------------------|---------------------------------------------------------------------------------------------------------------|---|

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

|                                    |                                                                                                               |   |

# **Summary**

| Abstract                                                        | 5  |

|-----------------------------------------------------------------|----|

| Chapter 1                                                       | 7  |

| 1.0 Introduction                                                | 7  |

| 1.2 Thesis organization                                         | 8  |

| Chapter 2                                                       | 11 |

| 2.0 Ideal A/D Converter                                         | 11 |

| 2.1 Pipeline ADC                                                | 12 |

| 2.3 MDAC operation                                              | 13 |

| 2.4 Pipelined ADC Performance Characteristics                   | 15 |

| 2.5 Double sampling tecnique                                    | 16 |

| 2.6 Derivation of the Operational Amplifier Parameters          | 17 |

| 2.6.1 Open loop DC-Gain                                         | 18 |

| 2.6.2 Gain Bandwidth                                            | 19 |

| 2.6.3 Slew Rate                                                 | 21 |

| 2.6.4 Noise considerations                                      | 22 |

| Chapter 3                                                       | 25 |

| 3.0 Introduction                                                | 25 |

| 3.1 Current losses                                              | 26 |

| 3.1.1. Tunnelling                                               | 26 |

| 3.1.2. GIDL                                                     | 28 |

| 3.1.3 DIBL                                                      | 29 |

| 3.2 Punchtrough                                                 | 29 |

| 3.3 Surface scattering                                          | 30 |

| 3.4 Velocity saturation                                         | 31 |

| 3.5 Impact ionization                                           | 31 |

| 3.6 Hot electrons                                               | 32 |

| 3.7 The modification of the threshold voltage due to SC Effects | 32 |

| 3.8     | Output conductance reduction              | 35 |

|---------|-------------------------------------------|----|

|         | 3.8.1 Lightly doped drain implant         | 36 |

|         | 3.8.2 Halo Implant                        | 36 |

|         | 3.8.3 Anti Punchthrough Implant           | 38 |

| Chapter | 4                                         | 41 |

| 4.0     | Introduction                              | 41 |

|         | 4.1.1 Fifth stage amplifier: differential | 41 |

|         | 4.1.2 Folded cascode architecture         | 43 |

|         | 4.1.3 Cascode structure                   | 44 |

|         | 4.1.4 Double input pair                   | 46 |

|         | 4.1.5 Biasing strategy                    | 51 |

|         | 4.1.6 Power down switches                 | 54 |

|         | 4.1.7 Noise                               | 57 |

| 4.2     | .0 Stage 3 amplifier                      | 58 |

|         | 4.2.1 Telescopic cascode                  | 59 |

|         | 4.2.2 Output stage                        | 60 |

|         | 4.2.3 Two stages amplifier compensation   | 61 |

| Chapter | 5                                         | 67 |

| 5.0     | Introduction                              | 67 |

| 5.1     | Stage 5 common mode regulator topologies  | 67 |

|         | 5.1.1 Inverter based comparator           | 68 |

|         | 5.1.2 Current based comparison            | 68 |

|         | 5.1.3 Voltage buffers comparison          | 69 |

| 5.2     | Stage 5 common mode rejection             | 71 |

| 5.3     | Stage 3 commmon mode feedback regulator   | 73 |

| Chapter | 6                                         | 79 |

| 6.0     | Introduction                              | 79 |

| 6.1     | Reusability                               | 79 |

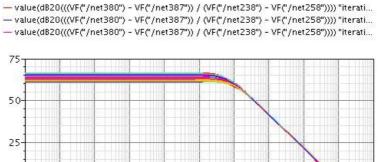

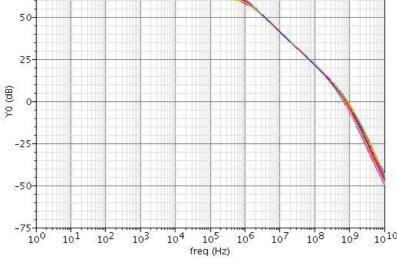

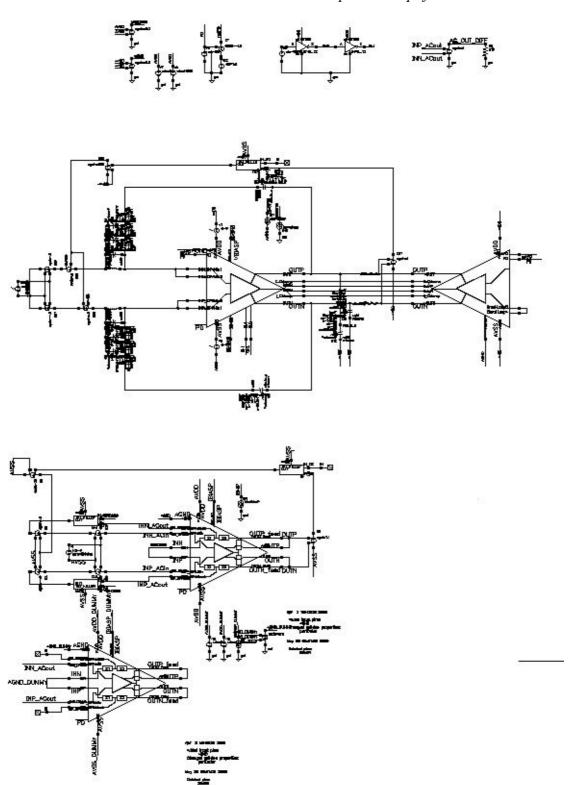

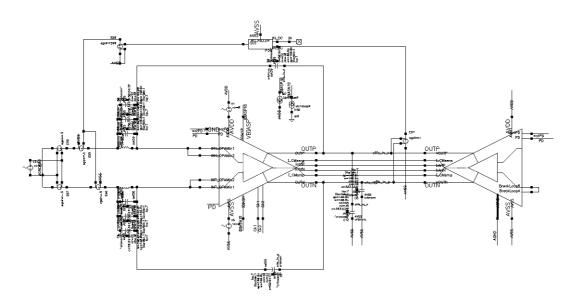

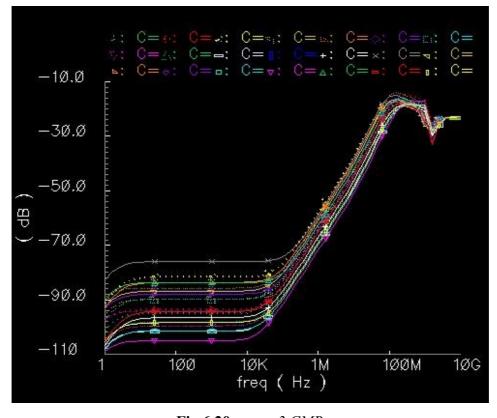

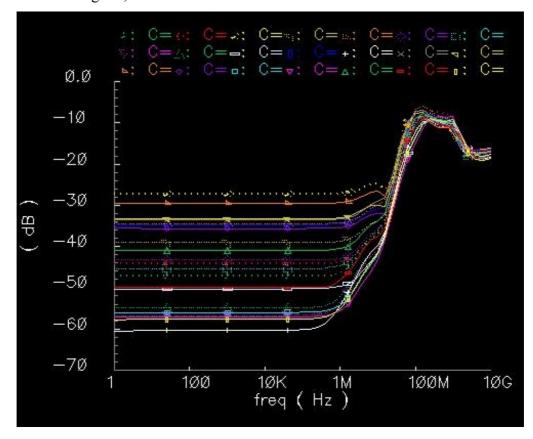

|         | 6.2.1 Stage 5 op-amp AC behaviour         | 81 |

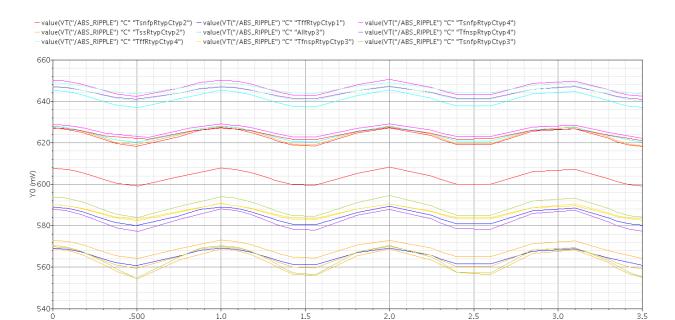

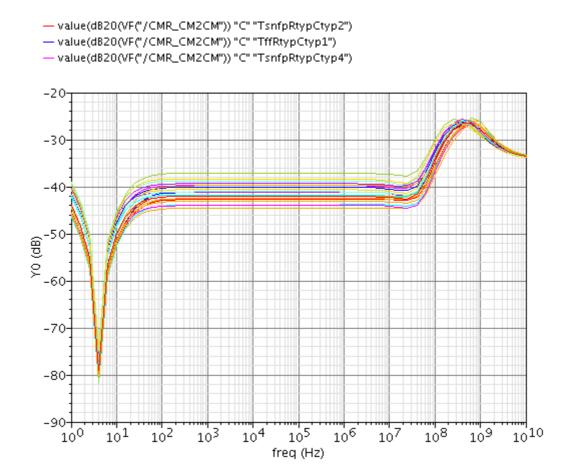

|         | 6.2.2 Stage 5 CM behaviour                | 84 |

|         | 6.2.3 Max dynamic configuration           | 88 |

| 6.2.4 Noise                             | 90  |

|-----------------------------------------|-----|

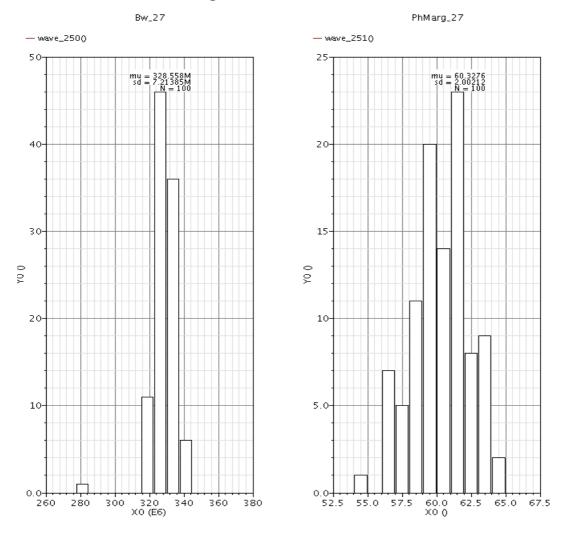

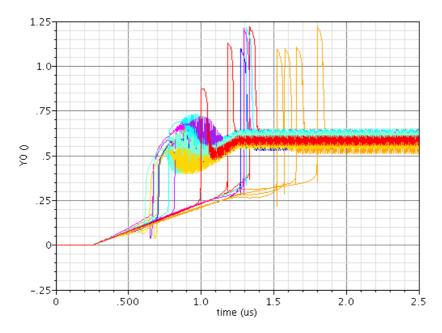

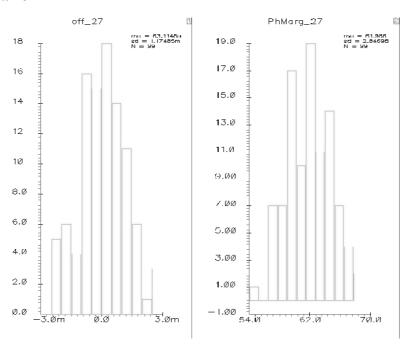

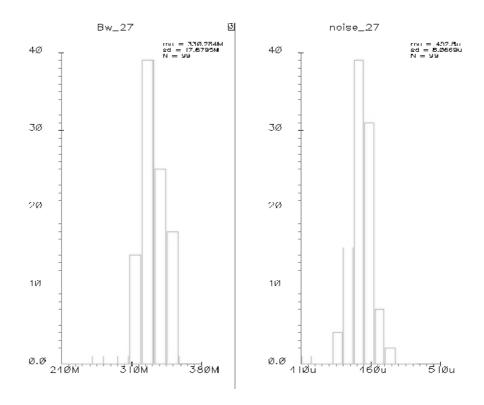

| 6.2.5 Montecarlo                        | 91  |

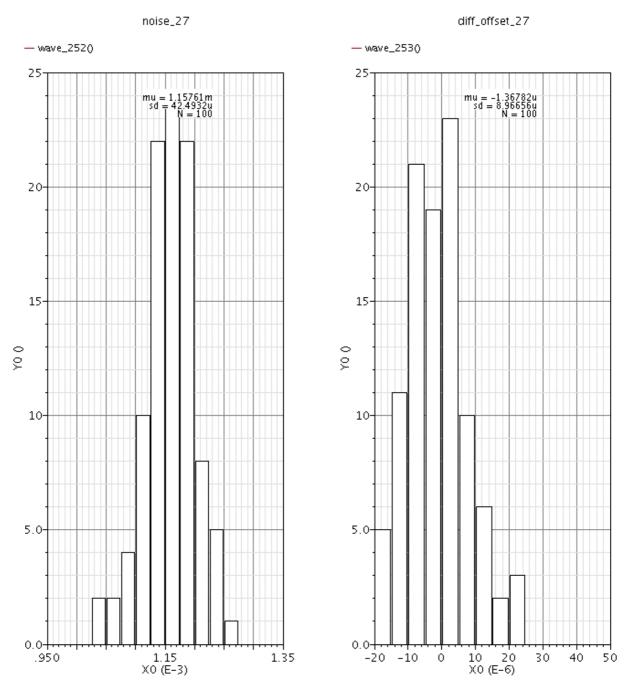

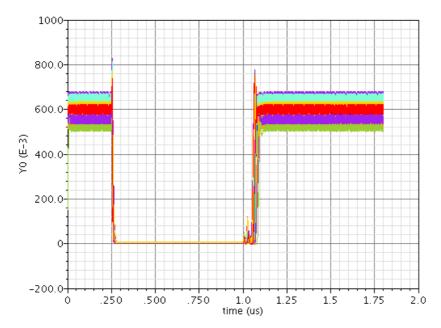

| 6.2.6 Start-up and switch down          | 93  |

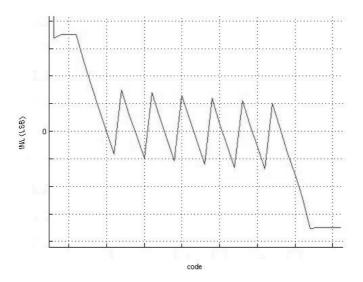

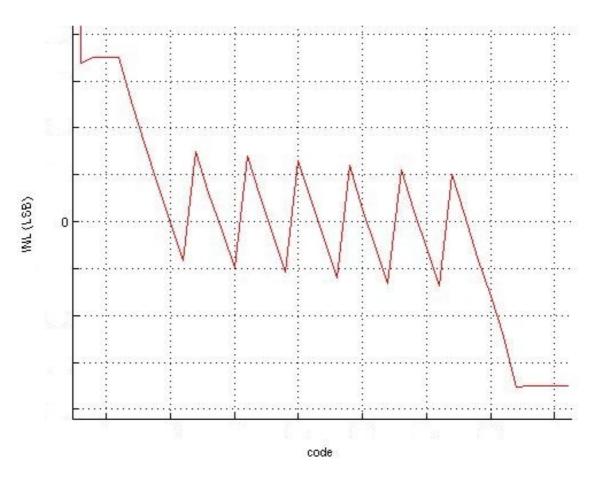

| 6.2.6 INL simulation                    | 95  |

| 6.3.0 Stage 3 characterization          | 97  |

| 6.3.1 AC behaviour                      | 97  |

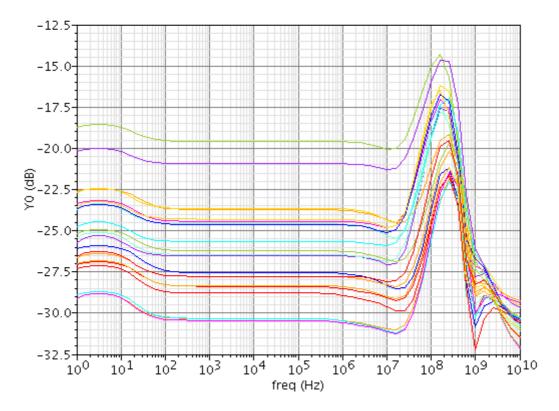

| 6.3.2 CM behaviour                      | 97  |

| 6.3.3 Max dynamic configuration         | 101 |

| 6.3.4 Noise                             | 102 |

| 6.3.5 Montecarlo                        | 102 |

| Chapter 7                               | 105 |

| 7.0 Introduction                        | 105 |

| 7.1 Main sources of variations          | 106 |

| 7.2 Interdigit structure                | 107 |

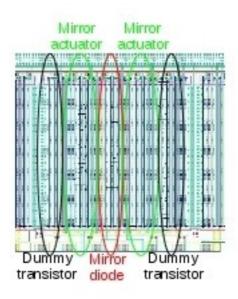

| 7.3 Antenna effect and antenna diodes   | 108 |

| 7.4 Dummy transistors                   | 110 |

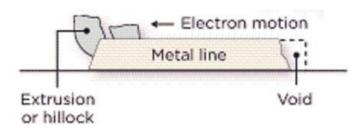

| 7.5 Electromigration                    | 112 |

| 7.6 General consideration for layouting | 114 |

| Chapter 8                               | 117 |

| 8.0 Introduction                        | 117 |

| 8.1 Future Work                         | 118 |

|                                         |     |

| Appendix A                              | 121 |

| ••                                      |     |

| Appendix B                              | 129 |

| Appendix C                              | 131 |

| - 4 | - |

|-----|---|

|-----|---|

# **Abstract**

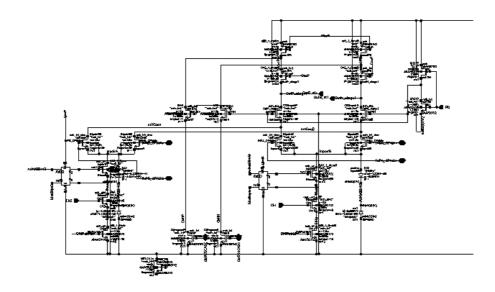

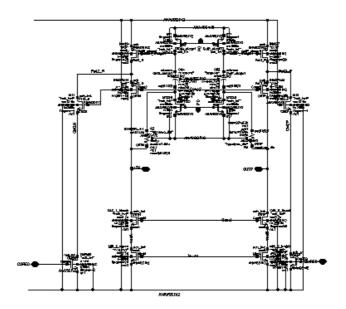

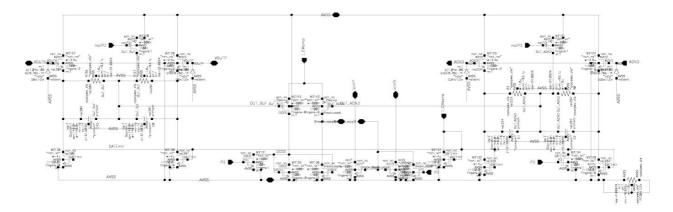

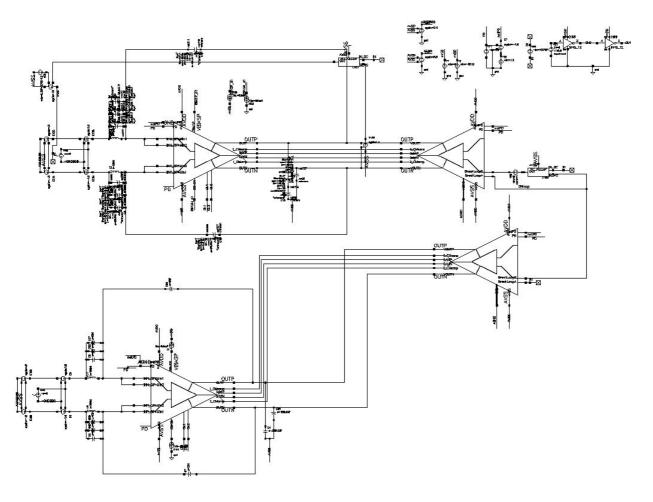

This paper explains the choices taken for the design of two full differential operational amplifiers. These op amp have been designed for the third and the fifth stage of a pipelined A/D Converter. It shows also the solutions found to reach high gain, wide bandwidth and short settling time, without degrading too much the output swing.

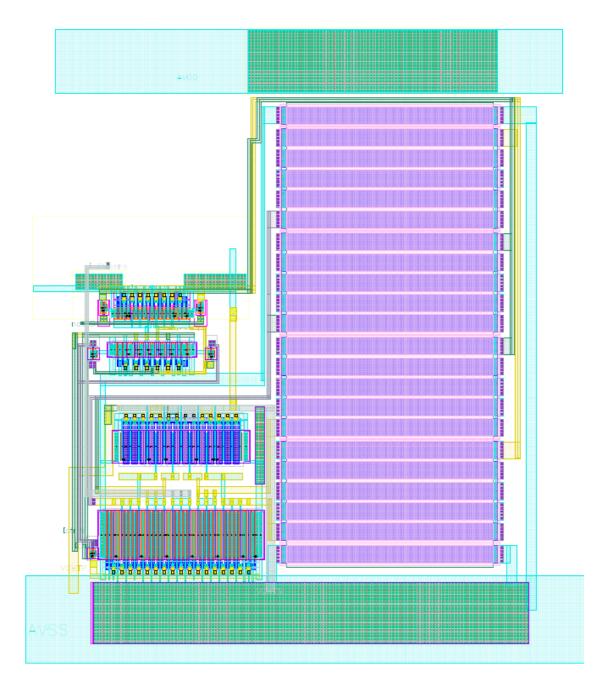

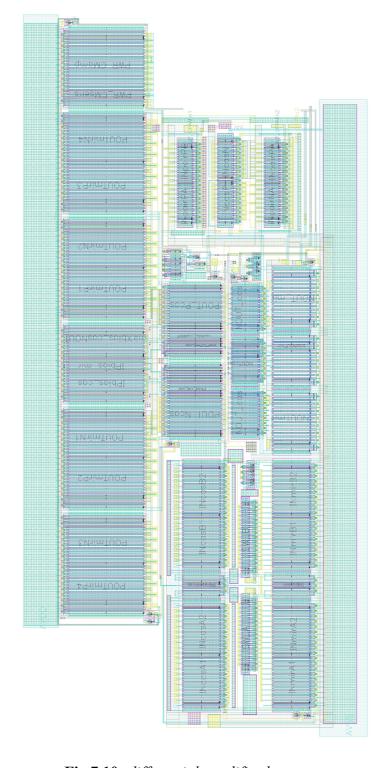

First the operational amplifier specification are extracted starting from the ADC architecture, then the issues related to the sub-micrometrical design are analysed; the different structures tested are then presented and the motivation of the final topology choice are shown. It presents then the op amp schematic implementation, the simulation results and the layout with the 90nm TSMC design kit.

|   | _ |   |

|---|---|---|

| - | b | - |

# **Chapter 1**

# Introduction

#### 1.0 Introduction

Operational Amplifiers are one of the most widely used building blocks for analog and mixed-signal systems. Nowadays, complementary metal-oxide semiconductor technology has become dominant over bipolar technology for analog circuit design in a mixed-signal system due to the industry trend of applying standard process technologies to implement both analog circuits and digital circuits on the same chip.

While many digital circuits can be adapted to a smaller device level with a smaller power supply, most existing analog circuitry requires considerable change or even a redesign to accomplish the same feat. With transistor length being scaled down to tens of nanometers, analog circuits are becoming increasingly more difficult to improve upon, in fact, if small geometries can improve speed decreasing the parasitic capacitance, the gain can be heavily affected. So, gain enhancement techniques are required, but these methods often require more complicated circuit structures and higher power supply voltage, and may produce a limited output voltage swing or introduce a significant noise contribution.

This thesis summarizes the work produced during a six months stage by nSilition sprl, a fabless company specialized in the design of high performances, low power converters. The design object was a 14bit, 200MS/s ADC. The converter is

implemented with a six stages pipeline architecture; the design is based on switch-capacitor circuitry. Each stage consists of an OTA and a subADC, and stage 5 and stage 3 OTA are the main objects of this dissertation. The devices are implemented through TSMC 90nmRF process technology.

Analog circuit design requires a good understanding of how the system and circuit work. Unlike digital circuitry which works with two distinct states, many parameters are under consideration for analog circuits which work with continuous values. Due to the multi-dimensional variables of an analog circuit, any slight change in the analog configuration like current, voltage, a transistor parameter, a device model, a manufacturing process, or a modified layout may cause significantly different performance. For analog design engineers, a good design methodology including intuition, mathematical methods, and specialized tools are assets. The design tools consists on Virtuoso Front to Back Design Environment for the schematics and layout, Matlab and Excel for the specifications extraction.

All the specifications required have been met.

#### 1.2 Thesis organization

The thesis is organized into eight chapters.

- Chapter 1 introduces the problem.

- Chapter 2 reviews the basic theory of A/D converters and the principle of the

pipelining; the main characteristics of the converter of the project are described

as well as the methodology used for the extraction of the amplifier specifications

in each stage.

- <u>Chapter 3</u> describes the main side effects related to the use of short channel devices and how they will affect the schematic modelization and the layout.

- In <u>Chapter 4</u> the design of two differential amplifiers is discussed. The different trade-off between gain, bandwidth and stability are presented, and the chosen solutions are explained.

- In <u>Chapter 5</u> the designs of the common mode regulators are discussed. Several different architectures are presented, the one chosen is described as well as the modifications applied to the main amplifier to reach the stability specifications.

- <u>Chapter 6</u> deals on the simulation sets: the testbenches are presented as well as the simulation results.

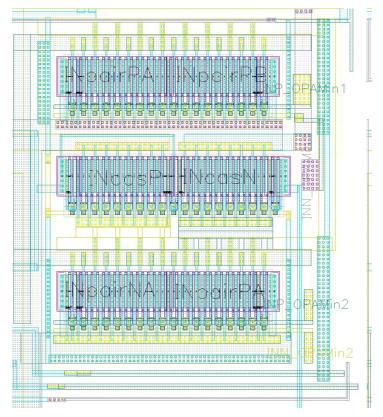

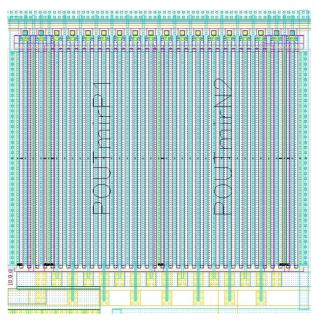

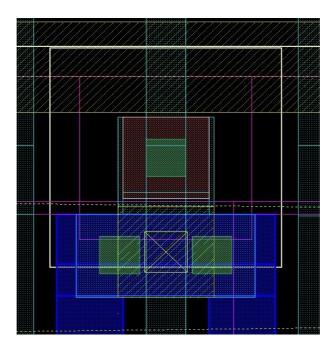

- In <u>Chapter 7</u> the layout work is shown. The main source of issues are presented as well as the solution chosen. The whole amplifier layout is shown.

- <u>Chapter 8</u> analyses the power consumption and describes the possible future works

|   |   | _  |   |

|---|---|----|---|

|   | 1 | 11 |   |

| - | 1 | u  | _ |

# Chapter 2

# **Pipeline converters**

# 2.0 Ideal A/D Converter

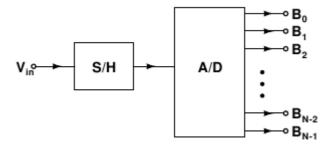

An analog-to-digital converter performs the quantization of analog signals into a number of amplitude-discrete levels at discrete time points. A basic block diagram of an A/D converter is shown in Fig. 2.1.

Fig 2.1: basic A/D converter

A sample-and-hold amplifier is added to the input to sample the analog input and to hold the signal information at the sampled value during the time needed for the conversion into a digital number. The analog input value  $V_{\rm IN}$  is converted into an N-bit digital value using the equation

$$\frac{V_{in}}{V_{ref}} = D_{out} + e_q = \sum_{m=0}^{N-1} B_m 2^m + e_q$$

(2.1)

In the equation,  $R_{\text{ref}}$  represents a reference value, which may be a reference

voltage, current or charge.  $B_{N-1}$  is the most significant bit and  $B_0$  is the least significant bit of the converter. The quantization error  $e_q$  represents the difference between the analog input signal  $V_{in}$  divided by  $R_{ref}$  and the quantized digital signal  $D_{out}$  when a finite number of quantization levels is used. Eq. 2.1 can be partly rewritten as

$$D_{out} = \sum_{m=0}^{N-1} B_m 2^m \tag{2.2}$$

The sampling operation of analog signals introduces a repetition of input signal spectra at the sampling frequency and multiples of the sampling frequency. To avoid aliasing of the spectra, the input bandwidth must be limited to not more than half the sampling frequency (Nyquist criterion).

# 2.1 Pipeline ADC

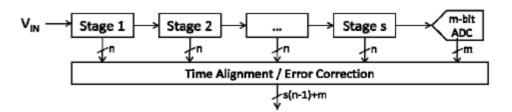

The pipelined is a popular architecture for modern applications of analog-to-digital converters due to its high sustained sampling rate, low power consumption, and linear scaling of complexity. Figure 2.2 shows a block diagram of a pipelined ADC. The term "pipelined" refers to the stage-by-stage processing of an input sample  $V_{\rm IN}$ .

**Fig 2.2:** basic pipeline ADC architecture

In the above diagram, the analog input voltage  $V_{\rm IN}$  enters the ADC. Each subsequent pipeline stage of the ADC resolves a certain n number of bits to be contributed to the final conversion output. The number of bits that each stage is responsible for quantizing is usually on the order of 1–5 bits. Simultaneously, after each stage has finished quantizing its input sample to n bits, it outputs an analog residue voltage that serves as the input to the next stage. After s stages of conversion, an m-bit ADC resolves the lower bits of the overall ADC digital output.

Each stage's digital decision is then passed to a digital block that properly timealigns the output bits and corrects for any errors in each stage. The final digital decision is then produced.

# 2.3 MDAC operation

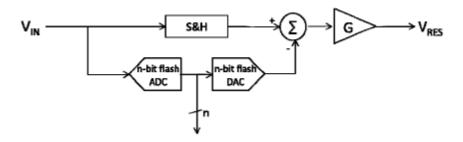

Each stage displayed in the block diagram shown above can be explored further. A typical pipeline stage is displayed in Fig. 2.3.

Fig 2.3: MDAC architecture

The input voltage is sampled and held in the sample-and-hold circuit embedded in each stage. Subsequently, an n-bit flash ADC quantizes the analog voltage and produces a digital decision of n bits. The digital decision is then fed through an n-bit flash DAC to be re-converted into an analog signal. The summation node presented in the above diagram takes the input voltage from the sample-and-hold circuit and subtracts the DAC voltage from it. This difference voltage is then fed through a gain stage with gain G to produce the residue voltage, the output voltage of this stage. In a typical pipelined ADC implementation, like the one under design, the sample-and-hold circuit and flash DAC are implemented in a single switched-capacitor circuit called a multiplying DAC, or MDAC. The amplification of the residue usually occurs with a closed-loop operational amplifier.

In equation form, the output of each pipeline stage can be described as:

$$V_{res} = G(V_{in} - DV_{res}) \tag{2.3}$$

The residue voltage,  $V_{RES}$ , becomes the input voltage to the next stage. The digital decisions versus input voltage and the residues versus input voltage of a typical pipelined ADC are displayed in Fig 2.4.

Fig 2.4: output of a MDAC

In Fig 2.4 the input voltage is swept through the whole operative range. The residue represents the amplified remainder from the subtraction of the DAC output voltage from the stage input voltage.

The pipelined ADC theory of operation is that each stage is responsible for quantizing a certain set of bits that will eventually become integrated into the final conversion output. For the generalized pipeline ADC described previously, each stage is responsible for quantizing n bits of the input sample. The final ADC output consists of a weighted sum of each stage's digital decision. The weightings are determined by the interstage gains, or the gains of the residue amplifiers within each stage. The final output is weighted according to:

$$x = \frac{D(0)}{G_0} + \frac{D(1)}{G_0 G_1} + \dots + \frac{D(N_s - 1)}{G_0 G_1 \dots G_{N_s - 1}}$$

(2.4)

where D(i) and G<sub>i</sub> represent the digital decision and the residue amplifier gain of each pipeline stage. The above equation suggests that later stages have a smaller weight in the final ADC output. This is indeed the case, as later stages resolve the lower bits of the overall conversion.

In the above example,  $D(N_s-1)$  represents the digital decision made by the final flash ADC, responsible for resolving the least significant bits of the output.

As mentioned before, each stage in a generalized pipelined ADC is responsible for resolving n bits of the ADC output, while the final flash ADC is responsible for

quantizing the m least significant bits of the ADC output. It is evident from the serialized operation of the pipelined ADC that some sort of time-alignment and error-correction circuitry is required for aligning each stage's digital decision to produce the final output.

## 2.4 Pipelined ADC Performance Characteristics

In general, the pipeline architecture enables the implementation of relatively high-resolution ADCs without sacrificing processing speed or power draw. Additionally, the linear complexity scaling inherent to the pipeline architecture makes the implementation of higher-resolution pipeline ADCs more manageable than with another ADC architecture.

The architecture of the pipelined ADC enables it to have a high throughput rate. This is evident in that pipelined ADCs can have sampling rates of a few MSps up to 200Msps, like the device discussed here. The reasoning for this is that the sample-and-hold circuit can begin processing the next analog input voltage sample as soon as the DAC, summation node, and gain amplifier have finished processing the previous sample. This pipelining action allows a high sustained sampling rate. Additionally, since each stage is only responsible for quantizing a low number of bits relative to the overall resolution of the pipeline ADC, each stage processes each sample relatively quickly.

The architecture of the pipelined ADC also allows it to scale linearly as complexity increases. In the generalized pipeline ADC discussed earlier, each stage has a small flash ADC that performs the quantization of the input sample. These flash ADCs are comprised of many comparators that are responsible for quantizing the sample. For an n-bit flash ADC, 2<sup>n</sup> comparators are needed to perform the conversion. In a pipeline ADC, higher overall resolution is obtained effectively by adding additional small flash ADCs in the form of having more stages.

A 14-bit pipeline ADC with 6 stages, 2.8 bits per stage, is implemented using only 42 comparators. This is in stark contrast to a 14-bit pure flash ADC, which would require  $2^{14} = 16384$  comparators in order to quantize the sample. The complexity in a pipeline ADC scales linearly and not exponentially, as is the case in a flash ADC. It also follows that fewer required comparators translates to much less power dissipation and power draw, another advantage of the pipeline architecture.

Although the pipeline ADC allows for high speed, lower power dissipation, and low complexity, there are still tradeoffs. For instance, the serialized nature of the conversion process means that there is a significant time delay between the sample that enters the first sample and hold of the first stage and when the digital alignment circuitry produces the correct output code.

Each stage in a pipeline ADC delays the data output by approximately one additional clock cycle. This data latency has to be accounted for when implementing a pipelined ADC.

Even in spite of these tradeoffs, the pipelined ADC architecture enables an ADC to have relatively high resolution, high speed, and low power dissipation, all with very few tradeoffs.

## 2.5 Double sampling tecnique

The property of the successive ADC stages working in opposite clock phases can be exploited by sharing the operational amplifier, the comparators and the all the logic part between two parallel component ADCs. This approach uses the double-sampling concept of switched capacitors circuits.

By using this technique, the equivalent sampling rate is doubled, but still the power dissipation remains almost the same as for an ADC having traditional single sampled pipeline stages with a half sample rate. The area can be reduced up to 40%. In contrast, the complexity of the pipeline stage is increased and more clock signals with different phases are needed.

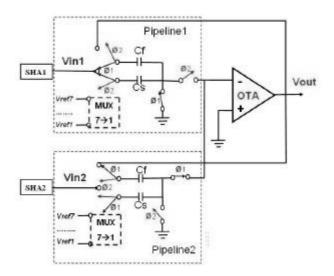

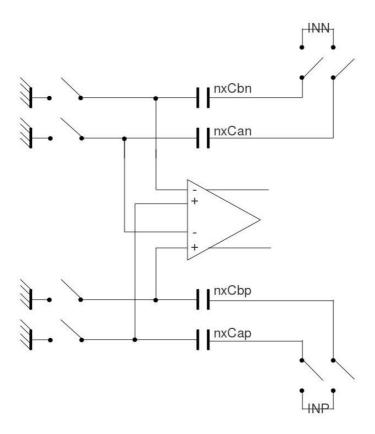

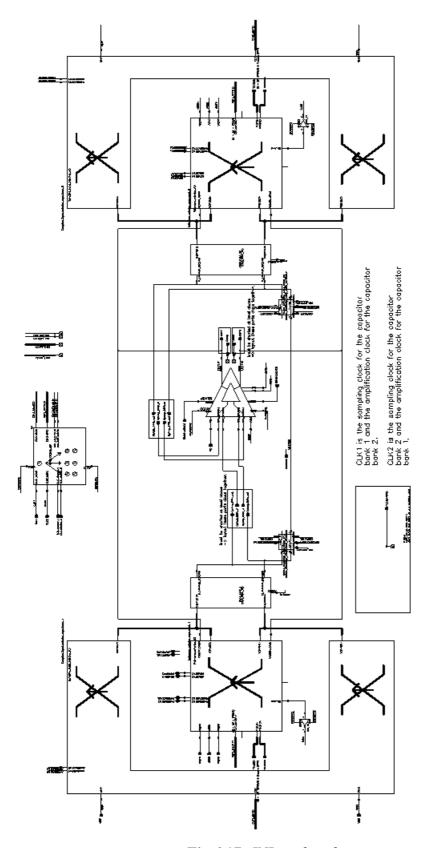

Scheme of the double sampling multiplying D/A converter is shown in fig 2.5.

Fig 2.5: double-sampling MDAC architecture

The capacitors of two parallel channels working on opposite clock phases share the same amplifier. While the pipeline1 samples the Vin1 signal onto the Cs and Cf capacitors independently of the amplifier, the pipeline2 switches to the amplification phase.

Two important side effects are caused by the amplifier sharing. First, the amplifier load capacitance is increased and affects its bandwidth. Second, the amplifier input offset is never reset; this can be tolerated by an adequate amplifier open loop DC-gain. The second one is not so critical in this design because of the differential architecture used, and thereby a symmetric compensation is possible.

# 2.6 Derivation of the Operational Amplifier Parameters

To calculate the DC-gain of the amplifier in a multiplying D/A converter it is necessary to deal with the resolution; instead, for the slew rate and GBW specifications, the sampling speed of the A/D converter is the key parameter.

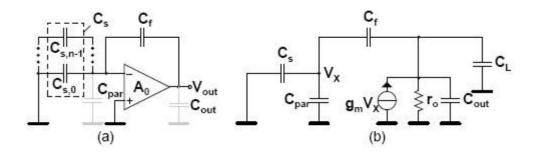

Fig 2.6: hold mode MDAC

The topology presented in fig 2.6 is assumed to be in the hold mode as single-ended for simplicity. However, all the calculations are performed for a fully differential topology. In this configuration, the input signal is sampled to the sampling capacitors

$$C_s = \sum_{j=0}^{n-1} C_{s,j} \tag{2.5}$$

and feedback capacitor  $C_f$ .

## 2.6.1 Open loop DC-Gain

The settling error at the output of the operational amplifier in a multiplying D/A converter, resulted from the finite open loop DC gain  $A_0 = g_m r_o$  is approximately given by

$$\varepsilon_0 = \frac{1}{A_0 \cdot f} \tag{2.6}$$

where *f* is the feedback factor

$$f = \frac{C_f}{C_f + \sum_{j=0}^{n-1} C_{s,j} + C_{par}}$$

(2.7)

which can be approximated in case of  $C_s$ ,  $C_f \gg C_{in}$  to equal

$$f \approx \frac{1}{2^{B_i}} \tag{2.8}$$

Assuming that the errors  $\varepsilon_{A0,i}$ , caused by the finite DC-gain in all the m = k-1 stages with a resolution of  $B_i + r$  bits, are the only error sources, the total input error of a N-bit A/D converter is

$$\varepsilon_{tot} = \sum_{i=1}^{m} \frac{\varepsilon_{A_{0,i}}}{\prod_{l=1}^{i} 2^{B_l}}$$

(2.9)

Applying some substitutions, the total error at the input can be rewritten

$$\varepsilon_{tot} = \sum_{i=1}^{m} \frac{2^{B_i}}{A_{0,i} \cdot \prod_{l=1}^{i} 2^{B_l}}$$

(2.10)

where  $A_{0,i}$  is the open loop DC-gain of the amplifier in the i<sup>th</sup> stage. At the same time, the total error at the ADC input must be less than LSB/2, which corresponds to  $\varepsilon_{tot} < 1/2^{\rm N}$  for an *N*-bit ADC. The inequality for the dimensioning of the amplifier open loop DC-gains becomes in general case

$$\sum_{i=1}^{m} \frac{2^{B_i}}{A_{0,i} \cdot \prod_{l=1}^{i} 2^{B_l}} < \frac{1}{2^N}$$

(2.11)

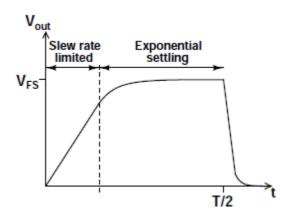

#### 2.6.2 Gain Bandwidth

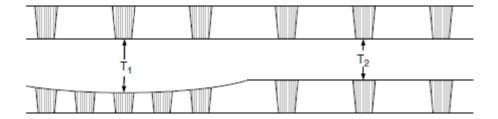

The successive pipeline stages operate in opposite clock phases, which gives a settling time of a half of the clock cycle (T/2). The settling time is determined first by the slew rate (SR) and finally by the gain bandwidth of the amplifier, as indicated in Fig. 2.7. Again, the MDAC topology of Fig. 2.6(a) is considered as fully differential.

Fig 2.7: settling of the output

The most commonly used OTAs can be modeled with a single-pole small-signal model of Fig. 2.6(b). The GBW frequency of an OTA is related to the transconductance  $g_m$  by

equation

$$GBW = \frac{g_m}{2\pi C_{L,tot}}$$

(2.12)

where the total load capacitance  $C_{L,tot} = C_L + C_{out}$  includes the parasitic output capacitance  $C_{out}$ . Using the symbols of Fig. 2.6(b), the corner frequency for the settling in the hold mode is

$$\omega_{-3dB} = \frac{gm}{C_{L,H}} \cdot f = \frac{g_m}{\frac{C_{L,tot}}{f} + \sum_{j=0}^{n-1} C_{s,j} + C_{par}}$$

(2.13)

It was arbitrarily chosen to reserve one third of the settling time for the SR limited part and two thirds for the GBW limited exponential settling. The error  $\varepsilon_t$  caused by the incomplete exponential settling during  $T/3 = 1/(3f_s)$  is given by

$$\varepsilon_{\tau} = e^{\frac{-\omega_{-3dB} \cdot 1}{3f_s}} = e^{\frac{-\frac{g_m}{(C_{L,lot}} + \sum_{j=0}^{m-1} C_{s,j} + C_{par})3f_s}}$$

(2.14)

In order to fulfill the resolution requirement, the settling error must be less than LSB/2, this case reduced to the input of the stage i, which results in a condition

$$\varepsilon_{\tau,i} < \frac{1}{2^{N_i}} \tag{2.15}$$

where  $N_i$  is the resolution of the remaining back-end pipeline including the ith stage. By combining Eq 2.8, 2.14, and 2.15, and solving the amplifier transconductance  $g_m$  yields

$$g_m > 3\ln 2 \cdot 2^{B_i} \cdot N_i \cdot f_S \cdot kC_{L:tot}$$

(2.16)

where the constant k>1 is the ratio between the effective load capacitance in the feedback configuration  $C_{L;H}$  and in open loop  $C_{L;tot}$ , resulting in

$$k = \frac{C_{L,H}}{C_{L,tot}} = 1 + \frac{C_f(\sum_{j=0}^{N-1} C_{s,j} + C_{par})}{(C_L + C_{out}) + (C_f + \sum_{j=0}^{N-1} C_{s,j} + C_{par})}$$

(2.17)

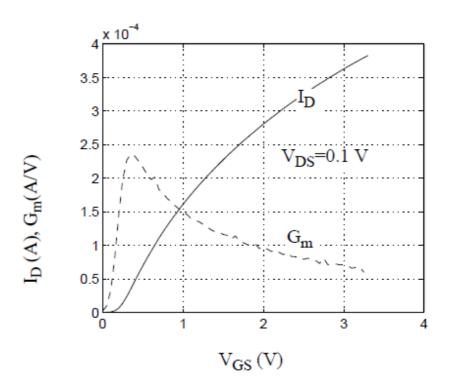

On the other hand, the transconductance is related to the width W, length L, and drain current  $I_D$  of the transistor by

$$g_m = \sqrt{2\mu C_{ox} \frac{W}{L} I_D} \tag{2.18}$$

where  $\mu$  is the mobility and  $C_{ox}$  the gate oxide capacitance. By substituting Eq. 2.18 into

Eq. 2.16, a condition for the minimum drain current of one transistor of the amplifier input differential pair  $I_D$  can be derived, and this can be expressed in terms of the minimal gain bandwidth

$$GBW > \frac{3\ln 2}{2\pi} \cdot N_i f_s \cdot \left( 2^{B_i} + \frac{\sum_{j=0}^{n-1} C_{s,j} + C_{par}}{C_{L,tot}} \right)$$

(2.19)

An interesting special case occurs when all the pipeline stages are identical, having  $B_i=B$  with equal correlated settling errors  $\epsilon_{t;i}=\epsilon_t$  being the only error sources. The total error reduced to the input of an N bit pipeline ADC is given by

$$\varepsilon_{tot} = \varepsilon_{\tau} \cdot \frac{1 - \frac{1}{2^{mB}}}{2^{B} - 1} \tag{2.20}$$

Again, for an N bit ADC it must hold that  $\epsilon_{tot} < 1/2^N$ . By combining this to Eqs. 2.8, 2.14, and 2.20, for the transconductance  $g_m$  holds

$$g_m > 3 (Nln2 - ln(2_B - 1)) \cdot 2^B \cdot f_S \cdot kC_{L;tot}$$

(2.21)

#### 2.6.3 Slew Rate

The slew rate of a single-stage OTA, like a folded cascode amplifier, is linearly dependent on the maximal current  $I_{max}$  charging and discharging the load capacitance.

To assure symmetrical slewing of the output, the currents of the output stages have to be equal to the current of the input stage, which indicates  $I_{max} = 2I_D$ . In a pipeline stage, the load capacitance during the slewing depends on the capacitor charging in the previous operation phase. In the worst case, the total load capacitance is  $C_{L;tot}+C_f$ . Using the symbols of Fig. 2.6(b), the slew rate is given in this case by

$$SR = \frac{I_{max}}{C_L + C_{out} + C_f} = \frac{2I_D}{C_{L,tot} + C_f}$$

(2.22)

For a worst-case slewing of the differential full-scale voltage  $V_{pp;diff}$ , the SR limited part being one third of the settling time, holds the condition

$$\frac{T}{6} \cdot SR > V_{FS,diff} \tag{2.23}$$

Substituting Eq. 2.22 into the inequality of Eq. 2.23, the minimum drain current set by the slew rate is given by

$$ID > 3f_{S} \cdot V_{FS; diff} \cdot (C_{L;tot} + C_{f})$$

$$(2.24)$$

#### 2.6.4 Noise considerations

The errors in each stage come from different sources:

- the finite gain of the amplifier;

- the incomplete settling;

- the mismatch in the capacitances or in the transistors.

It can be demonstrated that the last source is not critical for a stage number lower than 6; moreover the mismatch in the capacitor can be corrected by calibration. Furthermore, considering an equal contribution from all the sources, the allowed error increase from stage to stage by a factor equal to the interstage gain; this implies that the largest contribution will come from the first stages. So the capacitors can be scaled down from stage to stage with a factor equal to the square of the interstage gain, a relation coming from the area dependency model:

$$\sigma^2 \left( \frac{\Delta C}{C} \right) = \frac{A_C^2}{WL} = \frac{A_C^2 C_{ox}}{C} , \qquad (2.25)$$

down to a minimum dictated by other constraints.

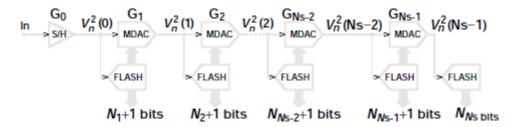

Fig 2.7: noise through the pipeline

Concerning the input referred noise

$$V_{n,inref}^{2} = \frac{V_{n}^{2}(0)}{G_{0}^{2}} + \frac{V_{n}^{2}(1)}{G_{0}^{2}G_{1}^{2}} + \dots + \frac{V_{n}^{2}(N_{s}-1)}{G_{0}^{2}G_{1}^{2}\dots G_{N_{s}-1}^{2}}$$

(2.26)

where  $N_s$  is the number of stages and  $G_x$  is the residual gain of stage x.

The thermal noise comes mainly from the switches and the amplifiers. It can be modelized in a MDAC as following:

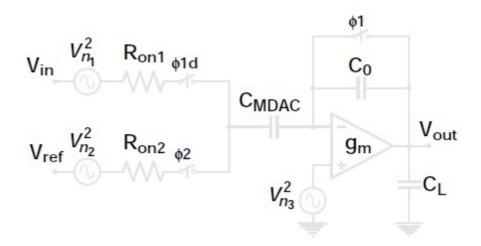

Fig 2.8: noise source modelization

Considering:

$$G = \frac{C_{MDAC}}{C_0}$$

$$R_{on2} = \frac{1}{\alpha q_m}$$

(2.27)

with  $\alpha$  a design variable,

$$R_{eq} pprox rac{2}{3 g_m}$$

$B_{eq} pprox rac{\pi}{2} rac{g_m}{2 \pi C_{eq}}$   $C_{eq} = C_{MDAC} + C_L + rac{C_{MDAC} C_L}{C_0}$

it is possible to express the noise at the output as:

$$V_{n,outref}^{2} = \frac{kT}{C_{MDAC}} + (4kTR_{on2} + 4kTR_{eq}) \cdot B_{eq} \cdot G^{2}$$

(2.28)

where the first addend represents the sampled and held contribution, the first addend inside brackets is the broadband contribution from the switches during the amplification phase, and the second addend inside brackets is the contribution coming from the amplifier.

| - 24 | - |

|------|---|

|------|---|

# Chapter 3

# Design issues in short channel devices

## 3.0 Introduction

As the technology scales beyond 100-nm sizes, the traditional design approach needs to be modified to take into account the increased process variation, interconnect processing difficulties, and other physical effects.

It can be experienced a significant increase in gate tunnelling current, due to the thin oxide. Subthreshold leakage and gate tunnelling are no longer second-order effects. If these effects are not taken care of, the result will be a dysfunctional devices, especially for digital circuits, but also the analog environment will be heavily changed.

Typically, processor designers tape out their design when the verification confidence level is high enough. Debug continues on silicon, which is usually several orders of magnitude faster and would result in getting a product to market sooner. Now, due to the increased mask cost and longer fabrication turnaround time, the trade-off to arrive at the most cost-effective product and shortest time to market will certainly be different [28].

The transistor figure of merit is now deviating from the reciprocal of the gate length. Furthermore, global wiring is not scaling, whereas wire resistance below  $0.1~\mu m$  is increasing exponentially. This is due primarily to surface scattering and grain-size

limitations in a narrow trench, resulting in carrier scattering and mobility degradation. The gate dielectric thickness is approaching atomic dimensions and at 1.2 nm in the 90nm node is about five atomic layers of oxide. Source—drain extension resistance is getting to be a larger proportion of the transistor "on" resistance. Source—drain extension doping has been increased significantly, and the ability to reduce this resistance has to be traded off with other short-channel effects, such as hot-carrier injections and leakage current due to band-to-band tunnelling. Source—drain diffusions are getting so thin that implants are at the saturation level and resistance can no longer be reduced unless additional dopants can be activated.

The main effects related to the reduced dimensions of the devices are the following:

- -the current losses

- -the mobility degradation

- -the threshold shift

- -the gate capacitance shift

- -the g<sub>ds</sub> degradation

#### 3.1 Current losses

The device under design has no consumption particularly stringent specification; of course power must be minimized, but, since it is not the main goal, the leakage in devices like the amplifier can be neglected (it is not the case instead for the switches, the bootstrap or other other circuital elements, but, since it is not object of this dissertation, the problem will be ignored).

The mail losses are related on:

- -gate tunnelling through the oxide

- -junction losses

- -hot carrier current

- -gate induced drain leakage

## 3.1.1. Tunnelling

The electron wave function, for oxides below 8-10nm, can spread up to the anode; in particular, depending on the electric field, several cases are possible:

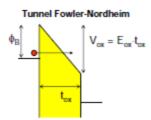

a)  $E_{ox} > \phi_B / t_{ox}$ : the voltage drop is higher than the barrier. In this case, since the tunnelling is an energy conservative process, the electron sees a triangular potential barrier, having an effective depth of  $t_{eff} = \phi_B / E_{ox}$ , as depicted in fig 3.1.

Fig 3.1: Fowler-Nordheim tunnelling

This process, named Fowler-Nordheim Tunnel, implies that the electron reaches the conduction band of the oxide and crosses it up to the anode, following the relation:

$$J_{FN} = A \cdot E_{OX}^2 \cdot \exp(\frac{-B}{E_{OX}}) \tag{3.1}$$

where B a constant related on the barrier height and on the type of oxide.

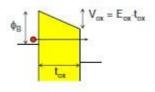

b)  $E_{ox} < \phi_B / t_{ox}$ : the voltage drop is lower than the barrier height and the electron sees a trapezoidal barrier; it jumps directly from the conduction band of the cathode to the one of the anode, so this process is named Direct Tunnel.

**Fig 3.2:** Fowler-Nordheim tunnelling

The expression is similar to the Fowler-Nordheim case:

$$J_D \simeq A \cdot E_{OX}^2 \cdot \exp\left(\frac{-B}{E_{OX}} \cdot \left(1 - \left(1 - \frac{q \cdot E_{OX} \cdot t_{OX}}{\varphi_B}\right)^{3/2}\right)\right)$$

(3.2)

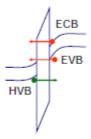

c) the Hole Valence Band tunnelling, where the process is similar to the previous cases

but involving holes instead of electrons; although it is less probable, since the barrier is intrinsically higher (5eV).

d) the Electron Valence Band tunnelling, where the hypothesis is that the electron has an energy at the same level of free energy level in the anode. The gate voltage required is around 1.5V, but, when an electron crosses the oxide, it sees a barrier of about 4.2eV, so this happens only for an oxide thickness lower than 2-3nm.

Fig 3.3: different tunnelling

e) the Band-to-band tunnelling; when the doping is high, the charge space region drops: if also the potential between source and drain is high, then the band bending is strong. This means that the electrons from the cathode see a triangular voltage barrier Eg high; so the electron can jump in the conduction band by tunnelling.

The expression is similar to the one for the Fowler-Nordheim; the difference is in the carrier concentration and in the state function density:

$$J_{b-b} = \frac{A \cdot E \cdot V_d}{\sqrt{E_g}} \cdot \exp\left(\frac{-\beta \cdot E_g^{3/2}}{E}\right)$$

(3.3)

#### 3.1.2. GIDL

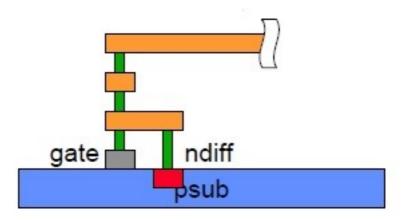

It happens typically when the gate is grounded and the drain is at Vdd. The MOS is off, there is no channel and the substrate is in accumulation. All the silicon surface is in accumulation, so it behaves like a high doped p semiconductor, where the Fermi level is close to the valence band. Then, at the Si/SiO<sub>2</sub> interface, it forms a p+/n/n+ junction which can create a band-to-band tunnel leakage.

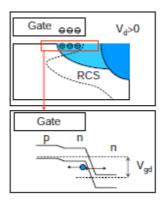

Fig 3.4: gate induced drain lowering

#### 3.1.3 **DIBL**

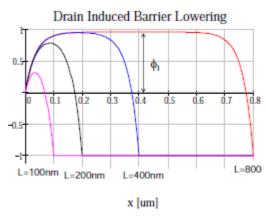

The current flow in the channel depends on creating and sustaining an inversion layer on the surface. If the gate bias voltage is not sufficient to invert the surface ( $V_{GS} < V_{T0}$ ), the carriers (electrons) in the channel face a potential barrier that blocks the flow.

Increasing the gate voltage reduces this potential barrier and, eventually, allows the flow of carriers under the influence of the channel electric field. In small-geometry MOSFETs, the potential barrier is controlled by both the gate-to-source voltage  $V_{GS}$  and the drain-to-source voltage  $V_{DS}$ . If the drain voltage is increased, the potential barrier in the channel decreases, leading to drain-induced barrier lowering (DIBL). The reduction of the potential barrier eventually allows electron flow between the source and the drain, even if the gate-to-source voltage is lower than the threshold voltage.

**Fig 3.5:** *Drain-induced barrier lowering*

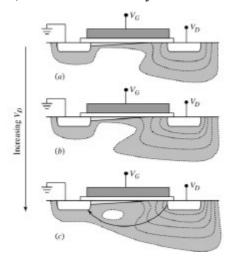

## 3.2 Punchtrough

The expressions for the drain and source junction widths are:

$$x_{dD} = \sqrt{\left(\frac{2\varepsilon_{Si}}{qN_a}\right)\left(V_{DS} + \varphi_{Si} + V_{SB}\right)}$$

(3.4)

and

$$x_{dS} = \sqrt{\left(\frac{2\varepsilon_{Si}}{qN_a}\right)(\varphi_{Si} + V_{DB})}$$

(3.5)

where  $V_{SB}$  and  $V_{DB}$  are source-to-body and drain-to-body voltages.

When the depletion regions surrounding the drain extends to the source, so that the two depletion layers merge (i.e., when  $x_{dS} + x_{dD} = L$ ), punchtrough occurs. Punchthrough can be minimized with thinner oxides, larger substrate doping, shallower junctions, and obviously with longer channels.

It can be a destructive effect, so it must be strictly avoided.

Fig 3.6: punchtrough

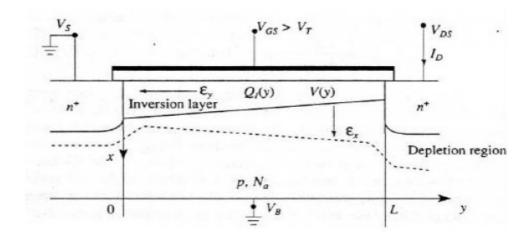

## 3.3 Surface scattering

When the channel length becomes smaller due to the lateral extension of the depletion layer into the channel region, the longitudinal electric field component  $e_y$  increases, and the surface mobility becomes field-dependent. Since the carrier transport in a MOSFET is confined within the narrow inversion layer, and the surface scattering (that is the collisions suffered by the electrons that are accelerated toward the interface by  $e_x$ ) causes reduction of the mobility, the electrons move with great difficulty parallel to the interface, so that the average surface mobility, even for small values of  $e_y$ , is about half as much as that of the bulk mobility.

Fig 3.7: MOS cross section showing the field contributions

## 3.4 Velocity saturation

The performance short-channel devices is also affected by velocity saturation, which reduces the transconductance in the saturation mode. At low  $e_y$ , the electron drift velocity  $v_{de}$  in the channel varies linearly with the electric field intensity.

It can be noted that the drain current is limited by this effect instead of pinchoff. This occurs in shortchannel devices when the dimensions are scaled without lowering the bias voltages.

Using  $v_{de(sat)}$ , the maximum gain possible for a MOSFET can be defined as

$$g_{m} = Wc_{ox}V_{de(sat)}$$

(3.6)

## 3.5 Impact ionization

Another undesirable short-channel effect, especially in NMOS, occurs due to the high velocity of electrons in presence of high longitudinal fields that can generate electronhole pairs by impact ionization, that is, by impacting on silicon atoms and ionizing them.

It happens as follow: normally, most of the electrons are attracted by the drain, while the holes enter the substrate to form part of the parasitic substrate current. Moreover, the region between the source and the drain can act like the base of an npn transistor, with the source playing the role of the emitter and the drain that of the

collector. If the holes are collected by the source, and the corresponding hole current creates a voltage drop in the substrate material of the order of 0.6V, the normally reversed-biased substrate-source pn junction will conduct appreciably. Then electrons can be injected from the source to the substrate, similar to the injection of electrons from the emitter to the base. They can gain enough energy as they travel toward the drain to create new e-h pairs. The situation can worsen if some electrons generated due to high fields escape the drain field to travel into the substrate, thereby affecting other devices on a chip.

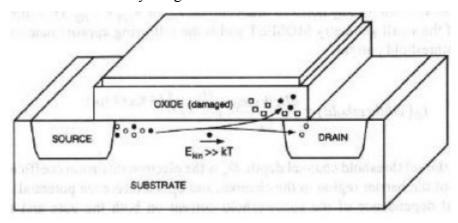

#### 3.6 Hot electrons

Another problem, related to high electric fields, is caused by so-called hot electrons. This high energy electrons can enter the oxide, where they can be trapped, giving rise to oxide charging that can accumulate with time and degrade the device performance by increasing  $V_T$  and affect adversely the gate's control on the drain current.

Fig 3.8: hot-electron damages

# 3.7 The modification of the threshold voltage due to Short-Channel Effects (SCE)

The equation giving the threshold voltage at zero-bias

$$V_{T0} = V_{FB} + 2\varphi_F + \left(\frac{1}{C_{ox}}\right)\sqrt{2q \cdot \varepsilon_{Si} \cdot N_A(2\varphi_F)} + \frac{qD_I}{C_{ox}}$$

(3.7)

is accurate in describing large MOS transistors, but it collapses when applied to small-geometry MOSFET. In fact that equation assumes that the bulk depletion charge is only due to the electric field created by the gate voltage, while the depletion charge near n+

source and drain region is actually induced by pn junction band bending. Therefore, the amount of bulk charge the gate voltage supports is overestimated, leading to a larger  $V_T$  than the actual value.

The electric flux lines generated by the charge on the MOS capacitor gate electrode terminate on the induced mobile carriers in the depletion region just under the gate. For short-channel MOSFET, on the other hand, some of the field lines originating from the source and the drain electrodes terminate on charges in the channel region. Thus, less gate voltage is required to cause inversion. This implies that the fraction of the bulk depletion charge originating from the pn junction depletion and hence requiring no gate voltage, must be subtracted from the  $V_T$  expression.

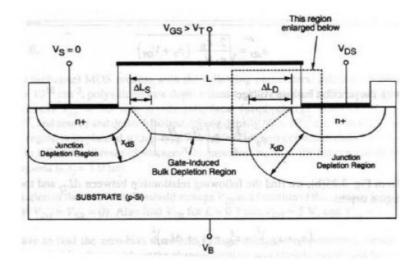

Fig 3.9: gate-induced bulk depletion region

The figure shows the simplified geometry of the gate-induced bulk depletion region and the p-n junction depletion regions in a short channel MOS transistor. It can be noted that the bulk depletion region is assumed to have and asymmetric trapezoidal shape, instead of a rectangular shape, to represent accurately the gate-induced charge. The drain depletion region is expected to be larger than the source depletion region because the positive drain-to-source voltage reversed-biases the drain-substrate junction. We recognize that a significant portion of the total depletion region charge under the gate is actually due to the source and drain junction depletion, rather than the bulk depletion induced by the gate voltage. Since the bulk depletion charge in the short channel device is smaller than expected, the threshold voltage expression must be modified to account

for this reduction:

$$V_{T0 \text{short ch}} = V_{t0} - \Delta V_{t0}$$

where  $V_{T0}$  is the zero-bias threshold voltage calculated using the conventional longchannel formula and  $\Delta V_{T0}$  is the threshold voltage shift (reduction) due to the shortchannel effect. The reduction term actually represents the amount of charge differential between a rectangular depletion region and a trapezoidal depletion region.

Let  $\Delta L_S$  and  $\Delta L_D$  represent the lateral extent of the depletion regions associated with the source junction and the drain junction, respectively. Then, the bulk depletion region charge contained within the trapezoidal region is:

$$Q_{B0} = -\left(1 - \frac{\Delta L_S + \Delta L_D}{2L}\right) \sqrt{4q \epsilon_{Si} N_A \varphi_f}$$

(3.8)

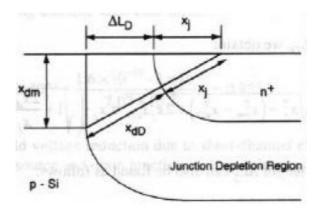

To calculate  $\Delta L_S$  and  $\Delta L_D$ , the simplified geometry shown in the figure can be useful.

Fig 3.10: geometry of the depletion region

Here,  $x_{dS}$  and  $x_{dD}$  represent the depth of the pn-junction depletion regions associated with the source and the drain, respectively. The edges of the source and drain diffusion regions are represented by quarter-circular arcs, each with a radius equal to the junction depth,  $x_j$ . The vertical extent of the bulk depletion region into the substrate is represented by  $x_{dm}$ . The junction depletion region depths can be approximated by

$$x_{dD} = \sqrt{\left(\frac{2\epsilon_{Si}}{qN_A}\right)(V_{DS} + \varphi_0)}$$

(3.9)

and

Chapter 3: Design issues in short channel devices

$$x_{dS} = \sqrt{\left(\frac{2\epsilon_{Si}}{qN_A}\right)(\varphi_0)} \tag{3.10}$$

with the junction built-in voltage

$$\varphi_0 = \frac{kT}{q} \ln \left( \frac{N_D N_A}{n_i^2} \right) \tag{3.11}$$

From figure,

$$\Delta L_D \approx x_j \left( \sqrt{1 + \frac{2x_{dD}}{x_j}} - 1 \right) \tag{3.12}$$

Similarly, the length  $\Delta L_S$  can also be found as follows:

$$\Delta L_S \approx x_j \left( \sqrt{1 + \frac{2x_{dS}}{x_j}} - 1 \right) \tag{3.13}$$

Now, the amount of the threshold voltage reduction  $\Delta V_{T0}$  due to short-channel effects can be found as:

$$\Delta V_{T0} = \frac{1}{C_{ox}} \cdot \sqrt{4q \,\epsilon_{Si} \, N_A \,\varphi_F} \cdot \frac{x_j}{2L} \cdot \left[ \left( \sqrt{1 + \frac{2x_{dD}}{x_j}} - 1 \right) + \left( \sqrt{1 + \frac{2x_{dS}}{x_j}} - 1 \right) \right]$$

(3.14)

The threshold voltage shift term is proportional to  $x_j/L$ . As a result, this term becomes more prominent for MOS transistors with shorter channel lengths, and it approaches zero for long channel MOSFET where  $L >> x_j$ .

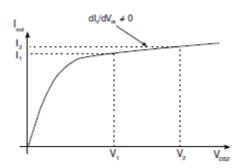

#### 3.8 Output conductance reduction

High performance logic devices are optimized for good drive current, low leakage and SCE control which incorporate super halo and double-pocket structures. These structures however, often result in low output resistance, device gain, transconductance-to-drive current ratio and matching properties [1]. Low output resistance is the result of increase ID with VD in saturation regime. Three components are associated with this increase, namely channel length modulation (CLM), drain-induced-barrier-lowering (DIBL) and substrate current body effect (SCBE).

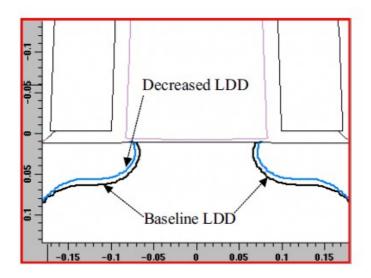

It can be found that gds is most sensitive to LDD dose, halo dose, halo tilt and APT dose and energy.

# 3.8.1 Lightly doped drain implant

Fig 3.11: Junction profile for different LDD dose

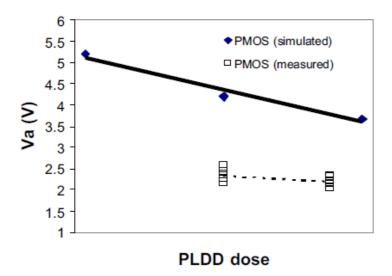

Fig 3.12 shows the sensitivity of  $V_A$  to LDD dose for a PMOS transistor;  $V_A$  is defined as

$I_{\text{D}}/g_{\text{ds}}-V_{\text{D}}$ , the Early voltage.

If the LDD dose is increased,  $V_A$  decreases because the effective channel becomes shorter, as shown in Figure 3.11. Shorter channel length results in larger residual DIBL thus causing output resistance to decrease.

Fig 3.12:  $V_A$  dependence on PLDD dose

## 3.8.2 Halo Implant

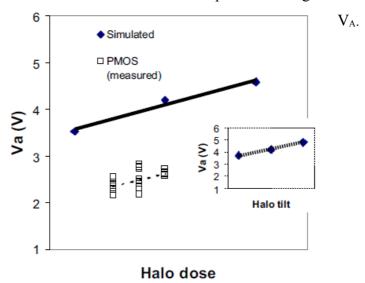

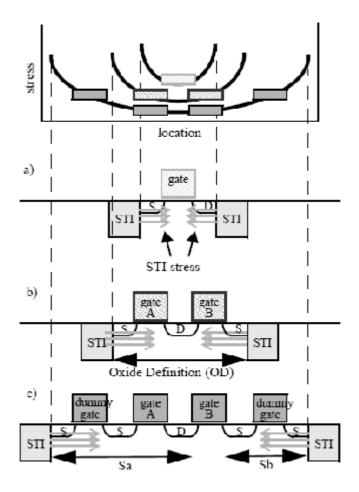

The halo is a p+ implant applied in the proximity of the source and drain junctions; its purpose is to reduce the effects of charge sharing, DIBL and punchthrough.

Figure 3.13 shows the drawback of this technique: increasing the halo dose increases

Fig 3.13:  $V_A$  dependence on halo dose

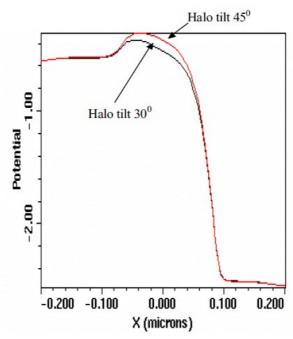

Increasing the halo tilt angle also increases  $V_A$  as shown in the inset: a larger tilt angle places the halo implant almost at the centre of the channel. The additional arsenic in the channel lessens the effect of DIBL as shown in Figure 3.14. However, increasing halo dose also causes  $I_{dsat}$  to decrease. Experimental studies have also shown that pocket implant has tradeoff effects on  $V_A$  and  $I_{dsat}$ .

Fig 3.14: Potential barrier shifts at different halo tilt angle

#### 3.8.3 Anti Punchthrough Implant

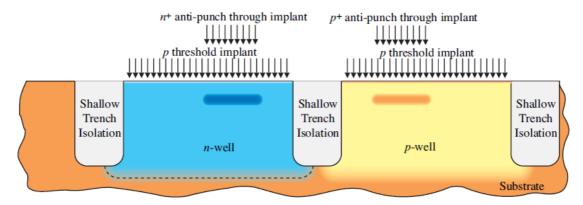

The natural thresholds of the NMOS is about 0V and of the PMOS is about 1.2V. An p implant is used to make the NMOS harder to invert and the PMOS easier resulting in threshold voltages balanced around zero volts.

Fig 3.15: Anti punchthrough implants

Also an implant can be applied to create a higher-doped region beneath the channels to prevent punch-through from the drain depletion region extending to source depletion region. This technique is typically named anti punchthrough (APT) implant.

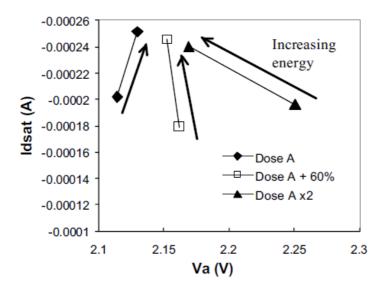

**Fig 3.16:** Effects of APT implant on  $V_A$  and  $I_{dsat}$

Fig 3.16 shows the plot of  $I_{dsat}$  versus  $V_A$  at different APT implant conditions. As APT energy implant is increased,  $V_A$  shows a contradict trend depending on the implant dose used. At high dose and high energy, the plot is shifted to the up-left when energy is

increased. However, the plot shifted to the up-right as energy is increased at low APT implant dose and energy. At low dose and energy, increasing the APT implant energy forms super steep retrograde channel, which has positive effects for analog applications.

| - 40 - |

|--------|

|--------|

# **Chapter 4**

# **Differential Amplifier design**

#### 4.0 Introduction

In general, operational amplifiers are amplifiers with an open loop gain high enough to ensure that the closed loop transfer characteristic with negative feedback is approximately independent of the op amp gain. To ensure wide swing and noise immunity, a fully differential architecture is used; so a differential and a common mode behaviour will be investigated

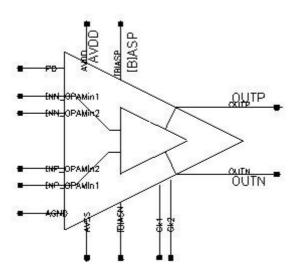

## 4.1.1 Fifth stage amplifier: differential

The design effort is directed towards the power consumption minimization. Different circuital topologies have been taken in exam: the goal is to reach the following specifications:

| Gain                 | 48,29dB              |

|----------------------|----------------------|

| GBW                  | 1177MHz              |

| Dynamic Range        | 1.1Vpp               |

| Noise (inp_referred) | 41,19nV/ $\sqrt{Hz}$ |

| Current Capability   | 0.28mA               |

**Table 4.1:** OpAmp stage 5 specifications

The dynamic range specification implies that at least 0.55 over the 1.2V available must be dedicated to the output swing; this limits the number of devices than can be stacked in the output branches and, consequently, the resistance. At the same time, previous considerations demonstrate that the  $g_m r_0$  in this technology is low, so it seems to be mandatory to cascode the output.

At the state of the art, three different topologies seem to meet the specifications required:

- -the folded-cascode;

- -the active-cascode;

- -the two-stage architecture.

Working in an purely intuitive way, if the first met the specifications, it would automatically be better than the second, because the power consumption is mainly related on bandwidth, so the boosters would only increase the current consumption.

Finally, assuming that the folded-cascode topology has enough gain, what to do is to choose between a single stage or a two stages architecture.

In an industrial environment, where the human effort is a parameter to take into account in a design, the more efficient methodology is probably to design the single stage device, to study the technology limits, then to design a two stage amplifier for a more sophisticated MDAC (for instance the stage 3 MDAC) and finally to choose which one is more indicated for the project purpose.

#### 4.1.2 Folded cascode architecture

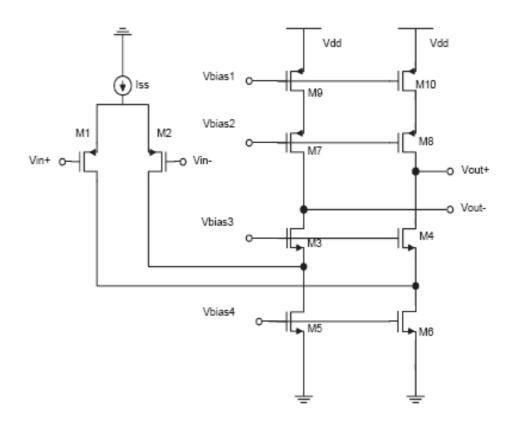

Fig 4.1: folded cascode architecture

The most important advantage of the folded structure lies in the voltage output swing because it does not "stack" the cascode transistor on top of the input device. The lower swing of the output is given by

$$V_{\min} = V_{\text{ds,sat3}} + V_{\text{ds,sat5}}, \tag{4.1}$$

and the upper end by

$$V_{\text{max}} = V_{\text{dd}} - (V_{\text{ds,sat7}} + V_{\text{ds,sat9}}). \tag{4.2}$$

Thus the peak to peak swing on each side is therefore:

$$V_{\text{swing}} = V_{\text{dd}} - 4 * V_{\text{ds,sat}}. \tag{4.3}$$

Using the half circuit depicted in fig. 4.2(a), and writing that

$$|A_{v}| = G_{m}R_{out}, \tag{4.4}$$

it is possible to calculate the equivalent  $G_m$  and  $R_{out}$ . As shown in Fig. 4.2(b), the output of the circuit current is approximatively equal to the drain current of M1, as the

impedance seen looking into the source of M3 is much lower than  $R_{on1} || R_{on5}$ .

Fig 4.2: half circuit representation

The use of a cascode structure allows to reach a very high impedance seen from the output node. In fact, as previously discussed, in 90nm technology the  $g_{ds}$  is relatively high, due to physical (the channel length) and technological (the halo structure) aspects.

#### 4.1.3 Cascode structure

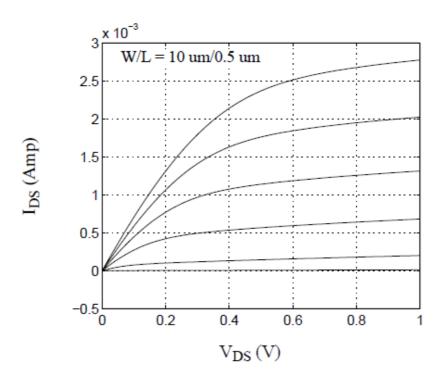

To increase the gain of the CMOS stage, the transconductance of the stage can be improved or the output resistance can be enhanced. The output resistance increases in proportion to a decrease in bias current as shown in Eq. 4.5

$$r_{ds} = \frac{1}{\lambda I_{DP}} \tag{4.5}$$

where  $I_{DP}$  is the drain pinchoff current and  $\lambda$  is the channel length modulation factor.

Instead the transconductance increases as the square root of the increase in bias current in a relation that can be simplified by the following:

$$g_{\rm m} = \frac{\partial i_{\rm D}}{\partial V_{\rm os}} = \sqrt{2\mu C_{\rm ox}(W/L) I_{\rm D}}$$

(4.6)

It is power efficient to increase the output resistance by lowering the bias current.

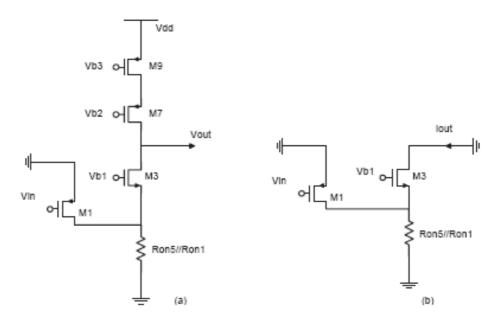

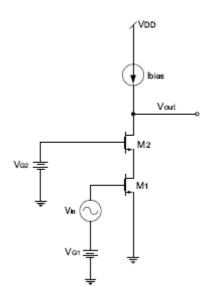

Fig. 4.3 shows a single stage amplifier using a conventional cascode connection where the common-gate stage device M2, biased by a voltage supply  $V_{G2}$ , is added to the input common-source stage M1.  $V_{G1}$ ,  $V_{G2}$ , and  $I_{bias}$  are chosen to make M1 and M2 to operate in their active regions.

Fig. 4.3: cascode structure

Assuming the current source I<sub>bias</sub> is ideal, the output resistance is

$$r_{out} = r_{ds1} + r_{ds2} + (g_{m2} + g_{mb2})r_{ds1}r_{ds2}. (4.7)$$

The midband voltage gain for the circuit of Fig. 4.3 is

$$A_0 = -[g_{ml}r_{dsl} + g_{ml}r_{dsl}(g_{m2} + g_{mb2})r_{ds2}], \tag{4.8}$$

where  $g_{m1}$  and  $g_{m2}$  are the transconductance of M1 and M2 individually,  $r_{ds1}$  and  $r_{ds2}$  denote the drain to source resistance of M1 and M2 at the bias point used, and  $g_{mb2}$  represents the transconductance that models the body effect of M2. As indicated by Eq. 4.8, it is clear that the cascode structure can achieve significantly higher voltage gain than a simple MOS stage by providing a higher output resistance. However, this configuration requires that the bias voltage  $V_{G2}$  for M2 be  $V_T + 2V_{eff}$ . The drain of M2 is set higher than  $V_{G2}$  in order to allow for the voltage swing. The operation of this cascode connection has limitations for low voltage, low power applications due to the bias voltage requirement and limited output swing. To achieve an even higher gain, more cascode devices can be added in the cascode stack connection to form a "triple cascode". But this further reduces the output swing, so in 1.2V Vdd technology cannot be implemented.

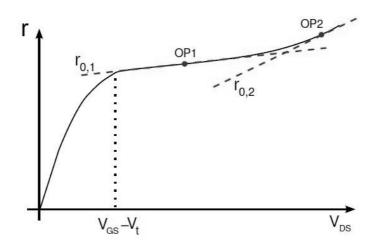

Another aspect to take into account is the rds variation related to the  $V_{ds}$  reduction: in fact, as depicted in fig4.4, the gds can drop when cascode  $V_{ds}$  comes close to the overdrive value. As previously described, this is a consequence of the Halo implant that reduces the effective channel length.

Fig 4.4: effect of the drain-source voltage on the output resistance

So the gain of the whole device will be  $G_m R_{out}$ , and the bandwidth, or better the dominant pole location will be:

$$\omega_{-3dB} = 1/R_{out}C_{out} \tag{4.9}$$

which allows to calculate the gain bandwidth product:

$$GBW = \frac{g_{ml}}{2\pi \cdot C_{out}} \tag{4.10}$$

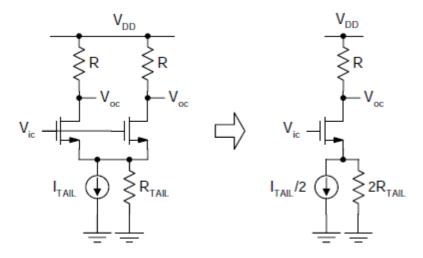

#### 4.1.4 Double input pair

Before deciding which type of transistors to use as input-pair, several aspects must be taken into account:

- 1) The electrons mobility is considerably higher than the mobility of the holes.  $g_m$ , and thereby the gain and unity gain frequency will be higher when using NMOS instead of PMOS-transistors, for the same input capacitance (that is, the W/L ratio).

- 2) With an NMOS input pair the impedance at the folding points will be lower, due to the intrinsic lower impedance of the PMOS transistors. Both the gain as well as the

phase margin will be lower than if using PMOS at the input, for the same sizes of the transistors.

- 3) NMOS transistors have lower thermal noise (a parameter related to the g<sub>m</sub>).

- 4) PMOS transistors have lower 1/f noise.

Since high gain is needed, NMOS transistors at the input has been preferred over PMOS. Also, since correlated double sampling will be used, the 1/f noise is reduced, which also make NMOS a better choice from the point of view of the noise.

Another degree of freedom in this circuital topology is the amount of current flowing into the input and the output branches. Typically, once the current capability specification is known, this value is applied at the output, and at the same time at the input to reach the same slewing behaviour when the current is flowing in the two directions relatively the output node.

Intuitively, a small amount of current at the output branch will implies good gain and lower bandwidth, since the MOS effective resistance is inversely proportional to this parameter; on the other side, more current in the input pair will consists in increased bandwidth and gain, since  $g_m$  is proportional to the square root of the current:

$$g_m = \sqrt{2k \frac{W}{L} I_D} \tag{4.11}$$

Here the bottleneck is the gain, so the choice has been to use the minimum amount of current at the output meeting the current capability specifications and increase the one at the input until the gain and bandwidth requirements were met.

This will clearly implies a different behaviour at the output when the signal rises and drops, due to the different current capability available. Simulations demonstrate that this can be not a problem in switching capacitor circuit until the minimum current available is enough to met the slewing specifications.

A drawback can be found in the  $g_{ds}$  of the transistors where both the current for the output and the one for the input pair flow. In fact huge transistors will be necessary to have enough  $V_{ds}$ , and since the current is high, also the metal width of the connections will be increased. This implies a high parasitic capacitance which, in

parallel with the input pair cascode and the output cascode, determines the secondary pole of the amplifier. This imposes the limit to the maximum over-bias for the input pair.

Another aspect to take into account is that, in the nodes of fig 4.5, besides the sum of

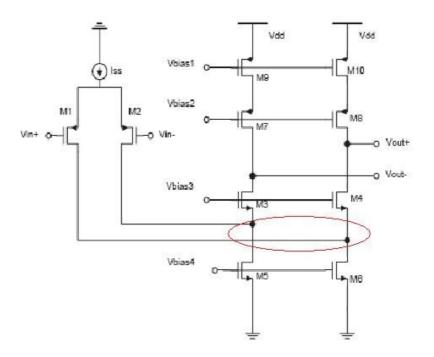

Fig 4.5: the bottleneck

the parasitic capacitance, there is also the parallel of the resistances of the mirror transistors with the input pair transistors. Since the node between the input pair and the tail current generator is a virtual ground, and since the input pair devices have a very small channel length to minimize the input capacitance maximizing the  $g_m$ , the relative  $g_{ds,input\_pair}$  will be also high. So several dB of gain can be lost; the solution chosen has been to stack a cascode transistors between the input pair and the node highlighted in fig 4.5. These devices were chosen identical to the input pair devices, mainly to obtain an easier symmetry when layouting, and biased at  $V_{dd}$  so no additional biasing circuitry was needed.

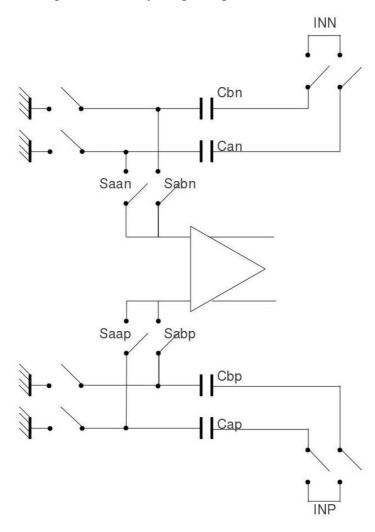

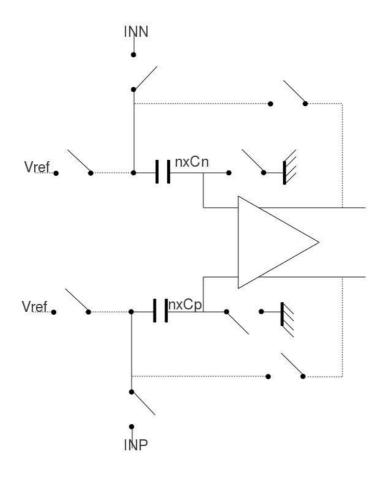

An other peculiarity of the topology lies in the presence of two input pairs. Each of them is driven by a switch connected to a clock signal so that when a pair is turned

on, the other is off.

In fact verifications by simulations show the presence of an unexpected  $\Delta Q$  at the input of the amplifier, and further investigations demonstrate that it was due to the charges pumped by the bootstrap circuit and by Saap, Sabp, Saan and Sabn switches.

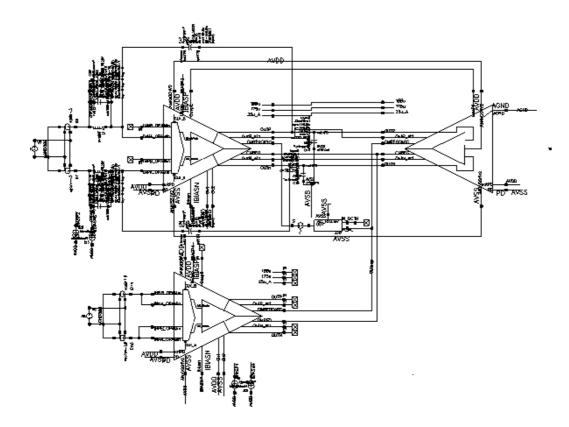

Fig 4.6: MDAC in double sampling configuration

In particular, at the moment these switches close, there is a  $\Delta Q$  pumped from the ground through the parasitic capacitor, and this, of course, generates an error on the value sampled on the capacitor, and an error on the bottom plate voltage of the capacitors. This will imply an extra error later at the end of the amplification phase.

In a single sampling configuration this problem does not exist, because there is no switch in the feedback path of the op-amp.

Fig 4.7: MDAC in single sampling configuration

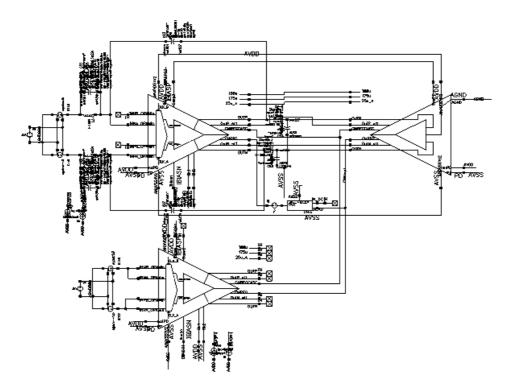

From this consideration comes the solution chosen, which is to remove the critical switches by creating a multiple path. This means that the amplifier will have two input pairs, but the extra stored charge is avoided.

This clearly implies the need of extra area and a clock signal, but the power consumption remains nearly unaltered.

Fig 4.8: MDAC in double sampling configuration, proposed topology

# 4.1.5 Biasing strategy

In the project it is assumed to have a 50uA current source, generated by a bandgap circuit. This means that this current will be proportional to the supply voltage.

What is needed is to bias:

- the transistors used as current source;

- the cascode transistors.

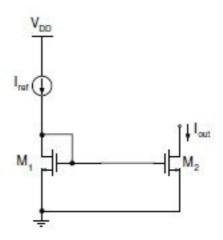

For the first case the 50uA can be simply fed into a device in diode configuration; the voltage at the gate can then be used to bias a scaled version of the same device to reach the current desired.

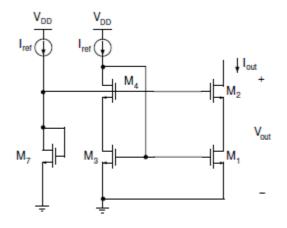

Fig 4.9: basic current mirror

The two devices have the same gate voltage, but the  $V_{ds}$  can be different. This implies a mismatch in the current (assuming that the gates have the same dimensions), which can be represented:

$$\Delta I = I_2 - I_1 \approx \frac{V_2 - V_1}{r_0} = \frac{\Delta V_{DS,2}}{r_0}$$

(4.12)

Fig 4.10: current mismatch due to Early effect

To avoid this deviation, since every current mirror is part of a cascode, an easy solution is to use the cascode itself to fix the  $V_{ds}$ , as shown in fig 4.11.

Fig 4.11: cascoded current mirror

Using this strategy the topology has robust current mirrors.

What still remains is to bias the cascode transistors. Investigating a particular case, for instance the NMOS cascodes in the output branch, it is clear that the goal is to have a DC voltage high enough to leave M<sub>3</sub> and M<sub>1</sub> in saturation, but low enough to leave M2 also in saturation when Vout is at its minimum, or, better, when the main amplifier operates at its full swing. So the desired voltage is:

$$V_{gs7} = V_{t2} + V_{ov2} + V_{ov1}$$

(4.13)

Fig 4.12: cascode transistor biasing

In fig 4.12 it is shown a diode connected MOS working as voltage reference; the current is generated by a cascoded current mirror.

Several different solutions have been taken into account; but the diode connected MOS has the advantage that it is simple, small and has a low and adjustable power consumption. Its output node has also a low impedance, which means that the rejection to the supply noise will be good.

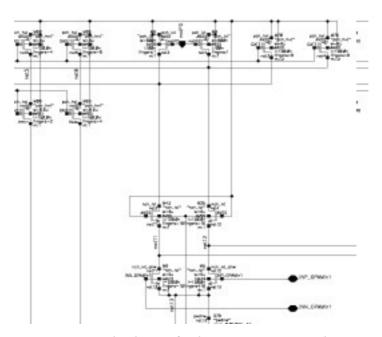

#### 4.1.6 Power down switches

It is mandatory to introduce in the design the possibility to power down the circuit even if the supply is still connected. It simply consists in adding to some nodes switches to power down the current sources or the biasing of some transistors so that it is impossible for the current to flow in certain conditions.

In fig 4.13 the power down switches are highlighted

Fig 4.13: power down switches

The strategy rely mainly on:

-to stop the current coming from the external current source, obtained applying a switch in series between the current source and the mirror transistor;

Fig 4.14: current stopping switch

-switch off the current mirrors, by shorting the gate voltage to ground or Vdd;

Fig 4.15: turning off switches for current mirrors

-shorting the current stored in big capacitance node to a power rail

Fig 4.16: discharge for big capacitance nodes

The problem arises on the turning on of the circuit. In fact the biasing of the different cascode devices depends on the current generated by the current mirrors, which, at the same time, contain a cascode.

Fig 4.17: start-up for the cascode bias

The solution adopted is the one shown in fig 4.17: the circuit guarantees a low current

flowing in the diode connected MOS which bias the cascodes, allowing it to generate some voltage gap which will converge at the desired bias value once Vdd stabilizes.

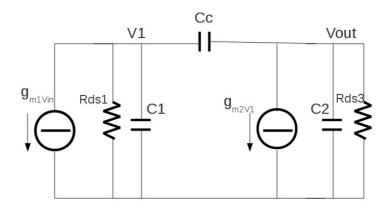

#### **4.1.7** Noise

Every transistor can be considered as a noise source, so it can be modellized as a current source having a spectral current density:

$$I_{out}^2 = 4kT\gamma g_m + \frac{KFg_m^2}{2\mu WLC_{ox}^2 f}$$

(4.14)

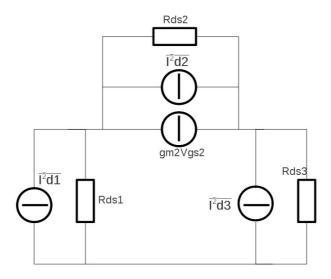

For simplicity a single pole model can be considered

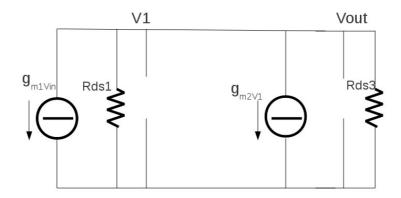

Fig 4.18: single pole model

where Rds3 indicates a cascoded structure.

The power spectral density of each device can be referred to the input:

$$V_{n1in}^2 = \frac{I_{ds1}^2(f)}{gm_1^2} \tag{4.15}$$

$$V_{n2in}^2 = \frac{I_{ds2}^2(f)}{gm_1^2gm_1^2r_{ds1}^2}$$

(4.16)

$$V_{n3in}^2 = \frac{I_{ds3}^2(f)}{gm_1^2} \tag{4.17}$$

Finally the total input referred noise will be the sum of each contribution:

$$V_{nOTA}^2 = \sum_{j=1}^3 V_{njin}^2 \tag{4.18}$$

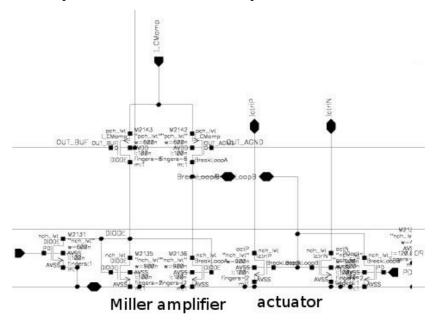

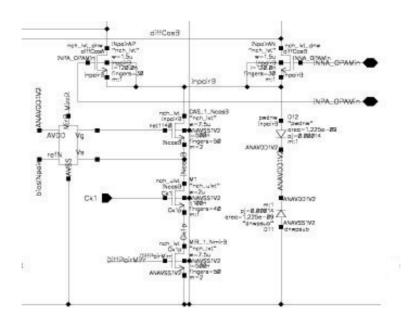

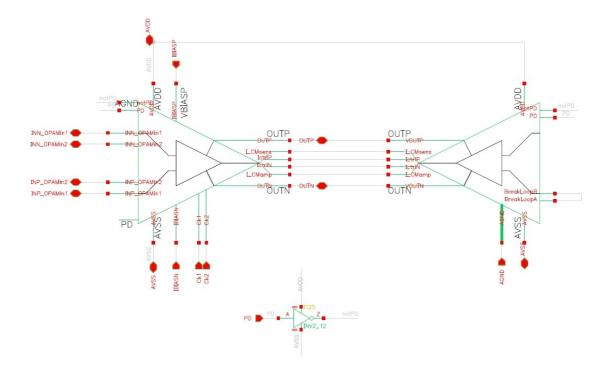

## 4.2.0 Stage 3 amplifier

These are the specifications to reach

| Gain                 | 70.79dB                |

|----------------------|------------------------|

| GBW                  | 1415MHz                |

| Dynamic Range        | 1.1Vpp                 |

| Noise (inp_referred) | $5.53$ nV/ $\sqrt{Hz}$ |

| Current Capability   | 0.42mA                 |

Some considerations: stage 5 op-amp was already at the limit for the technology given: in fact no more gain was affordable. Also the bandwidth was no freely increasable, since the bottleneck at the discussed mirror transistor would make the gain drop if the current was raised.

So a simple single stage amplifier with that kind of architecture can not reach the specifications required.

Also a boosted folded-cascode device would be ineffective, mainly for three reasons:

- 1) the current to have stable boosters can augment the power consumption up to 40%;

- 2) the doublet pole-zero which can degrade the slew rate;

- 3) the noise injected at the output node by the boosters, which have nearly the same amplification than the noise emitted by the input pair transistors.

The third reason is probably the most important, because noise specification, here but especially in the first and in the second MDAC, is the key parameter, or, better, the most difficult specification to achieve.

So it seems the case to use a two stages device. The behaviour concerning the voltage swing is the same as in the previous case: the second stage, which has a topology similar to the output part of stage 5 amplifier, can easily satisfy the requirements, and has the advantage that the gain requirements are less stringent.

Then, supposing that the second stage has a gain between 30 up to 40dB, a value easily reachable using a cascode structure, the first stage will need something around

20mV of swing. So a folded architecture is no more mandatory for neither of the stages, and this means that the current consumption can be reduced since there is a single path between the supply and the ground for each stage.

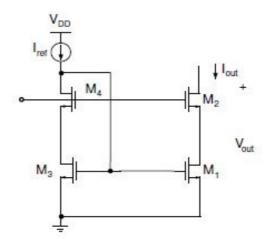

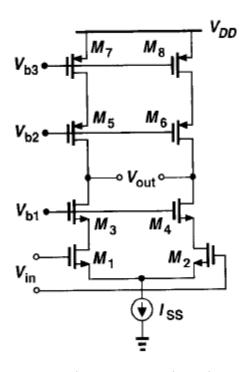

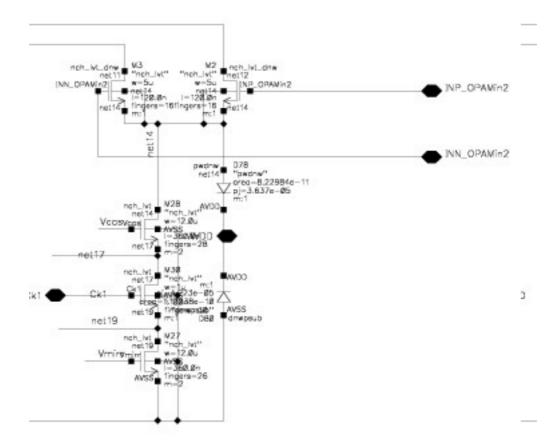

## 4.2.1 Telescopic cascode

The first stage is a telescopic cascode OTA, it means that a current source (cascoded, to improve the impedance, as described in the previous chapter) feeds of current an input pair which drives a cascoded load.

Fig 4.19: telescopic cascode architecture

The DC output voltage of the first stage is forced by a negative feedback to a value which, fed at the input of the second stage, bias this transistor to a fixed current value.

The gain characteristics can be easily extracted by the following:

$$A_0 = g_m R_{out} \tag{4.19}$$

where  $g_m$  is the transconductance of the input pair transistors and  $R_{out}$  is the real part of the impedance seen by the output node, that is

$$R_{out} = (r_{ds1} + r_{ds3} + (g_{m3} + g_{mb3})r_{ds1}r_{ds3}) \mid | (r_{ds7} + r_{ds5} + (g_{m5} + g_{mb5})r_{ds5}r_{ds7})$$

(4.20)

Instead the frequency behaviour depends on the location of the dominant pole, which is

$$f_{p1} = \frac{1}{2\pi \cdot R_{out} C_{out}} \tag{4.21}$$

which allows to calculate the gain bandwidth product:

$$GBW = \frac{g_{ml}}{2\pi \cdot C_{out}} \tag{4.22}$$

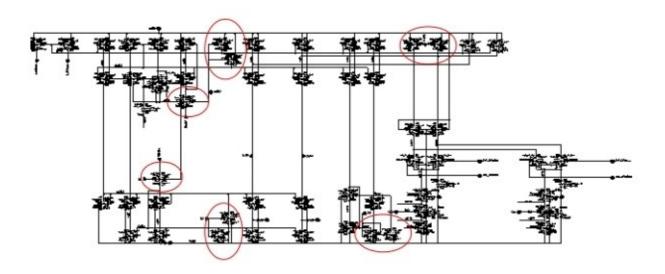

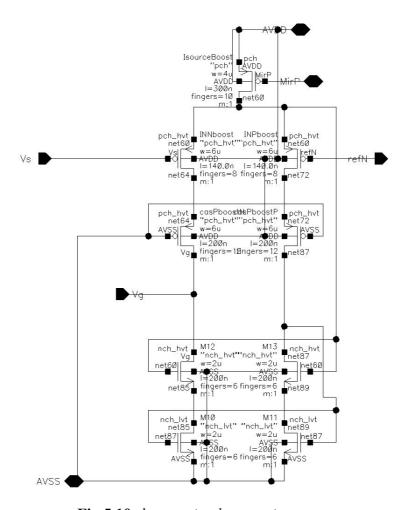

Fig 4.20: telescopic cascode amplifier schematic

As previously described, the input pair is doubled and driven by a switch like in stage 5 amplifier.

## 4.2.2 Output stage

This second stage is a couple of common-source transistors with a cascoded load. The DC gain is, as usual

$$A_0 = g_m R_{out} \tag{4.19}$$

and the dominant pole depends on the load and on Rout

$$f_{p1} = \frac{1}{2\pi \cdot R_{out} C_{out}} . \tag{4.21}$$

There is no common path between ground and supply, but the previous stage differential architecture guarantees that the sum of the current in the two output branches remains constant.

Fig 4.21: stage 3 amplifier: output stage

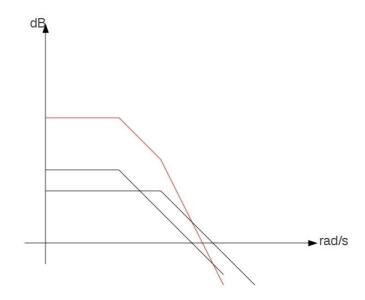

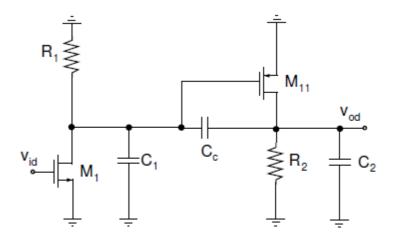

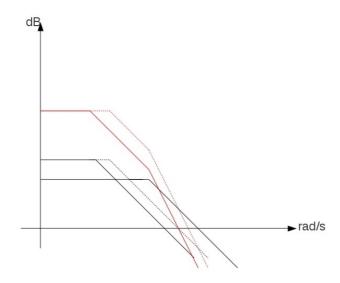

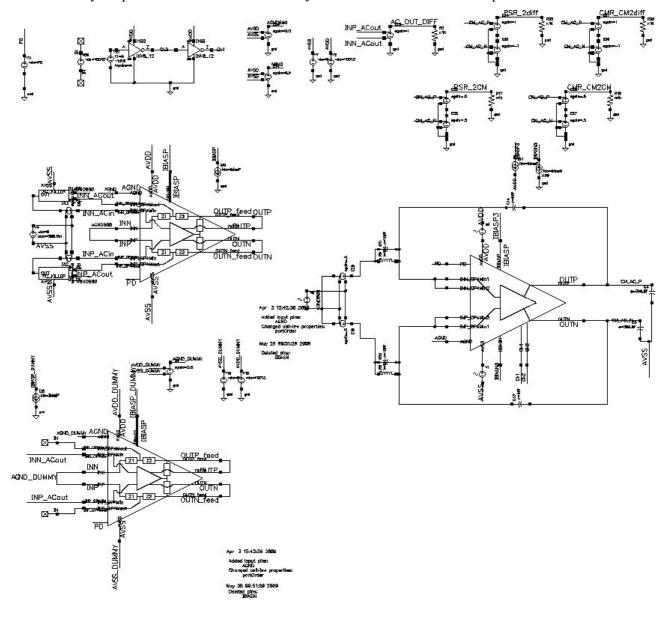

# 4.2.3 Two stages amplifier compensation

The main difference between a single stage and a two stages amplifier lies in the stability of the architecture itself. In fact, supposing that each stage has an unique dominant pole, it would be necessary a stage having challenging bandwidth characteristics.

Fig 4.22: Bode plot of a two stages amplifier

As depicted in fig 4.21, supposing that each stage has a dominant pole behaviour, the whole system will have a dominant pole at the same frequency of the slowest stage and the secondary one at the frequency of the other pole. So stability in feedback configuration is difficult to achieve, since the two stage have a similar bandwidth, and since each stage secondary poles are not considered.

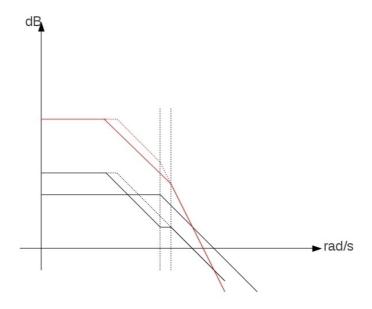

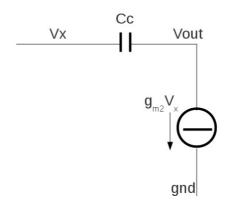

So a compensation is needed; the solution chosen is to use a "Miller" capacitor, which, intuitively, is a capacitor at the output of the first stage which impedance is amplified by the second stage OTA.

Fig 4.23: small signal schematic of a two stages amplifier

If Cc was placed in parallel to C1, then the behaviour of the two stages would be the following:

Fig 4.24: parallel compensation of a two stages amplifier

Since stability is a parameter linked to the ratio between the secondary pole and the 0dB frequency, a phase margin improvement is clear from the graph (both axes are logarithmic).

Instead, applying Cc in series between the outputs of the two stages, the small signal response becomes:

Fig 4.25: Miller compensation of a two stages amplifier

which is clearly better than the previous case, because the secondary pole shifts at higher frequencies leaving the 0dB cross unaltered.

Intuitively, what happens is that the effective impedance seen by the first stage is amplified by the second stage; but, at higher frequencies, when the gain of second stage starts to drop at its dominant pole, also the efficient value of the capacitor drops. This is why the first stage seems to have a zero located at the second stage dominant pole.

Also the second stage has a variation respect to the parallel case, in fact its bandwidth increases due to the fact that the efficient value of the Miller capacitor is reduced due to the attenuation imposed by the first stage.

This effect is called "pole splitting", since in the small signal plot of the whole amplifier the dominant pole move towards DC and the secondary pole increases its value.

An other fact to note is the presence of a zero in the Miller capacitor path. Intuitively,

the problem can be analized as follow:

Fig 4.26: small signal representation of a two stages amplifier

The two stages gain and bandwidth can be assumed to be very similar: this is mainly due to the fact that the gm is proportional to the square root of the current. This assertion allows to assume that  $C_c$  is much bigger than  $C_1$  and  $C_2$ , condition necessary to achieve stability. So, for a certain range of frequencies,  $C_1$  and  $C_2$  can be seen as open circuits; instead  $C_c$  can be assumed as a short, as shown in fig 4.25:

Fig 4.27: middle band representation of a two stages amplifier

So the whole second stage can be assumed as a diode connected transistor in parallel to a coscoded load, which means a total impedance of  $1/g_{m2}$ , making the  $R_{ds3}$  contribution uninfluent.

From the current point of view, instead, assuming the previous hypothesis, the system can be represented as follows:

Fig 4.28: second stage equivalent schematic

so the zero can be easily found:

$$\omega_{zero} = \frac{g_{m2}}{C_C} \tag{4.23}$$

where all the current generated by the first stage flow through the second stage transconductance.

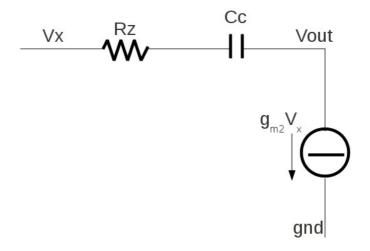

The problem can be easily solved placing a resistor in series with the Miller capacitor.

Fig 4.29: nulling resistor

So:

$$V_{out} = V_x \cdot (1 - g_{m2} R_z - \frac{g_{m2}}{sC_c})$$

(4.24)

If  $R_z = 1/g_{m2}$ , then Vout can never be null for any frequency.

| - 6 | 6 | - |

|-----|---|---|

|-----|---|---|

# Chapter 5

# Common mode feedback design

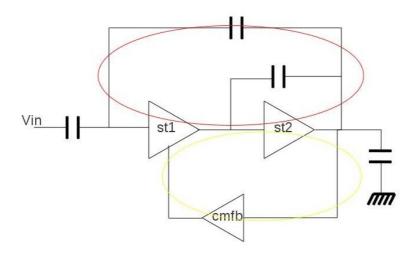

#### 5.0 Introduction

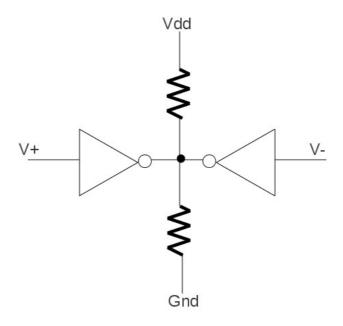

The common mode feedback circuit is a critical component in this kind of architecture: in fact what is needed is a device having

- 1) a wider bandwidth than the amplifier itself;

- 2) a low gain to achieve easily the stability;

- 3) an input dynamic range equal to the output range of the amplifier.

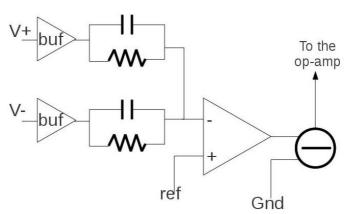

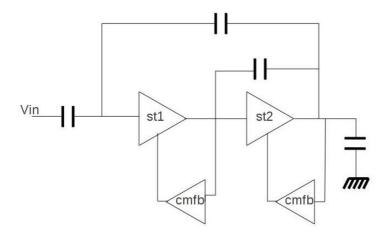

For high bandwidth structures, it is typically used a switched capacitor structure: it has a negative gain and no problems concerning the input range.

But it needs an operative clock that is the double of the one used for the main converter: this means the necessity of a clock generator and can be risky from the noise point of view (it would implies a tone at the double of the operative frequency). So a continuous time feedback regulator is mandatory.

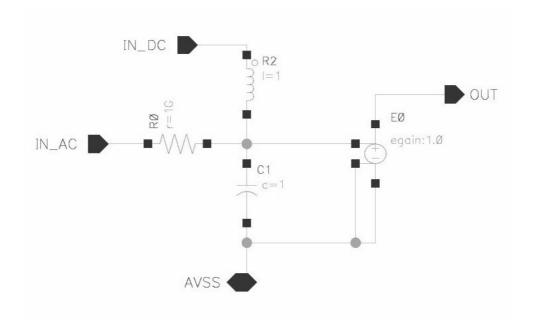

#### 5.1 Stage 5 common mode regulator topologies

The input dynamic range is probably the most critical specification for this device in low voltage technology, so it has been the first taken into account. Different architectures have been investigated.

#### **5.1.1** Inverter based comparator

The first topology considered consists in two inverters having two degeneration resistors, as shown in fig

Fig 5.1: inverter based comparison

This structure has a wide input range and a gain adjustable by changing the resistors value (which are made using transistors); the current consumption is instead related to the inverters sizes. The voltage value at the central node would be compared by an amplifier to the one produced by the same structure biased at AGND.

The drawback of this topology, however, is that it has only two degrees of freedom, the W/L ratio and the value of the resistors; so, even if it can be good enough for stage 5 amplifier, it seems no possible to use it for the wider bandwidth amplifiers.

#### 5.1.2 Current based comparison

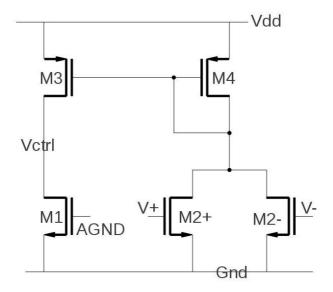

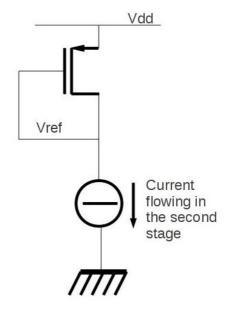

Another solution proposed is the one shown in fig 5.2. Here the current generated by the pair connected to the main amplifier output is fed, through a mirror, into a MOS biased at AGND, which is the desired voltage value for the DC output.  $M_1$  and the couple  $M_{2+}$  together have the same effective W/L ratio.

Fig 5.2: current based comparison