# A thermally aware performance analysis of quantum cellular automata logic gates

# Sujatha Kotte<sup>1</sup>, Ganapavarapu Kanaka Durga<sup>2</sup>

<sup>1</sup>Department of Electronics and Communication Engineering, University College of Engineering, Osmania University, Hyderabad, India <sup>2</sup>Department of Electronics and Communication Engineering, Maturi Venkata Subba Rao Engineering College, Hyderabad, India

# Article Info ABSTRACT

### Article history:

Received Jan 10, 2023 Revised Mar 24, 2023 Accepted Apr 7, 2023

#### Keywords:

Digital logic gates Low power circuit design Memory design Quantum cellular automata Very large-scale integration

# ADSTRACT

The high-performance digital circuits can be constructed at high operating frequency, reduced power dissipation, portability, and large density. Using conventional complementary-metal-oxide-semiconductor (CMOS) design process, it is quite difficult to achieve ultra-high-speed circuits due to scaling problems. Recently quantum dot cellular automata (QCA) are prosed to develop logic circuits at atomic level. In this paper, we analyzed the performance of QCA circuits under different temperature effects and observed that polarization of the cells is highly sensitive to temperature. In case of the 3-input majority gate the cell polarization drops to 50% with an increase in the temperature of 18 K and for 5 input majority. Further, the performance of majority gates also compared in terms of area and power dissipation. It has been noticed that the proposed logic gates can also be used for developing simple and complex and memory circuits.

This is an open access article under the <u>CC BY-SA</u> license.

### **Corresponding Author:**

Sujatha Kotte Department of Electronics and Communication Engineering, University College of Engineering, Osmania University Hyderabad, Telangana, India Email: sujathakotte24@gmail.com

# 1. INTRODUCTION

Emerging nano-technology such as carbon nanotubes [1], quantum dot cellular automata (QCA) [2], [3], nano magnetic logic, resonating tunnelling diodes, and spin-wave devices are designed to support the Moore's law trend in integrated circuits. A promising alternative is QCA technology. The advantages of QCA technology computing paradigm over complementary-metal-oxide-semiconductor (CMOS) technology, including degraded power, large density and fast operation in the terahertz frequencies. Due to the fact that QCA is distinct over existing technologies, it is evident that innovative and different design approaches are required to create the circuits.

The quantum dot cells are used to design the logic gates and also used for the signal transmission. The signal information is not represented by conventional voltage or current measurement; in fact, it is represented by the polarization of the quantum dot cell. Since the voltages and currents are not involved in the characterization of the output signal the QCA power designs are very minimal. The power analysis of QCA circuits has been reported in several papers [4], [5].

In the current literature, there are many papers available on design of the QCA circuits. In [6], [7], presented the XOR/XNOR gate circuits for QCA circuits modular design with 13 cells and also designed the full adder, parity circuit and comparator circuit. Later in, a modified XOR gate with a single layered structure using only 9 cells is explained. Therefore, the presented XOR gates occupies lesser area and lower latency.

The authors also designed full-adder, parity checker and binary to gray code converter using the modified XOR gate. It has been observed that 24% improvement in cost and 35.5% less power dissipation than the previously reported designs. In QCA circuits it values noting that the cell polarization is more sensitive to temperature variations and none of the previous studies addressed with issue. In this paper, we performed the temperature sensitive analysis of QCA circuits; especially analyzed the majority gates, which are the primary gates for the design in QCA technology. The cell polarization is highly sensitive to temperature. Therefore, we further performed the temperature sensitive analysis of the 3-inputs and 5-inputs majority gates.

# 2. QCA CIRCUITS

# 2.1. QCA basics

There are 4-quantum-dots stacked in a square arrangement to create a typical QCA cell. The polarization of stable state is determined by all parameters involved in electron charge, as shown in Table 1, two electrons can occupy these quantum dots based on the tunnelling process. At each of the four corners of a square QCA, 4-quantum-dots are situated [8], [9]. Six-dot and eight-dot QCA cell implementation is still a relatively new field of study [10], [11]. The cell polarization P = +1 represents "1" and P = -1 shows "0" [12], [13]. The polarization value can be determined by the electrostatic energy among cells *i* and *j*, this also be called as Kink energy can be calculated as (1) [14].

$$E_{i,j}^{m,n} = \frac{1}{4\pi\varepsilon_0\varepsilon_r} \sum_{m=1}^4 \sum_{n=1}^4 \frac{q_i^m - q_j^n}{\left|d_i^m - d_j^n\right|} \tag{1}$$

The Kink energy among the two cells can be calculated as (2).

$$E_{i,j}^{kink} = E_{i,j}^{opposite \ polarization} - E_{i,j}^{same \ polarization}$$

(2)

The parameter representation is presented in Table 1. For the opposite polarization the polarization values of  $P_i$  and  $P_j$  are considered to be not equal and for equal polarization are values are considered to be equal. The cell polarization of each can be calculated as (3),

$$E_{i,j} = \left(\frac{E_{i,j}^{kink}}{2\gamma} \sum_{j} P_{j}\right) / \sqrt{1 + \left(\frac{E_{i,j}^{kink}}{2\gamma} \sum_{j} P_{j}\right)^{2}}$$

(3)

where  $\gamma$  is the electron tunnelling energy inside the QCA cell.

|     | Table 1. Parameter representation |                                                                                                           |  |  |  |  |

|-----|-----------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| No. | Parameter symbol                  | Representation                                                                                            |  |  |  |  |

| 1   | $\varepsilon_0$                   | free space permittivity                                                                                   |  |  |  |  |

| 2   | $\varepsilon_r$                   | material permittivity                                                                                     |  |  |  |  |

| 3   | $q_i^m$                           | charge of electron on $m^{\text{th}}$ dot in $i^{\text{th}}$ cell                                         |  |  |  |  |

| 4   | $q_i^n$                           | charge of electron on $n^{\text{th}}$ dot in $j^{\text{th}}$ cell                                         |  |  |  |  |

| 5   | $ d_i^m - d_i^n $                 | gap among the $m^{\text{th}}$ dot in $i^{\text{th}}$ cell and $n^{\text{th}}$ dot in $j^{\text{th}}$ cell |  |  |  |  |

The QCA circuits require the clock signal for data synchronization and also it regulates the information flow and supplies the circuit power. There are four different clock zones are available in QCA each has the phase shift of 90°3 [15]–[17]. There are four different phases like switch, hold, release and relax in each clock. During switch phase, cells become polarized and they are ready to switch based on the kink energy. The inner dot barrier rises throughout in switch. The barriers have to keep high during the hold phase to ensure that the polarization current of the cell can be maintained [18], [19]. During the release, the inner dot barrier decreases and loose polarization [20], then it becomes non-polarized during the release phase and this situation continues during the relax phase.

#### 2.2. Fundamental components of QCA circuits: wire and inverter

The design elements such as wire and inverter are presented in this section. The primary components of QCA circuits are wire, inverter, majority and minority gates. The QCA wire illustrated in Figure 1, made of aligning QCA cells in a cascading manner. The signal flows from one to another side based on Coulomb's interaction between the electrons [21]–[23].

Figure 1. The interconnect wire structure of QCA Inverter

The inverter operation easily achieved by arranging the QCA cell in corner with the other cell. The inverter cell can be designed in two ways by using two and three-layer structures. The Figure 2 shows QCA inverters in two different types, whereas in Figure 2(a) the two layers are displaced by the length of the cell. It can be observed that the output cell becomes the logic 1 polarity in so far as the input driven by logic 0 [24], [25]. However, the inverter circuit is a not robust in nature and suffers with signal integrity issues due to the weak Coulomb interaction forces. This problem can be rectified by using a three-layered structure as represented in Figure 2(b).

Figure 2 QCA inverter (a) type-1 and (b) type-2

# 2.3. QCA logic circuit implementation using majority and minority gates

In QCA the logic circuits are implemented by the majority gates and minority gates. The AND and OR gates are designed with majority, NAND and NOR are implemented using the minority gate. The majority gate brings out the output value based on the input majority bit pattern [26]. The majority gate Boolean expression of can be represented as (4).

$$Maj(A, B, C) = AB + BC + AC \tag{4}$$

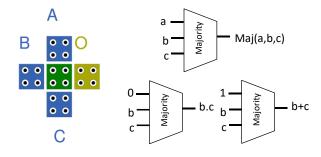

For designing the 2-input basic gates, the 3-input majority is required [27]. The circuit of 3-input majority is represented in Figure 3. The majority gate can also act as a 2-input AND/OR by fixing the appropriate polarization to one of the QCA cell. The (5) and (6) demonstrate the conversion of the majority gate to AND/OR operations by forcing 1-input to logic "0" or "1" and the operation of 5-input majority is stated in the (7) [28], [29].

$$M(A, B, 0) = F = A.B$$

(5)

$$M(A, B, 1) = F = B.1 + 1.A + A.B = A.B + A + B = B + A(1 + B) = A + B$$

(6)

$$M(A, B, C, D, E) = (ABC + ABE + ABD + ACD + ADE + ACE + BCE + BDE + BCD + CDE)$$

(7)

A thermally aware performance analysis of quantum cellular automata logic gates (Sujatha Kotte)

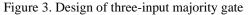

Design of the three different 5-input majority gates is depicted in Figure 4. Type-1 majority is placed in Figure 4(a) where connection to output is provided in same layer. However, type -1 majority gate suffers with input cell-cell cross-talk since the cells are very close to each other. Type-2 majority gate in Figure 4(b), where inputs cells accept all five signal inputs in the same direction at the first clock. In type-3 in Figure 4(c) majority gate has ten cells, the connection to output is provided in multi-layer because the output cell is enclosed by input cells, this gate also suffers with cell-cell cross talk, since all cells are closely arranged.

Figure 4. Different design techniques for five-input majority gate (a) type-1, (b) type-2 and (c) type-3

The minority gate generates the output value 0, if there are minority number of 0's in the input pattern. For example, the 3-input minority gate produces "0" if the input is (0,1,1). The design of 5-input minority gate and the conversion to NAND and NOR are represented in Figure 5. For the 5-input minority gate shown in Figure 5(a) the Boolean expression as (8).

$$Min (A, B, C, D, E) = \overline{(ABC + ACD + ACE + ADE + ABD + ABE + BCD + CDE + BCE + BDE)}$$

(8)

It can be observed that the minority gate produces output 1 when there is minority of "1" s in the input pattern, otherwise the circuit produces output 0. Similar to the majority gate, the minority functionality can be changed to NAND, NOR gates by changing the input cells polarization. The following equations demonstrate the conversion of the minority gate to NAND/NOR operations by forcing one of the inputs to logic "0" or "1". The QCA circuits for the implementation of three-input NAND, NOR are represented in Figures 5(b) and 5(c), respectively. Three-input NAND, NOR gates can be expressed as (9) and (10).

$$\operatorname{Min}\left(A, B, C, 0, 0\right) = \overline{(ABC)} \tag{9}$$

$$\operatorname{Min}\left(A, B, C, 1, 1\right) = \overline{\left(A + B + C\right)} \tag{10}$$

Figure 5. The structure of (a) five-input minority gate, (b) NAND gate, and (c) NOR gate

### 3. RESULTS AND DISCUSSION

Utilizing QCADesigner 2.0.3, simulations of majority, minority and proposed logic gate structures are performed [30]. The bistable approximation-simulation-engine and the coherence-vector-simulation-engine are used to simulate proposed architectures, and results were obtained from both engines. The default cell size is considered as  $18 \times 18$  nm<sup>2</sup>. In the simulations a total of 28,000 samples along with a 100 repetition per sample were utilized to support output results. We considered different conditions for the simulation test for exciting conditions; therefore, it approves consistency and success our designs.

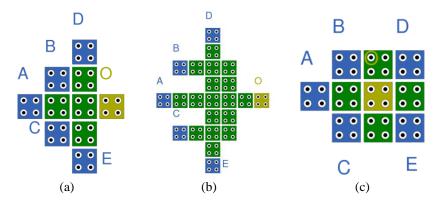

The simulation results of minority and majority gates are shown in Figure 6. The 3-input majority is represented in Figure 6(a) and results of 5-input majority are shown in Figure 6(b). In both figures, it can be observed that the output produces the logic 1, when there is a majority of 1's in the input pattern; otherwise, the gate produces logic 0. By fixing the 1-majority input either 1 or 0, we can design a two-input AND or OR gates. If one of polarization input cell is fixed to -1 (logic-0), the majority act as AND. Similarly, if one of polarization of input cell is fixed to 1 (logic-1), the majority act as an OR.

Figure 6. Results of (a) 3-input majority and (b) 5-input majority gates

Based on functional operation of minority gate, it can be observed that the output produces the logic 1, when there is a minority of 1's in the input pattern; otherwise, the gate produces logic 0. By fixing two inputs of minority gate either 1 or 0, we can design a three-input NAND or NOR gates. The simulations 3-input NAND and NOR are represented in Figure 7. It can be observed that functionality of logic gates is satisfied with the waveforms, that shows the accuracy of the design.

The comparison of cell area and power of different majority are analyzed and shown in Table 2. It has been noticed that the Type-2 majority gate occupies more area and dissipates more power than Type-1 and Type-3. The area of Type-2 majority gate is almost double than the Type-1 and Type-3 and power dissipation is also near equal to two times of Type-1 and 3. However, Type-2 majority gate most recommended gate due to easy access of output port and the input ports are almost isolate to each other. The cell area and power dissipation comparison of five-input majority and minority gates are presented in Table 3. It can be seen that the minority gate occupies cell lesser area and lesser power dissipation compared to the majority gate. The loss of power dissipation is observed to be 10%.

| 9.🛫                                                               |   |   |  |  |           |   |  |  |           |     |       |        |   |  |

|-------------------------------------------------------------------|---|---|--|--|-----------|---|--|--|-----------|-----|-------|--------|---|--|

| max: 1.00e+000                                                    |   |   |  |  |           |   |  |  |           |     |       |        |   |  |

| min: -1.00e+000                                                   |   |   |  |  |           |   |  |  |           |     |       |        |   |  |

| la <u>ve</u> , , , , , , , , , , , , , , , , , , ,                |   |   |  |  |           |   |  |  |           |     |       |        |   |  |

| max: 1.00e+000                                                    |   |   |  |  |           |   |  |  |           |     | <br>1 |        |   |  |

| A<br>min: -1.00e+000                                              |   |   |  |  |           |   |  |  |           |     | <br>  |        |   |  |

| 0,-                                                               | 0 |   |  |  |           |   |  |  |           |     |       |        |   |  |

| max: 1.00e+000                                                    |   |   |  |  |           |   |  |  |           |     | r     |        |   |  |

| тіп: -1.00е+000                                                   |   |   |  |  |           |   |  |  |           |     |       |        |   |  |

| 0,-                                                               | 0 |   |  |  |           |   |  |  |           |     |       |        |   |  |

| max: 9.51e-001                                                    |   | Т |  |  | $\square$ | Г |  |  | $\square$ | 777 |       | $\neg$ | 5 |  |

| min: -9.51e-001                                                   |   |   |  |  |           |   |  |  |           |     | <br>  |        |   |  |

| le100001200013000140001500016000170001800019000110000111000112000 |   |   |  |  |           |   |  |  |           |     |       |        |   |  |

| max: 9.51e-001                                                    |   |   |  |  |           |   |  |  |           |     |       |        |   |  |

| min: -9.51e-001                                                   |   |   |  |  |           |   |  |  | Ш         | Ш   |       | Ш      |   |  |

Figure 7. Timing waveform of three-input NAND and NOR gates

| Table 2. Comparisons of cell area and power | er |

|---------------------------------------------|----|

| dissination of different majority gates     |    |

|                              | Junt Ind | ijonny ga | ues   |    |

|------------------------------|----------|-----------|-------|----|

| Parameter                    | 5- I     |           |       |    |

|                              | Type1    | Type2     | Type3 |    |

| Cell Area (nm <sup>2</sup> ) | 3,234    | 7,452     | 3,234 | Ce |

| Power Dissipation (meV)      | 7.9      | 19.0      | 9.7   | Po |

Table 3. Comparisons of cell area and power

| dissipation of majority and minority gates |            |            |  |  |  |  |  |

|--------------------------------------------|------------|------------|--|--|--|--|--|

| Parameter                                  | 5-majority | 5-minority |  |  |  |  |  |

|                                            | gate       | gate       |  |  |  |  |  |

| Cell Area (nm <sup>2</sup> )               | 7,452      | 7,128      |  |  |  |  |  |

| Power Dissipation (meV)                    | 19.0       | 17.2       |  |  |  |  |  |

The comparative results of QCA with that of CMOS logic gates designed at 32 nm technology node is placed in Table 4. The comparison results show that the area occupied by the QCA are very small compared to CMOS logic gates. Moreover, the power of QCA is in order of eV; whereas the power of the CMOS is in order of  $\mu$ W.

Table 4. Comparisons of QCA and CMOS logic gates NOT AND OR NAND Area (µm<sup>2</sup>) NOR 0.10021 0.045 0.07416 0.10021 QCA 0.0716 CMOS 2.87 8.92 8.94 8.12 8.23

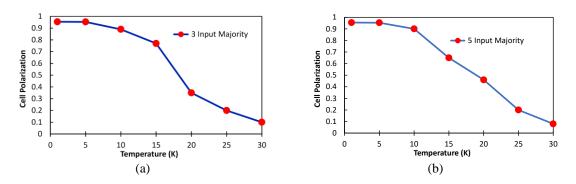

It is worthy to discuss that QCA cells are highly sensitive to temperature changes. Therefore, we performed the temperature sensitive analysis and results are shown in Figure 8. The 3- majority and 5-majority gates and represented in Figures 8(a) and 8(b), respectively. The graph is drawn between the change in temperature and cell polarization. As can be seen from Figure 8(a), it is polarization maintains its value nearly constant level up to 15 K, and further increasing the temperature the cell loses the polarization and becomes unstable. The same analysis can also be analyzed from Figure 8(b). Therefore, we may conclude that the QCA gates computational fidelity is good for the temperature range T < 15 K, more or less acceptable in the above range of 15 K.

Figure 8. Temperature variations impact on polarization (a) three-input majority and (b) five-input majority gate

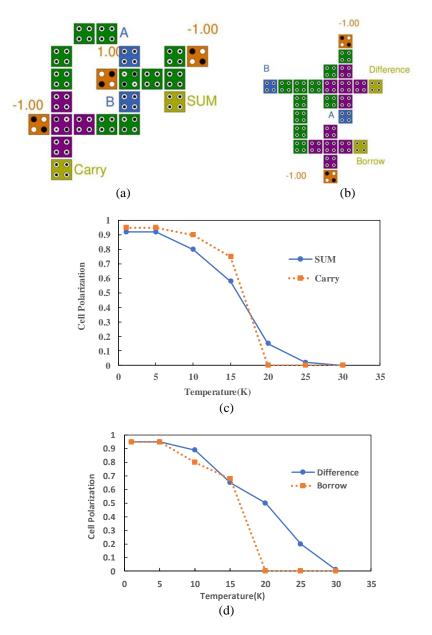

Less complex combinational circuits like half-adder and half-subtractor are also designed in the QCA technology and shown in Figure 9. The adder and subtractor QCA circuits are shown in Figures 9(a) and 9(b) and their temperature sensitive analysis results are shown in Figures 9(c) and 9(d). It can be observed that the cell becomes unstable at the temperature of 10 K.

Figure 9. Design of combinational circuits in QCA (a) half adder, (b) half subtractor, (c) temperature variation analysis of half adder, and (d) temperature variation analysis of half subtractor

### 4. CONCLUSION

This work analyses a majority and minority gate using QCA. The majority gates are designed in various possible styles. The power dissipation and circuit area of Type-2 majority is observed to be higher than the other types. However, Type-2 majority is recommended for the design of digital logic gates in QCA due to high fan-out and less noise sensitivity. The majority is further used to design the AND and OR gates and the minority gate is used to design the NAND and NOR gates. It is observed that all logic gates are correctly functioning. Also, less complex combinational circuits like half adder and subtractor circuits are also designed. Finally, temperature sensitive analysis is performed for 3-and 5-majority gates and observed that circuits become unstable at temperatures more than 15 K. The logic gates can be extended in the future to design complex digital circuits.

A thermally aware performance analysis of quantum cellular automata logic gates (Sujatha Kotte)

#### REFERENCES

- A. Pulimeno, M. Graziano, and G. Piccinini, "Molecule interaction for QCA computation," in 2012 12th IEEE International Conference on Nanotechnology (IEEE-NANO), Aug. 2012, pp. 1–5, doi: 10.1109/NANO.2012.6322051.

- [2] C. S. Lent and P. D. Tougaw, "A device architecture for computing with quantum dots," *Proceedings of the IEEE*, vol. 85, no. 4, pp. 541–557, Apr. 1997, doi: 10.1109/5.573740.

- [3] W. Liu, L. Lu, M. O'Neill, and E. E. Swartzlander, "Cost-efficient decimal adder design in quantum-dot cellular automata," in 2012 IEEE International Symposium on Circuits and Systems, May 2012, pp. 1347–1350, doi: 10.1109/ISCAS.2012.6271491.

- [4] Y. Gang, W. Zhao, J.-O. Klein, C. Chappert, and P. Mazoyer, "A high-reliability, low-power magnetic full adder," *IEEE Transactions on Magnetics*, vol. 47, no. 11, pp. 4611–4616, Nov. 2011, doi: 10.1109/TMAG.2011.2150238.

- [5] E. P. Blair and C. S. Lent, "Quantum-dot cellular automata: an architecture for molecular computing," in *International Conference on Simulation of Semiconductor Processes and Devices, SISPAD 2003*, 2003, pp. 14–18, doi: 10.1109/SISPAD.2003.1233626.

- [6] A. Pulimeno, M. Graziano, A. Sanginario, V. Cauda, D. Demarchi, and G. Piccinini, "Bis-ferrocene molecular QCA wire: Ab Initio simulations of fabrication driven fault tolerance," *IEEE Transactions on Nanotechnology*, vol. 12, no. 4, pp. 498–507, Jul. 2013, doi: 10.1109/TNANO.2013.2261824.

- [7] K. Navi, R. Farazkish, S. Sayedsalehi, and M. Rahimi Azghadi, "A new quantum-dot cellular automata full-adder," *Microelectronics Journal*, vol. 41, no. 12, pp. 820–826, Dec. 2010, doi: 10.1016/j.mejo.2010.07.003.

- [8] R. K. Cavin, P. Lugli, and V. V. Zhirnov, "Science and engineering beyond moore's law," *Proceedings of the IEEE*, vol. 100, pp. 1720–1749, May 2012, doi: 10.1109/JPROC.2012.2190155.

- [9] M. Soeken, L. G. Amaru, P.-E. Gaillardon, and G. De Micheli, "Exact synthesis of majority-inverter graphs and its applications," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 36, no. 11, pp. 1842–1855, Nov. 2017, doi: 10.1109/TCAD.2017.2664059.

- [10] S. Angizi, S. Sarmadi, S. Sayedsalehi, and K. Navi, "Design and evaluation of new majority gate-based RAM cell in quantum-dot cellular automata," *Microelectronics Journal*, vol. 46, no. 1, pp. 43–51, Jan. 2015, doi: 10.1016/j.mejo.2014.10.003.

- [11] E. AlKaldy, A. H. Majeed, M. S. Zainal, and D. M. Nor, "Optimum multiplexer design in quantum-dot cellular automata," *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, vol. 17, no. 1, pp. 148–155, Jan. 2020, doi: 10.11591/ijeecs.v17.i1.pp148-155.

- [12] A. Roohi, R. Zand, S. Angizi, and R. F. DeMara, "A parity-preserving reversible QCA gate with self-checking cascadable resiliency," *IEEE Transactions on Emerging Topics in Computing*, vol. 6, no. 4, pp. 450–459, Oct. 2018, doi: 10.1109/TETC.2016.2593634.

- [13] L. H. B. Sardinha, A. M. M. Costa, O. P. V. Neto, L. F. M. Vieira, and M. A. M. Vieira, "NanoRouter: A quantum-dot cellular automata design," *IEEE Journal on Selected Areas in Communications*, vol. 31, no. 12, pp. 825–834, Dec. 2013, doi: 10.1109/JSAC.2013.SUP2.12130015.

- [14] M. Kianpour, R. Sabbaghi-Nadooshan, and K. Navi, "A novel design of 8-bit adder/subtractor by quantum-dot cellular automata," *Journal of Computer and System Sciences*, vol. 80, no. 7, pp. 1404–1414, Nov. 2014, doi: 10.1016/j.jcss.2014.04.012.

- [15] P. D. Tougaw and C. S. Lent, "Dynamic behavior of quantum cellular automata," *Journal of Applied Physics*, vol. 80, no. 8, pp. 4722–4736, Oct. 1996, doi: 10.1063/1.363455.

- [16] V. Pudi and K. Sridharan, "A bit-serial pipelined architecture for high-performance DHT computation in quantum-dot cellular automata," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, no. 10, pp. 2352–2356, Oct. 2015, doi: 10.1109/TVLSI.2014.2363519.

- [17] F. Ahmad, S. Ahmed, V. Kakkar, G. M. Bhat, A. N. Bahar, and S. Wani, "Modular design of ultra-efficient reversible full addersubtractor in QCA with power dissipation analysis," *International Journal of Theoretical Physics*, vol. 57, no. 9, pp. 2863–2880, Sep. 2018, doi: 10.1007/s10773-018-3806-3.

- [18] N. Safoev and J.-C. Jeon, "A novel controllable inverter and adder/subtractor in quantum-dot cellular automata using cell interaction based XOR gate," *Microelectronic Engineering*, vol. 222, Feb. 2020, doi: 10.1016/j.mee.2019.111197.

- [19] P. Wang, M. Niamat, S. Vemuru, M. Alam, and T. Killian, "Comprehensive majority/minority logic synthesis method," in 2013 13th IEEE International Conference on Nanotechnology (IEEE-NANO 2013), Aug. 2013, pp. 694–697, doi: 10.1109/NANO.2013.6720858.

- [20] V. Pudi and K. Sridharan, "New decomposition theorems on majority logic for low-delay adder designs in quantum dot cellular automata," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 59, no. 10, pp. 678–682, Oct. 2012, doi: 10.1109/TCSII.2012.2213356.

- [21] A. M. Chabi, S. Sayedsalehi, S. Angizi, and K. Navi, "Efficient QCA exclusive-or and multiplexer circuits based on a nanoelectronic-compatible designing approach," *International Scholarly Research Notices*, vol. 2014, pp. 1–9, Oct. 2014, doi: 10.1155/2014/463967.

- [22] K. Kong, Y. Shang, and R. Lu, "An optimized majority logic synthesis methodology for quantum-dot cellular automata," *IEEE Transactions on Nanotechnology*, vol. 9, no. 2, pp. 170–183, Mar. 2010, doi: 10.1109/TNANO.2009.2028609.

- [23] P. Wang, M. Niamat, and S. Vemuru, "Minimal majority gate mapping of 4-variable functions for quantum cellular automata," in 2011 11th IEEE International Conference on Nanotechnology, Aug. 2011, pp. 1307–1312, doi: 10.1109/NANO.2011.6144617.

- [24] S. Sheikhfaal, S. Angizi, S. Sarmadi, M. Hossein Moaiyeri, and S. Sayedsalehi, "Designing efficient QCA logical circuits with power dissipation analysis," *Microelectronics Journal*, vol. 46, no. 6, pp. 462–471, Jun. 2015, doi: 10.1016/j.mejo.2015.03.016.

- [25] M. Goswami, B. Sen, and B. K. Sikdar, "Design of low power 5-input majority voter in quantum-dot cellular automata with effective error resilience," in 2016 Sixth International Symposium on Embedded Computing and System Design (ISED), Dec. 2016, pp. 101– 105, doi: 10.1109/ISED.2016.7977063.

- [26] H. Balijepalli and M. Niamat, "Design of a nanoscale quantum-dot cellular automata configurable logic block for FPGAs," in 2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS), Aug. 2012, pp. 622–625, doi: 10.1109/MWSCAS.2012.6292097.

- [27] A. H. Majeed, "An ultra-low complexity of 2:1 multiplexer block in QCA technology," *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, vol. 21, no. 3, pp. 1341–1346, Mar. 2021, doi: 10.11591/ijeecs.v21.i3.pp1341-1346.

- [28] M. R. Bonyadi, S. M. R. Azghadi, N. M. Rad, K. Navi, and E. Afjei, "Logic optimization for majoritygate-based nanoelectronic circuits based on genetic algorithm," in 2007 International Conference on Electrical Engineering, Apr. 2007, pp. 1–5, doi: 10.1109/ICEE.2007.4287307.

- [29] S. M. Dadgar, R. Farazkish, and A. Sahafi, "Presentation of a fault tolerance algorithm for design of quantum-dot cellular automata circuits," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 12, no. 5, pp. 4722–4733, Oct. 2022, doi: 10.11591/ijece.v12i5.pp4722-4733.

[30] K. Walus, T. J. Dysart, G. A. Jullien, and R. A. Budiman, "QCADesigner: A rapid design and simulation Tool for quantum-dot cellular automata," *IEEE Transactions on Nanotechnology*, vol. 3, no. 1, pp. 26–31, Mar. 2004, doi: 10.1109/TNANO.2003.820815.

# **BIOGRAPHIES OF AUTHORS**

Sujatha Kotte 🗊 🕄 🖾 🗘 received B. Tech in Electronics and Communication Engineering in 2006 from Jawaharlal Nehru University, Hyderabad, India, M. Tech in embedded systems in 2011 from JNTU, Hyderabad, and pursuing a Ph.D. in low power VLSI design from Osmania University, Hyderabad, India. She is worked as an Assistant Professor, in various Engineering colleges. Her research interests include nanoelectronics, quantum dot cellular automata, carbon nanotubes, and digital VLSI design. She can be contacted at sujathakotte24@gmail.com.

**Ganapavarapu Kanaka Durga B K** received B. Tech in Electronics and Comm. Engineering in 1989 from Nagarjuna University, M.E in systems & control engineering in 1997 from Osmania University, Hyderabad, India, and Ph.D. in Low Power VLSI Design in 2010 from JNTU, Hyderabad, India. Currently, she works as a principal and professor in the department of electronics and communication engineering, at MaturiVenkataSubba Rao Engineering College, Hyderabad, India. She has been working in MaturiVenkataSubba Rao (MVSR) Engineering College since 1991, her area of interest is low-power VLSI design, analog electronics and nanoelectronics, she can be contacted at email: kanakadurga\_ece@mvsrec.edu.in.