University of Texas Rio Grande Valley ScholarWorks @ UTRGV

Theses and Dissertations

8-2020

# Improving Hardware Implementation of Cryptographic AES Algorithm and the Block Cipher Modes of Operation

Chu-Wen Cheng The University of Texas Rio Grande Valley

Follow this and additional works at: https://scholarworks.utrgv.edu/etd

Part of the Electrical and Computer Engineering Commons

### **Recommended Citation**

Cheng, Chu-Wen, "Improving Hardware Implementation of Cryptographic AES Algorithm and the Block Cipher Modes of Operation" (2020). *Theses and Dissertations*. 636. https://scholarworks.utrgv.edu/etd/636

This Thesis is brought to you for free and open access by ScholarWorks @ UTRGV. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks @ UTRGV. For more information, please contact justin.white@utrgv.edu, william.flores01@utrgv.edu.

# IMPROVING HARDWARE IMPLEMENTATION OF CRYPTOGRAPHIC AES ALGORITHM AND THE BLOCK CIPHER MODES OF OPERATION

A Thesis by CHU-WEN CHENG

Submitted to the Graduate College of The University of Texas Rio Grande Valley In partial fulfilment of the requirements for the degree of

MASTER OF SCIENCE IN ENGINEERING

August 2020

Major Subject: ELECTRICAL ENGINEERING

# IMPROVING HARDWARE IMPLEMENTATION OF CRYPTOGRAPHIC AES ALGORITHM AND THE BLOCK CIPHER MODES OF OPERATION

A Thesis by Chu-Wen Cheng

### COMMITTEE MEMBERS

Dr. Sanjeev Kumar Chair of Committee

Dr. Weidong Kuang Committee Member

Dr. Wenjie Dong Committee Member

August 2020

Copyright 2020 Chu-Wen Cheng All Rights Reserved

### ABSTRACT

Cheng, Chu-Wen, <u>Improving Hardware Implementation Of Cryptographic AES Algorithm And</u> <u>The Block Cipher Modes Of Operation</u>. Master of Science in Engineering (MSE), August 2020, 149 pp., 19 tables, 127 figures, 45 references.

With ever increasing Internet traffic, more business and financial transactions are being conducted online. This is even more so during these days of COVID-19 pandemic when traditional businesses such as traditional face to face educational systems have gone online requiring huge amount of data being exchanged over Internet. Increase in the volume of data sent over the Internet has also increased the security vulnerabilities such as challenging the confidentiality of data being sent over the Internet. Due to sheer volume, all data will need to be effectively encrypted. Due to increase in the volume of data, it is also important to have encryption/decryption functions to work at a higher speed to maintain the confidentiality of sensitive data.

In this thesis, our goal is to enhance the hardware speed of encryption process of the standard AES scheme and its four variants such as AES-128, AES-192, AES-256 and new AES-512 and implement such functions on an FPGA. We also consider the FPGA implementation of different modes of AES operation.

By employing parallelism and pipelining approach, we attempt to speed up various computational components of AES implementations using the Quartus II onto Intel's FPGA. This approach shows improvement in the response speed, data throughput and latency.

iii

### DEDICATION

The contribution and dedication of many people is hidden behind my small achievement. I want to dedicate this thesis to

My parents

For supporting and encouraging me to believe in myself.

My wife

For taking care of me and kids' need in every way and letting me concentrate on my study.

### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to all committee members, Professor Sanjeev Kumar, Professor Weidong Kuang, and Professor Wenjie Dong, for their support. Special thanks to Dr. Kumar, Chair of Committee, for his patience, advisement, motivation, and immense knowledge in my studies which aided in accomplishing this thesis. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better advisor and mentor for my master study.

Besides my advisor, I would like to thank the rest of my thesis committee: Professor Weidong Kuang, and Professor Wenjie Dong, for their insightful comments and encouragement. I thank my fellow colleague in networking lab for the stimulating discussions, for the time we were working together on conference or journal paper and in our group meeting. Their friendships are what I hope to keep forever even after I graduate.

Most importantly, none of this could have happened without my family. My parents have been kind and supportive to me over the last several years and I truly appreciate my wonderful wife taking great care of my kids while I am in school. This dissertation stands as a testament to their unconditional love and encouragement.

The support for the research in this thesis is provided in part by the grant awarded to Dr. Sanjeev Kumar by the National Science Foundation (NSF), Houston Endowment Chair in Science, Math, and Technology Fellowship, and Lloyd Benston Jr. Endowment Fellowship.

## TABLE OF CONTENTS

| Page                                                |

|-----------------------------------------------------|

| ABSTRACTiii                                         |

| DEDICATIONv                                         |

| ACKNOWLEDGEMENTSvi                                  |

| TABLE OF CONTENTS                                   |

| LIST OF TABLES                                      |

| LIST OF FIGURES                                     |

| CHAPTER I. INTRODUCTION1                            |

| 1.1 Statement of the Problem2                       |

| 1.2 Symmetric Encryption Algorithm-AES              |

| 1.2.1 Background                                    |

| 1.2.2 Substitute bytes                              |

| 1.2.3 Shift Rows                                    |

| 1.2.4 Mix Columns9                                  |

| 1.2.5 Add Round Key10                               |

| 1.2.6 Key expansion of AES-128, 192, 256 and 512 11 |

| 1.3 Block Cipher Modes of Operation13               |

| 1.3.1 Background13                                  |

| 1.3.2 Modes of operation14                          |

| 1.3.2.1 Electronic Codebook (ECB)14                 |

|         | 1.3.2.2            | Cipher Block Chaining (CBC)               | 15 |

|---------|--------------------|-------------------------------------------|----|

|         | 1.3.2.3            | Cipher Feedback Mode (CFB)                | 17 |

|         | 1.3.2.4            | Output Feedback Mode (OFB)                | 19 |

|         | 1.3.2.5            | Counter Mode (CTR)                        | 20 |

|         | 1.4 Hardware and   | Software Design Assessment                | 22 |

|         | 1.5 Thesis Outline | e                                         | 23 |

| CHAPTER | R II. HARDWARE     | E IMPLEMENTATION OF IMPROVED MIX COLUMN   |    |

|         | COMPUTAT           | ION OF CRYPTOGRAPHIC AES                  | 24 |

|         | 2.1 Rijndael Mix   | Column Computation                        | 24 |

|         | 2.2 Design Metho   | ods and Discussion                        | 26 |

|         | 2.3 Result and Ar  | nalysis                                   | 29 |

|         | 2.4 Conclusion     |                                           | 33 |

| CHAPTER | R III. A FAST IMF  | PLEMENTATION OF THE RIJNDAEL SUBSTITUTION |    |

|         | BOX FOR CI         | RYPTOGRAPHIC AES                          | 34 |

|         | 3.1 Rijndael Subs  | titution Box Computation                  | 38 |

|         | 3.2 Design Metho   | ods and Discussion                        | 39 |

|         | 3.3 Result and Ar  | nalysis                                   | 48 |

|         | 3.4 Conclusion     |                                           | 51 |

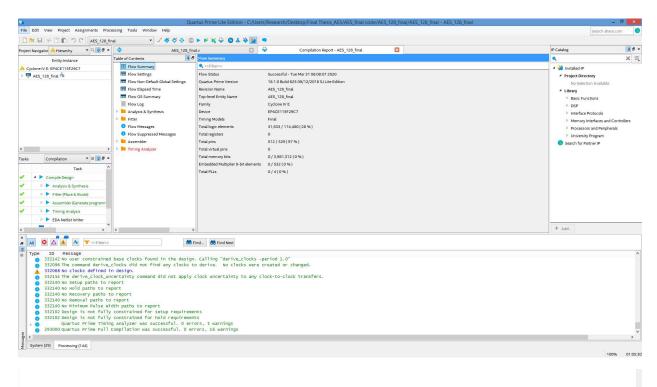

| CHAPTER | R IV. PERFORMA     | ANCE COMPARISON OF AES VARIANTS USING     |    |

|         | HARDWARI           | E IMPLEMENTATIONS ON FPGA                 | 52 |

|         | 4.1 Rijndael Key   | Expansion Computation                     | 52 |

|         |                    |                                           |    |

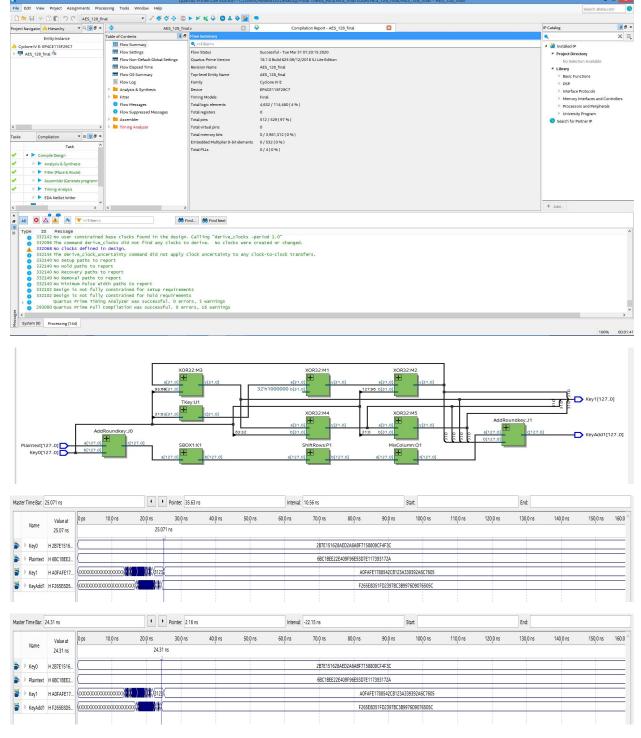

| 4.2 Design Methods and Discussion55                              |

|------------------------------------------------------------------|

| 4.3 Result and Analysis55                                        |

| 4.4 Conclusion60                                                 |

| CHAPTER V. COMPARISON AND ANALYSIS                               |

| 5.1 Avalanche Effect                                             |

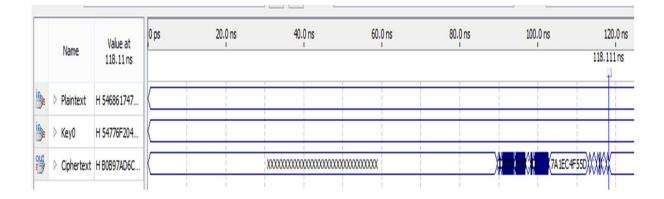

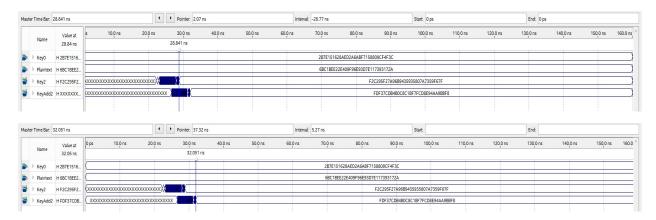

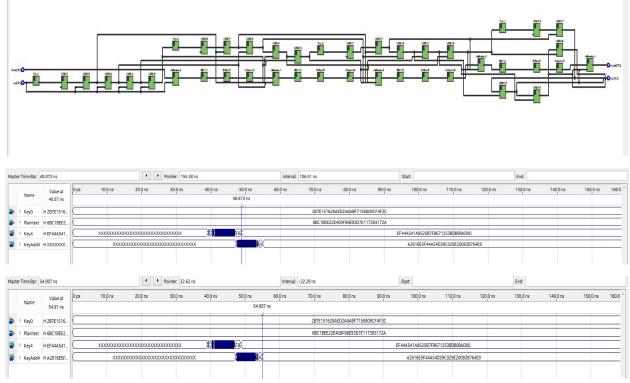

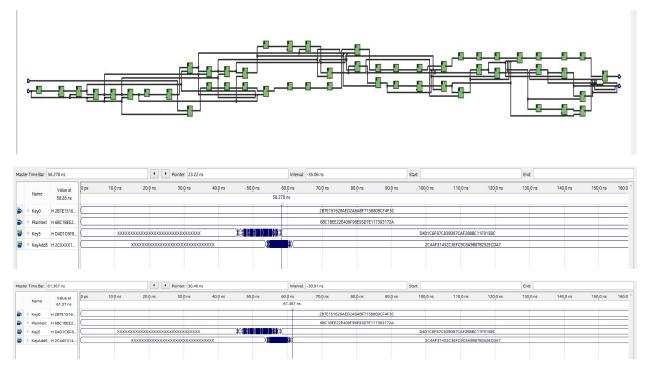

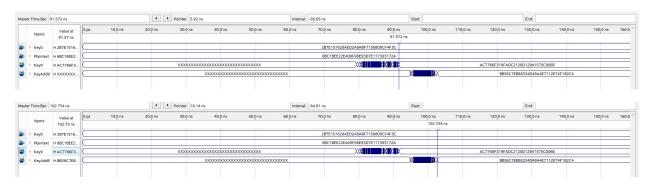

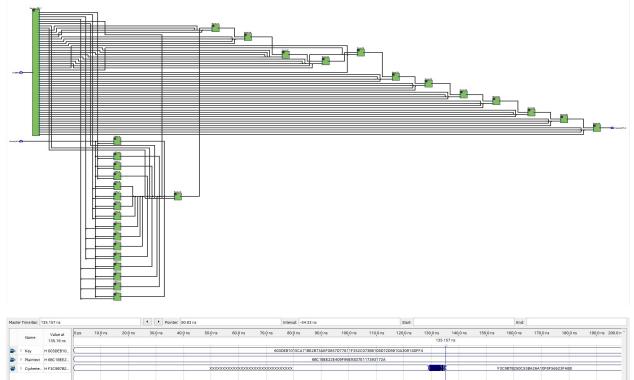

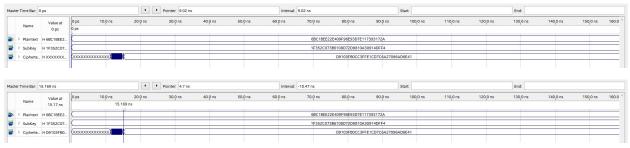

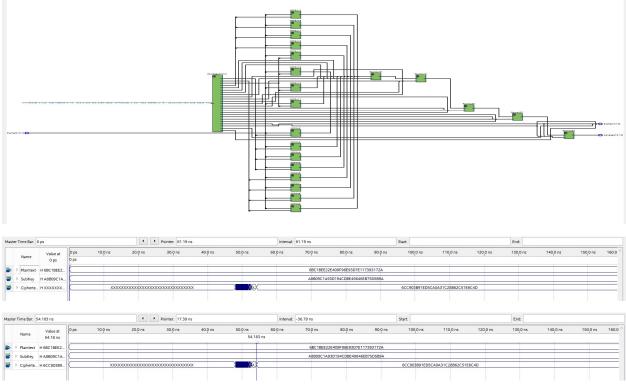

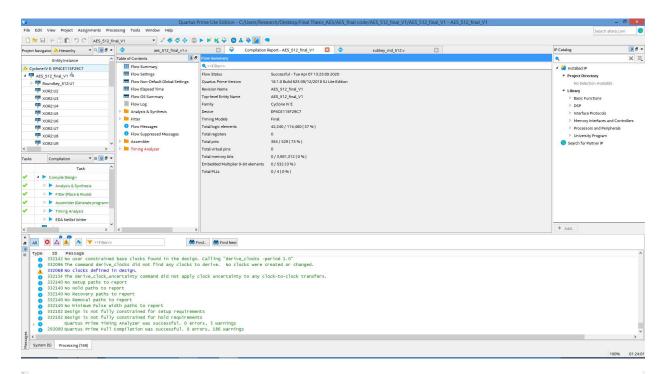

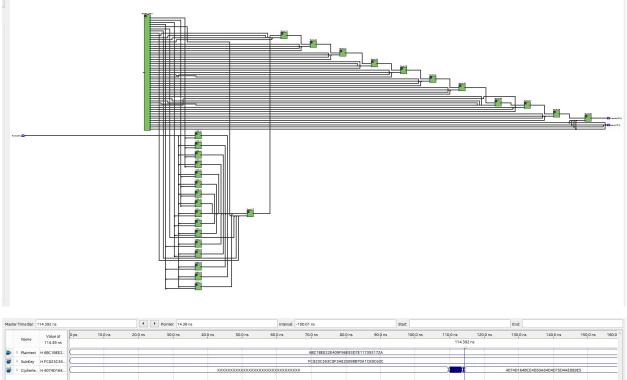

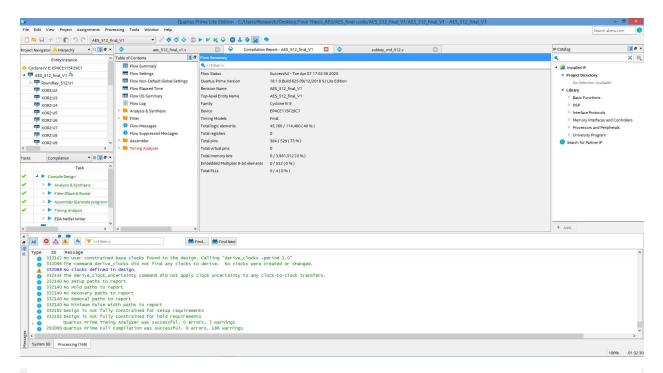

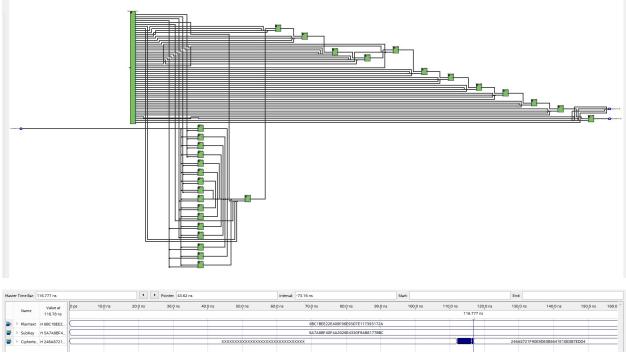

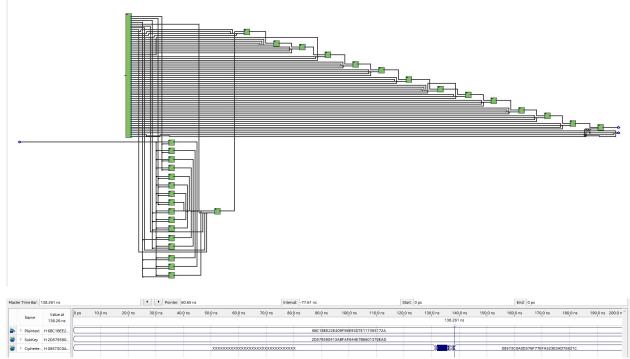

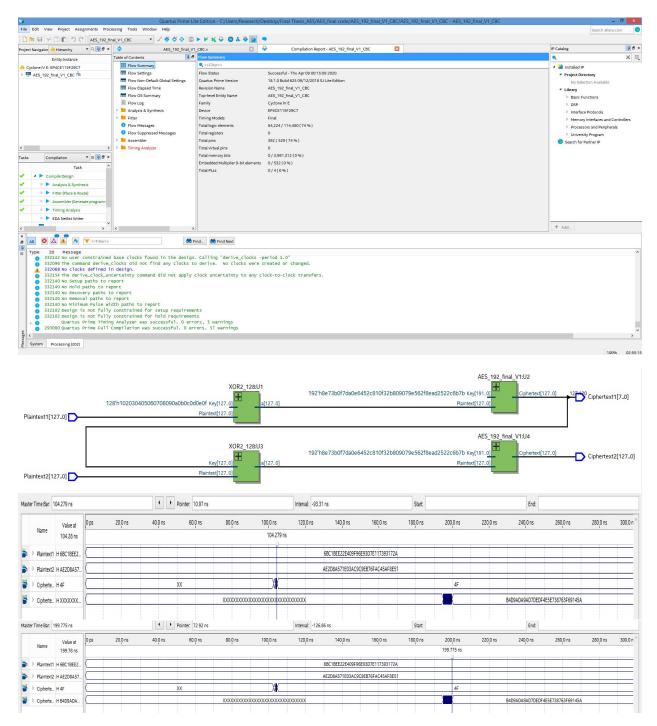

| 5.2 Timing Simulation of AES In ECB Mode63                       |

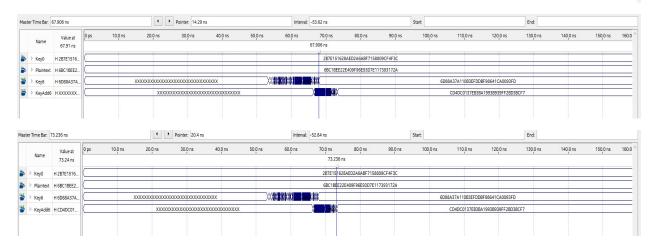

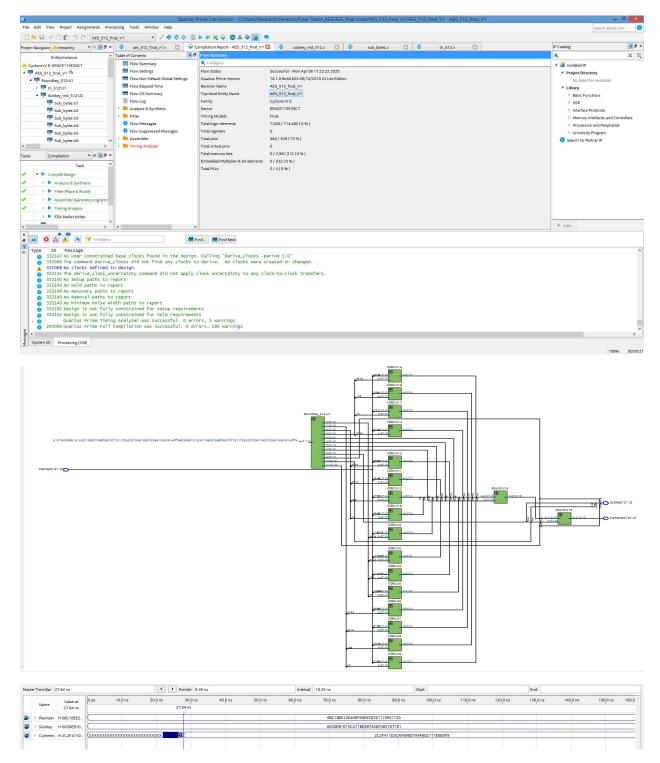

| 5.2.1 Timing Simulation of AES-12863                             |

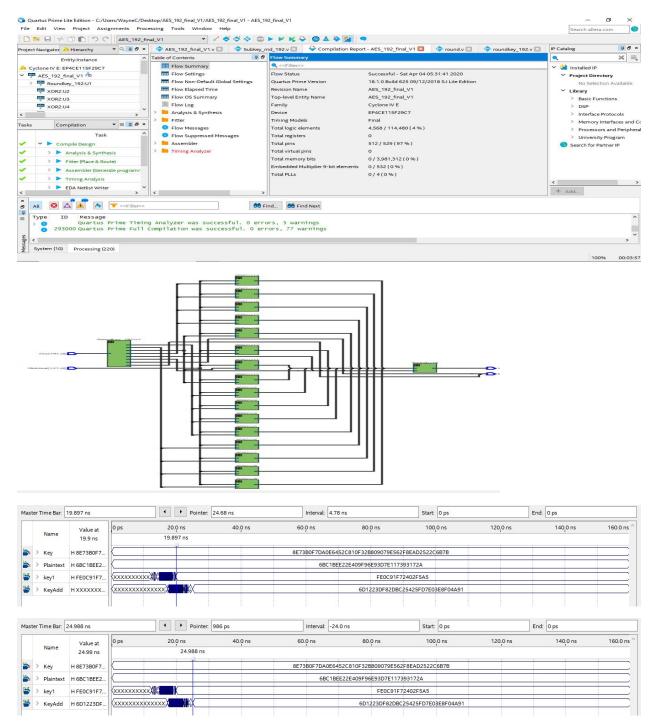

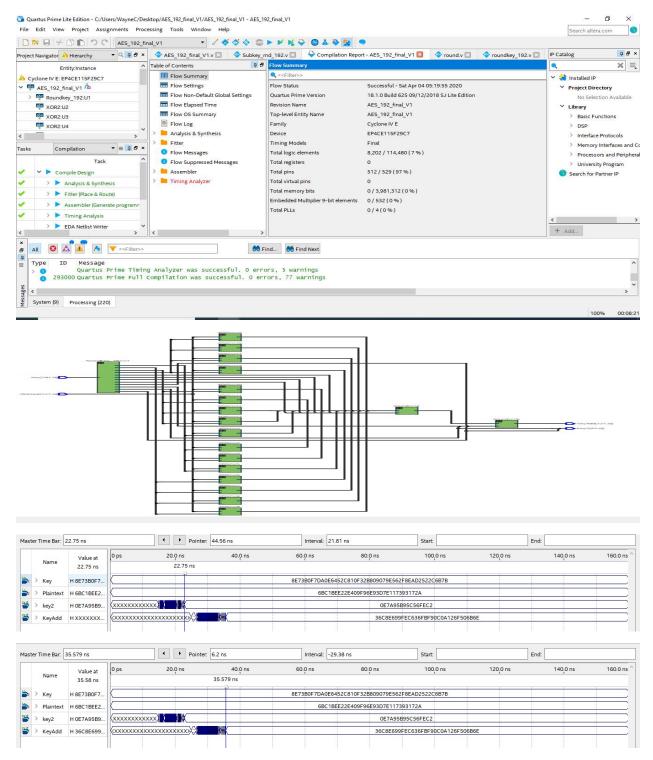

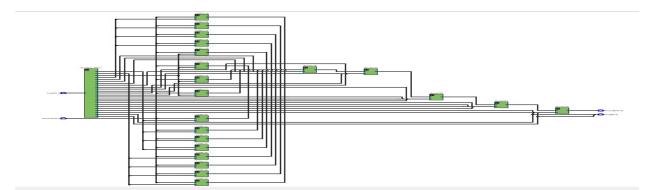

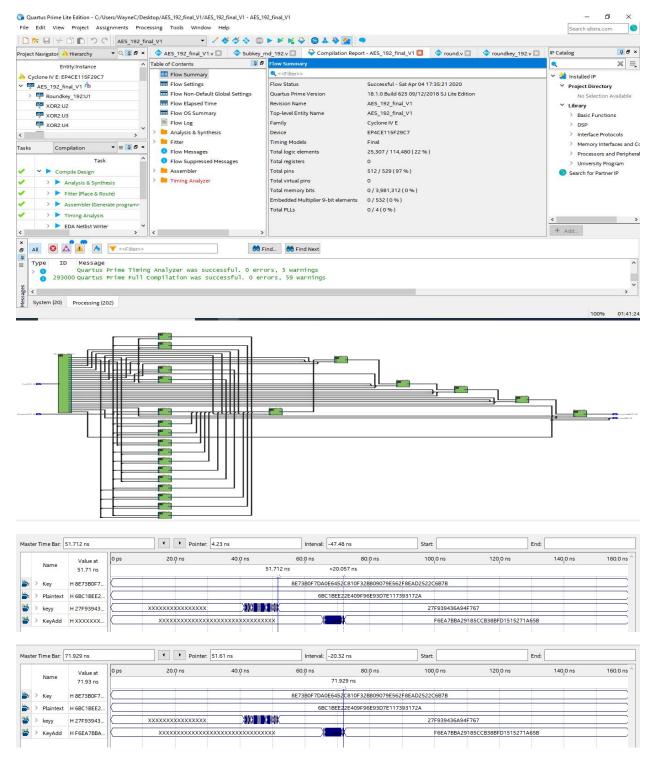

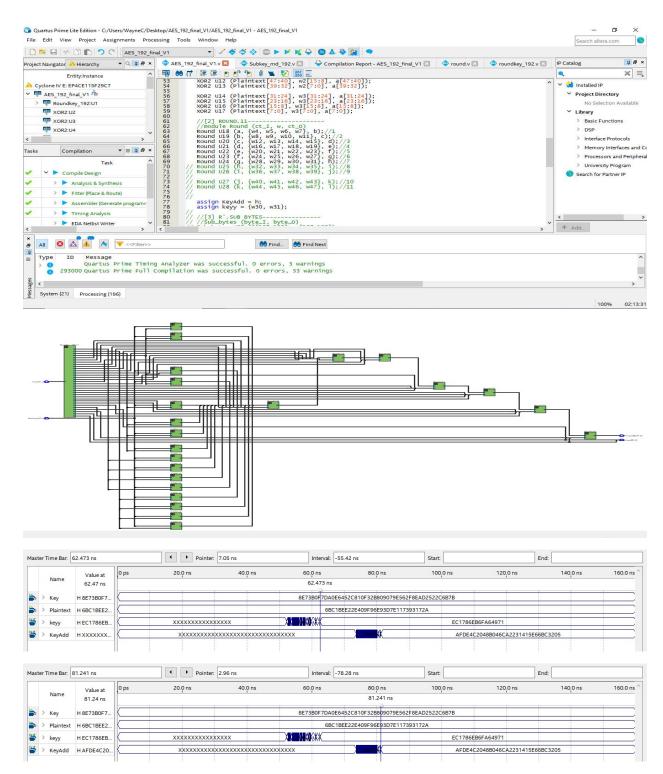

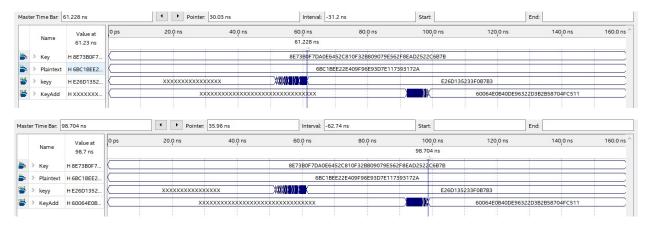

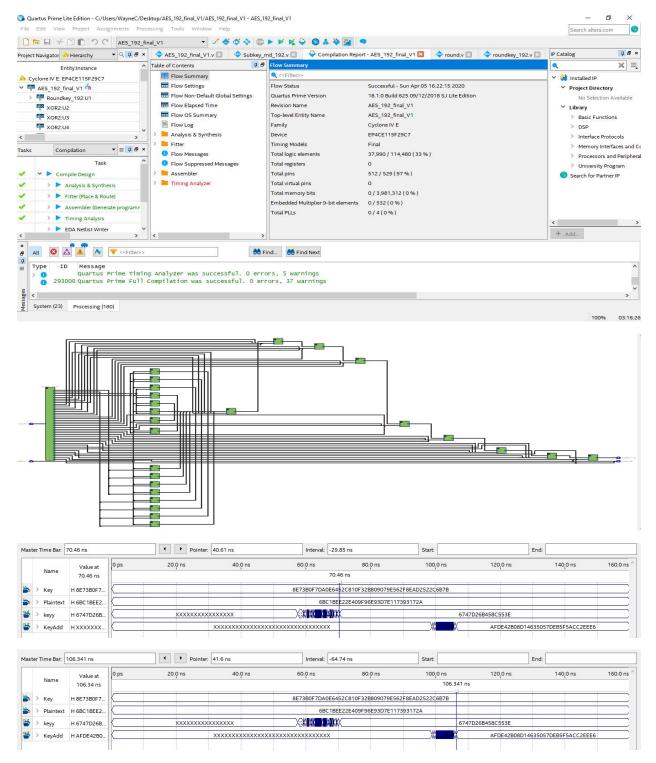

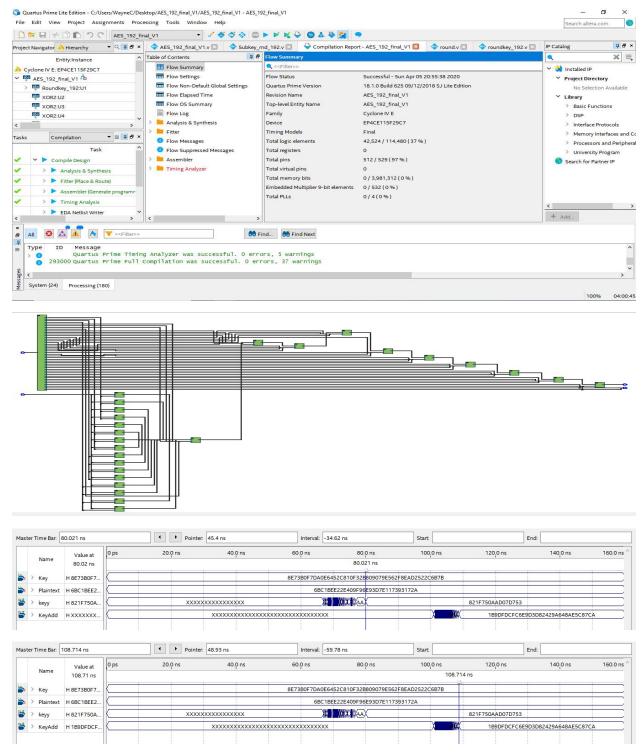

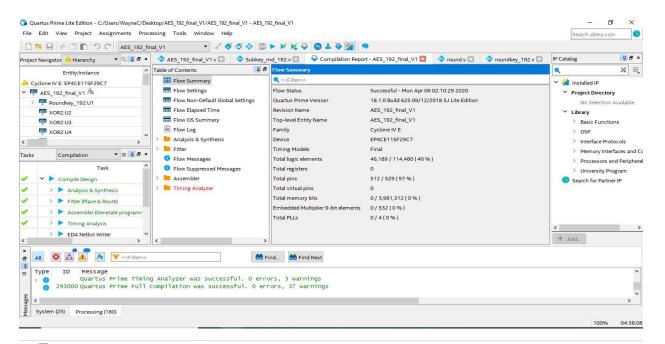

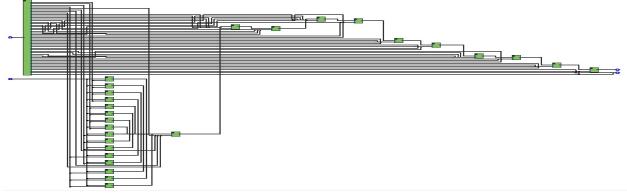

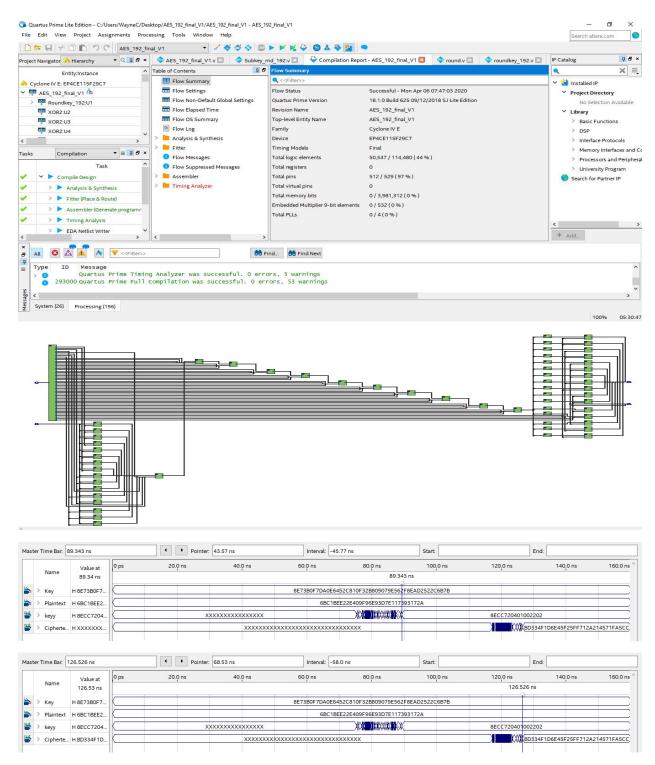

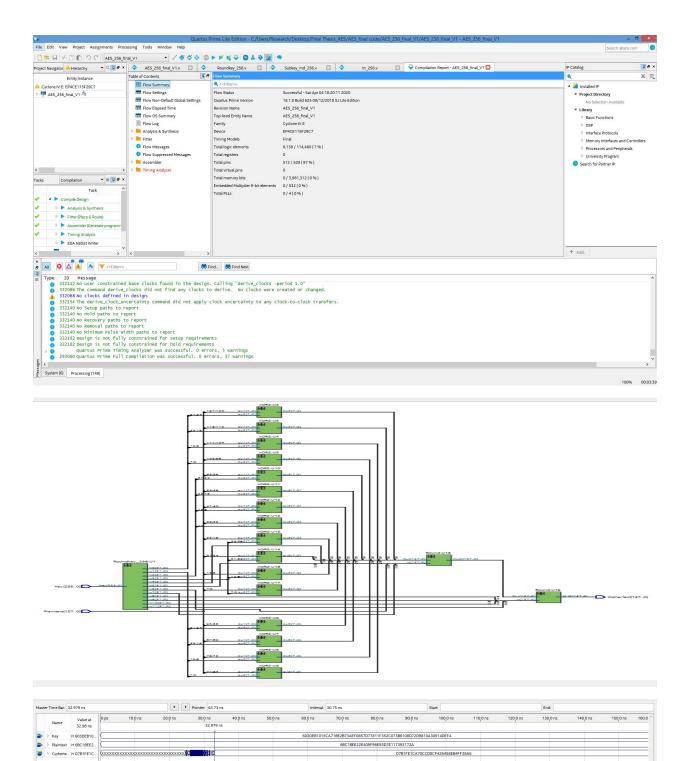

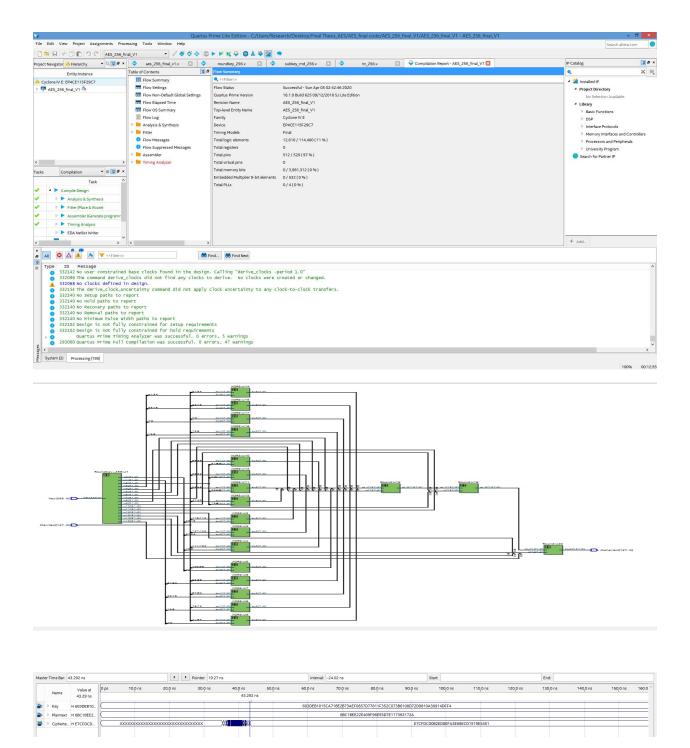

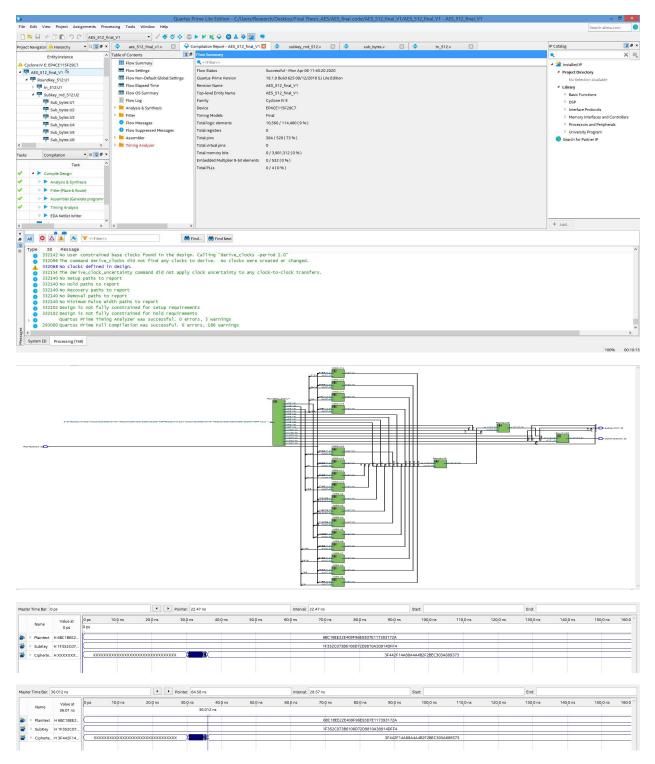

| 5.2.2 Timing Simulation of AES-19276                             |

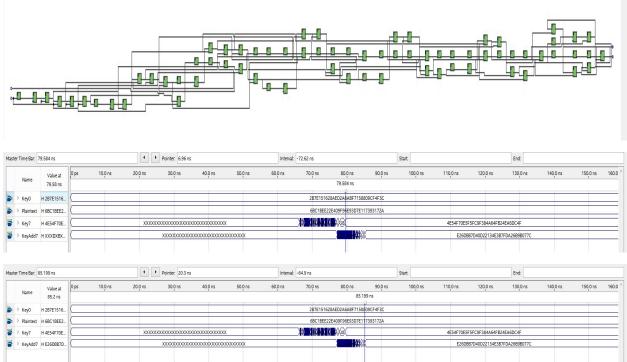

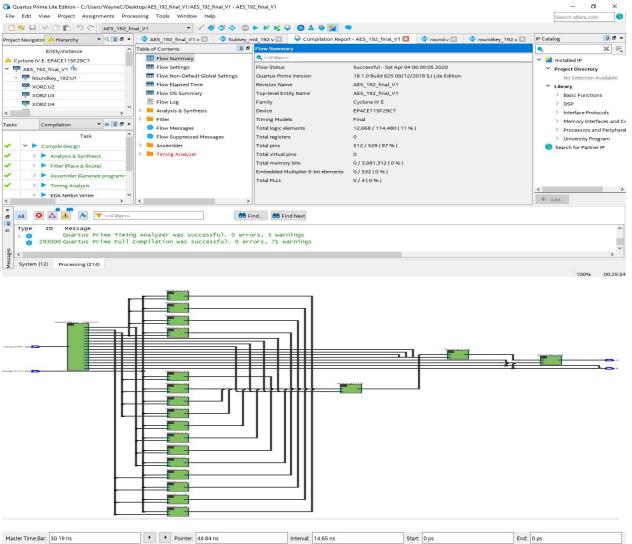

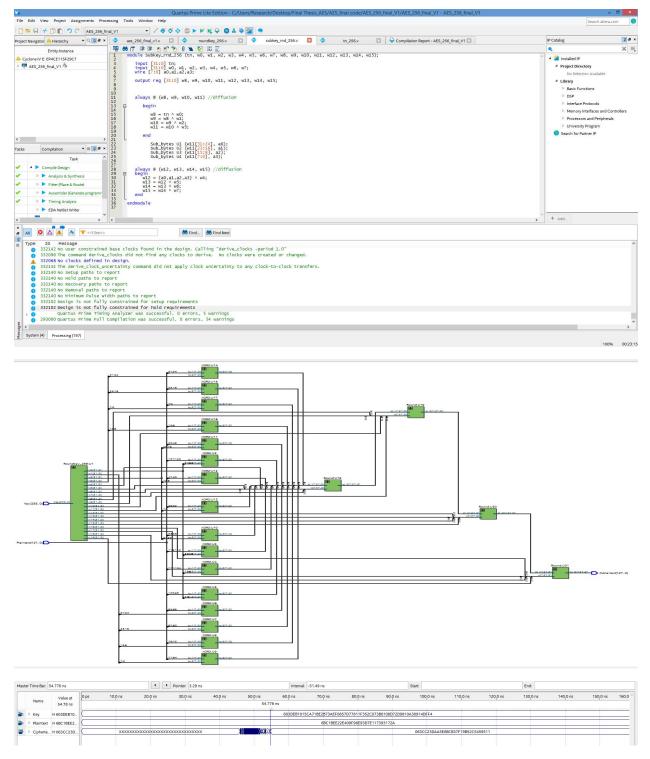

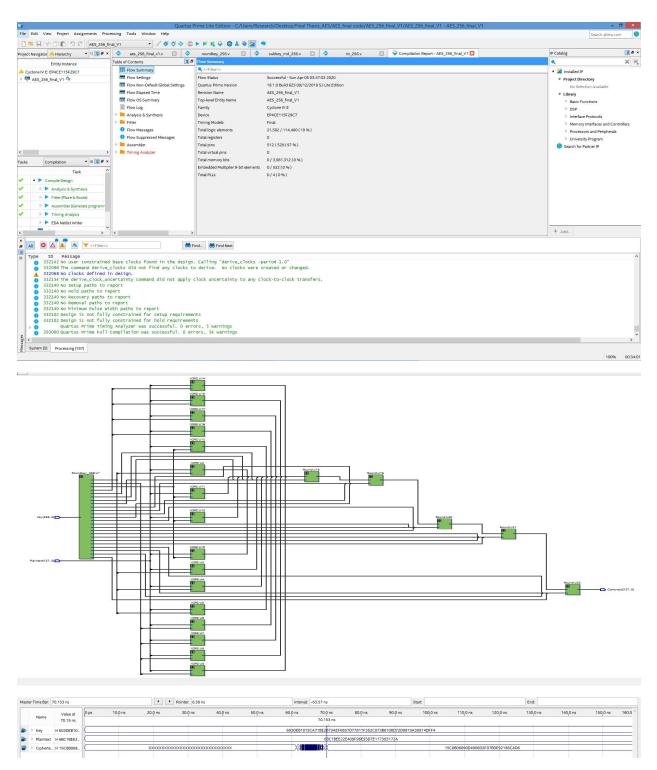

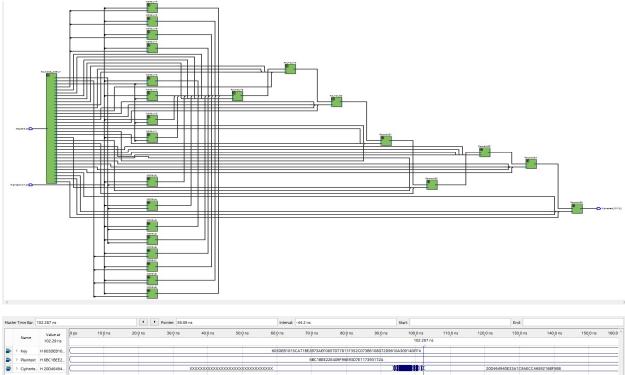

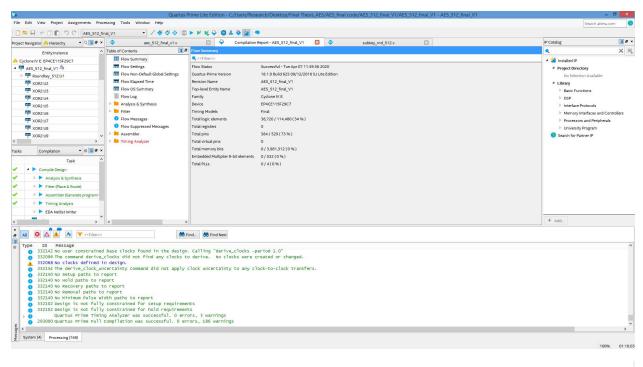

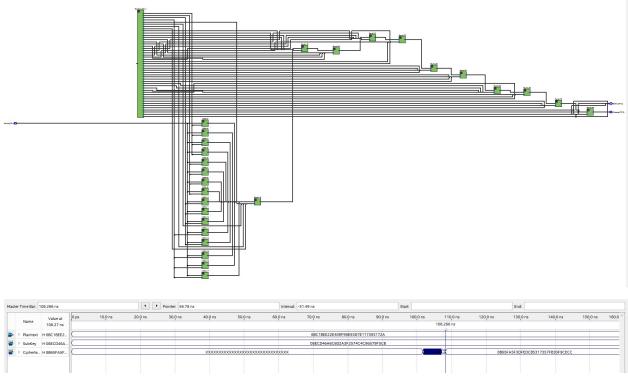

| 5.2.3 Timing Simulation of AES-256                               |

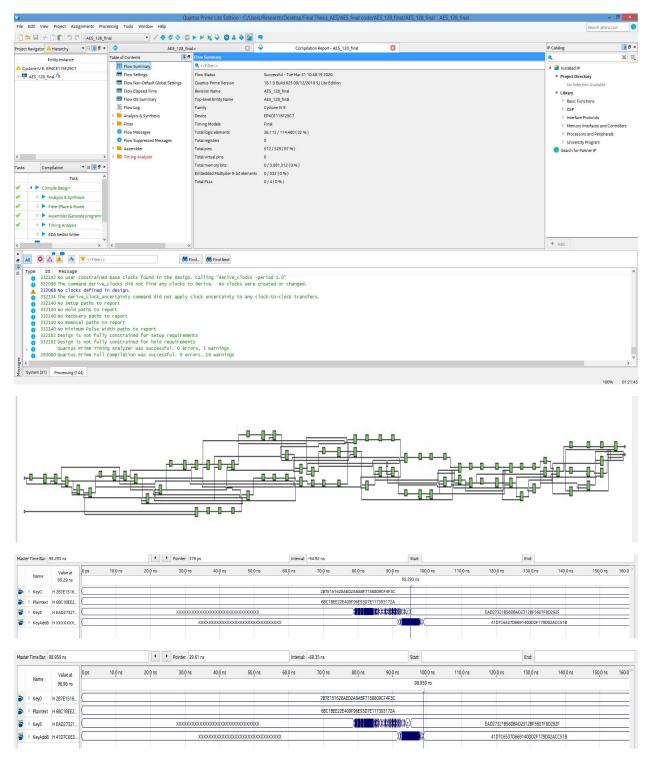

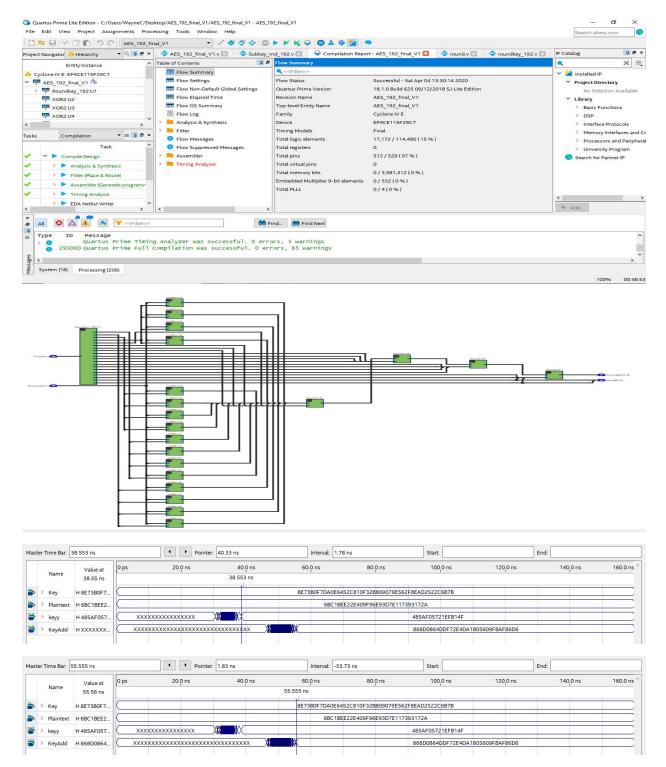

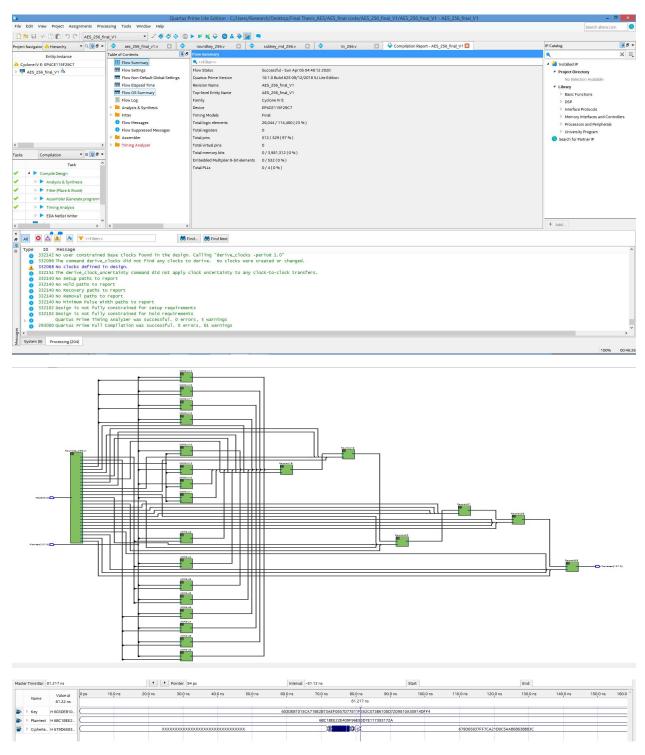

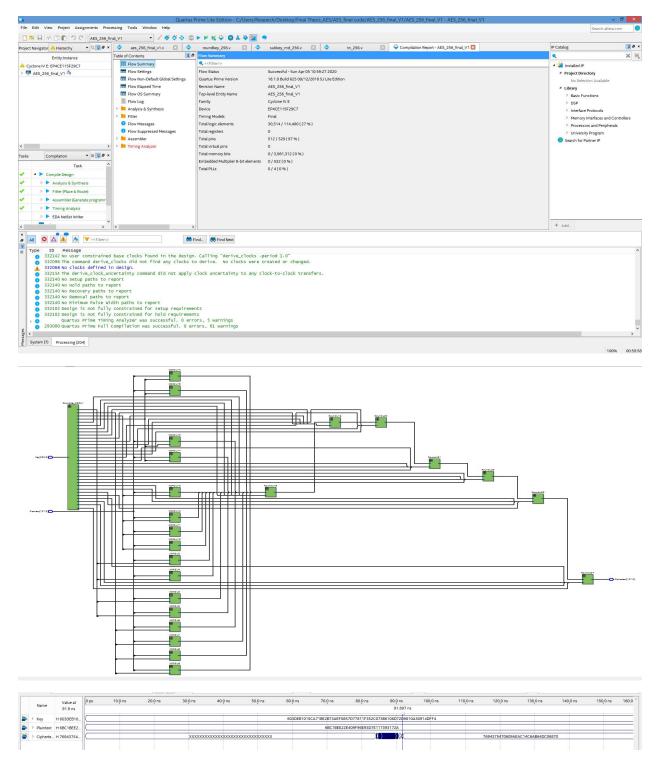

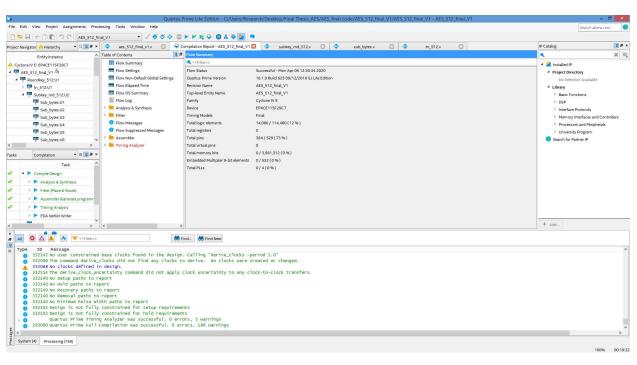

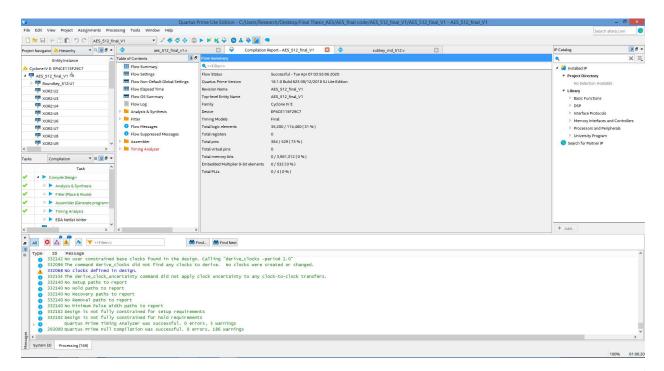

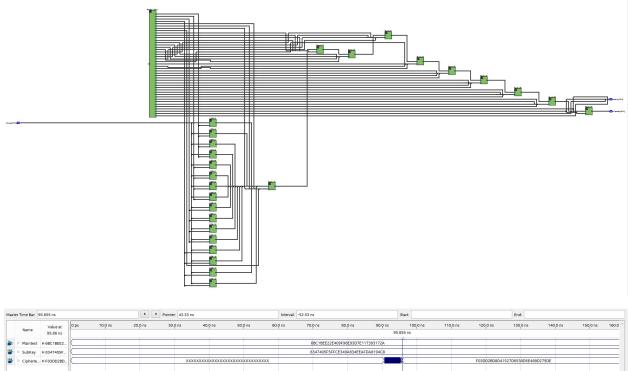

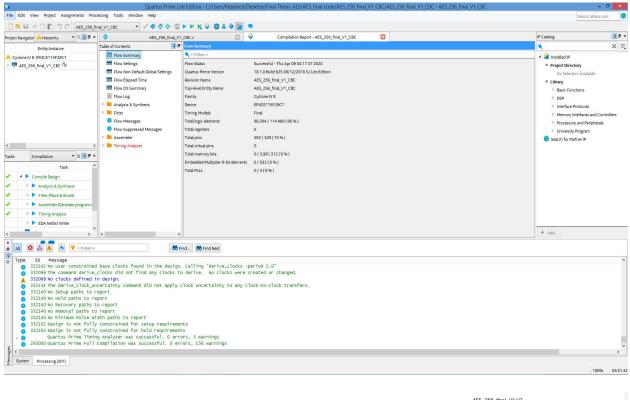

| 5.2.4 Timing Simulation of AES-512106                            |

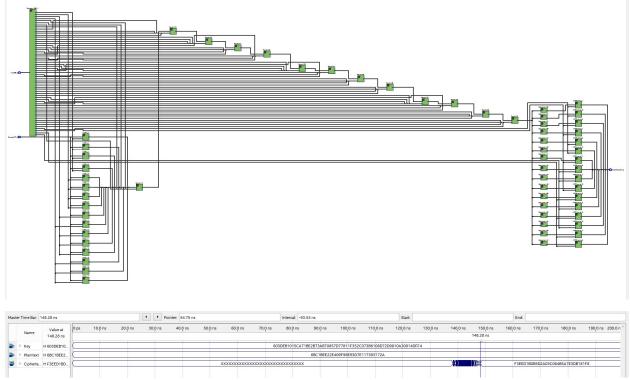

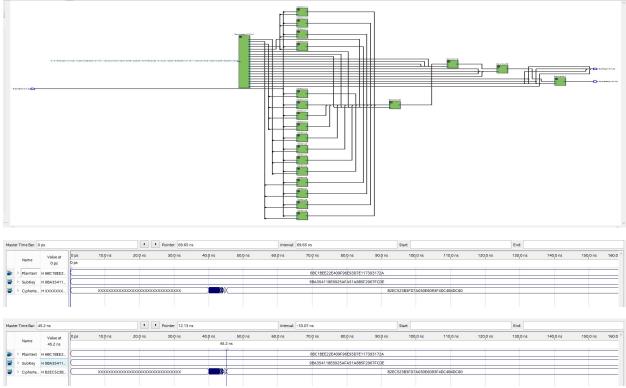

| 5.3 Timing Simulation of AES In CBC Mode124                      |

| 5.3.1 Timing Simulation of AES-128124                            |

| 5.3.2 Timing Simulation of AES-192130                            |

| 5.3.3 Timing Simulation of AES-256131                            |

| 5.3.4 Timing Simulation of AES-512132                            |

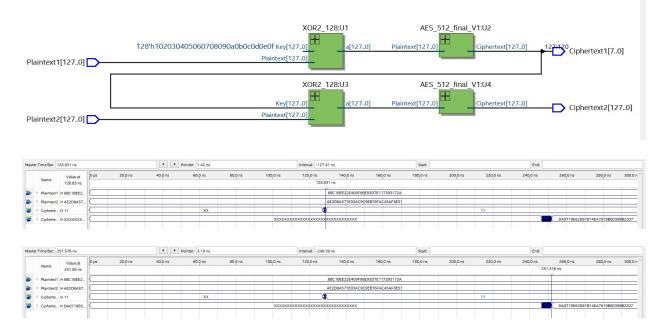

| 5.4 Comparing of Timing Simulation of AES In ECB and CBC Mode133 |

| CHAPTER VI. CONCLUSION AND FUTURE WORK142                        |

| 6.1 Conclusion142                                                |

| 6.2 Future Work                                                  |

| REFERENCES                                                       |

| BIOGRAPHICAL SKETCH                                              |

## LIST OF TABLES

| Table 1: AES Parameters                                        |

|----------------------------------------------------------------|

| Table 2: S-Box                                                 |

| Table 3: Delay of Plaintext Encryption                         |

| Table 4: Time Delay and Memory results of both implementations |

| Table 5: Design Parameter Comparison49                         |

| Table 6: Total Module Count for AES-12850                      |

| Table 7: Delay of Plaintext Encryption                         |

| Table 8: Delay of Key Expansion                                |

| Table 9: Avalanche Effect of DES62                             |

| Table 10: Avalanche Effect of AES62                            |

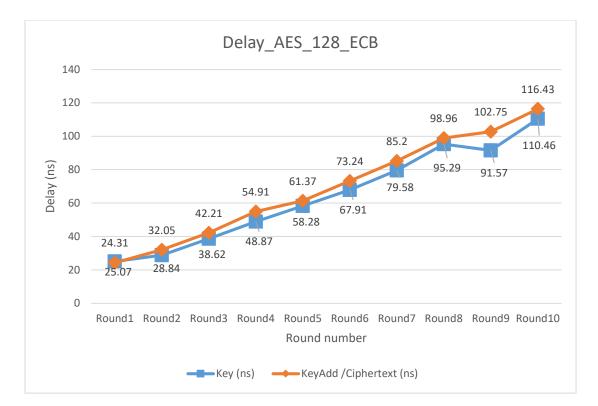

| Table 11: Delay_AES_128_ECB74                                  |

| Table 12: Delay_AES_192_ECB                                    |

| Table 13: Delay_AES_256_ECB104                                 |

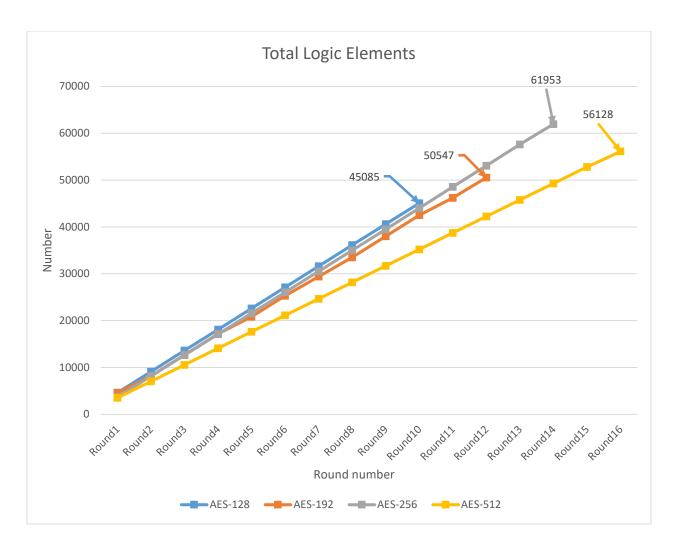

| Table 14: Delay_AES_512_ECB122                                 |

| Table 15: Delay_AES_128_CBC    128                             |

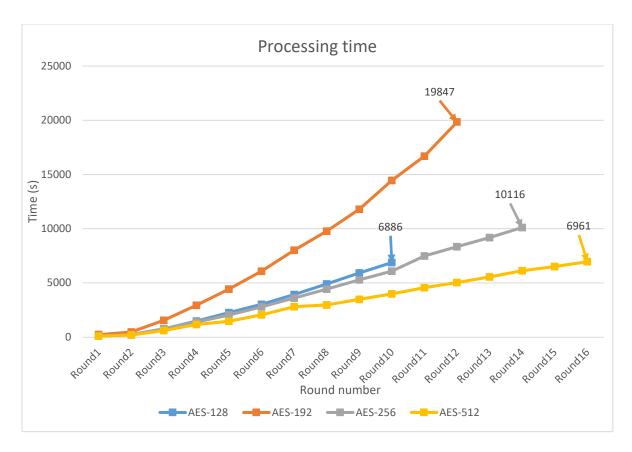

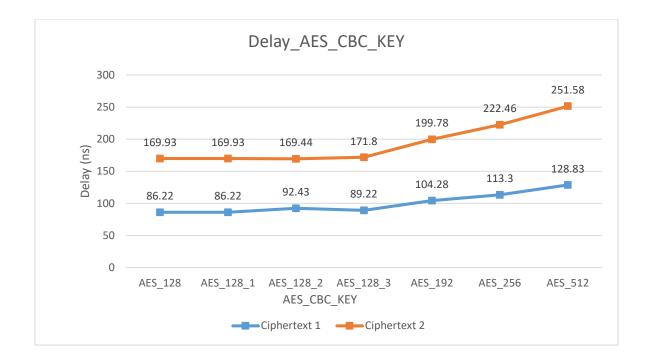

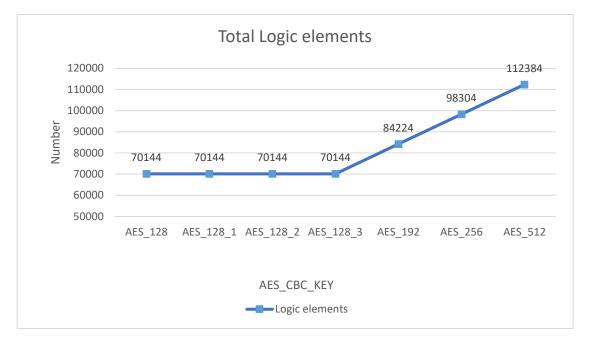

| Table 16: Delay_AES_ECB_KEY    133                             |

| Table 17: Total Logic Elements_AES_ECB_KEY                     |

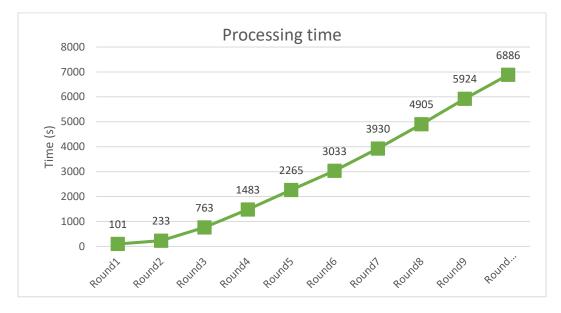

| Table 18: Processing time_AES_ECB_KEY                          |

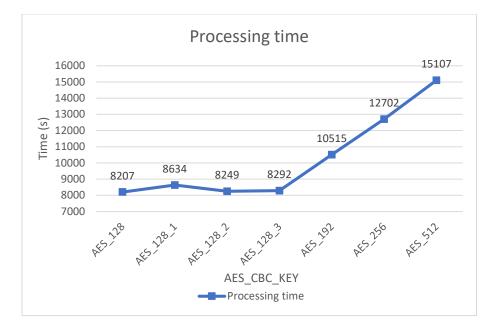

| Table 19: Performance_AES_CBC_KEY139                           |

## LIST OF FIGURES

| Page                                                                    |

|-------------------------------------------------------------------------|

| Figure 1: AES-128 Structure                                             |

| Figure 2: Substitute bytes                                              |

| Figure 3: Shift Rows                                                    |

| Figure 4: MixColumns                                                    |

| Figure 5: AddRoundKey10                                                 |

| Figure 6: AES-128 Key Expansion11                                       |

| Figure 7: AES-192 Key Expansion12                                       |

| Figure 8: AES-256 Key Expansion12                                       |

| Figure 9: AES-512 Key Expansion13                                       |

| Figure 10: Electronic codebook mode of operation (ECB)15                |

| Figure 11: Cipher block chaining mode of operation (CBC)16              |

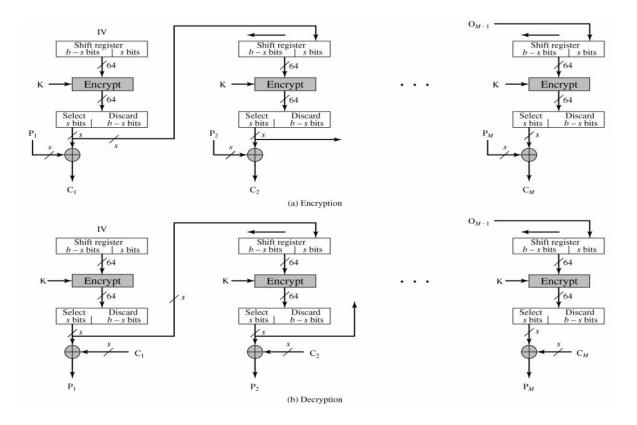

| Figure 12: Cipher feedback mode of operation (CFB)18                    |

| Figure 13: Output feedback mode of operation (OFB)19                    |

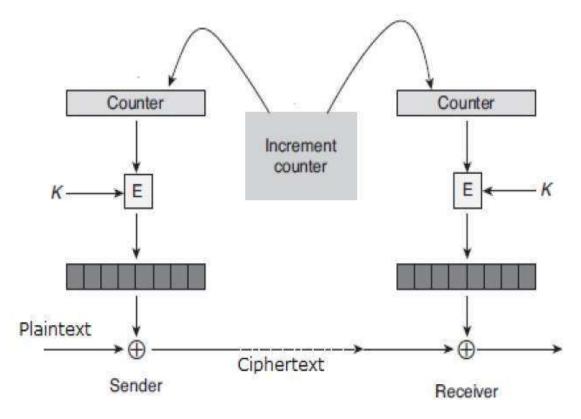

| Figure 14: Counter mode of operation (CTR)21                            |

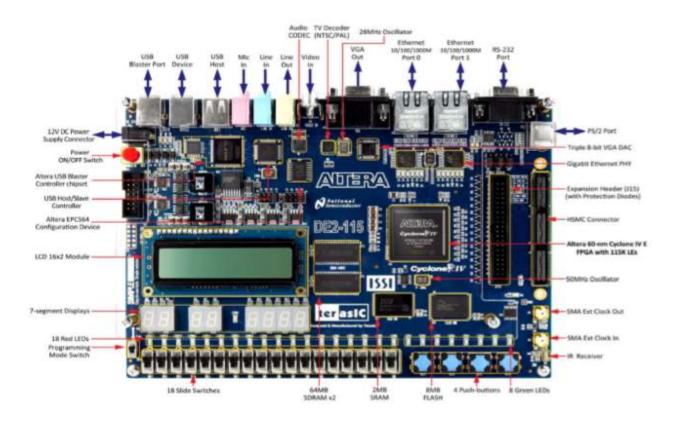

| Figure 15: Altera Cyclone IV 4CE115 FPGA Device                         |

| Figure 16: Basic information about the computer                         |

| Figure 17: Rijndael Mix Columns computation example25                   |

| Figure 18: Internal schematic of each submodule                         |

| Figure 19: Module block diagram for parallelized configuration approach |

| Figure 20: Internal schematic of M4 submodule                  |

|----------------------------------------------------------------|

| Figure 21: Delay of M2 submodule                               |

| Figure 22: Delay of M3 submodule                               |

| Figure 23: Delay of M4 submodule                               |

| Figure 24: Timing simulation showing delay without parallelism |

| Figure 25: Timing simulation showing delay with parallelism    |

| Figure 26: Time delay analysis of mixed columns                |

| Figure 27: Substitute Bytes                                    |

| Figure 28: S-Box table                                         |

| Figure 29: S-box Matrix Computation in GF (2 <sup>8</sup> )    |

| Figure 30: Baseline RTL40                                      |

| Figure 31: Design 1 S-box Segmentation41                       |

| Figure 32: Design 1 Module Map41                               |

| Figure 33: Design 1 RTL42                                      |

| Figure 34: Design 2 S-box Segmentation43                       |

| Figure 35: Design 2 Module Map43                               |

| Figure 36: Design 2 RTL44                                      |

| Figure 37: Design 3 RTL45                                      |

| Figure 38: Design 4 RTL46                                      |

| Figure 39: Design 5 RTL47                                      |

| Figure 40: Average Delay (in nanoseconds) Comparison           |

| Figure 41: Comparison of Number of Logic Elements used    |

|-----------------------------------------------------------|

| Figure 42: Add Round Key53                                |

| Figure 43: AES-512 Key Expansion                          |

| Figure 44: Delay of Mix Columns Module                    |

| Figure 45: Delay of ShiftRows Module                      |

| Figure 46: Delay of Key Module                            |

| Figure 47: Delay of XOR32 Module                          |

| Figure 48: Delay of SBOX1 Module                          |

| Figure 49: Delay of Key Expansion Module                  |

| Figure 50: Delay of Round Module                          |

| Figure 51: Delay of Encryption Module                     |

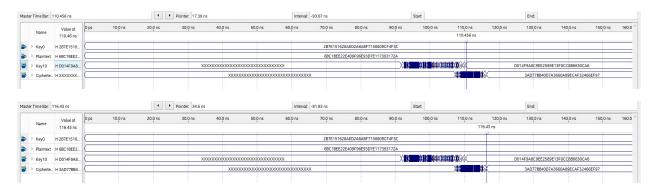

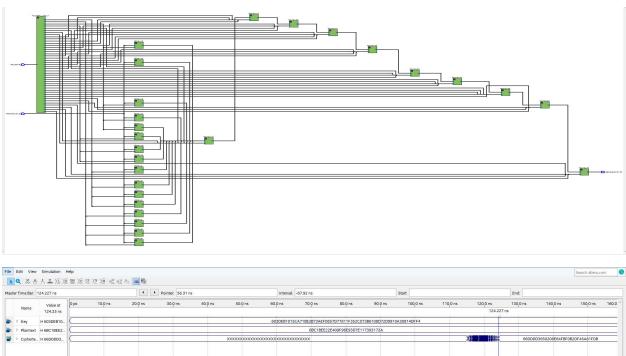

| Figure 52: Timing Simulation For AES-128 after Round 164  |

| Figure 53: Timing Simulation For AES-128 after Round 265  |

| Figure 54: Timing Simulation For AES-128 after Round 366  |

| Figure 55: Timing Simulation For AES-128 after Round 467  |

| Figure 56: Timing Simulation For AES-128 after Round 5    |

| Figure 57: Timing Simulation For AES-128 after Round 669  |

| Figure 58: Timing Simulation For AES-128 after Round 770  |

| Figure 59: Timing Simulation For AES-128 after Round 871  |

| Figure 60: Timing Simulation For AES-128 after Round 972  |

| Figure 61: Timing Simulation For AES-128 after Round 1073 |

| Figure 62: Delay_AES_128_ECB                            | 75 |

|---------------------------------------------------------|----|

| Figure 63: Processing time_AES_128_ECB                  | 75 |

| Figure 64: Timing Simulation For AES-192 after Round 1  | 76 |

| Figure 65: Timing Simulation For AES-192 after Round 2  | 77 |

| Figure 66: Timing Simulation For AES-192 after Round 3  |    |

| Figure 67: Timing Simulation For AES-192 after Round 4  |    |

| Figure 68: Timing Simulation For AES-192 after Round 5  | 80 |

| Figure 69: Timing Simulation For AES-192 after Round 6  |    |

| Figure 70: Timing Simulation For AES-192 after Round 7  |    |

| Figure 71: Timing Simulation For AES-192 after Round 8  |    |

| Figure 72: Timing Simulation For AES-192 after Round 9  |    |

| Figure 73: Timing Simulation For AES-192 after Round 10 | 85 |

| Figure 74: Timing Simulation For AES-192 after Round 11 | 86 |

| Figure 75: Timing Simulation For AES-192 after Round 12 | 87 |

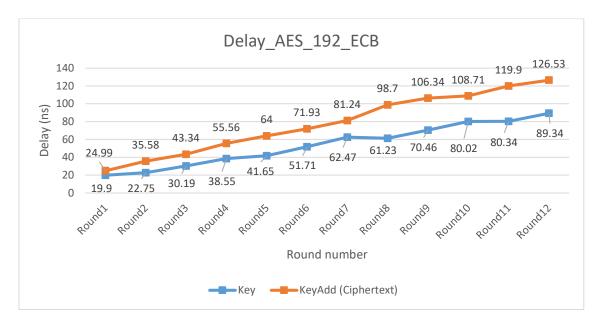

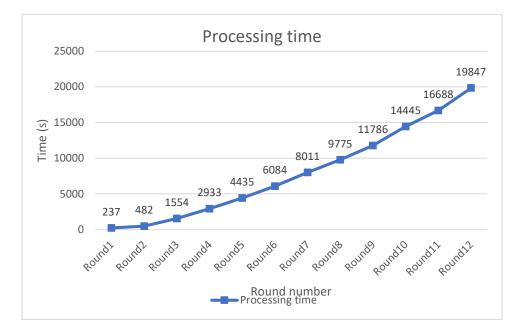

| Figure 76: Delay_AES_192_ECB                            | 89 |

| Figure 77: Processing time_AES_192_ECB                  | 89 |

| Figure 78: Timing Simulation For AES-256 after Round 1  |    |

| Figure 79: Timing Simulation For AES-256 after Round 2  |    |

| Figure 80: Timing Simulation For AES-256 after Round 3  |    |

| Figure 81: Timing Simulation For AES-256 after Round 4  |    |

| Figure 82: Timing Simulation For AES-256 after Round 5  | 94 |

| Figure 83: Timing Simulation For AES-256 after Round 695    |

|-------------------------------------------------------------|

| Figure 84: Timing Simulation For AES-256 after Round 796    |

| Figure 85: Timing Simulation For AES-256 after Round 897    |

| Figure 86: Timing Simulation For AES-256 after Round 998    |

| Figure 87: Timing Simulation For AES-256 after Round 1099   |

| Figure 88: Timing Simulation For AES-256 after Round 11100  |

| Figure 89: Timing Simulation For AES-256 after Round 12101  |

| Figure 90: Timing Simulation For AES-256 after Round 13102  |

| Figure 91: Timing Simulation For AES-256 after Round 14103  |

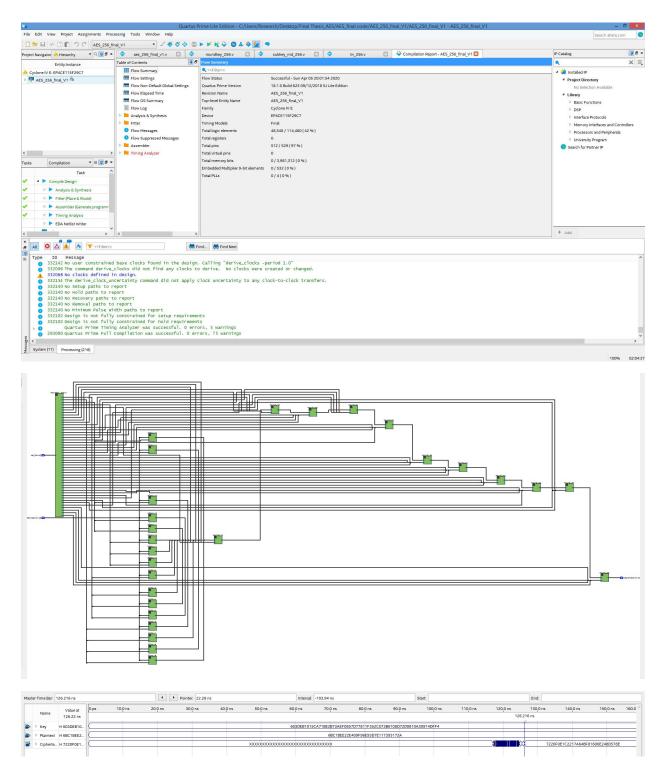

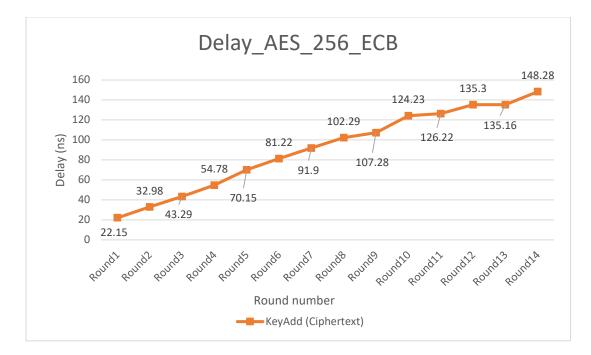

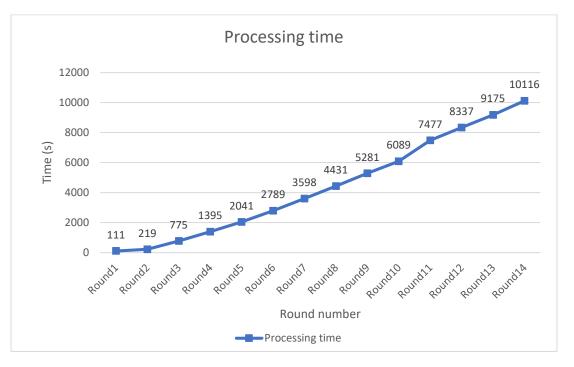

| Figure 92: Delay_AES_256_ECB105                             |

| Figure 93: Processing time_AES_256_ECB105                   |

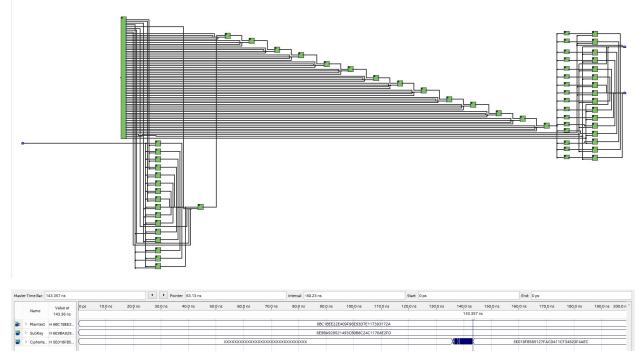

| Figure 94: Timing Simulation For AES-512 after Round 1106   |

| Figure 95: Timing Simulation For AES-512 after Round 2107   |

| Figure 96: Timing Simulation For AES-512 after Round 3108   |

| Figure 97: Timing Simulation For AES-512 after Round 4109   |

| Figure 98: Timing Simulation For AES-512 after Round 5110   |

| Figure 99: Timing Simulation For AES-512 after Round 6111   |

| Figure 100: Timing Simulation For AES-512 after Round 7112  |

| Figure 101: Timing Simulation For AES-512 after Round 8113  |

| Figure 102: Timing Simulation For AES-512 after Round 9114  |

| Figure 103: Timing Simulation For AES-512 after Round 10115 |

| Figure 104: Timing Simulation For AES-512 after Round 11 | 116 |

|----------------------------------------------------------|-----|

| Figure 105: Timing Simulation For AES-512 after Round 12 | 117 |

| Figure 106: Timing Simulation For AES-512 after Round 13 | 118 |

| Figure 107: Timing Simulation For AES-512 after Round 14 | 119 |

| Figure 108: Timing Simulation For AES-512 after Round 15 | 120 |

| Figure 109: Timing Simulation For AES-512 after Round 16 | 121 |

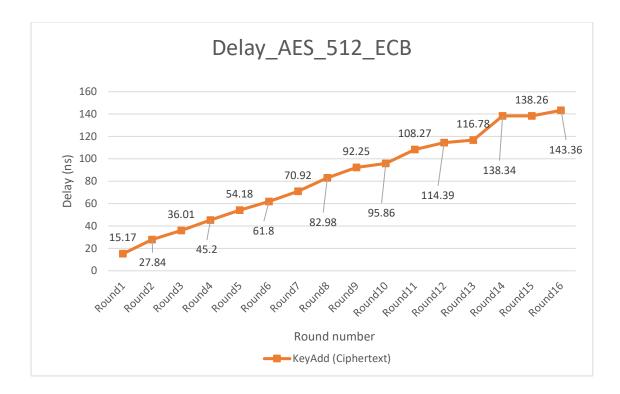

| Figure 110: Delay_AES_512_ECB                            |     |

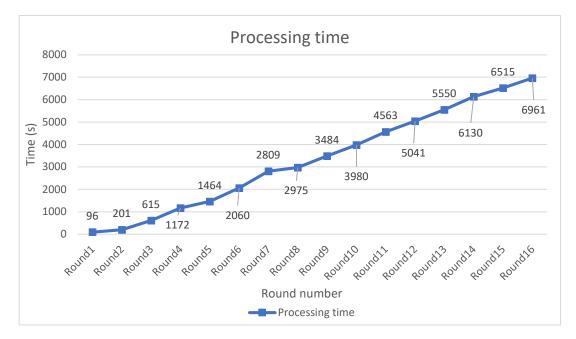

| Figure 111: Processing time_AES_512_ECB                  | 123 |

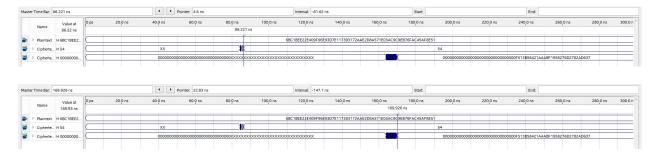

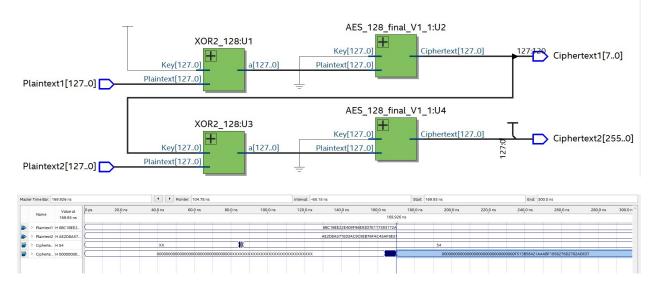

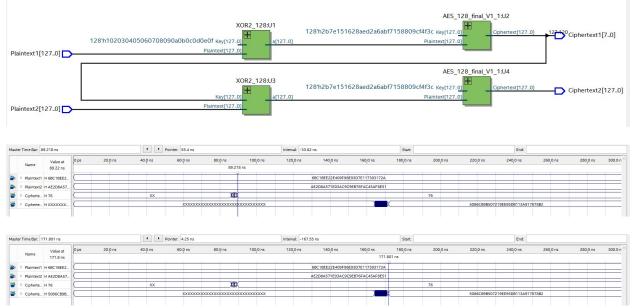

| Figure 112: Timing Simulation For AES-128 in CBC Mode    | 124 |

| Figure 113: Timing Simulation For AES-128_1 in CBC Mode  | 125 |

| Figure 114: Timing Simulation For AES-128_2 in CBC Mode  | 126 |

| Figure 115: Timing Simulation For AES-128_3 in CBC Mode  | 127 |

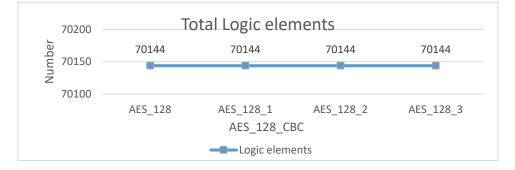

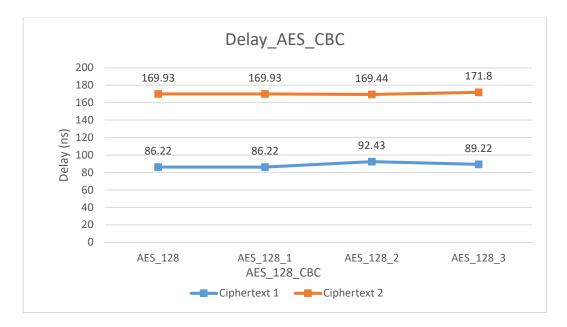

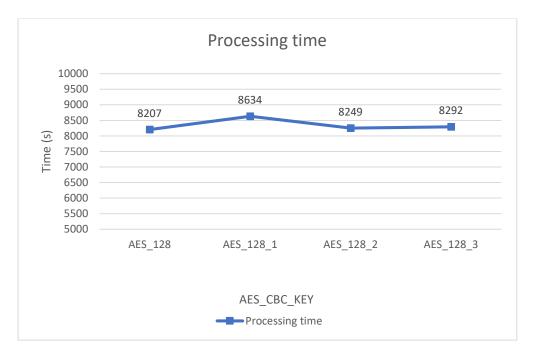

| Figure 116: Total Logic elements_AES_128_CBC             | 128 |

| Figure 117: Delay_AES_128_CBC                            | 129 |

| Figure 118: Processing time_AES_128_CBC                  |     |

| Figure 119: Timing Simulation For AES-192 in CBC Mode    | 130 |

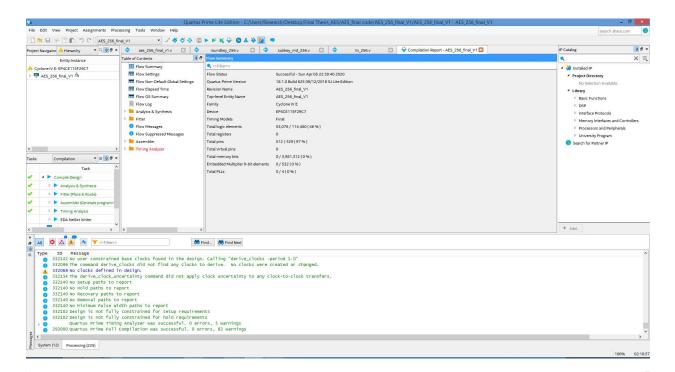

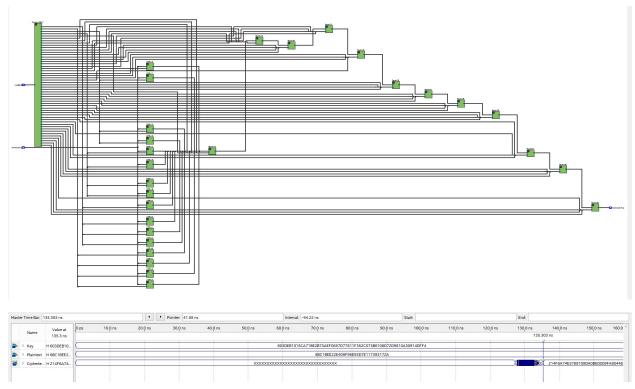

| Figure 120: Timing Simulation For AES-256 in CBC Mode    | 131 |

| Figure 121: Timing Simulation For AES-512 in CBC Mode    | 132 |

| Figure 122: Delay_AES_ECB_KEY                            | 134 |

| Figure 123: Total Logic Elements_AES_ECB_KEY             | 136 |

| Figure 124: Processing time_AES_ECB_KEY                  | 138 |

| Figure 125: Delay_AES_CBC_KEY                | 140 |

|----------------------------------------------|-----|

| Figure 126: Total Logic Elements_AES_CBC_KEY | 140 |

| Figure 127: Total Logic Elements_AES_CBC_KEY | 141 |

# CHAPTER I INTRODUCTION

With today's development and expansion of networks and internet-connected devices, information security is an issue of increasing concern. Cryptography plays a key role in information security by providing confidentiality when transmitting data. It prevents unauthorized access so that data is not disturbed. With the emergence and rapid growth of cloud computing, current encryption technologies are often threatened making it important to study the characteristics of existing algorithms to match this advancement. Confidentiality is one of the focuses in network security for digital communication systems, where large data blocks go through a cryptographic algorithm with a cipher key that increases the security and complexity of the output ciphertext. For the past several years, multiple security algorithms have been developed as standard to be utilized in the data encryption process, such as the Data Encryption Standard (DES), Triple Data Encryption Standard (3DES), and the current one, designated by the U.S. National Institute of Standards and Technology (NIST), the Advanced Encryption Standard (AES).

AES, also known as Rijndael algorithm, is a symmetric encryption algorithm that has a minimum input data block size of 128-bits which undergo a series of permutations, substitutions, and digital logic operations over several rounds. Encryption algorithms are always improving on ciphertext complexity, required hardware storage allocation, and execution time. Field Programmable Gate Arrays (FPGA's) are a hardware alternative for encryption algorithm

1

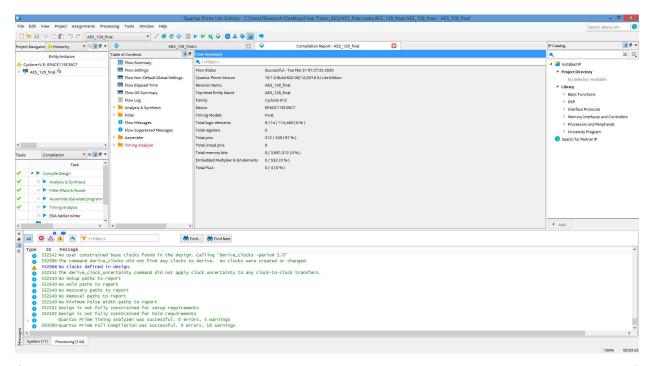

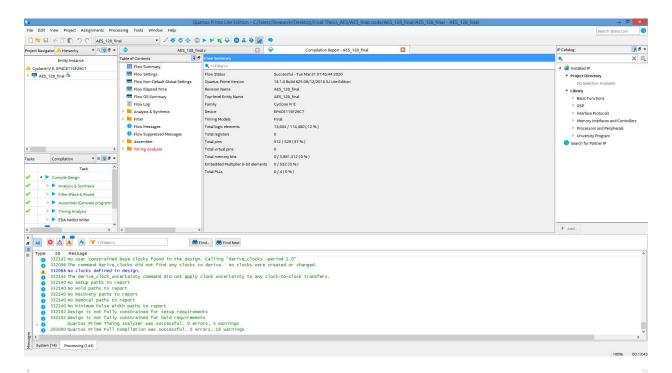

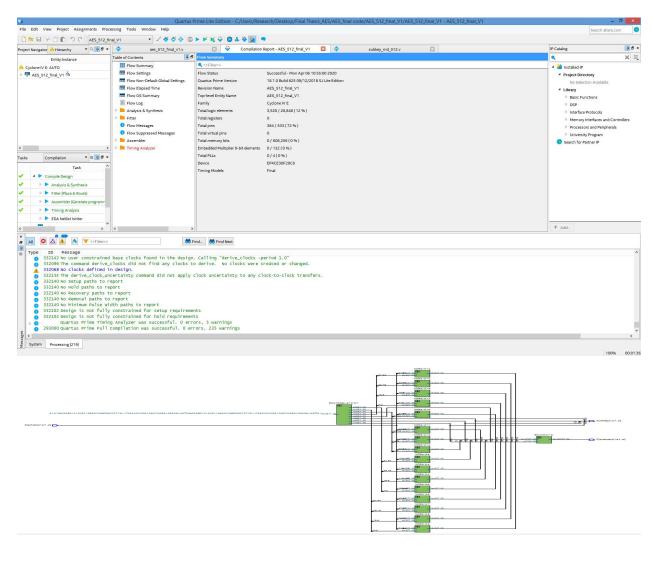

implementation because, although the logic units in it are fixed, the functions and interconnections between them are based on the user's design which allow for improvement in performance and speed. The research presented in this thesis focuses on improving performance by analyzing the AES algorithm for efficient implementations, on an Altera Cyclone IV FPGA using the Intel Quartus II software and Verilog Hardware Description Language.

#### **1.1 Problem Statement**

With the emergence of high-performance cloud computing and increase in traditional businesses such as shopping and education moving completely on Internet during these days of pandemic, it is important to keep confidential data safe. Due to huge volume of data being exchanged over Internet, it is even more important for the security encryption schemes to efficiently utilize hardware implementations to perform at much higher speeds to provide fast, efficient, and secure data transmissions. There have been several AES hardware implementations related work done in literature [8-44]. Many literatures have proposed Mix Column Computation and S-box hardware lookup table implementations however none of the prior work utilized implementation on newer Intel's Cyclone IV FPGA involving parallelism and pipelining together. In this thesis, we hypothesize that various AES components can be made faster by utilizing parallelism and pipelining in their computation via FPGA implementations thus improving the overall speed of AES encryption process.

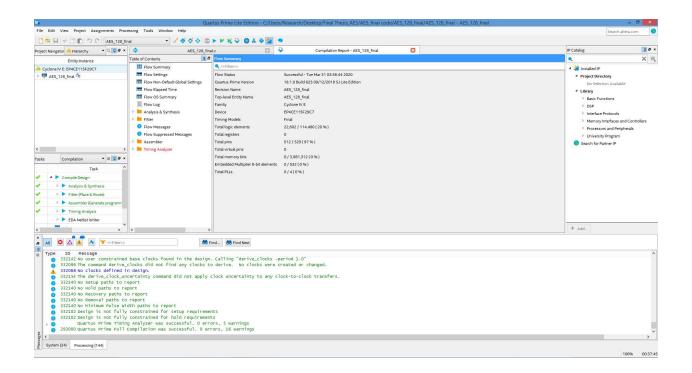

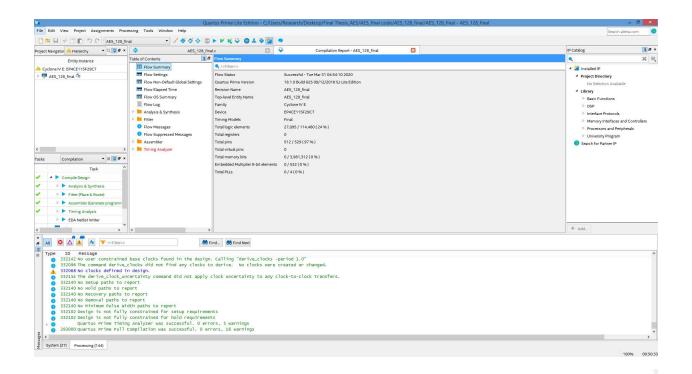

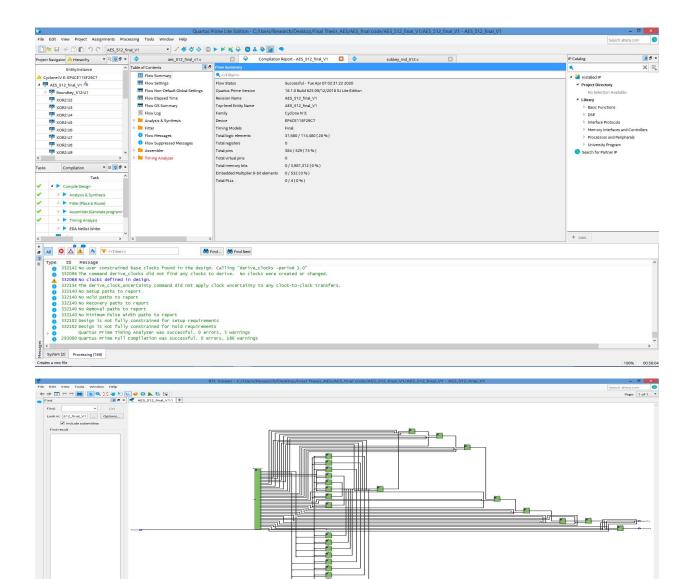

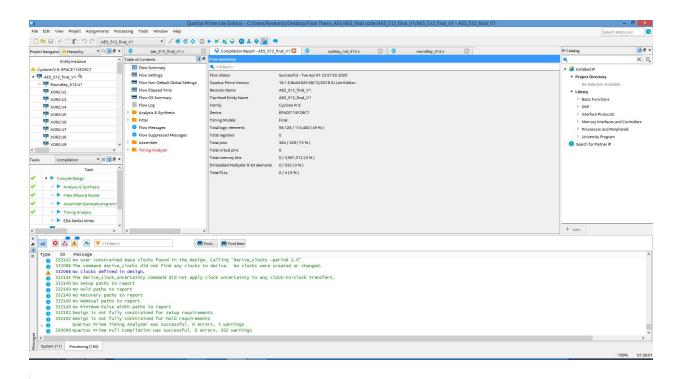

Some of our published work showed processing speed improvement for components such as AES Mix Columns module [28] and S-box module [45] where parallelism and pipelining in the computation were utilized to improve overall AES performance of those functions. In this thesis, we considered the FPGA implementation for the entire AES algorithm based on improvement on these components. This thesis also presents high speed, fully pipelined FPGA implementation of AES Encryption in two different operation modes. Furthermore, we also evaluated the overall performance for the four variants of AES such as AES-128, AES-192, AES-256, and AES-512. The work in this thesis aims to speed up overall AES encryption by reducing processing delays and optimize silicon area for such implementations. Comparisons are conducted on both a theoretical basis and through timing simulations on the Intel Quartus II software to reveal the implication of increased complexity on the hardware performance of AES. Our work in this thesis involves Writing Verilog Code for design and verification of digital circuit and Simulating the code on "Quartus II".

### 1.2 Symmetric Encryption Algorithm- AES Algorithm

### 1.2.1 Background

The Advanced Encryption Standard (AES), also known as Rijndael, is an electronic data encryption specification established by the National Institute of Standards and Technology (NIST) in 2001 [1]. AES is a subset of the Rijndael block cipher. Developed by two Belgian cryptographers Vincent Rijmen and Joan Daemen, they submitted a proposal to NIST during the AES selection process. Rijndael is a series of passwords and block size passwords.

In the United States, AES was announced by the National Institute of Standards and Technology on November 26, 2001 as the US FIPS PUB 197 (FIPS 197) and is now used worldwide. It replaces the Data Encryption Standard (DES) released in 1977. The algorithm described by AES is a symmetric key algorithm, meaning that the same key is used to encrypt and decrypt data.

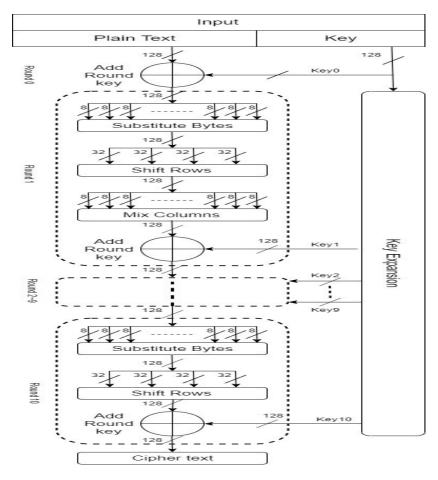

Figure.1 shows the overall structure of the AES encryption process. The cipher takes a plaintext block size of 128 bits, or 16 bytes. The key length can be 16, 24, 32, or 64 bytes (128, 192, 256, or 512 bits). The algorithm is referred to as AES-128, AES-192, AES-256, or AES-512, depending on the key length. The input to the encryption and decryption algorithms is a single 128-bit block.

Figure 1: AES-128 Structure

The cipher consists of rounds, where the number of rounds depends on the key length: 10 rounds for a 16-byte key, 12 rounds for a 24-byte key, 14 rounds for a 32-byte key, 16 rounds for a 64-byte key (Table 1).

| Key Size<br>(words/bytes/bits)             | 4/16/128 | 6/24/192 | 8/32/256 | 16/64/256 |

|--------------------------------------------|----------|----------|----------|-----------|

| Plaintext Block Size<br>(words/bytes/bits) | 4/16/128 | 4/16/128 | 4/16/128 | 4/16/128  |

| Number of Rounds                           | 10       | 12       | 14       | 16        |

| Round Key Size<br>(words/bytes/bits)       | 4/16/128 | 4/16/128 | 4/16/128 | 4/16/128  |

| Expanded Key Size<br>(words/bytes)         | 44/176   | 52/208   | 60/240   | 68/272    |

Table 1: AES Parameters

The overall data computation [1], [2] to obtain Rijndael cipher consists of

- 1. An initial "Add Round key' step to add obscurity

- 2. 9/11//13/15 rounds of 4 steps to adds confusion, diffusion, non-linearity

- Substitute bytes: Uses an S-box to perform a byte-by-byte substitution of the block

- Shift-Rows: A simple permutation

- Mix-Columns: A substitution that makes use of arithmetic over GF (2<sup>8</sup>)

- Add-Round-Key: A simple bitwise XOR of the current block with a portion of the expanded key

- A Final 10th/12th/14<sup>th</sup>/16<sup>th</sup> step of Substitute bytes, ShiftRows, and AddRoundKey to add obscurity

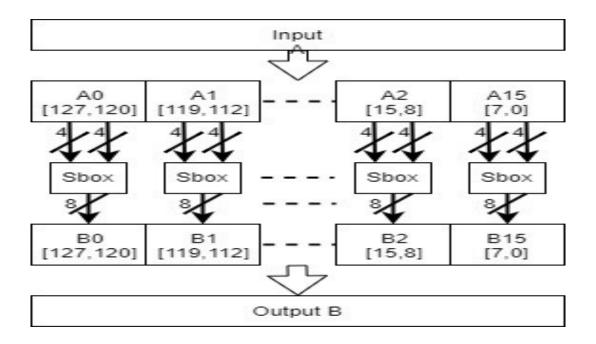

### **1.2.2 Substitute bytes**

The forward substitute byte transformation, called SubBytes, is a simple table lookup (Figure 2). AES defines a matrix of byte values, called an S-box (Table 2), that contains a permutation of all possible 256 8-bit values. Each individual byte of State is mapped into a new byte in the following way: The leftmost 4 bits of the byte are used as a row value and the rightmost 4 bits are used as a column value. These row and column values serve as indexes into the S-box to select a unique 8-bit output value.

In this layer, each byte in the state will be substituted by values obtained from substitution boxes. This is done to achieve more security according to diffusion-confusion Shannon's principles for cryptographic algorithms design.

Figure2: Substitute bytes

|   | 0  | 1  | 2  | 3  | 4  | 5          | 6  | 7  | 8  | 9          | A  | В  | С          | D          | Е  | F          |

|---|----|----|----|----|----|------------|----|----|----|------------|----|----|------------|------------|----|------------|

| 0 | 63 | 7C | 77 | 7B | F2 | 6B         | 6F | C5 | 30 | 01         | 67 | 2B | FE         | D7         | AB | 76         |

| 1 | CA | 82 | CO | 7D | FA | 59         | 47 | FO | AD | D4         | A2 | AF | 9C         | A4         | 72 | 00         |

| 2 | B7 | FD | 93 | 26 | 36 | Ŧ          | F7 | CC | 34 | A5         | ЕЪ | F1 | 71         | D8         | 31 | 15         |

| 3 | 04 | C7 | 23 | C3 | 18 | 96         | 05 | 9A | 07 | 12         | 80 | E2 | EB         | 27         | B2 | 75         |

| 4 | 09 | 83 | 2C | 1A | 1B | 6E         | 5A | A0 | 52 | 3B         | D6 | B3 | 29         | E3         | 2F | 84         |

| 5 | 53 | Dl | 00 | ED | 20 | FC         | B1 | 5B | 6A | CB         | BE | 39 | <b>4</b> A | <b>4</b> C | 58 | Œ          |

| 6 | D0 | EF | AA | FB | 43 | <b>4</b> D | 33 | 85 | 45 | <b>F</b> 9 | 02 | 7F | 50         | x          | 9F | <b>A</b> 8 |

| 7 | 51 | A3 | 40 | 8F | 92 | 9D         | 38 | F5 | BC | B6         | DA | 21 | 10         | FF         | F3 | D2         |

| 8 | CD | 0C | 13 | EC | Ŧ  | <b>9</b> 7 | 44 | 17 | C4 | A7         | 7E | 3D | 64         | 5D         | 19 | 73         |

| 9 | 60 | 81 | Æ  | DC | 22 | 2A         | 90 | 88 | 46 | EE         | B8 | 14 | DE         | 5E         | 0B | DB         |

| A | E0 | 32 | 3A | 0A | 49 | 06         | 24 | 5C | Ø  | D3         | AC | 3  | 91         | 95         | E4 | 79         |

| В | E7 | C8 | 37 | 6D | 8D | D5         | 4E | A9 | 6C | 56         | F4 | EA | ଷ          | 7A         | AE | 08         |

| С | BA | 78 | 25 | Æ  | 1C | Aб         | B4 | C6 | E8 | DD         | 74 | 1F | <b>4</b> B | BD         | 8B | 8A         |

| D | 70 | Æ  | B5 | 66 | 48 | 03         | Ю  | 0E | 61 | 35         | 57 | B9 | 86         | Cl         | 1D | 9E         |

| Е | E1 | F8 | 98 | 11 | 69 | D9         | 8E | 94 | 9B | 1E         | 87 | E9 | CE         | 55         | 28 | DF         |

| F | 8C | A1 | 89 | 0D | BF | Вб         | 42 | 68 | 41 | 99         | 2D | 0F | B0         | 54         | BB | 16         |

Table 2: S-Box

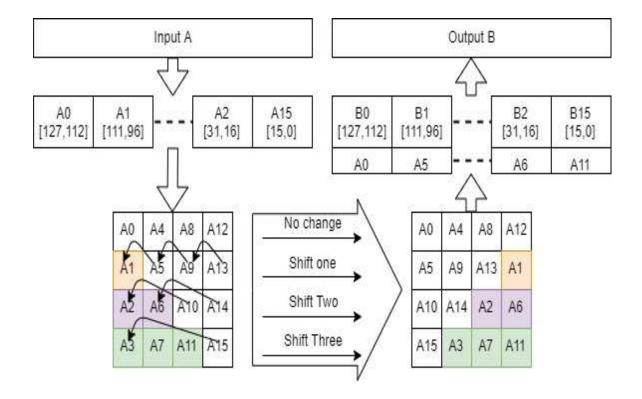

### 1.2.3 Shift Rows

.

The forward shift row transformation, called ShiftRows, is depicted in Figure 3. The first row of State is not altered. For the second row, a 1-byte circular left shift is performed. For the third row, a 2-byte circular left shift is performed. For the fourth row, a 3-byte circular left shift is performed. The following is an example of ShiftRows.

This layer is to provide diffusion for all the state. It contains two sub-layers to ensure the high-degree diffusion after transformation for many rounds.

Figure3: Shift Rows

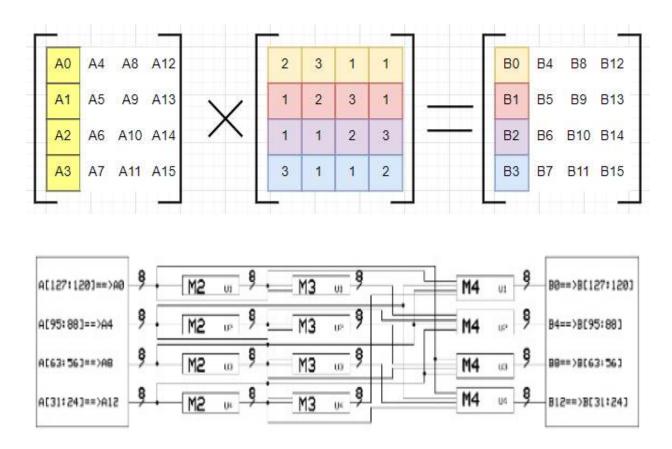

### **1.2.4 MixColumns**

The forward mix column transformation, called MixColumns, operates on each column individually [3]. Each byte of a column is mapped into a new value that is a function of all four bytes in that column. The transformation can be defined by the following matrix multiplication on State (Figure 4).

This layer is to provide diffusion for all the state. It contains two sub-layers to ensure the high-degree diffusion after transformation for many rounds.

Figure4: MixColumns [28]

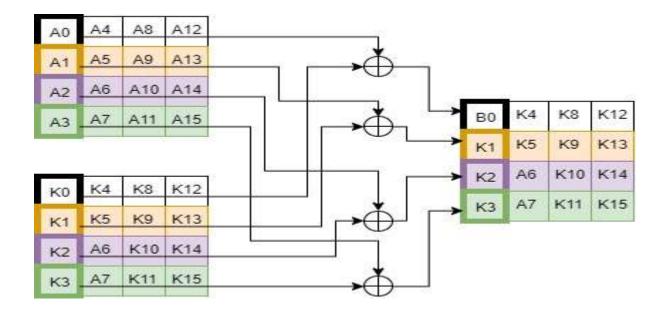

## 1.2.5 AddRoundKey

In the forward add round key transformation, called AddRoundKey, the 128 bits of State are bitwise XORed with the 128 bits of the round key. As shown in Figure 5, the operation is viewed as a columnwise operation between the 4 bytes of a State column and one word of the round key; it can also be viewed as a byte-level operation.

In this layer, the operation is to conduct XOR operation on round key (round key is obtained from the extension of secret key operation) and state. This layer is to establish the relationship between the key and the cipher-text more complicated and to satisfy the confusion principle.

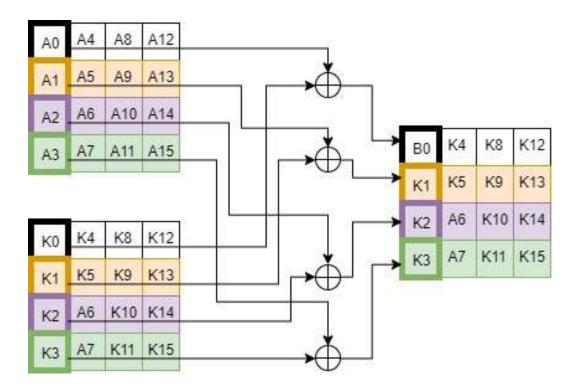

Figure 5: AddRoundKey

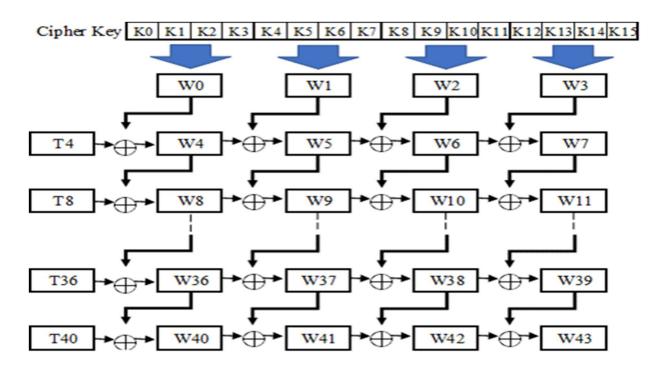

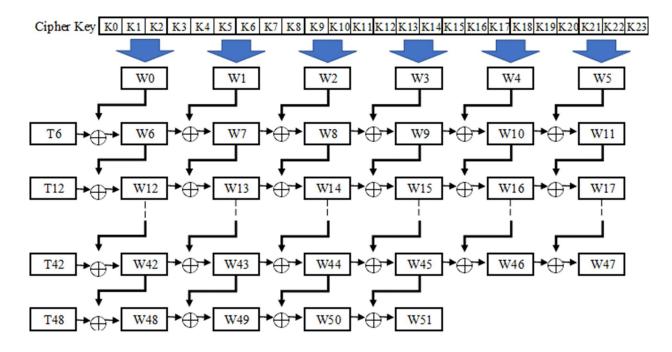

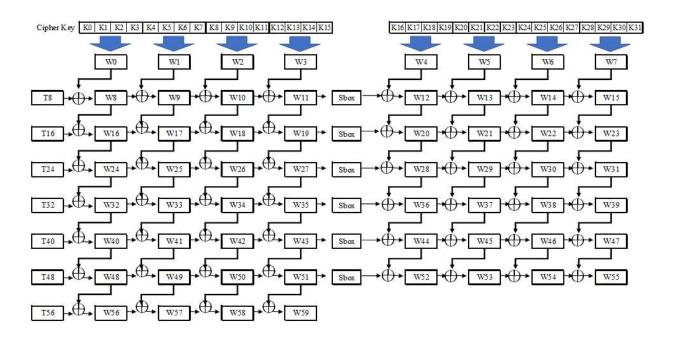

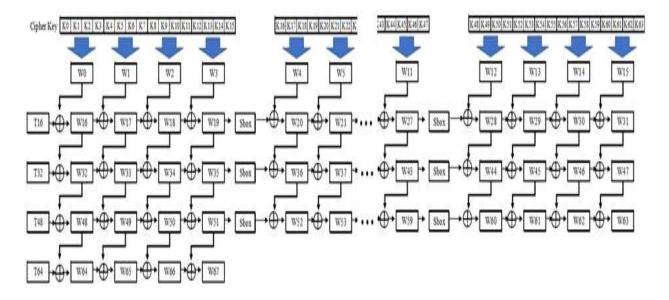

### 1.2.6 Key expansion of AES-128, 192, 256, and 512

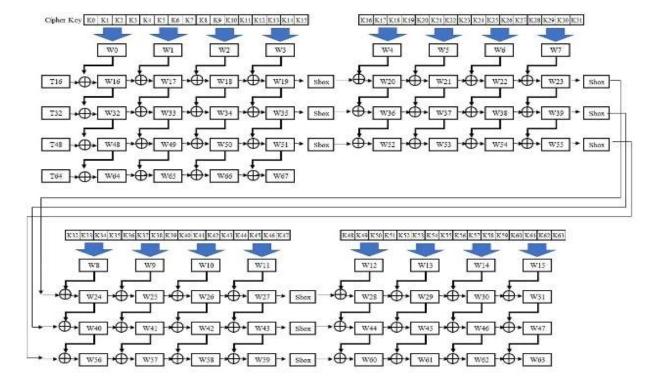

The AES key extension algorithm takes a four-word (16-byte) key as input and produces a linear array of 44/52/60/68 words (176/208/240/272bytes). This is enough to provide a fourcharacter round key for the initial AddRoundKey phase and each field, 10/12/14/16 rounds of password. The key is copied into the first four words of the extended key. The rest of the extended key is filled with four words at a time. Each added word depends on the previous word and the word is returned in four positions. In three of the four cases, a simple XOR was used. For words in the w array whose position is a multiple of 4/6/8/10, a more complex function is used. Figure 6,7,8,9 illustrate the generation of the extended key, using the symbol " $\oplus$ "to represent the complex function.

Figure 6: AES-128 Key Expansion

Figure7: AES-192 Key Expansion

Figure 8: AES-256 Key Expansion

Figure 9: AES-512 Key Expansion

# **1.3 Block Cipher Modes of Operation**

# 1.3.1 Background

A mode of operation is a technique for enhancing the effect of a cryptographic algorithm or adapting the algorithm for an application such as applying a block cipher to a sequence of data blocks or a data stream. It can be used with any symmetric block cipher algorithm such as DES, 3DES or AES. NIST originally defined four modes of operation, as part of FIPS 81, through which block ciphers can be applied to a variety of applications. However, with newer applications the NIST extended the list of federal recommended modes to five in Special Publication 800-38A.

### **1.3.2 Modes of Operation**

In this section, we will discuss the different modes of operation of a block cipher. These are procedural rules for a generic block cipher. Interestingly, the different modes result in different properties being achieved which add to the security of the underlying block cipher. A block cipher processes the data blocks of fixed size. Usually, the size of a message is larger than the block size. Hence, the long message is divided into a series of sequential message blocks, and the cipher operates on these blocks one at a time.

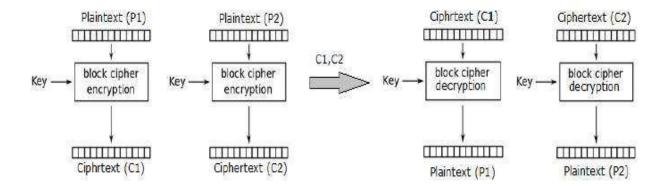

### 1.3.2.1 Electronic Codebook (ECB)

This mode is a most straightforward way of processing a series of sequentially listed message blocks. The user takes the first block of plaintext and encrypts it with the key to produce the first block of ciphertext. He then takes the second block of plaintext and follows the same process with same key and so on so forth. The ECB mode is deterministic, that is, if plaintext block p1, p2..., pM are encrypted twice under the same key, the output ciphertext blocks will be the same.

In fact, for a given key technically we can create a codebook of ciphertexts for all possible plaintext blocks. Encryption would then entail only looking up for required plaintext and select the corresponding ciphertext. Thus, the operation is analogous to the assignment of code words in a codebook, and hence gets an official name – electronic codebook mode of operation (ECB). It is illustrated as follows –

14

Figure 10: Electronic codebook mode of operation (ECB) [2]

In reality, any application data usually have partial information which can be guessed. For example, the range of salary can be guessed. A ciphertext from ECB can allow an attacker to guess the plaintext by trial-and-error if the plaintext message is within predictable.

For example, if a ciphertext from the ECB mode is known to encrypt a salary figure, then a small number of trials will allow an attacker to recover the figure. In general, we do not wish to use a deterministic cipher, and hence the ECB mode should not be used in most applications.

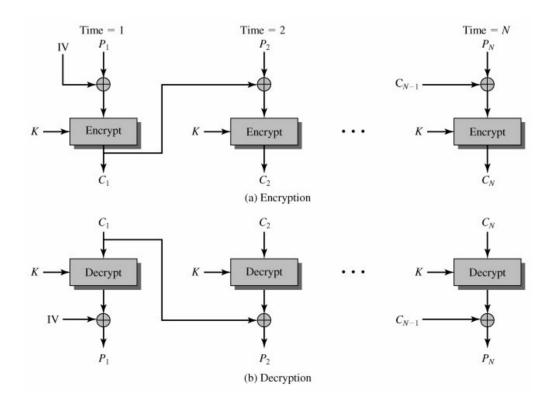

# **1.3.2.2** Cipher Block Chaining (CBC)

CBC mode of operation provides message dependence for generating ciphertext and makes the system non-deterministic. The operation of CBC mode is depicted in the following illustration. The steps are as follows –

- Load the n-bit Initialization Vector (IV) in the top register.

- XOR the n-bit plaintext block with data value in top register.

- Encrypt the result of XOR operation with underlying block cipher with key K.

- Feed ciphertext block into top register and continue the operation till all plaintext blocks are processed.

- For decryption, IV data is XORed with first ciphertext block decrypted. The first ciphertext block is also fed into to register replacing IV for decrypting next ciphertext block.

Figure 11: Cipher block chaining mode of operation (CBC) [2]

In CBC mode, the current plaintext block is added to the previous ciphertext block, and then the result is encrypted with the key. Decryption is thus the reverse process, which involves decrypting the current ciphertext and then adding the previous ciphertext block to the result. Advantage of CBC over ECB is that changing IV results in different ciphertext for identical message. On the drawback side, the error in transmission gets propagated to few further blocks during decryption due to chaining effect. It is worth mentioning that CBC mode forms the basis for a well-known data origin authentication mechanism. Thus, it has an advantage for those applications that require both symmetric encryption and data origin authentication.

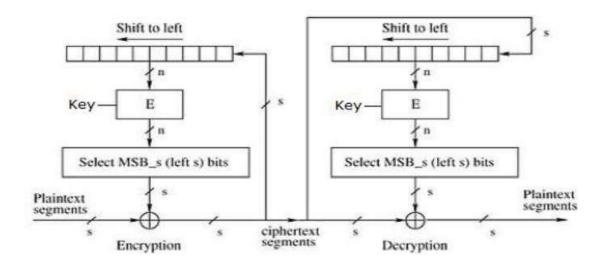

### **1.3.2.3** Cipher Feedback Mode (CFB)

In this mode, each ciphertext block gets 'fed back' into the encryption process in order to encrypt the next plaintext block. The operation of CFB mode is depicted in the following illustration. For example, in the present system, a message block has a size 's' bits where 1 < s <n. The CFB mode requires an initialization vector (IV) as the initial random n-bit input block. The IV need not be secret. Steps of operation are –

- Load the IV in the top register.

- Encrypt the data value in top register with underlying block cipher with key K.

- Take only 's' number of most significant bits (left bits) of output of encryption process and XOR them with 's' bit plaintext message block to generate ciphertext block.

- Feed ciphertext block into top register by shifting already present data to the left and continue the operation till all plaintext blocks are processed.

- Essentially, the previous ciphertext block is encrypted with the key, and then the result is XORed to the current plaintext block.

• Similar steps are followed for decryption. Pre-decided IV is initially loaded at the start of decryption.

Figure 12: Cipher feedback mode of operation (CFB) [2]

CFB mode differs significantly from ECB mode, the ciphertext corresponding to a given plaintext block depends not just on that plaintext block and the key, but also on the previous ciphertext block. In other words, the ciphertext block is dependent of message. CFB has a very strange feature. In this mode, user decrypts the ciphertext using only the encryption process of the block cipher. The decryption algorithm of the underlying block cipher is never used. Apparently, CFB mode is converting a block cipher into a type of stream cipher. The encryption algorithm is used as a key-stream generator to produce keystream that is placed in the bottom register. This key stream is then XORed with the plaintext as in case of stream cipher. By converting a block cipher into a stream cipher, CFB mode provides some of the advantageous properties of a stream cipher while retaining the advantageous properties of a block cipher. On the flip side, the error of transmission gets propagated due to changing of blocks.

# 1.3.2.4 Output Feedback (OFB) Mode

It involves feeding the successive output blocks from the underlying block cipher back to it. These feedback blocks provide string of bits to feed the encryption algorithm which act as the key-stream generator as in case of CFB mode. The key stream generated is XOR-ed with the plaintext blocks. The OFB mode requires an IV as the initial random n-bit input block. The IV need not be secret.

Figure 13: Output feedback mode of operation (OFB) [2]

### 1.3.2.5 Counter (CTR) Mode

It can be considered as a counter-based version of CFB mode without the feedback. In this mode, both the sender and receiver need to access to a reliable counter, which computes a new shared value each time a ciphertext block is exchanged. This shared counter is not necessarily a secret value, but challenge is that both sides must keep the counter synchronized. Both encryption and decryption in CTR mode are depicted in the following illustration. Steps in operation are –

- Load the initial counter value in the top register is the same for both the sender and the receiver. It plays the same role as the IV in CFB (and CBC) mode.

- Encrypt the contents of the counter with the key and place the result in the bottom register.

- Take the first plaintext block P1 and XOR this to the contents of the bottom register. The result of this is C1. Send C1 to the receiver and update the counter. The counter update replaces the ciphertext feedback in CFB mode.

- Continue in this manner until the last plaintext block has been encrypted.

- The decryption is the reverse process. The ciphertext block is XORed with the output of encrypted contents of counter value. After decryption of each ciphertext block counter is updated as in case of encryption.

Figure 14: Counter mode of operation (CTR) [2]

It does not have message dependency and hence a ciphertext block does not depend on the previous plaintext blocks. Like CFB mode, CTR mode does not involve the decryption process of the block cipher. This is because the CTR mode is really using the block cipher to generate a keystream, which is encrypted using the XOR function. In other words, CTR mode also converts a block cipher to a stream cipher. The serious disadvantage of CTR mode is that it requires a synchronous counter at sender and receiver. Loss of synchronization leads to incorrect recovery of plaintext. However, CTR mode has almost all advantages of CFB mode. In addition, it does not propagate error of transmission at all.

### 1.4 Hardware and Software Design Assessment

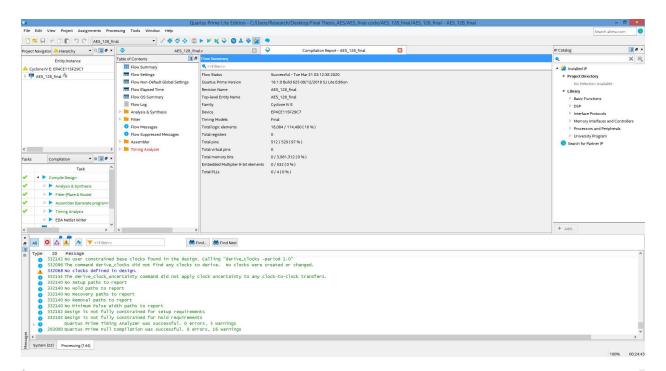

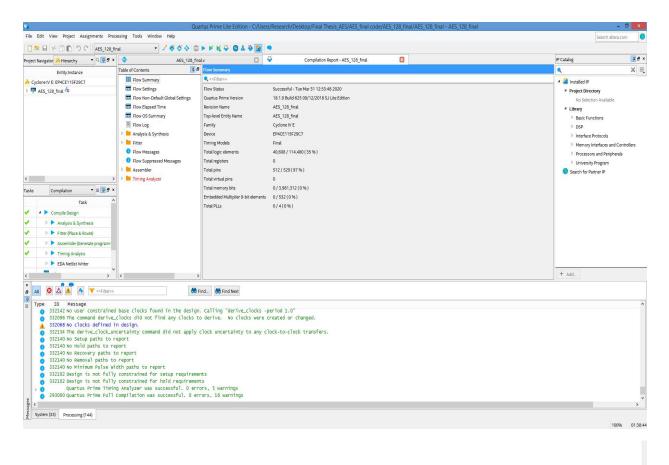

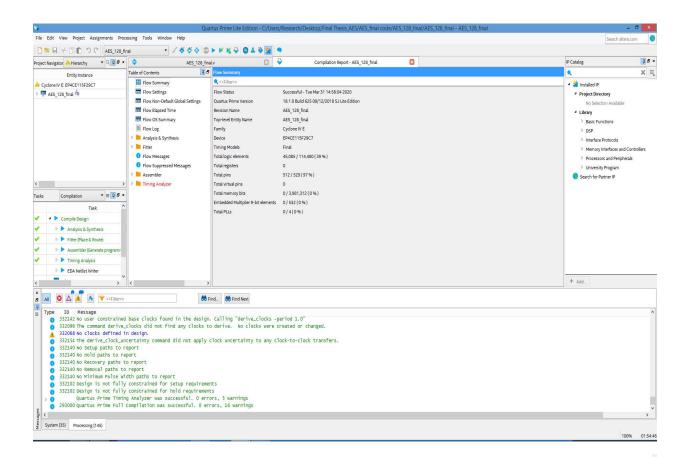

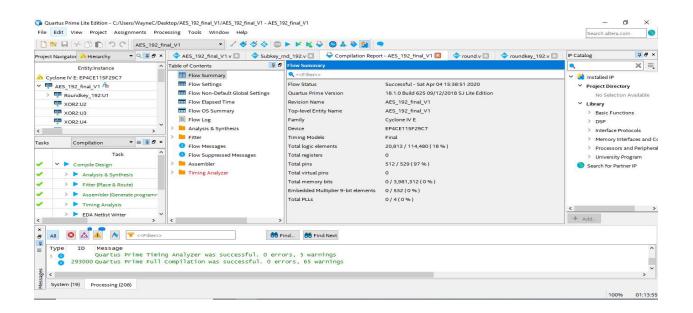

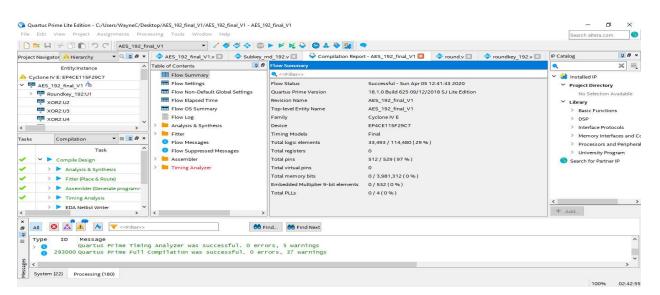

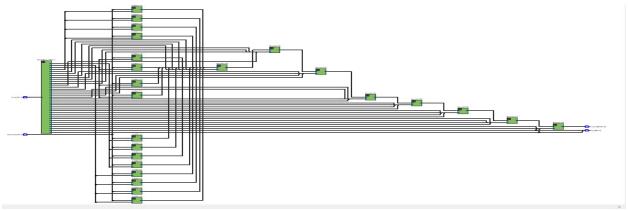

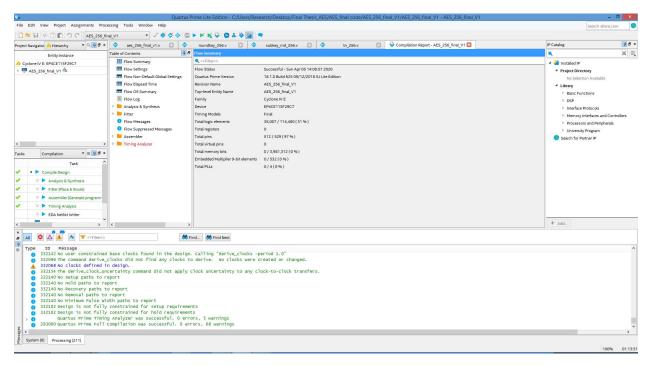

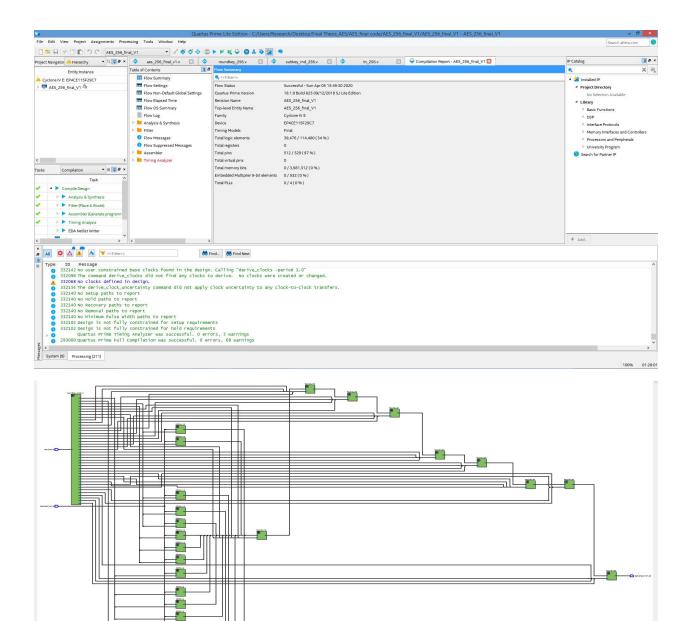

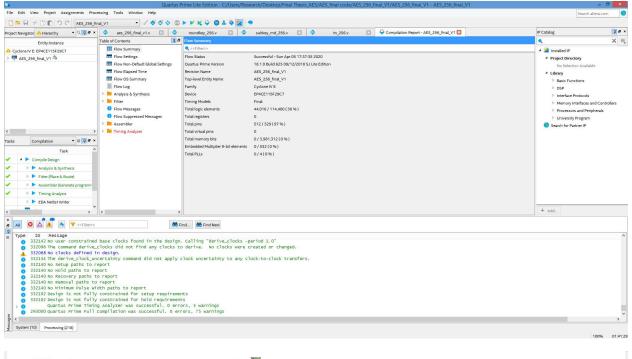

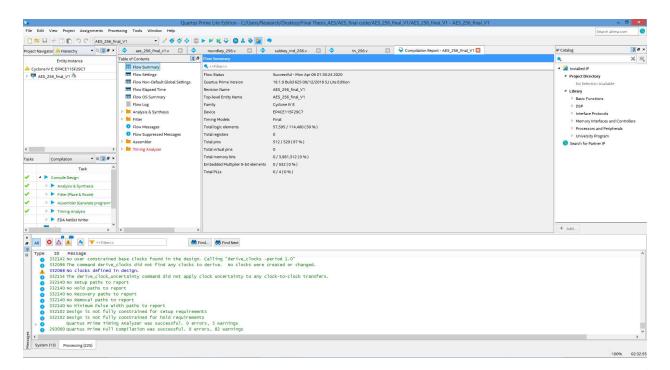

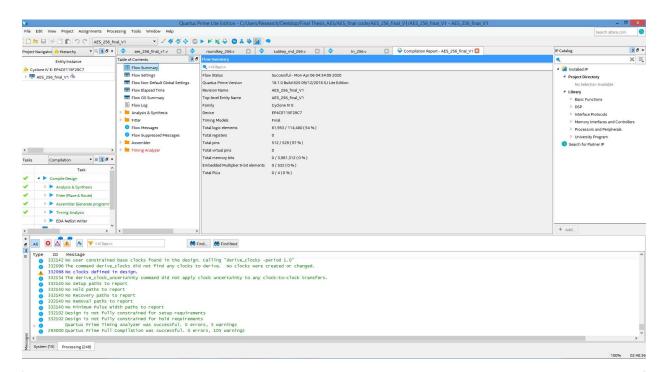

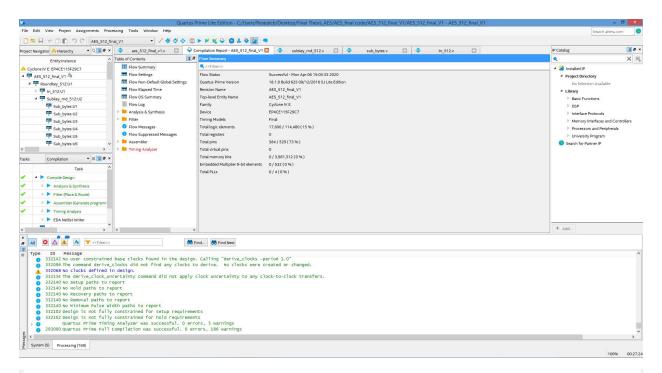

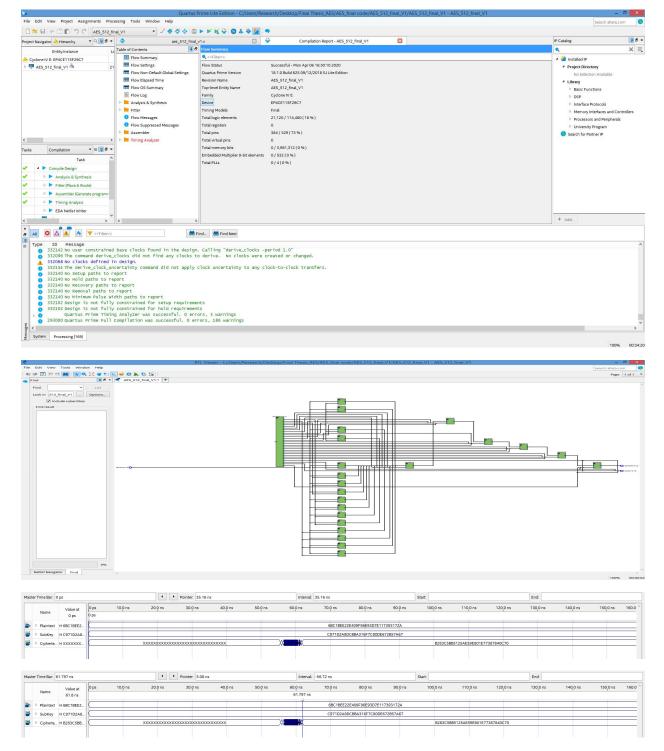

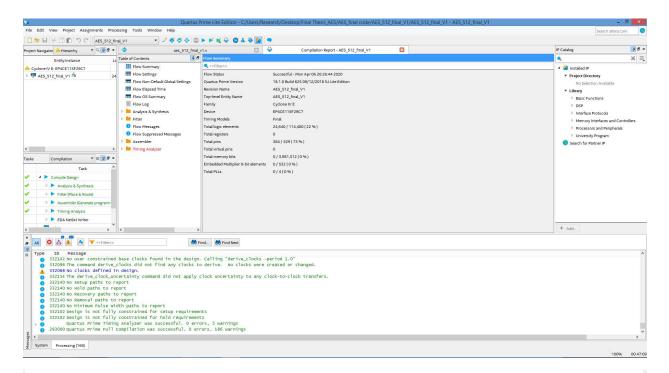

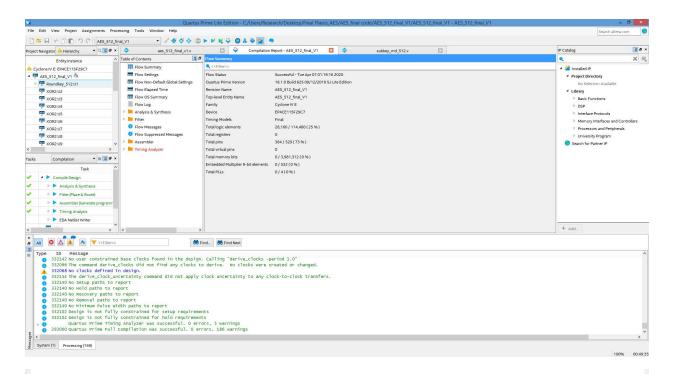

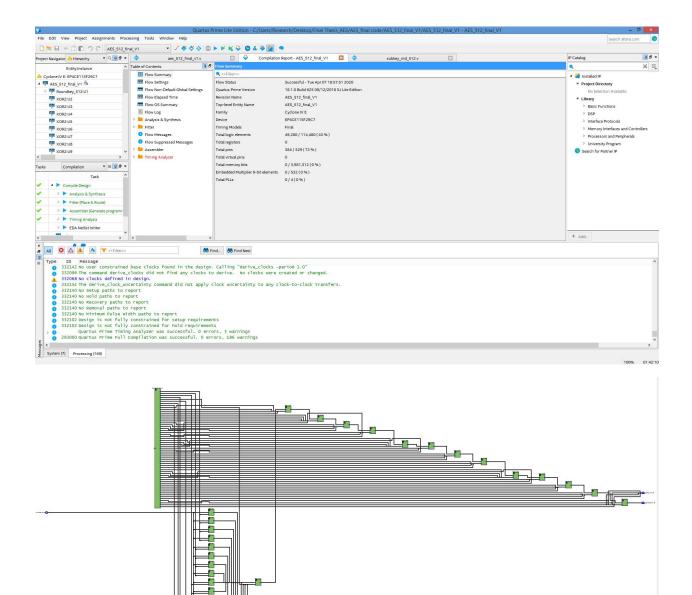

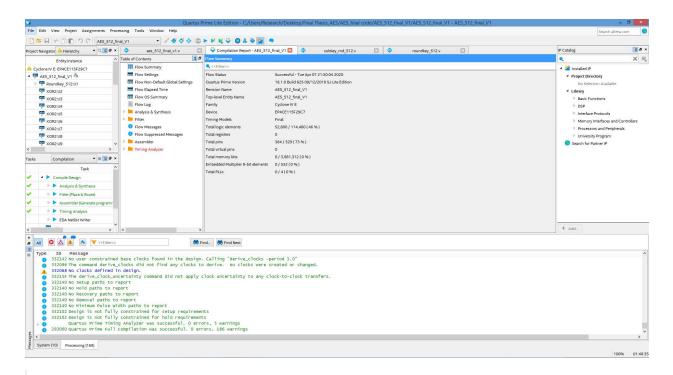

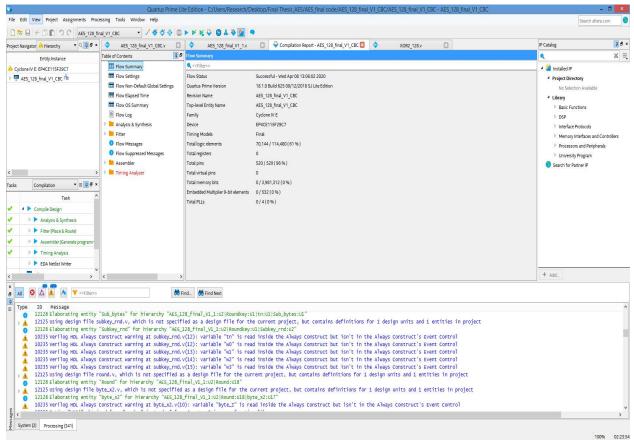

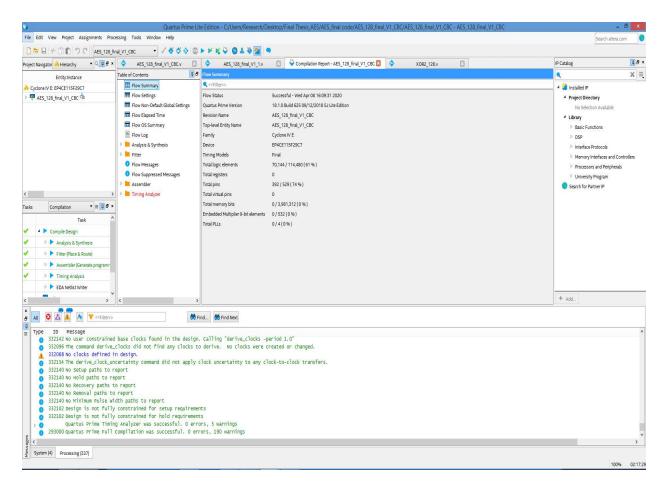

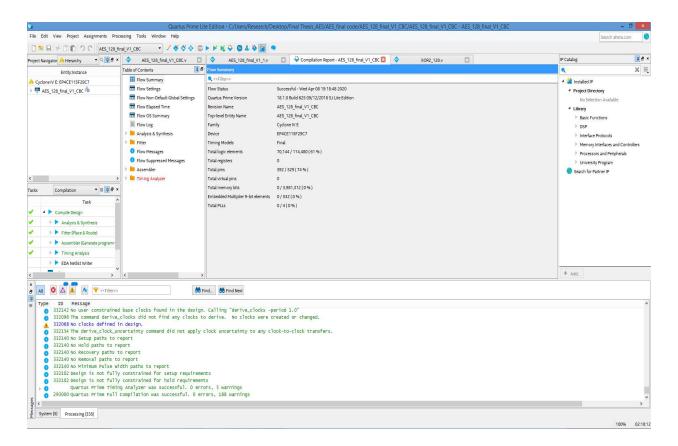

We use the EDA tools available on the Altera website to evaluate our designs [4-7]. These tools, the Quartus II Web Edition and the Altera University Program Simulator, allow code to be built, compiled, synthesized, simulated, and finally programmed into DE2 hardware. In this work, we use Altera's Cyclone IV DE2-115 board EP4CE115F29 platform as shown in Figure 15. Cyclone IV technology was released in 2017. The model EP4CE115F29C7 has a density of 114,480 LE and it contains an internal 50 MHz clock. The development board is available on the Terasic website. The basic information about the computer we run the experiments is shown as Figure 16.

Figure 15: Altera Cyclone IV 4CE115 FPGA Device [7]

Windows edition -

Windows 8.1 Pro

© 2013 Microsoft Corporation. All rights reserved.

Get more features with a new edition of Windows

System

| Processor:              | Intel(R) Core(TM) i5-2400S CPU @ 2.50GHz 2.50 GHz |

|-------------------------|---------------------------------------------------|

| Installed memory (RAM): | 8.00 GB                                           |

| System type:            | 64-bit Operating System, x64-based processor      |

Figure 16: Basic information about the computer

## **1.5 Thesis Outline**

This thesis is organized as follows. The first chapter discusses the introduction of cryptography, a brief overview of the symmetric encryption algorithm- AES, a brief overview of block cipher mode of operation, and problem statement. Chapter II discusses the Mix Column modules in detail and how to improve the computation by parallelism and pipelining. Chapter III focuses the S-box modules in detail how to improve the computation by parallelism and pipelining. Chapter IV discusses the performance comparison of AES variants which is the Key Expansion in detail. Chapter V gives the experimental results and simulation analysis of AES scheme and its four variants including AES-128, AES-192, AES-256 and new AES-512 with different modes of operation, on the FPGA platform. Finally, Chapter VI provides conclusion and the future work.

### CHAPTER II

# HARDWARE IMPLEMENTATION OF IMPROVED MIX COLUMN COMPUTATION OF CRYPTOGRAPHIC AES

With today's development and expansion of networks and internet-connected devices, information security is an issue of increasing concern. Confidentiality is one of the focuses in network security for digital communication systems, where large data blocks go through a cryptographic algorithm with a cipher key that increases the security and complexity of the output ciphertext. AES is a symmetric encryption algorithm that has a minimum input data block size of 128-bits which undergo a series of permutations, substitutions, and digital logic operations over several rounds. Encryption algorithms are always improving on ciphertext complexity, required hardware storage allocation, and execution time. Field Programmable Gate Arrays (FPGA's) are a hardware alternative for encryption algorithm implementation because, although the logic units in it are fixed, the functions and interconnections between them are based on the user's design which allow for improvement. The research presented focuses on the development and analysis of an efficient AES-128 Mix Columns algorithm implementation, utilized in the data block encryption rounds, on an Altera Cyclone IV FPGA using the Intel Quartus II software and Verilog Hardware Description Language.

#### 2.1 Rijndael Mix Column Computation

Intensive computation of AES takes place in the Rijndael Mix Column segment. The Mix Column transformation operates on each column of the 4-byte by 4-byte matrix formed from the input 128-bit data block. Each byte of the column is mapped into a new value that is a function of all four bytes in that column. The implementation of Mix Columns is based on the mathematical analysis in the Galois field, GF ( $2^8$ ). For the AES algorithm this irreducible polynomial is:

$$m(x) = x^8 + x^4 + x^3 + x + 1$$

(Equation 2.1.1)

The columns of the matrix are multiplied by modulo  $x^4 + 1$  with a fixed polynomial c (x), given by:

$$c(x) = [03]x^3 + [01]x^2 + [01]x + [02]$$

(Equation 2.1.2)

This polynomial is coprime to  $x^4 + 1$  and therefore invertible. Only the multiplication module and the 32-bit XOR module of each processing unit (one column) are needed for the design because the elements of the multiplication and addition in the Galois field are commutative and associative. In Figure 17 shows a Mix Columns computation example. With this approach, the function of Mix Columns can be achieved.

| For example:                                                                 |

|------------------------------------------------------------------------------|

| 1. {02.BF}                                                                   |

| {BF} . {02} = 1011 1111 << 1                                                 |

| =0111 1110 🕀 0001 1011                                                       |

| =0110 0101                                                                   |

| 2. {03.5D}                                                                   |

| {5D} . {03} = {0101 1101 . 02} ⊕ { 0101 1101}                                |

| = 1011 1010 🕀 0101 1101                                                      |

| = 1110 0111                                                                  |

| ∴ r1 = {01.D4} + {02.BF} + {03.5D} + {01.30}                                 |

| $= (1101\ 0100) \oplus (0110\ 0101) \oplus (1110\ 0111) \oplus (0011\ 0000)$ |

| = 0110 0110                                                                  |

| $=(66)_{16}$                                                                 |

|                                                                              |

Figure17: Rijndael Mix Columns computation example

Many researchers have published comparative analysis and optimized the speed of hardware implementations on the performance of different modes of operation. The results, from [8-20], reveal that the scheme has low hardware resource consumption, high throughput and an excellent overall performance ratio. Here, we focus on the development and analysis of an efficient AES-128 Mix Columns algorithm implementation in two different approaches.

## 2.2 Design Methods and Discussion

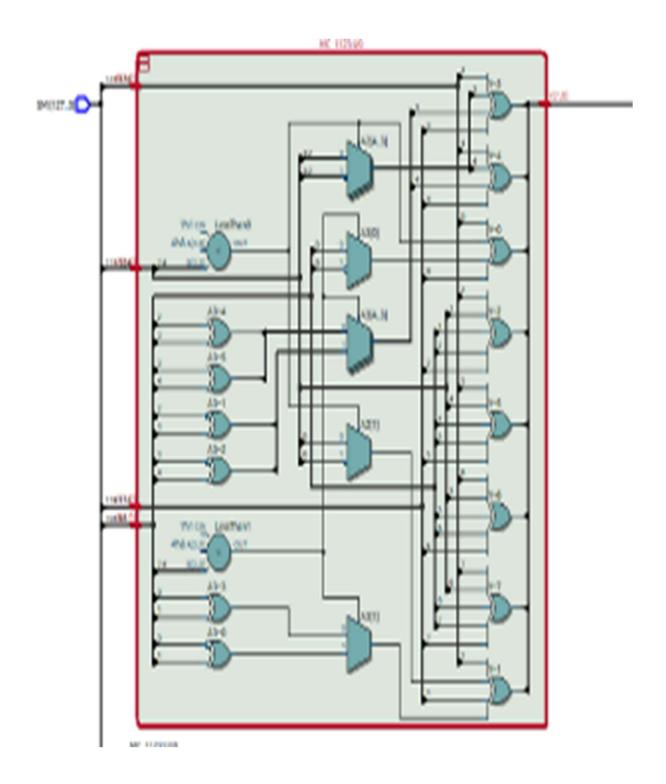

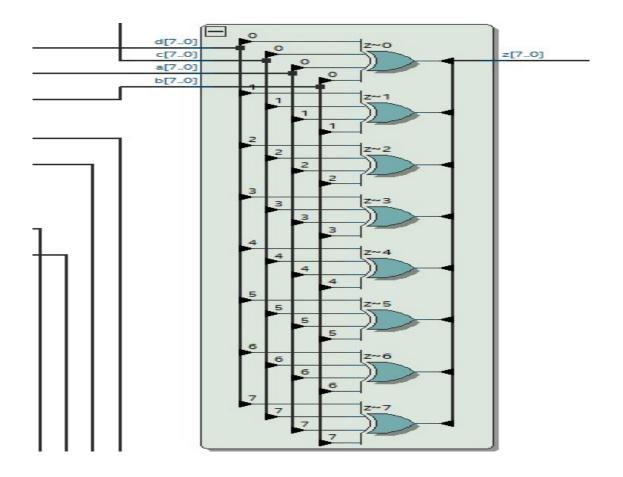

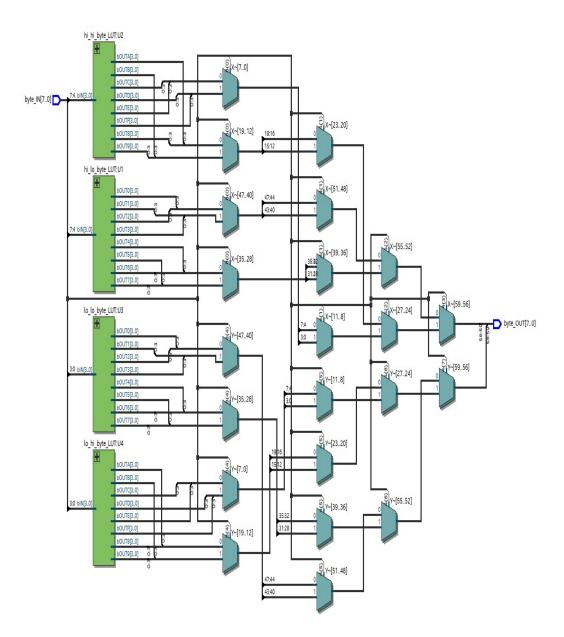

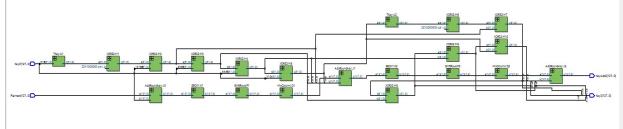

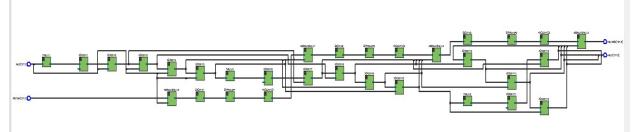

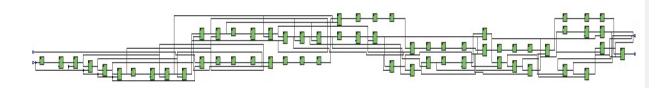

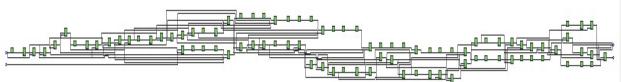

Our first approach involved building the circuit modules around the traditional rowcolumn multiplication method. This was done by creating codes for each row of the Rijndael mix columns matrix producing a total of four distinct sub-modules (shown in Figure 18). Each module would take 4 bytes (a column of the incoming data block matrix) and produce a single corresponding byte of the output matrix. This approach resulted in a circuit configuration that was simplistic in concept, however based on Figure 19, the circuit reveals only partial bit parallelization which could potentially deter the performance of the circuit because of misaligned clock cycles.

Our second approach focused on forcing a more parallel behavior into the circuit to align the input signals together potentially resulting in decreased delay. As seen in Figure 20, three distinct sub-modules were created that separate the Rijndael multiplication with factors 2 and 3 and adds an additional module 'M4' as a 4-input XOR function. Each of the 16 bytes of the input data block matrix will go through the same sub-modules, aligning them during their clock cycles, and producing the 16-byte output matrix at approximately the same cycle.

26

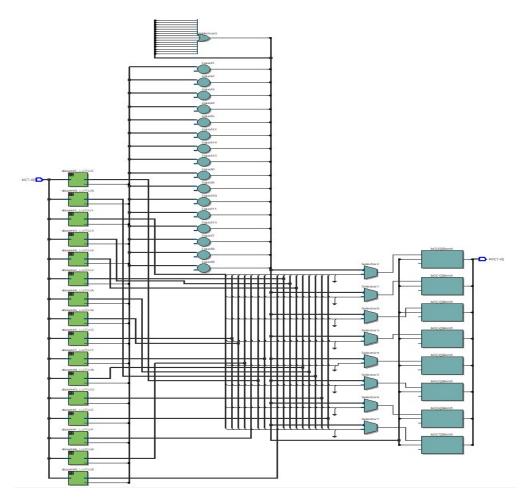

Figure 18: Internal schematic of each submodule

|                   | or m     | 70560-51      |               |        |                      |

|-------------------|----------|---------------|---------------|--------|----------------------|

| A[127:120]==>a_00 | 8        | - <u>M2 u</u> |               | M4 ui  | ₿b_00==>B[127:120]   |

| A[95:88]==>a_01   | 9        | M2 w 9        |               | M4 uz  | 8b_01==>B[95:88]     |

| A[63:56]==>a_02   | <u>8</u> | M2 u3 8       |               | M4 u3  | B b_02==>B[63:56]    |

| A[31:24]==>a_03   | <u>8</u> | M2 4 8        | - M3 ut - L   | M4 🗤   | Bb_03==>B(31:24)     |

| A[119:112]==>a_10 | 9        | M2 vs 8       |               | M4 u5  | ₿b_10==>B[119:112    |

| A[87:80]==>a_ll   | 9        | M2 16 8       | - M3 u6 7 1 1 | M4 16  | B                    |

| A[55:48]==>a_12   | ₿ [      | M2 v 8        | M3 u7 8       | M4 u?  | B b_12==>B[55:48]    |

| A[23:16]==>a_13   | 8        | M2 us 8       | - M3 us       | M4 ua  | ₿b_13==>B[23:16]     |

| A[111:104]==>a_20 | 8        | M2 v9 8       |               | M4 u9  | Bb_20==>B[111:104]   |

| A[79:72]==>a_21   | 8        | M2 UI8 8      |               | M4 U18 | Bb_21==>B[79:72]     |

| A[47:40]==>a_22   | <u>8</u> | M2 011 8      | M3 u1 8       | M4 v11 | B<br>b_22==>B[47:40] |

| A[15:8]==>a_23    | <u>8</u> | M2 U12 8      | M3 ute /      | M4 u12 | B<br>b_23==>B(15:8)  |

| A[103:96]==>a_30  | 9        | M2 U13 8      |               | M4 U13 | Bb_30==>B(103:96)    |

| A[71:64]==>a_31   | 9        | M2 UI4 8      |               | M4 014 | Bb_31==>B[71:64]     |

| A[39:32]==>a_32   | ₿ [      | M2 U15 8      | M3 uts 8      | M4 u15 | ₿b_32==>B[39:32]     |

| A[7:0]==>a_33     | 8        | M2 UI6 8      | M3 UL6 8      | M4 U16 | ₿<br>b_33==>B[7:0]   |

Figure 19: Module block diagram for parallelized configuration approach

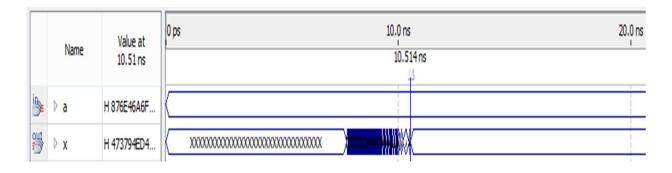

Figure 20: Internal schematic of M4 submodule

# 2.3 Result and Analysis

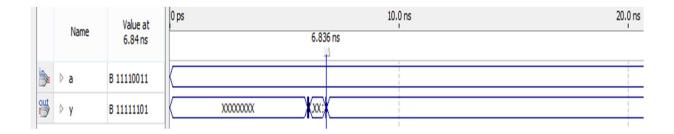

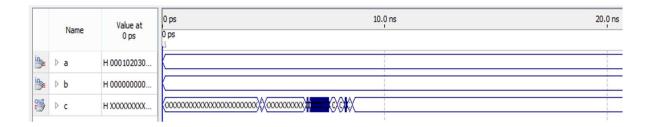

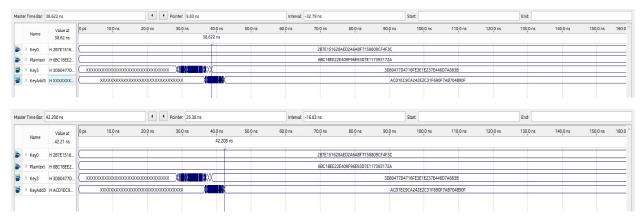

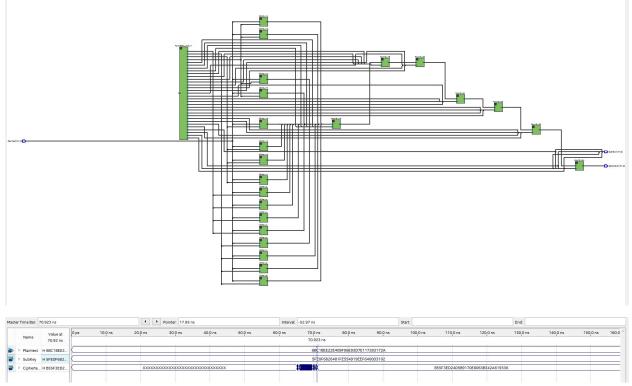

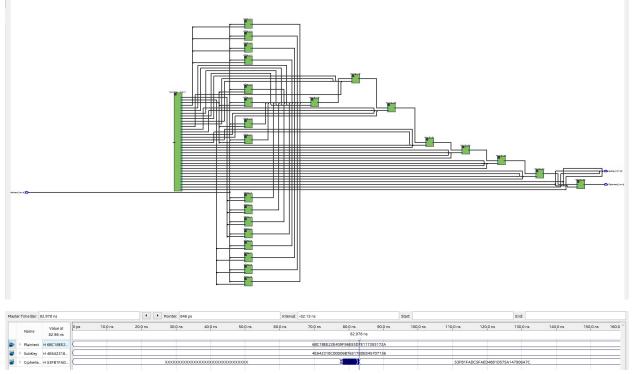

The following data presented is modeled after previous performance comparison attempts mentioned in [8-20]. According to the AES algorithm we mentioned in Section 2, we can distinguish Rijndael Mix Column into many operations or functions. In addition, we used the Quartus II software to perform the timing simulations for each operation or function in each step, as shown in Figure21~25. Finally, we developed the following tables to compare the performance.

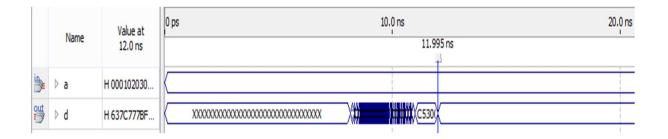

# Figure 21: Delay of M2 submodule

|           |            | Value at   | 0 ps 10.0 ns                     | 20.0 ns |

|-----------|------------|------------|----------------------------------|---------|

|           | Name       | 7.02 ns    | 7.024 ns                         |         |

| <u>is</u> | ⊳ a        | B 11110011 |                                  |         |

| in        | ⊳ b        | B 11001111 |                                  |         |

| 쐥         | ⊳ <b>у</b> | B 00111100 | (XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |         |

# Figure 22: Delay of M3 submodule

|    | Name | Value at<br>8.33 ns | 0 ps 10.0 ns 8.325 ns  | 20.0 ns |

|----|------|---------------------|------------------------|---------|

| in | ⊳ a  | B 11110011          |                        |         |

| in | ⊳b   | B 11001111          |                        |         |

| in | ⊳c   | B 10101010          |                        |         |

| in | ⊳d   | B 11111111          |                        |         |

| 쐥  | ⊳z   | B 01101001          | XXXXXXXXXX XXXX 10 100 |         |

# Figure 23: Delay of M4 submodule

|          |       | Value at   | 0 ps | 10.0 ns | 20.0 ns  | 30.0 ns |

|----------|-------|------------|------|---------|----------|---------|

|          | Name  | 16.02 ns   |      |         | 16.02 ns |         |

| 5        | > SMI | H 876E46A6 |      |         |          |         |

| <b>3</b> | > SMO | H 4X3794ED |      | xxxx)   | ₩¥       |         |

Figure 24: Timing simulation showing delay without parallelism

|          | Norma | Value at   | 0 ps      | 10.0 ns | 20.0 ns | 30.0 ns |  |  |  |  |

|----------|-------|------------|-----------|---------|---------|---------|--|--|--|--|

|          | Name  | 10.67 ns   | 10.672 ns |         |         |         |  |  |  |  |

| -        | > a   | H 876E46A6 |           |         |         |         |  |  |  |  |

| <b>*</b> | > x   | H 473794ED |           |         |         |         |  |  |  |  |

# Figure 25: Timing simulation showing delay with parallelism

| Function         | Operation Type         | Processing | AES 128 |       |

|------------------|------------------------|------------|---------|-------|

| Sub Bytes        | Substitution (S-Box)   | 1          | 2       | 10    |

| Shift Row        | Assign                 | 7.         | 10      |       |

|                  | M2 (Left Shift + XOR2) | 6.84       |         | 9     |

| Mix Columns      | M3(XOR2)               | 7.02       | 10.51   | 9     |

|                  | M4(XOR4)               | 8.83       | 10.51   | 9     |

| Add Round<br>Key | XOR2                   | 7.         | 11      |       |

|                  | Total Processing Time  | e (ηs)     |         | 369.3 |

Table 3: Delay of Plaintext Encryption

The results in Table 3 for Mix Columns were obtained for each submodule operation.

The final simultaion shows that the delay for each operation combines to give a reduced parallel

result.

| Prog.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 333 | lware<br>mption | Delay<br>(ηs) | Delay (ms) |         |         |              |        |                      |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|---------------|------------|---------|---------|--------------|--------|----------------------|--|--|

| , in the second s | TLE | PVM             | 128 bits      | 1Kbyte     | 1Mb yte | 10Mbyte | 100Mb yte    | 1Gbyte | 10G byte             |  |  |

| Without<br>parallelism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 224 | 5699MB          | 16.01         | 0.009      | 9.0     | 90.1    | 900.6        | 900563 | 9005625              |  |  |

| With<br>parallelism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 192 | 5517MB          | 10.66         | 0.006      | 6.0     | 60.0    | <u>599.6</u> | 599625 | <mark>5996250</mark> |  |  |

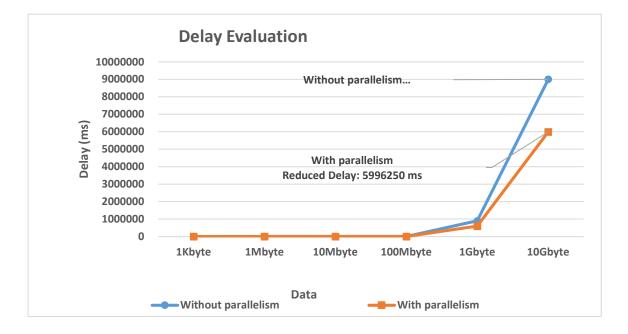

Table 4: Time Delay and Memory results of both implementations

Figure 26: Time delay analysis of mixed columns

The results and calculations shown in Table 3 evaluate the Total Logic Elements (TLE) and the Peak Virtual Memory (PVM) of the non-parallelized program "Without parallelism" and

the parallelized one "With parallelism". The graphical evaluation of the gathered data is depicted below.

Compared to the non-parallelized program, the parallelized version showed a significant decrease in needed logic elements and virtual memory for implementation. Based on the data in Table 4, at 10 GB of input data the parallelized implementation reduces the Rijndael Mix Columns operation delay by approximately 33.4%.

Based on encryption time for Mix Columns, we created a Delay Evaluation (Table 4) and made a plot to show the performance of the different approaches in terms of encryption time. We plotted for different file sizes shown in Figure 26 and observed that the 2nd approach, which parallelized the circuit signals more, had less time delay than the 1st approach. It was also noticed that the difference in memory allocation and size corresponded to the difference in delay.

## **2.4 Conclusion**

In this Chapter, we conduct our study on the most popular encryption algorithm AES. We targeted one mode of operation, Cipher Block Chaining (CBC), in terms of encryption time and delay on the Mix columns section. The results in Table 4 reveals that using parallelism in signal processing results in reduced time delay, logic elements and virtual memory. In the following chapter, we will focus on other sections for parallelization and try to implement AES on the FPGA. Finally, we will be able to obtain optimized area and speed hardware implementations of AES based on the sub-pipelined architecture.

#### CHAPTER III

# A FAST IMPLEMENTATION OF THE RIJNDAEL SUBSTITUTION BOX FOR CRYPTOGRAPHIC AES

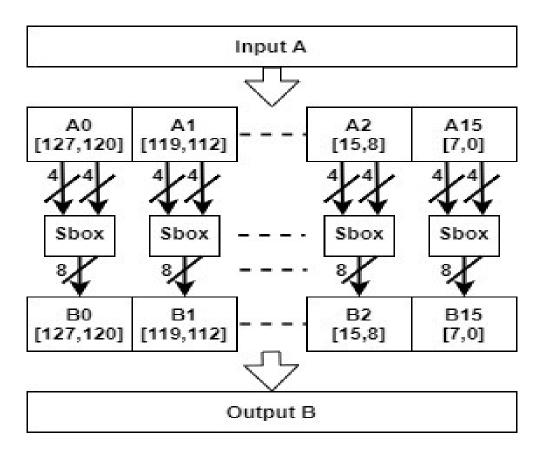

Today's current standard in Cryptography is the Symmetric Advanced Encryption Standard (AES) as selected by the US National Institute of Standards and Technology (NIST). It is also known as Rijndael Encryption Algorithm. Compared to various components of the AES, Rijndael S-box (substitution box) is the only non-linear component of the cryptosystem and significantly affects the overall performance of the AES encryption scheme. In this chapter, we investigate various implementations for improving the hardware performance of the Rijndael Sbox component of the AES algorithm in terms of delay and size on the Altera Cyclone IV FPGA (Field programmable gate arrays) using the Intel Quartus II software and Verilog Hardware Description Language (Verilog HDL).

The AES encryption algorithm accepts blocks of 128 or 192 or 256 bits and applies a series of substitutions and permutations [1-2]. A special substitution termed as "SubBytes Transformation" is also called Rijndael S-box, named after its designers. S-box is the main core structure of every block cipher system and controls the hardware complexity of Rijndael cipher elements due to its particular characteristics, a non-linear byte substitution and operating on each of the State bytes independently. The purpose of S-box is to produce confusion between the ciphertext and the secret key. There are  $256 = 16 \times 16$  possible 8-bit numbers, and so the S-box can be represented as a  $16 \times 16$  table mapping inputs to outputs.

S-box provides reversible conversion of plain text segments during the encryption process, while providing the opposite conversion during the decryption process. It is a single simple function that is applied to each byte over and over again during the encryption phase. Each of the 256 possible byte values is converted to another byte value by the transformation, which is a complete permutation as mentioned at Chapter 1. As a result, no two different byte values are changed to the same byte values.

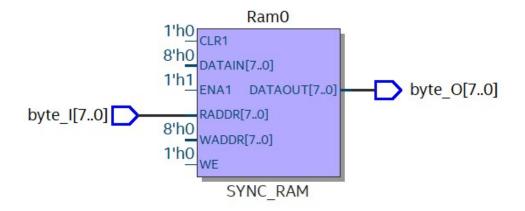

Figure 27: Substitute Bytes

The AES S-box is shown as Figure 27[1-2]. To find the output from the S-box table, the byte input is split into two 4-bit halves. The first half provides the row number and the second

half provides the column number for the Byte substitution. For example, an S-box transformation of 8'b11000011or 0xC3 can be found in a cell at the intersection of a row labeled C0 in hexadecimal and a column labeled 03 in hexadecimal. Therefore, 8'b11000011or 0xC3 becomes 8'b00101110 or 0x2E.

Several hardware implementations related work is available in literature [8-20]. Many literatures have proposed S-box hardware lookup table implementations [21-27]. To reduce LUT space requirements, the basic idea of Shannon's expansion theorem is applied. It helps achieve a logical design that has a greater number of levels with less implementation cost. This optimization technique reduces the complexity of the whole S-box which means it requires fewer arithmetic operations. As it simplifies table indexing, it simply consumes less power. Besides this optimization technique, including a smaller number of iterations will decrease the delay producing algebraic and matrix operations. In this chapter, we simulate different design techniques for the AES non-linear byte substitution in the Quartus-II simulator for a Cyclone IV FPGA platform. We verified the output performance of various implementations of the S-box in terms of delay and size.

|    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09         | θa | 0b | θc | 0d | 0e | Øf |

|----|----|----|----|----|----|----|----|----|----|------------|----|----|----|----|----|----|

| 00 | 63 | 7c | 77 | 7b | f2 | 6b | 6f | c5 | 30 | 01         | 67 | 2b | fe | d7 | ab | 76 |

| 10 | ca | 82 | c9 | 7d | fa | 59 | 47 | fØ | ad | <b>d</b> 4 | a2 | af | 9c | a4 | 72 | c0 |

| 20 | b7 | fd | 93 | 26 | 36 | Зf | f7 | cc | 34 | a5         | e5 | fl | 71 | d8 | 31 | 15 |

| 30 | 04 | c7 | 23 | c3 | 18 | 96 | 05 | 9a | 07 | 12         | 80 | e2 | eb | 27 | b2 | 75 |

| 40 | 09 | 83 | 2c | 1a | 1b | 6e | 5a | a0 | 52 | Зb         | d6 | b3 | 29 | e3 | 2f | 84 |

| 50 | 53 | dl | 00 | ed | 20 | fc | b1 | 5b | 6a | cb         | be | 39 | 4a | 4c | 58 | cf |

| 60 | dΘ | ef | aa | fb | 43 | 4d | 33 | 85 | 45 | f9         | 02 | 7f | 50 | Зc | 9f | a8 |

| 70 | 51 | a3 | 40 | 8f | 92 | 9d | 38 | f5 | bc | b6         | da | 21 | 10 | ff | f3 | d2 |

| 80 | cd | Θc | 13 | ec | 5f | 97 | 44 | 17 | c4 | a7         | 7e | 3d | 64 | 5d | 19 | 73 |

| 90 | 60 | 81 | 4f | dc | 22 | 2a | 90 | 88 | 46 | ee         | b8 | 14 | de | 5e | Θb | db |

| aθ | eΘ | 32 | 3a | 0a | 49 | 06 | 24 | 5c | c2 | d3         | ac | 62 | 91 | 95 | e4 | 79 |

| bθ | e7 | c8 | 37 | 6d | 8d | d5 | 4e | a9 | 6c | 56         | f4 | ea | 65 | 7a | ae | 08 |

| cØ | ba | 78 | 25 | 2e | 1c | a6 | b4 | c6 | e8 | dd         | 74 | 1f | 4b | bd | 8b | 8a |

| dØ | 70 | 3e | b5 | 66 | 48 | 03 | f6 | 0e | 61 | 35         | 57 | b9 | 86 | c1 | 1d | 9e |

| eθ | e1 | f8 | 98 | 11 | 69 | d9 | 8e | 94 | 9b | 1e         | 87 | e9 | ce | 55 | 28 | df |

| fØ | 8c | a1 | 89 | 0d | bf | e6 | 42 | 68 | 41 | 99         | 2d | Of | b0 | 54 | bb | 16 |

Figure 28: S-box table [2]

Figure 29: S-box Matrix Computation in GF (2<sup>8</sup>)

### 3.1 Rijndael S-Box Computation

S-box treats the values as a polynomial in Galois Field in factor  $2^{8}(GF(2^{8}))$  [1-2, 21-27], irreducible polynomial uses  $x^{8} + x^{4} + x^{3} + x^{1} + 1$ . It's calculation basically involves two steps:

- The inverse multiplication: derived from multiplicative inverse over GF (2<sup>8</sup>). "00" is mapped to itself.

- The affine transformation: applying the affine (on GF  $(2^8)$ ) transformation.

Using Rijndael's finite field for affine transformations the following expresses it as an equation for an input vector signal "X".

$$GF(2^8) = \frac{X}{(x^8 + x^4 + x^2 + x + 1)}$$

(Equation 3.1.1)

Equation 1.1 shows the affine transform in Galois Field (2<sup>8</sup>) as a function, with the characteristic irreducible polynomial as the denominator. This polynomial is represented in hardware as the binary string "100011011" for Boolean addition operations in the algorithm. The matrix representation of this function for S-box is shown in Figure 28. The input signal "b[7:0]" represents the 8-bit multiplicative inverse vector which undergoes Boolean XOR and addition operations to obtain the S-box output vector "a[7:0]." Figure 29 has various equations displayed in Boolean logic for quick implementation that represent the vector computation that occurs within the Rijndael multiplication and are shown in sequence as equations below.

$s = b \oplus (b \ll 1) \oplus (b \ll 2) \oplus (b \ll 3) \oplus (b \ll 4) \oplus 63_{16}$  (Equation 3.1.2)

$s_i = b_i \oplus b_{(i+4)mod8} \oplus b_{(i+5)mod8} \oplus b_{(i+6)mod8} \oplus b_{(i+7)mod8} \oplus c_i$ (Equation 3.1.3)

$s = (b x 31_d) \mod 257_d \oplus 99_d \qquad (Equation 3.1.4)$

However, the Rijndael S-box is not economical because it is based on the LUTs and uses more resources during implementation. To achieve high throughput and low power consumption, many literatures have proposed S-box hardware lookup table implementations [21-27]. In this chapter, we focused on how to efficiently implement pipeline technology utilizing FPGA platform to make S-box fast and verify the performance of various implementations of S-box in terms of latency and size.

### 3.2 Design Methods and Discussion

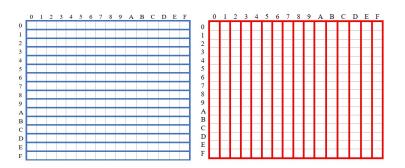

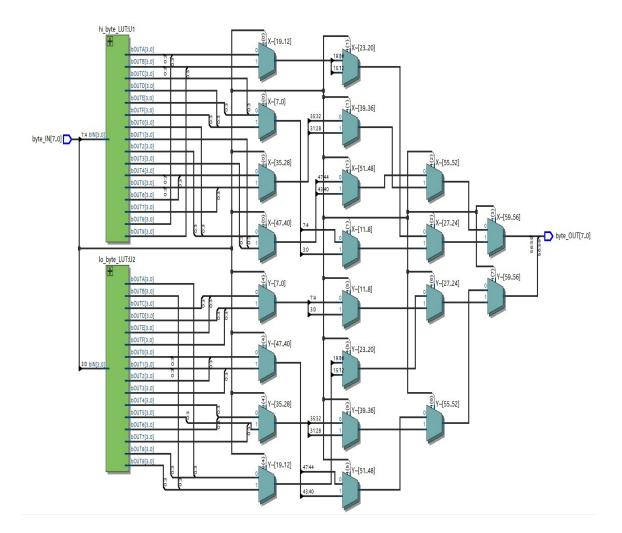

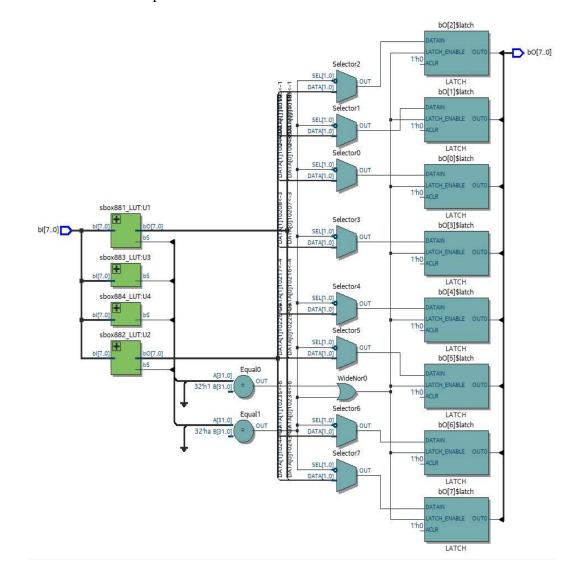

This research proposes three unique new designs based on restricting the way the S-box is implemented. The baseline implementation is a 256-line Look-Up-Table (LUT) that is conducted using sequential logic. Using the LUT in the design logic can significantly impact the amount of logic elements (LE's) that get used up by the FPGA. This method of adopting the basic principles of Shannon's expansion theorem achieves a logical design, which a greater number of levels, reduces the space requirement of the LUT, and lowers the implementation cost. This optimization technique reduces the complexity of the S-box module which results in fewer arithmetic operations. As it simplifies table indexing, it additionally consumes less power. This design, along with the reduced number of iterations, significantly lowers the delay for the algebraic and matrix operations. The designs are shown in the figures below and depict how the S-box is segmented to create smaller LUT's combined with multiplexer (MUX) logic for the correct output selection.

# **Baseline:**

The baseline Verilog HDL module implements the Substitution Box as a single LUT. The Register Translation Language (RTL) shows the baseline LUT module in Figure 30. This module is a direct implementation of the standard Rijndael Substitution Box shown in Figure 2, where an 8-bit input vector corresponds to a specific 8-bit output vector. This module relies on sequential logic, which consumes both a significant amount of hardware Logic Elements (LE's) and processing time from input to output.

Figure 30: Baseline RTL

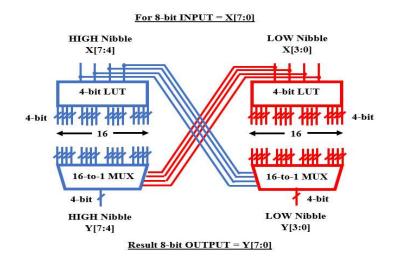

## **Design 1 (Row Column Parallelization of S-Box):**

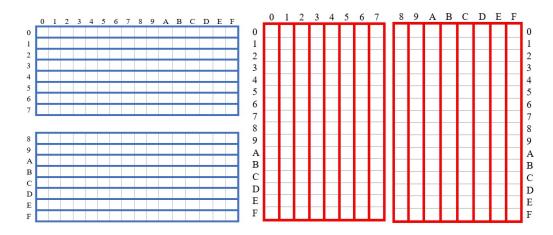

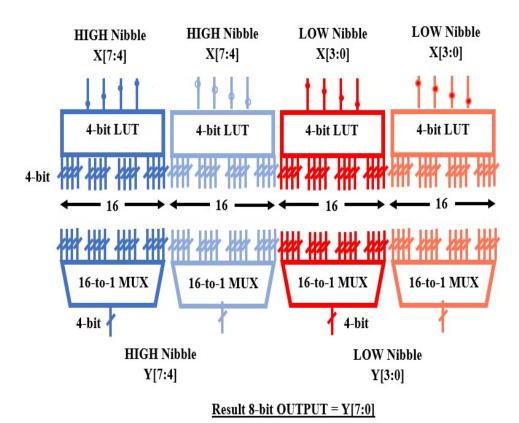

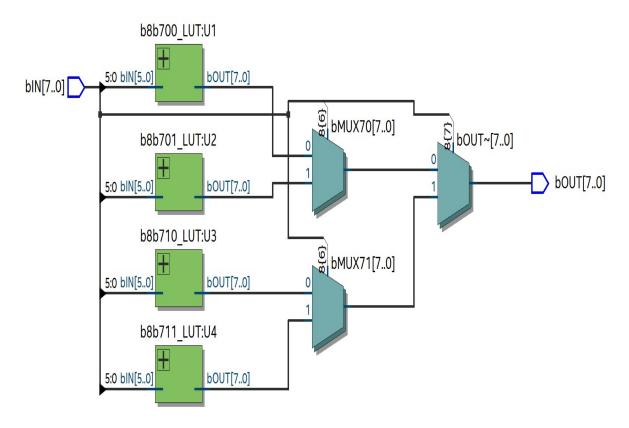

Design 1 aims to parallelize the Substitution Box by determining each corresponding 4bit output in the same amount of clock cycles. This approach for the Substitution Box focuses on separating the rows and columns of the 256-byte LUT (Figures 31-33). Each value in the row and column of the Substitution Box uses a nibble of the input byte-wise vector to determine the corresponding substitute value. This design utilizes 2 LUT's for each nibble (HIGH and LOW) of the input byte-wise vector and generates 16 possible output values that feed into a 16-to-1 Multiplexer (MUX) which uses the opposite nibble to select the correct 4-bit output. The module then concatenates the output of each MUX to create the correct corresponding output byte-wise vector.

Figure 31: Design 1 S-box Segmentation

Figure 32: Design 1 Module Map

Figure 33: Design 1 RTL

### **Design 2 (Expanded RC Parallelization of S-Box):**

Design 2, shown in Figures 34-36, aims to extend the technique of Design 1 by creating 4 LUT's instead of 2 for further parallelization. This design further segments the LUTs required to compute the corresponding substitute value. Through this LUT segmentation extension of the baseline Rijndael LUT S-Box, Design 2 attempts to produce the correct byte-wise output while increasing its LUT variable search, compared to Design 1, in the same clock cycle.

Figure 34: Design 2 S-box Segmentation

# For 8-bit INPUT = X[7:0]

Figure 35: Design 2 Module Map

Figure 36: Design 2 RTL

# Design 3 (Reduced LUT Parallization of S-Box): Design 3, shown in Figure 37-38,

aims to parallelize the Rijndael S-Box by creating size reduced LUT's from the standard Substitution Box, shown in Figure 27. The standard Substitution Box is separated into 4 LUT's one for each 8-byte by 8-byte quadrant. The byte-wise input vector goes through each of the 4 LUT's with only a single LUT generating the correct output vector while the others produce a logic zero. The output of all LUT's are then fed into a 4-to-1 byte-wise adder that combines all values to determine the output 8-bit substitution value.

Figure 37: Design 3 RTL

**Design 4 (Further Re. LUT Parallelization of S-Box):** Design 4 aims to further reduce the LUT parallelization technique of Design 3 by creating smaller LUT's from the segmented quadrants. This approach extends the segmentation of the Rijndael S-Box by four times compared to Design 3. The aim of Design 3 and 4 is to parallelize the process of determining the correct output value by reducing the memory consumption of the sequential logic used to generate the LUT's. The use of an adder to determine the output increases the LE cost of the module but attempts to significantly reduce the processing delay.

Figure 38: Design 4 RTL

**Design 5 (Shannon's Expansion of S-Box):** Design 5, shown in Figure 39, uses Shannon's expansion to reduce the processing time and cost consumption of the Substitution Box. This design uses the 8th and 7<sup>th</sup> MSB's (most significant bits) of the input byte-wise vector to determine the correct output substitute value through MUX logic. The input to the MUX logic includes four 6-byte x 6-byte LUT's that represent the possible outcomes that could be selected based on all variations of the 8<sup>th</sup> and 7<sup>th</sup> MSB such as "00", "01", "10", and "11". This approach, like the previous designs, aims to not only increase the searching process on the same clock cycle but reduce the LUT size for each search to achieve low LE cost and faster throughput.

Figure 39: Design 5 RTL

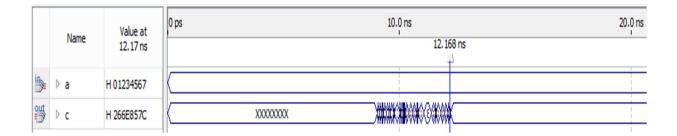

#### **3.3 Result and Analysis**

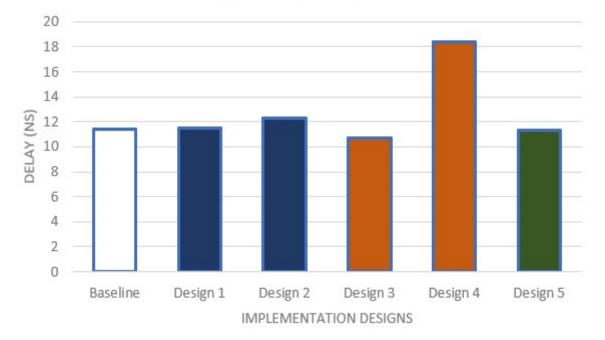

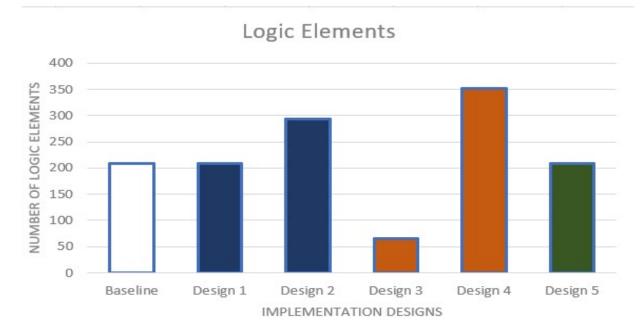

The implementation of all Substitution Box designs was simulated on the Cyclone IV FPGA using NIST test vectors; the results are shown in Table 5. The baseline design is the initial direct implementation of the Rijndael Substitution Box from [1-2]. The baseline generated an average of 11.41 nanoseconds of delay while consuming 208 LE's. The results from the first implementation, displayed in Table 5, showed an increase in both average delay by 0.11 ns for design 1 and 0.52 ns for design 2. Design 3 showed the most efficient output compared to the baseline LUT; design 3 was able to generate the correct output 1.08 ns faster and with a 31.3% decrease in LE hardware consumption.

The Substitute Bytes module is repeated a total of 200 times, shown in Table 6, in the final implementation of AES-128. Compared to the other submodules that make up the AES-128 algorithm, only the byte-wide 2-input XOR (XOR2) module was instanced more than Substitute Bytes by a total of 120 times (Table 6). To improve the AES-128 algorithm in efficiency and throughput, it is crucial to target the most repetitive submodule since improvements in its implementation would be magnified. However, the XOR2 submodule is simply an expanded XOR gate that requires significantly less LE consumption than the Substitute Bytes module which is a 256-byte size LUT. The I/O delay and LE consumption for design 3 would be multiplied by the module count and would reduce the total delay of the AES encryption algorithm by approximately 200 ns compared to the baseline. The concept for design 3 and the other implementations, show the effectiveness of pipelining in processor operations. By segmenting the LUT into separate modules, each can be executed on the same clock cycle and reduce the overall delay of the process.

This was expected to bring a trade-off between the hardware consumption to reduce the delay however design 3 was able to improve on both areas.

Many literatures have proposed S-box hardware lookup table implementations [21-27]. The logic design using the basic principles of Shannon's expansion theorem is achieved. By comparing the suggested designs to other reported techniques, analysis of the results indicates that the proposed design 3 is capable of significantly outperforming the other four designs in terms of delay and area as measured by the simulation. From the simulations of the proposed designs, we observed that the throughput can be increased by reducing the delay of the critical path taken by the input byte-wise vector specifically in the LUT segment. By targeting one of the most utilized modules in the AES computation scheme, the efficiency of the overall implemented algorithm can be improved on. The achieved lower LE cost and faster throughput will multiply based on the number of instances of the submodule included in the final design of AES-128 and can lead to improvements in the extended iterations of AES such as AES-192, AES-256, and AES-512[30-40].

| Design   | Average Delay (ns) | Logic Elements | Virtual Pins |  |  |

|----------|--------------------|----------------|--------------|--|--|

| Baseline | 11.41              | 208 (<1%)      | 16 (3%)      |  |  |

| Design 1 | 11.52              | 208 (<1%)      | 16 (3%)      |  |  |

| Design 2 | 12.33              | 294 (<1%)      | 16 (3%)      |  |  |

| Design 3 | 10.73              | 65 (<1%)       | 16 (3%)      |  |  |

| Design 4 | 18.41              | 352 (<1%)      | 16 (3%)      |  |  |

| Design 5 | 11.36              | 208 (<1%)      | 16 (3%)      |  |  |

|                  | AES-128 Top Level Module |                             |           |                            |  |  |  |  |  |  |

|------------------|--------------------------|-----------------------------|-----------|----------------------------|--|--|--|--|--|--|

| Sub module       | Instances                | Peak Virtual<br>Memory (MB) | Pins/529  | Logic Elements<br>/114,480 |  |  |  |  |  |  |