University of Texas Rio Grande Valley ScholarWorks @ UTRGV

Theses and Dissertations - UTB/UTPA

12-2014

# A 129NW Neural Amplifier and Gm-C Filter for EEG Using gm/ID Methodology

Samuel A. Gallegos University of Texas-Pan American

Follow this and additional works at: https://scholarworks.utrgv.edu/leg\_etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Gallegos, Samuel A., "A 129NW Neural Amplifier and Gm-C Filter for EEG Using gm/ID Methodology" (2014). *Theses and Dissertations - UTB/UTPA*. 982. https://scholarworks.utrgv.edu/leg\_etd/982

This Thesis is brought to you for free and open access by ScholarWorks @ UTRGV. It has been accepted for inclusion in Theses and Dissertations - UTB/UTPA by an authorized administrator of ScholarWorks @ UTRGV. For more information, please contact justin.white@utrgv.edu, william.flores01@utrgv.edu.

# A 129nW NEURAL AMPLIFIER AND G<sub>m</sub>-C FILTER

## FOR EEG USING $g_m/I_D$ METHODOLOGY

A Thesis

by

## SAMUEL A. GALLEGOS

Submitted to the Graduate School of The University of Texas - Pan American In partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

December 2014

Major Subject: Electrical Engineering

## A 129nW NEURAL AMPLIFIER AND Gm-C FILTER

## FOR EEG USING $g_m/I_D$ METHODOLOGY

## A Thesis by SAMUEL A. GALLEGOS

## COMMITTEE MEMBERS

Dr. Hasina F. Huq Chair of Committee

Dr. Heinrich D. Foltz Committee Member

Dr. Weidong Kuang Committee Member

December 2014

Copyright 2014 Samuel A. Gallegos

All Rights Reserved

#### ABSTRACT

Gallegos, Samuel A., <u>A 129nW Neural Amplifier and G<sub>m</sub>-C Filter For EEG Using g<sub>m</sub>/I<sub>D</sub></u> <u>Methodology</u>. Master of Science (MS), December, 2014, 87 pp., 3 tables, 48 figures, 25 references, 7 chapters.

This Thesis presents a low-power analog front-end amplifier and  $G_m$ -C filter for biomedical sensing applications, specifically for Electroencephalogram (EEG) use. The proposed neural amplifier uses a supply voltage of 1.8V, it has a mid-band gain of 40.75dB, and consumes a total current of 71.82nA, for a total dissipated power of 129.276nW. Also presented is the design of a 3<sup>rd</sup> order Butterworth Low Pass G<sub>m</sub>-C Filter which makes use of 14.7nS transconductors; the proposed filter has a pass band suitable for EEG recording use (1-100Hz). The amplifier and filter utilize current sources without bias resistances which provide 56nA and (1.154nA x 5) respectively. The proposed neural amplifier occupies a chip area of 0.275mm<sup>2</sup> in a 0.3µm TSMC process. Simulation of the schematic and extracted chip layout is presented, along with a comparison of similar published works. Finally, a projected power consumption calculation for a multichannel system based on this system is offered.

#### DEDICATION

To my mother who rests in peace; the completion of my studies would not have been possible without the love and support of my family. Thank you for your everlasting love, support, guidance, and patience.

To my best friend and the sunshine in my life. The completion of this manuscript would not have been possible without your encouragement and support. Thank you for always being there for me with the biggest smile.

#### ACKNOWLEDGMENTS

I would like to thank Dr. Hasina Huq, chair of my Thesis committee, for all her guidance and advice during this research project. Also, I would like to thank Dr. Heinrich Foltz and Dr. Weidong Kuang for taking time to be part of my thesis committee, as well as for their feedback and suggestions.

I would like to thank Dr. Heinrich Foltz not as my committee member but as an outstanding Electrical Engineering professor; thank you for your patience and for lighting students' candles with your knowledge; thank you for sharing all that experience in a manner that has truly been nourishing.

Finally, I would like to extend my gratitude to my colleagues in the Graduate Lab for their support and good laughs during the completion of this thesis project.

# TABLE OF CONTENTS

| ABSTRACT                                                          | iii  |

|-------------------------------------------------------------------|------|

| DEDICATION                                                        | iv   |

| ACKNOWLEDGEMENTS                                                  | v    |

| TABLE OF CONTENTS                                                 | vi   |

| LIST OF TABLES                                                    | viii |

| LIST OF FIGURES                                                   | ix   |

| CHAPTER I. INTRODUCTION.                                          | 1    |

| Background Information                                            | 3    |

| The Electroencephalogram (EEG)                                    | 3    |

| The Operational Transconductance Amplifier (OTA)                  | 7    |

| The G <sub>m</sub> -C Filter                                      | 15   |

| Thesis Structure                                                  | 18   |

| CHAPTER II. LITERATURE REVIEW                                     | 20   |

| CHAPTER III. THE $g_m/I_D$ METHODOLOGY                            | 28   |

| Obtaining the plot of $g_m/I_D$ vs. $I_D/(W/L)$ for NMOS and PMOS | 30   |

| CHAPTER IV. OPERATIONAL TRANSCONDUCTANCE AMPLIFIER DESIGN         | 35   |

| The Bias Circuit for the OTA                                      | 36   |

| Design of the Amplifier's Physical Layout                         | 38   |

| Simulation of the OTA                                    | 40 |

|----------------------------------------------------------|----|

| CHAPTER V. Gm-C FILTER DESIGN.                           | 42 |

| Design of the G <sub>m</sub> -C Filter's Physical Layout | 46 |

| Simulation of the G <sub>m</sub> -C Filter               | 47 |

| CHAPTER VI. THE NEURAL AMPLIFIER                         | 49 |

| Design of the Neural Amplifier Physical Layout           | 52 |

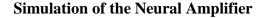

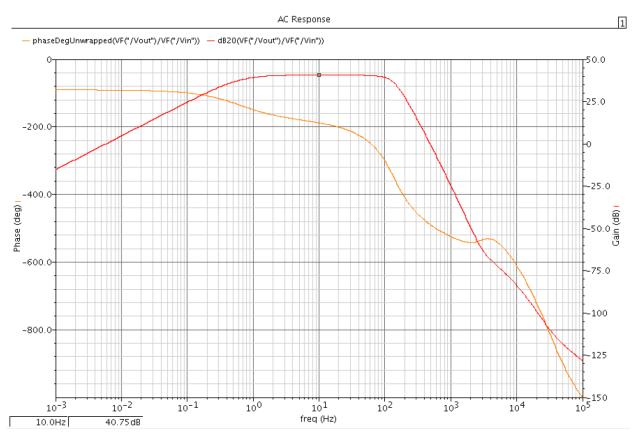

| Simulation of the Neural Amplifier                       | 54 |

| Projected Multi-Channel Amplifier for EEG                | 58 |

| CHAPTER VII. CONCLUSION                                  | 59 |

| Future Work                                              | 59 |

| REFERENCES                                               | 61 |

| APPENDIX A                                               | 66 |

| TSMC 25 Spice NMOS and PMOS Transistor Models.           | 67 |

| APPENDIX B                                               | 69 |

| Neural Amplifier LVS Log File                            | 70 |

| APPENDIX C                                               | 72 |

| Neural Amplifier Simulation Input Files                  | 73 |

| BIOGRAPHICAL SKETCH                                      | 87 |

# LIST OF TABLES

| Table 1: OTA AND CURRENT REFERENCE TRANSISTOR SIZES          | 37 |

|--------------------------------------------------------------|----|

| Table 2: G <sub>m</sub> -C FILTER OTA TRANSISTOR SIZES       | 44 |

| Table 3: NEURAL AMPLIFIER SIMULATION RESULTS COMPARISON WITH |    |

| PUBLISHED WORKS                                              | 57 |

## LIST OF FIGURES

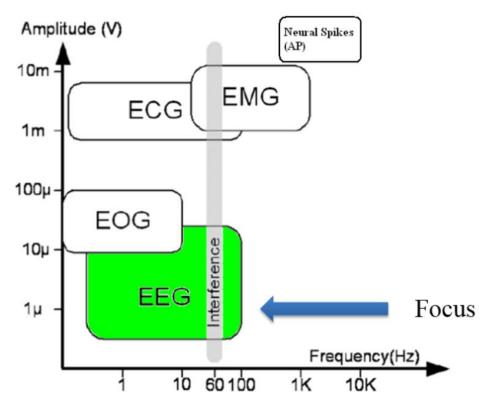

| Figure 1: Frequency and amplitude ranges of different biopotential signals [7]                     | 2    |

|----------------------------------------------------------------------------------------------------|------|

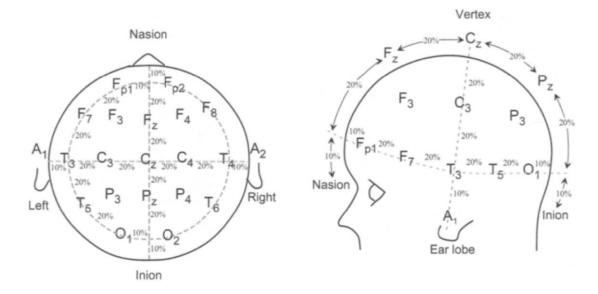

| Figure 2: The international 10/20 system for recording of clinical EEGs                            | 4    |

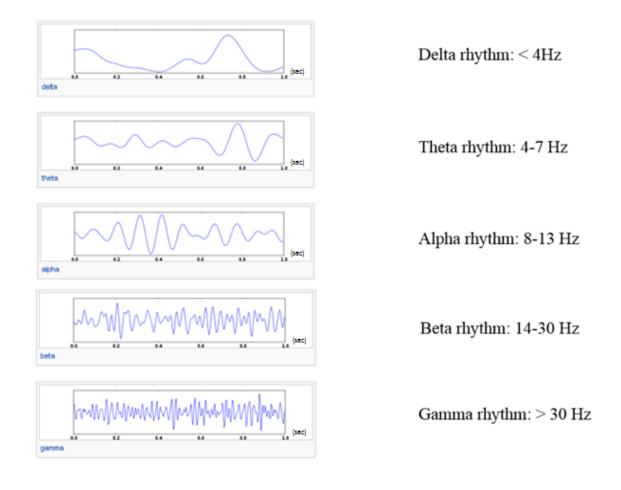

| Figure 3: Examples of the different kinds of rhythms observed in an EEG                            | 5    |

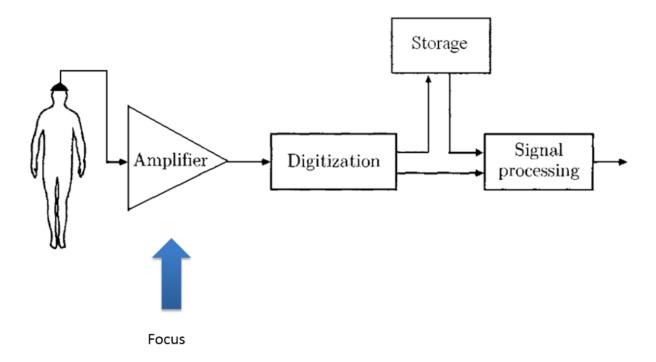

| Figure 4: Block diagram describing the main steps in biomedical signal acquisition                 | 7    |

| Figure 5: A schematic of the differential pair input stage [25]                                    | 8    |

| Figure 6: Example plot of currents I <sub>1</sub> and I <sub>2</sub> vs differential input voltage | 9    |

| Figure 7: Simple transconductance amplifier and its symbol [25]                                    | 10   |

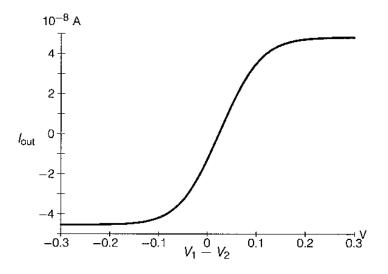

| Figure 8: Circuit setup to measure <i>I</i> <sub>out</sub> vs. the differential input voltage      | 11   |

| Figure 9: <i>I</i> <sub>out</sub> of the OTA vs differential input voltage                         | 12   |

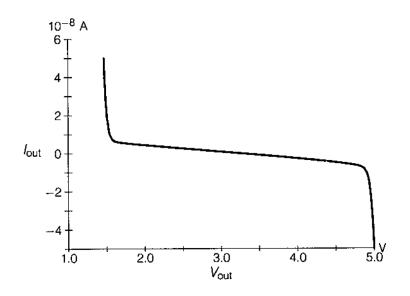

| Figure 10: Output current as a function of the output voltage. [25]                                | 13   |

| Figure 11: Wide Range Transconductance Amplifier with NMOS differential input pair                 | . 15 |

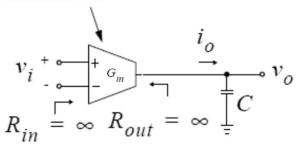

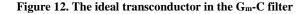

| Figure 12: The ideal transconductor in the G <sub>m</sub> -C filter                                | 16   |

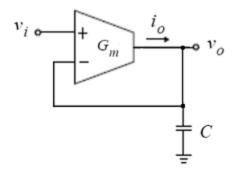

| Figure 13: Simple single pole G <sub>m</sub> -C low pass filter                                    | 17   |

| Figure 14: Frequency response dB gain of the simple single pole $G_m$ -C low pass filter           | 18   |

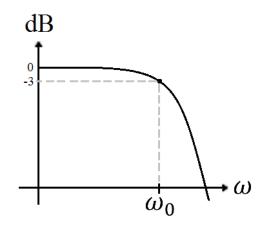

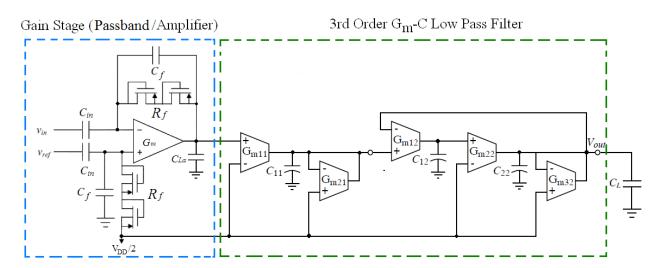

| Figure 15: Overall system diagram for the neural amplifier integrated circuit                      | 19   |

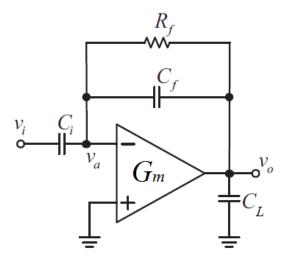

| Figure 16: Capacitive Feedback Network for neural amplifier [9]                                    | 21   |

| Figure 17: Theoretical CFN neural amplifier proposed by Harrison and Charles in [1, 2]             | . 22 |

| Figure 18: The OTA based neural amplifier proposed by Harrison and Charles in [1, 2]               | . 23 |

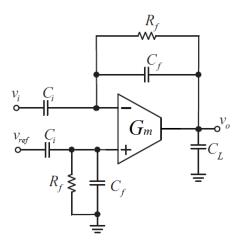

| Figure 19: The OTA based neural amplifier proposed by Wattanapanitch, et al in [6]                 | 24   |

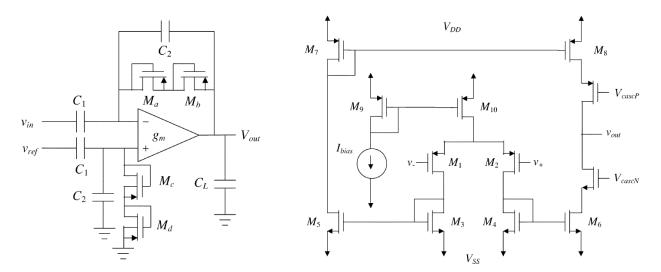

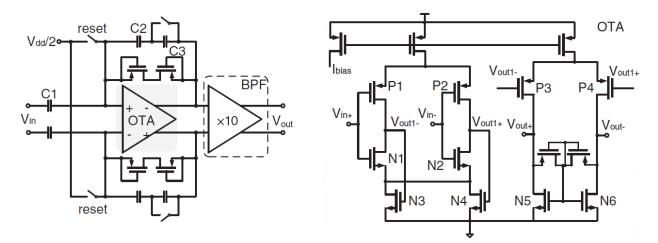

| Figure 20: The proposed neural amplifier and OTA [3]                                             | 26   |

|--------------------------------------------------------------------------------------------------|------|

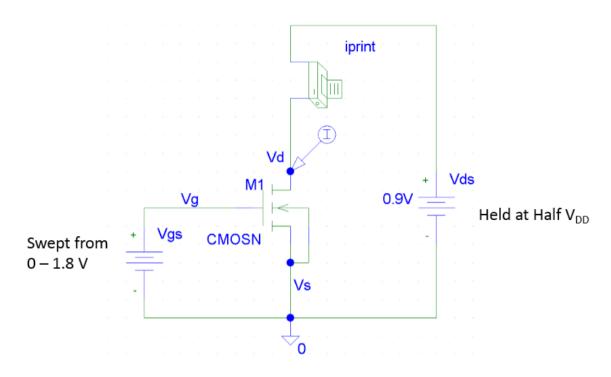

| Figure 21: Test circuit to characterize the NMOS transistor in the 300nm TSMC process.           | . 31 |

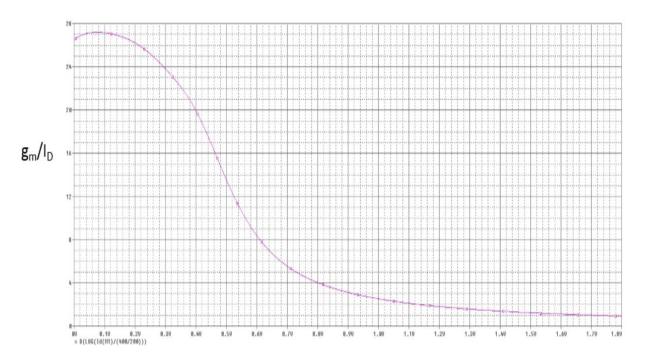

| Figure 22: $g_{nn}/I_D$ vs. $V_{GS}$ curve for NMOS with TSMC 25 transistor model                | 31   |

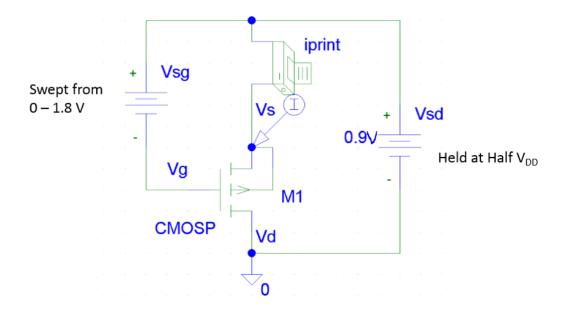

| Figure 23: Test circuit to characterize the PMOS transistor in the 300nm TSMC process.           | 32   |

| Figure 24: $g_m/I_D$ vs. $V_{GS}$ curve for PMOS with TSMC 25 transistor model                   | 32   |

| Figure 25: $g_m/I_D$ vs. $I_D/(W/L)$ curve for NMOS and PMOS with 300nm TSMC process             | 33   |

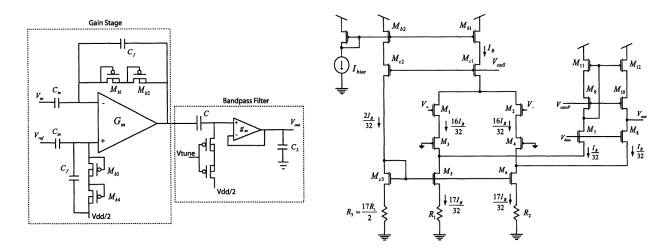

| Figure 26: 108.9nW Folded Cascode Operational Transconductance Amplifier                         | 36   |

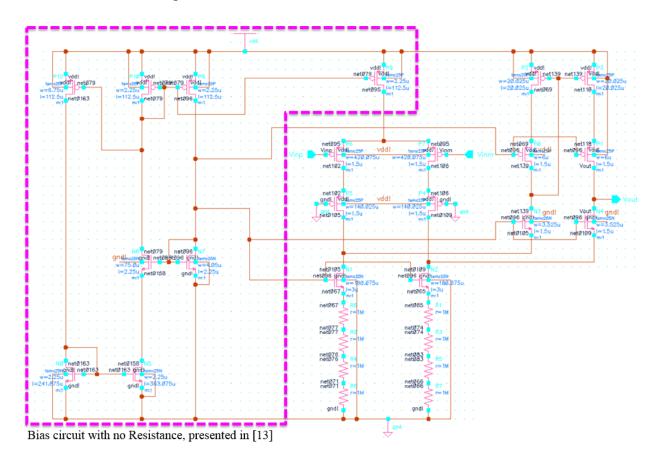

| Figure 27: CMOS current reference proposed in [13]                                               | 37   |

| Figure 28: The OTA with its 56nA current reference circuit                                       | 38   |

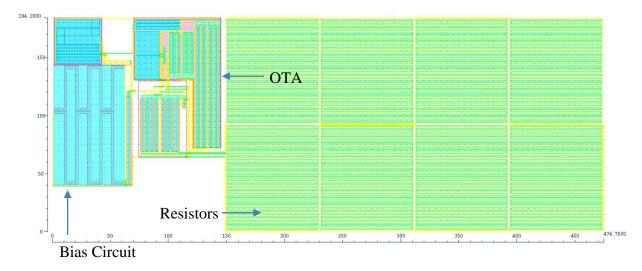

| Figure 29: Amplifier Layout (including bias circuit) with an area of $474.75 \times 184.2 \mu m$ | 39   |

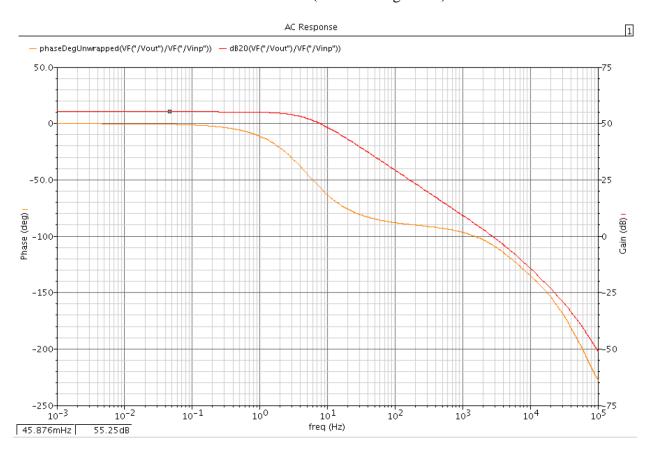

| Figure 30: Open-loop frequency response of the OTA's schematic                                   | 40   |

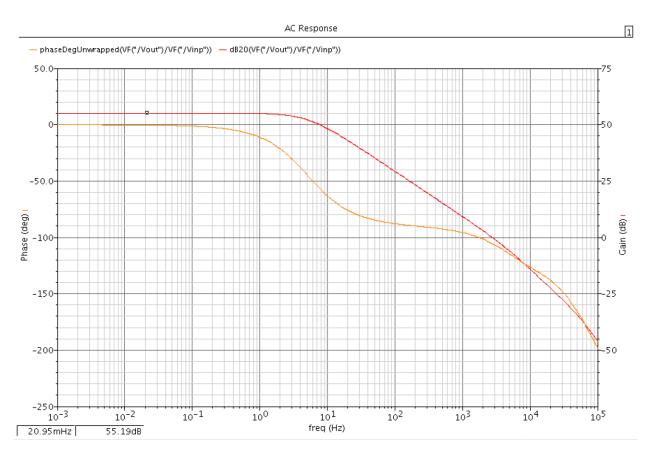

| Figure 31: Open-loop frequency response of the OTA's extracted layout                            | 41   |

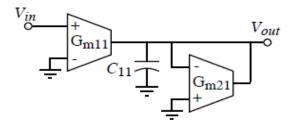

| Figure 32: First order G <sub>m</sub> -C stage                                                   | 43   |

| Figure 33: Second order G <sub>m</sub> -C stage                                                  | 43   |

| Figure 34: Telescopic cascoded amplifier used as the OTA for the $G_m$ -C filter                 | 44   |

| Figure 35: 14.7nS NMOS cascoded diff. pair transconductor used in the $G_m$ -C filter            | 45   |

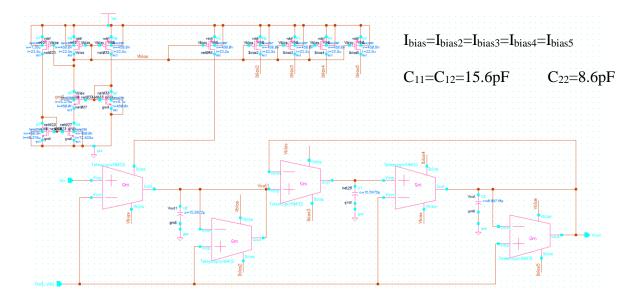

| Figure 36: 3 <sup>rd</sup> order G <sub>m</sub> -C low pass filter schematic with bias circuit   | 45   |

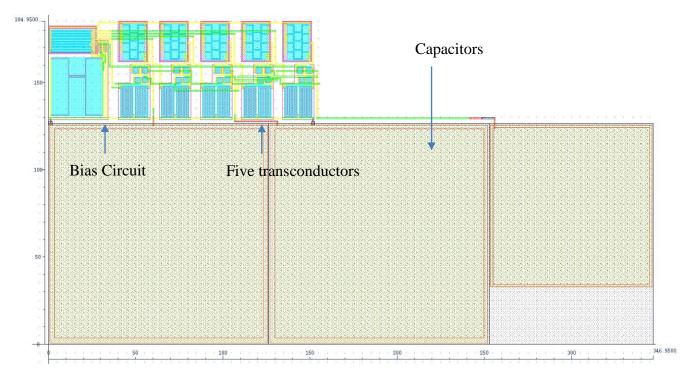

| Figure 37: G <sub>m</sub> -C Filter Layout in the 300nm TSMC process                             | 46   |

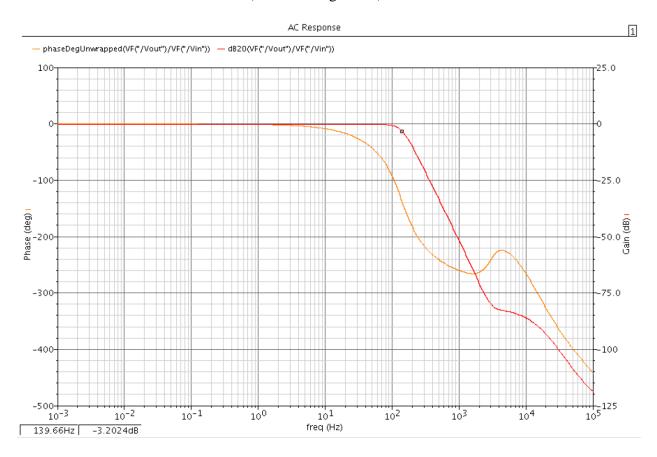

| Figure 38: Frequency response of the G <sub>m</sub> -C filter's schematic                        | 47   |

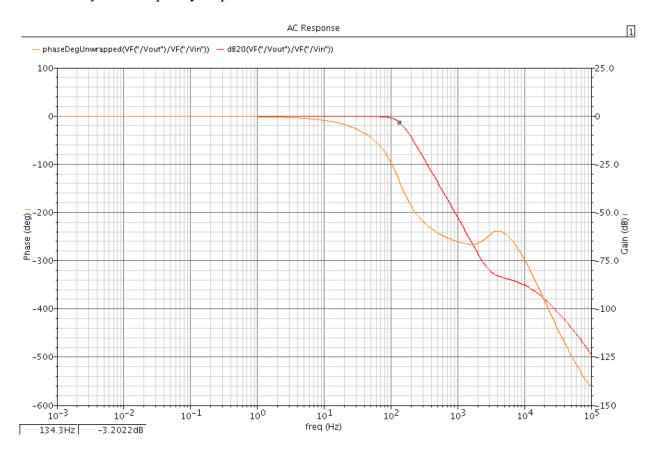

| Figure 39: Frequency response of the G <sub>m</sub> -C filter's extracted layout                 | 48   |

| Figure 40: The proposed neural amplifier                                                         | 49   |

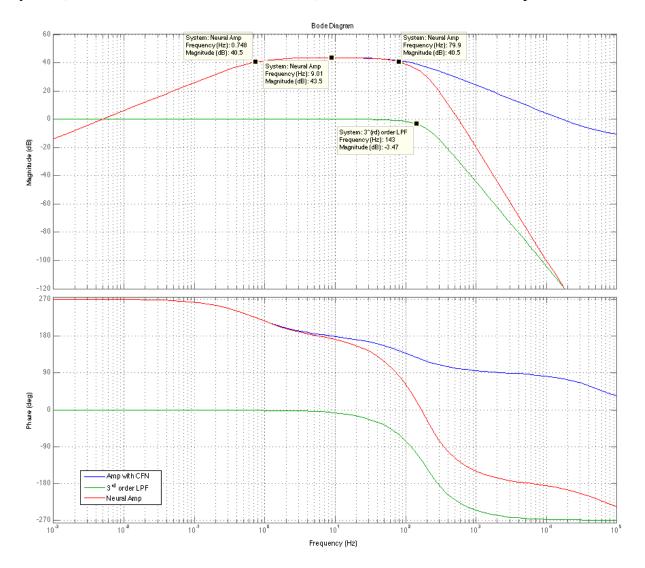

| Figure 41: MATLAB bode plots for all stages of the neural amplifier                              | 50   |

| Figure 42: Complete schematic of the neural amplifier                                            | 51   |

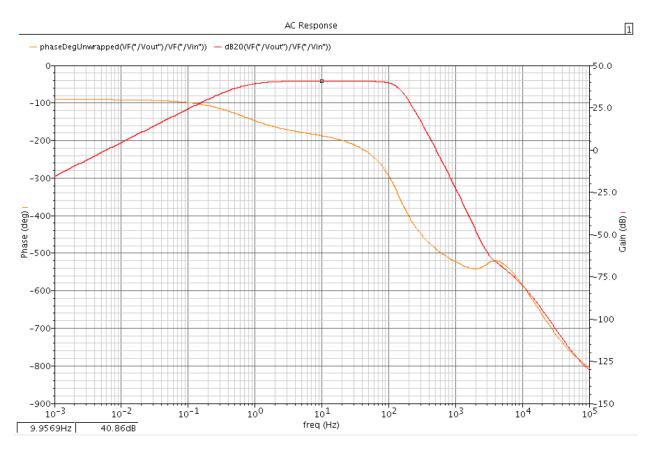

| Figure 43: Frequency Response of the Neural Amplifier's schematic                              | 52 |

|------------------------------------------------------------------------------------------------|----|

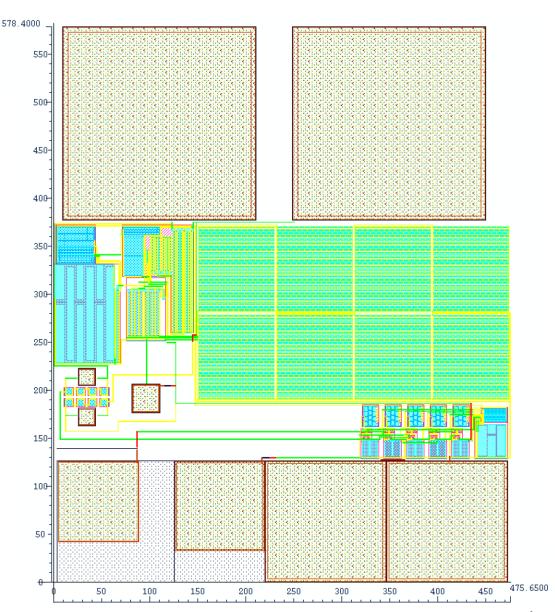

| Figure 44: Neural Amplifier IC Layout with an area of $475.65 \times 578.4 \mu m (0.275 mm^2)$ | 53 |

| Figure 45: Frequency Response of the Neural Amplifier's extracted layout                       | 54 |

| Figure 46: Squared output noise of the Neural Amplifier's extracted layout                     | 55 |

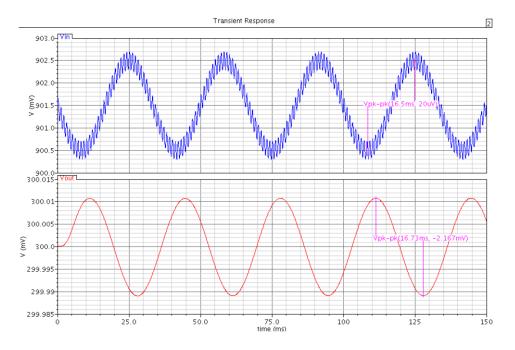

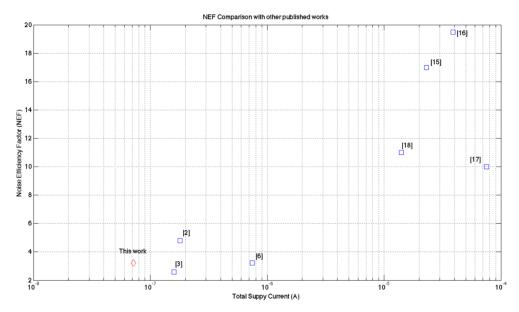

| Figure 47: Transient simulation of the system to a noise affected input signal                 | 56 |

| Figure 48: NEF vs. Total Supply Current comparison                                             | 56 |

#### CHAPTER I

#### INTRODUCTION

In recent years, research has been done on the miniaturization and development of low power, low noise integrated circuits (ICs) for biosignal sensing applications [1-8] due to their need in the medical field among clinicians and scientists in the field of neuroscience. These circuits need to be capable of amplifying biosignals in the milli Hertz to kilo Hertz range (as seen in Figure 1) while rejecting large DC offsets generated at the electrode-tissue interface [1]. These integrated circuits are being developed for implantable and portable wireless biosensor devices [3], in which multi-electrode neural recordings, for basic neuroscience research, are becoming increasingly common. The knowledge obtained from the studies in this area is beginning to enable clinical and neuroprosthetic applications for paralyzed patients, along with the use of brain controlled computer interfaces, and it is improving the diagnosis and monitoring of patients with epilepsy and sleep disorders.

The purpose of these integrated circuits is to sense biosignals with high fidelity and low power consumption. This is because biophysical signals are, in general, very weak (in the range of a few  $\mu$ V to mV) as can be seen in Figure 1, which leads to noise related concerns. These types of devices are also battery operated which makes low power consumption critical to reduce battery size, extend operating hours and minimize heat dissipation [8]. To address these critical concerns, this thesis project proposes circuits built with transistors operating in weak inversion

1

(subthreshold) that allow for the implementation of systems working below the microwatt range with low levels of input referred noise [5].

The analog front-end (AFE) amplifier plays a crucial role in biosensor integrated circuits because it usually determines the signal-to-noise ratio (SNR) of the entire neural recording system; therefore it is the most important component to ensure reliable monitoring of neural signals [3].

This thesis presents a low power, analog front-end amplifier and filter for use in neural measuring and recording applications. The proposed integrated circuit is intended for Electroencephalogram (EEG) applications in which, as shown in Figure 1, the biopotential signals vary in magnitude from  $1\mu$ V to  $100\mu$ V and in frequency from ~1-100Hz. It should also be noted and taken into account the interference at 60Hz from the power lines, which appear in the middle of the band of interest making it difficult to filter out.

Figure 1. Frequency and amplitude ranges of different biopotential signals [7].

Figure 1 shows the frequency and amplitude ranges of a few biopotential signals that are encountered in common measurements such as the Electrocardiogram (ECG) –which measures cardiac signals; the Electroencephalogram (EEG) –which measures electrical signals from groups of neurons in the brain, right at the scalp; the Electromyogram (EMG) –which measures the electric signals that make muscles contract; and the Electrooculogram (EOG) –which measures electric charge difference between the front and back of the eye and is then correlated with eye movement. One can also observe a higher amplitude type of signal beginning around 1 KHz, called Action Potential (AP) or Neural Spike, this is an undesired signal for the Electroencephalogram measurement and therefore needs to be attenuated and filtered out.

Before diving into the following chapters dealing with the design of the circuits proposed in this thesis, let us first cover brief information on the electroencephalogram measurement, what it is, its uses, and applications; as well as review of the types of circuits used in the system presented in this thesis, such as the operational transconductance amplifier and the  $G_m$ -C filter.

#### **Background Information**

#### The Electroencephalogram (EEG)

The electroencephalogram (EEG) reflects the electrical activity of the brain as recorded by placing several electrodes on the scalp. The EEG is widely used for diagnostic evaluation of various brain disorders such as determining the type and location of the activity observed during an epileptic seizure, as well as for the study of sleep disorders such as: insomnia, hypersomnia, circadian rhythm disorders, and parasomnia. The brain activity may also be recorded during surgery by attaching the electrodes directly to the uncovered brain surface; the resulting invasive recording is named an electrocorticogram (ECoG) [14].

3

Another application for the EEG is of particular interest and is currently the research focus of many neuro scientists —brain-computer interface (BCI). Such an interface enables a subject to communicate with and control the external world without using the brain's normal output through peripheral nerves and muscles [22-24]. This type of interface significantly benefits subjects with severe neuromuscular disorders by allowing them to operate a neuroprothesis [14].

The clinical EEG is commonly recorded using a standardized system for electrode placement, called the International 10/20 system. This particular recording system employs 21 electrodes attached to the surface of the scalp at locations defined by certain anatomical reference points; the numbers 10 and 20 are percentages signifying relative distances between different electrode locations on the skull perimeter. Bipolar as well as unipolar electrodes are used in clinical EEG acquisition. Bipolar electrodes require a reference electrode either distantly or taken as the average of all electrodes [14]. A map of the electrode placement is shown in Figure 2.

Figure 2. The International 10/20 system for recording of clinical EEGs. The anatomical reference points are defined as the top of the nose (nasion) and the back of the skull (inion). The letters F, P, C, T, O, and A denote frontal, parietal, central, temporal, occipital, and auricle, respectively. Note that odd-numbered electrodes are on the left side, evennumbered electrodes are on the right side, and z (zero) is along the midline [14].

In their book, *Bioelectrical Signal processing in Cardiac and Neurological Applications*, the authors explain that studies have indicated that the total number of electrodes used in the brain mapping applications should be 64 or higher in order to provide sufficient detail [14]. This statement leads to the conclusion that the International System, which consists of 21 electrodes, although minimal for clinical acquisition is not adequate for high quality recordings.

The measured signals at the scalp often exhibit oscillatory, repetitive behavior and may be referred to as rhythms. These brainwave signals, or rhythms, in the EEG range (1–100Hz) can be broken down as shown in Figure 3:

Figure 3. Examples of the different kinds of rhythms observed in an EEG.

**Delta rhytm**, **<4Hz**. The delta rhythm is typically seen during deep sleep and it is characteristic of having a large amplitude. It is usually not observed in the awake, normal adult, but is indicative of cerebral damage or brain disease (encephalopathy).

**Theta rhythm, 4-7 Hz.** The theta rhythm occurs during certain stages of sleep, as well as when a person is drowsy.

Alpha rhythm, 8-13 Hz. The alpha rhythm is most noticeable in normal subjects who are relaxed and awake with their eyes closed; this brain rhythm is suppressed when the eyes are open. The amplitude of the alpha rhythm is largest in the occipital regions.

**Beta rhythm, 14-30 Hz.** The beta rhythm is fast with and has a low amplitude, it is associated with an activated cortex and it can be observed during certain sleep stages. The beta rhythm is mainly observed in the frontal and central regions of the scalp.

Gamma rhythm, >30 Hz. The gamma rhythm is related to a state of active information processing of the cortex. Using an electrode located over the sensorimotor area and connected using high-sensitivity recording techniques, the gamma rhythm can be observed during finger movements.

The clinical interpretation of the EEG has evolved into a discipline in its own right, where the human interpreter has to draw conclusions based on the frequency, amplitude, morphology, and spatial distribution of the brain waves. The EEG remains a very powerful tool in the diagnosis of many diseases such as epilepsy, sleep disorders, and dementia. It also remains important for real-time monitoring of patients in a coma or with encephalopathy. The technical demands on equipment for recording EEGs are relatively modest and are, for a basic recording setup, restricted to a set of electrodes, a signal amplifier, and a personal computer for data

6

storage, signal analysis, and graphical presentation [14]. Figure 4 gives an illustration of the typical stages followed for this type of signal acquisition.

Figure 4. Block diagram describing the main steps in biomedical signal acquisition for analysis. The signal is often processed at the time of acquisition, but may also be stored on a local hard disk or a server on the web for later retrieval and processing [14]. This thesis focuses on the first block of the diagram (acquisition of the EEG).

#### The Operational Transconductance Amplifier (OTA)

The most important building block of the circuit designed in this project is the Operational Transconductance Amplifier (OTA). This type of amplifier is a device that generates a current as its output, as a function of the difference between two input voltages  $V_1$  and  $V_2$ ; that difference is called the differential input voltage. This circuit is also called a *differential transconductance amplifier*. An ordinary *conductance* circuit turns a voltage difference across two terminals into a current through the same two terminals. A *transconductance* circuit turns a voltage difference and the circuit into a current somewhere else in the circuit. In the transconductance amplifier, a voltage difference between two inputs created a current as the output. [25]

The differential transconductance amplifier is used in all the parts of the circuit designed in this project, it is used at the front end as an Operational Transconductance Amplifier with a high open-loop gain, and it is used several times, in a different configuration, in the filter. To understand the operation of such circuits and the neural amplifier as a whole, it is important to understand the idea of how a basic differential transconductor amplifier works.

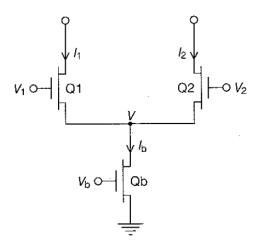

First, let us discuss the differential pair, shown in Figure 5. This circuit is used as an input stage in which transistor Qb is used as a current source and its current  $I_b$  is normally saturated at a value set by the bias voltage  $V_b$ . This bias current is then divided between Q1 and Q2 as a function between the difference in the voltages  $V_1$  and  $V_2$  where the input is applied.

Figure 5. A schematic of the differential pair input stage [25]

The saturated drain current  $I_{sat}$  is given by the following equation, where  $I_0$  and  $\kappa$  are constants.

$$I_{\text{sat}} = I_0 e^{\kappa V_{\text{g}} - V_{\text{s}}} \tag{1}$$

If equation (1) is then applied to transistors Q1 and Q2, one obtains

$$I_1 = I_0 e^{\kappa V_1 - V}$$

and  $I_2 = I_0 e^{\kappa V_2 - V}$

Applying Kirchoff's current law to node V, yields

$$I_{\rm b} = I_1 + I_2 = I_0 e^{-V} \left( e^{\kappa V_1} + e^{\kappa V_2} \right)$$

Solving this equation for  $e^{-V}$  and substituting it in the equations obtained for  $I_1$  and  $I_2$ , yields

$$I_1 = I_b \frac{e^{\kappa V_1}}{e^{\kappa V_1} + e^{\kappa V_2}} \quad \text{and} \quad I_2 = I_b \frac{e^{\kappa V_2}}{e^{\kappa V_1} + e^{\kappa V_2}}$$

(2)

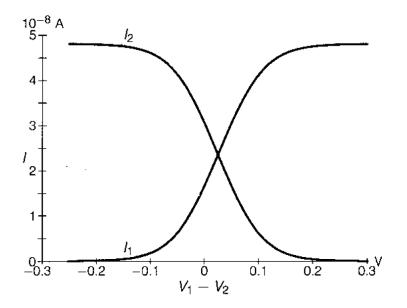

From these two equations (2) for  $I_1$  and  $I_2$  one can see that if  $V_1$  is more positive than  $V_2$  by many  $kT/(q\kappa)$ , transistor Q2 gets turned off, which makes all the current flow through Q1, the current on Q2 is approximately equal to zero and the current  $I_1$  is approximately equal to  $I_b$ . The same behavior can be observed on the other side, where if  $V_2$  is more positive tan V1 by many  $kT/(q\kappa)$  then transistor Q1 gets turned off, which makes all the current flow through Q2, making the current on Q1 approximately equal to zero and the current  $I_2$  approximately equal to  $I_b$ . This behavior can be observed graphically in Figure 6, where, as an example, the currents  $I_1$  and  $I_2$  and plotted as a function of the differential input voltage  $V_1$ - $V_2$ .

Figure 6. A graphical example of the currents I<sub>1</sub> and I<sub>2</sub> as a function of the input differential voltage V<sub>1</sub>-V<sub>2</sub>. Note that the curves do not cross at zero differential input voltage due to mismatch between Q1 and Q2 [25].

Furthermore, if one takes the difference of currents  $I_1$  and  $I_2$  as many of the differential transconductance amplifiers do to generate an output current that is proportional to it, we get

$$I_1 - I_2 = I_b \frac{e^{\kappa V_1} - e^{\kappa V_2}}{e^{\kappa V_1} + e^{\kappa V_2}}$$

Then, if one multiplies the numerator and denominator by a factor of  $e^{-(VI + V2)/2}$  the difference equation can be expressed as

$$egin{aligned} I_1 - I_2 &= I_\mathrm{b} rac{e^{\kappa (V_1 - V_2)/2} - e^{-\kappa (V_1 - V_2)/2}}{e^{\kappa (V_1 - V_2)/2} + e^{-\kappa (V_1 - V_2)/2}} \ &= I_\mathrm{b} anh rac{\kappa (V_1 - V_2)}{2} \end{aligned}$$

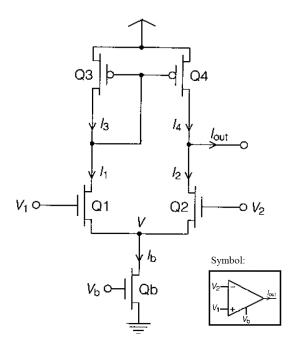

The hyperbolic tangent function obtained in equation exhibits the actual real-world behavior of the amplifier output current. The *tanh* function goes through the origin with a slope of one, becomes +1 for large positive numbers and it becomes -1 for large negative numbers. Figure 7 shows a simple transconductance amplifier, which is the basis of many of the circuits presented in this thesis.

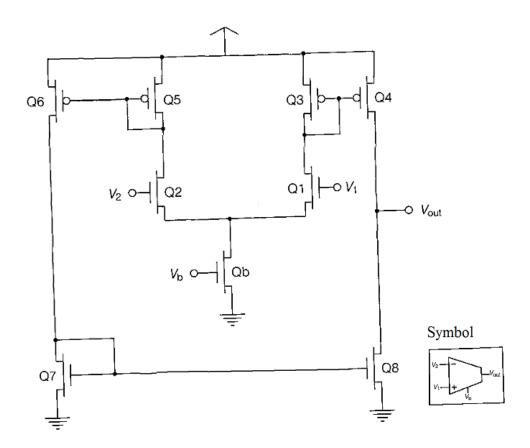

Figure 7. Simple Transconductance Amplifier and its symbol [25]

The circuit of the simple transconductance amplifier in Figure 7 consists of a differential pair just like the one shown in Figure 5 with a current mirror cascoded on top of it. The current mirror is used to subtract the currents of the differential pair  $I_1$  and  $I_2$ , it does this by reflecting the current  $I_1$  to Q4, which makes the output current  $I_{out}$  equal to  $I_1$ - $I_2$ , given by the equation derived previously

$$I_1 - I_2 = I_b \tanh \frac{\kappa (V_1 - V_2)}{2}$$

(3)

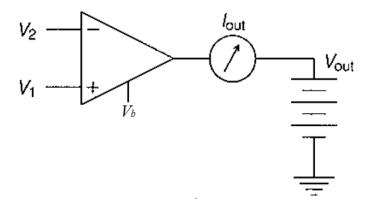

To verify this behavior, one can measure the output current of the amplifier as a function of the differential input voltage by keeping the output voltage midway between  $V_{DD}$  and ground, as shown in Figure 8.

Figure 8. Set up to measure output current as a function of the differential input voltage. The ideal current meter should have zero resistance. V<sub>out</sub> is held midway between V<sub>DD</sub> and ground [25]

Figure 9 shows the output current plotted as a function of the differential input voltage. One can observe that the curve closely exhibits the expected behavior of the hyperbolic tangent function. Also, one can determine the effective value of  $kT/(q\kappa)$  by extrapolating the slope of the curve at the origin to the two asymptotes. The difference between the positive and negative intercepts should be  $4kT/(q\kappa)$  [25].

Figure 9. Output current of the transconductance amplifier as a function of the differential input voltage. [25]

For the example curve shown in Figure 9, using the procedure mentioned, one can determine that  $kT/(q\kappa)$  for this particular example is approximately 43mV, which gives  $\kappa$  as approximately 0.58. The transconductance, G<sub>m</sub>, of the amplifier is defined as the slope of the *tanh* function at the origin in the equation for the output current. From Figure 9, one can determine that G<sub>m</sub> is approximately 560nS. The transconductance of the amplifier is defined as the slope determine that G<sub>m</sub> is approximately 560nS. The transconductance of the amplifier is defined as the change in the output current divided by the change in the differential input voltage, the equation for G<sub>m</sub> is then

$$G_{\rm m} = \frac{\partial I_{\rm out}}{\partial V_{\rm in}} = \frac{I_{\rm b}}{2kT/(q\kappa)} \tag{4}$$

Now let us consider the case when the output voltage is not held constant as in Figure 8. Let us plot the output current, but this time, as function of the output voltage. This is shown in Figure 10, where one can observe the limitations of this circuit due to transistor mismatches, transistors coming out of saturation, as well as the finite slope of the drain curves in saturation [25].

Figure 10. Output current as a function of the output voltage. [25]

Figure 10 shows that the output current decreases as the output voltage increases. The decrease in the output current per change in the output voltage is called the output conductance, G<sub>out</sub>, of the circuit and is given by equation (5):

$$G_{\rm out} = -\frac{\partial I_{\rm out}}{\partial V_{\rm out}} = \frac{\partial I_2}{\partial V_{\rm out}} - \frac{\partial I_4}{\partial V_{\rm out}}$$

(5)

The output conductance is the inverse of the output resistance of the circuit and it is the negative slope of the middle region of the plot in Figure 10. The output conductance, G<sub>out</sub>, is approximately 3.6nS from Figure 10. The open-circuit voltage gain of the circuit should be given then by the following equation:

$$A = \frac{G_{\rm m}}{G_{\rm out}} \quad or \quad A = G_{\rm m} R_{out} \tag{6}$$

Using the values we have obtained for  $G_m$  and  $G_{out}$ , the open-circuit gain of the simple transconductance amplifier example is A = 560nS / 3.6nS = 156.

Finally, let us consider the importance of the Early Voltage and how it affects the amplifier's gain. The slope of the saturated part of the drain curves of a given transistor has a

slope proportional to the current level transistor's drain curve in saturation. In other words, the  $V_{ds}$  intercept occurs at a voltage  $V_0$  (the Early Voltage) that is approximately independent of the current level [25].

$$rac{\partial I_{\mathrm{sat}}}{\partial V_{\mathrm{ds}}} pprox rac{I_{\mathrm{sat}}}{V_0}$$

As seen previously both  $G_{out}$  and  $G_m$  are proportional to the bias current, which makes the explicit dependence on the current level to cancel out and makes the voltage gain independent of the bias current. The change in current over the change in voltage can be expressed in terms of the Early Voltage values  $V_0$ .

$$\frac{1}{A} = \left(\frac{1}{V_{\rm N}} + \frac{1}{V_{\rm P}}\right)\frac{2}{\kappa} \tag{7}$$

In equation (7),  $V_N$  is the Early Voltage for Q2 and  $V_P$  is the Early Voltage for Q4, and both are expressed in kT/q units. This equation allows one to compute the gain of any output stage composed of complementary n and p channel transistors. Because the Early voltage  $V_0$  of a given transistor is proportional to its length [25], one can make the gain of the amplifier randomly high by increasing the length of the output transistors and sacrificing silicon area in the chip.

Figure 11 shows an improved version of the transconductance amplifier shown in Figure 7. This circuit has current mirrors on both sides of the differential pair, and an extra one on the further leg from the output to achieve the differential output current  $(I_1-I_2)$  of the transconductance amplifier. Such circuit is used by Harrison in the neural amplifiers presented in [1] and [2].

Figure 11. Wide Range Transconductance Amplifier with NMOS differential input pair. [25]

The major advantage of this wide-range amplifier over the simple transconductance amplifier is that it does not have the limitations that the simple one has; in this circuit, both input and output voltages can run almost up to  $V_{DD}$  and almost down to ground, without affecting the operation of the circuit [25].

#### The G<sub>m</sub>-C Filter

The filter is a critical building block in any biosignal acquisition system, it is needed not only to enhance the quality of the signal but to add selectability to the system. Signals in biopotential acquisition systems, as mentioned before, are very weak which makes them especially susceptible to noise. The type of filter used in the system presented in this thesis is a G<sub>m</sub>-C Filter, meaning it is made up of transconductors and capacitors. This kind of circuit is an analog continuous-time filter, as well as active—meaning it uses power.  $G_m$ -C filters are suitable for applications with frequencies less than 100MHz, which is the case of the system presented here, where the EEG band is 1-100Hz as seen before in Figure 1.

In comparison with discrete-time switched-capacitor filters such as those used in digital systems, continuous-time filters possess the advantage of lower power consumption, since they only drive capacitive loads, as well as not having the switching noise that the switched-capacitor filters inherently have. Among all continuous-time filters, the G<sub>m</sub>-C topology appears to be the most reasonable choice for integrated circuits [20], where it is hard to achieve specific inductor values to construct LC passive filters. In G<sub>m</sub>-C filters, the cutoff frequency is proportional to the transconductance g<sub>m</sub>, which allows a low-power implementation for the acquisition of low frequency biopotential signals. G<sub>m</sub> has to be minimized in order to achieve an ultra-low cutoff frequency with a reasonable area and power [20].

To achieve performance on a  $G_m$ -C filter it is important for the transconductor to behave as an ideal operational transconductance amplifier, it should have a very high gain, as well as have a very high input and output resistance, ideally infinite, as seen in Figure 12. In essence, the transconductor operates as a voltage-controlled current source, where the output current is:

$$i_o = G_m v_i \tag{8}$$

Transconductor

This is important because as explained before, because  $G_m$  needs to be low to achieve the low cutoff frequencies needed in these type of applications, the output resistance of the transconductor needs to be very high to achieve a high gain.

Let us take a look at a very simple single pole circuit that behaves as a  $G_m$ -C low pass filter, such as the one shown in Figure 13.

Figure 13. Simple single pole Gm-C low pass filter

To obtain the transfer function of the circuit shown in Figure 13, let us begin by applying Kirchoff's Current Law at the output node  $v_o$ , where the impedance of the capacitor is 1/sC:

$$\frac{v_o - 0}{1/_{SC}} - i_o = 0$$

As explained before, the operational transconductor amplifier behaves as a voltage controlled current source, of which the output current is a function of the differential input voltage. This is expressed with the following equation:

$$i_o = G_m(v_i - v_o)$$

Substituting this equation in the previous equation, one gets

$$\frac{v_o - 0}{1/_{SC}} - G_m(v_i - v_o) = 0$$

Solving for the transfer function  $v_o / v_i$  yields

$$\frac{v_o}{v_i} = \frac{\frac{G_m}{C}}{s + \frac{G_m}{C}} = \frac{\omega_0}{s + \omega_0}$$

From the obtained transfer function, we can observe that it is the same as a single order system transfer function and that the circuit behaves as a single pole low pass filter, where the cutoff frequency is  $\omega_0 = G_m/C$ . The gain plot of the frequency response of this circuit is shown in Figure 14.

Figure 14. Frequency response dB gain plot of the simple single pole G<sub>m</sub>-C low pass filter

In a similar manner Chapter V will present how this theory is applied to the design of a  $3^{rd}$  order Butterworth  $G_m$ -C filter that meets the frequency needs of the system.

## **Thesis Structure**

The following chapters of this Thesis are organized as follows, Chapter II presents and reviews relevant published literature on the subject matter related to this Thesis; Chapter III explains the  $g_m/I_D$  methodology used in the design of the circuits presented, as well as its importance, application, and relevance to the system; Chapter IV is dedicated to explaining how the methodology described in Chapter II to was used to design the front-end OTA; Chapter V is dedicated to the description of the design of the G<sub>m</sub>-C Filter used in the system; Chapter VI

presents the simulation results and comparison of the system to similar published works; and finally, Chapter VII gives a conclusion and provides suggestions and details for future work on this project.

Before we continue to the following chapters, let us take a look at the overall system architecture of the system proposed in this thesis for the neural amplifier. This diagram can be seen in Figure 15 and is composed of the analog front-end Operational Transconductance amplifier (OTA), which will need something at the input to block the DC offsets created at the scalp. It will be connected in a negative feedback configuration for stability and to achieve the desired gain. A 3<sup>rd</sup> order Butterworth Low Pass G<sub>m</sub>-C Filter will follow the operational transconductance at the front end and it will have a proper cutoff frequency for the EEG band that will also be enough to attenuate the Neural Spikes described in Figure 1, which are present beginning at 1 kHz. A capacitive load will be used to simulate the next system in the signal acquisition diagram shown in Figure 4, such as an analog to digital converter.

Figure 15. Overall system diagram for the Neural Amplifier analog front-end integrated circuit. The system consists of a unit to block the DC offsets created at the scalp, the OTA with its closed-loop feedback and bias to achieve the desired gain, a filter to capture the signals in the desired band and attenuate Neural Spikes, and finally a load to simulate the next block in the acquisition system such as an analog to digital converter.

### CHAPTER II

### LITERATURE REVIEW

Increasing interest and advances in neuroscience over the past decade, as mentioned in Chapter I, have led to the need for development, as well as, improvement of circuits to utilize in neural recording applications such as the EEG. This chapter focuses on reviewing a few of the neural amplifiers published in literature in the last decade, especially those scholar publications relevant to this thesis project. A comparison between these published works and the system presented in this manuscript will be presented in Chapter VI.

There have been a significant amount of neural amplifiers published in literature in recent years, most of which aim at low-noise and low power [1-8]. For a better comparison among these published circuits, as well as to aid in the understanding of their efficiency, a figure of merit, called Noise Efficiency Factor (NEF), was introduced in by Steyaert, Sansen, and Zhongyuan in [12]. The NEF compares the power-noise tradeoff among amplifiers and it is widely used to compare neural-amplifier designs. The noise efficiency factor is defined as:

$$NEF = V_{rms, in} \sqrt{\frac{2 \cdot I_{tot}}{\pi \cdot U_T \cdot 4kT \cdot BW}}$$

(9)

where  $V_{rms}$  is the total equivalent input noise,  $I_{tot}$  is the total current consumed by the system,  $U_T$  is the thermal voltage KT/q ( $\approx 25$ mV at room temperature), k is Boltzmann's constant, T is the temperature in Kelvin, and BW is the bandwidth of the system.

One of the reasons for choosing to use the Capacitive Feedback Network (shown in Figure 16) for the neural amplifier proposed in this manuscript, comes from a recent publication titled, "*A review of low-noise amplifiers for neural applications*" [9] where the authors present a comparative study of three topologies for neural recording applications: Capacitive Feedback Network (CFN), Miller Integrator Feedback Network (MIFN), and Capacitive Amplifier Feedback Network (CAFN). These configurations are some of the more common topologies presented in literature. In the study made by the authors in [9], these three topologies are analyzed in terms of area, power consumption and noise performance. The authors come to the conclusion that "based upon theoretical developments and transistor-level explorations, [the study] reveals that the [Capacitive Feedback Network] CFN achieves the best performance in terms of area and power consumption for a given input-referred noise specification." [9]

Figure 16. Capacitive Feedback Network for neural amplifier [9]

This simple structure has a bandpass shaped frequency response, on which one can achieve a desired mid-band gain, as well as the desired low and high cutoff frequencies by picking the values of the input capacitor  $C_i$ , the feedback capacitor  $C_f$  and resistor  $R_f$ , and the load capacitor  $C_L$ . This behavior is dependent on having an operational transconductance

amplifier with a very high open-loop gain and a very high output resistance, and one where its transconductance is given by the transconductance of one of its input transistors.

A pioneer publication that has been a reference, not only to this project, but that has been cited multiple times by most of the researched papers reviewed during this research project is the *"Low Power Low Noise Amplifier for Neural Recording Applications*" presented by Harrison in 2002 [1] along with a similar follow-up paper that was published a year later in 2003 by Harrison and Charles [2]. The neural amplifier presented by Harrison and Charles utilizes the Capacitive Feedback Network mentioned before; the configuration presented in this research paper is shown in Figure 17. In this neural amplifier, a wide-range current mirror Operational Transconductance Amplifier, such as the one shown in Figure 11, is utilized. This type of circuit is not very power and noise efficient as much of the current that it draws is wasted in the current mirrors. The neural amplifier proposed by Harrison and Charles in [1, 2] has a dual supply voltage of  $\pm 2.5$  V and consumes 180 nA of current, which yields a 900 nW power consumption. The authors also report that amplifier has a measured gain of 39.8 dB and a bandwidth of 14 mHz - 30 Hz; an input-referred noise of 1.6uVrms was measured on this device, yielding a NEF of 4.8. The amplifier was built in a 1.5um CMOS technology and occupies a chip area of 0.22mm<sup>2</sup>.

Figure 17. Theoretical Capacitive Feedback Network neural amplifier proposed by Harrison and Charles in [1, 2] on which two series diode-connected pMOS act as the Rf resistors

In [1, 2] the authors use pseudo-resistors made with a couple of MOS-bipolar devices joined as diode-connected pMOS transistors to replace the  $R_f$  resistors in Figure 17. Two of this devices as connected in series to reduce distortion for large output signals. The authors mention that "with positive V<sub>GS</sub>, the parasitic source-well-drain p-n-p bipolar junction transistor (BJT) is activated, and the device acts as a diode-connected BJT" [2]. The authors claim to have measured a resistance greater than  $10^{11} \Omega$  for small voltage changes across the pseudo resistors. The proposed neural amplifier with Capacitive Feedback Network and the diode-connected pseudo-resistors is shown in Figure 18.

If one looks at the operational transconductance amplifier used in the neural amplifier proposed in [1, 2], shown in Figure 18, and compares it with the one shown in Figure 11, one can observe that the circuit proposed in [1, 2] uses pMOS transistors instead of nMOS transistors for the differential input pair. This is because a major concern for a low-frequency circuit, whose main purpose is to have low noise, is flicker noise (also called 1/f noise). The authors explain that, "flicker noise in pMOS transistors is typically one to two orders of magnitude lower than flicker noise in nMOS transistors as long as  $|V_{GS}|$  does not exceed the threshold voltage" [2].

Figure 18. The neural amplifier configuration and the OTA proposed by Harrison and Charles in [1, 2]

A second reference research publication of particular importance to the research project presented in this manuscript is the "*Energy-Efficient Micropower Neural Recording Amplifier*" [6] proposed by Wattanapanitch, Fee, and Sarpeshkar in 2007. In it, the authors propose a novel folded cascode topology for the operational transconductance amplifier, shown in Figure 19, which they claim appears to be the lowest power and most energy-efficient neural recording amplifier reported to date (2007). A modified version of this folded cascode topology for the operational transconductance amplifier was adopted in the research project presented in this manuscript. In the research paper [6] the authors report that their proposed amplifier, when configured to measure Local Field Potentials (EEG range), uses a 2.8 V supply voltage and consumes 743 nA of current, which yields 2.08  $\mu$ W of total power consumption. They also claim that their proposed amplifier achieves a mid-band gain of 40.9 dB over a bandwidth ranging from 392 mHz to 295 Hz. An input-referred noise of 1.66 $\mu$  V<sub>rms</sub> was measured on this device, corresponding to a NEF of 3.21. This energy-efficient micropower neural amplifier was built in AMI's 0.5  $\mu$ m CMOS process and occupies a chip area of 0.16mm<sup>2</sup>.

Figure 19. The neural amplifier configuration and the OTA proposed by Wattanapanitch, Fee, and Sarpeshkar in [6]

We can observe from Figure 19 that the authors in [6] also use the Capacitive Feedback Network topology for their neural amplifier. In this design, however, the authors use a band-pass filter after the front-end amplifier, which can be tuned with an external voltage  $V_{tune}$ , to adjust the frequency range to measure different type of signals. The reader should note that this bandpass filter is made up of a high-pass filter that uses a capacitor *C* and a pseudo-resistor like the ones presented by Harrison and Charles in [1, 2] followed by a simple  $G_m$ -C low pass filter just like the one presented in the example in Chapter I. The folded cascode topology for the operational transconductance amplifier used in the circuit is also shown in Figure 19. In this circuit, the authors use a severe  $1/16^{\text{th}}$  current scaling as well as 17 source-degenerated current mirrors for the current mirrors made up by transistors  $M_{c3}$ ,  $M_5$ , and resistors  $R_3$  and  $R_1$ .

A more recent publication made in 2012 (this thesis project was started in the Fall of 2012) by Liu, Zou, Goh, Ramamoorthy, Dawe, and Je describes an "800nW neural recording amplifier with enhanced noise efficiency factor" [3]. This amplifier uses a very low 1 V power supply and consumes a total current of 160 nA, yielding a 160 nW power consumption. This amplifier has a gain of 40 dB similar to the other systems reviewed in this chapter, as well as most of the amplifiers in literature, and a bandwidth of 200 mHz to 430 Hz; an input-referred noise of  $5.71 \,\mu$ V<sub>rms</sub> was measured on this device, corresponding to a very good NEF of 2.59. The amplifier was built in a 0.18 $\mu$ m CMOS technology and occupies a chip area of 0.05mm<sup>2</sup>. The neural amplifier used, is shown in Figure 20. One can observe in this figure that the authors use a fully differential configuration for the amplifier, as well as a Capacitive Feedback Network similar to the ones in the publications reviewed in this chapter. The fully differential structure helps to reduce the effect of the common mode noise [3]. The front-end amplifier is

then followed by a bandpass filter that provides additional gain; details are not given by the authors on the structure of the filter nor are details given on the bias circuits and currents needed. This last point will become particularly important in Chapter VI where a comparison between the system proposed in this thesis and several of the amplifiers reviewed in this chapter is made. When presenting their results, particularly current consumption, most authors in the publications that were reviewed during this research come to the conclusion that this is not reported because bias circuits can be shared by many parts of the integrated circuit, although this statement is true, it is important to establish how such currents are sourced because it can be done with numerous different types of bias circuits, some of which are more power efficient than others.

Figure 20. The proposed neural amplifier and OTA [3]

Finally, a comprehensive overview in the topic of neural recording systems is summarized and explained in a recent publication by Gosselin titled "*Recent Advances in Neural Recording Microsystems*" [19]. This research paper describes the most relevant developments made in this area and gives insight to the approaches taken by several researchers to tackle problems in neural recording and acquisition systems. This journal paper examines most of the circuit topologies presented in this chapter and provides a comparison between the most power and noise efficient operational transconductance amplifier structures that constitute the core of most of the neural amplifiers published to date, discussing their characteristics and advantages. This publication is extensive and particularly useful since it has reviewed 106 research publications related to neural recording microsystems published in the past 30 years.

Now that we have reviewed some of the neural amplifiers in literature, described the techniques used in these circuits, and established a concise figure of merit, in the NEF, to adequately compare these designs. It is time to describe the design of the neural amplifier proposed in this thesis project, beginning with the methodology used in the circuits.

### CHAPTER III

## THE g<sub>m</sub>/I<sub>D</sub> METHODOLOGY

As explained in previous chapters, it is imperative for the neural amplifier's circuits to achieve high efficiency and low power. To be able to achieve these criteria, a transistor characterization methodology, known as  $g_m/I_D$ , was applied; the theory and application to the circuits in this project is described in this chapter. This methodology's importance to the thesis project presented in this manuscript comes from the fact that it was used as a sizing tool to help determine the sizes of the transistors, making them operate in a desired region that is power efficient, such as the subthreshold region. This design method was originally introduced and explained in detail by Silveira, Flandre, and Jespers in their publication to the synthesis of a silicon-on-insulator micropower OTA" [11].

In this publication, the authors define the  $g_m/I_D$  methodology as "a new design methodology that allows a unified synthesis methodology in all regions of operation of the MOS transistor." Furthermore, they explain that their method, "provides an alternative [to traditional analysis methods] taking full advantage of the moderate inversion region to obtain a reasonable speed-power compromise. The method exploits the transconductance over DC drain current ratio  $(g_m/I_D)$  relationship versus the normalized current  $[I_D/(W/L)]$ " [11].

28

Why use the  $g_m/I_D$  method? Well, the authors argue that the choice of  $g_m/I_D$  is based on its relevance for the following three reasons:

1) It is strongly related to the performances of analog circuits

- 2) It gives an indication of the device operating region.

- 3) It provides a tool for calculating the transistors dimensions.

The  $g_m/I_D$  ratio is also referred to as the transconductance efficiency and it is a measure of how efficiently a transistor translates current (hence power) into transconductance. This means that the higher the value of this ratio, the higher the transconductance obtained is at a constant value [11]. It is used because for deep submicron processes and subthreshold region of operation, analytical or hand methods for synthesizing analog circuits rely on classic square law model equations that are no longer accurate and useful in describing the behavior of the transistor in all regions of operation and therefore not good for design purposes.

The authors in their journal paper [11] define  $g_m/I_D$  as the derivative of the logarithm of the normalized I<sub>D</sub> with respect to V<sub>G</sub> as shown in equation (10):

$$\frac{g_m}{I_D} = \frac{1}{I_D} \frac{\partial I_D}{\partial V_G} = \frac{\partial (\ln I_D)}{\partial V_G} = \frac{\partial \left\{ \ln \left[ \frac{I_D}{\left( \frac{W}{L} \right)} \right] \right\}}{\partial V_G}$$

(10)

Equation (10) will be used to obtain the plots that indicate the transistor's mode of operation. But first, let us consider the dependence of  $g_m/I_D$  on the transistor size since one needs to specify transistor sizes to characterize the transistors through simulation. The authors state that the normalized current  $I_D/(W/L)$  as well as the  $g_m/I_D$  ratio are independent of the transistors size. This means that the relationship between " $g_m/I_D$  and the normalized current is a unique

characteristic for all transistors of the same type (nMOS or pMOS) in a given batch" [11]. In other words,  $g_m/I_D$  is a universal characteristic governing all the transistors that belong to the same technology or process.

### Obtaining the plot of $g_m/I_D$ vs. $I_D/(W/L)$ for NMOS and PMOS

The  $g_m/I_D$  design methodology is based on measuring, or more specifically characterizing the transistor through simulation and using the different plots obtained as lookup tables in the design process to size the transistors in a way that they achieve the desired currents (and therefore the desired power consumption) at the required bias voltages.

Because the system was aimed at low power it was decided that a low voltage process should be used instead of a traditional 5V digital process used in introductory academic VLSI classes. The lowest voltage and smallest process available to me for the implementation of the design was a 2.5 V TSMC process, however since this specification is only a limit, it was decided that 1.8V could be used in that same process. The Spice TSMC 25 models given in Appendix A for both NMOS and PMOS transistors, for the 300nm TSMC process in use, were obtained from wafer test data for a similar process provided by MOSIS (www.mosis.com). Using equation (10) for  $g_m/I_D$  and these transistor models, the circuits in Figures 21 and 23 were simulated to characterize the transistors in this technology and obtain the desired plots.

In the test circuit shown in Figure 21,  $V_{DS}$  was held at  $V_{DD}/2$  since there is not a lot of variation for any changes in  $V_{DS}$ ;  $V_{GS}$  is swept from 0V to  $V_{DD}$  (1.8V). This simulation will yield a plot of  $I_D$  vs.  $V_{GS}$  which one can turn into a plot of  $g_m/I_D$  vs.  $V_{GS}$  with the help from the trace calculator in PSpice and the equation for  $g_m/I_D$ .

30

Figure 21. Test circuit to characterize the NMOS transistor in the 300nm TSMC process.

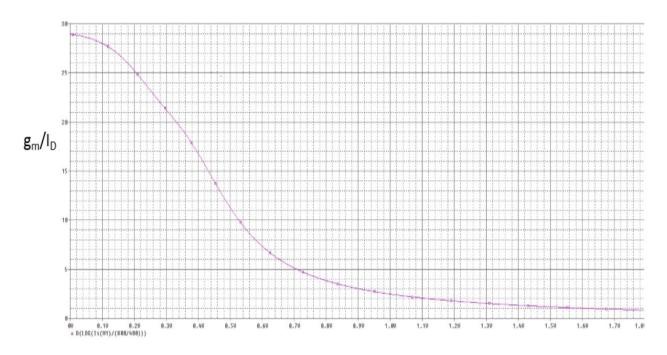

Figure 22 below shows the obtained  $g_m/I_D$  vs. V<sub>GS</sub> plot for the NMOS in the 300nm TSMC process.

Figure 22.  $g_m/I_D$  vs. V<sub>GS</sub> curve for NMOS with TSMC 25 transistor model

31

In a similar manner, the PMOS was characterized using the circuit shown in Figure 23. For the PMOS V<sub>DS</sub> was again held at V<sub>DD</sub>/2 and V<sub>SG</sub> was swept from 0V to V<sub>DD</sub> (1.8V). This simulation yielded a plot of I<sub>D</sub> vs. V<sub>GS</sub> which was turned into a plot of  $g_{m}/I_D$  vs. V<sub>SG</sub>, shown in Figure 24.

Figure 23. Test circuit to characterize the PMOS transistor in the 300nm TSMC 25 process.

Figure 24. g<sub>m</sub>/I<sub>D</sub> vs. V<sub>SG</sub> curve for PMOS with TSMC 25 transistor model

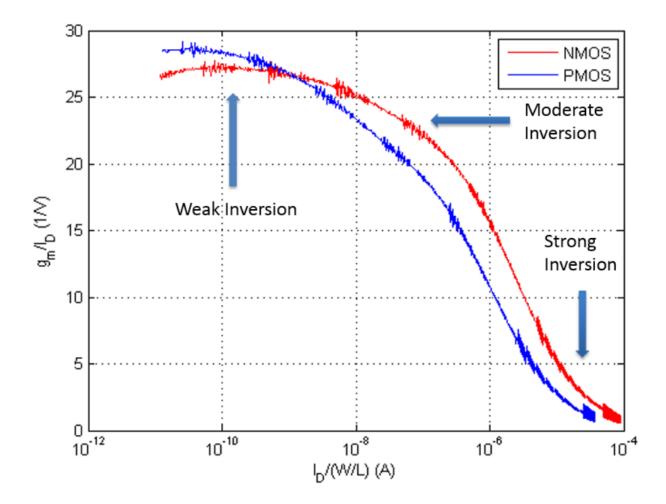

Using the obtained PSpice simulation plots of  $g_m/I_D$  vs. V<sub>GS</sub> and V<sub>SG</sub> respectively, the next step in the design process was to obtain the plot of  $g_m/I_D$  vs. the normalized current  $I_D/(W/L)$ . Exporting the data of I<sub>D</sub> and  $g_m/I_D$  from the two plots shown in Figures 22 and 24 to a numerical computation program such as MATLAB, one is able to normalize the current data and obtain the desired of  $g_m/I_D$  vs.  $I_D/(W/L)$ . This plot is shown in Figure 25 below.

Figure 25. Transconductor efficiency  $(g_m/I_D)$  vs. normalized current  $(I_D/(W/L))$  curves for NMOS and PMOS in the 300nm TSMC process using the TSMC 25 transistor model.

The significance of the plot shown in Figure 25 comes from the fact that it is also an indicator of the mode of operation of the transistor; one can observe that the derivative of  $g_m/I_D$  is maximum in the weak inversion region (subthreshold) where the I<sub>D</sub> dependence versus V<sub>G</sub> is

exponential while it is quadratic in strong inversion, becoming almost linear deeply in the strong inversion because of the saturation velocity [11].

From this plot determining the sizes of transistors becomes a straightforward exercise, for example, consider the case of an NMOS transistor desired to operate in weak inversion (subthreshold), where, from the plot  $g_m/I_D = 25 \text{ l/V}$ ; also let us say that in this hypothetical example, the current through this transistor is needs to be 100nA. Then, by looking at the plot in Figure 25, one can observe that the normalized current value corresponding to  $g_m/I_D = 25 \text{ l/V}$  is  $I_D/(W/L) \approx 10^{-8}$  or 10nA. Since the value of  $I_D$  needs to be 100nA one can see that

$$10 \text{ nA} = \frac{100 \text{ nA}}{W/L}$$

Arbitrarily choosing the length L of the transistor to be the minimum for the process L=300nm, for example, yields

$$W = \frac{100 \text{ nA}}{10 \text{ nA}} (300 \text{ nm}) = 300 \,\mu\text{m}$$

As a conclusion to this chapter, let us state and review the step by step transistor sizing procedure for the  $g_m/I_D$  methodology:

- 1) Determine bias current for the circuit and based on it determine currents on all branches

- Determine the region of operation desired for a given transistor according to circuit operation: subthreshold (weak inversion); linear (moderate inversion); saturation (strong inversion)

- 3) Using the obtained  $g_m/I_D$  vs.  $I_D/(W/L)$  plot, pick a value for  $g_m/I_D$  (Based on region of operation), read the corresponding normalized current  $I_D/(W/L)$ , using this value and the drain current through the transistor, solve for W/L

### CHAPTER IV

### OPERATIONAL TRANSCONDUCTANCE AMPLIFLIER DESIGN

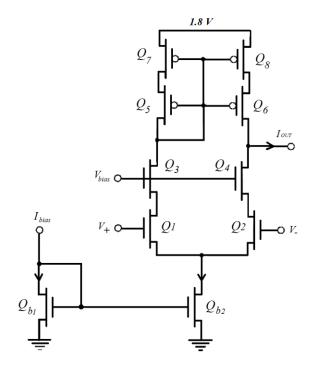

As we begin describing the components that make up the neural amplifier proposed in this project, this chapter focuses on the design of the operational transconductance amplifier used in the neural amplifier. It is important to remember that for the amplifier to function as an operational transconductance amplifier, its open-loop gain should be ideally infinite, however realistically it should be high enough so that its unity gain bandwidth is wide enough to encompass within it a pass band shaped response of ~40dB mid-band gain with bandwidth of 1-100 Hz as this will be the shape of the neural amplifier's closed-loop frequency response once the capacitive feedback is added.

Initially, a wide-range current mirror operational transconductance amplifier, such as the one presented in Chapter I (Figure 11), was chosen but this circuit was not able to meet the power consumption goals because, as explained in the Chapter II review, this topology is inherently not very power efficient as it wastes a lot of precious current in the two current mirrors that achieve its transconductance operation. Instead, the circuit topology for the operational transconductance amplifier was chosen to be similar to the one presented in [6] (described in Chapter II) because as stated in the review "*Recent advances in neural recording microsystems*" [19] presented in Chapter II, this topology is one of the more power efficient. Furthermore, this structure was modified to achieve a simpler OTA that would operate in a similar manner with a supplied bias current, as seen in Figure 26

35

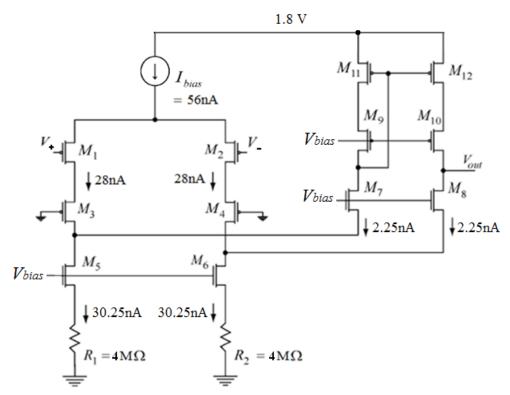

Using the plot of  $g_{m}/I_D$  vs.  $I_D/(W/L)$  obtained in Chapter III and a modified amplifier circuit topology similar to the one presented for the OTA in [6], the transistor sizes were determined based on the total bias current (chosen to be 56nA) and the individual currents through each transistor that was determined to be drawn from the 1.8V source to meet power consumption constraints. A simplified schematic of the amplifier is shown in Figure 26.

Figure 26. 108.9nW Folded Cascode Operational Transconductance Amplifier

#### The Bias Circuit for the OTA

The circuit in Figure 26 requires a bias circuit to provide the 56nA of current; to achieve this, a "*CMOS current reference without resistance*" was carefully chosen to be used; this circuit in shown in Figure 27 and was proposed by Oguey and Aebischer in [13]. The authors state that this bias circuit is ideal for sourcing currents from 1nA to 100nA and even though the bias circuit added to the amplifier makes it consume more than the 56nA of current, its power consumption

is not included in the power calculation of the entire system because one of this current sources can be shared by all the channels in a multi-channel neural amplifier system.

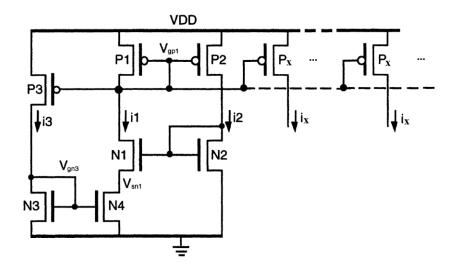

Figure 27. CMOS current reference proposed in [13]

The current is generated as soon as the power supply is turned on in the left part of the circuit in Figure 27 and then mirrored a couple of times. The current can be set by changing the sizes of transistors N1, N2, P1, and P2; and this current reference can be replicated and scaled as many times as needed with transistors,  $P_x$ , as shown in Figure 27. The sizes, determined through  $g_{nn}/I_D$  methodology, for the OTA and for the current reference are shown in Table I below.

| Transistor sizes (μm)             |         |        |                   |      |         |

|-----------------------------------|---------|--------|-------------------|------|---------|

| OTA                               | W       | L      | Current Reference | W    | L       |

| M <sub>1</sub> , M <sub>2</sub>   | 420.075 | 1.5    | N1                | 75   | 2.25    |

| M <sub>3</sub> , M <sub>4</sub>   | 140.025 | 1.5    | N2                | 4.05 | 2.25    |

| M <sub>5</sub> , M <sub>6</sub>   | 180.075 | 3      | N3                | 2.25 | 241.875 |

| M <sub>7</sub> , M <sub>8</sub>   | 3.525   | 1.5    | N4                | 2.25 | 363.075 |

| M <sub>9</sub> , M <sub>10</sub>  | 6       | 1.5    | P1, P2, Px        | 2.25 | 112.5   |

| M <sub>11</sub> , M <sub>12</sub> | 20.025  | 20.025 | P3                | 6.75 | 112.5   |

Table 1. OTA and Current Reference Transistor Sizes

Figure 28 shows the completed Cadence schematic of the OTA, including the bias circuit. Notice that the resistors shown in the schematic in Figure 26 are broken into four  $1M\Omega$  in series.

This was done for physical layout design purposes, more specifically so that the Layout vs Schematic (LVS) check passed.

Figure 28. The OTA with its 56nA current reference circuit.

# Design of the Amplifier's Physical Layout

The amplifier's physical layout was designed in the 300nm TSMC process as shown in Figure 29 below, it occupies an area of 474.75µm x 184.2µm. This layout also includes the bias circuit for the amplifier, which can be seen in the far left of Figure 29. It is important to note that in a multi-channel system where several amplifiers are needed, as is the common use for this type of circuits, only <u>one</u> bias circuit would be needed. This will be explained further in Chapter VI.

Figure 29. Amplifier Layout (including bias circuit) with an area of 474.75µm x 184.2µm

Circuits in this kind of applications and with this power consumption constraints consume currents that are several orders of magnitude smaller than other circuits. Having such small currents require bias resistors that are extremely large, which is impractical in an integrated circuit where area is a precious resource. Therefore, it is a much better approach to achieve the required small bias currents using only transistors, as these can be physically implemented very easily in the integrated circuit and also save a significant amount of chip area.

Resistors were made with polysilicon and silicide block due to the lack of a higher resistivity per square material in the TSMC 25 process. The 4 $\Omega$  resistors shown in Figure 26 were broken up and a unit 1M $\Omega$  resistor layout was made, then four of these were placed in series to achieve the 4M $\Omega$  resistance shown in the schematic (Figure 28). The physical layout of the eight unit resistors that make up the two 4M $\Omega$  resistors that are part of the amplifier circuit can be seen in the far right of the amplifier layout (Figure 29).

The layout for a single channel amplifier without the bias circuit would only occupy an area of approximately  $354 \mu m \times 184 \mu m$ .

## Simulation of the OTA

This section presents the simulated open-loop frequency response for both the schematic and layout of the operational transconductance amplifier designed in this chapter. Figure 30 shows the simulation results for the schematic (shown in Figure 28).

Figure 30. Open-loop frequency response of the OTA's schematic

After the physical layout was designed and it was confirmed that the Device Rule Check (DRC) passed, the extracted physical layout, including parasitic capacitances was generated. This cell is a more realistic representation of how the actual manufactured integrated circuit will behave. This extracted layout was cross-referenced and checked with the schematic circuit in a Layout vs. Schematic (LVS) check, and as can be confirmed in Appendix B, the netlists for both cells matched. Figure 31 shows the extracted layout's frequency response simulation.

Figure 31. Open-loop frequency response of the OTA's extracted layout

One can observe in this figure that the OTA meets the requirements to be used as an operational transconductance amplifier by having a high open-loop gain (55.12dB = 575), an excellent phase margin ( $\sim 80^{\circ}$ ) and a unity gain frequency of  $\sim 3$  kHz, which is enough to encompass a closed-loop bandpass shaped response from 1 Hz to 100 Hz and a mid-band gain of  $\sim 40dB$ . The OTA was simulated with a load of 12pF.

### CHAPTER V

### **G**<sub>m</sub>-C FILTER DESIGN

The next component that makes up the neural amplifier proposed in this thesis project is a filter that will follow up the front-end amplifier describe in Chapter IV. The design of a  $3^{rd}$  order Butterworth G<sub>m</sub>-C low pass filter in presented in this chapter.

Remember that the neural amplifier is intended for recording of EEG, where the Local Field Potentials range from 1-100Hz. The Capacitive Feedback Network introduced by Harrison in [1, 2] shapes the frequency response as a pass-band, however the high frequency cutoff of this pass-band may not decrease fast enough to attenuate noise at higher frequencies. Therefore to be able to attenuate the neural spikes described in Chapter I (Figure 1) beginning at around 1 kHz, the circuit proposed in this chapter uses 14.7nS transconductors and a sharper roll-off after a cutoff frequency of 150Hz that attenuate undesired noise signals by a greater amount than with only the CFN described in Chapter II. The 3<sup>rd</sup> order filter is comprised, as can be observed, from equation (11) of a single order stage, of which the circuit is shown in Figure 32, followed by a second order stage, of which circuit is shown in Figure 33. The transfer functions of these two stages are then matched to their counterparts made from a 3<sup>rd</sup> order Butterworth polynomial. Remember that  $\omega_c=2\pi f_c$ , where  $f_c$  was chosen to be 150 Hz.

$$\frac{\omega_c}{(s+\omega_c)} \cdot \frac{G_0 \omega_c^2}{(s^2+\omega_c s+\omega_c^2)} = \frac{300\pi}{(s+300\pi)} \cdot \frac{(300\pi)^2}{(s^2+300\pi s+(300\pi)^2)}$$

(11)

Figure 32. First order Gm-C Stage

Figure 33. Second order Gm-C stage

One can derive the transfer functions for each of these stages following the same procedure described in the example in Chapter I, these transfer functions are shown in terms of their circuit components in the right hand side of equations (12) and (13). The transfer function of the first order stage and the design method to match it to the corresponding product in the Butterworth third order equation (11) is shown in equation (12)

$$\frac{\omega_c}{(s+\omega_c)} = \frac{300\pi}{(s+300\pi)} = \frac{\frac{G_{m11}}{C_{11}}}{\left(s + \frac{G_{m11}}{C_{11}}\right)}$$

(12)

The transfer function of the second order stage and the design method followed to match it to its corresponding product in the Butterworth third order equation (11) is shown in equation (13).

$$\frac{G_0\omega_c^2}{(s^2 + \omega_c s + \omega_c^2)} = \frac{(300\pi)^2}{(s^2 + 300\pi s + (300\pi)^2)} = \frac{\frac{G_{m12}G_{m22}}{C_{12}C_{22}}}{\left(s^2 + \frac{G_{m32}}{C_{22}}s + \frac{G_{m12}G_{m22}}{C_{12}C_{22}}\right)}$$

(13)

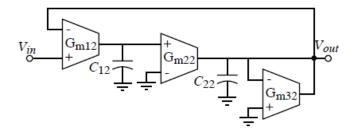

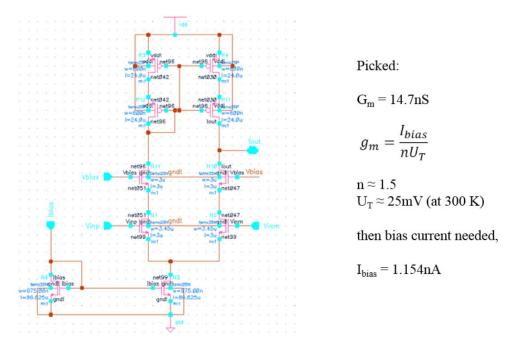

Notice from the circuits shown in Figures 32 and 33 that several transconductors make up filter's circuit. To be able to construct one single physical layout for a transconductor and use it for all the transconductors in the  $G_m$ -C filter, the value of  $G_m$  for all transconductors was chosen to be the same, 14.7nS. Then matching equations (12) and (13) with this know value for  $G_m$ , the values for the rest of the capacitors are easily obtained.

A simple current mirror transconductance amplifier like the one described in Chapter I was used to achieve the required transconductance. This cell, shown in Figure 34, was cascoded to increase its output resistance and therefore to increase the gain (refer to Chapter I), enabling the transconductors to be used as OTAs in the circuit. Figure 35 shows the Cadence schematic of the 14.7nS NMOS differential pair transconductor used in the G<sub>m</sub>-C filter, along with the procedure to calculate the bias current needed. Table 2 shows the sizes of the transistors in the filter's OTA.

Figure 34.Telescopic cascoded amplifier used as the OTA for the Gm-C filter

| Transistor sizes (µm)           |       |        |  |  |  |

|---------------------------------|-------|--------|--|--|--|

| Filter OTA                      | W     | L      |  |  |  |

| Q <sub>1</sub> , Q <sub>2</sub> | 3.45  | 3      |  |  |  |

| Q <sub>3</sub> , Q <sub>4</sub> | 3     | 3      |  |  |  |

| Q <sub>5</sub> , Q <sub>6</sub> | 0.6   | 24     |  |  |  |

| Q <sub>7</sub> , Q <sub>8</sub> | 0.6   | 24     |  |  |  |

| $Q_{b1}, Q_{b2}$                | 0.975 | 86.625 |  |  |  |

Table 2. G<sub>m</sub>-C filter OTA transistor sizes

Figure 35. 14.7nS NMOS cascoded differential pair transconductor used in the Gm-C filter

The complete schematic of the  $3^{rd}$  order  $G_m$ -C low pass filter, including the bias circuit that provides the five identical bias currents for the transconductors, is shown in Figure 36 below. The bias circuit used to source the five transconductors is similar to the one used for the OTA in Chapter IV, except this time it was designed to output five 1.154nA currents instead of a single 56nA current.

Figure 36. 3<sup>rd</sup> order G<sub>m</sub>-C low pass filter schematic with its bias circuit

The  $G_m$ -C Filter consumes 17.637nA, corresponding to 31.75nW of power, including the bias circuit. However, remember that one bias circuit is enough for an entire multichannel system, so a more important figure is the power consumption per channel (without the bias circuit). That being the case, the  $G_m$ -C filter consumes 6.092nA, corresponding to 10.966nW of power per channel.

### **Design of the Gm-C Filter's Physical Layout**

The designed layout for the filter in the 300nm TSMC process is shown in Figure 37 below, it occupies an area of 346.95 $\mu$ m x 184.95 $\mu$ m. Since only one bias circuit is needed to implement a multichannel system the total area occupied by the filters can be reduced in a multichannel system. The capacitors were built as MIM (Metal-Insulator-Metal) capacitors due to the lack of polysilicon layers in the TSMC process used. These type of capacitors have a lower capacitance per area (1fF/ $\mu$ m<sup>2</sup>) than polysilicon ones which increases the area they use.

Figure 37. Gm-C Filter Layout in the 300nm TSMC process

# Simulation of the G<sub>m</sub>-C Filter

This section presents the simulated frequency response for both the schematic and layout of the  $3^{rd}$  order  $G_m$ -C low pass filter designed in this chapter. Figure 38 below shows the simulation results for the schematic (shown in Figure 36).

Figure 38. Frequency response of the G<sub>m</sub>-C filter's schematic

After the physical layout was designed and it was confirmed that the Device Rule Check (DRC) passed, the extracted physical layout, including parasitic capacitances was generated. As explained in Chapter IV, this cell is a more realistic representation of how the actual manufactured integrated circuit will behave. This extracted layout was cross-referenced and checked with the schematic circuit in a Layout vs. Schematic (LVS) check, and as can be confirmed in Appendix B, the netlists for both cells matched. Figure 39 below shows the extracted layout's frequency response simulation.

Figure 39. Frequency response of the G<sub>m</sub>-C filter's extracted layout

As can be seen in Figure 39 the filter layout behaves as intended in the design, it has the sharper falling edge of a 3<sup>rd</sup> order filter and a cutoff frequency of ~140 Hz. Comparing figures 38 and 39, it can be observed that the extracted layout response closely matches the schematic response. Any discrepancies in the accuracy of the cutoff frequency are attributed to parasitic capacitances in the extracted layout, which affect the designed values of the capacitors, therefore affecting the cutoff frequency.

# CHAPTER VI

### THE NEURAL AMPLIFIER

Now that we have presented all the components of the neural amplifier, this chapter will focus on describing how these components are put together to realize the entire system. The full  $3^{rd}$  order filter, as well as the neural amplifier are shown in Figure 40. The Capacitive Feedback configuration for the gain stage was presented in [1] and explained in Chapter II; the mid-band gain  $A_M$  is set by  $C_{in}/C_f$ , and the bandwidth is  $g_m/(A_MC_L)$ , where  $g_m$  is the transconductance of the operational transconductance amplifier (OTA). The input capacitors  $C_{in}$  get rid of the DC offset generated at the electrode-tissue interface and the transistors in the feedback loop are used as pseudo-resistors to deliver a bias voltage to the input transistors of the amplifier, as well as set the low frequency cutoff of the amplifier's frequency response.

Figure 40. The proposed neural amplifier

Using nodal analysis and the procedure described in Chapter I, the transfer functions of the gain stage, as well as that of the entire system were derived. Equation 14 below shows the derived transfer function of the gain stage OTA with its Capacitive Feedback Network.

$$\frac{V_{out}}{V_{in}} = \frac{s^2 C_{in} C_f R_f + s (C_{in} - C_{in} G_m R_f)}{s^2 (C_{La} C_f R_f + C_{La} C_{in} R_f + C_f C_{in} R_f) + s (C_{La} + C_{in} + C_f G_m R_f) + G_m}$$

(14)

The transfer function of the  $3^{rd}$  order  $G_m$ -C filter is given by the product equations 12 and 13 (Chapter V). Figure 41 below shows the theoretical bode plots obtained for each stage of the system (the OTA with CFN and the  $G_m$ -C filter), as well as the entire neural amplifier.

Figure 41. MATLAB Bode plots for all stages of the neural amplifier

To verify the theoretical response, the completed neural amplifier was simulated in Cadence; its schematic is shown in Figure 42 below.

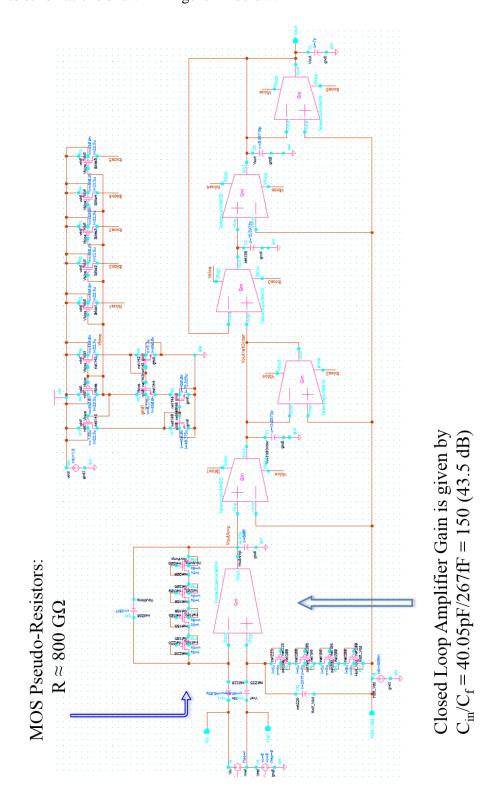

Figure 42. Complete schematic of the neural amplifier

The transistors in the feedback loop were measured to have a resistance of ~800G $\Omega$  to small changes in the voltage across them; their *W/L* ratio was set to 6µm/6µm. This high resistance is needed to achieve a low frequency cutoff in the milliHertz range. The closed-loop gain was set to be 150 (43.5dB) as shown in Figure 42.

Figure 43. Frequency response of the Neural Amplifier's schematic.

The circuit's schematic frequency response (Figure 43) shows agreement with the theoretical plots in Figure 41.

## Design of the Neural Amplifier's Physical Layout