## University of Texas Rio Grande Valley ScholarWorks @ UTRGV

Theses and Dissertations - UTB/UTPA

4-2006

## The optimization of amplifiers for UWB applications

Kyoung D. Kim University of Texas-Pan American

Follow this and additional works at: https://scholarworks.utrgv.edu/leg\_etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Kim, Kyoung D., "The optimization of amplifiers for UWB applications" (2006). *Theses and Dissertations - UTB/UTPA*. 737. https://scholarworks.utrgv.edu/leg\_etd/737

This Thesis is brought to you for free and open access by ScholarWorks @ UTRGV. It has been accepted for inclusion in Theses and Dissertations - UTB/UTPA by an authorized administrator of ScholarWorks @ UTRGV. For more information, please contact justin.white@utrgv.edu, william.flores01@utrgv.edu.

## NOTE TO USERS

Page(s) missing in number only; text follows. Page(s) were scanned as received.

61

This reproduction is the best copy available.

## THE OPTIMIZATION OF AMPLIFIERS FOR UWB APPLICATIONS

A Thesis

by

Kyoung D. Kim

Submitted to the Graduate School of the University of Texas-Pan American In fulfillment of the requirements for the degree of

MASTER OF SCIENCE

April 2005

Major Subject: Electrical Engineering

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

## THE OPTIMIZATION OF AMPLIFIERS FOR UWB APPLICATIONS

A Thesis by Kyoung D. Kim

Approved as to style and content by:

TTA Per

Foltz, Heinrich Ph.D. Chair of Committee

Supering

Son, Jae Sok Ph.D. Committee Member

Timmer, Douglas Ph.D. Committee Member

April 2005

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### ABSTRACT

Kim, Kyoung D, <u>The Optimization Amplifiers For UWB Applications</u>. Master of Science and Engineering (MSE). April 2006, 174 pp.; 147 figures, 14 tables, references, 16 titles.

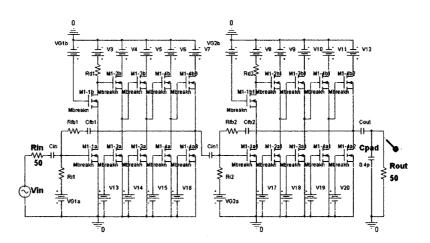

Optimizations of 0.18  $\mu$ m and 0.5  $\mu$ m MOSFET amplifiers without using inductors for UWB applications are presented. A 3 dB bandwidth from 3.1 GHz to 9.9 GHz with minimum 9.6 dB of transducer gain at 10.6 GHz and approximate 92.8 mWatts of total power consumption are achieved. The source and load impedances were 50 ohms. Also, the number of capacitors and resistors has been minimized. To predict characteristics more precisely, the pad capacitance is added to the output port. In addition, a different feedback topology is presented which gives a lower Noise Figure with maximum 7.73 dB at 10.6 GHz with 300 ohms feedback resistance.

#### DEDICATION

This thesis is dedicated all the people who supported me.

이 논문을 나의 사랑하는 아내 유미와 항상 웃음을 주는 딸 민아 그리고 한국에 계신 부모님들을 비롯한 모든 가족들에게 바칩니다.

#### ACKNOLWEDGEMENT

This thesis has been possible with the help of many people. First and foremost, I am deeply thankful for my advisor Dr. Heinrich Foltz, for his continued support and guidance in my research, and his assistance in writing this thesis. It was a great opportunity and I was really excited to work on this research. I would like to thank the other members of committee, Dr. Jae Sok Son, and Dr. Douglas Timmer for the assistance and willingness for my thesis.

## TABLE OF CONTENTS

| ABSTRACTiii                                                           |

|-----------------------------------------------------------------------|

| DEDICATION iv                                                         |

| ACKNOLWEDGEMENT                                                       |

| TABLE OF CONTENTS                                                     |

| LIST OF TABLES xv                                                     |

| Chapter 1 INTRODUCTION 1                                              |

| Chapter 2 UWB Introduction                                            |

| Chapter 3 Previous Approaches to the design of UWB amplifiers         |

| Chapter 4 Designing UWB amplifier                                     |

| Chapter 5 Considerations of UWB amplifier                             |

| Chapter 6 Optimizing UWB amplifier                                    |

| Chapter 7 Proposed UWB amplifier quality characteristics measurements |

| Chapter 8 Conclusions 142                                             |

| Appendix A MOSFET electrical parameters                               |

| Appendix B Designing with 0.5 $\mu$ m MOSFETs                         |

| Appendix C Another feedback topologies                                |

| Appendix D Conclusions of the another feedback topologies             |

| VITA                                                                  |

#### LIST OF FIGURES

| Page                                                                                  |

|---------------------------------------------------------------------------------------|

| Figure 1 Definition of UWB                                                            |

| Figure 2 Comparison of conventional NB and UWB signal concept                         |

| Figure 3 FCC UWB Limits                                                               |

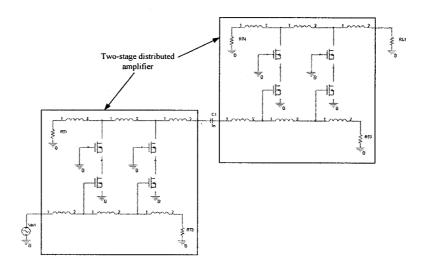

| Figure 4 Three-stage distributed amplifier9                                           |

| Figure 5 Cascaded two-stage distributed amplifier 10                                  |

| Figure 6 Common Gate small signal equivalent circuit                                  |

| Figure 7 LNA circuit schematic 12                                                     |

| Figure 8 Typical schematic of cascode feedback LNA                                    |

| Figure 9 The resonant circuit for broadband input matching                            |

| Figure 10 The complete schematic of LNA 15                                            |

| Figure 11 Narrowband LNA topology. (a) Overall schematic. (b) Small-signal equivalent |

| circuit at the input17                                                                |

| Figure 12 UWB LNA topology                                                            |

| Figure 13 MOSFET structure simulation by Silvaco                                      |

| Figure 14 n-MOSFET device with bias voltages                                          |

| Figure 15 MOSFET $V_G$ - $I_D$ Graph by Silvaco simulation                            |

| Figure 16 Common-source MOSFET amplifier circuit                                      |

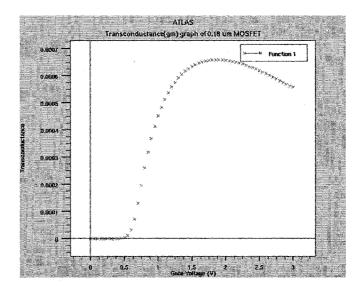

| Figure 17 Transconductance graph from Silvaco simulation                              |

| Figure 18 The cross-sectional view of a nMOSFET with various capacitances             |

| Figure 19 (a) Common-source MOSFET high frequency model (b) its small signal model  |

|-------------------------------------------------------------------------------------|

|                                                                                     |

| Figure 20 (a) Common-gate MOSFET high frequency model and (b) high-frequency        |

| small signal model                                                                  |

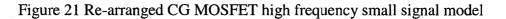

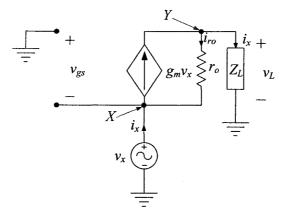

| Figure 21 Re-arranged CG MOSFET high frequency small signal model                   |

| Figure 22 Re-arranged CG MOSFET for input impedance, Z <sub>in</sub>                |

| Figure 23 Basic cascode amplifier configuration                                     |

| Figure 24 CASCODE small signal circuit for frequency response                       |

| Figure 25 Circuit to find $R_{gdl}$                                                 |

| Figure 26 Shunt-peaked amplifier                                                    |

| Figure 27 CASCADE topology                                                          |

| Figure 28 IP3, P1dB, IMD graph                                                      |

| Figure 29 3 <sup>rd</sup> order intercept point (IP3)                               |

| Figure 30 Actual IP3 simulation graph with two different input sources (8 GHz & 8.2 |

| GHz)                                                                                |

| Figure 31 Initial circuit for optimization                                          |

| Figure 32 Simple CS amplifier with a feedback                                       |

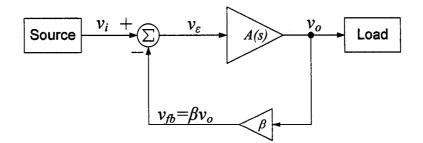

| Figure 33 Negative series-shunt feedback amplifier block diagram                    |

| Figure 34 Comparison of the magnitude Bode plot of $A_f(j\omega)$ and $A(j\omega)$  |

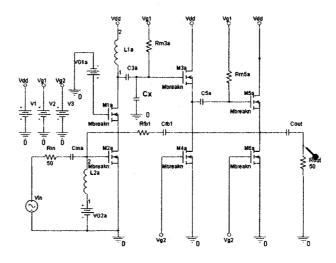

| Figure 35 Parasitic capacitance to ground at the output end of the CASCODE stage 66 |

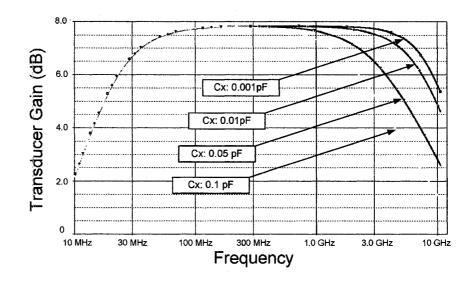

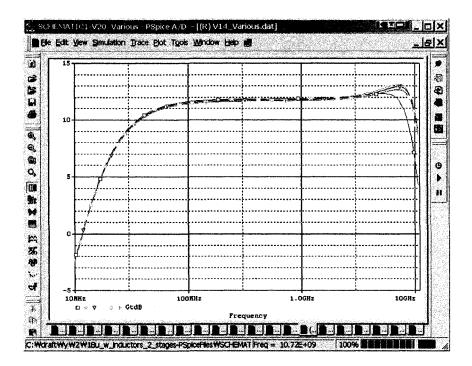

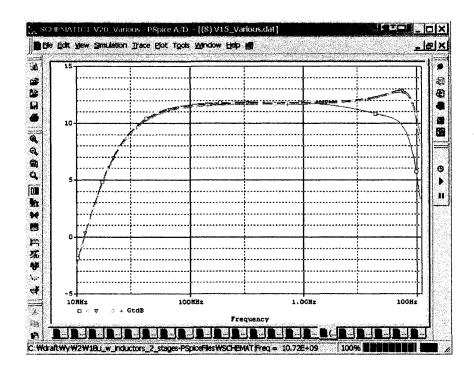

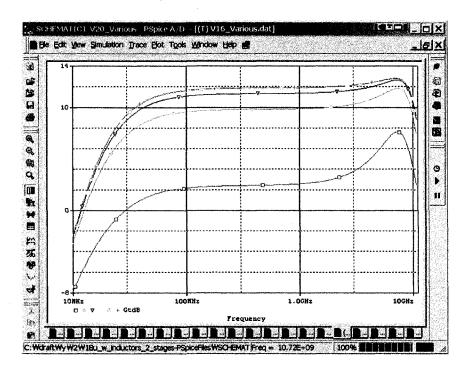

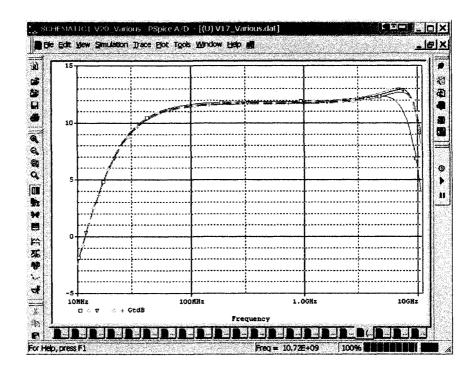

| Figure 36 Transducer gain (dB) with different Cx                                      |

|---------------------------------------------------------------------------------------|

| Figure 37 Modified circuit to resolve the capacitor and the Transducer gain issues 67 |

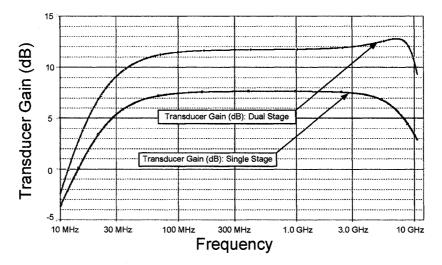

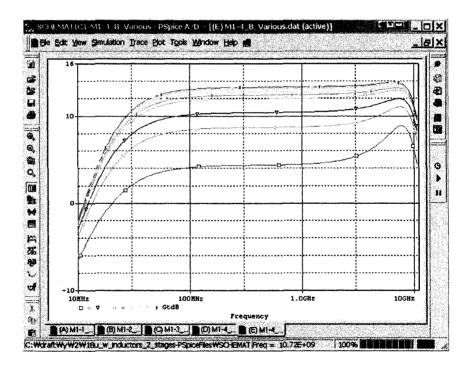

| Figure 38 Transducer gain comparison of dual stages and a single stage                |

| Figure 39 Circuit with a Pad capacitor at the output node                             |

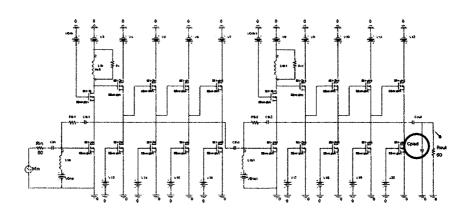

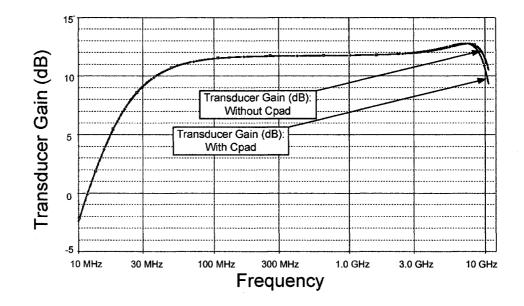

| Figure 40 Transducer gain comparison with and without a Pad capacitor                 |

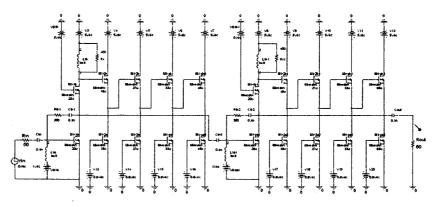

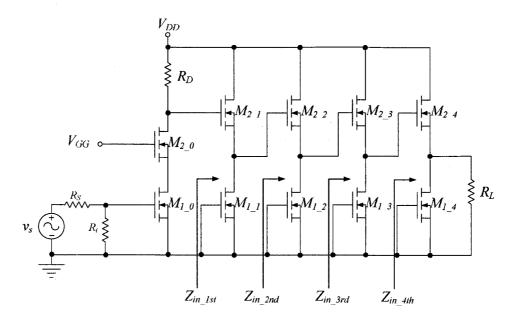

| Figure 41 Circuit without inductors                                                   |

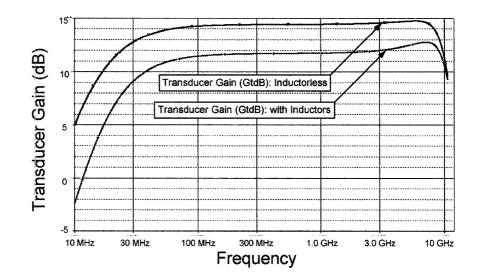

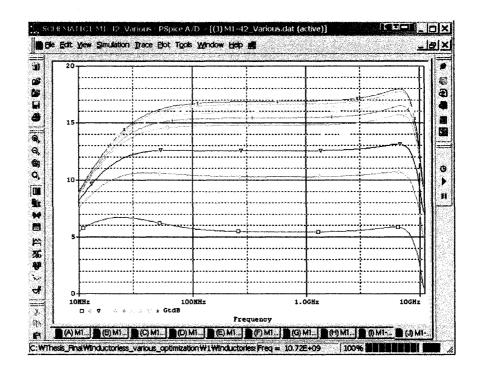

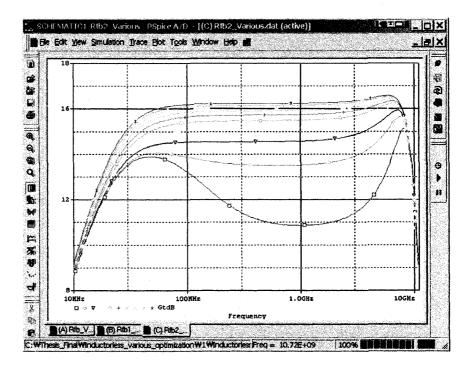

| Figure 42 Transducer gain comparison with and without inductors                       |

| Figure 43 CASCODE total input resistance circuit                                      |

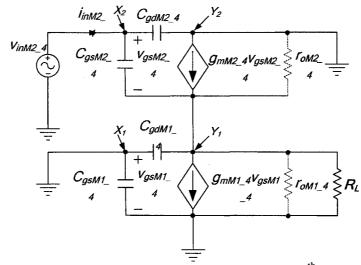

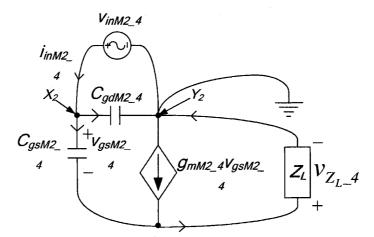

| Figure 44 Small signal circuit of the 1 <sup>st</sup> stage74                         |

| Figure 45 Simplified circuit of Figure 6374                                           |

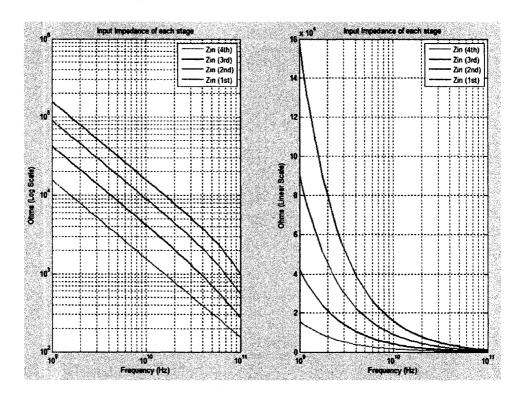

| Figure 46 Input Impedance Graphs of each stage79                                      |

| Figure 47 Initial layout                                                              |

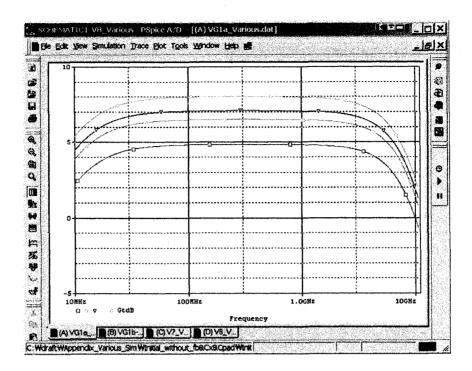

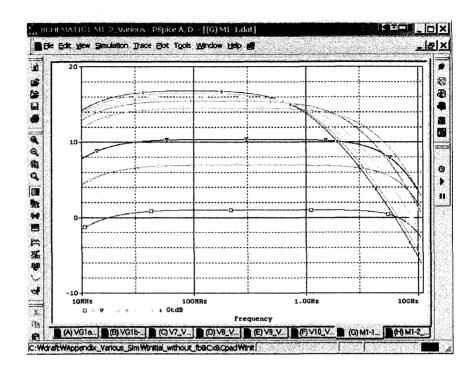

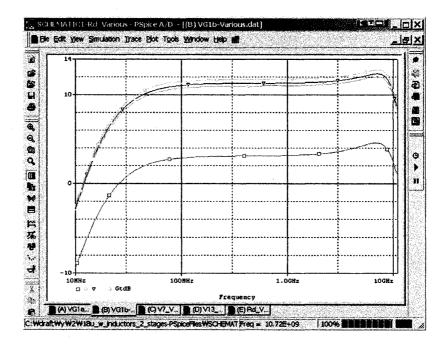

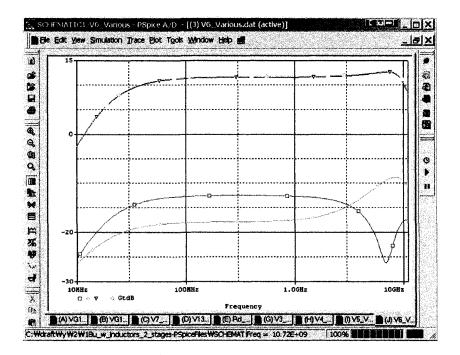

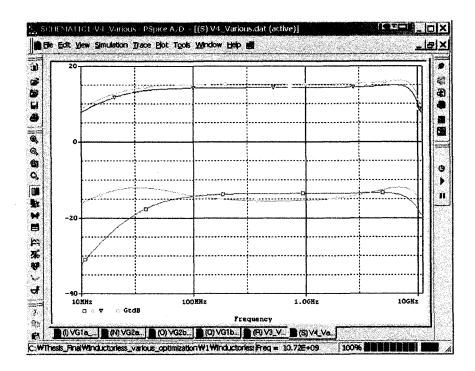

| Figure 48 VG1a optimization                                                           |

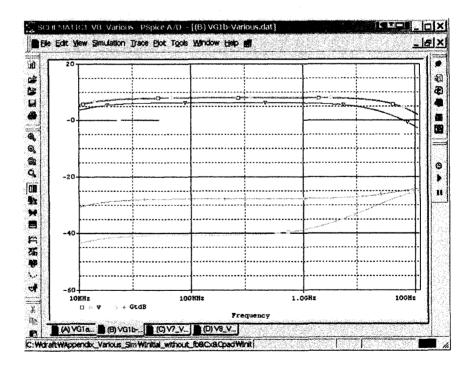

| Figure 49 VG1b optimization                                                           |

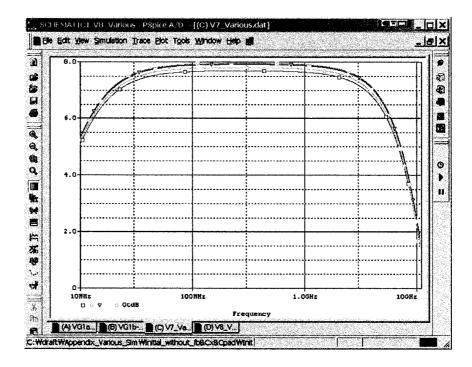

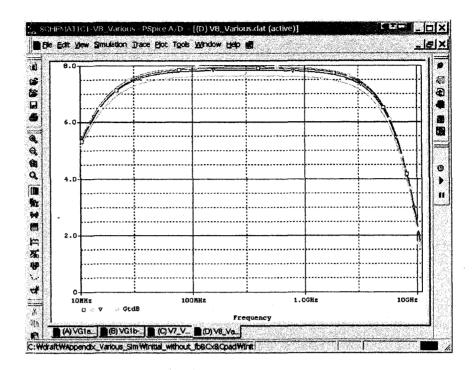

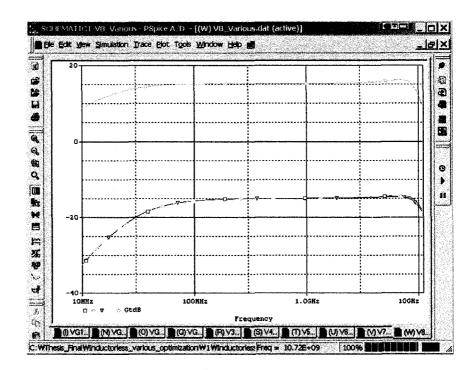

| Figure 50 V7 optimization                                                             |

| Figure 51 V8 optimization                                                             |

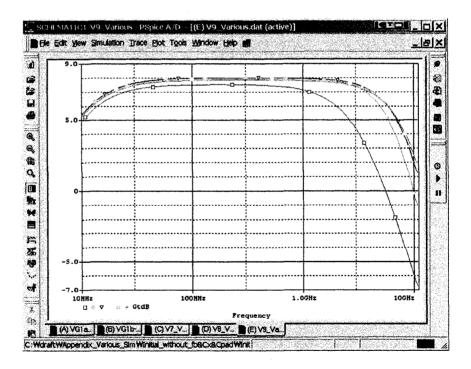

| Figure 52 V9 optimization                                                             |

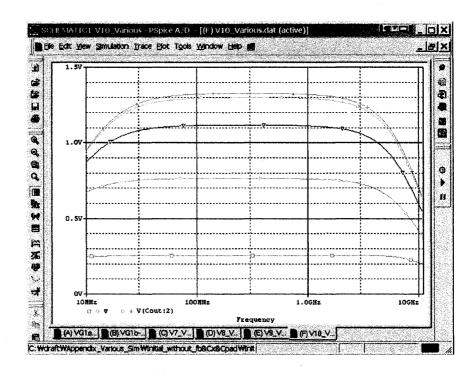

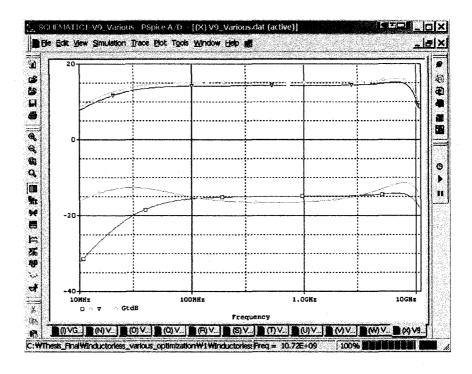

| Figure 53 V10 optimization                                                            |

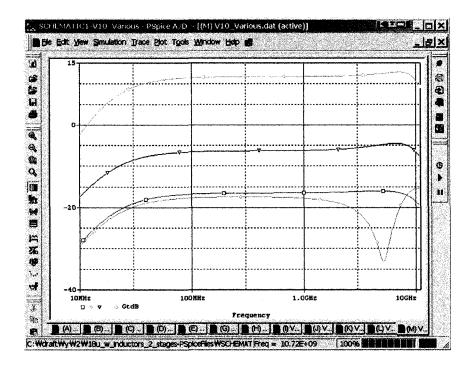

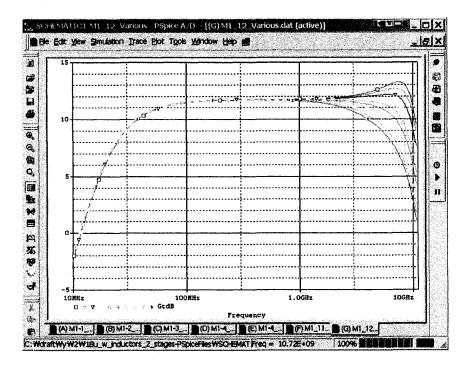

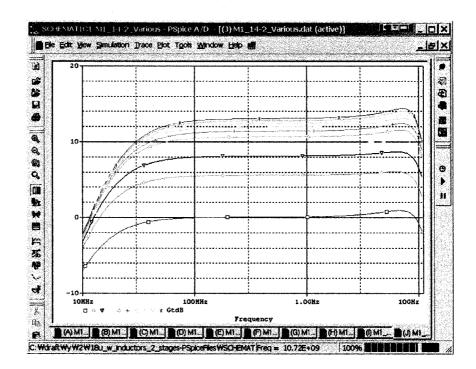

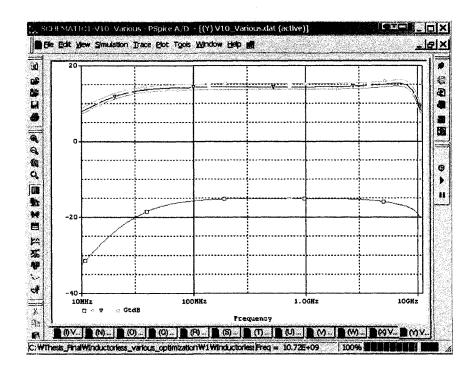

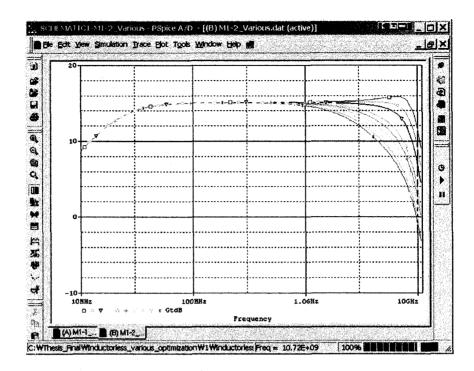

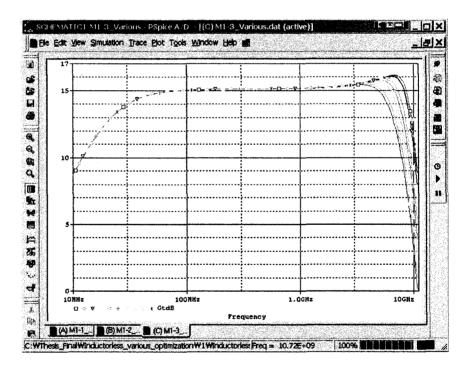

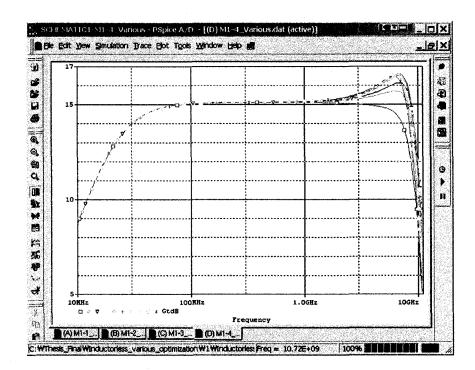

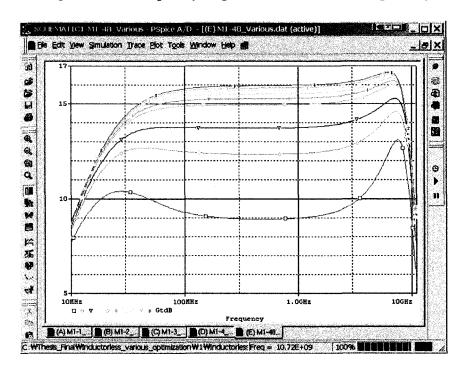

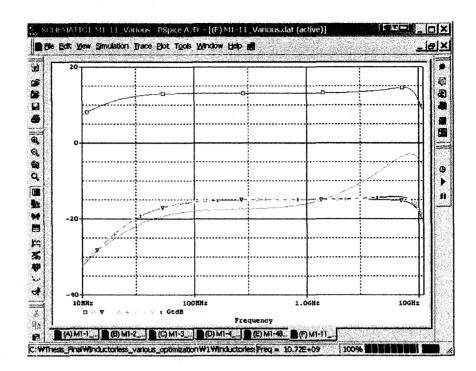

| Figure 54 M1-1 width optimization                                                     |

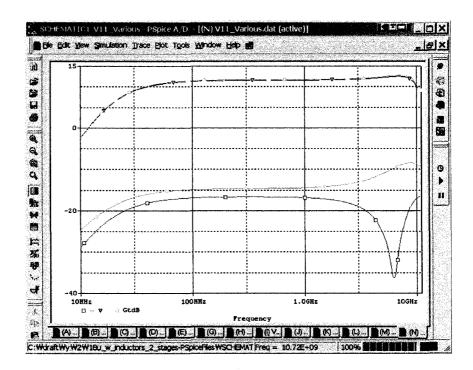

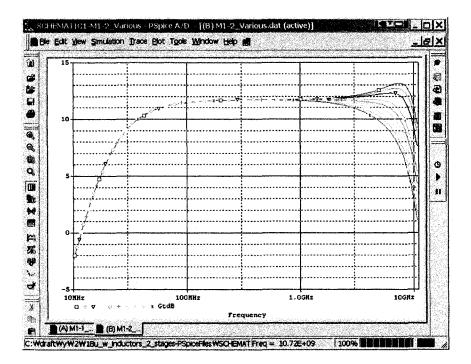

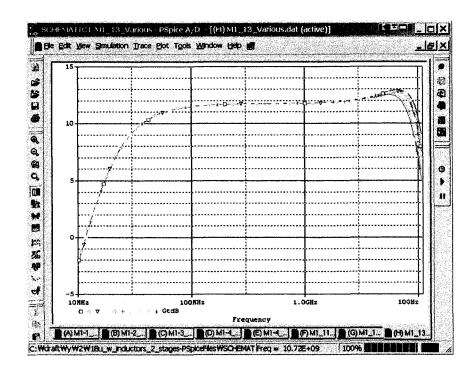

| Figure 55 M1-2 width optimization                                                     |

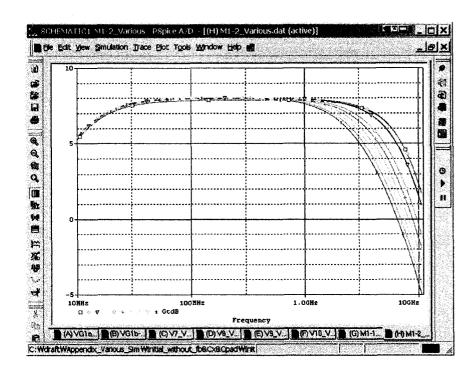

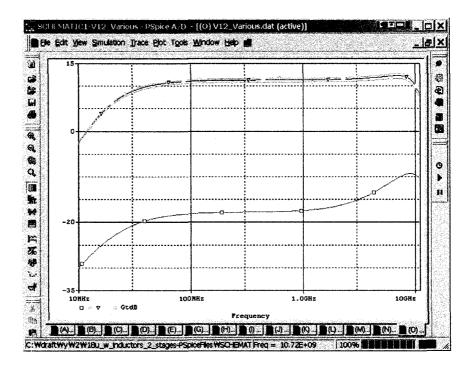

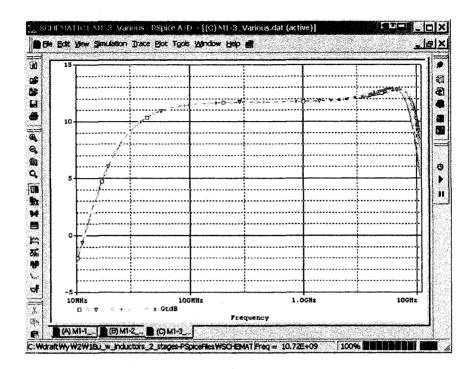

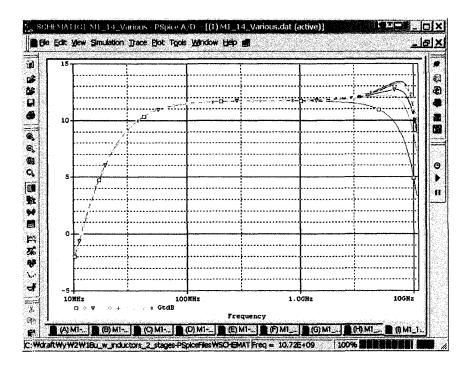

| Figure 56 M1-3 width optimization                                                     |

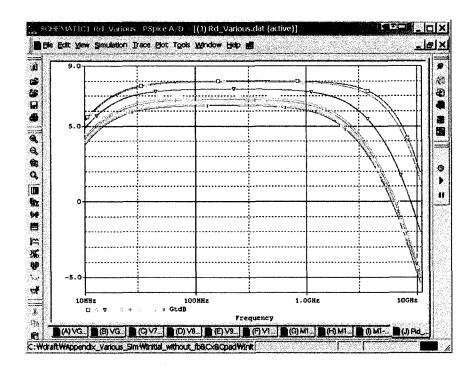

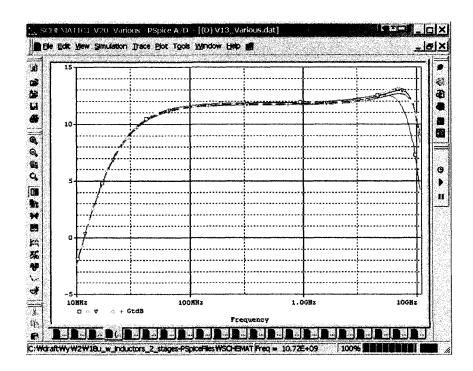

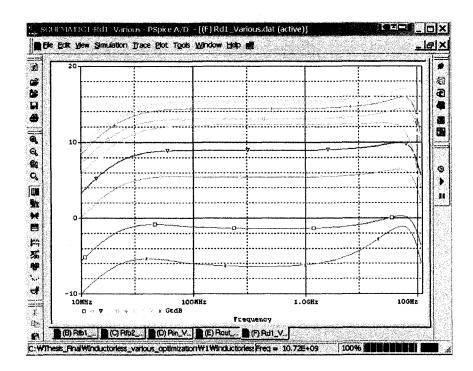

| Figure 57 Rd optimization              |

|----------------------------------------|

| Figure 58 Input resistance             |

| Figure 59 Output resistance            |

| Figure 60 2 <sup>nd</sup> phase layout |

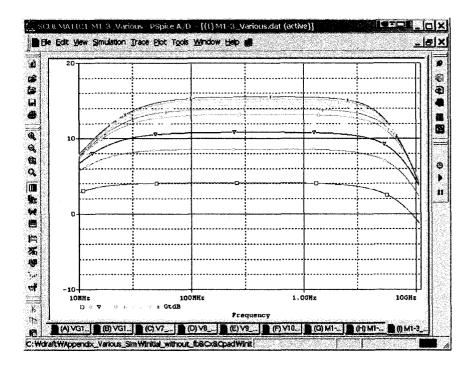

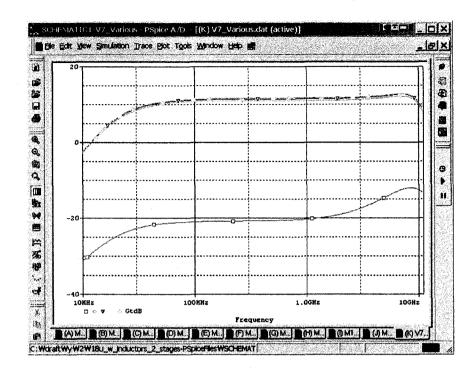

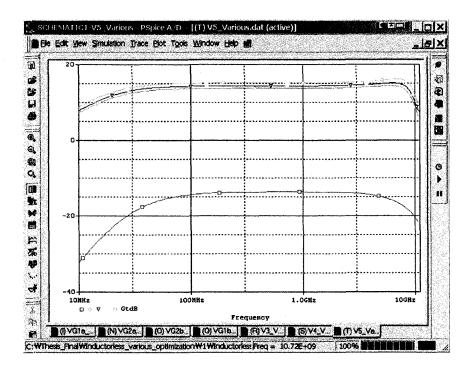

| Figure 61 VG1a optimization91          |

| Figure 62 VG1b optimization91          |

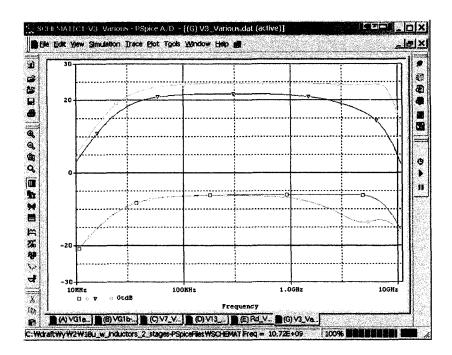

| Figure 63 V3 optimization              |

| Figure 64 V4 optimization              |

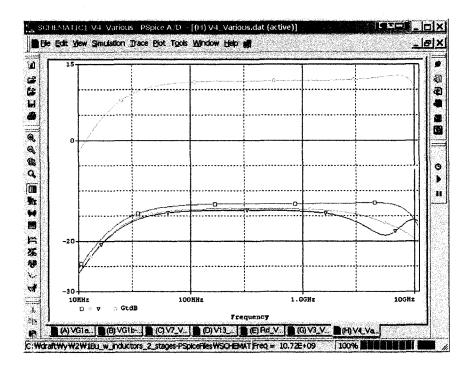

| Figure 65 V5 optimization              |

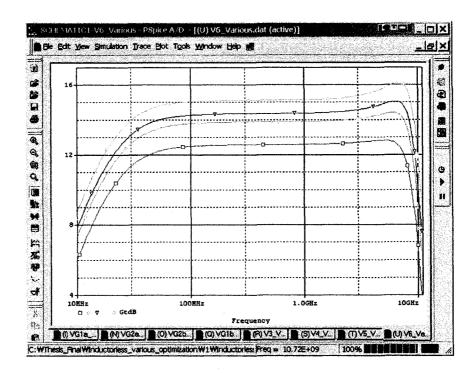

| Figure 66 V6 optimization              |

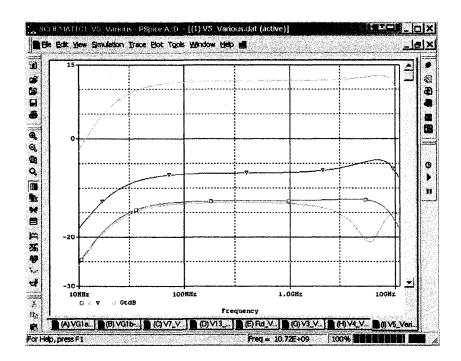

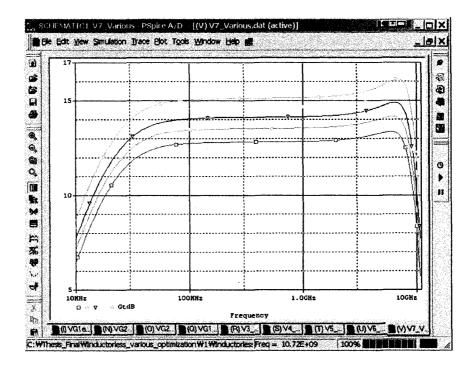

| Figure 67 V7 optimization              |

| Figure 68 V8 optimization              |

| Figure 69 V9 optimization              |

| Figure 70 V10 optimization             |

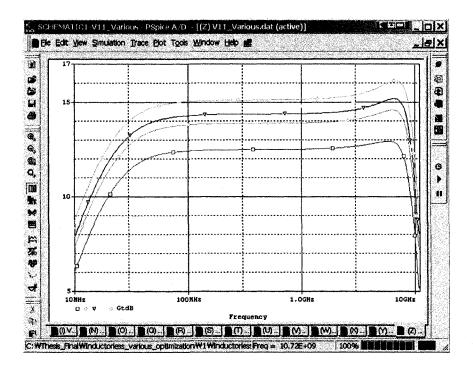

| Figure 71 V11 optimization             |

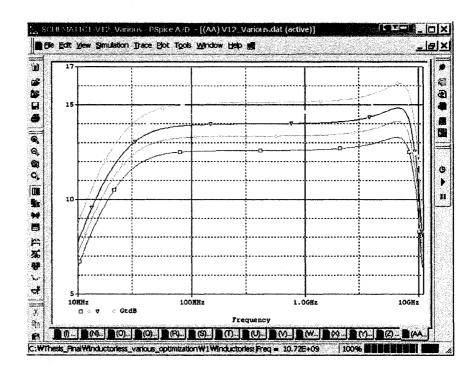

| Figure 72 V12 optimization             |

| Figure 73 V13 optimization             |

| Figure 74 V14 optimization             |

| Figure 75 V15 optimization             |

| Figure 76 V16 optimization             |

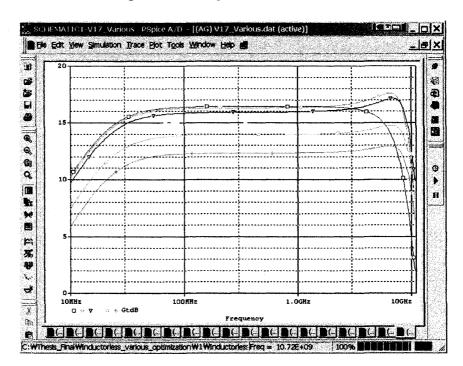

| Figure 77 V17 optimization             |

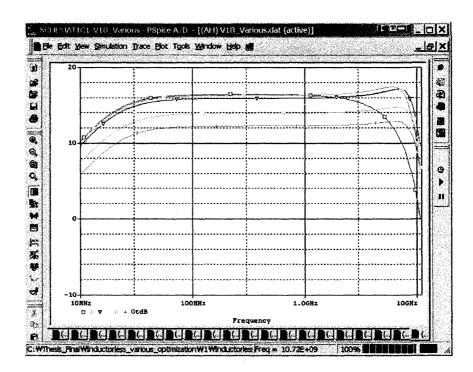

| Figure 78 V18 optimization 100                          |

|---------------------------------------------------------|

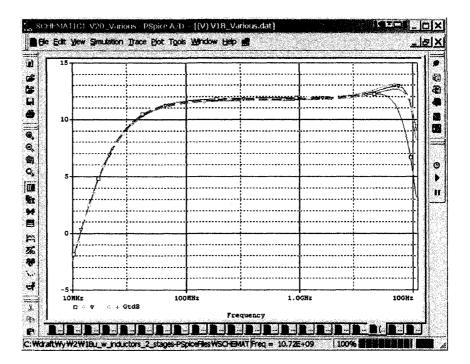

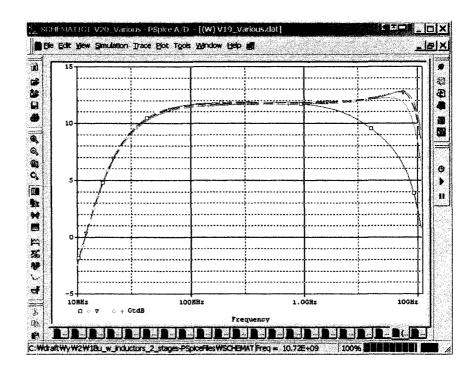

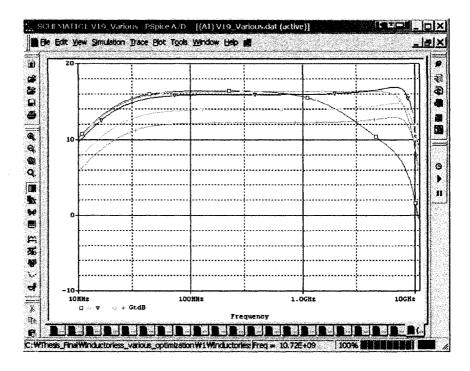

| Figure 79 V19 optimization 101                          |

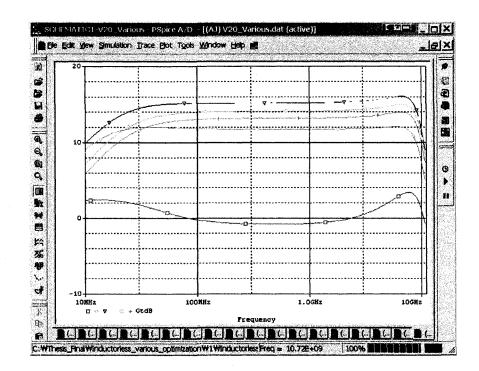

| Figure 80 V20 optimization 101                          |

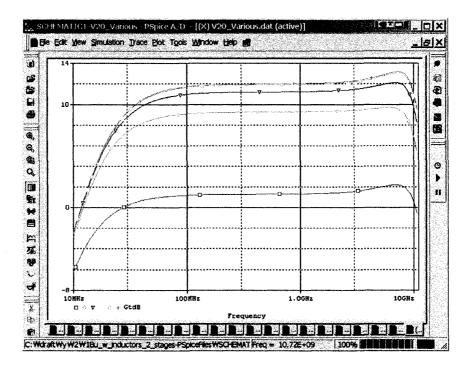

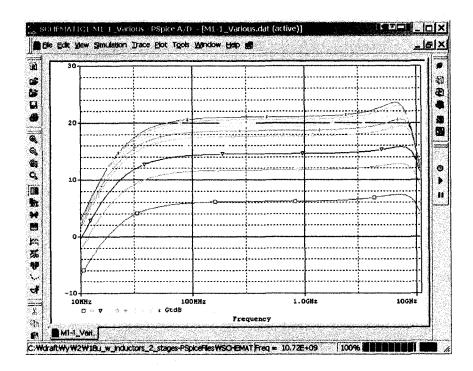

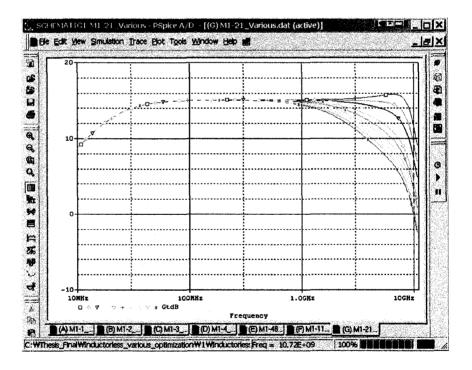

| Figure 81 M1-1a & M1-1b MOSFET width optimization 103   |

| Figure 82 M1-2a and M1-2b MOSFET width optimization 103 |

| Figure 83 M1-3a and M1-3b MOSFET width optimization 104 |

| Figure 84 M1-4a8 & M1-4b8 MOSFET width optimization 104 |

| Figure 85 M1-1a1 & M1-1b1 MOSFET width optimization 105 |

| Figure 86 M1-2a1 & M1-2b1 MOSFET width optimization 105 |

| Figure 87 M1-3a1 & M1-3b1 MOSFET width optimization 106 |

| Figure 88 M1-4a1 & M1-4b1 width optimization 106        |

| Figure 89 M1-4a2 & M1-4b2 MOSFET width optimization 107 |

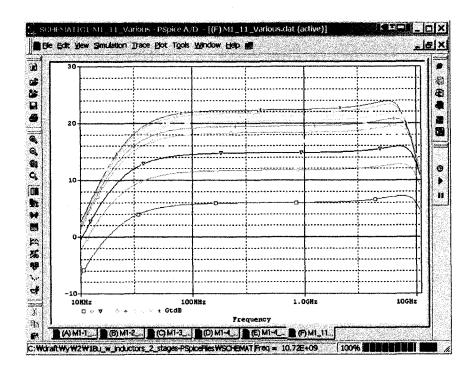

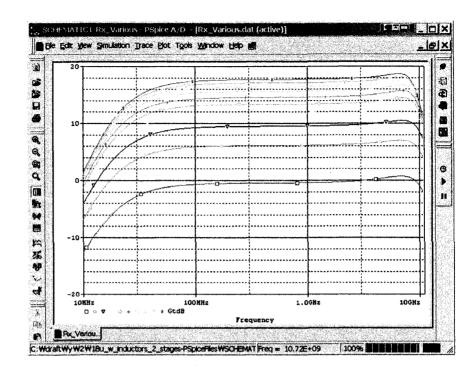

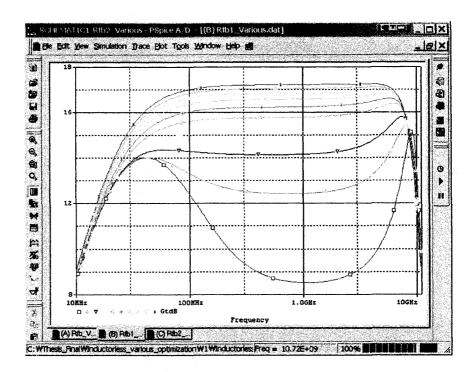

| Figure 90 Rx optimization 109                           |

| Figure 91 Rx1 optimization 109                          |

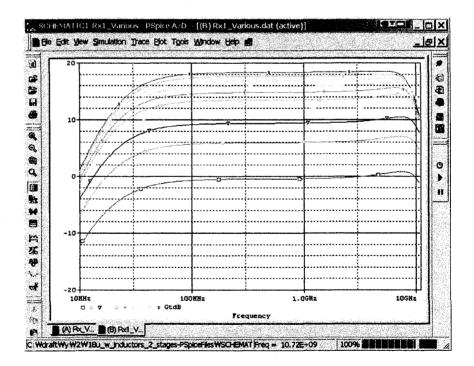

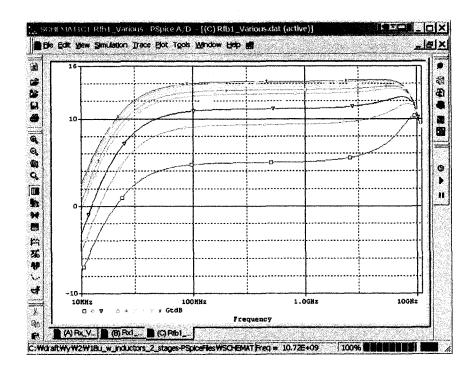

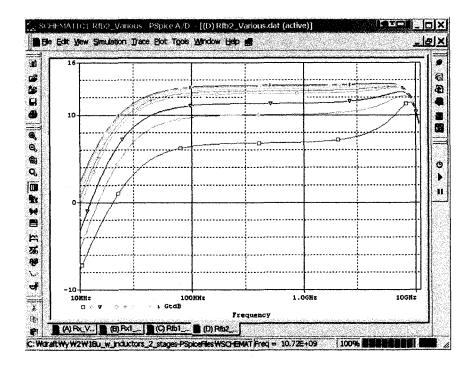

| Figure 92 Rfb1 optimization                             |

| Figure 93 Rfb2 optimization110                          |

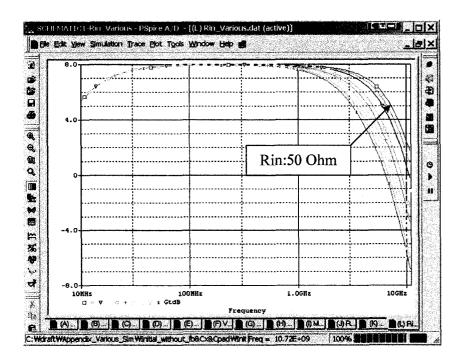

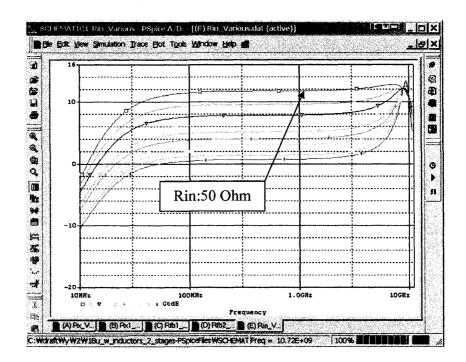

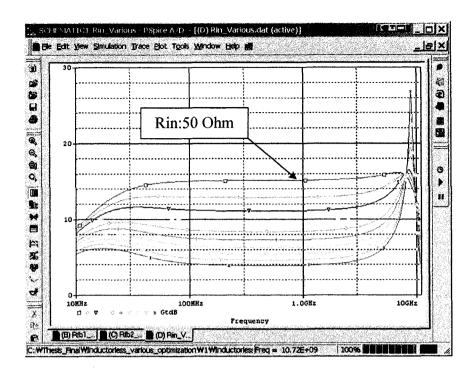

| Figure 94 Rin optimization 111                          |

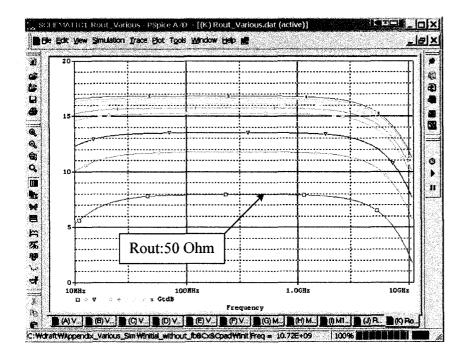

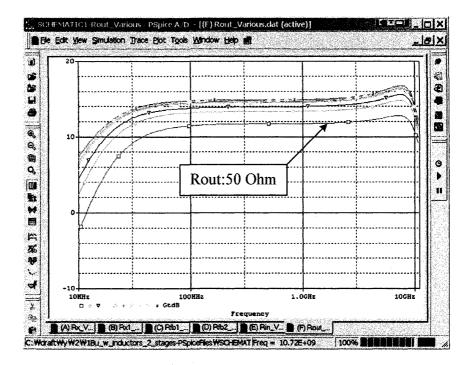

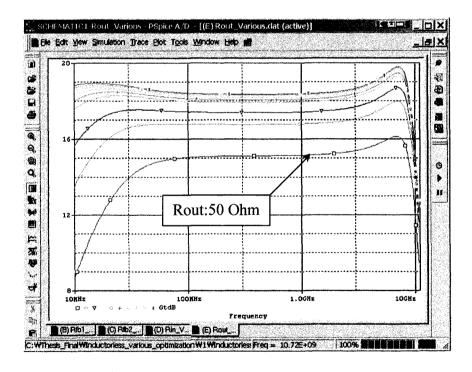

| Figure 95 Rout optimization 111                         |

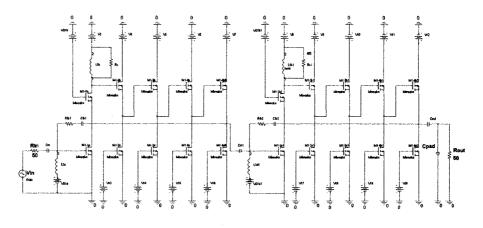

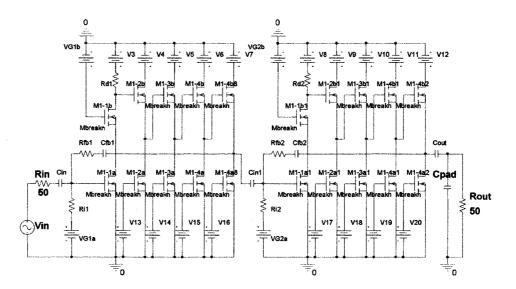

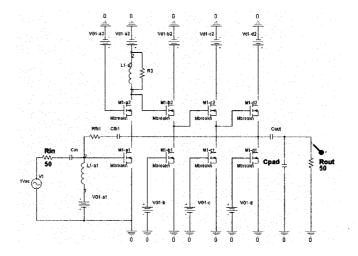

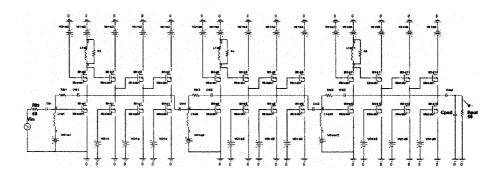

| Figure 96 Proposed inductorless layout                  |

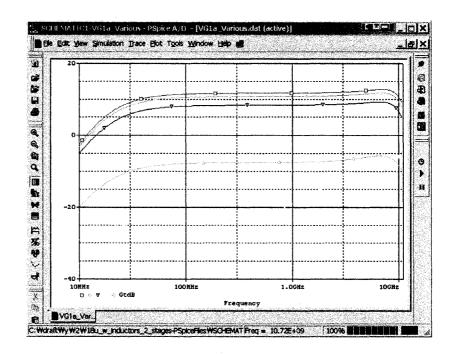

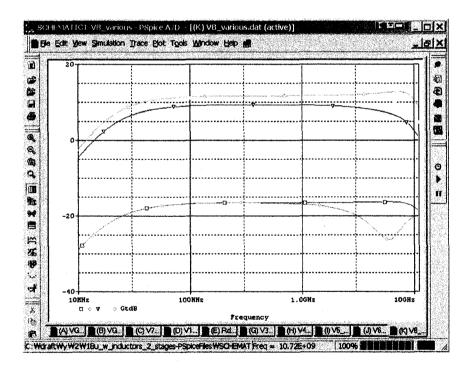

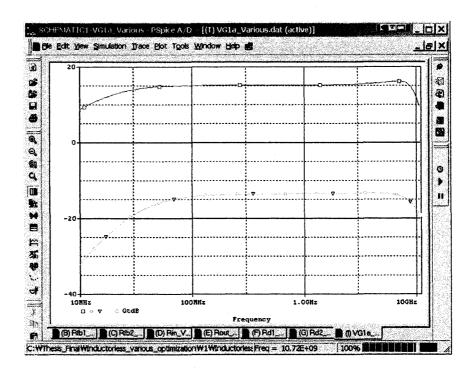

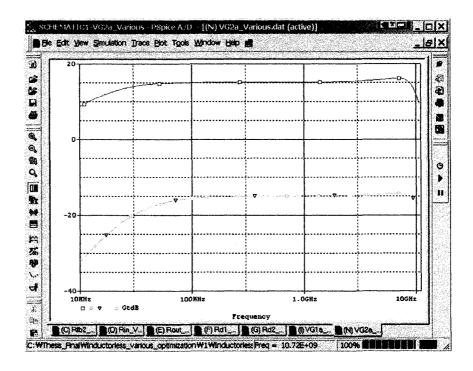

| Figure 97 VG1a optimization114                          |

| Figure 98 VG2a optimization114                          |

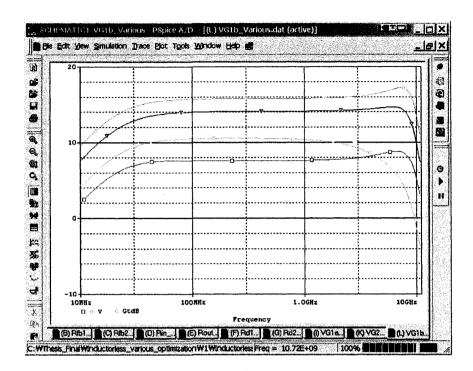

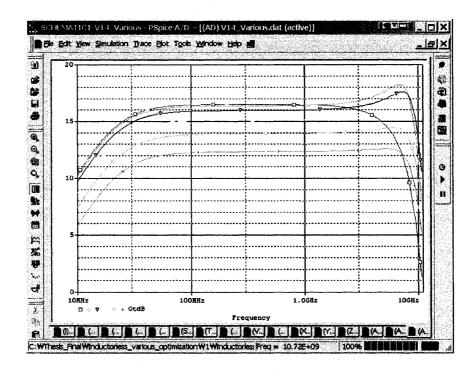

| Figure 99 VG1b optimization                               |

|-----------------------------------------------------------|

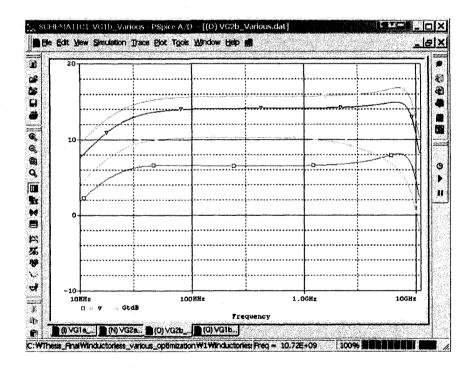

| Figure 100 VG2b optimization 115                          |

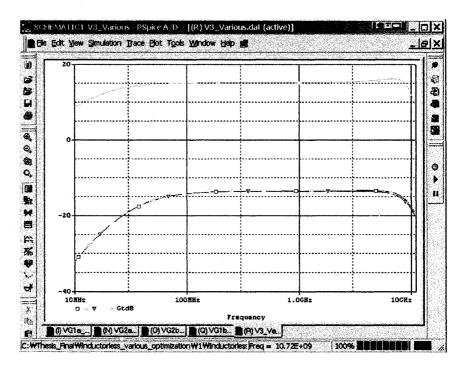

| Figure 101 V3 optimization 116                            |

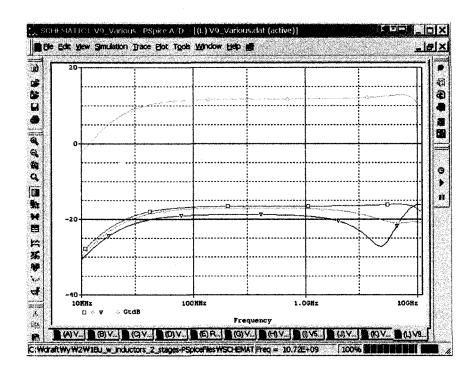

| Figure 102 V4 optimization 117                            |

| Figure 103 V5 optimization 117                            |

| Figure 104 V6 optimization 118                            |

| Figure 105 V7 optimization 118                            |

| Figure 106 V8 optimization 119                            |

| Figure 107 V9 optimization 119                            |

| Figure 108 V10 optimization 120                           |

| Figure 109 V11 optimization 120                           |

| Figure 110 V12 optimization 121                           |

| Figure 111 V13 optimization 122                           |

| Figure 112 V14 optimization 123                           |

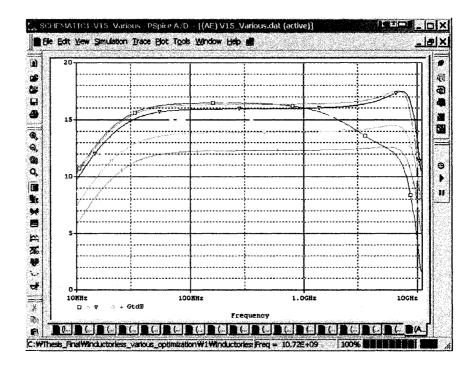

| Figure 113 V15 optimization 123                           |

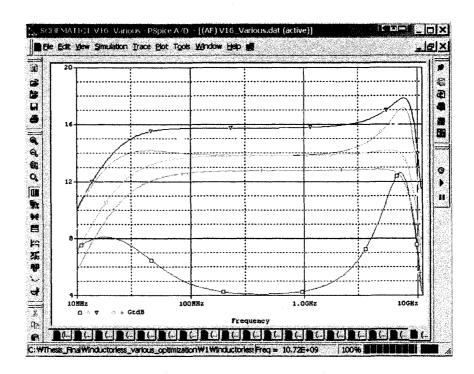

| Figure 114 V16 optimization 124                           |

| Figure 115 V17 optimization 124                           |

| Figure 116 V18 optimization 125                           |

| Figure 117 V19 optimization 125                           |

| Figure 118 V20 optimization 126                           |

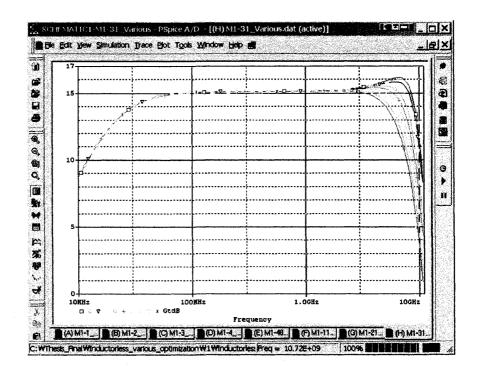

| Figure 119 Width of M1-1a & M1-1b MOSFET optimization 127 |

| Figure 120 Width of M1-2a & M1-2b MOSFET optimization 128              |

|------------------------------------------------------------------------|

| Figure 121 Width of M1-3a & M1-3b MOSFET optimization 128              |

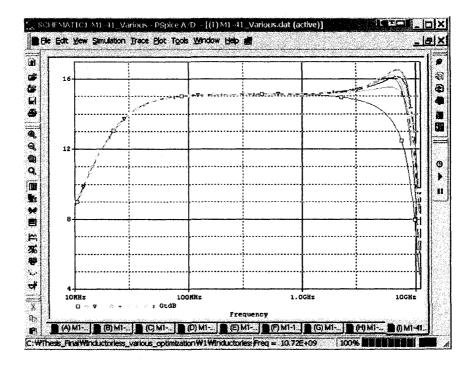

| Figure 122 Width of M1-4a & M1-4b MOSFET optimization 129              |

| Figure 123 Width of M1-4a8 & M1-4b8 MOSFET optimization 129            |

| Figure 124 Width of M1-1a1 & M1-1b1 MOSFET optimization 130            |

| Figure 125 Width of M1-2a1 & M1-2b1 MOSFET optimization 130            |

| Figure 126 Width of M1-3a1 & M1-3b1 MOSFET optimization                |

| Figure 127 Width of M1-4a1 & M1-4b1 MOSFET optimization                |

| Figure 128 Width of M1-4a2 & M1-4b2 MOSFET optimization 132            |

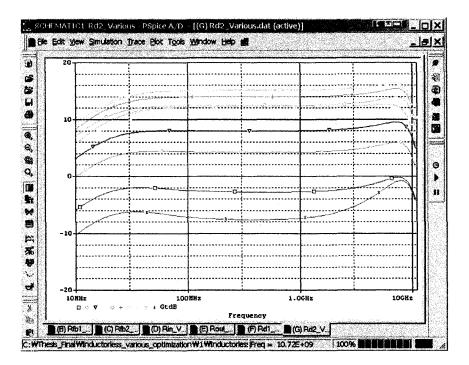

| Figure 129 Rd1 optimization                                            |

| Figure 130 Rd2 optimization                                            |

| Figure 131 Rfb1 optimization                                           |

| Figure 132 Rfb2 optimization                                           |

| Figure 133 Rin optimization                                            |

| Figure 134 Rout optimization                                           |

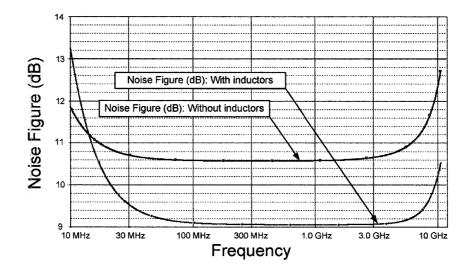

| Figure 135 Noise Figure (dB) comparison with and without inductors 139 |

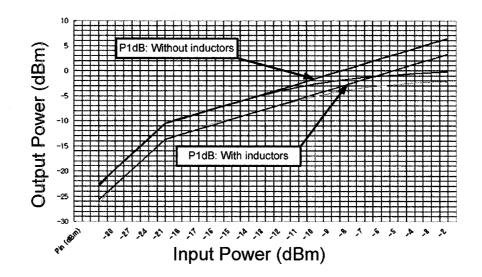

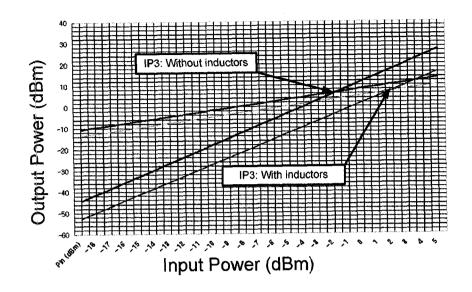

| Figure 136 P1 dB comparison with and without inductors                 |

| Figure 137 IP3 comparison with and without inductors                   |

| Figure A- 1 Basic circuit with 0.5 $\mu$ m MOSFETs | 148 |

|----------------------------------------------------|-----|

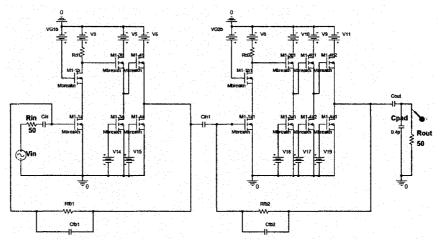

| Figure A- 2 UWB amplifier with 0.5 $\mu$ m MOSFETs | 149 |

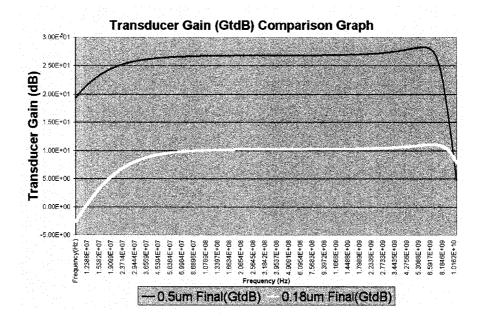

| Figure A- 3 Transducer gain comparison graph 150                                |

|---------------------------------------------------------------------------------|

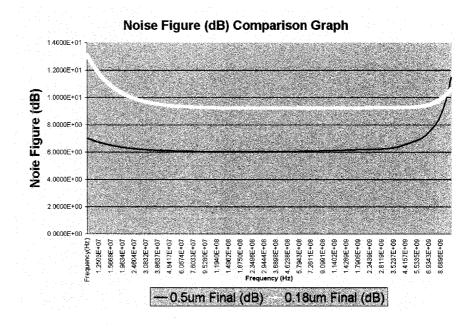

| Figure A- 4 Noise Figure (dB) comparison graph 151                              |

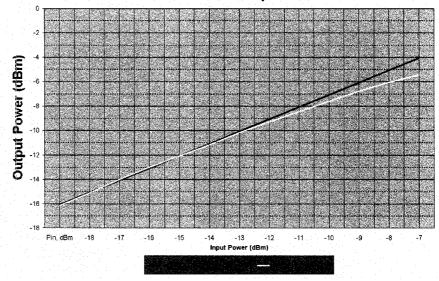

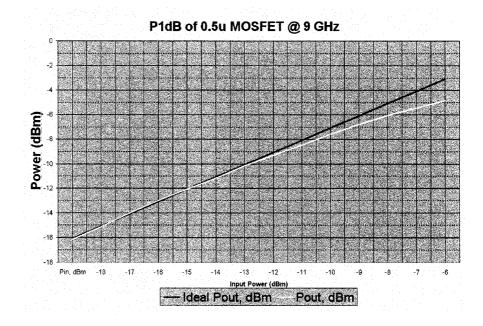

| Figure A- 5 P1dB of 0.18 $\mu$ m MOSFET amplifier                               |

| Figure A- 6 P1dB of 0.5 $\mu$ m MOSFET amplifier                                |

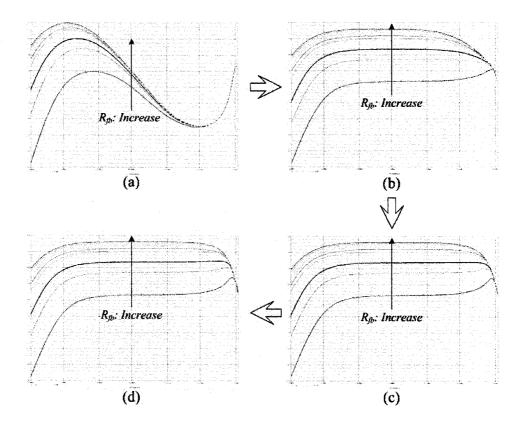

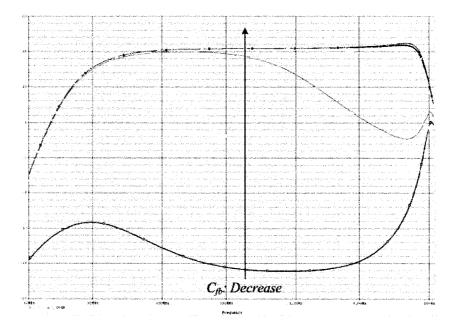

| Figure A-7 Schematic with R-C parallel-connected feedbacks                      |

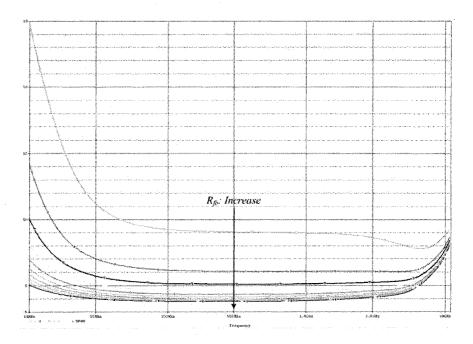

| Figure A-8 Transducer gains ( $G_t$ dB) with different feedback resistances and |

| capacitances155                                                                 |

| Figure A- 9 Transducer gain ( $G_t$ dB) with different feedback capacitances    |

| Figure A- 10 Noise figure (dB) variations with different feedback resistances   |

#### LIST OF TABLES

| Table 1 Effects on feedback resistance (NF <sub>min</sub> & G <sub>max</sub> ) |

|--------------------------------------------------------------------------------|

| Table 2 Simulation results of broadband LNA    15                              |

| Table 3 Summary of the simulation result of the referenced papers    20        |

| Table 4 Bandwidth versus n                                                     |

| Table 5 UWB quality characteristics    60                                      |

| Table 6 Optimization table of each bias voltage (CG)    97                     |

| Table 7 Optimization table of each bias voltage (CS)    102                    |

| Table 8 MOSFET width effects comparison table    107                           |

| Table 9 Resistances effect comparison table    112                             |

| Table 10 Bias voltage comparison table    116                                  |

| Table 11 Drain voltage comparison table    121                                 |

| Table 12 Bias voltage of CS comparison table    126                            |

| Table 13 MOSFET width effects comparison table    132                          |

| Table 14 Resistances effect comparison table    137                            |

#### CHAPTER 1

#### **INTRODUCTION**

Since UWB technology had been approved for commercialization by FCC, many engineers have been researching to meet its requirements. One of the requirements is the amplifier. It has been a technical challenge because UWB requires Ultra-Wideband as it represents. Therefore, many people have tried to breakthrough it and introduced several different approaches.

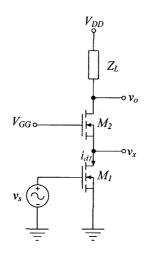

In this thesis, cascoded type which is among the approaches will be introduced. Though it gives better performances versus single stages of MOSFET amplifiers, such as Common-Source and Common-Gate, its performances should be enhanced to meet UWB requirements, especially frequency response. In addition, many other performances are needed to be enhanced as well, such as Transducer gain, total power consumption, and Noise Figure, etc. This thesis will show various optimizations of the introduced amplifier for UWB applications include the feedback topologies.

In chapter 2, the UWB technologies and applications will be briefly introduced. In chapter 3, previous approaches to the design of UWB amplifiers will be presented with comparisons. In chapter 4, at first fundamental theories of single MOSFETs<sup>\*</sup> amplifiers will be re-visited and the technical limitations for UWB applications will be shown and then the proposed solution of this thesis which is a cascoded type will be shown with advantages against single MOSFET amplifiers. After this, the simulation of the initial

1

schematic platform will be shown. As stated previously, the initial platform should be enhanced to satisfy the UWB application, so that multistage approach will be introduced with its effects. In chapter 5, the optimizations of the proposed design will be shown. In this chapter, feedback topologies will be introduced to enhance the gain flatness and 3 dB bandwidth with eliminating passive elements. In chapter 6, the measurements of proposed design will be presented. Finally, in chapter 7, conclusions will be stated.

Additionally, in the appendices, the optimizations with 0.5  $\mu$ m MOSFETs amplifier will be shown and a different design with a different feedback topology will be shown.

The lastly shown design in appendix with a different feedback topology gives much better Noise Figure which is one of the most important factors in receivers. Unlikely transmitters, receivers require a low noise to amplify the received signal with minimizing the noise. However, the design proposed in this thesis does not really satisfy the desired noise figure.

Though it gives a promising simulation result of noise figure, its research has not been done thoroughly because the new feedback topology has been found in the closing period of my research.

2

#### CHAPTER 2

#### **UWB INTRODUCTION**

Since the 1980s UWB technology has been researched for military purposes and recently it has shown possibilities of using it in wireless applications. Though it has interference issues with current wireless communications, the FCC (Federal Communications Commission) approved UWB for commercial applications on 2002.

UWB is a wireless communications technology which enables highly reliable communications through high-speed and high-performance wireless networks. In addition, the technology can be used for military purposes which require low interception and detection devices, and anti-collision devices, etc.

#### 2.1 UWB DEFINITION

UWB refers to electromagnetic signal waveforms that have instantaneous fractional bandwidths greater than 0.25 with respect to a center frequency. There are two other classes identified by signal fractional bandwidth: narrowband, where the fractional bandwidth is less than 1%, and wideband, with a fractional bandwidth from 1 to 25%. Therefore, it differs substantially from conventional narrowband radio frequency (RF).

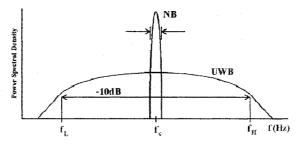

Figure 1 Definition of UWB

Fractional BW:

$$\frac{f_H - f_L}{\left(\frac{f_H + f_L}{f_C}\right)} \ge 0.20$$

Where

$f_H$ : Upper 10 dB down point

$f_L$ : Lower 10 dB down point

$f_C$ : Center frequency

#### 2.2 UWB FREQUENCY ALLOCATIONS AND POWER LIMITS

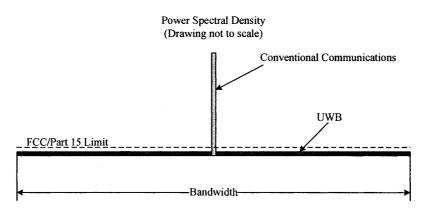

Figure 2 Comparison of conventional NB and UWB signal concept

UWB is a unique and new usage of a recently legalized frequency spectrum. UWB devices can use frequencies from 3.1 GHz to 10.6 GHz – a band more than 7 GHz wide. Each channel can have a bandwidth of more than 500 MHz, depending on its center frequency.

To allow for such a large signal bandwidth, the FCC put in place severe broadcast power restrictions. But by doing so, UWB devices can make use of an extremely wide frequency band while not emitting enough energy to be noticed by narrower band devices nearby, such as 802.11a/r radios.

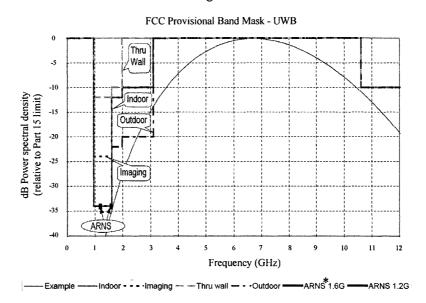

Strict power limits (Figure 3) mean the devices themselves must be low-power consumers. Because of the low power requirements, it is feasible to develop cost-effective CMOS implementations of UWB devices.

Regulation

Figure 3<sup>1</sup> FCC UWB Limits

\* ARNS: Aeronautical navigation services

#### 2.3 APPLICATIONS

UWB applications can be divided into the military and commercial areas.

#### 2.3.1 MILITARY APPLICATIONS

Fine spatial resolution, low probability of interception, and noninterfering signal waveforms are some of the features that make UWB radar appealing. Therefore, UWB radar offers solutions to defense requirements such as passive target identification, target imaging and discrimination, and signal concealment from electronic warfare equipment and antiradiation missiles.

The UWB radar's fine spatial resolution gives a capability for target imaging and discrimination of targets. Target clutter separation is a major problem in look-down radar

<sup>&</sup>lt;sup>1</sup> Taken from "UWB Applications and Interference (UWB Colloquium 23<sup>rd</sup> July 2002)," Presenter: Ewan Frazer

and limits the ability to detect small radar cross section (RCS) low altitude flying targets or surface. In addition, the UWB radar could provide features such as detection surveillance or tracking systems with a low probability of detection by spectral characteristics of the signal.

#### 2.4 COMMERCIAL (WIRELESS) APPLICATIONS

UWB technology offers a solution for the bandwidth, cost, power consumption, and physical size requirements of next-generation consumer electronic devices. UWB enables wireless connectivity with consistent high data rates across multiple devices and PCs within the digital home and the office. This emerging technology provides the high bandwidth that multiple digital video and audio streams require throughput the home<sup>2</sup>.

A number of practical usage scenarios are well suited to UWB. In these scenarios system implementations based on UWB Radio Technology could be beneficial and potentially welcomed by industry and service providers alike<sup>3</sup>:

- High-data-rate wireless personal are network (HDR-WPAN)

- Wireless Ethernet interface link (WEIL)

- Intelligent wireless are network (IWAN)

- Outdoor peer-to-peer network (OPPN)

<sup>&</sup>lt;sup>2</sup> Intel White paper, "Ultra-Wideband (UWB) Technology."

<sup>&</sup>lt;sup>3</sup> Composite Reconfigurable Wireless Networks: The EU R&D Path Towards 4G, "Ultra-Wideband Radio Technology: Potential and Challenges Ahead." By Domencio Porcino, Phillips Research and Walter Hirt, IBM Zurich Research Laboratory

#### CHAPTER 3

#### PREVIOUS APPROACHES TO THE DESIGN OF UWB AMPLIFIERS

Since the FCC approved UWB technology for commercialization, various approaches have been made to the design of CMOS-based UWB amplifiers. In this section, the different methods shown below will be shown and compared.

- 3.1 10.6 GHz CMOS cascaded two-stage distributed amplifier for ultrawideband application

- Ultra-wideband CMOS low noise amplifier with active input matching

- Design of CMOS UWB low noise amplifier with cascode feedback

- An ultra-wideband CMOS low noise amplifier for 3 5 GHz UWB system

#### 3.1 3.1 ~ 10.6 GHz CMOS CASCADED TWO-STAGE DISTRIBUTED AMPLIFIER FOR ULTRA-WIDEBAND APPLICATION [1]

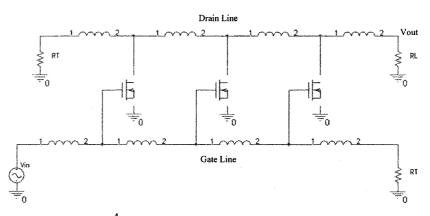

The work employed a topology in which several gain stages are in parallel and series-inductors are introduced to separate capacitances of the input and output node of adjacent gain stages.

Figure 4<sup>4</sup> Three-stage distributed amplifier

This topology builds two artificial transmission lines, a gate and a drain line as shown in Figure 4. Output current is combined additively by the current flowing from each gain stage.

This topology results in low gain with very wide bandwidth.

A 3.1~10.6 GHz CMOS Cascaded Two-stage Distributed Amplifier for Ultra-Wideband Application has been proposed by Kuan-Hung Chen and Chorng-Kuang Wang in Aug. 4-5, 2004 IEEE Asia-Pacific Conference on Advanced System Integrated Circuits [1].

This paper proposed a cascaded two-stage distributed amplifier (CTDA) as shown in Figure 10 to give higher gain, better input-output isolation, and high output impedance.

<sup>&</sup>lt;sup>4</sup> Redrawn the Fig. 1 from the reference [1]

The CTDA can achieve a voltage gain of 12~24 dB using less power consumption. In this work, an 18 dB voltage gain CTDA consuming only 54 mW has been presented for UWB application and the noise figure is between 5 dB and 7 dB.

Figure 5<sup>5</sup> Cascaded two-stage distributed amplifier

<sup>&</sup>lt;sup>5</sup> Redrawn the Fig. 3 from the reference [1]

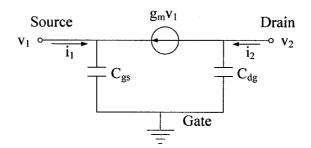

#### 3.2 ULTRA WIDEBAND CMOS LOW NOISE AMPLIFIER WITH ACTIVE INPUT MATCHING [2]

To improve impedance matching for the full band of frequency of operation, there are three main wideband topologies – resistive termination, shunt series feedback, and common gate.

Though all these three methods provide wideband matching at the price of increase noise, the common gate (CG) topology can be a good candidate for wideband impedance matching.

In [2], the authors propose a new LNA with broadband input matching and excellent gain flatness operating at the frequency range of 3.1 GHz to 4.8 GHz with 0.18  $\mu$ m CMOS process.

Figure 6<sup>6</sup> Common Gate small signal equivalent circuit

The first step is the selection of transistor size and the bias point of M1 to yield  $\operatorname{Re}|Z_{11}| = \frac{1}{g_m} = 50\Omega$ .

<sup>&</sup>lt;sup>6</sup> Redrawn the Figure 1. (b) from the reference [2]

Figure 7<sup>7</sup> LNA circuit schematic

The next step is the selection of optimal bias point of second stage of M2, so that it operates at its maximum  $f_T$ .

In addition, this paper uses a shunt resistor feedback configuration to reduce  $|S_{12}|$ and noise figure. Also, with adding an inductor  $L_f$  in the feedback path, the gain flatness at higher frequencies can be improved.

This paper shows that the proposed design can achieve with 0.18  $\mu$ m CMOS at the frequency range of 3.1 GHz to 4.8 GHz as follows.

- Noise Figure (dB): 3.95 dB to 4.3 dB

- $S_{12}$ : less than -43 dB

- Power Gain: 16.5 dB

<sup>&</sup>lt;sup>7</sup> Redrawn the Figure 2 from the reference [2]

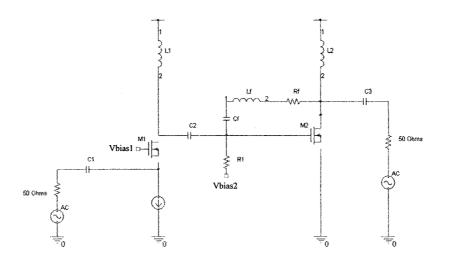

# 3.3 DESIGN OF CMOS UWB LOW NOISE AMPLIFIER WITH CASCODE FEEDBACK [3]

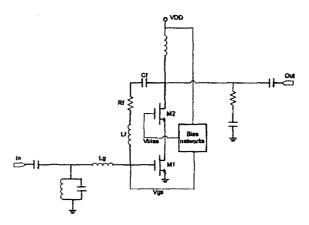

In [3], the authors describe a broadband LNA for UWB applications with 0.18  $\mu$ m CMOS technology based on cascode feedback topology.

The cascode configuration is being used to reduce the high frequency roll-off of the input devices due to the Miller effect and the negative feedback is to give better stability and bandwidth (Figure 8).

Figure 8<sup>8</sup> Typical schematic of cascode feedback LNA

To achieve a gain of over 15 dB and the NF of less than 2 dB, the feedback resistance was chosen to be between 800  $\Omega$  and 1000  $\Omega$  (Table 1).

Table 1<sup>9</sup> Effects on feedback resistance (NF<sub>min</sub> & G<sub>max</sub>)

| Feedback Resistance | NF <sub>min</sub> (dB) | G <sub>max</sub> (dB) |

|---------------------|------------------------|-----------------------|

| 2000 Ω              | 1.08                   | 19.16                 |

| 1000 Ω              | 1.44                   | 16.22                 |

| 800 Ω               | 1.59                   | 15.22                 |

<sup>8</sup> Redrawn the Fig. 1. from the reference [3]

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

| 500 Ω | 2.01 | 13.0  |

|-------|------|-------|

| 300 Ω | 5.15 | 10.37 |

A broad matching technique with a lossy gain-compensating network such as aresonant circuit [4] provides lower input reflection coefficients and a lower NF because a lossy resonant circuit can imitate the behavior of a negative capacitor or inductor in the resonance frequency range.

The resonant circuit for broadband input matching is shown in Figure 9<sup>9</sup>. The gate inductor (L<sub>g</sub>) is applied to form 50  $\Omega$  input match as well as increasing gain.

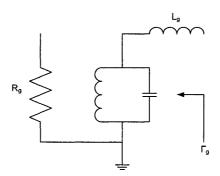

Figure 9 The resonant circuit for broadband input matching

<sup>&</sup>lt;sup>9</sup> Taken from the reference [3]. (Fig. 3.)

Figure 10<sup>10</sup> The complete schematic of LNA

The designed circuit schematic of the CMOS cascode feedback LNA is shown in Figure 10. In Figure 10, the RC feedback ( $R_f \& C_f$ ) in cascode circuit improves the  $S_{11}$ . The inductor ( $L_f$ ) in the feedback stage is used to broaden bandwidth and to improve gain flatness at the upper band edge.

With this proposed design, a maximum power gain of 15.3 dB at 4 GHz and a minimum power gain of 14.5 dB at 7 GHz were achieved. The flatness of gain within 0.8 dB in the frequency range where achieved. The noise figure was 1.4 dB and 1.9 dB between 3 GHz and 7 GHz.

Simulation results are shown in Table 2.

Table 2<sup>11</sup> Simulation results of broadband LNA

| Process        | 0.18 μm RF CMOS |  |

|----------------|-----------------|--|

| Supply Voltage | 1.8 V           |  |

<sup>10</sup> Taken from the reference [3]. (Fig. 6.)

<sup>11</sup> Redrawn the Table II from the reference [3]

| Frequency Range   | 3 ~ 7 GHz               |  |

|-------------------|-------------------------|--|

| Power Gain (S21)  | 15 dB                   |  |

| Gain Flatness     | < 0.8 dB                |  |

| Noise Figure (NF) | < 1.9 dB @ 7 GHz        |  |

| Power Consumption | 21 mW with bias network |  |

At the operation voltage of 1.8 V single supply, this amplifier has less than 1.9 dB noise figure, 15 dB gain within flatness 0.8 dB, and less than -10 dB input and output return loss from 3 GHz to 7 GHz with 21 mW power consumption.

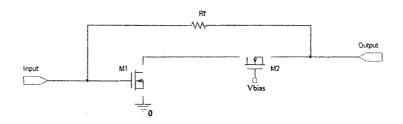

#### 3.4 AN ULTRA-WIDEBAND CMOS LOW NOISE AMPLIFIER FOR 3-5 GHz UWB SYSTEM [5]

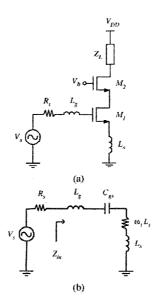

In this paper, an ultra-wideband (UWB) CMOS low noise amplifier (LNA) topology that combines a narrowband LNA with a resistive shunt-feedback is proposed.

Figure  $11^{12}$ (a) shows a typical narrowband cascade LNA topology. In Figure 11(a), the inductor  $L_s$  is added for simultaneous noise and input matching and  $L_g$  for the impedance matching between the source resistance  $R_s$  and the input of the LNA [6].

Figure 11 Narrowband LNA topology. (a) Overall schematic. (b) Small-signal equivalent circuit at the input.

Figure 11(b) shows the small –signal equivalent circuit for the input part of the

overall LNA, where  $C_{gs}$  represents the gate-source capacitance of the input transistor  $M_1$ .

The  $\omega_T$  represents the cutoff frequency of transistor  $M_I$ , the equality factor Q of

the series resonating input circuit shown in Figure 11(b) can be given by [7]

<sup>12</sup> Copied from the reference [5] (Fig. 1.)

$$Q_{NB} = \frac{1}{(R_s + \omega_T L_s) \cdot \omega_0 \cdot C_{gs}}$$

(3.1)

where  $\omega_0$  represents the resonant frequency. Since the fractional -3 dB bandwidth of a typical *RLC* series resonant circuit is inversely proportional to its *Q*-factor (BW<sub>-3 dB</sub> =  $\omega_0/Q_{NB}$ ), the LNA shown in Figure 12 (a) is unsuitable for wideband application.

Figure 12<sup>13</sup> UWB LNA topology.

(a) Overall schematic. (b) Small-signal equivalent circuit at the input.

where  $\omega_0$  represents the resonant frequency. Since the fractional -3 dB bandwidth of a typical *RLC* series resonant circuit is inversely proportional to its *Q*-factor (BW<sub>-3 dB</sub> =  $\omega_0/Q_{NB}$ ), the LNA shown in Figure 8 (a) is unsuitable for wideband application.

$<sup>^{13}</sup>$  Copied from the reference [5] (Fig. 2.)

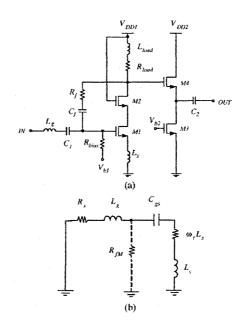

Figure 12 (a) shows the proposed wideband LNA topology. In Figure 12 (b), the resistor  $R_{fM} [= R_f / (1 - A_v)]$  represents the Miller equivalent input resistance of  $R_f$ , where Av is the open-loop voltage gain of the LNA.

In Figure 12 (a),  $R_f$  is added as a shunt-feedback element,  $L_{load}$  is used as a shunt peaking inductor at the output [8], the capacitor  $C_f$  is used for ac coupling purpose, the source follower of  $M_3$  and  $M_4$  is added for measurement purpose only, and  $C_1$  and  $C_2$  are ac coupling capacitors.

From the Figure 12 (b), the input impedance is determined by  $\omega_T L_s$ . Therefore, the feedback resistor  $R_f$  plays a main role to reduce the *Q*-factor of the resonating narrowband LNA input circuit. The *Q*-factor of the circuit shown in Figure 12 (b) can be approximately given by

$$Q_{WB} \approx \frac{1}{\left[R_{s} + \omega_{T}L_{s} + \frac{\left(\omega_{o}L_{g}\right)^{2}}{R_{fM}}\right] \cdot \omega_{0} \cdot C_{gs}}.$$

(3.2)

From (1.2), and considering the inversely linear relation between the -3 dB bandwidth and the *Q*-factor, the narrowband LNA in Figure 12 (a) can be converted into a wideband amplifier by the proper selection of  $R_{f}$ .

This topology is applied for a 3.1-5 GHz UWB amplifier implementation based on 0.18  $\mu$ m CMOS technology. The measured results show more than 9 dB of input return loss, a higher than 11 dB output return loss, a peak gain of 9.8 dB over the -3 dB bandwidth of 2-4.6 GHz, while dissipating 7 mA from 1.8 V supply. The minimum NF is 2.3 dB at 3 GHz and stays at less than 3 dB up to 4 GHz, but rises up to 5.2 dB at 5 GHz.

## 3.5 SUMMARY OF DIFFERENT APPROACHES

The following Table 3 shows the summarized simulation result from the referenced papers.

Table 3 Summary of the simulation result of the referenced papers

| Referenced Paper                                                                                          | Technology   | Frequency (GHz) | E Figin (dB)                                    | 4 <b>T</b>    | Power Consumption<br>(mW)                    |

|-----------------------------------------------------------------------------------------------------------|--------------|-----------------|-------------------------------------------------|---------------|----------------------------------------------|

| 1. A 3.1 ~ 10.6 GHz CMOS<br>Cascaded Two-stage<br>Distributed Amplifier for<br>Ultra-Wideband Application | TSMC 0 18 µm | 3.1 ~ 10.6      | 18                                              | 5~7           | 54                                           |

| 2. Ultra Wideband CMOS<br>Low Noise Amplifier with<br>Active Input Matching                               |              | 3.1 ~ 6.1       | 15.5 ~ 17                                       | 3.9~4.3       | 21                                           |

| <ol> <li>Design of CMOS UWB<br/>Low Noise Amplifier with<br/>Cascode Feedback</li> </ol>                  |              | 3~7             | 15 dB<br>Min.: 14.5 @7 GHz<br>Max.: 15.3 @4 GHz |               | 21 (w/bias network)<br>15 (w/o bias network) |

| 4. An Ultra-Wideband<br>CMOS Low Noise Amplifier<br>for 3-5 GHz UWB System                                |              | 2~4.6           | 9.8                                             | 2.3 (minimum) | 12.6 (only core LNA)                         |

Table 3. A summary of the simulation result of the referenced papers.

Based on the simulation (measured) data, paper 1 covers whole UWB frequency band with highest gain and highest power consumption. Paper 3 shows overall better result than paper 2. Paper 4 adopted a feedback resistor to reduce the *Q*-factor of the narrowband amplifier input impedance. As a result it shows advantages in overall performance (NF, power gain, power dissipation, chip size, number of external components, etc.), compared to the distributed and conventional shunt-feedback amplifiers for UWB applications.

# CHAPTER 4

# DESIGNING UWB AMPLIFIER

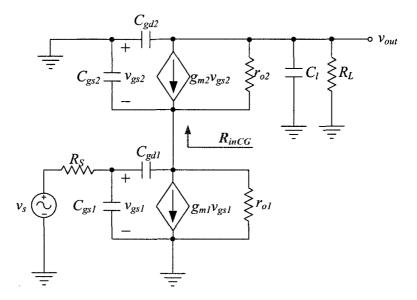

In this section, the basic theories of MOSFET, common-source single stage and common-gate MOSFET, and cascode topology will be shown and analyzed. By analyzing the high frequency characteristics of single stage MOSFET amplifiers, the need of a new design of, such as cascode topology will be shown.

Though cascoded topology gives better performances against single MOSFET amplifiers, it is required to enhance them to meet UWB requirements. Various considerations in broadband and multistage amplifiers will be shown.

# 4.1 MOSFET THEORY

In this section, the basic materials for MOSFET will be reviewed. These information have taken from various materials [9] [10] [11] [12] [13] [14] [15] [16].

# 4.1.1 MOSFET FUNDAMENTALS

In this chapter we are concerned with describing the fundamentals of MOSFET. MOS structures are assumed ideal and the long-channel enhancement-mode MOSFETs are focused.

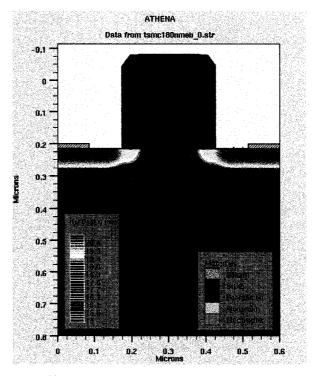

Figure 13<sup>14</sup> MOSFET structure simulation by Silvaco

<sup>&</sup>lt;sup>14</sup> Project done for ELEE63201 with Edward Banatoski, Ph.D. Simulated TSMC 180nm MOSFET through Silvaco Athena.

As shown in Figure 13 MOSFET (Metal Oxide Semiconductor Field Effect Transistor) has a structure of source and drain diffusion to the MOS capacitor which has a vertical stacking structure of metal (Gate), oxide, and semiconductor.

The MOSFET has become by far the most widely used electronic device, especially in the design of integrated circuits (ICs), which are circuits fabricated on a single silicon chip.

Compared to BJTs, MOSFETs can be made quite small and their manufacturing process relatively simple. Also, their operation requires comparatively little power. In addition, it is possible to implement digital and analog together.

All of these properties have made it possible to build VLSI circuits such as those for memory and microprocessors.

Therefore, MOSFET-based integrated circuits have become the dominant technology in the semiconductor industry. There are thousands of MOS-transistor circuits in production ranging from rather simple logic gates used in digital-signal processing to custom designs with both logic and memory functions on the same silicon chip.

#### 4.1.2 MOSFET IV CHARACTERISTICS

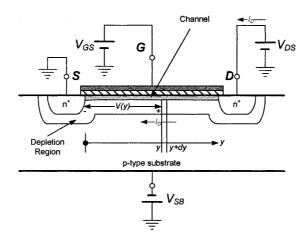

The next Figure 14 shows the MOSFET with proper bias voltages.

Figure 14 n-MOSFET device with bias voltages

When  $V_{GS} < V_T$ , the MOSFET is cutoff. If  $V_{GS} > V_T$ , inversion occurs and a conducting channel establishes. The channel conductivity is determined by the vertical electrical field, which is controlled by the voltage,  $V_{GS} > V_T$ . Nonzero  $V_{DS}$  produces a horizontal electrical field and causes current  $I_D$  to flow.

The drain current  $I_D$  is

$$I_{D} = K_{n} \frac{W}{L} \left( (V_{GS} - V_{T}) V_{DS} - \frac{1}{2} V_{DS}^{2} \right)$$

(4.1)

Where

$$K_{n} \triangleq \mu_{n} C_{OX} = \frac{\mu_{n} \varepsilon_{OX}}{t_{OX}}$$

$$(4.2)$$

$C_{ox}$ : The gate oxide capacitance per unit area

24

$$\left(=\frac{\varepsilon_{ox}}{t_{ox}}=\frac{3.9\cdot\varepsilon_{o}}{t_{ox}}=\frac{3.9\cdot(8.854\times10^{-14})}{t_{ox}}\right)$$

In saturation region (4.1) becomes as follows with  $(V_{GS} - V_T) = V_{DS}$

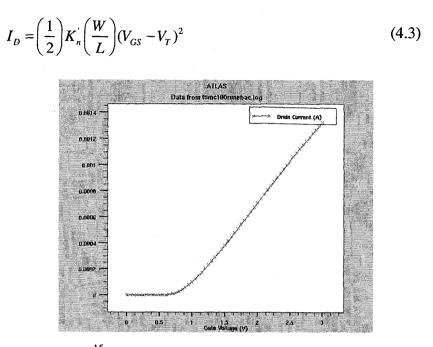

Figure  $15^{15}$  MOSFET  $V_G$  -  $I_D$  Graph by Silvaco simulation

Furthermore, (4.3) becomes as follows with a channel-length modulation

$$I_{D} = \left(\frac{1}{2}\right) K_{n}' \left(\frac{W}{L}\right) (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS})$$

(4.4)

Where

$$\lambda$$

: Channel-length modulation factor (= $\frac{1}{V_A}$ ) (4.5)

Figure 15 shows the relation between drain current  $I_D$  and gate voltage  $V_G$ . The drain current starts flowing when  $V_G$  is larger than  $V_T$  and gradually increase until a

<sup>&</sup>lt;sup>15</sup> Project done for ELEE63201 with Edward Banatoski, Ph.D. Simulated TSMC 180nm MOSFET through Silvaco Athena.

certain level of  $V_G$ . Based on the Figure 15, the larger  $V_G$  gives the higher  $I_D$ . However,  $V_G$  cannot be increased above a certain point (refer to the Figure 17) because the transconductance will be decreased.

#### 4.1.3 SMALL-SIGNAL EQUIVALENT CIRCUIT OF MOSFET

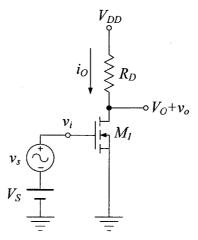

Figure 16 Common-source MOSFET amplifier circuit

## 4.2 SMALL-SIGNAL ANALYSIS

The total output current  $(i_o)$  when MOSFET  $(M_1)$  operates in saturation is as follows (neglected channel-length modulation):

$$i_{o} = \left(\frac{1}{2}\right) K_{n}' \left(\frac{W}{L}\right) (V_{GS} + v_{gs} - V_{T})^{2}$$

(4.6)

$$i_{o} = \frac{V_{DD} - (V_{o} + v_{o})}{R_{D}}$$

(4.7)

With (4.6) and (4.7), the output voltage  $(v_o)$  is shown below.

26

$$v_{o} = -R_{D}K_{n}'\left(\frac{W}{L}\right)\left\{(V_{GS} - V_{T})v_{gs} + \frac{v_{gs}^{2}}{2}\right\}$$

$$= -R_{D}K_{n}'\left(\frac{W}{L}\right)(V_{GS} - V_{T})v_{gs}\left\{1 + \frac{v_{gs}}{2(V_{GS} - V_{T})}\right\}$$

(4.8)

The small-signal output current,  $i_o = \frac{-v_o}{R_D}$ , becomes as follows.

$$i_{o} = K_{n}' \left(\frac{W}{L}\right) (V_{GS} - V_{T}) v_{gs} \left\{ 1 + \frac{v_{gs}}{2(V_{GS} - V_{T})} \right\}$$

(4.9)

From (4.8) distortions occurs when  $v_{gs}$  is large. To make the distortion rate less than 10 %, the magnitude of small-signal input voltage ( $|v_{gs}|$ ) should satisfy the following.

$$|v_{gs}| \le 0.2(V_{GS} - V_T)$$

(4.10)

When (4.10) is valid, the  $v_{s}^2$  term can be neglected from the equation (4.8) and the small-signal output voltage( $v_o$ ) and output current( $i_o$ ) can be shown as follows.

$$v_o = -R_D K_n' \left(\frac{W}{L}\right) (V_{GS} - V_T) v_{gs}$$

(4.11)

$$i_o = K_n \left(\frac{W}{L}\right) (V_{GS} - V_T) v_{gs}$$

(4.12)

#### 4.3 TRANSCONDUCTANCE

One of the most important components of a MOSFET ac analysis is find the voltage-to-current ratio (a proportional constant between  $i_o$  and  $v_{gs}$  in (4.12)). When the MOSFET operates in saturation region, it indicates how well a device converts a voltage to a current. The change in drain current that will result from a change in gate-to-source voltage can be determined using the transconductance factor  $g_m$  in the following way [10].

Figure 17<sup>16</sup> Transconductance graph from Silvaco simulation

$$g_{m} \triangleq \frac{\Delta I_{O}}{\Delta V_{GS}} = \frac{\partial i_{o}}{\partial v_{GS}}$$

(4.13)

From (4.12), transconductance( $g_m$ ) becomes as follows.

<sup>&</sup>lt;sup>16</sup> Project done for ELEE63201 with Edward Banatoski, Ph.D. Simulated TSMC 180nm MOSFET through Silvaco Athena.

$$g_{m} = K_{n}' \left(\frac{W}{L}\right) (V_{GS} - V_{T}) = \frac{2I_{O}}{\left(V_{GS} - V_{T}\right)}$$

(4.14)

Transconductance represents the sensitivity of the device: for high  $g_m$ , a small changes in  $V_{GS}$  results in a large change in  $I_O$ .

Figure 17 shows the relations between gate voltage and transconductance. There is a gate voltage which gives the maximum of transconductance. For designing amplifier, the proper gate (bias) voltage should be used.

#### 4.4 OUTPUT RESISTANCE

Increasing drain-source voltage in an n-channel MOSFET increases the width of the depletion region around the Drain and reduces the effective channel length in the saturation region. This effective is called channel-length modulation and causes the Drain current to increase.

$$r_{o} \triangleq \left\{ \frac{\partial i_{o}}{\partial v_{DS}} \right|_{at Q} \right\}^{-1} = \frac{1}{\lambda I_{o}}$$

$$(4.15)$$

#### 4.5 SINGLE STAGE MOSFET ANALYSIS

This section will show the analysis of the two different types of MOSFETs' topologies (common-source (CS) and common-gate (CG)) for high-frequency characteristics. The two main characteristics of transducer gain and high frequency response will be discussed though there are many other characteristics.

MOSFETs have internal gate capacitive effect. The gate electrode forms a parallel-plate capacitor with the channel, with the oxide layer serving as the capacitor dielectric.

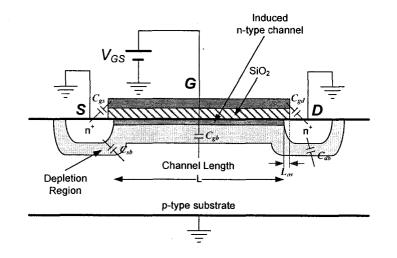

Figure 18 The cross-sectional view of a nMOSFET with various capacitances

As Figure 18 shows five main different capacitances in MOSFET. Gate capacitances are  $C_{gs}$ ,  $C_{gd}$ , and  $C_{gb}$  and depletion capacitances are  $C_{sb}$  and  $C_{db}$ .

Based on the Meyer model which is being commonly used in SPICE simulation, each gate capacitances (neglect body effect coefficient  $\gamma$ ) can be expressed as follows.

$$C_{gs} = W \cdot CGSO + \frac{2}{3}W \cdot L \cdot C_{ox}$$

(4.16)

$$C_{ad} = W \cdot CGDO \tag{4.17}$$

$$C_{ab} = L \cdot CGBO \tag{4.18}$$

where

$$CGSO = CGDO = L_{ov} \times C_{ox}$$

(4.19)

where  $L_{ov}$  is the overlap length between the gate-source and gate-drain as shown in Figure 8. The intrinsic value of  $C_{gd}$  is zero because the channel is the pinched-off at the drain end. However, the value of  $C_{gd}$  has a parasitic value due to the overlap that depends on the layout. As  $C_{gd}$  plays an important role in deciding the bandwidth of some amplifiers, its influence cannot be ignored. [11]

Here are the typical values of CGSO, CGDO, and CGBO of TSMC T3CV 0.18  $\mu$ m MOSFET<sup>17</sup>.

$$CGSO = CGDO = 7.9 \times 10^{-10}$$

(4.20)

$$CGBO = 1 \times 10^{-12}$$

(4.21)

<sup>&</sup>lt;sup>17</sup> Electrical parameters are shown in Appendix A-1.

#### 4.5.1 COMMON-SOURCE MOSFET HIGH-FREQUENCY MODEL

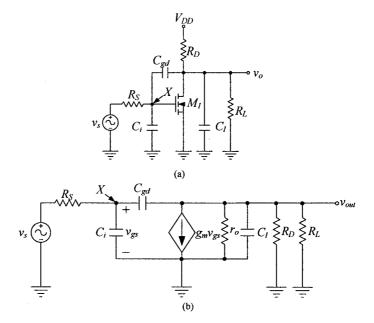

The common-source amplifier uses the gate as an input ports and drain as an output port as shown in Figure 19 which includes internal capacitances for high frequency analysis.

Figure 19 (a) Common-source MOSFET high frequency model (b) its small

signal model

Where

$C_i = C_{gs} + C_{gb}$  + input wiring capacitances

$C_l = C_{db}$  + output wiring capacitances

$C_{\rm gd}$  itself is much smaller than  $C_{\rm gs}$  and usually set to zero. However, because of

the Miller's effect, it becomes the major factor for frequency response.

# 4.5.2 TRANSDUCER GAIN $(G_T)$ OF CS MOSFET

The gain that we are interested in RF transistors is the power gain of the device, rather than just the voltage or current gain because voltage and current gains alone no longer mean anything when an impedance level changes in a circuit. [12]

Transducer Power Gain  $(G_T)$

$$G_T = \frac{P_L}{P_{AVS}} = \frac{Power \ delivered \ to \ the \ load}{Power \ available \ from \ the \ source}$$

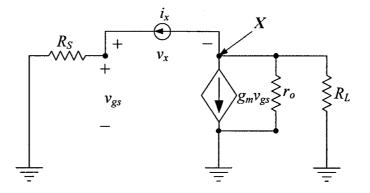

From Figure 11, the relations between  $v_{out}$  and  $v_x$  is as follows

$$v_{out} = -g_m v_x (R_L \| sC_0) = -g_m v_x \frac{R_L}{1 + R_L sC_0}$$

(4.22)

Where  $R_{L}^{'} = (r_{o} \| R_{D} \| R_{L})$  and the relations between  $v_{s}$  and  $v_{x}$  is

$$v_s = \left(1 + sR_sC_1\right)v_x \tag{4.23}$$

Therefore, voltage gain  $\left(\frac{v_{out}}{v_s}\right)$  becomes

$$\frac{v_{out}}{v_s} = \frac{-g_m R'_L}{(1 + sR_s C_I)(1 + sR'_L C_O)}$$

(4.24)

From the definition of  $(G_T)$ ,

$$P_{L} = |i_{L}|^{2} R_{L} = \left|\frac{v_{out}}{R_{L}}\right|^{2} R_{L} = \frac{|v_{out}|^{2}}{R_{L}}$$

(4.25)

$$P_{AVS} = \frac{|v_{S}|^{2}}{4R_{S}}$$

(4.26)

Transducer gain  $(G_T)$  becomes

$$G_{T} = \frac{P_{L}}{P_{AVS}} = \frac{\left(\frac{|v_{out}|^{2}}{R_{L}^{'}}\right)}{\left(\frac{|v_{S}|^{2}}{4R_{S}}\right)} = 4\frac{R_{S}|v_{out}|^{2}}{R_{L}^{'}|v_{S}|^{2}} = 4\left(\frac{R_{S}}{R_{L}^{'}}\right)\left|\frac{v_{out}}{v_{S}}\right|^{2}$$

(4.27)

Therefore, by substituting (4.27) with (4.24), transducer gain  $(G_T)$  of a single stage CS amplifier becomes

$$G_{T}(s) = 4 \left(\frac{R_{s}}{R_{L}}\right) \left| \frac{g_{m}R_{L}}{(1 + sR_{L}C_{o})(1 + sR_{s}C_{I})} \right|^{2}$$

(4.28)

# 4.5.3 FREQUENCY RESPONSE OF CS MOSFET

The frequency of the applied signal can have a very important effect on the response of a single-stage or multistage network. The frequency dependent parameters of the small-signal equivalent circuits and the stray capacitive elements associated with the active device and network will limit the high-frequency response of the system.

In this section the frequency response of CS amplifier in high-frequency will be analyzed to estimate the upper 3 dB frequency.

From (4.24), high frequency gain of the CS amplifier is as follows

$$|A_{\nu}(s)| = \left|\frac{v_{out}(s)}{v_{s}(s)}\right| = \left|\frac{A_{M}}{(1 + sR_{s}C_{I})(1 + sR_{L}C_{O})}\right|$$

(4.29)

Where  $A_{\mathcal{M}} \left(= g_{\mathcal{M}} R_{L}^{'}\right)$  is mid-band gain.

Equation (4.29) can be rearranged as follows

$$A_{v}(s) = \frac{v_{out}(s)}{v_{s}(s)} = \frac{A_{M}}{\left(1 + \frac{s}{\omega_{P1}}\right)\left(1 + \frac{s}{\omega_{P2}}\right)}$$

(4.30)

From (4.30) the input pole  $\omega_{P1}$  and the output pole  $\omega_{P2}$  are as follows

$$\omega_{P1} = \frac{1}{R_s C_I} = \frac{1}{R_s \left( C_{gs} + (1 + A_v) C_{gd} \right)}$$

(4.31)

$$\omega_{P2} = \frac{1}{R_L' C_0} = \frac{1}{R_L' \left( C_{db} + \left( 1 + \frac{1}{A_v} \right) C_{gd} \right)}$$

(4.32)

$$\approx \frac{1}{R_L' \left( C_{db} + C_{gd} \right)} \qquad (\because A_v \gg 1)$$

By comparing the (4.31) and (4.32), the  $\omega_{P1}$  is the dominant pole of the commonsource amplifier and becomes

$$\omega_{P1} = \omega_{H} = \frac{1}{R_{s} \left( C_{gs} + (1 + A_{v}) C_{gd} \right)}$$

(4.33)

Therefore, bandwidth (BW) of CS amplifier is

$$BW \triangleq f_H - f_L \cong f_H = \frac{1}{2\pi \cdot R_s \left( C_{gs} + (1 + A_v) C_{gd} \right)}$$

(4.34)

The multiplication effect that  $C_{gd}$  undergoes comes about because it is connected between two nodes whose voltages are related by a large negative gain  $(1 + A_{p})$ . This Miller effect causes the CS amplifier to have a large total input impedance  $C_{I}$  and hence a low  $\omega_{H}$ .

#### 4.6 COMMON-GATE MOSFET HIGH-FREQUENCY MODEL

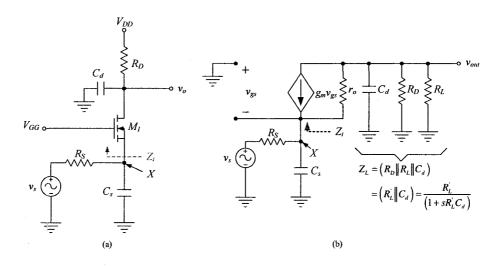

Common-gate amplifier applies DC bias voltage into gate node, input voltage into source node, and uses drain as an output port as shown in Figure 20. This amplifier gives large positive voltage gain with low input resistance and high output resistance.

Figure 20 (a) Common-gate MOSFET high frequency model and (b) highfrequency small signal model

# 4.6.1 TRANSDUCER GAIN $(G_{\tau})$ OF CG MOSFET

To find the transducer gain  $(G_T)$ , Figure 20 (b) is re-arranged as shown in Figure

21. [13]

By applying KCL at node X, we can find the current  $(i_s)$  flows at the resistor

$(R_s)$

$$i_s + i_{ro} = g_m v_x + i_x$$

(4.35)

$$i_{s} = g_{m}v_{x} + i_{x} - i_{ro} = i_{x} + i_{L} = sC_{i}v_{x} + \frac{v_{out}}{Z_{L}}$$

(4.36)

Noting that the supply voltage must equal voltage across  $R_s$  plus  $v_x$  as follows

$$v_{s} = R_{s}i_{s} + v_{x} = \left(sC_{i}v_{x} + \frac{v_{out}}{Z_{L}}\right)R_{s} + v_{x}$$

$$= \left(sR_{s}C_{i} + 1\right)v_{x} + \left(\frac{R_{s}}{Z_{L}}\right)v_{out}$$

$$(4.37)$$

$$V_{out}$$

$$V_{out}$$

$v_{s} \bigcirc C_{s} \longrightarrow v_{gs}$

$Z_L$

From (4.37),  $v_x$  can be expressed as follows

$$v_{x} = \frac{\left(v_{s} - \left(\frac{R_{s}}{Z_{L}}\right)v_{out}\right)}{\left(1 + sR_{s}C_{i}\right)}$$

(4.38)

Also the voltage  $v_{out}$  must equal  $v_x$  plus the voltage across  $r_o$

$$v_{out} = v_{r_o} + v_x = r_o \left( g_m v_x - i_L \right) + v_x$$

=  $\left( 1 + g_m r_o \right) v_x - r_o i_L = \left( 1 + g_m r_o \right) v_x - \left( \frac{r_o}{Z_L} \right) v_{out}$  (4.39)

With applying (4.39), we can have the relations between  $v_{out}$  and  $v_s$  as follows.

$$v_{out} = (1 + g_m r_o) \frac{\left(v_s - \left(\frac{R_s}{Z_L}\right) v_{out}\right)}{(1 + sR_sC_i)} - \left(\frac{r_o}{Z_L}\right) v_{out}$$

$$= \frac{(1 + g_m r_o)}{(1 + sR_sC_i)} v_s - \left(\frac{(1 + g_m r_o)R_s + r_o(1 + sR_sC_i)}{Z_L(1 + sR_sC_i)}\right) v_{out}$$

(4.40)

From (4.40)  $\left(\frac{v_{out}}{v_s}\right)$  can be find as follows.

$$\left(\frac{v_{out}}{v_{s}}\right) = \left(\frac{\frac{(1+g_{m}r_{o})}{(1+sR_{s}C_{i})}}{1+\left(\frac{(1+g_{m}r_{o})R_{s}+r_{o}(1+sR_{s}C_{i})}{Z_{L}(1+sR_{s}C_{i})}\right)}\right)$$

(4.41)

$$= \left(\frac{\left(1+g_m r_o\right)}{\left(1+s R_S C_i\right)\left(1+\frac{r_o}{Z_L}\right)+\left(1+g_m r_o\right)\left(\frac{R_S}{Z_L}\right)}\right)$$

Where,

$$Z_{L} = \left(R_{D} \| R_{L} \| C_{d}\right) = \left(R_{L} \| C_{d}\right) = \frac{R_{L}}{\left(1 + sR_{L}C_{d}\right)}$$

(4.42)

Therefore,

$$\left(\frac{v_{out}}{v_s}\right)$$

becomes as follows

38

$$\frac{(1+g_m r_o)R_L}{\left(\left(R_L + r_o + (1+g_m r_o)R_s\right) + s\left(R_S(R_L + r_o)C_i + r_oR_LC_d + R_SR_L(1+g_m r_o)C_d\right) + s^2 r_oR_SR_LC_iC_d\right)}$$

(4.43)

The transducer gain  $(G_T)$  of a single stage CG amplifier becomes

$$G_{T}(s) = 4 \left( \frac{R_{s}}{R_{L}} \right) \times$$

$$\left| \frac{(1 + g_{m}r_{o})R_{L}}{\left| \left( \left( R_{L} + r_{o} + (1 + g_{m}r_{o})R_{s} \right) + s \left( R_{s}(R_{L} + r_{o})C_{i} + r_{o}R_{L}C_{i} + R_{s}R_{L}(1 + g_{m}r_{o})C_{d} \right) + s^{2}r_{o}R_{s}R_{L}C_{i}C_{d} \right|^{2} \right|^{2}$$

$$(4.44)$$

# 4.6.2 FREQUENCY RESPONSE OF CG MOSFET

Finding the input impedance of CG amplifier make it easier to find the frequency response of the CG MOSFET.

To find the input impedance  $(Z_{in})$  of CG amplifier, we need an input impedance circuit shown in Figure 22.

Figure 22 Re-arranged CG MOSFET for input impedance,  $Z_{in}$

By KCL at node X of Figure 14 is

$$i_{x} = g_{m}v_{x} - i_{r_{0}} = g_{m}v_{x} - \frac{Z_{L}i_{x} - v_{x}}{r_{0}}$$

(4.45)

Therefore, the input impedance  $\left(Z_{in} = \frac{v_x}{i_x}\right)$  is

$$Z_{in} = \frac{r_o + Z_L}{1 + g_m r_o}$$

(4.46)

From Figure 13 (b),

$$C_s = C_{gs} + C_{bs} \tag{4.47}$$

$$C_d = C_{gd} + C_{bd} \tag{4.48}$$

Where  $C_{bs}$  is the junction capacitance between bulk and source and  $C_{bd}$  is the junction capacitance between bulk and drain and omitted for simplification.

Dominant pole  $\omega_p$  becomes

$$\omega_p = \omega_H = \frac{1}{\left(R_s \| Z_{in}\right) \cdot C_i} \tag{4.49}$$

The input impedance  $Z_{in} = \frac{r_o + Z_L}{1 + g_m r_o}$  varies depends on the  $Z_{in}$  as

$$Z_{in,MIN}\Big|_{at \ Z_{\rm L}=0} \cong \frac{1}{g_m} \tag{4.50}$$

$$Z_{in,MAX.}\Big|_{at \ Z_{L}=\infty} = \infty \tag{4.51}$$

Therefore, the dominant pole exists between

$$\frac{1}{R_s \cdot C_i} \le \omega_H \le \frac{1}{\left(R_s \| \frac{1}{g_m}\right) \cdot C_i}$$

(4.52)

As a result, the minimum of  $\omega_{H}$  can be expressed as follows.

40

$$\frac{1}{R_s \cdot C_i} = \frac{1}{R_s \cdot \left\{ W \cdot CGSO + \frac{2}{3}W \cdot L \cdot C_{ox} \right\}}$$

(4.53)

The dominant pole of CS MOSFET amplifier which is given by (4.33) can be restated as follows to be compared with CG MOSFET amplifier.

$$\frac{1}{R_{s} \cdot \left\{W \cdot CGSO + \frac{2}{3}W \cdot L \cdot C_{ox} + W \cdot CGDO(1 + g_{m}R_{D})\right\}}$$

(4.54)

If we compare the  $\omega_{H,CS}$  (4.53) and  $\omega_{H,CG}$  (4.53), frequency response of CG amplifier is much higher than CS amplifier.

## 4.7 CASCODE AMPLIFIER TOPOLOGY

In the previous sections Common-Source and Common-Gate MOSFET configurations were presented. For conventional and narrowband purpose, the CS amplifier can be used. However, it cannot be used for UWB application because of the Miller Effect which drastically decrease the frequency response,  $\omega_{-3dB}$ . One of the possible ways of minimizing Miller effect is using a cascode topology which is shown in Figure 23.

Figure 23 Basic cascode amplifier configuration

The Drain current,  $i_{d1}$  of M1 is given as follows

$$i_{dMI} = g_{mMI} v_s \tag{4.55}$$

Therefore,  $v_x$  is given as follows

$$v_{x} = -i_{dM1} \cdot \left(r_{oM1} \| Z_{iM2}\right) \cong -i_{dM1} \cdot \left(r_{oM1} \| \frac{1}{g_{mM2}}\right)$$

$$\cong -i_{dM1} \cdot \frac{1}{g_{mM2}} = -\left(\frac{g_{mM1}}{g_{mM2}}\right) v_{s}$$

(4.56)

Where  $Z_{iM2} \cong \frac{1}{g_{mM2}}$  from (4.50)

From (4.14)

$$g_{mMI} = K_n' \left(\frac{W}{L}\right)_{MI} (V_{GS} - V_T)$$

$$g_{mM2} = K_n' \left(\frac{W}{L}\right)_{M2} (V_{GS} - V_T)$$

(4.57)

Therefore,

42

$$v_{x} = -\left(\frac{g_{mM1}}{g_{mM2}}\right)v_{s} = -\left(\frac{\left(\frac{W}{L}\right)_{M1}}{\left(\frac{W}{L}\right)_{M2}}\right)v_{s}$$

(4.58)

From (4.58) it is clear that  $v_x$  is proportional to the ratio of the widths and lengths of *M1* and *M2*. If *M1* and *M2* have same physical dimensions, the small signal gain  $\left(\frac{v_x}{v_s}\right)$

becomes -1.

As a result, the Miller effect becomes 2 (Miller constant). Therefore this cascode topology will have a better frequency response than single MOSFET CS transistors.

### 4.7.1 SMALL SIGNAL ANALYSIS OF CASCODE AMPLIFIER

The CASCODE is a very useful two-transistor stage that provides the performance of a CS stage with a much small Miller effect and much larger output resistance. Therefore, it gives better high-frequency performance and higher output resistance.

#### 4.8 OUTPUT RESISTANCE OF CASCODE

From Figure 23 output resistance  $R_{out}$  can be found as follows.

$$g_{roM2}(v_o - v_2) = i_o + g_{mM2}v_2$$

(4.59)

$$g_{roM2}(v_o - v_2) = (g_{roM1} + g_{mM2})v_2$$

(4.60)

Therefore,

$$R_{out} = \frac{\left(g_{roM1} + g_{roM2} + g_{mM2}\right)}{g_{roM1}g_{roM2}} \cong \frac{g_{mM2}}{g_{roM1}g_{roM2}} = g_{mM2}r_{oM2}r_{oM1}(4.61)$$

From (4.61) it is evident that the output resistance of CASCODE is much larger than  $r_{oMI}$ .

### 4.9 HIGH-FREQUENCY RESPONSE OF CASCODE AMPLIFIER [16]

Figure 24 is shown as a high frequency equivalent circuit. Only  $C_{gs}$  and  $C_{gd}$  will be considered for simplifications.

Figure 24 CASCODE small signal circuit for frequency response

With the open-circuit time constants, the frequency response can be estimated as

follows

$$\tau_{gsI} = C_{gsI} R_s \tag{4.62}$$

For  $\tau_{gdl}$ , at first the resistance  $R_{gdl}$  that is seen by the capacitor  $C_{gdl}$  must be

found.

### 4.9.1.1 RE-VISIT CS AMPLIFIER

Figure 24 can be re-drawn to find the  $R_{gdl}$ .

The relation between  $i_x$  and  $v_x$  is given

$$(1 + g_m R_s)i_x = -\frac{1}{(r_o || R_L)} (R_s i_x - v_x)$$

(4.63)

Therefore, the resistance seen by the capacitor  $C_{gdl}$  is

$$R_{x} = R_{gdl} = (r_{o} || R_{L}) + R_{S} (1 + g_{m} (r_{o} || R_{L}))$$

$$= (r_{o} || R_{L}) + R_{S} (1 + |A_{v}|)$$

(4.64)

Notice that the term  $R_{s}(I + |A_{v}|)$  gives the largest contribution.

Figure 25 Circuit to find  $R_{gdl}$

Therefore,  $\tau_{gdl}$  is as follows

$$\tau_{gdl} = R_{gdl} C_{gdl} \tag{4.65}$$

From the calculation of time constants it has been shown that the largest time constant is associated with the drain-gate capacitance,  $C_{gdl}$ , even though hat capacitance is numerically the smallest one. The effect of this capacitance is multiplied by the gain  $(1+|A_v|)$ . As it has been explained previously, this is called Miller effect. This effect arises from connecting a capacitance across two nodes that have inverting voltage gain between them. One of the possible solutions of this problem is to isolate this capacitor so that it no longer appears across a gain stage. [11]

The CASCODE amplifier of Figure 16 shows the elimination Miller effect by performing this isolation. The output is at the drain of M2, while the input is at the gate of M1, and there is no capacitance directly across these two nodes.

#### 4.10 TIME-CONSTANT OF A CASCODE AMPLIFIER

At first, the input resistance of CG stage is already given in (4.46).

$$R_{inCG} = \frac{r_{oM2} + R_L}{1 + g_{mM2} r_{oM2}} \cong \frac{1}{g_{mM2}} \left( 1 + \frac{R_L}{r_{oM2}} \right)$$

(4.66)

The  $R_{gdl}$  from (4.64) becomes with  $R_{inCG}$  as follows

$$R_{gdl} = \left(r_{oMl} \| R_{inCG}\right) + R_{S} \left(1 + g_{mMl} \left(r_{oMl} \| R_{inCG}\right)\right)$$

(4.67)

Therefore, the time constant  $au_{gdl}$  is given

$$\tau_{gdl} = R_{gdl}C_{gdl} = C_{gdl}\left\{ \left( r_{oMl} \| R_{inCG} \right) + R_{S} \left( 1 + g_{mMl} \left( r_{oMl} \| R_{inCG} \right) \right) \right\}$$

(4.68)

For the amplifier M2, time constants are

$$\tau_{gs2} = C_{gs2} \left( r_{oM2} \| R_{inCG} \right) \tag{4.69}$$

$$\tau_{gs2} \cong C_{gs2} R_L \tag{4.70}$$

and, finally,

$$\tau_L \cong C_l R_L \tag{4.71}$$

As a result, the bandwidth estimation is

$$BW \approx \frac{1}{\tau_{total}} = \frac{1}{\tau_{gs1} + \tau_{gd1} + \tau_{gs2} + \tau_{gd2}}$$

$$= \frac{1}{\left\{ C_{gs1} R_{S} + \left( r_{oM1} \| R_{inCG} \right) + R_{S} \left( 1 + g_{mM1} \left( r_{oM1} \| R_{inCG} \right) \right) + C_{gs2} R_{L} + C_{I} R_{L} \right\}}$$

(4.72)

#### 4.11 BROADBAND AND MULTISTAGE AMPLIFIERS

So far, CASCODE amplifier has been shown a possible topology for UWB applications. Though it gives better performances against single stage topologies, it needs enhancements of gains and bandwidths. In this section various methods will be introduced and analyzed.

#### 4.11.1 CHANNEL LENGTH

Other than that, the simulation result shown below gives the role of MOSFET channel length. One of the ways to have better bandwidth is using short channel length. This section will explain the relations between channel length and frequency bandwidth.

## 4.11.1.1 UNITY-GAIN FREQUENCY ( $\omega_T$ )

The unity-gain is defined as the frequency at which the short-circuit current-gain of the common-source configuration become unity. This measurement assumes the steady state operation with sinusoidal excitation. A current source  $i_{in}$  is applied to the gate of the device, and the output current  $i_d$  is measured in the short-circuited drain circuit.

As previously shown in (4.3) and (4.14) the drain current  $I_D$  and the transconductance  $g_m$  is given by

$$I_{D} = \left(\frac{1}{2}\right) K_{n}' \left(\frac{W}{L}\right) (V_{GS} - V_{T})^{2}$$

(4.73)

$$g_m = K_n \left(\frac{W}{L}\right) (V_{GS} - V_T) \tag{4.74}$$

Therefore, the current gain  $A_i(j\omega)$  is

$$A_{i}(j\omega) = \frac{i_{d}}{i_{in}} = \frac{g_{m}}{j\omega(C_{gs} + C_{gd})} \cong \frac{g_{m}}{j\omega C_{gs}}$$

(4.75)

The unity-gain frequency is determined as the frequency where the absolute value of the current gain becomes equal to unity. If

$$\left|A_{i}\left(j\omega\right)\right| = 1 \tag{4.76}$$

Then

$$\omega_{T} = \frac{g_{m}}{C_{gs}} = \frac{K_{n}' \left(\frac{W}{L}\right) (V_{GS} - V_{T})}{\left(\frac{2}{3}\right) W L C_{ox}}$$

(4.77)

The result (4.77) shows that  $\omega_T \propto \frac{1}{L^2}$ , i.e. that for high-frequency operation the

device should be short and that  $\omega_T \propto (V_{GS} - V_T)$ . The second proportionality means that to amplify high frequencies the device has to carry a heavy current. However, increasing power is not always possible especially for the mobile communications, etc. Therefore, using short channel transistors are much better solution [14].

# 4.11.2 SHUNT-PEAKING METHOD TO ENHANCE BANDWIDTH

If a transistor is an ideal, then the only elements that control the bandwidth are R, L, and C. It can be represented as in Figure 26. [7]

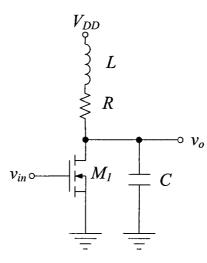

Figure 26 Shunt-peaked amplifier

As previously shown the gain of the amplifier is proportional to  $g_m R_L$ . The addition of an inductance in series with the load resistor introduces a zero. Therefore the impedance of the *RLC* network can be written as

$$Z(s) = (sL+R) \left\| \frac{1}{sC} = \frac{R\left(s\left(\frac{L}{R}\right) + 1\right)}{s^2 L C + sRC + 1}$$

(4.78)

Therefore, the magnitude of Z(s) can be expressed in frequency as follows

$$\left|Z(j\omega)\right| = R\sqrt{\frac{\left(\left(\frac{\omega L}{R}\right)^2 + 1\right)}{\left(1 - \omega^2 LC\right)^2 + \left(\omega RC\right)^2}}$$

(4.79)

51

It shows that the numerator has a term that increases with increasing frequency. In addition, the  $1 - \omega^2 LC$  term in the denominator contributes to an increase in  $|Z(j\omega)|$  for frequencies below the *LC* resonance as well.

Initially the inductor(s) will be used. However, inductors have some deficiencies of a low Q-factor and occupy a lot of chip area. Therefore, if it is possible, it is preferable not to use those. The solution with trade-offs will be shown later.

# 4.11.3 CASCADING TOPOLOGY

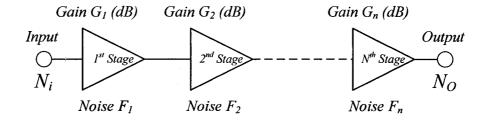

Figure 27 CASCADE topology

As shown in Figure 27 n<sup>th</sup> transistor stage connected directly to the output of a (n-1)<sup>th</sup> stage. Therefore, there will be several major elements to be considered for designing amplifiers with CASCADE topology as follows.

- Change of overall power (voltage) gain

- Change of overall Noise Figure

- Change of IP3

- Change of overall frequency response

For convenient, only dual-stage performance parameters will be analyzed for the following sub-sections.

#### 4.12 OVERALL GAIN, NOISE FIGURE, AND IP3 EFFECT

#### 4.12.1.1 OVERALL GAIN

At first, to increase power gain, a multistage amplifier circuit such as CASCADE topology should be considered. For cascaded circuit (refer to the Figure 27) the total power gain  $G_{total}$  of a dual-stage amplifier under linear operating conditions results in an addition of the individual gains  $G_1$  and  $G_2$

$$G_{total}\left(dB\right) = G_{1}(dB) + G_{2}(dB) \tag{4.80}$$

#### 4.12.1.2 NOISE FIGURE

Noise is a form of background signal. A major part of the noise signal belongs to the input transducer; but other components within the circuit will each contribute noise.

The comparison between the desired signal and noise background are defined quantitatively by the *signal-to-noise* ratio,

$$\frac{S}{N} = \frac{(Signal \ Power)}{(Noise \ Power)}$$

(4.81)

The S/N at the output of an amplifier is weaker than it is at the input, due to the fact that the amplifier has components that add noise. Therefore, for a network with gain G, the output noise is then

$$N_o = G\left(N_i + N_a\right) \tag{4.82}$$

as if an additional noise source  $N_a$  exists at the input.  $G \times N_a$  is the extra noise at the output arising from internal elements within the amplifier, sometimes called the equivalent system-noise input. The definition of noise factor is the ratio

$$F = \frac{N_o}{GN_i} = \frac{N_i + N_a}{N_i} = 1 + \frac{N_a}{N_i}$$

(4.83)

The dB form is called "noise figure" NF.

### 4.12.1.3 CASCADED STAGES

In cascaded stage, each stage contributes noise and has a noise factor and a gain (or loss). The total noise of the system is an equivalent input noise,  $N_a$ , as defined in (4.83).

In the cascaded system shown in Figure 27, the total noise in terms of their noise factors and gains.

For the 1<sup>st</sup> stage, having noise factor  $F_1$  and power gain  $G_1$ , the equivalent input noise, according to (4.83), is

$$N_{al} = N_i F_l - N_i = N_i (F_l - 1)$$

(4.84)

Similarly, the equivalent input noise at the 2<sup>nd</sup> stage is  $N_{a2}=N_i(F_2-1)$ , and at the input noise of the 3<sup>rd</sup> stage is  $N_{a3}=N_i(F_3-1)$ , etc. but noise at the input to the 2<sup>nd</sup> stage represents an equivalent input noise at the 1<sup>st</sup> stage of

$$N_{a2} = \frac{N_{a2}}{G_l}$$

(4.85)

Therefore, the entire input noise of the dual stage is

$$N_{a} = N_{i} \left( F_{I} - I \right) + N_{i} \frac{\left( F_{2} - I \right)}{G_{I}}$$

(4.86)

Since  $F(N_i+N_a)/N_i$ , then the overall system noise figure is

$$F_{total}(dB) = F_{I}(dB) + \frac{(F_{2}(dB) - I)}{G_{I}(dB)}$$

(4.87)

Where

$$F_1$$

and  $F_2$  denote the noise figure of stage 1 and 2.

This process can be extended to more stages in like manner, for which

$$F_{rotal}(dB) = F_{I}(dB) + \frac{\left(F_{2}(dB) - I\right)}{G_{I}(dB)} + \frac{\left(F_{3}(dB) - I\right)}{G_{I}(dB)G_{2}(dB)} + \frac{\left(F_{4}(dB) - I\right)}{G_{I}(dB)G_{2}(dB)G_{3}(dB)} + \cdots + (4.88)$$

From (4.88) the gain of the 1<sup>st</sup> stage should be high enough to decrease total noise figure of the system.

# 4.13 3<sup>RD</sup> ORDER INTERCEPT POINT (IP3)

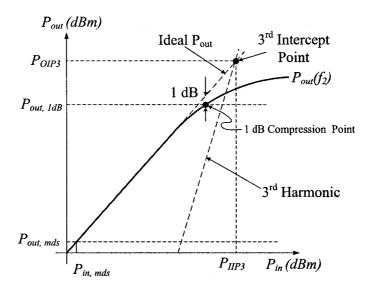

When active devices driven with a large enough RF signal, they will generate undesirable spurious signals. How much spurious generated by the device is dependent on the linearity of the devices.

There are couple of factors which determine the linearity of RF devices, such as 1 dB compressed point (P1dB), Intermodulation distortion (IMD), and 3<sup>rd</sup> order intercept point (IP3).

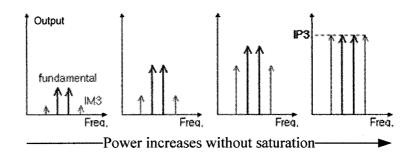

Figure 28 IP3, P1dB, IMD graph

In this section, IP3 will be analyzed how it is being affected by cascading stages as follows.

By definition, IP3 is the point where fundamental power meets IM3 power under the condition that the two power increase without saturating as shown in Figure 28.

Figure 29 3<sup>rd</sup> order intercept point (IP3)

In non-linear system, output signal y can be expressed with input signal x as follows

$$y = a + bx + cx^2 + dx^3 + \dots$$

(4.89)

From (4.89), the IM3 term  $dx^3$  has 3 times slope in dB scale than the fundamental frequency term *bx*. Therefore, there is an assumed point where they meet each other.

In modern communication systems, the IP3 is a very important criterion to measure the linearity of amplifiers.

From Figure 35, if the minimal detectable signal  $P_{in,mds}$  at 3 dB above thermal noise at the input is given by  $P_{in,mds} = kTB+3dB+F_1$ , the minimal detectable output power  $P_{out,mds}$  becomes [16]

$$P_{out,mds}(dBm) = kTB(dBm) + 3dB + F_{total}(dB) + G_{total}(dB)$$

(4.90)

The dynamic properties are also affected. For instance, the third-order intercept point (*IP3*) changes to

$$IP3_{total} (dBm) = \frac{1}{\left(\frac{1}{IP3_{1}(dBm)}\right) + \left(\frac{1}{(G_{2}IP3_{2})(dBm)}\right)}$$

(4.91)

57

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Where  $IP3_1$  and  $IP3_2$  are the third order intercept points associated with stage 1

and 2.

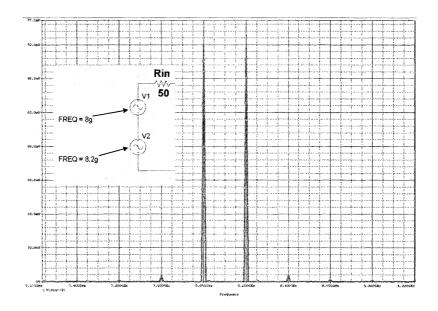

Figure 30 Actual IP3 simulation graph with two different input sources (8 GHz & 8.2 GHz)

# 4.14 FREQUENCY RESPONSE EFFECTS

Since a  $(n+1)^{th}$  stage connected directly to the output of a  $n^{th}$  stage, there will be significant change in the overall frequency response mainly because of the capacitances, such as the wiring capacitances, parasitic capacitances, and Miler capacitances, etc.

In case of each stage have a unit DC gain and a single pole of the amplfier's transfer function is then

$$H(S) = \frac{1}{\tau s + 1} \tag{4.92}$$

In a CASCADE that has nth stages have an overall transfer function of

$$A_H(S) = \left(\frac{1}{\tau s + 1}\right)^n \tag{4.93}$$

Solving for -3 dB bandwidth by computing the magnitude of the transfer function is then

$$\left|A_{H}(j\omega)\right| = \left|\left(\frac{1}{\tau s + 1}\right)\right|^{n} = \frac{1}{\sqrt{2}}$$

(4.94)

Therefore, the bandwidth is a as follows

$$\omega = \frac{1}{\tau} \sqrt{\left(2^{(1/n)} - 1\right)}$$

(4.95)

| n | $\sqrt{\left(2^{(1/n)}-1\right)}$ |

|---|-----------------------------------|

| 2 | 0.64                              |

| 3 | 0.51                              |

| 4 | 0.43                              |

| 5 | 0.39                              |

Table 4 Bandwidth versus n

Therefore, from (4.95) it is necessary to optimize the maximum bandwidth in a cascaded amplifier with a gain requirement.

# CHAPTER 5

# CONSIDERATIONS OF UWB AMPLIFIER

In this section, standard considerations to meet the main desired quality characteristics shown in Table 5 will be presented.

| Table 5 | UWB | quality | characteristics |

|---------|-----|---------|-----------------|

|---------|-----|---------|-----------------|

| Target Characteristics                |                  |  |  |

|---------------------------------------|------------------|--|--|

| Frequency Range                       | 3.1 to 10.6 GHz  |  |  |

| Minimum Desired Transducer Gain (dB)  | 10 dB @ 10.6 GHz |  |  |

| Maximum Desired Power Consumption (W) | 100 mWatts       |  |  |

| Minimum Desired Noise Figure (dB)     | < 10 dB          |  |  |

| Input/Output resistance               | 50 ohm           |  |  |

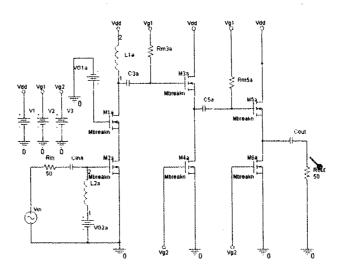

With previous technical considerations, the initial circuit shown in Figure 39 will

be used for optimization.

The optimization procedure is as follows.

- Focus on achieving 3 dB bandwidth with a decent Transducer gain

- Eliminate capacitors in the circuit

- Take account the fabrication factor (PAD capacitance in the output port) for Transducer gain

• Eliminate inductors from the circuit

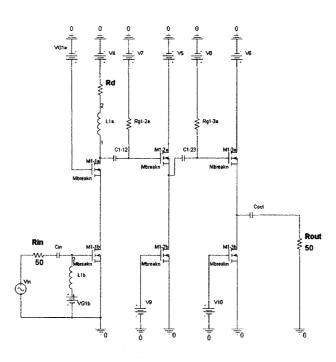

Figure 31 Initial circuit for optimization

With previous technical considerations, such as optimizing the lengths of MOSFETs, bias voltages, and the resistances, the initial circuit shown in Figure 31 has been achieved. The 1<sup>st</sup> stage is a CASCODE arrangement to provide voltage gain, while the two common drain stages that follow permit driving a 50 ohm load.

### 5.1 ACHIEVING 3 dB BANDWIDTH THROUGH FEEDBACK TOPOLOGIES

To meet the 3 dB bandwidth criteria, a feedback topology will be used. Negative feedback allows a flat gain response and reduces the input and output VSWR over wide frequency range. An additional advantage of the negative feedback is that it makes the circuit less sensitive to transistor-to-transistor parameter variations. The disadvantage of such circuit is that tend to limit maximum power gain of the transistor and increase its noise figure.

In amplifier design, negative feedback is applied to change gain (desensitize), reduce nonlinear distortion, reduce the effect of noise, control the input and output impedances, and extend the bandwidth with trading off the gain of an amplifier.

For UWB applications, we need to extend bandwidth almost 7 GHz with a decent gain flatness. Therefore, negative feedback will be one of the most important factors.

In this section the properties of negative feedback will be analyzed.

### 5.2 GAIN DESENSITIZATION

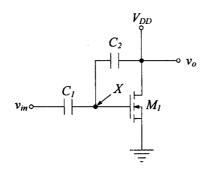

Figure 32 Simple CS amplifier with a feedback

From Figure 32  $v_o$  and  $v_x$  are as follows.

$$\frac{v_o}{v_x} = -g_m r_o \tag{5.1}$$

Perform KCL at node X,

$$(v_o - v_x)sC_2 = (v_x - v_{in})sC_1$$

(5.2)