University of Texas Rio Grande Valley ScholarWorks @ UTRGV

Theses and Dissertations - UTB/UTPA

5-2005

## Design and performance evaluation of switching architectures for high-speed Internet

Alvaro Munoz University of Texas-Pan American

Follow this and additional works at: https://scholarworks.utrgv.edu/leg\_etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Munoz, Alvaro, "Design and performance evaluation of switching architectures for high-speed Internet" (2005). *Theses and Dissertations - UTB/UTPA*. 773. https://scholarworks.utrgv.edu/leg\_etd/773

This Thesis is brought to you for free and open access by ScholarWorks @ UTRGV. It has been accepted for inclusion in Theses and Dissertations - UTB/UTPA by an authorized administrator of ScholarWorks @ UTRGV. For more information, please contact justin.white@utrgv.edu, william.flores01@utrgv.edu.

# DESIGN AND PERFORMANCE EVALUATION OF SWITCHING ARCHITECTURES FOR

## HIGH-SPEED INTERNET

A Thesis by ALVARO MUNOZ

Submitted to the Graduate School of the University of Texas-Pan American In partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

May 2005

Major Subject: Electrical Engineering

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

## DESIGN AND PERFORMANCE EVALUATION

## OF SWITCHING ARCHITECTURES FOR

## HIGH-SPEED INTERNET

### A Thesis by ALVARO MUNOZ

Approved as to style and content by:

Dr. Sanjeev Kumar Chair of Committee

Carrow Past 19-2-7N

Dr. Heinrich Foltz Committee Member

Dr. Zhixiang Chen Committee Member

May 2005

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### ABSTRACT

Munoz, Alvaro, <u>Design and Performance Evaluation of Switching Architectures for</u> <u>High-Speed Internet</u>, Master of Science (MS), May 2005, 119 pp., 64 figures, 4 tables, references, 57 titles.

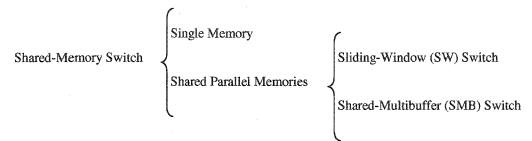

The motivation for this thesis is the desire to build faster and scalable routers that efficiently handle the exponential traffic growth in the Internet. The Internet forwards information through a mesh of routers and switches, which has to keep up with the increasing demands of traffic. Shared-memory based switches are known to provide the best throughput-delay performance for a given memory size. In this thesis performance of commonly used memory-sharing schemes for the shared memory switches are evaluated under balanced and unbalanced bursty traffic. The scalability of shared-memory switches has been a research issue for quite sometime. One approach is to employ multiple memory modules and use them in parallel to enhance the capacity. The two well-known architectures in this category are (i) shared-multibuffer (SMB) switch architecture invented by Yamanaka et al of Mitsubishi Electric Corporation, Japan; and (ii) the sliding-window (SW) switch architecture invented by Dr. Kumar of UTPA, Texas, USA. In this thesis, performance of these two architectures are evaluated and compared. Furthermore, in this thesis, the SW switch architecture is extended to enable priority switching to provide differentiated Quality of Service (QoS) for different traffic classes.

#### ACKNOWLEDGMENTS

This thesis has been possible with the help of many people. First and foremost, among these are my loving parents who I would like to thank for all their support to my education. I am deeply thankful for my advisor Dr. Sanjeev Kumar, for his continued support and guidance in both academic and personal matters, his help in defining the research problem, the frequent constructive discussions, his never-ending encouragement for me to excel in research, and the training in writing papers. It was a great opportunity and I was really excited to work on a new and an exceptional switching architecture invented by Dr. Kumar, namely the Sliding-Window Switch Architecture that has received global attention in this field. I thank Dr. Heinrich Foltz of Electrical Engineering and Dr. Zhixiang Chen of Computer Science for their willingness to serve as the committee members. I am also thankful for the research assistantship support and travel support from the Department of Electrical Engineering, CITeC, OBRR/NIH grant, and the Dean's office of the College of Science and Engineering at the UTPA.

## TABLE OF CONTENTS

| ABSTRACTiii                              |  |  |  |  |

|------------------------------------------|--|--|--|--|

| ACKNOWLEDGMENTS iv                       |  |  |  |  |

| TABLE OF CONTENTS                        |  |  |  |  |

| LIST OF TABLES                           |  |  |  |  |

| LIST OF FIGURES ix                       |  |  |  |  |

| CHAPTER 1 INTRODUCTION                   |  |  |  |  |

| 1.1 Background1                          |  |  |  |  |

| 1.2 Motivation                           |  |  |  |  |

| 1.3 Packet Switching                     |  |  |  |  |

| 1.4 Router and Switches                  |  |  |  |  |

| 1.5 Buffering Strategies                 |  |  |  |  |

| 1.5.1 Input Buffered Switches            |  |  |  |  |

| 1.5.2 Output Buffered Switches           |  |  |  |  |

| 1.5.3 Input and Output Buffered Switches |  |  |  |  |

| 1.5.4 Shared-Memory Switches             |  |  |  |  |

| CHAPTER 2 MEMORY-SHARING SCHEMES         |  |  |  |  |

| 2.1 Introduction                         |  |  |  |  |

| 2.2 Background                           |  |  |  |  |

| 2.3 Individual-Static Threshold Based Sharing Scheme                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.4 Global-Static Threshold Based Sharing Scheme                                                                                                                                                                                                                                                                                                                      |

| 2.4.1 Admittance Policy for Qualifying Output-Ports                                                                                                                                                                                                                                                                                                                   |

| 2.5 Dynamic Threshold Based Sharing Scheme                                                                                                                                                                                                                                                                                                                            |

| 2.6 SMDA Based Memory-Sharing Scheme                                                                                                                                                                                                                                                                                                                                  |

| 2.7 Performance Evaluation                                                                                                                                                                                                                                                                                                                                            |

| 2.7.1 Bursty-Traffic Model                                                                                                                                                                                                                                                                                                                                            |

| 2.7.2 Evaluation under Balanced Bursty-Traffic Conditions                                                                                                                                                                                                                                                                                                             |

| 2.7.3 Evaluation under Unbalanced Bursty-Traffic Conditions                                                                                                                                                                                                                                                                                                           |

| CHAPTER 3 SWITCHING ARCHITECTURES DEPLOYING SHARED PARALLEL                                                                                                                                                                                                                                                                                                           |

| MEMORY-MODULES                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                      |

| <ul><li>3.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                       |

| 3.2 Shared-Multibuffer (SMB) Switch Architecture                                                                                                                                                                                                                                                                                                                      |

| <ul><li>3.2 Shared-Multibuffer (SMB) Switch Architecture</li></ul>                                                                                                                                                                                                                                                                                                    |

| <ul> <li>3.2 Shared-Multibuffer (SMB) Switch Architecture</li></ul>                                                                                                                                                                                                                                                                                                   |

| <ul> <li>3.2 Shared-Multibuffer (SMB) Switch Architecture</li></ul>                                                                                                                                                                                                                                                                                                   |

| <ul> <li>3.2 Shared-Multibuffer (SMB) Switch Architecture</li></ul>                                                                                                                                                                                                                                                                                                   |

| <ul> <li>3.2 Shared-Multibuffer (SMB) Switch Architecture</li></ul>                                                                                                                                                                                                                                                                                                   |

| 3.2 Shared-Multibuffer (SMB) Switch Architecture483.2.1 Admittance Policy for the SMB-Switch Architecture503.2.2 Assignment of Memory-Module for the SMB-Switch Architecture513.3 Sliding-Window (SW) Switch Architecture543.3.1 Admission Control in SW-Switch Architecture573.3.2 Assignment Scheme–1 for i-Parameter593.3.3 Assignment Scheme –2 for i-Parameter60 |

| 3.4.3 Performance Comparison of SMB-Switch Architecture and SW-Switch |

|-----------------------------------------------------------------------|

| Architecture                                                          |

| CHAPTER 4 PRIORITY SWITCHING FOR ARCHITECTURE WITH MULTIPLE           |

| SHARABLE MEMORY-MODULES                                               |

| 4.1 Introduction                                                      |

| 4.2 Sliding-Window                                                    |

| 4.3 Admittance Policy for the SW-Switch Architecture with Priority    |

| 4.4 Determination of Self-Routing Parameters (i, j, k)                |

| 4.4.1 Determination of Parameters (j, k)                              |

| 4.4.2 Determination of i-Parameter                                    |

| 4.5 Memory Controllers                                                |

| 4.5.1 WRITE Stage                                                     |

| 4.5.2 READ Stage                                                      |

| 4.6 Illustration of the Sliding-Window Switch with Priority           |

| 4.7 Simulation Results                                                |

| CHAPTER 5 CONCLUSIONS                                                 |

| REFERENCES                                                            |

| VITA                                                                  |

## LIST OF TABLES

| Table 3.1 Worst-case memory-bandwidth requirement for packets to be written into    |

|-------------------------------------------------------------------------------------|

| memory-modules at 100% load in SW-switch architecture                               |

| Table 3.2 Worst-case memory-bandwidth requirement for packets to be written or read |

| into/from memory-modules at 100% load for SMB and SW architectures                  |

| Table 4.1 Worst-case memory-bandwidth requirement for SW-switch with priority for   |

| high priority class                                                                 |

| Table 4.2 Worst-case memory-bandwidth requirement for SW-switch with priority for   |

| low priority class                                                                  |

## LIST OF FIGURES

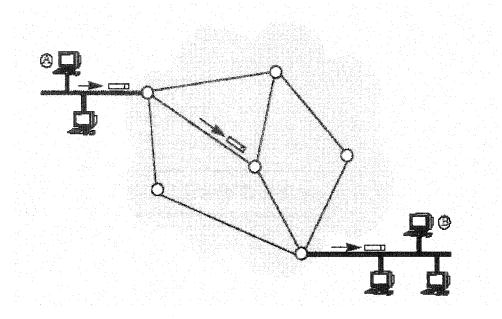

| Fig. 1.1 The nodes in the network cloud can be switches or routers. As they arrive at each |

|--------------------------------------------------------------------------------------------|

| node, packets sent from host A to host B get switched onto a path which leads them         |

| to host B [13]                                                                             |

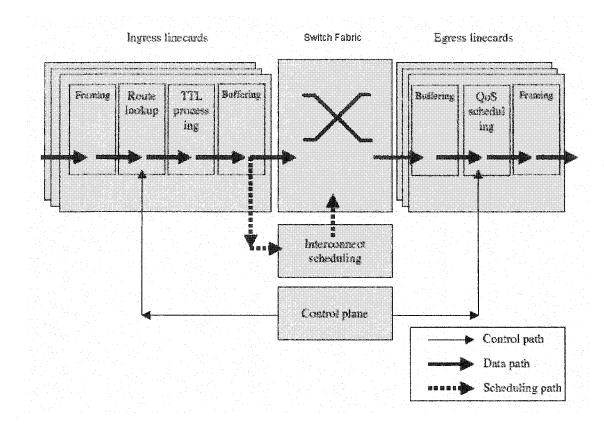

| Fig. 1.2 Functionality of a router or switch [5]                                           |

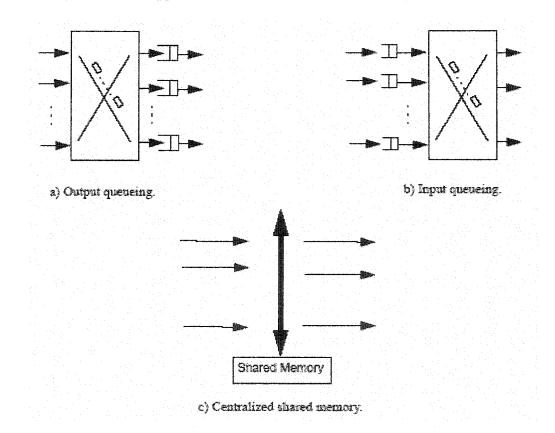

| Fig. 1.3 Various buffering strategies on switching architectures [13]7                     |

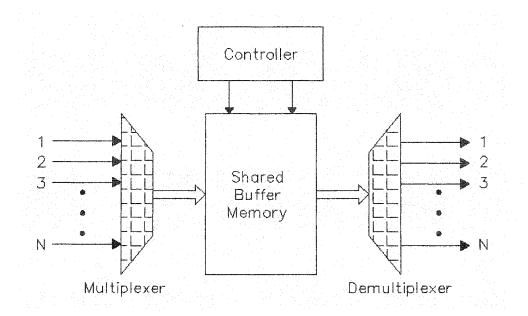

| Fig. 2.1 Basic architecture of shared-memory switches                                      |

| Fig. 2.2 Logical queue in shared-memory switch                                             |

| Fig. 2.3 Individual-static threshold scheme to regulate the sharing of the memory space 18 |

| Fig. 2.4 Global-static threshold scheme to regulate the sharing of the memory space 19     |

| Fig. 2.5 Dynamic threshold scheme to regulate the sharing of the memory space              |

| Fig. 2.6 Two-state ON-OFF model                                                            |

| Fig. 2.7 Average throughput with balanced bursty-traffic conditions for individual-static  |

| threshold based sharing scheme                                                             |

| Fig. 2.8 Packet-loss ratio (PLR) with balanced bursty-traffic conditions for individual-   |

| static threshold based sharing scheme                                                      |

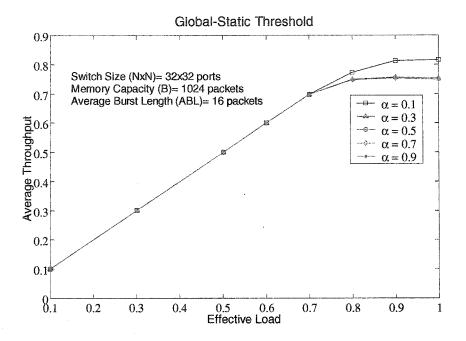

| Fig. 2.9 Average throughput with balanced bursty-traffic conditions for global-static      |

| threshold based sharing scheme                                                             |

| Fig. 2.10 Packet-loss ratio (PLR) with balanced bursty-traffic conditions for global-static |

|---------------------------------------------------------------------------------------------|

| threshold based sharing scheme                                                              |

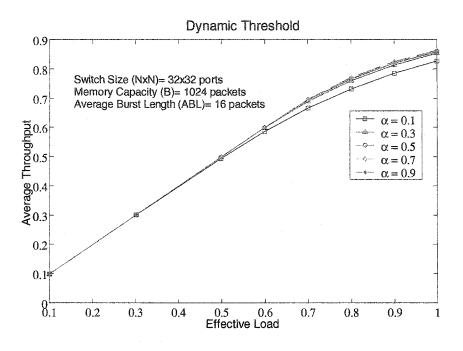

| Fig. 2.11 Average throughput with balanced bursty-traffic conditions for dynamic            |

| threshold based sharing scheme                                                              |

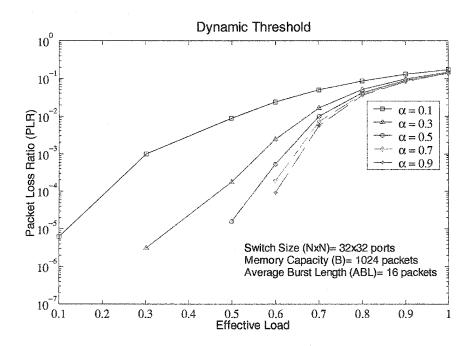

| Fig. 2.12 Packet-loss ratio (PLR) with balanced bursty-traffic conditions for dynamic       |

| threshold based sharing scheme                                                              |

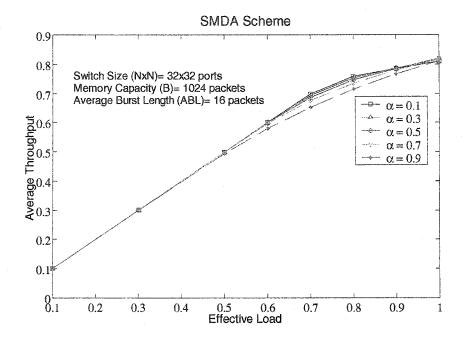

| Fig. 2.13 Average throughput with balanced bursty-traffic conditions for SMDA based         |

| sharing scheme                                                                              |

| Fig. 2.14 Packet-loss ratio (PLR) with balanced bursty-traffic conditions for SMDA          |

| based sharing scheme                                                                        |

| Fig. 2.15 Average throughput in a switch with balanced bursty-traffic and unbalanced        |

|                                                                                             |

| bursty-traffic                                                                              |

|                                                                                             |

| bursty-traffic                                                                              |

- Fig. 2.20 Packet-loss ratio (PLR) for very active output-ports and lightly active outputports in global-static threshold based sharing scheme with  $\alpha = 0.1, 0.2, \text{ and } 0.3.....41$

- Fig. 2.21 Packet-loss ratio (PLR) for very active output-ports and lightly active outputports in global-static threshold based sharing scheme with  $\alpha = 0.6, 0.7, \text{ and } 0.8....41$

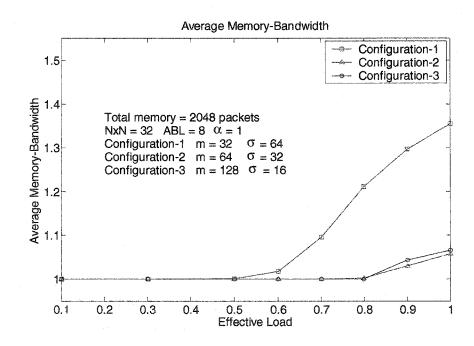

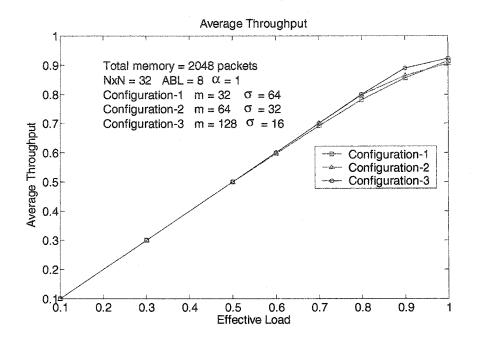

| Fig. | 3.10 Average throughput for SW architecture using assignment scheme-1 to write    |

|------|-----------------------------------------------------------------------------------|

|      | data-packets into memory-modules                                                  |

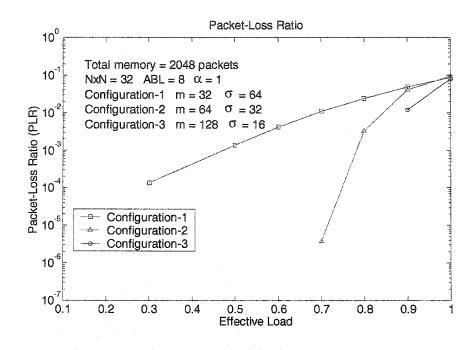

| Fig. | 3.11 PLR for SW architecture using assignment scheme-1 to write data-packets into |

|      | memory-modules                                                                    |

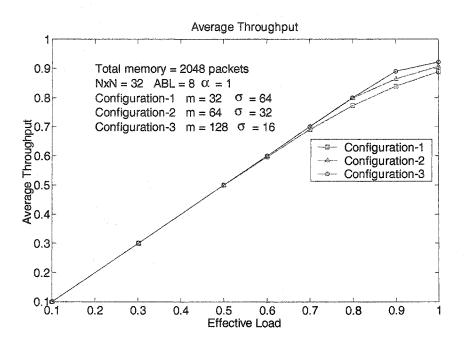

| Fig. | 3.12 Average throughput for SW architecture using assignment scheme-2 to write    |

|      | data-packets into memory-modules                                                  |

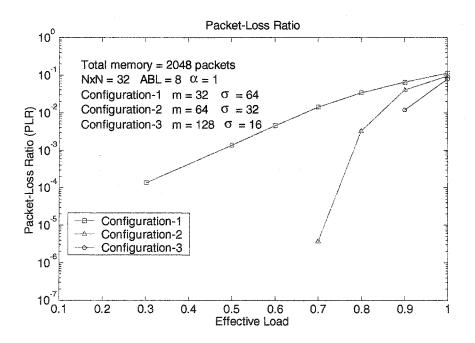

| Fig. | 3.13 PLR for SW architecture using assignment scheme-2 to write data-packets into |

|      | memory-modules                                                                    |

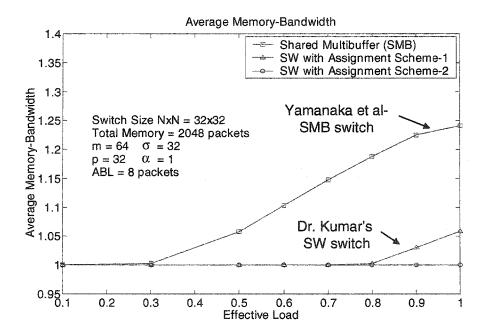

| Fig. | 3.14 Average memory-bandwidth evaluations of SMB and SW architectures at the      |

|      | READ and WRITE stages respectively                                                |

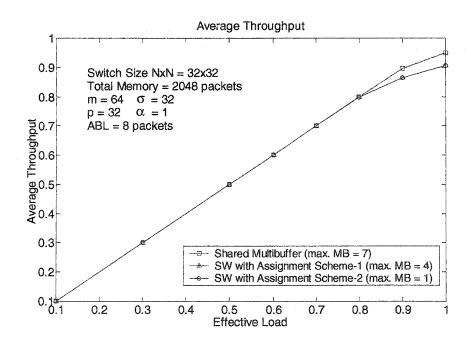

| Fig. | 3.15 Average throughput for SMB and SW architectures with unlimited memory-       |

|      | bandwidth requirement (maximum memory-bandwidth = 7)                              |

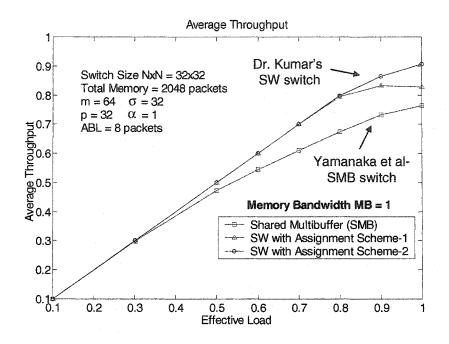

| Fig. | 3.16 Average throughput for SMB and SW architectures with memory-speed equal      |

|      | to the line-speed (memory-bandwidth = 1)                                          |

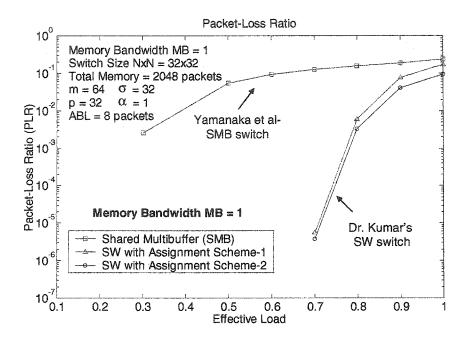

| Fig. | 3.17 Packet-loss ratio for SMB and SW architectures with memory-speed equal to    |

|      | the line-speed (memory-bandwidth = 1)                                             |

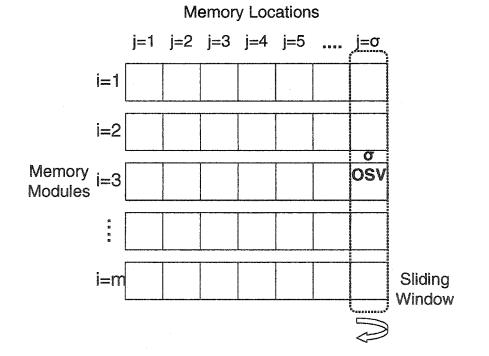

| Fig. | 4.1 Global memory in SW-switch architecture [42]                                  |

| Fig. | 4.2 Increment of variables SW.j and SW.k in the sliding-window                    |

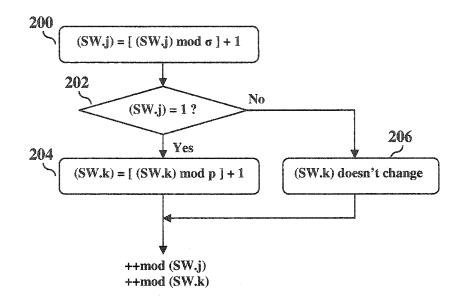

| Fig. | 4.3 Steps to admit packets into the SW-switch with priority                       |

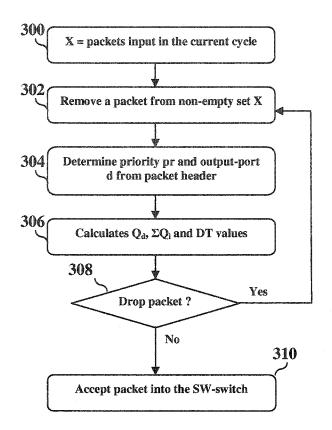

| Fig. | 4.4 Admittance policy for incoming packets                                        |

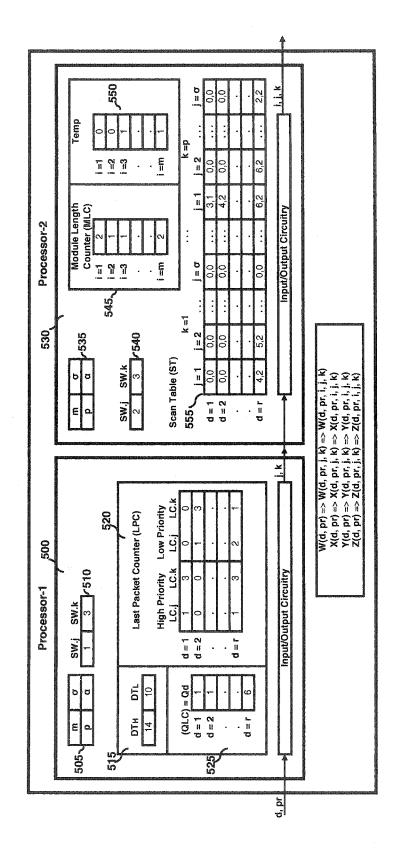

| Fig. | 4.5 Parameter assignment circuit that produce self-routing tag (i, j, k)          |

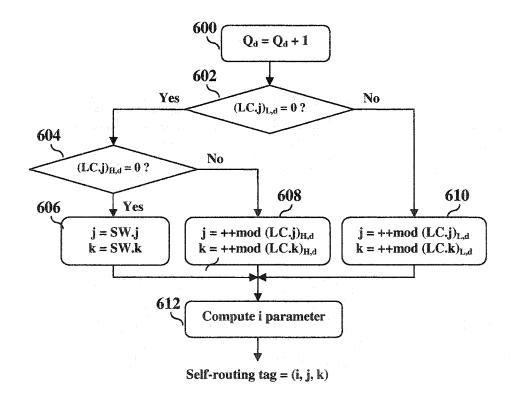

| Fig. | 4.6 Flow diagram to calculate j and k parameters for low priority class           |

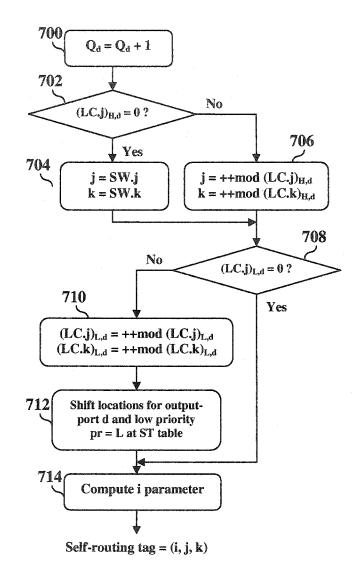

| Fig. | 4.7 Flow diagram to calculate j and k parameters for high priority class          |

|      |                                                                                   |

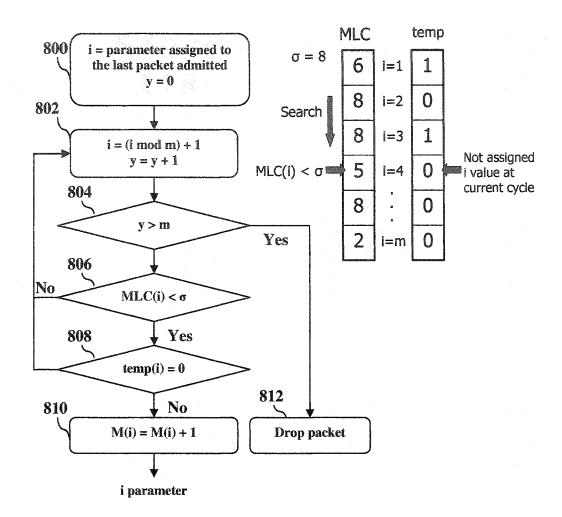

| Fig. 4.8 Scheme to assign i parameter                                                                      |

|------------------------------------------------------------------------------------------------------------|

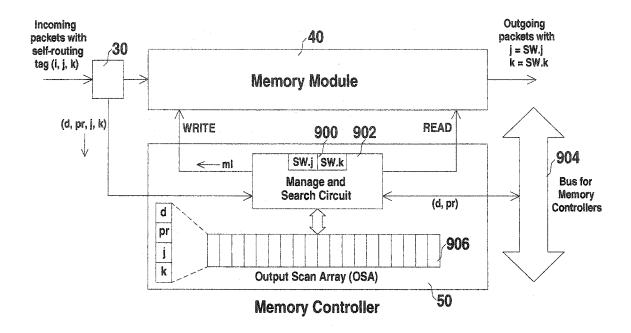

| Fig. 4.9 Memory controller for memory-module                                                               |

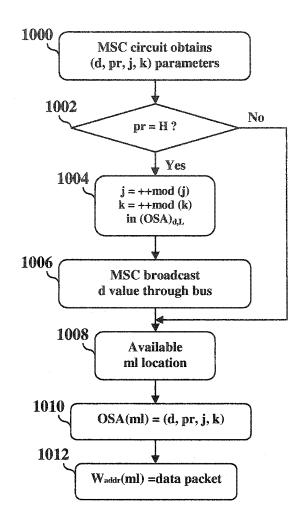

| Fig. 4.10 WRITE operation of packets to memory-modules                                                     |

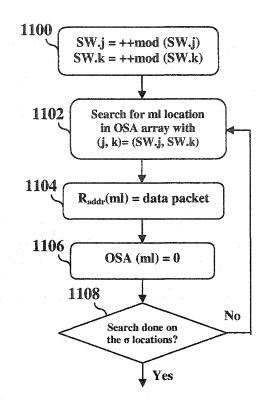

| Fig. 4.11 READ operation of packets from memory-modules                                                    |

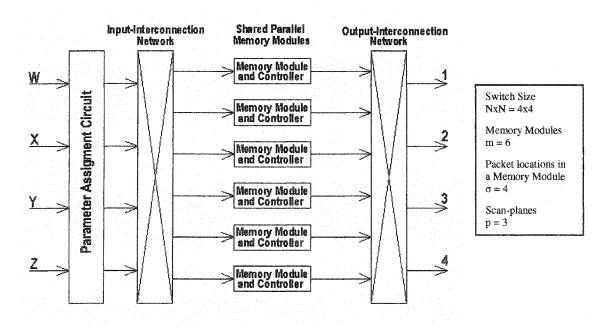

| Fig. 4.12 Example of a 4x4 SW-switch with priority and its configuration                                   |

| Fig. 4.13 Packet streams received and output in a 4x4 SW-switch with priority                              |

| Fig. 4.14 Counters for processor-1                                                                         |

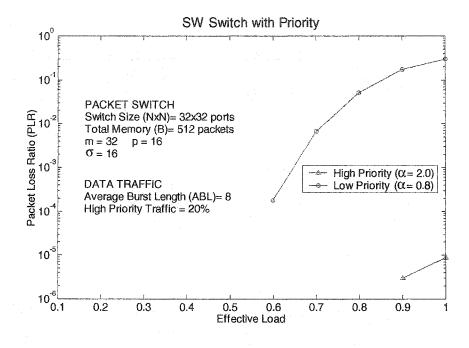

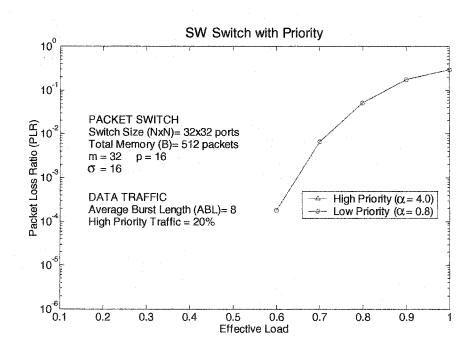

| Fig. 4.15 Packet-loss ratio (PLR) in SW-switch with priority ( $\alpha_H = 2.0$ and $\alpha_L = 0.8$ ) 102 |

| Fig. 4.16 Packet-loss ratio (PLR) in SW-switch with priority ( $\alpha_H = 4.0$ and $\alpha_L = 0.8$ ) 102 |

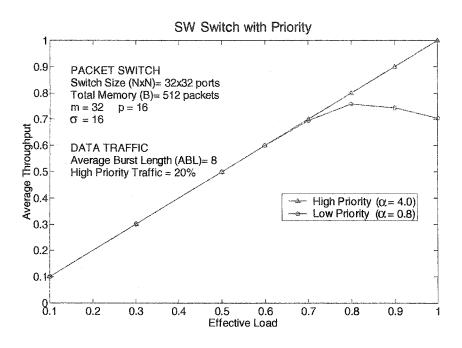

| Fig. 4.17 Average throughput in SW-switch with priority for the two priority classes . 104                 |

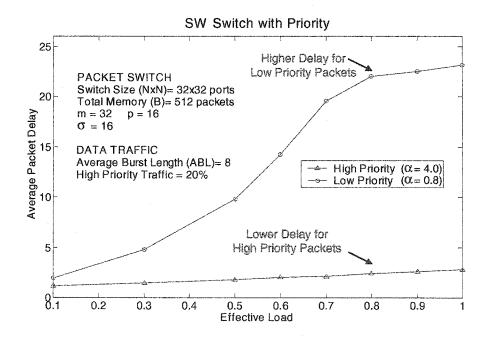

| Fig. 4.18 Packet latency in SW-switch with priority for the two priority classes 104                       |

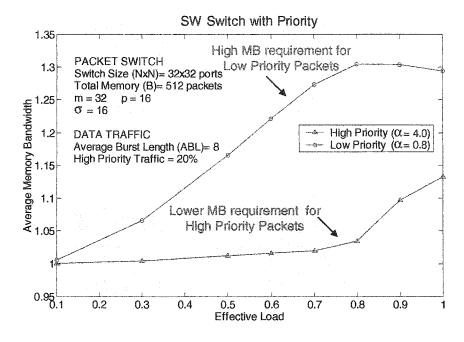

| Fig. 4.19 Average memory-bandwidth requirement for SW-switch with priority for the                         |

| two priority classes                                                                                       |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Background

The Internet has had a tremendous success in the last several decades, evolving from a small research network to a scalable and distributed network with a rapid development and deployment of applications and services. The exponential growth of the Internet is demonstrated by the tremendous increase in both the number of users [1] and the traffic growth that has already made the Internet carry more traffic than the phone network [2][3]. Advances in transmission technologies have provided abundant transmission bandwidth. Progress in optical transmission technologies [4], such as dense wave division multiplexing (DWDM), optical add-drop multiplexers, ultralong-haul lasers, and optical amplifiers, has a large impact on lowering costs of digital transmission. The advent of DWDM in 1996 has provided doubling of the capacity of fiber optics every 7 to 8 months [5]. However, the growth rate is expected to decrease to doubling every year as we start approaching the maximum capacity per fiber of 100 Tbit/s [6]. Historically, router capacity has increased slightly faster than Moore's law, multiplying

1

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

by 2.2 every 1.5 to 2 years. This has been due to advances in router architecture and packet processing [7].

#### 1.2 Motivation

The Internet originally provided best effort service but as the Internet becomes widely used, and more users have broadband access service such as asymmetric digital subscriber line (ADSL) and fiber to the home (FTTH), new application types uniting voice, video, and data traffic need to be delivered on the network infrastructure. Demands for systems that provide quality-of-service (QoS) to real-time applications and mission-critical financial data are increasing. The net effect of these driving forces is a set of new requirements that are placed on the routing and switching functions. These new requirements have put increasing demands on Internet routers and switches for supporting higher bandwidth, greater switching capacity, and efficient support for quality-of-service (QoS) in the network. This thesis focus on the design and evaluation of efficient Internet switching architectures that can face the challenges imposed on the next generation Internet by the scalability issues and QoS requirements of present and future Internet applications.

#### 1.3 Packet Switching

There are two fundamental types of underlying network infrastructures based on how traffic is multiplexed and switched inside a network: circuit-switching and packetswitching. A circuit-switched network provides a fixed connection to its hosts. In circuitswitching, a guaranteed amount of bandwidth is allocated to each connection and

available to the connection all the time. The most common example of a circuit-switched network is the public-switched telephone network (PSTN). Circuit-switching can be rather inefficient. An amount of bandwidth is dedicated for the duration of the connection, even if no data are being transferred. For a voice connection, utilization may be rather high but for bursty-traffic the utilization of networks resources is not efficient. An example of bursty-traffic is Web browsing. When a user clicks on a hyperlink, a new page needs to be downloaded as soon as possible from a server. When a user is looking at a recently downloaded page, there is almost no traffic. Thus a bursty stream in Internet requires a lot of bandwidth from the network whenever it is active and very little bandwidth when it is not active.

In contrast packet switching deals with the problem of transporting bursty-traffic efficiently. In packet-switched networks (Fig. 1.1), the data stream is broken up into small packets of data. Each packet contains a portion of the user's data plus some control information. The control information includes the information that the network requires to be able to route the packet through the network and deliver it to the intended destination. Theses packets are statistically multiplexed together with packets from other data streams inside the network. Therefore statistical multiplexing improves the bandwidth utilization of the network.

Fig. 1.1 The nodes in the network cloud can be switches or routers. As they arrive at each node, packets sent from host A to host B get switched onto a path which leads them to host B [13]

In a packet switched network, data-packets travel through a mesh of routers or switches over links towards their final destinations. The delivery of packets from host A to host B, as illustrated in Fig. 1.1, requires packets to pass through multiple routers and switches (nodes). As soon as a packet arrives at a node, the router decides to which output link the packet is to be switched, based on its IP address from packet's header, and transmits it to the corresponding output link. Contention occurs among packets for network resources when more than one packet is destined for the same output link at the same time. This is solved by queueing the packet(s) that could not access the destined output link and forwarding the packet(s) later from buffer when the output link becomes available. Buffers cause some important effects; the delay experience by packets at each node depends on how many packets are queued up ahead of it. This causes delay variations (jitter). On occasion, the traffic in some output links may be so high that it causes the buffers to overflow. When this happens, some of the packets must be dropped from the network.

#### 1.4 Router and Switches

A router receives traffic through its input-ports and sends it shortly afterwards through the appropriate output-ports. Information is sent either through fiber optics for the long haul and high speeds, or through copper cables for the short haul and mid-to-low speeds. Routers need to look up the destination address in a routing table to decide where to send a packet next, or in which queue it should be buffered. Packets also need to be scheduled to use the switch fabric, so that they go from the input-ports to the output-ports without contention. Conflicts are resolved by deferring the transmission of all but one of the conflicting packets until some later time when the contention has been cleared.

Fig. 1.2 shows the functional blocks of a router, also called a switch. When traffic arrives at the ingress linecard, the framing module extracts the incoming packet from the link-level frame. IP address is used to look up the routing table. A so-called longest-prefix matching method is used to find the output-port. In some applications, packets are classified based on the combined information of IP source/destination addresses, transport layer, port numbers, and type of protocol. Based on the result of classification, packets may be either discarded or handled at different priority levels. Then, any required operations on the packet's header are performed, such as decrementing the Time-To-Live (TTL) field, updating the packet checksum, and processing any IP options. After these operations, the packet is sent to the egress port through a switch fabric, which is rescheduled every time slot. Several packets destined to the same egress port could arrive

at the same time. Thus, any conflicting packets have to be queued in the input-port, the output-port, or a centralized shared-memory location.

Fig. 1.2 Functionality of a router or switch [5]

In the output linecard, some routers perform additional scheduling that is used to police or shape traffic, so that quality-of-service (QoS) guarantees are not violated. Finally, the packet is placed in a link frame and sent to the next hop. In addition to the datapath, routers have a control path that includes the system configuration, management, and exchange of routing table information. These are performed relatively infrequently. The router controller exchanges the topology information with other routers and constructs a routing table based on a routing protocol.

#### 1.5 Buffering Strategies

One of the central concerns in designing a high-capacity switch is limited memory-bandwidth [8][9]. For switches operating at high speed, the speed of the memory, which is a basic building block of queues, becomes a limiting factor. Switch speed is often limited by the rate at which the memory can operate. Depending on switch architecture, queueing can take place at different parts of the switch as shows in Fig. 1.3: at the inputs, at the outputs, at both inputs and outputs, or at a centralized location. The following subsections explain different buffering strategies and the advantages and disadvantages of theses approaches.

Fig. 1.3 Various buffering strategies on switching architectures [13]

#### 1.5.1 Input Buffered Switches

Input-buffering is characterized by the memory blocks located at the input ports as shown in Fig. 1.3 (b). At most one packet can arrive at and depart from each input in one time slot. Thus, the memory is only required to operate at twice the line rate. Unfortunately input buffering suffers from head-of-line (HOL) blocking and limits the throughput to 58.6% for uniform traffic [10]. HOL blocking occurs because packets for different outputs share the same first-in first-out (FIFO) queue.

When packets for different outputs share a FIFO queue, a packet, which may be destined to a free output, can be blocked by a packet in front of it, which may be destined to a busy output-port. Such a packet is called a HOL packet. The HOL packet may be destined to a different output but has to remain in the queue because its output is busy. As a result, some inputs and outputs are unnecessarily left idle and thus degrading the throughput performance. There are various techniques to reduce HOL blocking [11][12][13]. A technique called virtual output queueing (VOQ) aims to eliminate HOL blocking [14][15] but the scheduling problem in VOQ switches limit the scalability of this switch architecture. An *NxN* size VOQ switch need to manage  $N^2$  logical queues in all memory blocks and existing scheduling algorithms are either complex to run at high speed or only perform well under restricted conditions.

#### 1.5.2 Output Buffered Switches

Output-buffering is referred to as a technique in which all memory blocks are placed at the outputs [16][17][18] as shown in Fig. 1.3 (a). Memory independence among

output-ports enables output-buffered switches to guarantee a minimum-bandwidth between individual connections [19]. Nonblocking fabrics help to ensure that the adequacy of service delivered to a particular user should not depend on the detailed behavior of other users. Deterministic bounds on end-to-end delay and end-to-end buffer sizing results for lossless transmission are available under output-buffering; these results can be extended to arbitrary virtual path connection (VPC) structures [20]. In addition, because output-buffering do not suffer from HOL blocking at the input-ports, they can achieve 100% throughput for each output link. On the other hand output-buffering requires that all arriving packets must be immediately delivered to their outputs. An output-buffered switch of size NxN would require in the worst-case scenario N + 1write/read operations to be done in a memory block which limit the scalability of this buffering technique.

#### 1.5.3 Input and Output Buffered Switches

Input and output buffered switches are intended to combine the advantages of input buffering and output buffering [21][22][23]. In input buffering, the input buffer speed is comparable to the input line rate. In output buffering, there are up to L (1<L<N) packets that each output-port can accept at each time slot. If there are more than L packets destined for the same output-port, excess packets are stored in the input buffer. Since the output buffer memory only needs to operate at L times the line rate, a large-scale switch can be achieved by using input and output buffering. However, this type of switch requires a complicated arbitration mechanism to determine which of L packets among the N HOL packets may go to the output-port.

#### 1.5.4 Shared-Memory Switches

In shared-memory switch [24][25][26] incoming packets are time-division multiplexed into a single data stream and sequentially written to a shared-memory. Also packets are removed from shared-memory in a single output data stream and demultiplexed in several egress lines. The buffer-space is a centralized memory block (Fig. 1.3 c) used by all ports to write or read packets. Logically the buffer-space is partitioned in multiple logical queues, one for each output-port or even further for each traffic flow to provide quality-of-service (QoS). Shared-memory switches provide the best memory utilization. All input/output have access to the shared-memory and buffer space that is unused by other outputs can be employed by very active output-ports. A subject that should be taken into account in shared-memory switches is the efficient access of output-ports to the buffer-space. The problem is that a single port or group of ports can take over most of the buffer, preventing packets destined for less utilized ports from gaining access. This causes degradation in throughput performance of the switch. Optimal ways to share the buffer-space among all the input and output-ports by controlling the queue build-up inside the shared-memory switch for various traffic conditions have been discussed in [27][28][29][30][31][32][33].

A drawback, in the shared-memory switch is the speed at which the memory has to operate. Scaling a shared-memory switch to a larger size is constrained by an internal speedup requirement. For a switch of size NxN, the memory must be able to support Nread accesses by all the N outputs and N write accesses by all the inputs in a time slot, i.e., the memory must operate  $2 \cdot N$  times faster than the line rate. There are several

approaches to overcome traditional limitations in shared-memory switches. A method to scale a packet switch is to use multiple switches operating independently and then interconnect such switches in some fashion to build a large-scale switching system [34][35][36][37]. Parallel packet switch (PPS) architecture [34][35] is comprised of multiple identical lower speed packet switches in parallel. An incoming stream of packets is spread, packet by packet, by a demultiplexer across switches, and then recombined by a multiplexer at the output. However, PPS architecture requires coordination buffers in the multiplexers and de-multiplexers in order to employ a distributed scheduling algorithmic. Use of multistage interconnection networks (MINs) [36][37] to interconnect small-scale shared-memory switches to build large size shared-memory switch has been used. Although, it is shown in [42] that the optimal throughput performance of small-size shared-memory switches degrades significantly if the switch is grown to a larger-size switch by connecting these optimal-performance switches using MIN approach.

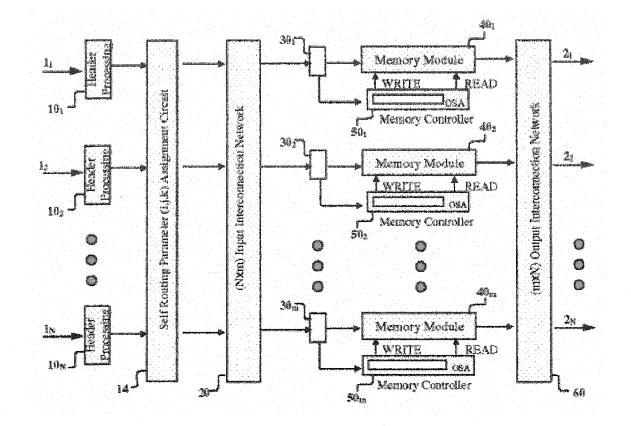

Shared-memory switches have been scaled using collectively multiple physicallyseparate memory-modules which as a group form a large memory block that it is intended to buffer packets that lost contention for switch resources. Allowing sharing of the total buffer space from the entire number of memory-modules among all the input and outputports [38][39][40][41][42][43]. A Shared-Multibuffer (SMB) switch design, proposed in [38][39][40], provides a complete sharing of all the memory-modules among all input and output-ports. The SMB-switch deploys a centralized controller to centrally control and manage all switching functions; such as their write/read operations for all incoming and outgoing packets, update idle and used memory addresses, provide instructions to input and output spatial (interconnection) switches on how to provide routing of data

packets corresponding to the input and output lines The main disadvantage of this approach is that the use of a centralized controller can become a performance bottleneck as the switch is grown to a larger size. The sliding-window (SW) switch architecture in [41][42] is a class of switching architecture, where physically separate multiple memory-modules are logically shared among all the ports of the switch, and the control is decentralized. Memory-modules are independent and they use their local memory controllers to perform write/read operations for data packets based only on the information available locally. Decentralized switching functions enable the SW-switch to operate in a pipeline fashion to enhance scalability and switching capacity.

#### CHAPTER 2

#### MEMORY-SHARING SCHEMES

#### 2.1 Introduction

Switching systems employing shared-memory have been known to provide the highest throughput and incur the lowest packet-loss compared to that of packet switches employing input or output buffering strategies under conditions of identical memory size and bursty-traffic. High-capacity shared-memory based switches are becoming popular due to new approaches to obtain high memory-bandwidth with the use of multiple memory-modules in parallel that efficiently emulate a big-size memory-module which is logically shared among ports. [38][41][42]. Internet traffic is inherently bursty in nature. With the increase in Internet traffic, the Internet switches have to be efficient in handling bursty-traffic. Because of their ability to achieve high throughput for a given memory resource deployed, the shared-memory switches are increasingly being used in high-performance Internet core routers and switches. For efficient sharing of a common memory space by the packets of the output-ports in a shared-memory switch, it is important to deploy some type of memory-sharing scheme. These memory-sharing

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

schemes have a direct impact on the throughput performance and utilization of its outputports [29][30][31][33]. In this chapter we present different types of memory-sharing schemes that can be possible for packets of different output-ports to share a common memory space. We also measure the performance of these memory-sharing schemes under bursty-traffic conditions. The bursty-traffic can be divided into two different types (i) Balanced bursty-traffic and (ii) unbalanced bursty-traffic. The balanced bursty-traffic has bursts of incoming packets uniformly distributed to the output-ports with each outputport having equal probability of receiving a burst of packets. In the unbalanced burstytraffic, some ports of the switch have higher probability of receiving bursts of traffic than other ports. Some examples of applications that can produce unbalanced bursty-traffic could be due to fixed geo-spatial location of videoconferencing sessions (e.g. business area of downtown), or live digital broadcast for sporting events which may be more popular with subscribers in certain geographical area. In this chapter, the switch outputports with higher probability of receiving bursts of packets are called very active ports and the ports with lower probability of receiving bursts of packets are called lightly active ports. To the best of our knowledge, no prior work has been done to compare all four different memory-sharing schemes under balanced and unbalanced bursty-traffic. In this chapter, we measure and compare the effect of balanced and unbalanced bursty-traffic on the performance of four memory-sharing schemes for the class of shared-memory packet switches used in Internet.

#### 2.2 Background

A shared-memory switch, as shown by Fig. 2.1, allows multiple broadband lines to share a common buffer-space for storing packets bound for various output-ports of the switch. The access to the memory is time multiplexed via a shared bus. Packets arriving on all input-ports are multiplexed into a single stream that is fed to the common memory for storage. At the same time, an output stream of packets is formed by retrieving packets from memory; the output stream is then demultiplexed, and packets are transmitted on the output-ports.

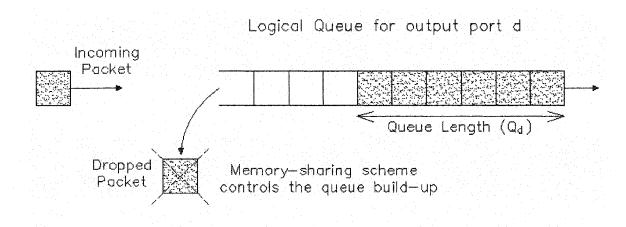

Inside the memory, packets are organized into separate logical queues. An individual logical queue per port is usually set, but there can be more if the switch supports various priority classes. A logical queue for output-port d is depicted in Fig. 2.2, incoming packets destined to output-port d causes queue length  $Q_d$  to expand and eventually packets are dropped if buffer-space is not available. A memory-sharing scheme selectively drops packets and controls the queue built-up inside memory before the buffer overflow. In effect, a memory-sharing scheme intends to provide to all the output-ports a fair access to the memory resources by controlling the use of buffer-space. Consequently, it maintains an efficient utilization of the switching system.

Fig. 2.1 Basic architecture of shared-memory switches

Fig. 2.2 Logical queue in shared-memory switch

It is necessary to have some kind of control on sharing of the common bufferspace among the packets for different output-ports of the switch. In the case of complete memory sharing, it is possible for packets of a given output-port or a group of outputports (monopolizing ports) to completely occupy the common buffer-space and in effect block the passage of packets belonging to non-monopolizing ports of the switch. The

provision of complete-sharing of the common memory results in unfair use of commonbuffer-space. Because of this, the complete-sharing of common-buffer-space in sharedmemory packet switches can result in starvation for some output-ports of the switch and inefficient output-utilization. In order to alleviate this problem of unfairness, it is common to restrict the occupancy of the common-buffer-space in order to always allow passage to all input-output pairs. The memory-sharing schemes, namely the individualstatic threshold, global-static threshold, dynamic threshold and SMDA based memorysharing schemes are used to restrict complete occupancy of the common memory by packets of a given output-port or a set of output-ports. In this chapter we compare the impact of various memory-sharing schemes on the throughput and packet-loss performance of a switch under a given bursty-traffic.

#### 2.3 Individual-Static Threshold Based Sharing Scheme

This is a straightforward scheme used to control, on an individual basis, the output-queue build-up inside the shared-memory switch. Under this scheme, a restriction is placed on the maximum length of the output queues [28] to a pre-determined value which is defined as the individual-static threshold value (ST). The individual-static threshold (ST) value is set to a multiple  $\alpha$  of the total buffer-space (B)

ST =  $\alpha$ ·B packets where  $0 < \alpha < 1$

An individual output queue  $(Q_d)$  inside the common buffer-space is not allowed to exceed the ST value. The packets of the output-queues that exceed ST value are dropped as illustrated in Fig. 2.3 if  $Q_d < ST$  packets then

Accept packets for the output-port d

else

Drop the packets for output-port d

Fig. 2.3 Individual-static threshold scheme to regulate the sharing of the memory space

This scheme prevents any individual output-queue from completely occupying the common buffer-space and hence attempts to improve fairness and switch throughput. This technique of restricting the maximum length of individual queues works well in preventing a single output queue from completely occupying the common buffer-space. However, at higher loads, it is still possible for a group of output queues to completely occupy the common memory and unfairly deny (drop) the packets belonging to other source-destination pairs to access the common buffer-space for switching purposes.

#### 2.4 Global-Static Threshold Based Sharing Scheme

According to this scheme [33], a restriction is put on the occupancy status of the entire global memory-space. In this scheme, a predetermined limit, called the global-static threshold value (GT) is imposed on the occupancy of the global memory-space (B). This GT value is calculated as follow; where  $(1-\alpha)$  is a proportionality constant imposed on the occupancy of global memory-space (B)

$GT = (1-\alpha) \cdot B$  packets where  $0 < \alpha < 1$

If the occupancy of the global memory-space reaches that threshold value (GT) then the packets only from qualifying output-ports are admitted to the remaining memory space =

$(\alpha \cdot B)$  packets. A predetermined admittance policy is used to qualify the output-ports whose packets will be admitted in the remaining memory space. An example of an admittance policy is given in the section below.

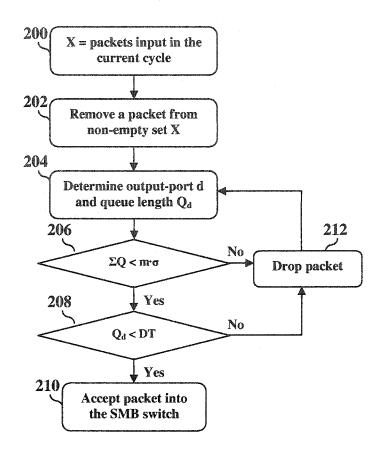

#### 2.4.1 Admittance Policy for Qualifying Output-Ports

Once the global-static threshold value (GT) is reached on the occupancy of the entire global memory-space then the admittance policy accept packets for only those output-ports whose output-queue length is less than ( $\alpha$ ·B) packets. Where *B* is the total shared-memory space and  $\alpha$  is a proportionality constant ( $0 < \alpha < 1$ ) imposed on the occupancy of global memory-space (B).

The output-ports with queue length less than  $(\alpha \cdot B)$  packets are considered underrepresented ports. Once the threshold limit GT is reached for the occupancy of the entire global memory-space then only the admittance policy goes in effect. The admittance policy selectively admits packets to the remaining memory space for only the underrepresented output-ports with queue length less than  $(\alpha \cdot B)$  packets. The algorithm for sharing of the common buffer-space among the packets of competing output-ports and with this admittance policy is given in Fig. 2.4

if  $(\Sigma Q_i) < GT$  packets then where  $GT = (1-\alpha) \cdot B$

Accept packets for all the output-ports

elseif  $Q_d < (\alpha \cdot B)$  packets then

Accept the packets for the output-port d else

Drop the packets for output-port d

Fig. 2.4 Global-static threshold scheme to regulate the sharing of the memory space

The global-static threshold based memory-sharing scheme achieves an efficient use of common buffer-space compared to individual-static threshold based memory-sharing scheme especially under conditions of low offered load. However, in the global-static threshold scheme the switch output-ports may not be fully utilized due to backlog in the remaining space =( $\alpha$ ·B) packets under conditions of high bursty-traffic loads.

#### 2.5 Dynamic Threshold Based Sharing Scheme

Dynamic threshold based memory-sharing scheme is described in detail in [30]. According to this scheme, the occupancy of the memory that dynamically changes with the traffic conditions impose dynamically changing restrictions on the active output-ports from entering the remaining memory space at any given time. Each queue length ( $Q_d$ ) inside common buffer-space is limited to a predetermined value called the dynamic threshold (DT) value. This DT value is function of the remaining buffer-space and it could increase or decrease depending on the traffic conditions at time t. Let *B* be the total buffer-space and  $\Sigma Q_i$  the sum of all queue lengths, i.e., the total memory used to store packets, then the dynamic threshold (DT) value at time t is calculated:

$DT(t) = \alpha \cdot (B - \Sigma Q_i)$  packets where  $\alpha > 0$

Where  $\alpha$  is proportionality constant of the available memory space (B –  $\Sigma Q_i$ ) at time *t*. Packets belonging to output queue lengths (Q<sub>d</sub>) with values less than DT are allowed to be stored in the remaining buffer-space; otherwise packets are dropped as illustrated in Fig. 2.5 if  $Q_d < DT$  packets then

Accept packets for the output-port d

else

Drop the packets for output-port d

Fig. 2.5 Dynamic threshold scheme to regulate the sharing of the memory space

Dynamic threshold scheme is inherently adaptive and dynamically respond in time according to the unused memory space. If there is sufficient buffer-space it allows active output-ports to increase their output queues as much as necessary. Contrary, if the buffer nearly overflows it imposes very restrictive conditions in a way only packet for less active ports are accepted. DT scheme reduces queue lengths by blocking new arrivals and waiting for the queue lengths of active ports to reduce naturally by the work of the switching system.

#### 2.6 SMDA Based Memory-Sharing Scheme

Another memory-sharing scheme, namely the shared-memory with dedicated access (SMDA) is similar to the scheme called sharing with minimum allocation (SMA) scheme mentioned in [29]. SMDA or SMA based memory-sharing scheme aims to guarantee full utilization of the output-ports first, and then attempts to maximize the throughput for a given bursty-traffic. Under this scheme, a packet switch uses both the shared-memory and dedicated memory for its output-ports. A small percentage of total memory is dedicated to each output-port and the remaining memory is shared among all the ports. For a given output-port, the dedicated memory is first used to store the packets and when the dedicated portion of the memory is full then only the packets can access shared-memory space of the switch.

Dedicated memory space for the SMDA scheme represents the minimum number of packet locations within memory space allocated to each output-port for its individual use and is calculated as following.

Dedicated memory per port =  $\frac{\alpha \cdot B}{N}$  packets where  $0 < \alpha < 1$

A portion of the total memory space B is divided equally among all the ports for its dedicated use. The amount of remaining memory space is shared among all the ports and is calculated as following.

Shared-memory space =  $B - N \cdot \frac{\alpha \cdot B}{N}$  packets

Here, *B* is the total memory space,  $\alpha$  is a proportionality constant for SMDA scheme and *N* is the number of I/O ports for *NxN* packet switch. Under this scheme, when the sharedmemory space is occupied due to traffic backlog then the inactive ports still have a dedicated memory to allow its packets a passage through the memory space. Unlike other memory-sharing schemes, the SMDA or SMA scheme guarantee full output-utilization even under the conditions of backlog that is common with bursty Internet traffic.

#### 2.7 Performance Evaluation

A simulation study is used to evaluate the performance of a shared-memory switch employing the various memory-sharing schemes. The measures of interest considered for performance evaluation are the offered load for a bursty-traffic of a given average burst length (ABL), the average throughput, and the Packet-loss ratio (PLR) for a given memory size used in the system. Section 2.7.1 describes the probability nature of the bursty-traffic. Next, section 2.7.2 evaluates the various memory-sharing schemes using a balanced bursty-traffic scenario where bursts of data-traffic are uniformly distributed to all the output-ports. Section 2.7.3 considers an unbalanced bursty-traffic scenario. Burst of incoming packets have a greater chance to be destined to some output-ports than others output-ports.

### 2.7.1 Bursty-Traffic Model

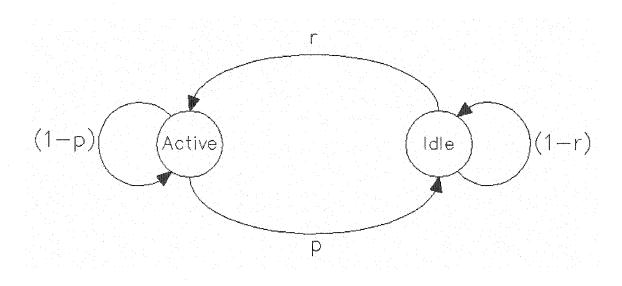

To study performance of the various memory-sharing schemes, a bursty-traffic [7][42] is generated using a two state ON–OFF model (Fig. 2.6). Packets arrive at each input in a slot-by-slot manner and each input alternates between active and idle periods of geometrically distributed duration. During an active period, packets destined for the same output arrive continuously in consecutive time slots. There is at least one packet in an active period. An active period is usually called a burst. For the duration of and idle period, there are consecutive empty time slots due to the absence of traffic.

Fig. 2.6 Two-state ON-OFF model

If p and r characterize the duration of the active and idle period, respectively, then the probability that the active period lasts for a duration of i time slots is given by

$$P(i) = p(1-p)^{i-1}$$

, for  $i \ge 1$

and the corresponding average burst length (ABL) is given by

$$E_{\scriptscriptstyle B}[i] = \sum_{i=1}^{\infty} i \cdot P(i) = \frac{1}{p}$$

Similarly, the probability that an idle period lasts for *j* time slots is

$$R(j) = r(1-r)^j \qquad \text{for } j \ge 0$$

and the corresponding mean idle period is given by

$$E_{l}[j] = \sum_{j=0}^{\infty} j \cdot R(j) = \frac{1-r}{r}$$

Hence, for a given p and r, the offered load L is given by

$$L = \frac{E_B[i]}{E_B[i] + E_I[j]} = \frac{r}{r + p - rp}$$

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### 2.7.2 Evaluation under Balanced Bursty-Traffic Conditions

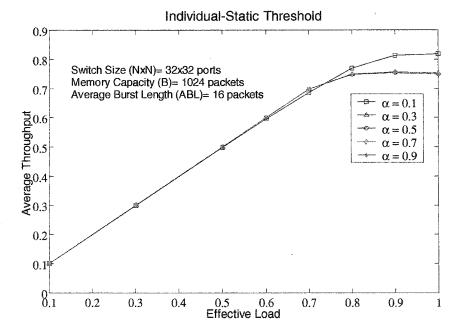

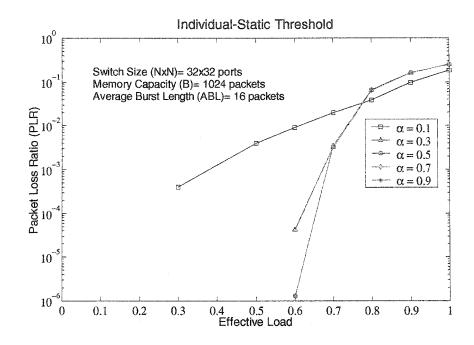

The shared-memory switch in the simulation study is an NxN = 32x32 ports where the input and output lines work at identical rates. The number of data-packets that can be stored in the shared-memory space is 1,024 packets. All ports have access to the common memory space which is organized into logical queues corresponding to the different output-ports. Each input line of the switch receives data-packets from a bursty source with an average burst length (ABL) = 16 packets. Incoming bursts of packets are uniformly distributed to the output-ports, i.e. bursts of packets have equal probability to be destined to any output-port. Values of  $\alpha$  constant utilized for the simulation are  $\alpha$  = 0.1, 0.3, 0.5, 0.7, and 0.9 for all memory-sharing schemes. The effect of the memorysharing scheme in the throughput performance and packet-loss is more evident at higher loads. As load is incremented for the switch, some packets might be dropped due to the lack of available memory space to buffer them. For that reason, the memory-sharing scheme should maximize the passage of packets through all input-output pairs by regulating the use of the memory space efficiently.

First, we evaluate average throughput (Fig. 2.7) in a shared-memory switch employing individual-static threshold based sharing scheme with  $\alpha = 0.1, 0.3, 0.5, 0.7$ and 0.9. We have a higher throughput at higher loads (>80%) with  $\alpha = 0.1$  compared to others values of  $\alpha$  constant. Value of  $\alpha = 0.1$  means that any queue length could take up to 10% of the buffer-space. While limiting the amount of buffer-space for output-ports at higher loads guarantees a reasonable good access of packets to all the output-ports, the advantage of shared buffer-space in the switch is reduced. As a result, at low and mid loads packets could be dropped even when there is idle buffer-space. For the throughput performance given for different  $\alpha$  values, we also measure the corresponding packet-loss ratio (PLR) with balanced bursty-traffic. Fig. 2.8 shows the occurrence of packet-loss at low loads (<60%) for  $\alpha = 0.1$ . This packet-loss is caused by the restriction in size for queue lengths that limits the use of buffer-space for output-ports. Also packet-loss at low loads varies considerably with different  $\alpha$  values. In the individual-static threshold scheme the setting of  $\alpha$  constant results difficult. At higher loads, it is preferable to have small  $\alpha$  values. However at low loads, there is significant packet-loss with small  $\alpha$  values; and it is necessary to have big  $\alpha$  values to allow queue length for output-ports to expand in order to allow packets enter the switch to use the available buffer-space.

Fig. 2.7 Average throughput with balanced bursty-traffic conditions for individual-static threshold based sharing scheme

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Fig. 2.8 Packet-loss ratio (PLR) with balanced bursty-traffic conditions for individual-static threshold based sharing scheme

Fig. 2.9 shows the average throughput in a shared-memory switch using the global-static threshold based sharing scheme to regulate the use of buffer-space. Throughput performance is higher with  $\alpha = 0.1$  compared to others  $\alpha$  values. For  $\alpha = 0.1$ , the global-static threshold is equal to 90% of the buffer-space. That means the memory is completely shared before the occupancy of buffer-space reaches 90% capacity and then after only packets for underrepresented ports are accepted into the switch according to the admittance policy. In the global-static threshold scheme, it is preferable to have a small  $\alpha$  value that allow a complete sharing of memory up to the threshold value; and when load increases close by the full memory capacity, packets are selectively admitted to the remaining of the buffer-space. For the throughput performance in Fig. 2.9, the corresponding packet-loss ratio (PLR) (Fig. 2.10) is also measured under identical balanced bursty-traffic conditions. Unlike PLR in individual-static threshold scheme (Fig.

2.8), PLR in global-static threshold scheme (Fig. 2.10) present less variation for different values of  $\alpha$  constant. Furthermore, there is no packet-loss in global-static threshold scheme at low loads (<60%) because queue lengths are no restricted in size at low loads.

Fig. 2.9 Average throughput with balanced bursty-traffic conditions for global-static threshold based sharing scheme

Fig. 2.10 Packet-loss ratio (PLR) with balanced bursty-traffic conditions for global-static threshold based sharing scheme

Evaluation of average throughput in a shared-memory switch using dynamic threshold based sharing scheme is presented in Fig. 2.11. Throughput is evaluated under balanced bursty-traffic. Dynamic threshold scheme achieves the highest throughput (86%) with large  $\alpha$  values at full load (100%) compared to the other memory- sharing schemes. Results for throughput are very similar as  $\alpha$  value is incremented. Therefore, dynamic threshold scheme is very robust for variations in  $\alpha$  constant. For the throughput performance, we also measure the corresponding packet-loss ratio (PLR) under identical balanced bursty-traffic conditions. PLR for large  $\alpha$  values is decreased;  $\alpha = 0.9$  represents that at any time, queue lengths for output-ports less than 90% of the idle buffer-space are permitted to built-in inside memory and their packets are accepted into the switch. In the dynamic threshold scheme, it is better to have big values of  $\alpha$  constant in order to obtain the lowest PLR when burst of packets are uniformly distributed to the output-ports.

Fig. 2.11 Average throughput with balanced bursty-traffic conditions for dynamic threshold based sharing scheme

Fig. 2.12 Packet-loss ratio (PLR) with balanced bursty-traffic conditions for dynamic threshold based sharing scheme

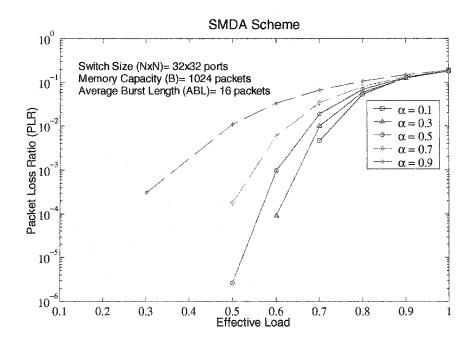

Fig. 2.13 shows the average throughput in a shared-memory switch using the SMDA based memory-sharing scheme with balanced bursty-traffic. Throughput performance is higher using small  $\alpha$  values. It is noticed that throughput in SMDA scheme (81%) is less than throughput for dynamic threshold scheme (86%) at full load (100%). This smaller throughput is explained due to the fact SMDA scheme dedicates an amount of buffer-space to each output-port exclusively, reducing the total amount of memory space shared by all output-ports. For the throughput performance, the corresponding packet-loss ratio (PLR) is also measured under identical balanced bursty-traffic conditions. SMDA scheme with  $\alpha = 0.1$  present the lowest packet-loss compared to other  $\alpha$  values. When  $\alpha = 0.1$ , the total memory space (1,024 packets) is divided in the dedicated memory (96 packets) and the shared memory (928 packets); where the dedicated memory (96 packets) allocates 3 packet locations exclusively to each output-port. It is better in the SMDA scheme to have a small amount of buffer-space dedicated to output-ports under balanced bursty-traffic conditions.

Fig. 2.13 Average throughput with balanced bursty-traffic conditions for SMDA based sharing scheme

Fig. 2.14 Packet-loss ratio (PLR) with balanced bursty-traffic conditions for SMDA based sharing scheme

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### 2.7.3 Evaluation under Unbalanced Bursty-Traffic Conditions

A switch with NxN = 32x32 ports is used for the simulation study. Buffer capacity in the shared-memory is 1,024 packets. All ports have access to the common memory space which is organized into logical queues corresponding to the different output-ports. Each input line of the switch receives data-packets from a bursty source with an average burst length (ABL) = 16 packets. Incoming bursts of packets are unevenly distributed to the output-ports. For that reason, some ports have a greater chance to receive packets than others. This unbalanced bursty-traffic scenario produces two classes of output-ports: very active output-ports and lightly active output-ports. In this simulation study, the probability that a burst of packets is destined to a very active port is considered to be four times greater than that of a lightly active port. Also, in this simulation, we consider the number of very active output-ports to be equal to that of the lightly active output-ports.

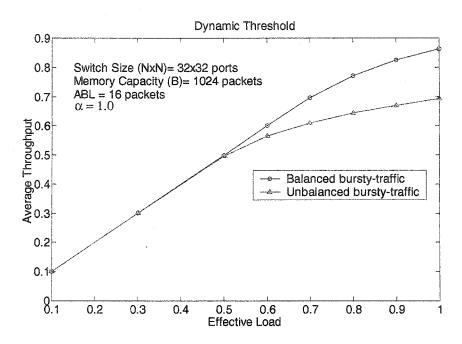

Packets destined to very active output-ports might attempt to take over most of the buffer-space; affecting the access to the switch to others packets destined to less active output-ports. This agglomeration of packets in highly loaded output-ports causes packets to be dropped due to insufficient buffer-space to handle these hot spots. In effect, an unbalanced bursty-traffic degrades the performance of a switching system. As illustrated in Fig. 2.15, average throughput in a switch with unbalanced bursty-traffic is considerably lower compared to the throughput with balanced bursty-traffic under identical switch resources and the memory-sharing scheme used.

Fig. 2.15 Average throughput in a switch with balanced bursty-traffic and unbalanced bursty-traffic

The memory-sharing scheme should avoid the starvation in buffer-space caused by some very active output-ports due to the unbalanced bursty-traffic. The overall utilization of the switching system could be maintained high, if packets destined for less active output-ports are permitted to gain a fair access to the buffer-space. Furthermore, performance of the lightly active output-ports compared to very active output-ports allows us to measure the effectiveness of the memory-sharing scheme under evaluation.

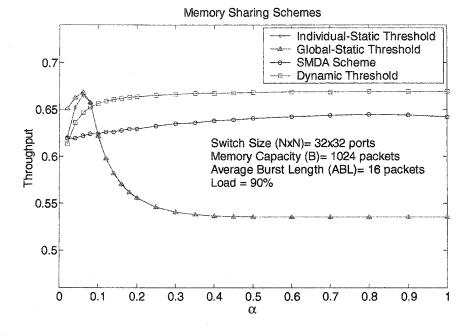

Throughput versus  $\alpha$  constant is shown in Fig. 2.16 for all memory-sharing schemes at 90% load. A high load (90%) will intensify the differences among the various memory-sharing schemes. The interval of  $\alpha$  constant extends in (0, 1) for all memory-sharing schemes except for the dynamic threshold scheme that could be any value greater than zero. Individual-static threshold and global-static threshold based sharing schemes have a high throughput at small  $\alpha$  values. For the applied load of 90% with unbalanced

bursty-traffic, both schemes namely the individual-static and global-static schemes experience a rapid degradation in performance when the  $\alpha$  value is increased.

Fig. 2.16 Throughput vs. a constant, for different memory-sharing schemes at 90% load

SMDA and dynamic threshold based sharing schemes are very stable in variations of  $\alpha$  constant. At high loads (90%) throughput increases slightly in SMDA scheme with greater  $\alpha$  values, nevertheless this means that a large percentage of memory is dedicated to each output-port which reduces the advantages of the sharing effect. Dynamic threshold scheme shows the best performance, and stays stable with variations in  $\alpha$ constant, but  $\alpha$  value could be greater than one.

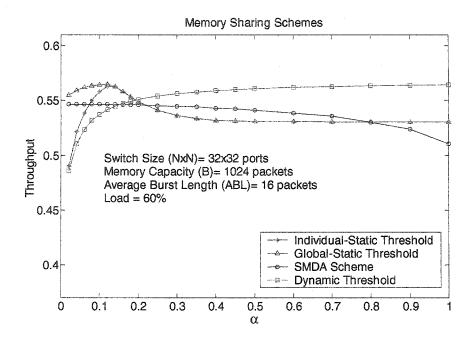

Fig. 2.17 shows the throughput versus  $\alpha$  constant, for all memory-sharing schemes at 60% load. Decreasing the switch-load slow down the throughput variations with different  $\alpha$  values compared to Fig. 2.16. Throughput performance for individual-

static threshold and global-static threshold schemes for 60% of applied load (Fig. 2.17) suffer a notable variation within the range they perform well at load of 90% (Fig. 2.16). SMDA scheme for 60% of applied load (Fig. 2.17) presents a decrease in throughput as  $\alpha$  is incremented. This is in contrast to the throughput value at higher load of 90% (Fig. 2.16). It is apparent that SMDA scheme performs well under overload conditions. However, for smaller loads of 60%, the SMDA throughput somewhat decreases with increase in  $\alpha$  value. This phenomenon occurs at low load because when  $\alpha$  is incremented more memory space is reserved for each output-port (dedicated buffer), which decreases the advantage of memory sharing. Under this situation, there is a higher probability that some ports may have empty buffers while other ports may be discarding packets due to their buffers being full.

Dynamic threshold scheme performs similarly at high and low loads. It adapts to the changing traffic conditions, while there is a high occupancy of the memory space only packets from underrepresented output-ports are accepted to the remaining bufferspace. On the other hand when most of the buffer-space is idle queue lengths are allowed to expand and packets are accepted for very active output-ports

Fig. 2.17 Throughput vs. a constant, for different memory-sharing schemes at 60% load

The remaining figures in this chapter presents packet lost ratio (PLR) for each memory-sharing scheme under evaluation. Because of the unbalanced distribution of traffic to the output-ports, the packet-loss ratio (PLR) is evaluated individually for each of the two different classes of the output ports. We should expect the very active output-ports to incur a higher packet-loss compared to lightly active output-ports. A good sharing policy should increase the utilization of the switching system by allowing the packets for less active output-ports to also have access to the shared memory resources for switching purposes.

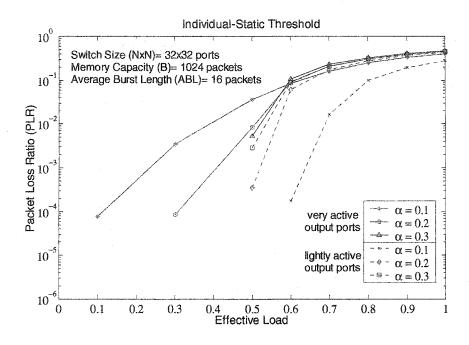

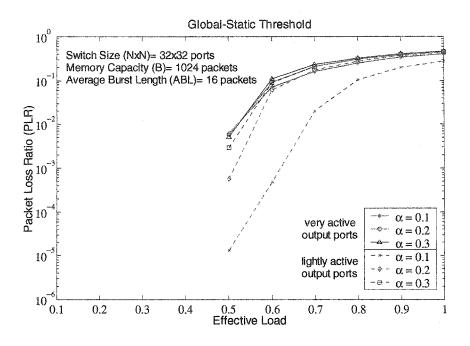

We evaluate in Fig. 2.18 and Fig. 2.19 the packet-loss ratio (PLR) using the individual-static threshold based sharing scheme under unbalanced bursty-traffic conditions. Individual-static threshold scheme with low values of  $\alpha$  constant (i.e.  $\alpha = 0.1$ , 0.2 and 0.3) causes the static threshold (ST) to be small. This in turn, limits to short

lengths the output queues. As shown in Fig. 2.18, there is packet-loss at low loads (<50%) caused by buffer-space denied to some output-ports due to the restriction imposed by the static threshold (ST). While a small ST value maintain short lengths in output queues and it ensures a fair access to buffer-space for output-ports; it also causes a great amount of buffer-space to be maintained idle when only a few output-ports are actively receiving packets. Therefore, at low loads some active output-ports are dropping packets (as seen with  $\alpha = 0.1$  and 0.2) even when there is available buffer-space due to restriction imposed by ST value. Fig. 2.18 also indicates an extensive variation in packetloss for the different values of  $\alpha$  constant and the resulting ST value. It implies that the Individual-static threshold scheme is not robust for variation of  $\alpha$  values and the imprecise setting of ST value can produce a poor performance of the switching system. Packet-loss ratio (PLR) is depicted in Fig. 2.19 with high values of  $\alpha$  constant (i.e.  $\alpha$  = 0.6, 0.7 and 0.8). Individual-static threshold scheme with high values of  $\alpha$  constant produces a large static threshold (ST) value. This allows output queues to expand to long lengths, not restricting their built in inside memory. As a value get closer to one, the Individual-static threshold scheme tends to complete share the buffer-space. Consequently, a large ST value permit packet destined for very active output-port to block packets destined for less active ports; and lightly active output-ports suffer the same packet-loss experienced by very active output-ports as shown in Fig. 2.19.

Fig. 2.18 Packet-loss ratio (PLR) for very active output-ports and lightly active outputports in individual-static threshold based sharing scheme with  $\alpha = 0.1, 0.2, \text{ and } 0.3$

Fig. 2.19 Packet-loss ratio (PLR) for very active output-ports and lightly active outputports in individual-static threshold based sharing scheme with  $\alpha = 0.6, 0.7, \text{ and } 0.8$

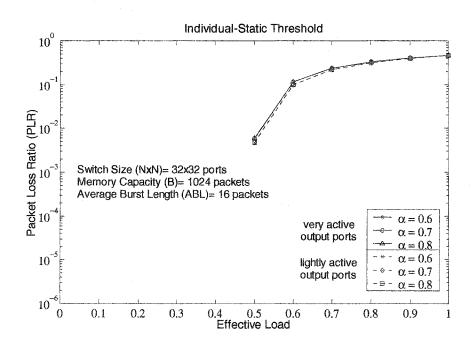

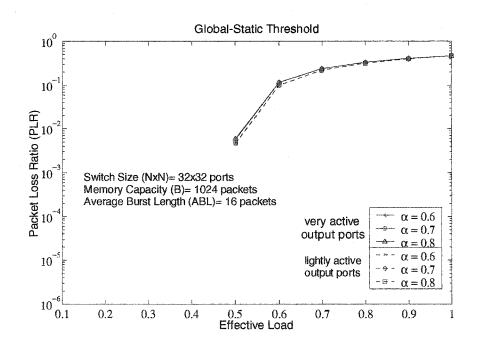

39

Packet-loss ratio (PLR) is evaluated in Fig. 2.20 and Fig. 2.21 for a sharedmemory switch using the global-static threshold based sharing scheme under unbalanced bursty-traffic conditions. Unlike Individual-static threshold scheme (Fig. 2.18), globalstatic threshold scheme (Fig. 2.20) with low values of  $\alpha$  constant (i.e.  $\alpha = 0.1, 0.2$  and 0.3) does not suffer packet-loss at low loads (<50%). Global-static threshold scheme allows the share of the buffer-space before the global threshold (GT) value is reached. After the GT value is reached only packet for less active output-ports are permitted to access the remaining buffer-space. Global-static threshold scheme also presents a wide variation in Packet-loss for the different values of  $\alpha$  constant; so we need to be careful in the setting of  $\alpha$  constant in order to obtain the desired performance of the switching system. Packet-loss ratio (PLR) is presented in Fig. 2.20 with high values of  $\alpha$  constant (i.e.  $\alpha = 0.6, 0.7$  and 0.8). Like individual-static threshold scheme (Fig. 2.18), globalstatic threshold scheme with high values of  $\alpha$  constant (Fig. 2.20) allows complete sharing of the buffer-space. As a result lightly active output-ports would incur the same packet-loss as that of very active output-ports. A higher value of global threshold (GT) allows most of the buffer-space to be completely shared. This can cause the very active output ports to monopolize the common memory space, which in turn would prevent the underrepresented output-ports from accessing the common buffer-space.

Fig. 2.20 Packet-loss ratio (PLR) for very active output-ports and lightly active outputports in global-static threshold based sharing scheme with  $\alpha = 0.1, 0.2$ , and 0.3

Fig. 2.21 Packet-loss ratio (PLR) for very active output-ports and lightly active outputports in global-static threshold based sharing scheme with  $\alpha = 0.6, 0.7, \text{ and } 0.8$

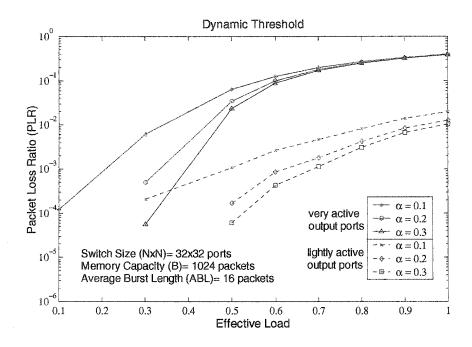

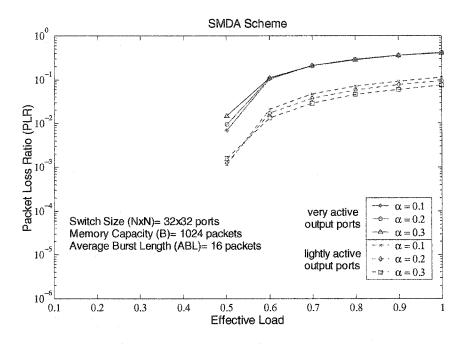

Fig. 2.22 and Fig. 2.23 show packet-loss ratio (PLR) in a shared-memory switch using the dynamic threshold based sharing scheme under unbalanced bursty-traffic conditions. The value of  $\alpha$  constant used in dynamic threshold scheme is  $\alpha > 0$ , with  $\alpha = 0.5$ , 1.0, 2.0, 3.0, 5.0 and 9.0. The dynamic threshold scheme offers the best performance compared to the others memory-sharing schemes in this simulation study.

First, lightly active output-ports have the lowest packet-loss ratio (PLR) compared to other memory-sharing schemes. Dynamic threshold scheme provides packets destined for lightly active output-ports the best access to memory resources in the presence of congested output-ports. Fig. 2.22 and Fig. 2.23 show a difference of two orders of magnitude in the PLR between lightly active and very active output-ports. A fair memory-sharing scheme should ensure that an output-port drops packets (if necessary) proportional to the traffic present on it. The dynamic threshold scheme always allows the lightly active output-ports to access the memory space for switching purposes and hence the packet-loss incurred for this class of ports stays extremely low.

Second, the dynamic threshold scheme shows very stable PLR for different values of  $\alpha$  constant. Different values of  $\alpha$  constant do not produce drastically different switch performance. In Fig. 2.23, only a large value of  $\alpha$  constant (i.e.  $\alpha = 9.0$ ) shows a slightly difference in PLR among lightly active output-ports.

Fig. 2.22 Packet-loss ratio (PLR) for very active output-ports and lightly active outputports in dynamic threshold based sharing scheme with  $\alpha = 0.5$ , 1.0, and 2.0

Fig. 2.23 Packet-loss ratio (PLR) for very active output-ports and lightly active outputports in dynamic threshold based sharing scheme with  $\alpha = 3.0, 5.0, \text{ and } 9.0$

43

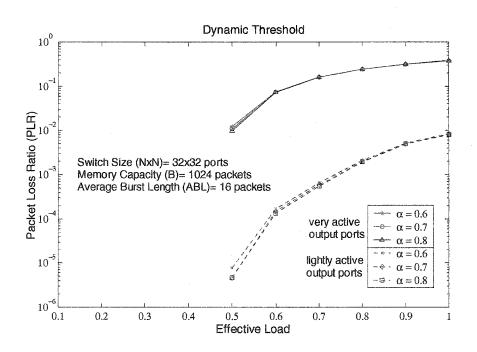

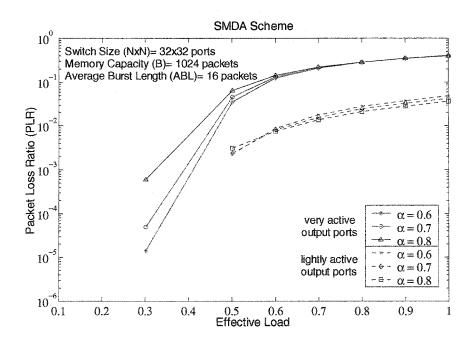

Fig. 2.24 and Fig. 2.25 depict the packet-loss ratio (PLR) incurred by a sharedmemory switch using the SMDA based memory sharing scheme under unbalanced bursty-traffic conditions. In the SMDA scheme each class of output-ports have similar packet-loss ratio (PLR) among them for the various values of  $\alpha$  constant. In SMDA scheme as the value of  $\alpha$  constant is incremented, more buffer-space is reserved exclusively for each output-port. Results in Fig. 2.24 and Fig. 2.25 show that the PLR value for lightly active output ports are slightly decreased at higher loads (>60%) for greater values of  $\alpha$  constant. This decrease in PLR is due to the fact that at high loads (> 60%), it is better for output-ports have more dedicated buffer-space. This will help prevent starvation for lightly active output ports even if the majority of the shared bufferspace is occupied by some very active output-ports. On the contrary if we dedicate too much buffer-space exclusively to each output-port (with high  $\alpha$  values) then the performance-enhancing effect of sharing will be diminished and higher PLR can be experienced at lower loads. Under this situation, the active output-ports drop packets due to the lack of buffer-space while other output-ports may have idle buffer-space. This waste in buffer-space causes packet-loss at lower loads (e.g. 30% load) as shown in Fig. 2.25.

Fig. 2.24 Packet-loss ratio (PLR) for very active output-ports and lightly active outputports in SMDA based sharing scheme with  $\alpha = 0.1, 0.2, \text{ and } 0.3$

Fig. 2.25 Packet-loss ratio (PLR) for very active output-ports and lightly active outputports in SMDA based sharing scheme with  $\alpha = 0.6, 0.7, \text{ and } 0.8$

45

# CHAPTER 3

# SWITCHING ARCHITECTURES DEPLOYING SHARED PARALLEL MEMORY-MODULES

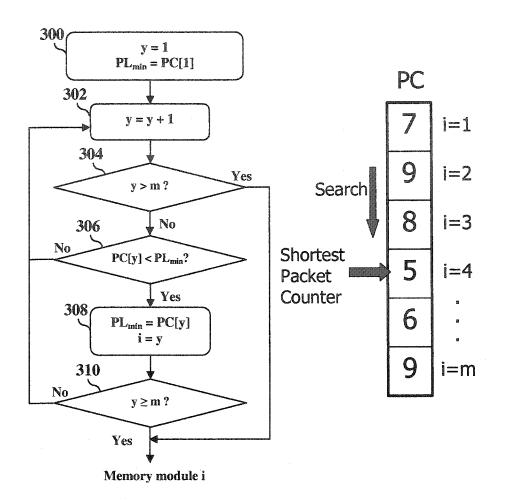

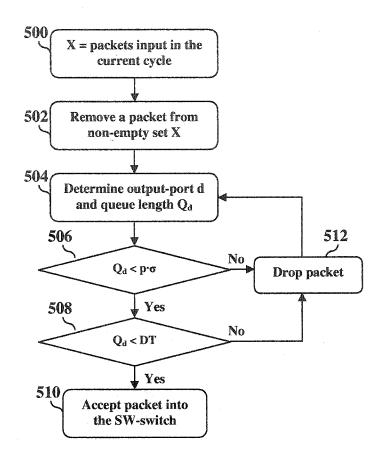

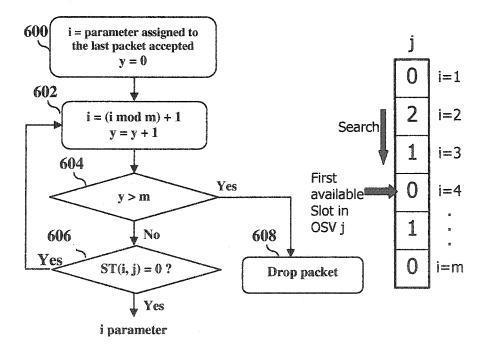

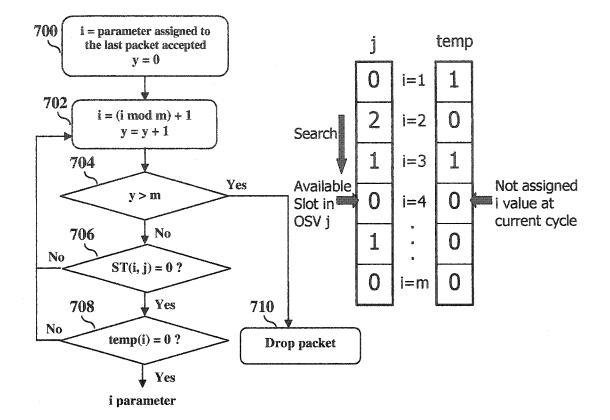

## 3.1 Introduction