# High Gain Magnetically Coupled Single Switch Quadratic Modified SEPIC DC-DC Converter

Soroush Esmaeili, Morteza Shekari, Milad Rasouli, Sara Hasanpour, Member, IEEE, Ashraf Ali Khan, Member, IEEE, and Hossein Hafezi, Senior Member, IEEE

Abstract-This article proposes, analyzes, and tests an improved high voltage gain dc-dc converter based on a singleended primary-inductor converter (SEPIC). The proposed magnetically coupled quadratic modified SEPIC converter (MCQ-MSC) employs a coupled transformer with an optimized design to obtain a high voltage boost factor by controlling the transformer's turn ratio along with the switching duty cycle. Thanks to the unique structure of the coupled transformer, high voltage gain is obtained at low turns ratio, which is highly desirable for high voltage applications and the compact size of the converter. In addition to the coupled transformer, a voltage-boosting module is utilized to achieve a very high output voltage for a low switching duty cycle. The proposed inverter has a single switch with a wide control range of duty cycle (0<D<1), causing low conducting losses and high efficiency. Furthermore, a clamping circuit is successfully designed to remove the leakage inductance effects of the coupled transformer on the power switch. The proposed MCQ-MSC drains a continuous current from the input dc source, which makes it a suitable choice for renewable energy sources (RES). The hardware prototype of the proposed converter is tested to verify the mathematical expressions and theoretical results.

*Index Terms*— Magnetically coupled inductors, SEPIC converter, single-switch topology, voltage-boosting module.

#### I. INTRODUCTION

n recent years, the applications of renewable energy sources **L**(RES) and energy storage systems (ESS) have sparked a heated debate among the diverse industrial sections. However, the main impediment of RES and ESS is their bounded voltage range with intermittent characteristics. Considering the crucial role of DC-DC converters in providing the required voltage for these applications, they can be exploited to convert the low and intermittent input voltage of PV sources (12-48 V) to the demanded voltage of the microgrids buses (200-800V) [1-2]. The same challenge is for electric vehicle (EV) applications [3]. On the other hand, conventional dc-dc boost converters such as ZETA, SEPIC, and CUK topologies suffer from a limited range of output voltage. To achieve an output voltage of 200-800V, converters must be controlled by a high switching duty cycle, which is practically not viable because turning on the power switches for long intervals causes operation malfunction, efficiency reduction, and high power losses. Consequently, the practical voltage boost factor in the aforementioned conventional converters is 4-5 [4].

To overcome the low voltage gain issues of the conventional converters, various techniques like switched inductors cells, switched capacitors cells, multi cells, and multi-stages have been employed [5]. For instance, in [1], a cascaded connection of the boost and buck-boost converters has been used to attain high voltage gain. A voltage multiplier cell, a boost converter in [3], and a switched capacitor in [4] have been exploited for voltage gain increment. Nonetheless, these techniques lead to high costs and volume of the converters. Various coupled inductor-based DC-DC converters have been introduced to generate a high output voltage with fewer circuit elements [6-10]. Generally, the voltage gain can be raised by increasing the transformer's turn ratio, which increases convert size and control complexity [11]. To avoid increasing the transformers' turn numbers for high voltage applications, quadratic boost, quadratic quadrupler boost, and quadratic flyback boost structures have been employed in [6-9]. Furthermore, to attain low switching loss with the zero voltage switching technique, the magnetizing inductance of the coupled transformer is used in [7].

Recently, many magnetically coupled inductor impedance source structures such as Y-source [12],  $\Gamma$ -source [13], and asymmetrical  $\Gamma$ -source [14] networks have been introduced to obtain a high voltage gain with a low switching duty ratio. Nevertheless, they suffer from the narrow duty cycle control range and huge voltage spikes on the power switches [15-16]. To limit the voltage spikes, various clamping circuits have been applied to the magnetic coupling impedance source networks [16]. However, their narrow duty ratio control range is still a significant problem. Modified semi-SEPIC converters based on coupled inductors with full duty cycle control have been proposed in [17-18] to eliminate the abovementioned drawbacks. These topologies increase the voltage gain by lowering the transformer's turn ratio. However, lowering the turn ratio must be done regularly. Otherwise, distortions in output waveforms occur, restricting the operation to low-power applications.

To overcome the drawbacks of conventional converters, a novel dual winding modified SEPIC converter is proposed in this paper [19]. This paper continues the earlier work in [20], briefly introducing a quadratic SEPIC converter. This paper presents a comprehensive presentation of the proposed converter; closed-loop control, dynamic response evaluations, parameters design, comparative analysis, power loss analysis, components load factors, and experimental results. The proposed converter integrates a coupled inductor with a voltage-boosting module to deliver a high output voltage for high-voltage applications. This paper is organized as follows; circuit description, operating principle, and coupled transformer's leakage inductance effect are given in section II. Section III deals with voltage gain analysis, the voltage stress on the semiconductors, and the dynamic behavior of the proposed system. Section IV provides a thorough comparison of the proposed and similar conventional topologies. Design consideration of the proposed converter is given in section V. Finally, the experimental results, power loss analysis, and components load factor evaluation are presented in sections VI, VII, and VIII, respectively.

## II. PROPOSED MAGNETICALLY COUPLED QUADRATIC MODIFIED SEPIC DC-DC CONVERTER (MCQ-MSC)

#### A. Circuits Description

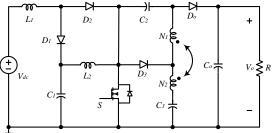

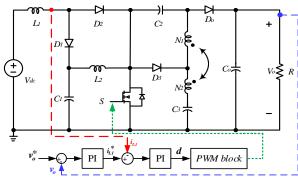

Fig. 1 shows the circuit diagram of the proposed MCQ-MSC. Similar to the original SEPIC converter, the proposed MCQ-MSC contains only one power switch (S), one input inductor  $(L_1)$ , one middle capacitor  $(C_2)$ , one output diode  $(D_0)$ , and one output capacitor (Co). The middle inductor in a conventional SEPIC topology is replaced with a coupled dual winding transformer with a turn ratio of n = N1/N2. In addition, the power switch is linked with the input source by a voltageboosting module. The boosting module includes one inductor  $(L_2)$ , one capacitor  $(C_1)$ , and two diodes  $(D_1, D_2)$ . One diode  $(D_3)$  and one capacitor  $(C_3)$  enhance the voltage gain further. The magnetizing inductance (L<sub>m</sub>) is modeled on the secondary winding, and an impedance source network connects the input and output sides of the converter. The proposed topology has the following main features: 1) exploiting a single power switch; 2) low conducting losses; 3) a wide range of duty cycle control (0 < D < 1); 4) simple control implementation; 5) continuous input current; 6) high voltage boost ability; 7) optimized coupled transformer's turn ratio; 8) non-isolated common-ground structure; 9) eliminating voltage spikes by using the clamping circuit and 10) removing leakage inductance effects without utilizing snubber circuit.

#### B. Operation Principle of the Proposed MCQ-MSC

To simplify the operation principle of the proposed converter following suppositions have been conceived: the components are ideal; the capacitors' and inductors' resistance are ignored; ON resistance of the power switch, voltage drop of diodes, and parasitic capacitance are neglected.

In a switching cycle of a Continuous Current Mode (CCM), there are three operation states as follows:

1) State I - interval [t<sub>0</sub> - t<sub>1</sub>]

As shown in Fig 2(a), the power switch and D2 are turned ON in state I, and  $D_1$ ,  $D_3$ , and  $D_0$  are reverse biased by capacitors  $C_1$ ,  $C_3$ , and  $C_0$ , respectively. Inductor  $L_1$  is charged by the input source ( $V_{dc}$ ) via the current path of  $V_{dc}$ - $L_1$ - $D_2$ -S- $V_{dc}$ .

Fig. 1. Proposed magnetically coupled quadratic modified SEPIC converter

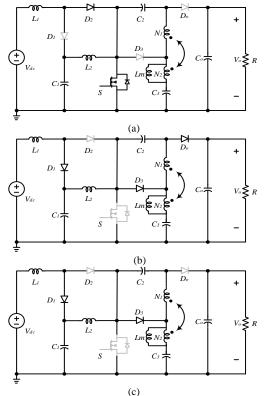

Also, the inductor  $L_2$  is energized by capacitor  $C_1$  with the current path of  $C_1$ - $L_2$ -S- $C_1$ . Windings  $N_1$  and  $N_2$  are charged through the current path of  $N_2$ - $N_1$ - $C_2$ -S- $C_3$ - $N_2$ . The resistive load is supplied through the output capacitor Co, which is isolated from the input source. In this interval, the current of  $L_1$ ,  $L_M$  and  $L_2$  are rising. Fig.3 demonstrates the critical characteristic current waveforms of inductors, diodes, and the power switch.

#### 2) State II - interval $[t_1 - t_2]$

Fig. 2(b) shows the operation state II when *C2 turns OFF*  $D_2$  and the power switch (*S*) is switched OFF. In this mode,  $L_1$  discharged the stored energy into  $C_1$  via the path of  $V_{dc}$ - $L_1$ - $D_1$ - $C_1$ - $V_{dc}$ .  $C_2$  is charged with  $L_2$  via the current path of  $C_1$ - $L_2$ - $C_2$ - $D_o$ - $C_o$ - $C_1$ . The saved energy in the coupled inductors is discharged to the  $C_3$  and load via the path of  $C_3$ - $N_2$ - $N_1$ - $V_o$ - $C_3$ . From  $t_1$  to  $t_2$ , the current of  $L_1$ ,  $L_M$ , and  $L_2$  are decreased, as shown in Fig. 3.

## 3) State III- interval $[t_2 - t_3]$

For steady-state analysis, the coupled inductor is assumed ideal. Nevertheless, its leakage inductance effect is noticeable. Due to the leakage inductance effect,  $D_o$  is turned OFF before the end of the switching period while the power switch is still OFF. This mode is demonstrated as mode III in Fig. 2(c). By designing a coupled inductor with high magnetizing inductance and low leakage inductance, the effect of this state can be ignored. The parasitic capacitor in the power switch and its resonance with the leakage inductance causes voltage spikes across the power switch. During state II, when the switch is turned OFF, the power switch is clamped to  $-V_{C2}+V_{Co}$ , shown in Fig. 2(b). Additionally, the saved energy in leakage inductance is absorbed by  $C_2$  and  $C_3$ , leading to the voltage spike voiding across the switch, shown in Fig. 2 (c). Hence, the snubber circuit is not needed in the proposed topology, which reduces size and cost.

Fig. 2. Equivalent circuits of the proposed MCQ-MSC. (a) State I. (b) State II. (c) State III.

Fig. 3. Characteristic waveforms of the MCQ-MSC in CCM.

Furthermore, considering the described operating principles in Fig. 2, the dynamic equations of the proposed MCQ-MSC can be extracted. In this regard, the voltages of all inductors  $(i_{L1}, i_{L2}, \text{ and } i_{Lm})$  and the currents of the capacitors (i<sub>C0</sub>, i<sub>C1</sub>, i<sub>C2</sub>, and i<sub>C3</sub>) should be calculated. Accordingly, all the dynamic equations are summarized in Table I.

#### **III. CIRCUIT ANALYSIS OF THE PROPOSED CONVERTER**

#### A. Voltage Gain Analysis in Steady-State

Ideally, the losses of the source, diodes, inductors, and power switch are neglected. In addition, the voltage ripples of the capacitors are negligible. Moreover, the voltage relation between windings  $N_1$  and  $N_2$  is assumed as:

$$\iota = \frac{V_{N1}}{V_{N2}} \tag{1}$$

Thus, from Fig. 2(a) and by applying Kirchhoff's Voltage Law (KVL) in state I, the voltage expressions of the inductors and magnetizing  $L_m$  are given as:

$$V_{L1} = V_{dc} \tag{2}$$

$$V_{12} = V_{C1}$$

(3)

$$V_{Lm} = \frac{V_{C3} - V_{C2}}{n - 1} \tag{4}$$

From Fig. 2(b) and by applying KVL in state II, the voltage equations of the inductors and the magnetizing  $L_m$  are:

$$V_{L1} = V_{dc} - V_{C1}$$

(5)

$$V_{L2} = V_{C1} + V_{C2} - V_{o}$$

(6)

$$V_{Lm} = \frac{-V_{C2}}{n} \tag{7}$$

$$V_{L2} = \frac{V_{C2}}{n} - V_{C3} + V_{C1}$$

(8)

Applying the volt-second balance principle for the inductors and magnetizing  $L_m$ , (9)-(11) are achieved where  $T_s$  represents the switching period.

$$\int_{0}^{DTs} V_{L1} dt + \int_{DTs}^{Ts} V_{L1} dt = 0$$

(9)

$$\int_{0}^{0} V_{L2} dt + \int_{DTs} V_{L2} dt = 0$$

(10)

$$\int_{0}^{10} V_{Lm} dt + \int_{DTs}^{10} V_{Lm} dt = 0$$

(11)

Also, the voltage across capacitors can be obtained as:

$$V_{c1} = \frac{1}{1 - D} V_{dc}$$

(12)

$$V_{C2} = \frac{nD}{(1-D)^2 (n-1)} V_{dc}$$

(13)

$$V_{C3} = \frac{n-1+D}{(1-D)^2 (n-1)} V_{dc}$$

(14)

In addition, the output dc voltage is achieved as:

$$V_o = \frac{n - 1 + nD}{(1 - D)^2 (n - 1)} V_{dc}$$

(15)

Hence, the voltage gain equation is obtained as:

$$G = \frac{V_o}{V_{dc}} = \frac{n-1+nD}{(1-D)^2 (n-1)}$$

(16)

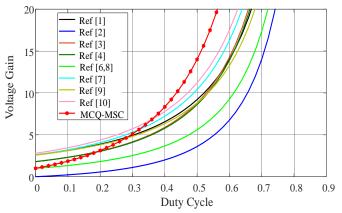

The voltage gain of the proposed converter from (16) is plotted in Fig. 4. It can be seen that the voltage gain of the proposed MCQ-MSC can be increased by decreasing n. This interesting feature of the proposed converter leads to lower the converter's size, control complexity, and implementation cost.

#### B. Voltage Stress on the Semiconductors

According to Fig. 2(b), the voltage stress on the switch is the difference between  $V_O$  and  $V_{C2}$ . Consequently, the voltage on the power switch ( $V_S$ ) is obtained as:

$$V_{S} = V_{o} - V_{C2} = \frac{(n-1)V_{o}}{n-1+nD}$$

(17)

From Fig. 2(a), the voltage stress on the diode  $D_I$  is derived as

$$V_{D1} = V_{C1} = \frac{(1-D)(n-1)V_o}{(n-1+nD)}$$

(18)

From Fig. 2(b), the voltage stress on the diode  $D_2$  is derived as

$$V_{D2} = V_o - V_{C1} - V_{C2} = \frac{D(n-1)V_o}{n-1+nD}$$

(19)

From Fig. 2(a), the voltage stress on the diode  $D_3$  is obtained IV.COMPARISON OF THE PROPOSED MCQ-MSC AND SIMILAR in (20).

$$V_{D3} = \frac{V_{C3} - V_{C2}}{n - 1} + V_{C3} = \frac{nV_o}{n - 1 + nD}$$

(20)

From Fig. 2(a), the voltage stress on the output diode  $(D_o)$ is derived as (21).

$$V_{Do} = V_o - V_{C2} = \frac{(n-1)V_o}{n-1+nD}$$

(21)

#### С. Dynamic Response Evaluations

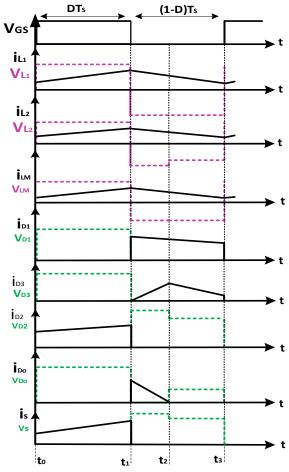

Considering the described operating principles in Fig. 2, the dynamic equations of the proposed MCQ-MSC can be extracted. In this regard, the voltages of all inductors  $(i_{L1}, i_{L2}, i_$ and  $i_{Lm}$ ) and the currents of the capacitors ( $i_{C0}$ ,  $i_{C1}$ ,  $i_{C2}$ , and  $i_{C3}$ ) should be calculated. Accordingly, all the dynamic equations are summarized in Table I. In this section, the frequency response (Bode plot) from input-to-output voltages (Vo/Vin) and control-to-output voltage (Vo/d) of the proposed converter obtained in Simulink/ MATLAB are depicted in Fig. 5 (a) and (b). Regarding these figures, the suggested converter is stable with nonminimum phase behavior. This is because of the right half-plane (RHP) zero in the control-to-output transfer function. The nonminimum phase behavior imposes an extra phase shift to the transfer function's loop gain and limits the converter's bandwidth. The values of parameters are Vin = 24 V, D = 0.52, f=40 kHz, R = 100  $\Omega$ , L<sub>1</sub> = L<sub>2</sub> = 200 uH, C<sub>1</sub> = C<sub>2</sub>=C<sub>3</sub>=C<sub>0</sub>= 100 uF. Bode Diagram from V0 / Vi

Fig. 5. Bode plot diagrams of the proposed converter. (a) input-to-output and (b) control-to-output.

## TOPOLOGIES

#### Voltage Stress Comparative analysis Α.

Table II compares similar quadratic non-isolated high gain converters for physical and operational features to demonstrate the proposed circuit's advantages. Physical features include the number of switches (s), diode (d), capacitor (s), coupledinductor (CI), inductor (L), and total device count (T). Also, operational ones consist of voltage gain, stress, boosting, and soft/hard switching. For a fair comparison, the transformer's turns ratio of the presented topology is supposed  $n=N_1/N_2$ .

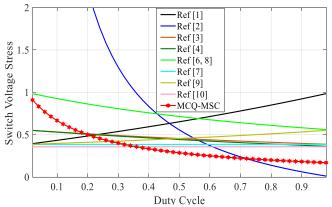

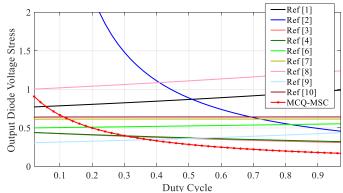

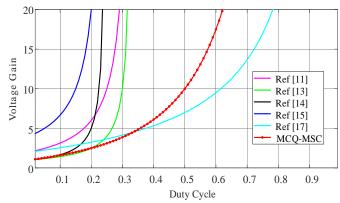

Fig. 6 to Fig. 9 compare the voltage gain and voltage stress across the semiconductors in the proposed and similar converters. Fig. 6 illustrates the voltage gain versus the switching duty cycle of the proposed and conventional topologies for n = 1.25 (see Table II). Accordingly, the proposed MCQ-MSC topology offers the highest voltage gain for the duty cycle range of D>0.35. Comparisons of the normalized maximum voltage stress across the power switch and the output diode  $(D_{\alpha})$  are provided in Fig. 7 and Fig. 8, respectively. MCQ-MSC offers the lowest voltage stress compared with similar conventional topologies. This leads to low-cost semiconductor switches and diodes with lower power loss. MCQ-MSC offers a broader switching duty ratio control range than the conventional transformer-based impedance source DC-DC converters.

Fig.6. Comparison of the voltage gains of the proposed MCQ-MSC and similar conventional converters for n=1.25

Fig. 7. Comparison of the normalized voltage stress on the power switch in the proposed MCQ-MSC and similar conventional topologies for n=1.25.

Fig. 8. Comparison of the normalized voltage stress on the output diode in the proposed MCQ-MSC and similar conventional topologies for n=1.25.

Fig. 9 proves that  $\Gamma$ -source [13] and asymmetrical  $\Gamma$ -source [14] networks and the proposed trans-inverse converters in [11] and [15] suffer from the narrow switching duty ratio control range.

Fig. 9. Comparison of the voltage gain and control range of duty cycle in the proposed MCQ-MSC and conventional trans inverse converters for n=1.5.

In addition, the proposed MCQ-MSC provides a higher voltage gain compared with the new trans-inverse semi-SEPIC converter [17], which offers a higher voltage gain in the minor switching duty cycle.

| TABLE I. DYNAMIC EQUATIONS OF THE PROPOSED MCQ-MSC<br>value |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |  |  |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|

| parameter                                                   | Mode I (t <sub>0</sub> <t< t<sub="">1)         Mode II (t<sub>1</sub><t< t<sub="">2)</t<></t<> |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |  |  |

| $L_1 \frac{di_{L1}}{dt}$                                    | V <sub>dc</sub>                                                                                | $v_{dc}$ - $v_{CI}$                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>dc</sub> - V <sub>CI</sub>    |  |  |

| $L_2 \frac{di_{L2}}{dt}$                                    | V <sub>CI</sub>                                                                                | $v_{CI} + v_{C2} - v_{CO}$                                                                                                                                                                                                                                                                                                                                                                                                                     | $v_{C1} - v_{C3} + \frac{v_{C2}}{n}$ |  |  |

| $L_m \frac{di_{Lm}}{dt}$                                    | $\frac{v_{C2} - v_{C3}}{1 - n}$                                                                | $-\frac{v_{C2}}{n}$                                                                                                                                                                                                                                                                                                                                                                                                                            | $-\frac{v_{c2}}{n}$                  |  |  |

| $C_o \frac{dv_{Co}}{dt}$                                    | $-\frac{\nu_a}{R}$                                                                             | $C_{o} \left( \frac{\frac{1}{(C_{3}+C_{o})} i_{L2} - \frac{1}{(C_{3}+C_{o})} \frac{v_{co}}{R} + \frac{C_{3}(n-1)}{C_{2}(C_{3}+C_{o})n^{2} + C_{o}C_{3}(n-1)^{2}} i_{Lm}}{-\frac{C_{3}(C_{3}+nC_{o})(n-1)}{C_{2}(C_{3}+C_{o})n^{2} + C_{o}C_{3}(n-1)^{2}} i_{L2}} - (\frac{\frac{C_{3}}{(C_{3}+C_{o})}(1 - \frac{C_{o}}{(C_{3}+C_{o})})(\frac{n-1}{n})^{2}}{(C_{2} + \frac{C_{o}C_{3}(n-1)^{2}}{(C_{3}+C_{o})n^{2}}})\frac{v_{co}}{R}} \right)$ | - <u>v</u> _<br><u>R</u>             |  |  |

| $C_1 \frac{dv_{c1}}{dt}$                                    | $-i_{L2}$                                                                                      | $i_{L1}$ - $i_{L2}$                                                                                                                                                                                                                                                                                                                                                                                                                            | $i_{L1} - i_{L2}$                    |  |  |

| $C_2 \frac{dv_{c2}}{dt}$                                    | $\frac{i_{Lm}}{n-1}$                                                                           | $C_{2} \left( \frac{\frac{1}{n}}{\frac{C_{o}C_{3}(1-\frac{1}{n})^{2}}{(C_{2} + \frac{C_{o}C_{3}(1-\frac{1}{n})^{2}}{(C_{3} + C_{o})}} i_{Lm} - \frac{\frac{1}{n}(C_{3} + C_{o}) + C_{o}(1-\frac{1}{n})}{(C_{2} + \frac{C_{o}C_{3}(1-\frac{1}{n})^{2}}{(C_{3} + C_{o})}} i_{L2} - \frac{n(n-1)C_{3}}{C_{2}(C_{3} + C_{o})n^{2} + C_{o}C_{3}(n-1)^{2}} \frac{v_{co}}{R} \right)$                                                                 | $\frac{i_{Lm} - i_{L2}}{n}$          |  |  |

| $C_3 \frac{dv_{c3}}{dt}$                                    | <u>i<sub>lm</sub></u><br>1-n                                                                   | $\left(\frac{1}{(1-n)} - \frac{C_2}{(1-n)(C_2 + \frac{C_oC_3(1-\frac{1}{n})^2}{(C_3 + C_o)})}\right)i_{Lm} - \left(\frac{C_2(n-1)(1-\frac{C_o}{(C_3 + C_o)})}{(1-n)(C_2 + \frac{C_oC_3(1-\frac{1}{n})^2}{(C_3 + C_o)})}\right)\frac{v_{co}}{R} + \left(-\frac{n}{(1-n)} - \frac{C_2(C_3 + C_o) + C_oC_2(n-1)}{(1-n)(C_2 + \frac{C_oC_3(1-\frac{1}{n})^2}{(C_3 + C_o)})}(C_3 + C_o)\right)i_{L2}$                                               | i <sub>L2</sub>                      |  |  |

TABLE I. DYNAMIC EQUATIONS OF THE PROPOSED MCQ-MSC

#### *B*. Components Load Factors Evaluation

This section investigates components load factors (CLFs) as an evaluation metric of the proposed converter. Since the number of the components in the proposed converter and the selected topologies is different, the CLF of the power switch, input inductor, coupled transformer, output diode, and output capacitor are investigated as a fair comparison, and according to [21-23], the CLF can be expressed by (22); Where  $(V^*, I^*)$ and  $P_{Total}$  represent the apparent power of a component and the total load power, respectively. Ideally, power losses are not considered, and it is assumed that  $P_{Total} = P_{IN} = V_{dc}$ .  $I_{L1}$ .

$$CLF = \frac{V^*.I^*}{P_{Total}}$$

(22)

In addition, the ripples of the RMS currents are ignored. For the used MOSFET, the peak voltage stress across the power switch is assumed as  $V^*$ , and the RMS value of its current is applied for  $I^*$ . Hence, the CLF of the power switch can be calculated as follow:

$$S - CLF = \frac{V_{sw,max} \cdot I_{S,RMS}}{V_{dc} \cdot I_{L1}}$$

(23)

Like the MOSFET CLF, the maximum blocking voltage of diode is chosen as  $V^*$ . Furthermore, the average current of the output diode is selected as  $I^*$ . Thus,

$$D_{O} - CLF = \frac{V_{D4,max} \cdot I_{DO,Avg}}{V_{dc} \cdot I_{L1}}$$

(24)

For the input inductor and coupled transformer, the average voltage and RMS current of the inductors and windings are selected as  $V^*$  and  $I^*$ , respectively. Hence, for the input inductor and coupled transformer, (25) and (26) are obtained.

$$L_1 - CLF = \frac{V_{L_1,Avg} \cdot I_{L1,RMS}}{V_{dc} \cdot I_{L1}}$$

(25)

$$T - CLF = \frac{V_{N_1,Avg} \cdot I_{N1,RMS} + V_{N_2,Avg} \cdot I_{N2,RMS}}{V_{dc} \cdot I_{L1}}$$

(26)

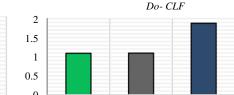

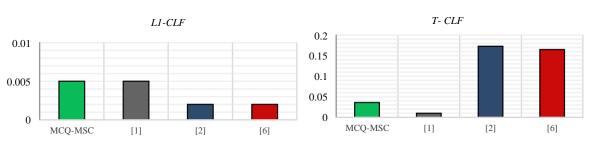

According to the obtained equations, the CLF amounts of the used components for the selected converters in [1], [2], [6], and the proposed converter at the boost factor of 13.8 are demonstrated in Fig. 10. It can be seen that MCQ-MSC

> S-CLF 8 6 4 2 0 MCQ-MSC

2 1.5 1 0.5 0 MCQ-MSC [1] S1 [2] S2 [2] [6]

[1]

[2]

[6]

Fig. 10. Values of the components load factors at G= 13.8.

provides lower semiconductors (power switch and output diode) CLF than the selected topologies. As a result, the proposed converter can be a better choice for high voltage applications when the lower stress of the semiconductors is a vital issue.

#### V.DESIGN CONSIDERATION OF THE PROPOSED MCQ-MSC

$L_l$ : The input inductor  $(L_l)$  limits the input current ripple. It can be designed based on (27). Where,  $\Delta I_{L1}$  represents the maximum permitted current ripple.

$$L_1 = \frac{V_{L1} \cdot D}{\Delta I_{L1} \cdot f_s} > \frac{V_{dc} \cdot D}{\Delta I_{in} \cdot f_s}$$

(27)

$L_2$ : For the allowable current ripple ( $\Delta I_{L2}$ ), the minimum value of the inductor  $L_2$  is calculated as:

$$L_{2} = \frac{V_{L2} \cdot D}{\Delta I_{L2} \cdot f_{s}} > \frac{V_{dc} \cdot D}{(1 - D)^{2} \Delta I_{Lin} \cdot f_{s}}$$

(28)

$L_m$ : Furthermore, the proper value of the magnetizing inductor of the coupled inductor can be determined by:

$$L_M > \frac{V_{Lm} \cdot (1-D)}{\Delta I_{LM} \cdot f_s} > \frac{nD \cdot V_{dc}}{(1-D)\Delta I_o \cdot (n-1)f_s}$$

(29)

Co: To limit the output voltage ripple, the output capacitor  $(C_o)$  can be obtained as in (30). Where  $\Delta V_{Co}$  is the maximum tolerant voltage ripple, usually recommended as 1%.Vo.

$$C_o = \frac{DV_{out}}{R_L \cdot \Delta V_{co} \cdot f_s} \tag{30}$$

$C_1$ ,  $C_2$ , and  $C_3$ : Moreover, other circuit capacitors can be designed based on their maximum current values and the allowable voltage ripple as in (31)-(33), where,  $\Delta V_{ci}$  is the maximum voltage ripple of each capacitor.

$$C_{1} = \frac{D.i_{L2}}{\Delta V_{C1}.f_{s}} = \frac{(1-D)GV_{out}}{\Delta V_{C1}R_{L}.f_{s}}$$

(31)

$$C_{2} = \frac{i_{C2} \cdot D}{\frac{1}{N_{C2}}} = \frac{i_{N2} \cdot D}{\frac{1}{N_{C2}}}$$

(32)

$$C_{3} = \frac{i_{C3} \cdot D}{\Delta V_{c3} \cdot f_{s}} = \frac{i_{N2} \cdot D}{\Delta V_{c3} \cdot f_{s}}$$

(33)

| Converter<br>Topology                 | [1]                                                                               | [3]                                                                        | [4]                                                                            | [6]                                                | [7]                                                                    | [8]                                                   | [P]                                                |

|---------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------|

| s                                     | 2                                                                                 | 1                                                                          | 1                                                                              | 1                                                  | 2                                                                      | 1                                                     | 1                                                  |

| d                                     | 4                                                                                 | 6                                                                          | 6                                                                              | 6                                                  | 6                                                                      | 5                                                     | 4                                                  |

| c                                     | 4                                                                                 | 5                                                                          | 5                                                                              | 4                                                  | 6                                                                      | 3                                                     | 4                                                  |

| CI+L                                  | 1+1                                                                               | 1+1                                                                        | 1+1                                                                            | 1+2                                                | 1+1                                                                    | 1+2                                                   | 1+2                                                |

| Т                                     | 12                                                                                | 14                                                                         | 14                                                                             | 14                                                 | 16                                                                     | 12                                                    | 12                                                 |

| Voltage Gain                          | $\frac{1 + D + 2(\frac{1 - D}{n})}{(1 - D)^2}$                                    | $\frac{1+\frac{1}{n}+\frac{D}{n}}{(1-D)^2}$                                | $\frac{(\frac{3D+2}{n}) + (2-D)}{2(1-D)^2}$                                    | $\frac{1+\frac{D}{n}}{(1-D)^2}$                    | $\frac{1+\frac{2}{n}}{(1-D)^2}$                                        | $\frac{1+\frac{D}{n}}{(1-D)^2}$                       | $\frac{n-1+nD}{(1-D)^2 (n-1)}$                     |

| Voltage -<br>Boosting<br>Technique    | Cascade Connection of<br>Boost and Buck-Boost<br>converters + Coupled<br>Inductor | Voltage<br>Multiplier<br>Cell+ Boost<br>Converter +<br>Coupled<br>Inductor | Switched-Capacitor +<br>Coupled Inductor                                       | Quadratic Boost<br>Converter + Coupled<br>Inductor | Quadratic<br>Quadrupler<br>Boost<br>Converter +<br>Coupled<br>Inductor | Quadratic Fly back<br>Converter + Coupled<br>Inductor | Quadratic Boost<br>Converter + Coupled<br>Inductor |

| Parameterized<br>switch<br>(Vs/Vo)    | $\frac{(1+D)}{1+D+2(\frac{1-D}{n})}$                                              | $\frac{1}{1 + \frac{1}{n} + \frac{D}{n}}$                                  | $\frac{\frac{(2+D(\frac{1}{n}-1))}{(\frac{3D+2}{n})+(2-D)}}{(\frac{2V_0}{n})}$ | $\frac{1}{1 + \frac{D}{n}}$                        | $\frac{1}{1+\frac{2}{n}}$                                              | $\frac{1}{1 + \frac{D}{n}}$                           | $\frac{(n-1)}{n-1+nD}$                             |

| Voltage Stress<br>on Output<br>Diodes | $\frac{(1 + \frac{2 - D}{n})V_o}{(1 - D)^2}$                                      | $\frac{(\frac{V_o}{n})}{1+\frac{1}{n}+\frac{D}{n}}$                        | $\frac{\frac{(\frac{2V_o}{n})}{(\frac{3D+2}{n}) + (2-D)}$                      | $\frac{(2+D(\frac{1}{n}-1))V_o}{1+(\frac{1}{n})D}$ | $\frac{(\frac{V_o}{n})}{1+\frac{2}{n}}$                                | $\frac{(1+D(\frac{1}{n}-1))V_{o}}{1+(\frac{D}{n})D}$  | $\frac{(n-1)V_o}{n-1+nD}$                          |

| Soft-Switching                        | No                                                                                | No                                                                         | No                                                                             | No                                                 | Yes                                                                    | No                                                    | No                                                 |

| Efficiency at Po=100W                 | 96.1 %                                                                            | 93.1 %                                                                     | 93 %                                                                           | 92.8 %                                             | 91 %                                                                   | 93 %                                                  | 93 %                                               |

## VI.EXPERIMENTAL RESULTS

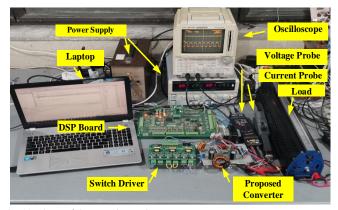

A hardware prototype of the proposed MCQ-MSC is designed, fabricated, and implemented to verify theoretical analyses. Considering the renewable sources' low output voltage, the proposed converter's input voltage is kept low (29 V), whereas the proposed converter's output voltage is considered high (400 V) as desired for the DC microgrids and electric vehicles. Under these conditions, the operation of the proposed topology is evaluated both in steady and dynamic state conditions. A photo of the experimental setup is depicted in Fig. 11. The circuit parameters of the proposed converter are given in Table III. The coupled inductor is executed using an iron powder core, and its turn ratio is n=1.35.

Fig. 11. Photo of the experimental setup.

TABLE III. CIRCUIT PARAMETERS

| THEE III. CINCOLI THINHETERS |                       |  |  |  |

|------------------------------|-----------------------|--|--|--|

| Components                   | Туре                  |  |  |  |

| MOSFET                       | IRFP460               |  |  |  |

| Diode                        | MUR860                |  |  |  |

| DSP                          | TMS320F28335          |  |  |  |

| Drivers                      | LPE113-01-01          |  |  |  |

| Voltage Sensor               | Minmax-MAU1511627     |  |  |  |

| Current Sensor               | Honeywell-CSNE151-100 |  |  |  |

| Switching frequency          | 40 kHz                |  |  |  |

| $L_1 = L_2$                  | 200µH                 |  |  |  |

| $C_1 = C_2 = C_3 = C_4$      | 100µF                 |  |  |  |

|                              |                       |  |  |  |

The dual loop PI controller is employed to analyse the proposed converter's closed-loop operation, shown in Fig. 12. The outer loop regulates the output voltage, and the inner loop controls the input inductor  $L_l$  current. The controller is implemented through a digital signal processor (DSP) with a sampling time (T<sub>S</sub>) of 100 microseconds.

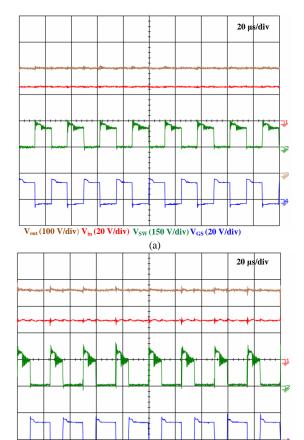

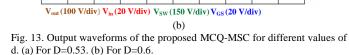

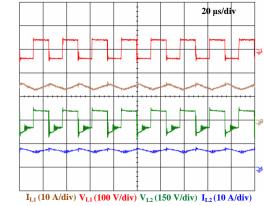

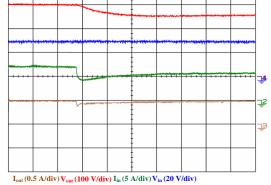

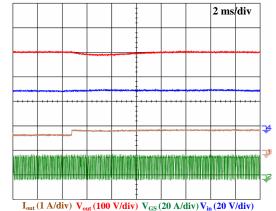

Fig. 13(a) illustrates the circuit's voltage waveforms for D=0.53. The input voltage is 29 V, and the output voltage approaches 400 V, verifying (16). Similarly, Fig. 13(b) shows identical waveforms for D=0.6. Fig. 14 shows the current and voltage waveforms of the inductors ( $L_1$  and  $L_2$ ) under steady-state operation. The performance of both inductor currents is stable and reacts smoothly at exact variation moments. In addition, the inductors' voltages confirm that  $L_1$  and  $L_2$  charge and discharge correctly. Also, the voltage and current waveforms of the switch are shown in Fig. 15.

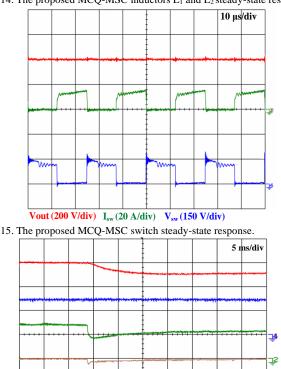

The proposed converter's transient response is first evaluated under a sudden change in the output voltage reference. Fig. 16 shows the dynamic response of the proposed converter when the output voltage reference changes from 400 volts to 350 volts while the input voltage is kept constant during the test. In such conditions, the output load Ro is 780  $\Omega$ . It is noted that the converter reacts rapidly to this change, and the output voltage reaches smoothly to its new level. Furthermore, the DC-DC converter is tested due to a load alteration. Fig. 17 demonstrates the transient performance of the proposed converter when the output load varies from Ro=640  $\Omega$  to Ro=500  $\Omega$ . As can be perceived, after an acceptable undershoot at the exact load alteration moment, the output voltage approaches the steady-state conditions. Also, the output current responds appropriately to this change.

Fig. 12. Schematic overview of the closed-loop control for MCQ-MSC.

Fig. 14. The proposed MCQ-MSC inductors L<sub>1</sub> and L<sub>2</sub> steady-state response.

Fig. 15. The proposed MCQ-MSC switch steady-state response.

Fig. 16. Transient response of the proposed MCQ-MSC when output voltage reference changes from 400 V to 350 V.

Fig. 17. Dynamic response of MCQ-MSC under a sudden output load change.

The significant power losses originate from the capacitors' semiconductors losses, magnetic losses, and ESR [24-26]. The switch power loss includes the MOSFET conduction and switching losses. Hence, the transistor's conduction loss is obtained from (34); Where  $r_{DS}$ ,  $I_{S,AVG}$  and  $I_{S,RMS}$  represent the On-resistance of MOSFET and average and RMS values of the transistor's current, respectively.

$$P_{con} = r_{DS} I_{S,RMS}^{2} + V_{DS,on} I_{S,AVG}$$

(34)

Likewise, the turn-on and turn-off switching power loss of the switch can be calculated from (35):

$$\begin{cases} P_{sw-ON} = 0.5 f_{sw} I_{DS(ON)} V_{DS} t_{ON} \\ P_{sw-OFF} = 0.5 f_{sw} I_{DS(OFF)} V_{DS} t_{OFF} \end{cases}$$

(35)

Where  $I_{DS(ON)}$  and  $I_{DS(OFF)}$  are the MOSFET current at turn-on and turn-off instants, respectively. Likewise,  $t_{ON}$  and  $t_{OFF}$ represent the time of turn-on and turn-off transition of the power switch. Hence, the switching power loss of the MOSFET is:

$$P_{SW} = P_{SW-ON} + P_{SW-OFF} = 0.5 f_{SW} V_{DS} (I_{DS(ON)} t_{ON} + I_{DS(OFF)} t_{OFF})$$

(36)

Hence, the power loss in the power switch is expressed by:

$$P_{FET} = P_{con} + P_{sw} = r_{DS} I_{S,RMS}^{2} + 0.5 f_{sw} V_{DS} (I_{DS(ON)} t_{ON} + I_{DS(OFF)} t_{OFF})$$

(37)

The forward voltage drop power losses of the diodes can be expressed by:

$$P_{V_F} = \sum_{i=1}^{4} V_F \ I_{Di}$$

(38)

Where  $V_F$  and  $I_{Di}$  are forward voltage drops and average currents of diodes. In addition, the power losses of the diodes due to their parasitic resistances ( $r_D$ ) are expressed by (39); Where  $I_{Di,RMS}$  is the RMS value of diodes' currents.

$$P_{r_D} = \sum_{i=1}^{4} r_D \cdot I_{Di,RMS}^2$$

(39)

Thus, the total power losses of the diodes can be obtained as:

$$P_D = P_{VF} + P_{r_D} = \sum_{i=1}^{4} V_F I_{Di} + \sum_{i=1}^{4} r_D . I_{Di,RMS}^2$$

(40)

The magnetic power losses come from core, copper, and ESR losses. From [24], the coupled inductors' core losses are gained by (41). Where  $B_{max}$ ,  $\beta$ ,  $K_{fe}$ ,  $A_c$ , and  $l_m$  present peak AC flux density, core loss exponent, core loss coefficient, core cross-sectional area, and mean magnetic path length, respectively.

$$P_{fe} = B_{max}^{\ \beta} K_{fe} A_c l_m \tag{41}$$

Additionally, the copper losses of the  $L_1$ ,  $L_2$ , and coupled inductors can be obtained from (42-44):

$$P_{cu,L1} = \frac{\rho I_{L1,RMS}^2 (MLT)}{W_A K_u}$$

(42)

$$P_{cu,L2} = \frac{\rho I_{L2,RMS}^{2} (MLT)}{W_{*} K_{*}}$$

(43)

$$P_{cu,T} = \frac{\rho \left( N_1 I_{N1,RMS} + N_2 I_{N2,RMS} \right)^2 (MLT)}{W_A K_u}$$

(44)

Where  $\rho$ ,  $I_{L1,RMS}$ ,  $I_{L2,RMS}$ , MLT, WA, Ku,  $N_I$ ,  $N_2$ ,  $I_{N1,RMS}$ , and  $I_{N2,RMS}$  present wire effective resistivity, input inductor's

RMS current, RMS current of  $L_2$ , mean length per turn, core window area, winding fill factor, the primary winding turns number, the secondary winding turns number, RMS current of the primary winding, and RMS current of the secondary winding, respectively. Also, the power losses of the magnetic components due to their parasitic resistances are expressed by:

$$P_{ESR,L} = r_{L1}I_{L1,RMS}^{2} + r_{L2}I_{L2,RMS}^{2} + r_{N1}I_{N1,RMS}^{2} + r_{N2}I_{N2,RMS}^{2}$$

$$(45)$$

Hence, the total magnetic components' power losses is:

$$P_{L} = P_{cu,L1} + P_{cu,L1} + P_{cu,T} + P_{fe} + P_{ESR,L}$$

(46)

The power losses of capacitors' ESRs are derived as:

$$P_{C} = P_{ESR,C} = \sum_{i=1}^{1} r_{Ci} \cdot I_{Ci,RMS}^{2}$$

(47)

Thus, the total power losses of the proposed converter can be attained as (48).

$$P_{Loss,Total} = P_S + P_D + P_L + P_C \tag{48}$$

The efficiency of the proposed MCQ-MSC is calculated based on the theoretical relations, simulation results, datasheets, and magnetic elements' design. Additionally,  $C_o$ ,  $r_{L1}$ ,  $r_{L2}$ ,  $r_{N1}$ ,  $r_{N2}$ ,  $r_C$  are about 5 nF, 0.2  $\Omega$ , 0.2  $\Omega$ , 0.1  $\Omega$ , and 0.08  $\Omega$ , respectively. Fig. 18. shows the calculated efficiency of the proposed converter for various load currents and output voltages.

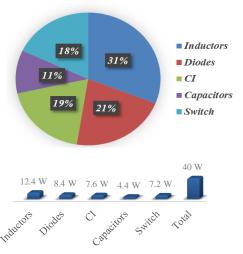

The full load efficiency (overall) is confirmed by experimental setup to be  $\eta=365 / (365+40) \approx 90$  percent. The power loss distribution at the full load (based on calculation) is shown in Fig. 19.

Fig. 18. Calculated efficiencies of the proposed MCQ-MSC for different load currents and output voltages

Loss Breakdown

Fig. 19. Power loss distribution at Po= 365W (based on calculation, overall efficiency confirmed by experiment at full load)

#### **VIII.** CONCLUSION

This paper proposes a new high-gain dc-dc converter suitable for high voltage and renewable energy applications. The proposed converter employs a single power switch, simplifying the control process. It integrates a coupled inductor and a voltage boosting module to achieve high output voltage applicable for DC microgrid and EV charging systems. Because of the unique design of the coupled transformer, the proposed converter attains a high voltage gain for a low and easily controllable value of the duty cycle. Unlike the conventional impedance source topologies and most other high voltage gain DC-DC topologies, the proposed MCQ-MSC provides a wide control range of switching duty cycle instead of the narrow range. The presented converter not only inherits the advantages of the non-isolated transformer types of quadratics and SEPIC converters but also offers a higher voltage transfer ratio with the low normalized voltage stress across its semiconductors. Besides, a clamping circuit provides a safe path for the leakage inductance energy and avoids generating voltage spikes across the power switch. Finally, experimental results have been presented to verify the proposed converter's operation.

#### REFERENCES

- S. Hasanpour, Y. P. Siwakoti, A. Mostaan, and F. Blaabjerg, "New semiquadratic high step-up dc/dc converter for renewable energy applications," *IEEE Transactions on Power Electronics.*, vol. 36, no. 1, pp. 433-446, Jan. 2021.

- [2] S. Hasanpour, A. Baghramian, and H. Mojallali, "Analysis and Modeling of a New Coupled-Inductor Buck-Boost DC/DC Converter for Renewable Energy Applications," *IEEE Trans. on Power Electron.*, vol.35, no. 8, pp. 8088 – 8101, Aug. 2020.

- [3] A. Mirzaee, S. Arab Ansari, and J. Shokrollahi Moghani, "Single switch quadratic boost converter with continuous input current for high voltage applications," *International Journal of Circuit Theory and Applications.*, vol. 48, no. 4, pp. 587–602, Apr. 2020.

- [4] P. Saadat and K. Abbaszadeh, "A single-switch high step-up DC–DC converter based on quadratic boost," *IEEE Trans. on Industrial Electron.*, vol.63, no. 12, pp. 7733-7742, Dec. 2016.

- [5] M. A. Salvador, T. B. Lazzarin, and R. F. Coelho, "High step-up DC–DC converter with active switched-inductor and passive switched-capacitor

networks," IEEE Trans. Ind. Electron., vol. 65, no. 7, pp. 5644–5654, Dec. 2018

- [6] S.W. Lee and HL Do, "High step-up coupled-inductor cascade boost DC– DC converter with lossless passive snubber," *IEEE Trans. on Industrial Electron.*, vol. 65, no.10, pp. 7753-7761, Oct.2018.

- [7] P. Upadhyay, R. Kumar, and S. Sathyan, "Coupled-inductor-based highgain converter utilising magnetising inductance to achieve soft-switching with low voltage stress on devices," *IET Power Electronics.*, vol. 13, no.3, pp. 576-591, Feb. 2020.

- [8] T. R. Choudhury, B. Nayak, and S. B. Santra, "A Novel Switch Current Stress Reduction Technique for Single Switch Boost-Flyback Integrated High Step Up DC–DC Converter," *IEEE Trans. on Industrial Electron.*, vol. 66, no.9, pp. 6876-6886, Sept. 2019.

- [9] B. Axelrod and Y. Berkovich, "DC-DC converter based on the switchedcoupled-inductor quadratic boost converter and diode-capacitor Dickson multiplier," *in EPE'17 ECCE Europe*, 2017, Warsaw, Poland, pp. 1-9.

- [10] X. Hu and C. Gong, "A high voltage gain DC–DC converter integrating coupled-inductor and diode–capacitor techniques," *IEEE Trans. on Power Electron.*, vol. 29, no. 2, pp. 789-800, Feb.2014.

- [11] Y. P. Siwakoti, F. Blaabjerg, and P. Chiang Loh, "High step-up trans inverse (Tx<sup>-1</sup>) DC-DC converter for the distributed generation system," *IEEE Trans. Ind. Electron.*, vol. 63, no. 7, pp. 4278–4291, Jul. 2016.

- [12] Y. P. Siwakoti, P. C. Loh, F. Blaabjerg, S. J. Andreasen, and G. E. Town, "Y-source boost DC/DC converter for distributed generation," *IEEE Trans. Ind. Electron.*, vol. 62, no. 2, pp. 1059–1069, Feb. 2015.

- [13] P. C. Loh, D. Li, and F. Blaabjerg, "F-Z-source inverters," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 4880–4884, Nov. 2013.

- [14] W. Mo, P. C. Loh and F. Blaabjerg, "Asymmetrical Γ-source inverters," *IEEE Trans Ind. Electron*, vol 61, no.2, pp 637-647, Feb 2014.

- [15] H. Liu, J. Wang, and Y. Ji, "A novel high step-up coupled-inductor DC-DC converter with reduced power device voltage stress," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol.7, no.3, pp. 1941–1948, Sept. 2019.

- [16] J. Ma, H. Liu, J. Chen, Y. Li, P. C. Loh, "A Family of Coupled Dual-Winding Impedance-Source Inverters with Continuous Input Currents and No DC-Link Voltage Spikes," *IEEE Journal of Emerging and Selected Topics in Power Electronics.*, Early access, Oct. 2020.

- [17] A. Mostaan., J. Yuan, Y. P. Siwakoti, Y., S. Esmaeili, F. Blaabjerg, "A trans-inverse coupled-inductor semi SEPIC DC/DC converter with full control range," *IEEE Trans. Power Electron.*, vol.34, no.11, pp. 10398-10402, May. 2019.

- [18] J. Yuan, A. Mostaan, Y.P. Siwakoti, F. Blaabjerg, "A modified Y-Source DC/DC converter with high voltage-gains and low switch stresses," *IEEE Trans. Power Electron.*, vol. 35, no.8, pp. 7716–7720, Aug. 2020.

- [19] K. P. Maroti, S. Esmaeili, A. Iqbal, M. Meraj, "High step-up single switch quadratic modified SEPIC converter for DC microgrid applications," *IET Power Electron.*, vol. 13, no. 16, pp. 3717-3726, Dec. 2020.

- [20] S. Esmaeili, S. Hasanpour, H. Hafezi, "New High Step-Up Coupled Dual Winding Quadratic Enhanced SEPIC DC-DC Converter," International Conference on Smart Energy Systems and Technologies (SEST), 2021, Vaasa, Finland.

- [21] B. Carsten, "Converter Component Load Factors-A Performance Limitation of Various Topologies," in Proc. PCI, Munich, Germany, 1988, pp. 31–49.

- [22] M. Kasper, D. Bortis and J. W. Kolar, "Classification and Comparative Evaluation of PV Panel-Integrated DC-DC Converter Concepts," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2511-2526, May 2014.

- [23] P. Wang and M. Chen, "Analysis and Design of Series Voltage Compensator for Differential Power Processing," *IEEE Journal of Emerging and Selected Topics in Power Electronics*,. Sept. 2021, doi: 10.1109/JESTPE.2021.3116091.

- [24] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, 2nd ed. Norwell, MA, USA: Kluwer, 2001.

- [25] M. K. Kazimierczuk, "Boost PWM DC-DC converter," in Pulse-Width Modulated DC-DC Power Converters, 2nd ed. Chichester, United Kingdom, 2016, pp. 98–106.

- [26] S. Esmaeili, E. Azimi, H. Hafezi, A. Mahmoudi, M. Jamil, and A. A. Khan, "Magnetically Coupled Single-Phase AC-AC Converter With Reduced Number of Passive Components," *IEEE Access*, vol. 10, pp. 79628 79643, Jul. 2022.

**Soroush Esmaeili** was born in Nowshahr, Iran. He received the B.Sc. degree in electrical engineering from the University of Guilan, Iran, in 2011, and the M.Sc. degree in power electronics from Mazandaran University of Science and Technology, Iran, in 2015. He is currently working toward the Ph.D. degree in electrical engineering at Memorial University of Newfoundland, St. John's, NL, Canada. His current research interest includes designing power electronics circuits for high voltage applications.

**Morteza Shekari** was born in North Khorasan Province, Iran, in 1986. He received his MSc degree in power electronics and electric machines from Shahid Beheshti University (SBU), Iran, in 2018. He is currently working in electronic calibration lab. His research interests include renewable energy generation systems (wind turbines), topology, and control of AC-DC converters.

Milad Rasouli received the B.sc. and M.sc. degrees in electrical engineering from Babol Noshirvani University of Technology, Babol, Iran, in 2014 and 2017, respectively. He is currently working toward the Ph.D. degree in the Department of computer and electrical engineering at the Lakehead University. His research interests include the control strategy of power converters and their applications in renewable energy and electric vehicles.

Sara Hasanpour was born in Iran, in 1979. She received the B.S. degree in electronic engineering from AzadIslamic University, Lahijan Branch, Iran, in 2002, the M.S. degree from the Isfahan University of Technology, Isfahan, Iran, in 2005, and the Ph.D. degree in power electronics engineering from University of Guilan, Rasht, Iran, in 2019. She received the best Ph.D. thesis award in power electronics engineering in Iran, awarded by the Power an 2020

Electronics Society of Iran, 2020.

She is currently assistant professor at Azad Islamic University, Ramsar Branch, Ramsar, Iran. Her major research interests include design and implementation of step-up/step-down switch-mode DC/DC converters with high-power density, renewable energy technologies, control and modeling of switched-mode DC/DC converters and electronic ballasts.

Ashraf Ali Khan (Member, IEEE) received the B.E. (Hons.) degree in electronics engineering from the National University of Sciences and Technology (NUST), Islamabad, Pakistan, in 2012, and the M.S. combined Ph.D. degree in energy engineering (majoring in power electronics) from Kyungpook National University, Daegu, South Korea, in 2018. He worked as a Postdoctoral Research and Teaching Fellow with The University of British Columbia,

Vancouver, BC, Canada. He has also worked as a Professor with the Okanagan College of Technology. He is currently working as an Assistant Professor with the Memorial University of Newfoundland, St. John's, NL, Canada, where he is the head of power electronics research group.

He is a chair of IEEE young professionals, Newfoundland section. Dr. Khan has authored or coauthored more than 70 technical papers published in various IEEE international conferences and IEEE journals.

His current research interests include high-efficiency grid-connected photovoltaic inverters, energy systems, and power factor correction circuits. He was a recipient of the IEEE Best Paper Award, in 2015, and the Best Researcher Awards, in 2015, 2016, and 2017. He has also received scholarships and awards from NICT Research and Development Fund Pakistan, NUST, Kyungpook National University, and BISE SWAT. He has served as the chairperson for several IEEE conferences.

Hossein Hafezi (M'17, SM'22) received the B.Sc. degree from the K. N. Toosi University of Technology, Tehran, Iran, in 2008, the M.Sc. degree from Dokuz Eylul University, Izmir, Turkey, in 2013, and the Ph.D. degree from the Energy Department, Politecnico di Milano, Milan, Italy, in 2017, all in electrical engineering. His employment experience includes working as a Postdoctoral Research Fellow with the Energy Department, Politecnico di Milano and as an Assistant Professor in School of Technology

and Innovations, Electrical Engineering at University of Vaasa, Finland.

Since September 2020, he joined Tampere University, Faculty of Information Technology and Communication Sciences as University Lecturer. His field of interests include power electronics converters design and control, power electronics and its applications in power quality improvement and smart grids systems, renewable energies integration into modern and smart grid systems and their effects on power quality and system operation, DC and Hybrid DC-AC low voltage distribution systems, Microgrid and electric power system studies.