MIR M.A.R KHAN

# On Design and Optimization of Convolutional Neural Network for Embedded Systems

#### MIR M.A.R KHAN

On Design and Optimization of Convolutional Neural Network for Embedded Systems

#### ACADEMIC DISSERTATION

To be presented, with the permission of the Faculty of Information Technology and Communication Sciences of Tampere University, for public discussion in the auditorium S2 of the Sähkötalo, Korkeakoulunkatu 3, Tampere, on 5 May 2023, at 12 o'clock.

#### ACADEMIC DISSERTATION

Tampere University, Faculty of Information Technology and Communication Sciences Finland

Responsible Professor

supervisor Timo Hämäläinen and Custos Tampere University

Finland

Supervisor Docent

Heikki Huttunen

Tampere University

Finland

Pre-examiners Professor Assistant Professor

Guillermo Payá Vayá Tomasz Kryjak

Technische Universität AGH University of Science

Braunschweig and Technology

Germany Poland

Opponent Senior University Lecturer

Jorma Laaksonen Aalto University

Finland

The originality of this thesis has been checked using the Turnitin OriginalityCheck service.

Copyright ©2023 author

Cover design: Roihu Inc.

ISBN 978-952-03-2891-7 (print) ISBN 978-952-03-2892-4 (pdf)

ISSN 2489-9860 (print) ISSN 2490-0028 (pdf)

http://urn.fi/URN:ISBN:978-952-03-2892-4

Carbon dioxide emissions from printing Tampere University dissertations have been compensated.

PunaMusta Oy – Yliopistopaino Joensuu 2023

# **PREFACE**

I'd like to thank Timo Hämäläinen and Jani Boutelier for supervising and guiding me throughout the research and writing the thesis. I would also like to thank Heikki Huttunen for his support and guidance.

#### **ABSTRACT**

This work presents the research on optimizing neural networks and deploying them for real-time practical applications. We analyze different optimization methods, namely binarization, separable convolution and pruning. We implement each method for the application of vehicle classification and we empirically evaluate and analyze the results. The objective is to make large neural networks suitable for real-time applications by reducing the computation requirements through these optimization approaches. The data set is of vehicles from 4 classes of vehicle types, and a convolutional model was used to solve the problem initially. Our results show that these optimization methods offer many performance benefits in this application in terms of reduced execution time (by up to  $5 \times$ ), reduced model storage requirements, without largely impacting accuracy, making them a suitable tool for use in streamlining heavy neural networks to be used on resource-constrained environments. The platforms used in the research are a desktop platform, and two embedded platforms.

# **CONTENTS**

| 1  | Intro | oduction                           | 17 |

|----|-------|------------------------------------|----|

| 2  | Back  | aground                            | 19 |

|    | 2.1   | Perceptron                         | 19 |

|    | 2.2   | Feed-forward neural networks       | 22 |

|    | 2.3   | Convolutions                       | 26 |

|    | 2.4   | Deep Convolutional Neural Networks | 27 |

| 3  | Met   | hodology                           | 29 |

|    | 3.1   | Application                        | 31 |

|    | 3.2   | Author's contributions             | 33 |

|    | 3.3   | Neural network                     | 34 |

|    | 3.4   | Optimization Challenges            | 35 |

|    | 3.5   | Dataset                            | 38 |

|    | 3.6   | Implementation                     | 39 |

| 4  | Sum   | mary of Results                    | 41 |

|    | 4.1   | Binarization                       | 41 |

|    | 4.2   | Separable Convolution              | 42 |

|    | 4.3   | Pruning                            | 44 |

|    | 4.4   | Conclusion of Results              | 45 |

| 5  | Rela  | ted work                           | 49 |

| 6  | Con   | clusion                            | 51 |

| Re | feren | ces                                | 53 |

|    |       |                                    |    |

# List of Figures

| 2.1     | Illustration of a perceptron                                             | 20   |

|---------|--------------------------------------------------------------------------|------|

| 2.2     | Plot of the sigmoid activation function                                  | 21   |

| 2.3     | Plot of the step function                                                | 22   |

| 2.4     | Plot of the hyperbolic tangent activation function                       | 23   |

| 2.5     | Plot of the ReLU activation function                                     | 24   |

| 2.6     | Artificial Neural Network with one hidden layer, not including bias      |      |

|         | terms                                                                    | 25   |

| 2.7     | Image Blurring                                                           | 27   |

| 3.1     | Visual outline of the research methodology                               | 32   |

| 3.2     | The principle of separable convolution, compared with regular con-       |      |

|         | volution                                                                 | 36   |

| 3.3     | Depthwise separable convolution, illustrated for one output featuremap   | . 36 |

| 3.4     | From left to right, a 'bus', 'normal car', 'truck', and a 'van'          | 38   |

| 4.1     | Performance/accuracy trade-off for different values of <i>K</i>          | 45   |

| 4.2     | Loss for convolutional layers 1 (left) and 2 (right) shown for different |      |

|         | values of <i>K</i>                                                       | 45   |

| 4.3     | Accuracy of the network on the validation set at retraining stages and   |      |

|         | fine-tuning stages.                                                      | 46   |

|         |                                                                          |      |

| List of | Tables                                                                   |      |

|         |                                                                          |      |

| 3.1     | A general outline of the elements of this work. The column date is       |      |

|         | associated with the paper published in that year                         | 31   |

| 3.2 | Technical specifications of the three platforms                      | 31 |

|-----|----------------------------------------------------------------------|----|

| 4.1 | Impact of different input-binarization schemes on classification ac- |    |

|     | curacy                                                               | 41 |

| 4.2 | Runtime per-layer (GTX1080), in the order of their execution         | 43 |

| 4.3 | Runtime of the network on each platform                              | 43 |

| 4.4 | Results of optimization methods at inference                         | 44 |

# **ABBREVIATIONS**

ANN Artificial Neural Network

CNN Convolutional Neural Network

cuDNN CUDA Deep Neural Network library

GEMM General Matrix Multiply

LBP Local Binary Patterns

# **ORIGINAL PUBLICATIONS**

Publication I M. Khan, H. Huttunen and J. Boutellier. Binarized Convolutional Neural Networks for Efficient Inference on GPUs. *EUSIPCO2018* (2018).

Publication II M. Khan, H. Lunnikivi, H. Huttunen and J. Boutellier. Comparing Optimization Methods of Neural Networks for Real-time Inference. *EUSPICO2019* (2019).

Publication III S. Payvar, M. Khan, R. Stahland, D. Mueller-Gritschnederand and J. Boutellier. Neural Network-based Vehicle Image Classification for IoT Devices. *IEE International Workshop on Signal Processing Systems* (2019).

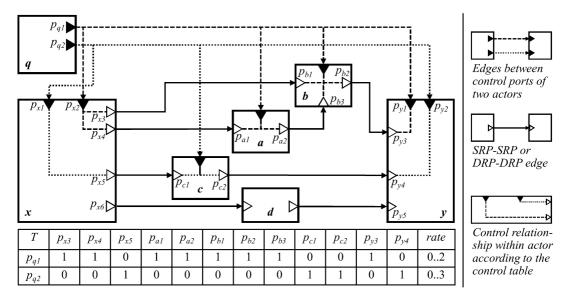

Publication IV J. Boutellier, Y. Ma, J. Wu, M. Khan and S. S. Bhattacharyya. VR-PRUNE: Decidable Variable-Rate Dataflow for Signal Processing Systems. *IEEE TRANSACTIONS ON SIGNAL PROCESSING*, VOL. 70, 2022 (2022).

# 1 INTRODUCTION

This work presents the research on optimizing neural networks and deploying them for real-time practical applications. By 'practical', we mean a setting where the neural network is running on an embedded device and is receiving data from a live camera source, and the inference is done in real time. The process starts by analyzing different optimization methods before selecting the most well-suited ones depending on the application. Once an optimization method is selected, we empirically evaluate the method by implementing it. Typically, the accuracy and the performance of the neural network is evaluated and compared with the original neural network across different platforms. Once enough empirical data is gathered, we focus on the deployment phase of the process by making it more efficient for specific hardware and the application.

The scope of this work is to explore the general advantages of optimization methods and their limits, not to satisfy a specified goal or meet certain performance requirements. This work is also not focused on finding neural network solutions, but rather use existing networks to be optimized for deployment and inference. This work also doesn't deal with safety-critical application, where the accuracy of the model is critical. Such applications also incorporate the concept of confidence in their model, which is out of scope of this work. The work is largely focused on a specific type of neural networks: *convolutional neural networks for image classification*. The optimizations are general, but are focused on deployment on embedded systems with parallel processing units.

The publications included can be categorized as follows: Specialized implementation of one optimization algorithm [33], empirical analysis and comparison of different optimization methods [34], deployment of an optimized method on an embedded system [53], and utilization of some features of the tool in high performance computing application in [4] showing versatility.

The research is mostly centered around optimizing neural networks in practical

setting, by analyze the results in performance and loss in accuracy. In the work, we also evaluate the practical benefits of these approaches. The research questions can be summarized as follows:

RQ1: What is the accuracy and performance trade-off from weight binarization, separable convolution, and weights pruning, and how they compare.

RQ2: How well the optimizations work in real-time embedded systems?

RQ3: How to speed up the process of design and deployment of neural network models?

This thesis is organized as follows: Section 2 discusses the background of neural networks and details about the algorithms, Section 3 discusses research methodology, Section 4 provides a summary of the results and their discussion, Section 5 discusses the related work, and Section 6 wraps up and concludes the thesis.

## 2 BACKGROUND

Machine Learning (ML) is a term that covers a wide range of approaches and methods of data analysis such as data classification, clustering and regression. Artificial Neural Networks (ANNs) fall under ML, and has a wide range of applications, that continued to expand over the past few years. ANNs are typically designed using supervised learning approaches such as the Backpropagation algorithm, where the network is initialized in a random configuration, that is then systematically and iteratively adjusted until the desired network behavior is achieved. Other approaches exist for designing ANNs, such as the works in [60][49] where neural network models are designed using genetic algorithms. Reinforcement learning is another method that can be used [62]. Neural networks have found great use in a variety of fields. Variations of ANNs have been applied in many areas such as image classification[55][58][22][31], speech recognition[18][71] [69], medical diagnosis [3][66][48][36][47], and object recognition [78][61][16][63][42]. This section provides the background for understanding how neural networks generally work and how the computations are done. Then the concept of convolutional neural networks are explained afterwards.

## 2.1 Perceptron

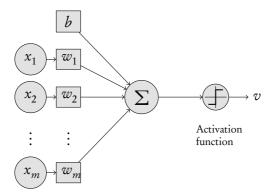

An ANN can essentially be thought of as a systen for processing information, with fundamental components known as "perceptrons" [27] (also called "neurons"). The perceptron has two basic components. First, it has a set of synapses or connecting links, each with an associated weight value as shown in Figure 2.1. The neuron computes its activation potential field v as a linear combination between input signal

Figure 2.1 Illustration of a perceptron

x and its weights.

$$v = \sum_{i=1}^{m} w_i x_i + b (2.1)$$

The parameter b in equation 2.1 is called the bias. This expression can be simplified by letting  $x_0 = 1$ , and  $w_0 = b$ , so that v can be rewritten as:

$$v = \sum_{i=0}^{m} w_i x_i \tag{2.2}$$

The second component is the activation function  $\phi$ , which is responsible for computing the perceptron's output  $y = \phi(v)$ . The choice of activation function is largely dependent on the desired behavior of the neural network. A list of activation functions that are commonly used are provided below with a brief explanation.

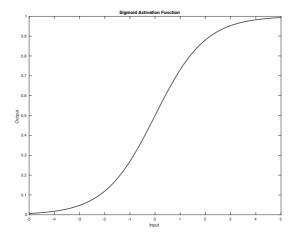

The logistic-sigmoid is a continuous function that compresses the value of its input from 0 to 1. It can be thought of as a smooth step function.

$$\sigma(x) = \frac{1}{1 + e^{-x}} \tag{2.3}$$

A plot of the sigmoid activation function is shown in Figure 2.2.

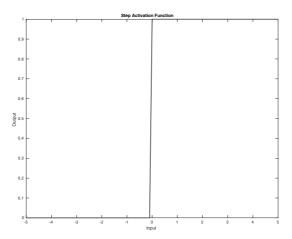

The step function is a discrete-valued function that outputs either a 0 or a 1.

$$s(x) = \begin{cases} 0 & \text{if } x < 0 \\ 1 & \text{if } x > 0 \end{cases}$$

(2.4)

Figure 2.2 Plot of the sigmoid activation function.

A plot of the step activation function is shown in Figure 2.3.

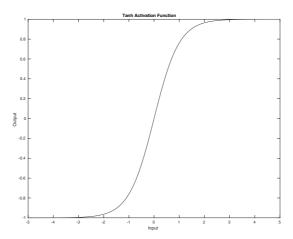

The tanh(x) function is a bipolar version of the logistic sigmoid function

$$\tanh(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}} \tag{2.5}$$

A plot of the tanh activation function is shown in Figure 2.4.

Softmax can output posterior probabilities and it is usually used at the output layer classification model to provide degree of certainty of the input belonging to one of the classes.

$$\operatorname{softmax}(x_j) = \frac{e^{xj}}{\sum m e^{x_m}} \tag{2.6}$$

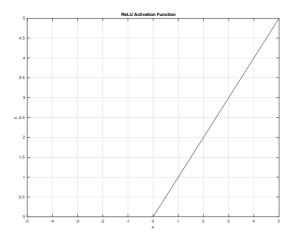

ReLU is a commonly used activation function which can reduce overfitting and is given as follows.

$$ReLU(x) = \max(0, x) \tag{2.7}$$

A plot of the ReLU activation function is shown in Figure 2.5.

Figure 2.3 Plot of the step function.

#### 2.2 Feed-forward neural networks

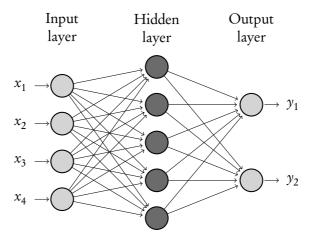

Typically a neural network is comprised of fundamental units called perceptrons. The network generally maps an input to an output that can include changes in the input's dimensionality. These days, neural networks can have multiple layers of computation before the final output layer. Between each layer, there is an activation function, a non-linearity, that can enhance the expressiveness of the network. The final layer in the network typically has a different activation function depending on the purpose. Figure 2.6 shows a neural network that receives an input  $x \in \mathbb{R}^4$ , which is used to generate an output  $y \in \mathbb{R}^2$ . Then essentially, the network provides a non-linear mapping from x to y.

Neural networks are implemented using techniques of linear algebra due to the large number of variables involved. Computing hardware such as (Graphical Processing Units) GPUs are often optimized to handle such operations efficiently. For a single neuron, what is known as its *induced local field* can be stated as a dot product:

$$v = \mathbf{w}^T \mathbf{x} \tag{2.8}$$

Figure 2.4 Plot of the hyperbolic tangent activation function.

Where the term  $\mathbf{w} = \begin{bmatrix} w_0 & w_1 & w_2 & \dots & w_n \end{bmatrix}^T$ , and  $\mathbf{x} = \begin{bmatrix} x_0 & x_1 & x_2 & \dots & x_n \end{bmatrix}^T$ .  $w_0$  is the bias term for the neuron, and  $x_0$  is set to 1. Each layer in the network can be characterized completely by its weights, or more conveniently as its weights matrix:

$$\mathbf{W} = \begin{bmatrix} w_0^0 & w_0^1 & w_0^2 & \dots & w_0^{n_b} \\ w_1^0 & w_1^1 & w_0^2 & \dots & w_1^{n_b} \\ w_2^0 & w_2^1 & w_0^2 & \dots & w_2^{n_b} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ w_m^0 & w_m^1 & w_m^2 & \dots & w_m^{n_b} \end{bmatrix}$$

This notation is convenient for its compact representation and usefullness when implemented in a programming language. We can interpret the number  $n_h + 1$  to denote the amount of neurons in the layer h, and m represents the dimensionality of the input to the layer, which is the same as the dimensionality of the weights vector of each neuron. We can compute the output of the layer as simply the result of the

Figure 2.5 Plot of the ReLU activation function.

matrix-vector product

$$\mathbf{W}^{T}\mathbf{x} = \begin{bmatrix} w_{0}^{0} & w_{1}^{0} & w_{2}^{0} & w_{3}^{0} & w_{4}^{0} \\ w_{0}^{1} & w_{1}^{1} & w_{2}^{1} & w_{3}^{1} & w_{4}^{0} \\ w_{0}^{2} & w_{1}^{2} & w_{2}^{2} & w_{3}^{2} & w_{4}^{2} \\ w_{0}^{3} & w_{1}^{3} & w_{2}^{3} & w_{3}^{3} & w_{4}^{3} \end{bmatrix} \begin{bmatrix} x_{0} \\ x_{1} \\ x_{2} \\ x_{3} \\ x_{4} \end{bmatrix}.$$

When an activation function  $\phi_h$  is applied to the matrix, it can simply be written as follows:

$$\mathbf{h} = \phi_h(\mathbf{W}^T \mathbf{x}) \tag{2.9}$$

It is common to evaluate the neural network for *batches* of inputs, especially during training. So if we have N inputs, each expressed as an m-vector in the columns of the matrix

Figure 2.6 Artificial Neural Network with one hidden layer, not including bias terms.

$$\mathbf{X} = \begin{bmatrix} x_1^1 & x_1^2 & x_1^3 & \dots & x_1^N \\ x_2^1 & x_2^2 & x_2^3 & \dots & x_2^N \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ x_m^0 & x_m^1 & x_m^2 & \dots & x_m^N \end{bmatrix},$$

then we can represent the output matrix  $\mathbf{Y}$  in a neural network with L-1 hidden layers, where the Lth layer represents the output layer  $\mathbf{Y}$ , as the following more general expression

$$\mathbf{Y} = \phi_I(\mathbf{W}_I^T \dots \phi_2(\mathbf{W}_2^T \phi_1(\mathbf{W}_1^T \mathbf{X}))\dots)$$

(2.10)

In order to avoid confusion, we clarify that the superscript in the elements of the matrix **X** does not denote exponentiation, but is rather an index, together with the subscripts, such that the superscript corresponds to columns, and the subscript corresponds to rows.

#### 2.3 Convolutions

Convolution is a commonly used operation in signal processing applications, and it is defined as

$$(f * g)(t) = \int_{-\infty}^{\infty} f(\tau)g(t - \tau)d\tau$$

(2.11)

In equation 2.11,  $f(\tau)$  and  $g(t-\tau)$  are the input functions, also known as the kernel and the signal, respectively. The integration is carried out over all possible values of  $\tau$ , from negative infinity to positive infinity. The variable t is the time parameter that specifies the point in time at which the convolution is evaluated. However, in image processing and digital systems, discrete convolution is more relevant. It is given as

$$(f * g)(n) = \sum_{-\infty}^{\infty} f[m]g[n-m]$$

(2.12)

In the discrete convolution equation 2.12, f and g are discrete functions, n is the index of the output signal, and m is the index of the input signal. More specifically, in image processing applications, the expression can be written in the 2D form:

$$y[i,j] = \sum_{m=-\infty}^{\infty} \sum_{m=-\infty}^{\infty} h[m,n] \cdot x[i-m,j-n]$$

(2.13)

where, x represents the input image, h is the kernel to be convolved with the input. The indices i and j depend on the image, while m and n relate to the kernel. For example, if the size of the kernel is  $5 \times 5$ , then the indices m and n would range from -2 to 2. The kernel is centered around each pixel in the image at each step in the calculation. Pixel values outside the border of the kernel are considered to be 0 in most applications.

Various image processing applications can be performed by applying a convolution kernel to an image. For example, a kernel

$$\mathbf{h} = \begin{bmatrix} \frac{1}{25} & \frac{1}{25} & \frac{1}{25} & \frac{1}{25} & \frac{1}{25} \\ \frac{1}{25} & \frac{1}{25} & \frac{1}{25} & \frac{1}{25} & \frac{1}{25} \\ \frac{1}{25} & \frac{1}{25} & \frac{1}{25} & \frac{1}{25} & \frac{1}{25} \\ \frac{1}{25} & \frac{1}{25} & \frac{1}{25} & \frac{1}{25} & \frac{1}{25} \\ \frac{1}{25} & \frac{1}{25} & \frac{1}{25} & \frac{1}{25} & \frac{1}{25} \end{bmatrix},$$

can be used to blur an image. By convolving the kernel  $\mathbf{h}$  with the picture of an apple shown in Figure 2.7, results in a blurred image as shown to its right.

In convolutional neural networks, convolution filters are used as part of the learnable parameters in the network.

Figure 2.7 Image Blurring

## 2.4 Deep Convolutional Neural Networks

Deep Convolutional Neural Networks (CNNs) are a type of neural network that are particularly effective in image and signal processing tasks. CNNs consist of several layers, each with different types of neurons. One important layer type in CNNs is the convolutional layer, which performs a convolution operation on the input data. The goal of the convolutional layer is to identify local patterns or features in the

input data that can be used to recognize more complex patterns at higher layers.

A convolutional layer has a set of filters, also known as kernels or weights, which are learned during the training process. Each filter is a small matrix of numbers that slides over the input data, performing a dot product at each location to produce an output feature map. The filter slides over the input data with a certain stride, which is the number of pixels or units it moves at each step. The output of the convolutional layer is a stack of feature maps, where each map represents a different pattern or feature that the layer has learned to detect.

Another important layer type in CNNs is the pooling layer, which downsamples the feature maps by taking a max or average value over small regions. This helps reduce the dimensionality of the feature maps and make the network more efficient. There are also other types of layers such as activation, batch normalization, and dropout layers that are commonly used in CNN architectures.

Training a CNN involves adjusting the weights of the network to minimize a loss function, which measures the difference between the predicted output and the actual output. This is typically done using an algorithm called backpropagation, which computes the gradient of the loss with respect to the network weights and updates them in the opposite direction to minimize the loss. However, training deep CNNs can be challenging due to issues such as vanishing gradients and overfitting, which can be mitigated using techniques such as weight initialization, batch normalization, and regularization.

CNNs have been successfully applied in many areas such as image classification, object detection, and natural language processing. Some well-known CNN architectures include LeNet-5, AlexNet, VGG, GoogLeNet, and ResNet, each with their own strengths and weaknesses. Recent advances in CNNs include attention mechanisms, transfer learning, and adversarial training, which have pushed the state-of-the-art in various domains. Overall, CNNs have proven to be a powerful tool for extracting meaningful information from complex data and are likely to continue to be an active area of research in the years to come.

## 3 METHODOLOGY

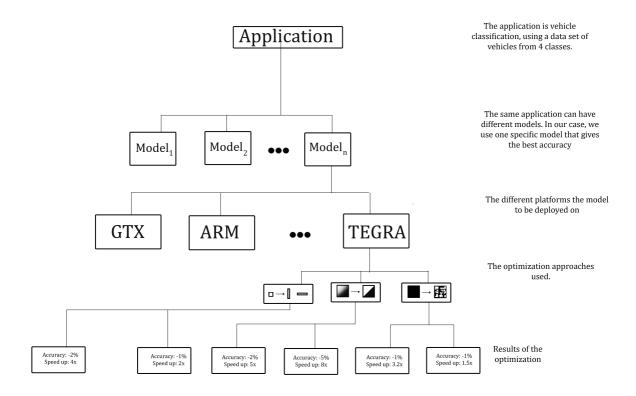

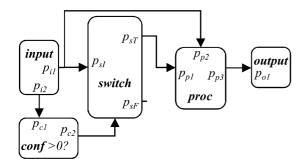

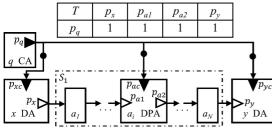

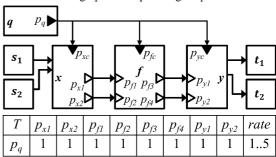

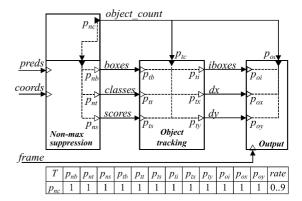

This section discusses the research methodology, including the tools used and implementations. The mfethods we discuss include binarization, separable convolution, pruning, and a method for automating the process abstraction to modelling. The languages used in our implementations are C, OpenCL, and CUDA. The platforms used include an Intel i7-7700K + NVIDIA GTX 1080, ARM Cortex-A72 + ARM Mali T860, and a Tegra X2 (NVIDIA Jetson). The main application use case is vehicle image classification using a private dataset because of industry relevance. We summarized these points in Figure 3.1. Additionally, we list the interconnection of the papers with various elements in the research in Table 3, where each column on the right represents the published paper in the year indicated in the column. The process starts with choosing an application, then a neural network solution that is best suited for the application is selected for further optimization. Depending on the deployment platform, the appropriate optimization approaches are chosen for testing and implementation while keeping into account factors such as memory requirements, performance and accuracy loss. Each step of the diagram is discussed in further detail in later sections.

| a) Method                    | 2018 | 2019 | 2019 | 2022 |

|------------------------------|------|------|------|------|

| Binarization                 | ×    | ×    | ×    |      |

| Separable Convolution        |      | ×    |      |      |

| Weight Pruning               |      | ×    | ×    |      |

| Packing                      | ×    | ×    | ×    |      |

| Popcount instruction         | ×    | ×    | ×    |      |

| Dataflow modelling + runtime |      |      |      | ×    |

| b) Languages                 |      |      |      |      |

|                              |      |      |      |      |

| С                                                                                                                                       |             |             | ×           | ×                |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|------------------|

| OpenCL/CUDA                                                                                                                             | ×           | ×           |             |                  |

| c) Platforms                                                                                                                            |             |             |             |                  |

| NVIDIA GTX                                                                                                                              | ×           | ×           |             |                  |

| NVIDIA Jetson                                                                                                                           | ×           |             |             |                  |

| XU3                                                                                                                                     |             |             |             | ×                |

| Mali                                                                                                                                    | ×           | ×           |             |                  |

| RISC-V (ETISS simulator)                                                                                                                |             |             | ×           |                  |

| ARM A53                                                                                                                                 |             |             | ×           |                  |

| i7                                                                                                                                      |             |             |             | ×                |

| d) Applications                                                                                                                         |             |             |             |                  |

| CNN based vehicle classification                                                                                                        | ×           | ×           | ×           | ×                |

| e) Datasets                                                                                                                             |             |             |             |                  |

|                                                                                                                                         |             |             |             |                  |

| Private data set                                                                                                                        | ×           | ×           | ×           | ×                |

| Private data set  f) Evaluation                                                                                                         | ×           | ×           | ×           | ×                |

|                                                                                                                                         | ×           | ×           | ×           | ×                |

| f) Evaluation                                                                                                                           |             |             |             | ×<br>×           |

| f) Evaluation Accuracy                                                                                                                  | ×           | ×           | ×           |                  |

| f) Evaluation  Accuracy Performance                                                                                                     | ×           | ×<br>×      | ×<br>×      | ×                |

| f) Evaluation  Accuracy Performance Memory                                                                                              | ×           | ×<br>×      | ×<br>×      | ×<br>×           |

| f) Evaluation  Accuracy Performance Memory Power                                                                                        | ×           | ×<br>×      | ×<br>×      | ×<br>×<br>×      |

| f) Evaluation  Accuracy Performance Memory Power Model complexity                                                                       | ×           | ×<br>×      | ×<br>×      | ×<br>×<br>×      |

| f) Evaluation  Accuracy Performance Memory Power Model complexity g) Author's Contributions                                             | ×<br>×<br>× | ×<br>×<br>× | ×<br>×<br>× | ×<br>×<br>×      |

| f) Evaluation  Accuracy Performance Memory Power Model complexity g) Author's Contributions Writing the paper                           | × × × ×     | ×<br>×<br>× | ×<br>×<br>× | ×<br>×<br>×<br>× |

| f) Evaluation  Accuracy Performance Memory Power Model complexity g) Author's Contributions Writing the paper Model design and training | × × × × ×   | ×<br>×<br>× | ×<br>×<br>× | ×<br>×<br>×<br>× |

**Table 3.1** A general outline of the elements of this work. The column date is associated with the paper published in that year.

| Platform | CPU             | GPU               | Memory      | Power |

|----------|-----------------|-------------------|-------------|-------|

| GTX      | Intel i7-7700K  | NVIDIA GTX 1080   | 32 GB DDR4  | 300 W |

| ARM      | ARM Cortex-A72  | ARM Mali T860     | 2 GB LPDDR4 | 15 W  |

| TEGRA    | NVIDIA Tegra X2 | NVIDIA Pascal GPU | 8 GB LPDDR4 | 15 W  |

**Table 3.2** Technical specifications of the three platforms.

Table 3.2 shows the three platforms used in this study, along with their abbreviated names, CPU, and GPU specifications. The Desktop platform (abbreviated as GTX) consists of an Intel i7-7700K CPU and an NVIDIA GTX 1080 GPU. The CPU has four physical cores and eight threads, with a base clock speed of 4.2 GHz and a maximum turbo frequency of 4.5 GHz. The GPU has 2560 CUDA cores and 8 GB of GDDR5 memory, with a base clock speed of 1607 MHz and a boost clock speed of 1733 MHz.

Thee embedded ARM system (abbreviated as ARM) is a low-power platform designed for use in mobile and embedded devices. It features an ARM Cortex-A72 CPU and an ARM Mali T860 GPU. The CPU has four cores, with a maximum clock speed of 2.5 GHz. The GPU has 16 shader cores and supports OpenGL ES 3.2, OpenCL 1.2, and Vulkan graphics APIs.

The embedded NVIDIA Jetson system (abbreviated as TEGRA) is another low-power platform designed for use in embedded devices. It features an NVIDIA Tegra X2 CPU and an NVIDIA Pascal GPU. The CPU has eight cores, with a maximum clock speed of 2.0 GHz. The GPU has 256 CUDA cores and 4 GB of LPDDR4 memory, with a base clock speed of 1302 MHz and a boost clock speed of 1455 MHz.

## 3.1 Application

The application chosen in this work is vehicle classification, and this area of application was chosen for various reasons such as the practical nature of the problem and as a continuation of on going research in the university in collaboration with industry. This particular application is highly industry relevant and is heavily utilized in com-

Figure 3.1 Visual outline of the research methodology

panies. A neural network solution is already proposed for the problem in [28], however, performance limitations led to further research for optimizing the solution for embedded devices [75]. We carry on and further optimize the problem. Generally, neural networks are known for being very redundant [29][9][21][64]. Many techniques exist in order to optimize various aspects of neural networks, and they can be categorized into several groups: pruning of parameters [23][23][15], quantization of weights [82][74][7], reduced precision weights [81][13][19][70], low-rank approximations [72][12][39][38], compact convolution kernels [46][80][57][25], and distillation [79][77][8][76][45].

The goal of such optimization approaches is to search for alternative solutions that preserve accuracy in a neural network while reducing utilization of resources such as memory and computation. In this work, we apply a selection of optimization methods, namely binarization, separable convolution, and pruning to this problem in present and analyze the results. Performance measurements are made on different

platforms, summarized below. Details are provided in later sections:

- Intel i7-7700K + NVIDIA GTX 1080

- ARM Cortex-A72 + ARM Mali T860

- Tegra X2 (NVIDIA Jetson)

Throughout the research, several standard datasets such as the MNIST and Cifar10 were used to verify the optimization approaches. Often, the papers that propose these methods have carried out their experiments on these standard datasets, allowing for direct comparison and verification of our implementation before applying it in other unexplored areas.

#### 3.2 Author's contributions

The contributions of this work includes implementing binarized convolutional neural networks and evaluating the performance on GPUs, empirical comparison of several optimization methods, including binarization, separable convolution, and pruning. Additionally, a dataflow model for automating the implementation of neural networks is presented.

Below is a detailed list of the roles of each of the authors in the publications, ordered by publication date, from oldest to recent.

- 1. Mir Khan came up with the idea for the research, planned and implemented all versions of the neural networks, ran the experiments and analyzed the results. Heikki Huttunen participated in the planing of the neural network and along with Jani Boutellier, reviewed the implementations and the results. While Mir Khan wrote the majority of the paper, Heikki Huttunen and Jani Boutellier also participated in writing, editing, and reviewing of the paper.

- 2. Mir Khan, Henri Lunnikivi, and Jani Boutellier came up with the idea for the research. Both Mir Khan and Henri Lunnikivi implemented the different versions of all the optimization approaches, ran the experiments, analyzed the results, and wrote most of the paper. Mir Khan's focus was on binarization and separable convolution, while Henri Lunnikivi focused on pruning and separable convolution. Heikki Huttunen and Jani Boutellier also participated in reviewing the results and editing and reviewing the manuscript.

- 3. Saman Payvar, Jani Boutellier, Rafael Stahl, and Daniel-Gritschender came up

with the idea for the research, and along with Mir Khan, were all involved in the development process. Saman Payvar ran most of the experiments and analyzed the results, while Mir Khan planned and implemented the binarized image classifier for the experiments and analyzed parts of the results. Majority of the paper was written by Saman Payvar, while Mir Khan, Jani Boutellier, Rafael Stahl, and Daniel-Gritschender were also heavily involved in writing, editing and reviewing the manuscript and reviewing of the results of the experiments.

4. Jani Boutellier came up with the idea for the research, and he, along with Yujunrong Ma, Jiahao Wu, and Mir Khan were involved in the development process. Mir Khan's focus was on integrating and interfacing with the neural networks, and planning and implementing the neural networks. Majority of the paper was written by Jani Boutellier, while Yujunrong Ma, Jiahao Wu, Mir Khan, and Shuvra S. Bhattacharyya were also involved in the writing, editing and reviewing of the manuscript.

#### 3.3 Neural network

We should emphasize that the focus of this research is not centered on finding neural network solutions for problems, but rather we take existing solution from other works, and then solve problems related to performance and deployment in resource-constrained environments such as mobile and embedded devices. The contributions of this works are mostly about extending neural network optimization approaches to specific application areas and neural network solutions. These contributions are highlighted in the next sections where our implementations are discussed in detail. Optimization approaches offer different benefits, for example, binarization can dramatically reduce the model's storage requirements depending on the choice of packing bitwidth, e.g., by up to 32X for a packing bitwidth of 32. On CPU platforms, where the model computes sequentially and assuming no parallelism, a similar speed up can be achieved. On GPU, the speed up is slightly lower due to parallelism. Binarization however results in the most reduction in accuracy. Pruning has the most significant impact on model size compression. Separable convolution offers a balance of benefits.

The results of paper [28] were reproduced and verified before any optimization

approaches were applied. The original network has 5 layers, starting with 2 convolutional layers, then followed by 2 dense layers. The convolutional layers use 5 × 5 filters, and each result in 32 featuremaps. The first dense layer receives the output of the final convolutional layer, and results in 100 outputs. The last layer before the final classification layer also results in 100 outputs. We perform the training in Tensorflow [2]. The weights are initialized according to [17]. We use ReLU [1] activations throughout the network and an RMSprop optmizer [24]. The experimental optimization approaches were first applied in Tensorflow and the accuracy results evaluated. Then the research goes to the next phase where the new version of the network is implemented in a number of different platforms using OpenCL and CUDA, and their execution time is evaluated on each platform.

# 3.4 Optimization Challenges

Convolution is a key operation and an important algorithm in image processing applications; the problem is that it is resource intensive and slow on CPUs. Although a large number of dedicated hardware exists for deep learning as presented in [5][67][6], many limitations are still present. The most commonly used approach for speeding up convolutions is to reduce the process into a matrix multiplication problem, which GPUs are optimized to handle. However, it is still very expensive to form the matrix that is then used for multiplication for computing the convolution.

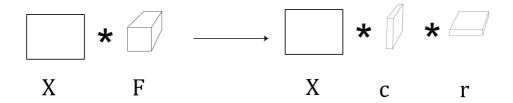

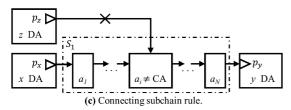

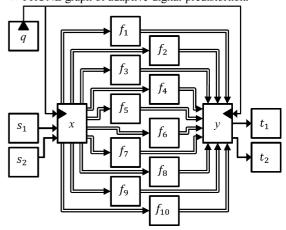

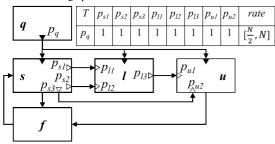

One approach to reduce the computation cost is using separable convolution or low-rank approximations, where each convolution operation is replaced by a combination of two smaller convolutions, resulting in a reduced total number of operations and memory requirements. More precisely, a  $k \times k$  convolution is replaced by a  $1 \times k$  convolution, followed by another  $k \times 1$  convolution. This approach is essentially expected to reconstruct the results of the full convolution through this cheaper process. Each smaller convolution has intermediate featuremaps that can be tuned for maximizing the balancing between performance and accuracy. This process is briefly illustrated in Figure 3.2.

Another variation of separable convolution exists called depthwise separable convolution and it's used heavily in MobileNet [25]. Instead of low rank separability, the separability is in the operations performed, where a regular convolution is re-

Figure 3.2 The principle of separable convolution, compared with regular convolution.

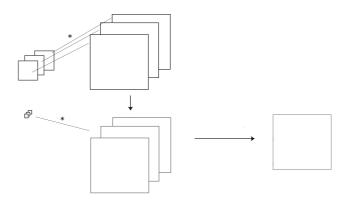

placed by a convolution applied separately per channel, followed by a 1x1 convolution, resulting in less computation. More precisely, a depthwise convolution of a  $b \times w \times c$  tensor with a  $k \times k$  kernel performs the convolution for each pixel with the  $k \times k$  kernel, but a separate set of  $1 \times 1 \times c$  kernels tensor is used to combine the channels and compute the featuremaps. This process is illustrated briefly in Figure 3.3, where an image with 3 channels is convolved with a set of filters with the same number of channels. However, the results (in blue, with the number of channels unchanged) are not combined as it is typically done in convolutions in neural networks. Instead, a separate set of filters with kernel size  $1 \times 1$  is convolved with the result and combined as usual. Then the result is shown in Green on the right.

Figure 3.3 Depthwise separable convolution, illustrated for one output featuremap.

Binarized neural networks is an approach where the weights and activations for intermediate computations are binarized to +1 and -1. For the MNIST data set a 7x speed up can be achieved [26]. Substantial speed up can be shown in CPU im-

plementation and evaluated on the ImageNet dataset by packing 1-bit weights into 32-bit words, enabling replacement of multiplication operations by logic XNORs. For a simple dot product this is shown as follows

$$\mathbf{a} \cdot \mathbf{b} = \mathbf{W} - 2 \times \text{popcount}(\text{xor}(A, B)),$$

(3.1)

In this research, we apply the binarized neural network approach and implement it for GPUs. At the time of this research, in this work, we obtained the first performance advantages offered by (Binarized convolutional neural networks) BCNN on GPUs. Additionally, we explored different approaches for the binarization of the first layer in the network, which is typically not binarized due to the increased reduction in accuracy. The approaches we explored include transforming the input using Local Binary Patterns (LBP) [51], thresholding on a grayscale input, and thresholding on a color input. Thresholding basically means that we choose a pixel value in the image, and all pixels above this value are set to 1, and the ones below it are set to 0. The results are presented and discussed in Section 4.

Pruning is a method for reducing the number of weights in a network in the fully-connected layers resulting in a sparse weights matrix, which allows the computation to be performed more efficiently using sparse matrix-vector multiplication. Pruning is a general approach where a criteria is used to eliminate weights with certain characteristics from the network by setting them to 0. In this work, the relevant approach to fix weights to 0 if they fall below the threshold  $T = \frac{max(W^l) + min(W^l)}{2}$ . This can result in a very large drop in the model's accuracy at this stage; however, by retraining the network for several epochs, the accuracy can largely be restored. Some implementations of this method incorporates L2 regularization in the initial training stage, which further increases the sparsity in the layers. The process is illustrated as pseudocode in Algorithm 1.

One of the advantages of this approach is the massive reduction in memory requirements. While there are no significant performance advantages on GPUs, there are techniques such as sparse matrix-vector multiplication that leverages the sparsity of the matrix to reduce the number of computations.

#### Algorithm 1 Fully-connected layer pruning procedure

```

1: for l in Layers do

for w in W^l do

2:

w \leftarrow \text{LoadPretrained}(w)

3:

4: for stage in Stages do

// Retrain with L2 regularization

5:

for epoch in Train Epochs do

6:

for l in Layers do

7:

for w in W^l do

8:

w \leftarrow \text{Update}(w, \eta, \frac{\partial \mathcal{L}(\mathbf{X})}{\partial \sigma_w})

9:

// Pruning stage

10:

for l in DenseLayers do

11:

T \leftarrow \frac{max(W^l) + min(W^l)}{min(W^l)}

12:

for w in W^l do

13:

if w < T then

14:

w \leftarrow 0

15:

// Fine-tune parameters

16:

for epoch in Tuning Epochs do

17:

18:

for l in Layers do

for w in NonZero(W^l) do

19:

w \leftarrow \text{Update}(w, \eta, \frac{\partial \mathcal{L}(\mathbf{X})}{\partial w})

20:

```

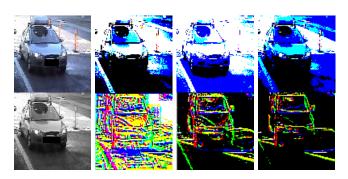

Figure 3.4 From left to right, a 'bus', 'normal car', 'truck', and a 'van'.

## 3.5 Dataset

The most commonly used dataset in this work is the private cars dataset obtained by a courtesy of a company working in this field. The data set has 6555 images. Each image is 96x96 32-bit color images around size of 108 KB. There are 4 categories of cars: bus, normal car, van, and truck, as illustrated in Fgure 3.4. The images have been taken by a camera in various weather and lighting conditions. The data is split into 80% for training, 10% for validation, and 10% for testing.

## 3.6 Implementation

In this section, we discuss the implementation stage of the research. After the neural network solution, target platforms, and the desired optimization approaches have been identified, the network is implemented in Tensorflow for training from scratch according to the specifications in the paper related to the network in question. Then this network is preserved for later verification before an optimized version of the network is implemented in Tensorflow and the accuracy is verified to be at least as good as with the first implementation. Once the correctness is verified, we proceed to implement the OpenCL/CUDA version.

After this step, a CUDA version is implemented. The implementation is verified again for correctness and then performance measurements are taken. This is done first on the desktop machine, and then later compiled and tested on the target platforms. If the target platform does not have a CUDA capable device, we reimplement the program in OpenCL. This process is very simple and can even be automated, as it mostly involves replacing terms in the kernel code from CUDA terms to OpenCL. While the host code is not as simple to translate, it is generic and involves little changes.

We also re-implement the original version of the network and the optimized version using vendor libraries, which claim to be optimized for the target platform. This is done in order to compare the performance of the vendor library implementation with our implementation, to insure that our implementation does not suffer from basic optimization issues. Additionally, we wish to know to full extent of performance benefits achieved from the neural network optimization approach applied.

These steps in the process be can summarized as follows:

- 1. The neural network is implemented in Tensorflow according to the specifications in the paper [28] and verified.

- 2. The network is reimplemented in Tensorflow with the optimization. Any parameters that are a part of the optimization approach are selected in this stage.

- 3. The new optimized version of the neural network is then implemented in OpenCL and CUDA in order to run on the target platforms. For performance comparison, we also implement this version of the network using vendor li-

braries such as ArmCL, cuDNN, and cuBLAS.

## 4 SUMMARY OF RESULTS

In this section, the results are summarized by optimization techniques.

### 4.1 Binarization

Table 4.1 shows the impact of input binarization on accuracy. It is typical in binarized neural networks to leave the first layer (the input layer) in full-precision, and binarize all subsequent layers. The last row in the table shows the accuracy of the network without any binarization. The rows 1 to 3 showcase different techniques of input binarization and how each method affects the accuracy. The 4th row is the result with only the first layer binarized.

Table 4.2 shows the speed-up achieved from binarization per layer on the GTX1080 platform. The speed-up expressed in the last row is relative to equivalent implementations with cuDNN. It should be noted that the equivalence is in terms of network accuracy performance, and not in terms of computation results, so in this case, even though the results from cuDNN and binarization may not match exactly, the final outputs of the neural network are largely similar as it pertains to classification accu-

Table 4.1 Impact of different input-binarization schemes on classification accuracy

| Method                 | Accuracy |

|------------------------|----------|

| LBP                    | 92.06%   |

| Thresholding Grayscale | 89.16%   |

| Thresholding RGB       | 92.52%   |

| No input binarization  | 94.20%   |

| Full-precision network | 97.09%   |

racy.

We can notice from Table 4.2 that the largest speed up is achieved in the final layer, where the layer is basically a matrix-vector multiplication. A speed-up of roughly  $32 \times$  is in-line with the results presented in the original binarized neural networks paper [26]. However, in the matrix-multiplication stage of convolution layers, the  $32 \times$  speed up was not achievable, mostly due to the overhead of packing the output of the preceding im2col3d matrix.

It is common to decompose convolutions on GPUs into two steps where the input is first rearranged (im2col) and then the convolution result is computed through a simple matrix-matrix multiplication. Im2Col3d in the first row refers to the 3d version of the im2col algorithm, rearranging an  $M \times N \times C$  matrix into  $P \times (M \times N)$  matrix, where  $P \in \mathbb{R}^{C \times K \times K}$ , for a kernal of size  $K \times K$ .

GEMM-convolution refers to General Matrix-matrix multiplication, which computes the final results of the convolution. The layer that follows is Max-Pooling, where a running window of size  $k \times k (k=2)$  in our case, moves throughout the image, and the maximum value in each window is retained while the other values are discarded. This reduces the dimensions of the image by k in each dimension. The final row represents the final layer in the network before the classification results are computed. This is simply a matrix-vector multiplication procedure.

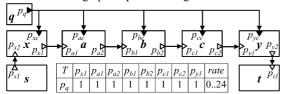

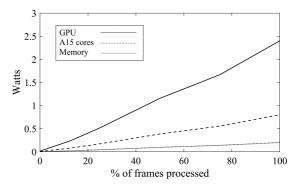

Table 4.3 shows the overall network speedup on 3 platforms, GTX1080, Mali T860 and the Tegra X2. We compare the execution time on each platform, implemented using the optimized vendor library and our implementation. cuDNN is the NVIDIA library for implementing neural networks. Arm CL is the vendor provided library for ARM platforms, and BCNN is our implementation. Additionally, we compare the performance with an additional step of optimization (binarized inputs) in the last row.

## 4.2 Separable Convolution

Table 4.4 compares the various advantages achieved through binarization, spearable convolution, and pruning, and how these methods compare with each other. The first two columns shows the implementations done with vendor libraries, which are expected to be optimal. The last two columns is our implementation. The GTX label refers to a desktop machine equipped with a GTX 1080 GPU, Mali refers to an

Table 4.2 Runtime per-layer (GTX1080), in the order of their execution

| Layer                                            | cuDNN          | Binarized    | Speed-up |

|--------------------------------------------------|----------------|--------------|----------|

| Im2col3d (96, 96, 3)                             | 21.63 μs       | 3.17μs       | 6.82×    |

| GEMM-convolution (32,5,5,3)                      | $37.54 \mu s$  | $8.61 \mu s$ | 4.36×    |

| Max-Pooling (96, 96, 32)                         | $5.22 \mu s$   | $8.26 \mu s$ | 0.63×    |

| Im2col3d (48,48,32)                              | $65.41 \mu s$  | $5.50 \mu s$ | 11.89×   |

| GEMM-convolution (32,5,5,32)                     | $69.28 \mu s$  | $8.10 \mu s$ | 8.55×    |

| Max-Pooling (48,48,32)                           | $5.38 \mu s$   | $2.66 \mu s$ | 2.02×    |

| Fully-Connected (100, $24 \times 24 \times 32$ ) | $200.03 \mu s$ | 6.28 µs      | 31.85×   |

Table 4.3 Runtime of the network on each platform

| Implementation Method      | GTX1080         | Mali T860       | Tegra X2        |

|----------------------------|-----------------|-----------------|-----------------|

| cuDNN (full-precision)     | $401.83 \mu s$  | $N/A^{\dagger}$ | 2.27 ms         |

| Arm CL (full-precision)    | $N/A^{\dagger}$ | 29.61 ms        | $N/A^{\dagger}$ |

| BCNN                       | $102.39 \mu s$  | 23.63 ms        | 0.53 ms         |

| BCNN with binarized inputs | <b>55.63</b> μs | 17.58 ms        | 0.41 ms         |

<sup>†</sup>Library not compatible with this platform.

embedded platform FireFly. The last 4 rows show the accuracy, memory requirements, number of multiplications, and number of additions for the whole network. It can be noted from the table that the biggest reduction in memory requirements is achieved with pruning, while the largest reduction in execution time is obtained through binarization.

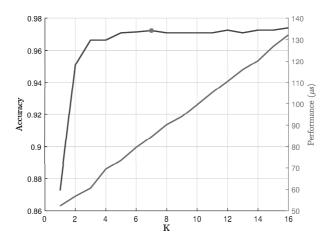

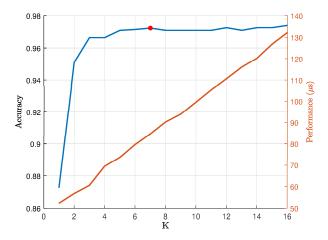

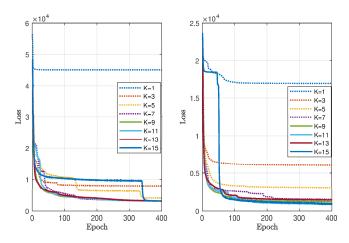

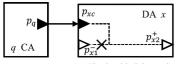

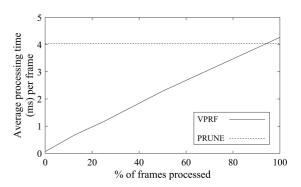

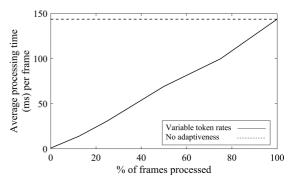

Figure 4.1 illustrates how the number of intermediate feature maps K in separable convolution affects the accuracy. The red dot corresponds to 7 intermediate featuremaps, which is our chosen value for the vehicle classifer implementation. This

Table 4.4 Results of optimization methods at inference

|                            | Baseline | Pruning | SepConv | BCNN    |

|----------------------------|----------|---------|---------|---------|

| GTX                        | 3.1 ms   | 0.7 ms  | 1.1 ms  | 0.06 ms |

| Mali                       | 120 ms   | 66 ms   | 80 ms   | 17.6 ms |

| Accuracy                   | 97.5%    | 95.5%   | 97.3%   | 94%     |

| Memory (KB)                | 7350     | 150     | 7254    | 230     |

| Muls (in 10 <sup>6</sup> ) | 82.95    | 81.53   | 18.30   | 0.43    |

| Adds (in 10 <sup>6</sup> ) | 86.12    | 84.35   | 20.37   | 0.43    |

value was chosen because it offers the best trade off between performance and accuracy. Even though a slightly higher accuracy can be achieved later at around K=12 as it appears in the graph, it comes at an increased cost in performance is clearly visible from the graph.

We also illustrate in Figure 4.2 how the loss in the neural network is affected by changing K. We can clearly see that higher values of K yields better accuracy performance, but this advantage diminishes at values close to K=9 at the bottom of the graph.

## 4.3 Pruning

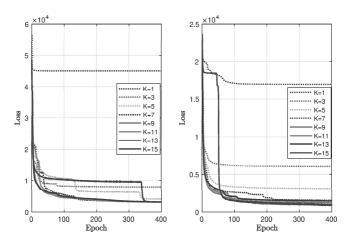

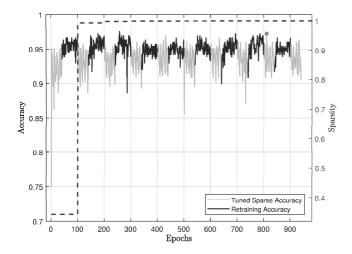

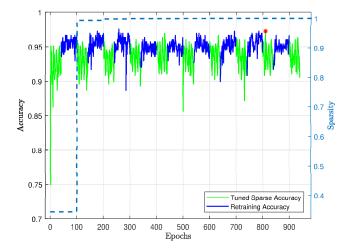

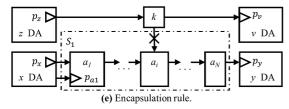

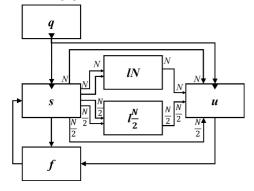

Figure 4.3 illustrates the process of pruning and how it impacts accuracy throughout the training and retraining phases. The level of sparsity throughout this process is also shown as dashed lines, with the range corresponding to the right vertical axis. The accuracy of the network starts to vacillate within a bigger range; however, an accuracy of 97% can be achieved at nearly 99% sparsity.

The green plot shows the fine-tuning stage, where the pruned weights are not up-

**Figure 4.1** Performance/accuracy trade-off for different values of K.

**Figure 4.2** Loss for convolutional layers 1 (left) and 2 (right) shown for different values of K.

dated and held at 0. The blue plot marks the stage where all the weights are updated and the previously pruned weights in the previous step are restored and re-updated. We report the accuracy on the validation set in Figure 4.3.

## 4.4 Conclusion of Results

Our results show that these optimization methods offer many benefits. The optimization method needs to be chosen depending on the optimization objective. For example, separable convolution can offer minor reduction in model size, and a mod-

Figure 4.3 Accuracy of the network on the validation set at retraining stages and fine-tuning stages.

est improvement in performance, and pruning can dramatically reduce the model size. While this reduces the number of operations and can offer benefits on CPUs, it is difficult to leverage this on GPUs without using specialized techniques of sparse matrix-multiplication, which have an overhead of processing the matrix. Binarization can both reduce the model size and improve the performance. The loss in accuracy is another thing to keep in mind when choosing an optimization method. For example, binarization can result in a large reduction in accuracy in some applications, but in other applications like the MNIST dataset where the images are black and white and the features are clear, the reduction in accuracy is very small, making binarization very suitable for this particular application.

We restate the three research questions:

RQ1: What is the accuracy and performance trade-off from weight binarization, separable convolution, and weights pruning, and how they compare.

RQ2: How well the optimizations work in real-time embedded systems?

RQ3: How to speed up the process of design and deployment of neural network models?

The dissertation has successfully answered the three research questions posed in the study. Firstly, regarding RQ1, the research examined the accuracy and performance trade-off resulting from weight binarization, separable convolution, and weight pruning techniques. The study employed a comprehensive evaluation framework to compare the three optimization techniques and determine their effective-

ness. The results indicated that weight binarization and separable convolution were more effective in reducing the model size while maintaining accuracy, whereas weight pruning offered better memory cost reduction. Secondly, the dissertation addressed RQ2 by evaluating the effectiveness of the optimization techniques in real-time embedded systems. The research employed a benchmarking methodology that assessed the performance of the models in various real-time scenarios. The results showed that the optimized models outperformed their non-optimized counterparts and could even achieve real-time performance on resource-constrained embedded devices. Lastly, RQ3 was answered by proposing a novel methodology that speeds up the process of designing and deploying neural network models. The methodology involved the use of automated tools that streamlined the optimization process, reducing the time and effort required for model design and deployment. The study demonstrated the effectiveness of the proposed methodology by evaluating its performance in several benchmark datasets and comparing it to existing approaches.

## 5 RELATED WORK

This work is mainly concerned with vehicle classification using neural networks and optimizing them for real-time inference. Many works show that neural networks are excellent at image classification applications [68][56][50][43][11], object recognition [37][59][68][73][41], and object detection [52][14][44].

Binarized neural networks is a method of optimizing neural networks for inference by reducing their size and number of computations. Some of the earliest works in BNNs were introduced in [35] [26] and their performance was demonstrated on the MNIST dataset on GPUs, and later it was extended [10] to the training phase of the neural network. The work in [54] demonstrated the performance advantages of the method on CPUs, which can result in up to  $32 \times \text{model}$  size reduction and speed up. This work extended binarized neural networks to convolutional neural networks and was the first to demonstrate the performance of binarized convolutional neural networks on GPUs in the use case of vehicle classification.

Separable convolution is a technique for reducing the model size and computation in a neural network by replacing convolutions with two separable convolutions [30]. A similar technique later appeared [25] [57] with a slightly modified approach that results in less computation, and is heavily used in MobileNet and its variants. This work demonstrated it works for detailed image classification applications such as vehicle classification.

Another approach for optimizing neural network inference is pruning, where a proportion of the parameters in the network are removed. The method reduces the parameters at very little loss of accuracy, and can have some minor performance advantages using sparse matrix-vector multiplication algorithms. These approaches largely have benefits in model size reduction. While any variations of this approach exist, the main difference is in the pruning criteria. Earlier pruning techniques simply removed weights that are low in magnitude, but more sophisticated approaches evolved later. A method was discussed in [40] where the second derivative of the loss

function used as the pruning criteria, their results show a reduction of model size by up to 4 times, with a slight increase in accuracy speed. More techniques emerged where the pruning criteria is closely connected with the loss function [32], and some approaches focused on pruning by removing individual neurons rather than the individual connections [65], or combining several different methods [20] for achieving better pruning results. Our results show that in the use case of vehicle classification, this method can offer great benefit in reducing the model size with low loss in accuracy; however, this does not translate to significantly reduced computation time on GPUs.

## 6 CONCLUSION

We presented our optimized implementations of a neural network for vehicle classification. Multiple optimization approaches have been evaluated on multiple platforms, and their impact on performance, and model size have been analyzed thoroughly. Our work shows that the best performance can be achieved through binarization, albeit at a greater loss in accuracy. However, in real-time applications, it could be more beneficial to classify multiple images over a period of time with low accuracy per classification, than classifying less images with higher classification accuracy. These optimization approaches are able to bring performance of such neural networks closer to real-time, making them suitable for such applications. A dataflow model has also been introduced for simplifying the process of implementing the neural network, paving the way for applying such optimizations automatically in the future.

In future work, we aim to expand on the generality of our results by testing our optimization approaches on a larger set of datasets and neural network architectures. This will allow us to assess the scalability of our approaches and identify any limitations in their applicability. Moreover, we plan to shift our focus towards automated optimizations, which could significantly reduce the time and effort required to optimize neural networks manually. To this end, we intend to explore high-level abstraction models and tools that can automate the optimization process based on user-defined constraints and objectives. This will enable us to efficiently explore the optimization space and identify the best optimization approaches for a given neural network and platform combination.

# **REFERENCES**

- [1] A. F. Agarap. Deep learning using rectified linear units (relu). *arXiv preprint* arXiv:1803.08375 (2018).

- [2] E. Allaire. *TensorFlow*. 2016.

- [3] F. Amato, A. López, E. M. Peña-Méndez, P. Vaňhara, A. Hampl and J. Havel. *Artificial neural networks in medical diagnosis*. 2013.

- [4] J. Boutellier, Y. Ma, J. Wu, M. Khan and S. S. Bhattacharyya. VR-PRUNE: Decidable Variable-Rate Dataflow for Signal Processing Systems. *IEEE TRANS-ACTIONS ON SIGNAL PROCESSING, VOL. 70*, 2022 (2022).

- [5] Y.-H. Chen, T. Krishna, J. S. Emer and V. Sze. Eyeriss: An Energy-Efficient Reconfigurable Accelerator for Deep Convolutional Neural Networks. *IEEE Journal of Solid-State Circuits* 52.1 (2017), 127–138. DOI: 10.1109/JSSC. 2016.2616357.

- [6] Y.-H. Chen, T.-J. Yang, J. Emer and V. Sze. Eyeriss v2: A flexible accelerator for emerging deep neural networks on mobile devices. *IEEE Journal on Emerging and Selected Topics in Circuits and Systems* 9.2 (2019), 292–308.

- [7] S. Chen, W. Wang and S. J. Pan. Metaquant: Learning to quantize by learning to penetrate non-differentiable quantization. *Advances in Neural Information Processing Systems* 32 (2019).

- [8] Y. Chen, N. Wang and Z. Zhang. Darkrank: Accelerating deep metric learning via cross sample similarities transfer. *Proceedings of the AAAI conference on artificial intelligence*. Vol. 32. 1. 2018.

- [9] Y. Cheng, F. X. Yu, R. S. Feris, S. Kumar, A. Choudhary and S.-F. Chang. An exploration of parameter redundancy in deep networks with circulant projections. *Proceedings of the IEEE international conference on computer vision*. 2015, 2857–2865.

- [10] M. Courbariaux, I. Hubara, D. Soudry, R. El-Yaniv and Y. Bengio. Binarized neural networks: Training deep neural networks with weights and activations constrained to+1 or-1. *arXiv* preprint arXiv:1602.02830 (2016).

- [11] C. Deng, X. Liu, C. Li and D. Tao. Active multi-kernel domain adaptation for hyperspectral image classification. *Pattern Recognition* 77 (2018), 306–315.

- [12] E. L. Denton, W. Zaremba, J. Bruna, Y. LeCun and R. Fergus. Exploiting linear structure within convolutional networks for efficient evaluation. *Advances in neural information processing systems* 27 (2014).

- [13] S. Ge. Efficient deep learning in network compression and acceleration. *Digital Systems*. IntechOpen London, UK, 2018.

- [14] S. Ge, J. Li, Q. Ye and Z. Luo. Detecting masked faces in the wild with lle-cnns. *Proceedings of the IEEE conference on computer vision and pattern recognition*. 2017, 2682–2690.

- [15] S. Ge, Z. Luo, S. Zhao, X. Jin and X.-Y. Zhang. Compressing deep neural networks for efficient visual inference. 2017 ieee international conference on multimedia and expo (icme). IEEE. 2017, 667–672.

- [16] M. Ghifary, W. B. Kleijn and M. Zhang. Domain adaptive neural networks for object recognition. *Pacific Rim international conference on artificial intelligence*. Springer. 2014, 898–904.

- [17] X. Glorot and Y. Bengio. Understanding the difficulty of training deep feedforward neural networks. *Proceedings of the thirteenth international conference* on artificial intelligence and statistics. JMLR Workshop and Conference Proceedings. 2010, 249–256.

- [18] A. Graves and N. Jaitly. Towards end-to-end speech recognition with recurrent neural networks. *International conference on machine learning*. PMLR. 2014, 1764–1772.

- [19] S. Gupta, A. Agrawal, K. Gopalakrishnan and P. Narayanan. Deep learning with limited numerical precision. *International conference on machine learning*. PMLR. 2015, 1737–1746.

- [20] S. Han, H. Mao and W. J. Dally. Deep compression: Compressing deep neural networks with pruning, trained quantization and huffman coding. *arXiv* preprint arXiv:1510.00149 (2015).

- [21] S. Han, J. Pool, J. Tran and W. Dally. Learning both weights and connections for efficient neural network. *Advances in neural information processing systems* 28 (2015).

- [22] T. He, Z. Zhang, H. Zhang, Z. Zhang, J. Xie and M. Li. Bag of tricks for image classification with convolutional neural networks. *Proceedings of the IEEE/CVF Conference on Computer Vision and Pattern Recognition*. 2019, 558–567.

- [23] Y. He, X. Zhang and J. Sun. Channel pruning for accelerating very deep neural networks. *Proceedings of the IEEE international conference on computer vision*. 2017, 1389–1397.

- [24] Hinton. Divide the gradient by a running average of its recent magnitude. *Lecture 6.5-rmsprop:*. *COURSERA: Neural networks for machine learning*. COURSERA. 2012.

- [25] A. G. Howard, M. Zhu, B. Chen, D. Kalenichenko, W. Wang, T. Weyand, M. Andreetto and H. Adam. Mobilenets: Efficient convolutional neural networks for mobile vision applications. *arXiv* preprint arXiv:1704.04861 (2017).

- [26] I. Hubara, M. Courbariaux, D. Soudry, R. El-Yaniv and Y. Bengio. Binarized neural networks. *Advances in neural information processing systems* 29 (2016).

- [27] E. Hunt. Perceptrons. 1971.

- [28] H. Huttunen, F. S. Yancheshmeh and K. Chen. Car type recognition with deep neural networks. 2016 IEEE intelligent vehicles symposium (IV). IEEE. 2016, 1115–1120.

- [29] Y. Izui and A. Pentland. Analysis of Neural Networks with Redundancy. *Neural Computation* 2.2 (1990), 226–238. DOI: 10.1162/neco.1990.2.2.226.

- [30] M. Jaderberg, A. Vedaldi and A. Zisserman. Speeding up convolutional neural networks with low rank expansions. *arXiv preprint arXiv:1405.3866* (2014).

- [31] N. Jmour, S. Zayen and A. Abdelkrim. Convolutional neural networks for image classification. 2018 international conference on advanced systems and electric technologies (IC\_ASET). IEEE. 2018, 397–402.

- [32] E. Karnin. A simple procedure for pruning back-propagation trained neural networks. *IEEE Transactions on Neural Networks* 1.2 (1990), 239–242. DOI: 10.1109/72.80236.

- [33] M. Khan, H. Huttunen and J. Boutellier. Binarized Convolutional Neural Networks for Efficient Inference on GPUs. *EUSIPCO2018* (2018).

- [34] M. Khan, H. Lunnikivi, H. Huttunen and J. Boutellier. Comparing Optimization Methods of Neural Networks for Real-time Inference. *EUSPICO2019* (2019).

- [35] M. Kim and P. Smaragdis. Bitwise neural networks. *arXiv preprint arXiv:1601.06071* (2016).

- [36] H. Kordylewski, D. Graupe and K. Liu. A novel large-memory neural network as an aid in medical diagnosis applications. *IEEE Transactions on Information Technology in Biomedicine* 5.3 (2001), 202–209.

- [37] A. Krizhevsky, I. Sutskever and G. E. Hinton. Imagenet classification with deep convolutional neural networks. *Communications of the ACM* 60.6 (2017), 84–90.

- [38] V. Lebedev, Y. Ganin, M. Rakhuba, I. Oseledets and V. Lempitsky. Speeding-up convolutional neural networks using fine-tuned cp-decomposition. *arXiv* preprint arXiv:1412.6553 (2014).

- [39] V. Lebedev and V. Lempitsky. Fast convnets using group-wise brain damage. Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition. 2016, 2554–2564.

- [40] Y. LeCun, J. Denker and S. Solla. Optimal brain damage. *Advances in neural information processing systems* 2 (1989).

- [41] J. Li, X. Liu, M. Zhang and D. Wang. Spatio-temporal deformable 3d convnets with attention for action recognition. *Pattern Recognition* 98 (2020), 107037.

- [42] M. Liang and X. Hu. Recurrent convolutional neural network for object recognition. *Proceedings of the IEEE conference on computer vision and pattern recognition*. 2015, 3367–3375.

- [43] L. Liu, P. Fieguth, Y. Guo, X. Wang and M. Pietikäinen. Local binary features for texture classification: Taxonomy and experimental study. *Pattern Recognition* 62 (2017), 135–160.

- [44] A. T. Lopes, E. De Aguiar, A. F. De Souza and T. Oliveira-Santos. Facial expression recognition with convolutional neural networks: coping with few data and the training sample order. *Pattern recognition* 61 (2017), 610–628.

- [45] Y. Luo, A. Chen, K. Yan and L. Tian. Distilling self-knowledge from contrastive links to classify graph nodes without passing messages. *arXiv* preprint arXiv:2106.08541 (2021).

- [46] N. Ma, X. Zhang, H.-T. Zheng and J. Sun. Shufflenet v2: Practical guidelines for efficient cnn architecture design. *Proceedings of the European conference on computer vision (ECCV)*. 2018, 116–131.

- [47] G. Marques, D. Agarwal and I. de la Torre Diez. Automated medical diagnosis of COVID-19 through EfficientNet convolutional neural network. *Applied soft computing* 96 (2020), 106691.

- [48] S. Moein. Medical diagnosis using artificial neural networks. IGI global, 2014.

- [49] D. J. Montana, L. Davis et al. Training feedforward neural networks using genetic algorithms. *IJCAI*. Vol. 89. 1989, 762–767.

- [50] K. Nogueira, O. A. Penatti and J. A. Dos Santos. Towards better exploiting convolutional neural networks for remote sensing scene classification. *Pattern Recognition* 61 (2017), 539–556.

- [51] T. Ojala, M. Pietikäinen and D. Harwood. A comparative study of texture measures with classification based on featured distributions. *Pattern recognition* 29.1 (1996), 51–59.

- [52] J. Pang, K. Chen, J. Shi, H. Feng, W. Ouyang and D. Lin. Libra r-cnn: Towards balanced learning for object detection. *Proceedings of the IEEE/CVF conference on computer vision and pattern recognition*. 2019, 821–830.

- [53] S. Payvar, M. Khan, R. Stahland, D. Mueller-Gritschnederand and J. Boutellier. Neural Network-based Vehicle Image Classification for IoT Devices. *IEE International Workshop on Signal Processing Systems* (2019).

- [54] M. Rastegari, V. Ordonez, J. Redmon and A. Farhadi. Xnor-net: Imagenet classification using binary convolutional neural networks. *European conference on computer vision*. Springer. 2016, 525–542.

- [55] W. Rawat and Z. Wang. Deep convolutional neural networks for image classification: A comprehensive review. *Neural computation* 29.9 (2017), 2352–2449.

- [56] S. Ren, K. He, R. Girshick and J. Sun. Faster r-cnn: Towards real-time object detection with region proposal networks. *Advances in neural information processing systems* 28 (2015).

- [57] M. Sandler, A. Howard, M. Zhu, A. Zhmoginov and L.-C. Chen. Mobilenetv2: Inverted residuals and linear bottlenecks. *Proceedings of the IEEE conference on computer vision and pattern recognition*. 2018, 4510–4520.

- [58] N. Sharma, V. Jain and A. Mishra. An analysis of convolutional neural networks for image classification. *Procedia computer science* 132 (2018), 377–384.

- [59] K. Simonyan and A. Zisserman. Very deep convolutional networks for large-scale image recognition. *arXiv preprint arXiv:1409.1556* (2014).

- [60] K. Sims. Evolving virtual creatures. *Proceedings of the 21st annual conference on Computer graphics and interactive techniques.* 1994, 15–22.

- [61] R. D. Singh, A. Mittal and R. K. Bhatia. 3D convolutional neural network for object recognition: a review. *Multimedia Tools and Applications* 78.12 (2019), 15951–15995.

- [62] H. F. Song, G. R. Yang and X.-J. Wang. Reward-based training of recurrent neural networks for cognitive and value-based tasks. *Elife* 6 (2017), e21492.

- [63] C. J. Spoerer, P. McClure and N. Kriegeskorte. Recurrent convolutional neural networks: a better model of biological object recognition. *Frontiers in psychology* 8 (2017), 1551.

- [64] S. Srinivas and R. V. Babu. Data-free parameter pruning for deep neural networks. *arXiv preprint arXiv:1507.06149* (2015).

- [65] S. Srinivas and R. V. Babu. Data-free parameter pruning for Deep Neural Networks. *CoRR* abs/1507.06149 (2015). arXiv: 1507.06149. URL: http://arxiv.org/abs/1507.06149.

- [66] B. Šter and A. Dobnikar. Neural networks in medical diagnosis: Comparison with other methods. *International conference on engineering applications of neural networks*. 1996, 427–30.

- [67] V. Sze, Y.-H. Chen, J. Emer, A. Suleiman and Z. Zhang. Hardware for machine learning: Challenges and opportunities. 2017 IEEE Custom Integrated Circuits Conference (CICC). IEEE. 2017, 1–8.

- [68] C. Szegedy, W. Liu, Y. Jia, P. Sermanet, S. Reed, D. Anguelov, D. Erhan, V. Vanhoucke and A. Rabinovich. Going deeper with convolutions. *Proceedings of the IEEE conference on computer vision and pattern recognition*. 2015, 1–9.

- [69] J. M. Tebelskis. *Speech recognition using neural networks*. Carnegie Mellon University, 1995.

- [70] V. Vanhoucke, A. Senior and M. Z. Mao. Improving the speed of neural networks on CPUs. (2011).

- [71] A. Waibel. Modular construction of time-delay neural networks for speech recognition. *Neural computation* 1.1 (1989), 39–46.

- [72] J. Wen, B. Zhang, Y. Xu, J. Yang and N. Han. Adaptive weighted nonnegative low-rank representation. *Pattern Recognition* 81 (2018), 326–340.

- [73] L. Wu, Y. Wang, J. Gao and X. Li. Deep adaptive feature embedding with local sample distributions for person re-identification. *Pattern Recognition* 73 (2018), 275–288.

- [74] Y. Wu, Y. Wu, R. Gong, Y. Lv, K. Chen, D. Liang, X. Hu, X. Liu and J. Yan. Rotation consistent margin loss for efficient low-bit face recognition. *Proceedings of the IEEE/CVF Conference on Computer Vision and Pattern Recognition*. 2020, 6866–6876.

- [75] R. Xie, H. Huttunen, S. Lin, S. S. Bhattacharyya and J. Takala. Resource-constrained implementation and optimization of a deep neural network for vehicle classification. 2016 24th European Signal Processing Conference (EUSIPCO). IEEE. 2016, 1862–1866.

- [76] Z. Xu, Y.-C. Hsu and J. Huang. Training shallow and thin networks for acceleration via knowledge distillation with conditional adversarial networks. *arXiv preprint arXiv:1709.00513* (2017).