Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

12-1997

# Microprogramming a Writeable Control Memory using Very Long Instruction Word (VLIW) Compilation Techniques

Randall S. Whitman

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Whitman, Randall S., "Microprogramming a Writeable Control Memory using Very Long Instruction Word (VLIW) Compilation Techniques" (1997). *Theses and Dissertations*. 5785. https://scholar.afit.edu/etd/5785

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

### AFIT/ENG/GCS/97D-19

Microprogramming a Writeable Control Memory using Very Long Instruction Word (VLIW) Compilation Techniques

> THESIS Randall S. Whitman Capt, USAF

AFIT/ENG/GCS/97D-19

# 19980127 076

DTIC QUALITY INSPECTED 5

Approved for public release; distribution unlimited

The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the United States Government.

AFIT/ENG/GCS/97D-19

# Microprogramming a Writeable Control Memory using Very Long Instruction Word (VLIW) Compilation Techniques

#### THESIS

Presented to the Faculty of the School of Engineering of the Air Force Institute of Technology Air University In Partial Fulfillment of the Requirements for the Degree of Master of Science

> Randall S. Whitman, B.S. Capt, USAF

> > December, 1997

Approved for public release; distribution unlimited

## Microprogramming a Writeable Control Memory

using

Very Long Instruction Word (VLIW) Compilation Techniques

Randall S. Whitman, B.S.

Capt, USAF

Approved:

the

25 NOV 97

Lt Col David M. Gallagher Thesis Advisor

25 Nov 97

Maj Mark A. Kanko Committee Member

uha Ĺл

Maj Richard A. Raines Committee Member

Date

Date

25Nov97

Date

#### Acknowledgements

I would like to thank my wonderful wife Susan for her loving support and continued hard work during this thesis effort. Her patience, cheerfulness, and love provided the strength and encouragement I needed to pursue this research. My children, Bethany, Randy Jr., Amy, Emily, Elizabeth, and William have been a wonderful blessing during these past 18 months. Their love and never-ending hugs and kisses will never be forgotten.

I would also like to my thesis advisor, Lt Col David Gallagher, for his help and guidance provided from the beginning. He has taught me much in the area of computer architectures and the process of performing difficult research for what appeared to be an overwhelming effort. I would also like to thank my committee members, Major Richard Raines and Maj Mark Kanko, for their assistance in making this thesis a reality.

I would most importantly like to thank the Lord Jesus Christ for the uncountable times He has picked me up from moments of discouragement. His faithfulness to my family and I remains a cherished cornerstone of support. The success of this thesis is surely a mark of His committeent to those He loves. He is ever faithful!

Randall S. Whitman

# Table of Contents

|                                                                                                  | Page |

|--------------------------------------------------------------------------------------------------|------|

| Acknowledgements                                                                                 | iii  |

| List of Figures                                                                                  | viii |

| List of Tables                                                                                   | ix   |

| Abstract                                                                                         | x    |

| I. Introduction                                                                                  | 1-1  |

| 1.1 Background                                                                                   | 1-1  |

| 1.2 Problem Statement                                                                            | 1-2  |

| 1.3 Scope                                                                                        | 1-2  |

| 1.4 Summary of Current Knowledge                                                                 | 1-2  |

| 1.5 Assumptions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 1-3  |

| 1.6 Approach                                                                                     | 1-3  |

| 1.7 Design Environment                                                                           | 1-3  |

| 1.8 Organization of Thesis                                                                       | 1-3  |

| II. Background                                                                                   | 2-1  |

| 2.1 Introduction $\ldots$                                                                        | 2-1  |

| 2.2 Microprogramming                                                                             | 2-1  |

| 2.2.1 Physical Layout                                                                            | 2-1  |

| 2.2.2 Control Memory                                                                             | 2-2  |

| 2.3 Exploiting the WCM: Past Efforts                                                             | 2-3  |

| 2.3.1 Methods of Loading the WCM                                                                 | 2-3  |

| 2.3.2 WCM Code Compilation                                                                       | 2-4  |

| 2.4 Code Optimizations                                                                           | 2-4  |

|             |          |                                                       | Page |

|-------------|----------|-------------------------------------------------------|------|

|             | 2.4.1    | Compaction                                            | 2-4  |

|             | 2.4.2    | Trace Scheduling                                      | 2-5  |

| 2.5         | VLIW 7   | Techniques                                            | 2-5  |

| 2.6         | The Wa   | fer Scale Signal Processor                            | 2-7  |

|             | 2.6.1    | Integer Datapaths and Control Core                    | 2-7  |

|             | 2.6.2    | Floating Point Units                                  | 2-7  |

| 2.7         | Conclus  | sion                                                  | 2-7  |

| III. Method | lology . |                                                       | 3-1  |

| 3.1         | Introdu  | ction                                                 | 3-1  |

| 3.2         | Program  | nmable Loops                                          | 3-1  |

| 3.3         | Microco  | de Execution Time Requirements                        | 3-2  |

|             | 3.3.1    | Integer ALU and Non-Pipelined Instructions $\ldots$ . | 3-3  |

|             | 3.3.2    | Pipelined Instructions                                | 3-5  |

|             | 3.3.3    | Branches                                              | 3-7  |

|             | 3.3.4    | Loads and Stores                                      | 3-8  |

| 3.4         | Instruct | ion Mix Summary                                       | 3-10 |

| 3.5         | Method   | s to Load the WCM                                     | 3-12 |

| 3.6         | The VH   | DL Simulator                                          | 3-13 |

| 3.7         | The Im   | pact Compiler                                         | 3-13 |

|             | 3.7.1    | Impact Code Generators                                | 3-13 |

| 3.8         | Dual Ta  | arget Code Generator for Microcoding                  | 3-15 |

|             | 3.8.1    | Phase 1 Modifications                                 | 3-15 |

|             | 3.8.2    | Phase 2 Modifications                                 | 3-16 |

|             | 3.8.3    | Phase 3 Modifications                                 | 3-17 |

| 3.9         | Conclus  | ion                                                   | 3-19 |

|     |         |                                            | Page |

|-----|---------|--------------------------------------------|------|

| IV. | Impact  | and the WSSP Code Generator: A Closer Look | 4-1  |

|     | 4.1     | Introduction                               | 4-1  |

|     | 4.2     | Overall Design Decisions                   | 4-2  |

|     | 4.3     | Overall Code Generator Process             | 4-4  |

|     | 4.4     | Phase 1                                    | 4-4  |

|     |         | 4.4.1 Set Fpmode                           | 4-4  |

|     |         | 4.4.2 Insert Preheader and Remove Labels   | 4-5  |

|     |         | 4.4.3 Annotate Instructions                | 4-6  |

|     |         | 4.4.4 Phase 1 Conclusion                   | 4-7  |

|     | 4.5     | Phase 2                                    | 4-7  |

|     |         | 4.5.1 Machine Description Files            | 4-7  |

|     |         | 4.5.2 Prepass Code Scheduling              | 4-10 |

|     |         | 4.5.3 Register Allocation                  | 4-10 |

|     |         | 4.5.4 Annotating Instructions              | 4-11 |

|     |         | 4.5.5 Postpass Scheduling                  | 4-13 |

|     | 4.6     | Phase 3                                    | 4-13 |

|     |         | 4.6.1 The WSSP Microinstruction Format     | 4-13 |

|     |         | 4.6.2 Microinstruction Data Structures     | 4-14 |

|     |         | 4.6.3 Create Entry and Exit Instructions   | 4-15 |

|     |         | 4.6.4 Create Microinstructions             | 4-17 |

|     |         | 4.6.5 Handle Branch Instructions           | 4-18 |

|     |         | 4.6.6 Print Microinstructions              | 4-18 |

|     |         | 4.6.7 Print Micro Call Instructions        | 4-19 |

|     | 4.7     | Conclusion                                 | 4-20 |

| v.  | Analysi | s and Conclusions                          | 5-1  |

|     | 5.1     | Introduction                               | 5-1  |

|     | 5.2     | The Benchmarks                             | 5-1  |

•

|                |         |                                                                                                                                 | Page   |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------|--------|

| 5.3            | Benchm  | arks Analysis and Conclusions                                                                                                   | 5-6    |

| 5.4            | Contrib | $utions \ldots \ldots$ | 5-7    |

|                | 5.4.1   | Dual-Target Compilation                                                                                                         | 5-7    |

|                | 5.4.2   | A Microcode Compiler for the WSSP                                                                                               | 5-7    |

| 5.5            | Recomm  | nendations and Future Work                                                                                                      | 5-7    |

|                | 5.5.1   | Minimize Microcode Preloading                                                                                                   | 5-7    |

|                | 5.5.2   | Marking the Microcode Control Blocks                                                                                            | 5-7    |

|                | 5.5.3   | Maximizing the Combining of Microinstructions                                                                                   | 5-8    |

|                | 5.5.4   | Use of Special Purpose Hardware                                                                                                 | 5-8    |

|                | 5.5.5   | WSSP Vector Instructions                                                                                                        | 5-8    |

|                | 5.5.6   | Microcode Branching                                                                                                             | 5-8    |

| 5.6            | Closing | Remarks                                                                                                                         | 5-9    |

| Bibliography . |         |                                                                                                                                 | BIB-1  |

| Vita           |         |                                                                                                                                 | VITA-1 |

N

## List of Figures

| Figure |                                    | Page |

|--------|------------------------------------|------|

| 3.1.   | Handling Branches in Microcode     | 3-9  |

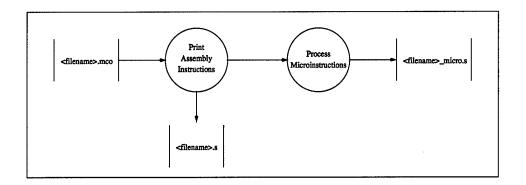

| 3.2.   | Code Generation Instruction Flow   | 3-14 |

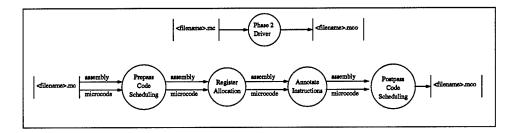

| 3.3.   | Phase 3 Process Overview           | 3-18 |

| 4.1.   | Code Generation Instruction Flow   | 4-1  |

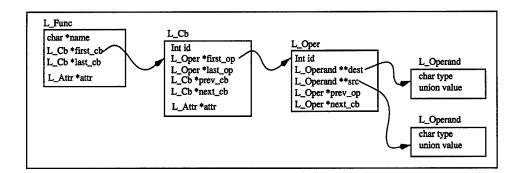

| 4.2.   | Lcode Data Structures              | 4-3  |

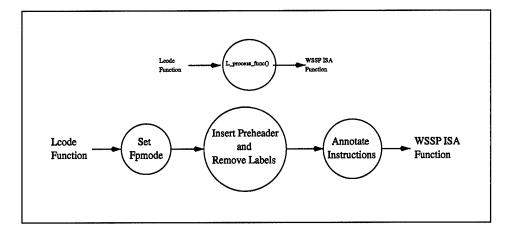

| 4.3.   | Phase 1 Main Processes             | 4-5  |

| 4.4.   | Preheader and Label Removal Result | 4-6  |

| 4.5.   | Phase 2 Main Processes             | 4-8  |

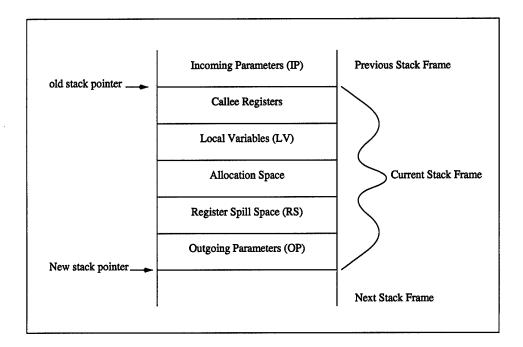

| 4.6.   | WSSP Phase 2 Stack                 | 4-12 |

| 4.7.   | Phase 3 Top Level Processes        | 4-14 |

| 4.8.   | Entry and Exit Instructions Flow   | 4-16 |

## List of Tables

| able  |                                                                      | Page |

|-------|----------------------------------------------------------------------|------|

| 3.1.  | Integer ALU Cycle Times                                              | 3-3  |

| 3.2.  | Cycles ALU for Assembly Instructions                                 | 3-4  |

| 3.3.  | Cycles for ALU Microcode without Combining                           | 3-4  |

| 3.4.  | Cycles for ALU Microcode with 80% Combining                          | 3-4  |

| 3.5.  | Cycles for FP ALU Assembly or Microcode with $100\%$ data dependence | 3-6  |

| 3.6.  | Cycles for FP ALU Microcode - No Combining                           | 3-6  |

| 3.7.  | Cycles for FP ALU Microcode with 80% Combining                       | 3-6  |

| 3.8.  | Cycles for FP MUL Microcode without Combining                        | 3-7  |

| 3.9.  | Cycles for FP MUL Microcode with 80% Combining                       | 3-7  |

| 3.10. | Example Instruction Mix                                              | 3-10 |

| 3.11. | Cycles Required for Microinstructions                                | 3-11 |

| 4.1.  | Microinstruction Print Format                                        | 4-19 |

| 5.1.  | Matrix Multiply Code                                                 | 5-3  |

| 5.2.  | Matrix Multiply Microcode                                            | 5-4  |

| 5.3.  | Precision Tracker Results                                            | 5-5  |

#### Abstract

Microprogrammed Digital Signal Processors (DSP) are frequently used as a solution to embedded processor applications. These processors utilize a control memory which permits execution of the processor's instruction set architecture (ISA). The control memory can take the form of a static, read only memory (ROM) or a dynamic, writeable control memory (WCM), or both. Microcoding the WCM permits redefining the processor's ISA and provides speedup due to its instruction level parallelism (ILP) potential. In the past, code generation efforts for microprogrammable processors focused on creating assembly and microcode as two separate steps.

In this thesis, an alternative approach was chosen which combines the separate code generation steps into one automated, dual-target compilation process using the advanced techniques of VLIW compiler technology. The architecture chosen for this effort is a microprogrammable DSP being developed by Rome Labs, New York. The prototype compiler developed in this effort has demonstrated the potential for speedup of microcoded program portions over their assembly code counterparts. Therefore, the feasibility of program speedup produced by a dual-target compiler using VLIW compilation techniques has been validated.

#### Microprogramming a Writeable Control Memory

using

Very Long Instruction Word (VLIW) Compilation Techniques

#### I. Introduction

#### 1.1 Background

During the 1970s and most of the 1980s, complex instruction set architectures and microprogramming were the standard programming practices most processors were designed around. During the 1980s, however, individuals like John Hennessy and David Patterson began a revolution of sorts to reduce the complexity of the instruction set into smaller, more easily digestible bites for a computer to handle. The result was the reduced instruction set computer (RISC) and the pipelined processors found in most applications of today. Interestingly though, microprogrammed processors are making their way into the marketplace again in the area of digital signal processors (DSPs). The renewed interest is mainly due to the decrease in the cost and size of memory and their low power usage ideal for embedded processors like DSPs.

Typically, microcoded processors use a read only memory (ROM) which contains the microcode to execute the instruction set architecture (ISA) of the processor. Some architectures also provide a writeable portion of control memory, the writeable control memory (WCM), which can be modified to adapt to application-specific requirements. Some work has been accomplished in the area of exploiting the WCM recently, but most has been accomplished in the later 1970s and early 1980s. These efforts had focused mainly on generating microcode using dated compiler methods and has left out the assembly code portion as a separate step, and therefore a separate tool in the process. Another point to be made is that the previous efforts did not have the added advantage of the improved compiler technology of today. One of these improvements is in the area of Very Long Instruction Word (VLIW) compilers. This method of compilation provides a means of multiple instruction issue in the same cycle to gain a program speedup. VLIW compila-

tion techniques may therefore be beneficial to a processor which posses the potential of multiple instruction issue due to the format of the microinstruction itself.

#### 1.2 Problem Statement

Rome Labs has created a microprgrammed DSP for which no microcode compiler currently exists. Therefore, the goal of this effort is to generate a dual target compiler, generating both assembly and microcode, for Rome Lab's Wafer Scale Signal Processor (WSSP) which encorporates many of the recent advances achieved in VLIW compiler technology.

#### 1.3 Scope

The scope of this effort will be a code generator which transforms C language programs into their WSSP assembly and microcode functional equivalents. This requires a methodology to handle the two separate architecture targets, assembly code and microcode, in a single pass rather than employing the multiple tools used by previous efforts. Creating a compiler to translate C language programs into WSSP code is a scope requiring much more time than has been alloted for this effort; therefore, a compiler front end had to be chosen to bring the C code into some intermediate language. This effort will translate the intermediate language into the target processor's assembly and microcode.

#### 1.4 Summary of Current Knowledge

Microcoded processors exist on the market today, but the methods companies most commonly use is to still hand microcode the chosen portions of the program [11]. Also, much work related to microcode compilation is designed toward the goal of creating a customized processor architecture which optimizes the generated microcode as in [6]. Therefore most of the research information gathered for this effort resides in the work done in the late 1970s and early 1980s as well as the current WSSP specifications provided by Rome Labs.

The WSSP processor actually had its origins here at AFIT during the late 1980s from

the efforts of Dr Richard Linderman, currently the lead engineer for the WSSP at Rome Labs, Lt Col David Gallagher [4], and Capt John Comtois [2]. The later two were thesis efforts which created the floating point application specific processor (FPASP) incorporated into the WSSP of today. This processor is explained in more detail in Chapter 2.

#### 1.5 Assumptions

A simulator was developed to emulate the WSSP until it has actually been manufactured and tested. The WSSP compiler will be created to meet the WSSP specifications, and the resulting code tested on the simulator. Changes to the WSSP may be made during actual testing of the chips, but may not be encorporated into this effort in time.

#### 1.6 Approach

Since generating a compiler from scratch is not feasible in the time alloted for this effort, a compiler front end was chosen from which the code generator was created. The compiler generates the intermediate code which is converted into both assembly and microcode. The code generator for the assembly code was previously created and so the goal now was to modify the current code generator to generate the microcode in one compilation pass. This was done in three steps to be explained later in the thesis.

#### 1.7 Design Environment

The code generator is written in the C programming language. The resulting assembly and microcode is assembled and linked using the SAS Assembler provided by Rome Labs, and execution of the code occurs on the VSIM simulator located at Rome Labs.

#### 1.8 Organization of Thesis

Chapter 1 has provided the background to this thesis effort and has defined the particular problem to be solved. The scope of the problem and an approach to its solution were also presented.

Chapter 2 addresses efforts which have been made in the past to create microcode

for processors using a WCM, what microcoding entails, and an introduction to the WSSP.

Chapter 3 describes the methodology used in solving the dual compilation problem for generating microcode and assembly code. It speaks to the three phases involved in a code generator to produce the target processor specific code.

Chapter 4 delves into much greater detail in describing the actual implementation modifications made to the WSSP code generator. This is done to benefit the interested reader, but more importantly to provide a foundation of understanding for future efforts and modifications to the code generator itself.

Chapter 5 describes the results and analysis of the two benchmarks used in verifying and validating the WSSP code generator. This chapter will also provide the conclusions from this effort and recommendations for future efforts.

#### II. Background

#### 2.1 Introduction

Since the goal of this effort is to generate a compiler for a microprogrammed processor, much research went into two specific areas. The first was to understand what a microprogrammed processor is and how it functions. The second was to find out what efforts have been performed beforehand to exploit this type of processor. Therefore, this chapter explains the previous efforts employed in exploiting a WCM. It also explains how this type of processor operates and is microprogrammed. A background in code optimizations and VLIW techniques are also required to explain what role they play in the dual target compiler created. Finally, a brief description of the WSSP digital signal processor by Rome Labs is given.

#### 2.2 Microprogramming

An excellent reference for microprogramming is given by [10]. The following is an explanation of a microprogram control unit and how it is programmed.

2.2.1 Physical Layout. A microprogram control unit is made of two parts: the control memory and the microprogram sequencer. The sequencer is composed of the circuits which handle determining the next address of the control memory. The sequencer contains a register called the control address register which holds the address of the control memory to be executed next. This address is determined from one of four possibilities which are a function of the current microinstruction being executed (except for the initial branch from a standard instruction to WCM execution. In this case, a memory mapping is used where the macro instruction specifies the address in the WCM execution should switch to). The control memory holds the control words, or microinstructions, to be executed. The control words are broken up into fields, each of which specifies some reaction of the processor components. It is determining the format of the microinstruction that is required in order to microprogram a processor. Microinstructions come in two formats, horizontal and vertical.

2.2.1.1 Horizontal Microinstructions. Horizontal instructions are designed so that each bit controls each microoperation and therefore consists of long control words of 1s and 0s. This allows for controlling a variety of components in parallel but usually not all bits are utilized. Since the words are long, this can be an expensive design choice. For example, a four bit microinstruction may use the first bit to control an add operation, the next bit to control a multiply, and so on. Some encoding can be used as well to group mutually exclusive operations into fields. These fields must be decoded and so involves more hardware than the non-encoded microinstruction. This added hardware also increases the cost and propagation time of the signals. Though it may reduce the size of the memory required, the added hardware may offset this benefit. The WSSP utilizes this type of microinstruction.

2.2.1.2 Vertical Microinstructions. Vertical instructions require decoding circuits external to the control memory and involve one or two levels of decoding. "Direct" decoding uses one level of decoding performed directly on the instruction. This means each field has its own decoder to control what ever hardware it's assigned. "Indirect" decoding uses two levels where the bits in one field determine the meaning of bits in another field. If the microinstruction controls a bus organized CPU (components are controlled by signals on the buses), this is classified as a vertical microinstruction with the decoders for the fields placed in the bus system itself.

2.2.2 Control Memory. The control memory can be a read only memory (ROM) or a writeable control memory/store (WCM/WCS) or both. Typically a ROM is used, but occasionally a WCM is utilized. Since the ROM is static, it is very limited in its use in that it is microprogrammed once and remains static throughout execution of the processor. The WCM/WCS may be written to during execution and so can change throughout program execution to provide dynamic control of the hardware. This capability of the WCM provides an opportunity to be exploited to gain significant speedup in a much more flexible way than the ROM.

#### 2.3 Exploiting the WCM: Past Efforts

2.3.1 Methods of Loading the WCM. Abd-Alla and Karlgaard discuss an optimization technique which uses trace information of program execution to optimize a microprogrammed processor's ISA [1]. This effort involved heuristic tuning in five phases to create the final microcode for the WCM. These phases were environment partitioning, execution tracing, architecture synthesis, microcode verification, and system translator communications. Their focus was an algorithm for the architecture synthesis phase which through successive iterations of program code on a general purpose processor, would eventually develop the optimal microcode architecture solution. Final results showed improvements of 7.9 and 4.4 times that of a general architecture for their two sample Fortran programs. Their final results were impressive, but too much overhead is incurred in attempting to generate the trace file through multiple iterations, and this is done on a separate processor. Liu and Mowle discuss four methods of generating microcode to exploit a WCM [9]. All four techniques utilize the inner most loops of a given program to be transformed into the microcode for the WCM. Each technique is described below.

2.3.1.1 Static Loading. The first technique, Static Loading of the inner loops, simply microcodes the inner loops in the program and loads them into the WCM (prior to execution) until no space is left. When the WCM is small, which it usually is, this technique is not very efficient.

2.3.1.2 Selective Loading. The second technique, Selective Loading, microcodes those inner loops with the best chance of gained speedup and loads them in the WCM first. The other loops follow until again the WCM is full. Their method of determining the "best chance of speedup" was to assign priorities to each loop based on the depth of the loop within all its outer loops. Therefore those loops most deeply nested are given the highest level of perceived gain and microcoded first.

2.3.1.3 Dynamic Overlaying. The third technique, Dynamic Overlaying, requires two steps. Step one is to identify all inner loops and convert them to microcode. Step two involves loading the microcoded inner loop into the WCM during runtime as

needed. This involves overhead and a bookkeeping mechanism which will be discussed in the next chapter.

2.3.1.4 User Aided. The final method allows the user to make use of any execution knowledge he or she may have in choosing which loop will be microcoded and how (static or dynamic overlay) it will be loaded into the WCM.

2.3.2 WCM Code Compilation. Rauscher and Agrawala demonstrated that compilers can generate microprograms automatically which improve the performance of a program on a given processor using a WCM (with the main memory holding the program portions that could not be translated into the WCM). Their work correlates very strongly with this effort since they used a compiler that would translate the high level language program code into an intermediate language, choose the program blocks which would produce the best gain in performance, and then microprogram those for use in the WCM [13]. What they did not have at their disposal were the advanced techniques available today. Also, their paper doesn't discuss code optimizations for increased performance due to improved code scheduling and instruction level parallelism. These code optimization techniques didn't emerge for a few years after the above efforts.

#### 2.4 Code Optimizations

There are actually a multitude of code optimizations in existence today, but only two schemes - compaction and trace scheduling - will be focused on.

2.4.1 Compaction. The desire of compaction is to reduce the overall number of cycles required for a given program or code sequence. Compaction achieves this by analyzing the instructions within a local block. A local block is a sequence of instructions where entrance into the block occurs only at the top instruction and exiting the block occurs at the end in a jump or return statement or possibly a merge into another block. To compact this code, dependency graphs are generated in order to determine which cycle each instruction may be executed while maintaining the functionality of the code. Instructions having no dependencies with each other and which don't require the same processor resources may be assigned to the same cycle. Once this is accomplished, instructions may now be moved from blocks to other blocks to reduce overall cycle time. In general, cycle time is reduced, but the result is not optimal since the field of view is too narrow, looking at local blocks one at a time.

Joseph Fisher proposed trace scheduling as a solution 2.4.2 Trace Scheduling. to this problem of nearsightedness [3]. In trace scheduling, the compiler determines the most frequently executed path through the code. This can be done a number of ways (like profiling). This trace is sequentially laid out by the compiler in what is termed a superblock. This superblock is then compacted. This whole process generates new blocks within the superblock. The optimization is good, however, it produces branches and/or jumps into or out of the trace. This may result in code not being executed due to a branch or jump. This problem must be handled through complex book keeping. The solution chosen is known as "tail duplication" where the necessary code is simply duplicated and placed at the end of the applicable block corresponding to the branch. The result is a savings in total cycles for the given code, over and above that of compaction. In Fisher's work, he provides an example where the code originally required 13 cycles to execute. Simple local block compaction reduced this to 11 cycles. However, trace scheduling brought it down to seven cycles. One drawback to compaction and trace scheduling is the potential increase in code size of the program. While this may not be a problem today due to the size of most memories, the problem can actually grow exponentially. Is this a problem when you're microprogramming for a limited-size WCM? To test this requires a space analysis which is discussed in the next chapter. In general, however, this shouldn't be an issue since inner loops, which are typically very small, are the primary pieces of code microcoded for the WCM.

#### 2.5 VLIW Techniques

Modern processors attempt to issue multiple instructions each cycle. There are two approaches to accomplishing this - dynamic scheduling and VLIW. A machine implementing dynamic scheduling, which uses hardware to schedule instructions during runtime, can issue multiple instructions in one clock cycle - but does so with a limited window of view. In VLIW architectures, the compiler generates the instruction scheduling prior to runtime. In doing so, the compiler ensures that there are no dependencies between instructions that issue at the same time and that there are sufficient hardware resources to execute them. This simplifies the instruction decoding and issue logic required in a machine using dynamic scheduling [12]. The benefit of a VLIW compiler is that it possesses full view of the source code as it generates each instruction word and has the number and type of all functional units of the targeted processor at its disposal. The parallelism needed for issuing multiple instructions is achieved through loop unrolling and scheduling code across basic blocks using a global scheduling technique as mentioned previously [7]. As the compiler processes the source code, it uses this global code access and processor architecture data to create a control flow graph of the code. Each node of the graph represents an instruction and carries with it the information of what resource it requires and what clock cycle it is free to issue. Based on the format of the VLIW (the fields of which specify the processor resources), the compiler groups instructions together that may issue in the same clock cycle. In this way, how the instructions flow through the machine is fully determined by the compiler [5]. Though VLIW techniques have these desirable traits, they are not without their problems. Cache misses can severely disrupt the compiler's plans when all following instructions must be stalled while the data is retrieved. This is due to the requirement to maintain the flow generated by the compiler for all instructions based on which clock cycle they issue and their latencies. Branches, 20-30% of code, create a similar problem as well. Fortunately much of this can be alleviated through trace scheduling and loop unrolling [5]. Another drawback to VLIW techniques is the nonportability of code. This is due to the processor-specific nature of the generated code. VLIW code must be recompiled before moving to another architecture.

*Microinstruction and VLIW Comparison Results.* Regardless of the drawbacks, it's obvious that microinstructions and VLIW compilation techniques possess similarities which could be combined to create processor-specific efficient microcode. And with this potential, all that is needed is a processor and the corresponding compiler to

demonstrate whether the concept is valid. The compiler chosen for this effort is the Impact compiler created by the University of Illinois. This will be examined in detail in Chapter 3.

#### 2.6 The Wafer Scale Signal Processor

The WSSP is a programmable digital signal processor optimized for power efficient floating-point computations [8]. It can compute eight IEEE 32-bit or four IEEE 64-bit floating point operations per clock cycle and is designed to interface with PCI buses. Each WSSP chip is comprised of two identical processors, A and B, and a shared I/O interface. Each processor is made up of two 32-bit data paths (upper and lower), a control unit (ROM and WCM), and a floating point unit for addition and multiplication. The chip architecture can be broken into three sections: the integer datapath and control core, the floating point unit, and the external I/O bus interface.

2.6.1 Integer Datapaths and Control Core. Each of the A and B processors contains dual 32-bit integer datapaths and control and memory interface circuits. Each integer datapath has two operand buses (A, B Buses) and one destination bus (C Bus) which connect the registers to an integer ALU to perform standard arithmetic and logical operations. Between the upper and lower datapaths, 44 general purpose registers are available as well as some special purpose capabilities like a barrel shifter. The WSSP uses external SRAM with no internal cache. This removes the cache miss problems associated with VLIW techniques.

2.6.2 Floating Point Units. The floating point unit is composed of an adder and a multiplier capable of two IEEE 754-1985 single-precision operations or one IEEE 754-1985 double-precision operation per cycle. Both units are pipelined two levels deep to provide increased throughput.

#### 2.7 Conclusion

Since such advanced compilation techniques are now at our disposal, we can apply them to this reemerging technology to improve its performance with a substantial speedup. The following chapter describes the appreciable gains between execution in and out of the WCM as well as the specific issues that arise and must be handled because of it. It also spells out the changes made to the Impact compiler to generate microcode.

#### III. Methodology

#### 3.1 Introduction

The approach explained in this thesis to exploit the WCM is to create a code generator for the WSSP which targets both standard machine instructions and microinstructions. The WSSP does not currently have a dual assembly and microinstruction code generator, and so a new tool must be created. Due to the smaller size of the WCM, and the usually smaller, yet repetitious, nature of loops in program code, this code generator will microcode the inner loops. The code generator will be based upon the Impact Compiler developed by the University of Illinois which compiles C programming language code. Once the code is generated, a VHDL simulator provided by Rome Labs will be used to determine the performance of the code. The following paragraphs will explain how micropgrogrammable loop identification can and will be done, methods of loading the WCM and the method chosen, a brief description of the VHDL simulator, and finally the modifications which need to be made to the Impact Compiler to generate both assembly instructions and microinstructions.

#### 3.2 Programmable Loops

A few techniques exist to identify the inner loop. Abd-Alla and Karlgaard used post-execution analysis of a trace file created during execution by saving to file information about references to main memory. This trace file documents the frequency that each instruction is executed. From this file, program loops are identified and marked [1]. Another approach is using graph theory to determine the program loops. This approach provides a view of the structure of the code for loops to be identified.

Shin and Malek proposed a systematic approach which also considers the functional aspect of looping [14]. First they define a microprogrammable loop as one that has a single entry and contains no calls to a procedure or function which cannot be expanded in line (one exit). Single entry can be determined using graph representation and analysis. They provide a method of determining whether a function called within the loop is expandable and still allow the loop to fit within the size constraints of the WCM. Due to limited time

in completing this effort, I will manually determine if a loop is microprogrammable or not, tag that loop as such for later processing, and leave future efforts to focus on changes to Impact to choose what code should be microcoded.

#### 3.3 Microcode Execution Time Requirements

Determining which loops should be placed in the WCM is essentially a time and space calculation. The actual number of cycles to execute the code in assembly language must be compared to the number of cycles required in microcode. Calculating the cycles for the assembly code is a simple matter given the cycles required for each instruction. However, it is not this simple when determining the execution time in microcode. Since this effort attempts to combine assembly instuctions into one microinstruction, accurate estimation of execution time cannot easily be done without fully generating the microcode. However, assuming about 80% of the assembly code can be combined, a reasonable estimate can be made on the merit of microprogramming the loop based on time savings. If this were the only issue to be considered for time, all loops should be microcoded provided they fit into the WCM. This is not the case, however, since there exists an overhead simply by attempting to use the WCM.

The overhead in execution time is generated for several reasons. When an assembly basic block (inner loop) is transformed into microcode, a few things must happen. One is that a mapping must be created pointing an assembly instruction to the microcode to be executed when called. The second is the actual microcode must be loaded into the WCM before it's executed. Both of these efforts are above and beyond what is required had the code simply been executed in assembly language. The key is that the loop must iterate enough times to overcome the cost of the overhead. The mapping effort costs 6 cycles and the loading of the microcode into the WCM costs 2\*N + 6 cycles, where N is the number of microinstructions which can range from 1 to 64. Fifteen additional cycles are required due to four load instructions (3 cycles each) associated with loading and mapping the microcode instructions and three cycles for the prefetching required going into and returning from the WCM. Another reason for overhead is that labels, or rather

the addresses they represent, are not available to the microcode compiler. These addresses are generated by the assembler right before run time and so are not available to the compiler. Therefore ALL labels appearing in a microcode portion of code must be moved into registers in assembly code prior to the microcode. This costs 2\*L cycles, where L is the number of labels. Therefore the range of the overhead for this processor is 6 + 2\*1 + 6 + 2\*L + 15 = 27 + 2\*L cycles to a max of 6 + 2\*64 + 6 + 2\*L + 15 = 155 + 2\*L cycles.

The following sections present an analysis of the different instruction types used by the WSSP.

3.3.1 Integer ALU and Non-Pipelined Instructions. Integer ALU instructions executed in assembly language require two cycles. This includes the cycle to prefetch the next assembly instruction before it's executed. If multiple ALU and non-pipelined instructions are sequentially executed in microcode, this prefetch overhead occurs only once since for every jump into microcode the next assembly instruction must only be fetched before returning to assembly code. Hence, the more of these type instructions that will fit into the microcode, the better you do on eliminating the additional prefetch cycles. Another point to make is that combining, or issuing on the same cycle, can occur as well when executing from microcode - so long as there are no resource conflicts between the operations. Due to the WSSP design, which can execute two integer instructions simultaneously, some combining can be accomplished of non-conflicting instructions. Thus two assembly instructions requiring two cycles each can be reduced into one microinstruction requiring only one cycle - achieving a best-case speedup of four. Consider the performance of five sequential ALU instructions, Table 3.1 shows the cycles required for each type of execution.

Table 3.1 Integer ALU Cycle Times

|                           | No. of Cycles |

|---------------------------|---------------|

| Assembly                  | 10            |

| Microcode (no combining)  | 5             |

| Microcode (80% combining) | 3             |

The difference in execution between assembly and microcode with no combining is the simple difference in the number of cycles required for execution - two cycles for assembly instructions and one cycle for microcode instructions. The prefetch in microcode is combined within the five microinstructions and so occurs only once in the entire sequence. The 80% combined is the result of just three microinstructions requiring execution since four of the assembly instructions were combined into two microinstructions. Tables 3.2, 3.3, and 3.4 depict the cycles required for each method where ex stands for execution.

Table 3.2

Cycles ALU for Assembly Instructions

| Instruction | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |

|-------------|----|----|----|----|----|----|----|----|----|----|

| 1           | ex | ex |    |    |    |    |    |    |    |    |

| 2           |    |    | ex | ex |    |    |    |    |    |    |

| 3           |    |    |    |    | ex | ex |    |    |    |    |

| 4           |    |    |    |    |    |    | ex | ex |    |    |

| 5           |    |    |    |    |    |    |    |    | ex | ex |

Table 3.3

Cycles for ALU Microcode without Combining

| Instruction | 1  | 2  | 3  | 4  | 5  |

|-------------|----|----|----|----|----|

| 1           | ex |    |    |    |    |

| 2           |    | ex |    |    |    |

| 3           |    |    | ex |    |    |

| 4           |    |    |    | ex |    |

| 5           |    |    |    |    | ex |

Table 3.4 Cycles for ALU Microcode with 80% Combining

| Instruction | 1  | 2  | 3  |

|-------------|----|----|----|

| 1 & 2       | ex |    |    |

| 3 & 4       |    | ex |    |

| 5           |    |    | ex |

It can be seen that simply executing in microcode can potentially produce a significant speedup for that section of code. Obviously, any combining less than 80% will still produce a speedup.

#### 3.3.2 Pipelined Instructions.

Floating Point ALU Instructions. Floating point (FP) ALU operations on the WSSP are pipelined instructions. Therefore, if no data dependencies exist between two instructions, one can be started in the current cycle and the following instruction started in the next cycle. Operations performed on the FP ALU are FP adds and FP subtracts. Since integer multiplies, FP multiplies and FP divides have different resource requirements than FP ALU instructions, they will be discussed separately.

FP operations require three cycles to execute both in assembly language and microcode. Unlike the integer ALU operations, the instruction prefetch is merged into the three cycles and so cannot be removed simply by executing the instruction in microcode. Two FP single precision operations can be executed simultaneously if there are no data dependencies and no resource conflicts. They will be pipelined if zero data dependencies exist but resource conflicts do exist. Table 3.5 shows the cycles required by executing five FP ALU instructions in assembly code. It also represents the cycles for execution in microcode when 100% data dependence exists between all instructions. With this much dependence between instructions, there is no benefit from using the WCM over simple execution in assembly code. However, this is not usually the case, and so a significant speedup can be obtained simply by converting the instructions into microcode as can be seen in Tables 3.6 and 3.7. These tables show that speedup is improved by 36.4% with no combining and no data dependencies, and slightly more than doubled (15/7 = 2.14) when 80% combining is possible. The reason for the cycle skips is resource bus contention. The FP ALU functional unit takes inputs from registers on two busses - one source comes from either the upper or lower B bus, and the other source comes from either the upper or lower C bus. Since the result is written on one of the C busses, a conflict would arise between the result of the completing instruction and the sources of a new instruction starting on the same cycle. (Other source paths are possible to remove this restriction but a patent pending on the FP ALU prevents specifics.)

Floating Point Multiply Instructions. The FP multiply instructions are essentially identical to the FP ALU instructions, except that there is no resource

| Instruction | 1  | 2  | 3 | 4  | 5  | 6 | 7  | 8  | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|-------------|----|----|---|----|----|---|----|----|---|----|----|----|----|----|----|

| 1           | ex | ex | w |    |    |   |    |    |   |    |    |    |    |    |    |

| 2           |    |    |   | ex | ex | w |    |    |   |    |    |    |    |    |    |

| 3           |    |    |   |    |    |   | ex | ex | w |    |    |    |    |    |    |

| 4           |    |    |   |    |    |   |    |    |   | ex | ex | w  |    |    |    |

| 5           |    |    |   |    |    |   |    |    |   |    |    |    | ex | ex | w  |

Table 3.5 Cycles for FP ALU Assembly or Microcode with 100% data dependence

Table 3.6

Cycles for FP ALU Microcode - No Combining

| Instruction | 1  | 2  | 3  | 4 | 5  | 6  | 7  | 8 | 9  | 10 | 11 |

|-------------|----|----|----|---|----|----|----|---|----|----|----|

| 1           | ex | ex | w  |   |    |    |    |   |    |    |    |

| 2           |    | ex | ex | w |    |    |    |   |    |    |    |

| 3           |    |    |    |   | ex | ex | w  |   |    |    |    |

| 4           |    |    |    |   |    | ex | ex | w |    |    |    |

| 5           |    |    |    |   |    |    |    |   | ex | ex | w  |

contention on the write back cycle. Therefore, these instructions can be truly pipelined from start to finish. The cycles required for assembly code and microcode with 100% dependencies is the same as the FP ALU instructions shown in Table 3.5. Tables 3.8 and 3.9 show the cycles required for execution in microcode with no combining and microcode with 80% combining respectively. The "w" represents the "write back" portion of the executing instruction.

Floating point multiplies produce a greater speedup than FP arithmetic operations since the resource conflict on the write back cycle doesn't exist. As long as there are zero data dependencies, pipelining alone more than halves the execution time. Achieving

Table 3.7

Cycles for FP ALU Microcode with 80% Combining

| Instruction | 1  | 2  | 3  | 4 | 5  | 6  | 7 |

|-------------|----|----|----|---|----|----|---|

| 1 & 2       | ex | ex | w  |   |    |    |   |

| 3 & 4       |    | ex | ex | w | ï  |    |   |

| 5           |    |    |    |   | ex | ex | w |

| Instruction | 1  | 2  | 3  | 4  | 5  | 6  | 7 |

|-------------|----|----|----|----|----|----|---|

| 1           | ex | ex | w  |    |    |    |   |

| 2           |    | ex | ex | w  |    |    |   |

| 3           |    |    | ex | ex | w  |    |   |

| 4           |    |    |    | ex | ex | w  |   |

| 5           |    |    |    |    | ex | ex | w |

Table 3.8 Cycles for FP MUL Microcode without Combining

Table 3.9 Cycles for FP MUL Microcode with 80% Combining

| Instruction | 1  | 2  | 3  | 4  | 5 |

|-------------|----|----|----|----|---|

| 1 & 2       | ex | ex | w  |    |   |

| 3 & 4       |    | ex | ex | w  |   |

| 5           |    |    | ex | ex | w |

80% combining produces a speedup of three. As a note, integer multiplies, INT MULT, are performed using the FP multiplier, require three cycles to execute, and have one restriction - no combining may occur since only one 32 bit integer multiply operation can be started at a time.

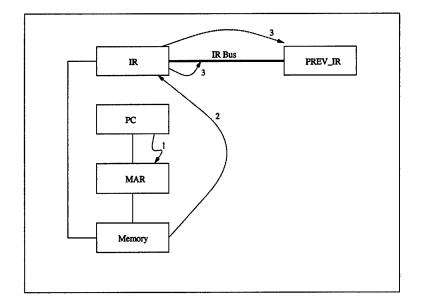

3.3.3 Branches. Branches in the WSSP are converted to (INT or FP) ALU compare and branch instructions. Both instructions can be pipelined with other instructions and are potentially combinable, providing an opportunity for speedup. The cycles for the compares were discussed in the INT ALU and FP ALU sections. The branch instruction itself requires two to four cycles. Four cycles are required for "less than or equal to" and "greater than or equal to" conditional branches. Performing branches in microcode generates some interesting problems.

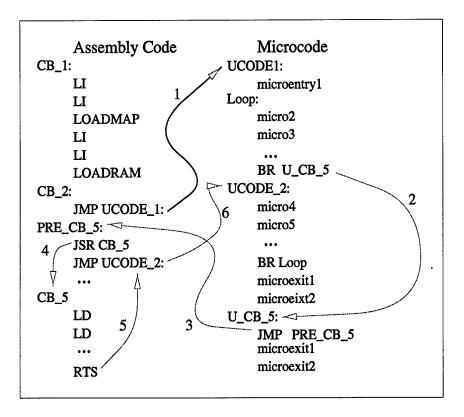

Branching in Microcode. Since branching normally requires the use of labels, branching in microcode isn't possible with a simple branch instruction (recall the discussion of labels for loads and stores and the need to move these labels into registers in assembly code prior to the jump to microcode) unless the target is also in microcode. What must be done is to insert jumps to branch handling portions of microcode which vector out of microcode to a branch handler in assembly which jumps to the required assembly code destination branch label. When execution is complete in the destination branch, a return is performed to the calling assembly branch handler which in turn makes another jump to the microinstruction following the original branch call in microcode. Figure 3.1 provides a picture of actual code showing how this can be done. For example, code begins executing at label CB\_1. The microinstructions on the right side of the figure are mapped to a location in the WCM (LOADMAP) and then loaded into that memory location (LOADRAM). The jump to microcode is made by executing JMP UCODE\_1. When the first branch in microcode is encountered and taken, which originally was a branch to CB\_5, the branch to the microcode branch handler (U\_CB\_5) occurs. The address of the PRE\_CB\_5 is loaded into the PC and the two microexit microinstructions are executed. The jump is made to the assembly code in PRE\_CB\_5 which simply jumps to CB\_5. Once CB\_5 is complete, the return to PRE\_CB\_5 is made. Finally, with the assembly portion complete, all that remains is a jump back to microcode - UCODE\_2.

All this jumping obviously generates some overhead - about eight cycles total. But instances will arise when it becomes necessary. A specific example for a microcode branch would be integer divides or mod operations. The WSSP ISA doesn't have instructions of this type and so branches must be made to predefined assembly library units. Rather than preclude microcoding because an integer divide or mod instruction appears in the code, it can be handled the above way provided the timing and space analysis determines it to be worthwhile.

3.3.4 Loads and Stores. These instructions require from 3 cycles up to 12 cycles to execute both in assembly and microcode. Byte-size loads and stores are the most costly. They also require the use of the same ALU unit as the INT ALU instructions and so functional unit conflicts arise frequently. Speedup comes from the fact that pipelining of loads and stores with each other and other instruction types is possible in microcode (combining is not possible due to resource conflicts). The cycles required for these instructions are identical to the FP multiplies, though no combining can occur.

Figure 3.1 Handling Branches in Microcode

#### 3.4 Instruction Mix Summary

Obviously code doesn't normally consist of only one type of instruction. And the analysis gets more complex as more instructions come into play. From the above analysis it can be seen that transforming the above instructions into microcode will produce a speedup over assembly language alone provided the overhead is overcome. The less data dependence and the more combining that exists, the more speedup that will occur. Rather than exhaust all the possibilities of instruction mixes, consider the following example.

Instruction Mix Example. Consider a code stream consisting of a mix of nine instructions of the types INT ALU, INT MULT, FP ALU, FP MULT, and BR (which becomes a compare/INT ALU operation and branch). For simplicity, assume there are no data dependencies between any instructions except the compare and branch. Table 3.10 shows the frequency of each instruction and the corresponding cycles in assembly and microcode.

| Instruction | Frequency | Assembly Cycles | Microcode Cycles |

|-------------|-----------|-----------------|------------------|

| INT ALU     | 2         | 2               | 1                |

| INT MUL     | 1         | 3               | 3                |

| FP ALU      | 2         | 3               | 3                |

| FP MUL      | 2         | 3               | 3                |

| INT CMP     | 1         | 2               | 1                |

| INT BR      | 1         | 2               | 2                |

Table 3.10

Example Instruction Mix

Cycles in Assembly. In assembly code, no combining or pipelining is possible. Each instruction executes its necessary number of cycles and then the following instruction executes until the instruction stream is exhausted. Therefore the total number of cycles in assembly code would be

Assembly

$$Cycles = I * \sum (F_i * C_i)$$

where I is the number of iterations,  $F_i$  is the frequency of the ith instruction, and  $C_i$  is the cycles required for the ith instruction. This code would then require I \* 23 cycles to execute.

Cycles in Microcode. The ALU (including CMP) and FP instructions can potentially be combined, no more than two into one, and the BR instruction can probably be absorbed into the last instructions (due to scheduling) and so not incur an additional two cycles. Since it can't be said that all of these instructions can be combined due to potential resource conflicts, assume 80% can. Therefore seven instructions of the nine possible can be combined. Note that different times result depending on how the instructions are combined. A multitude of potential combinations exist for combining this code depending on resources needed, and many of them will result in the minimum number of cycles required. The scheduler will chose one of the minimum cycle count solutions. Table 3.11 illustrates how each instruction is combined and the cycles they're executed in.

| Instruction    | 1  | 2  | 3  | 4  | 5  | 6 |

|----------------|----|----|----|----|----|---|

| 2 INT ALUs     | ex |    |    |    |    |   |

| INT MUL & CMP  |    | ex | ex | w  |    |   |

| 2 FP ALUs      |    |    | ex | ex | w  |   |

| 2 FP MULs & BR |    |    |    | ex | ex | w |

Table 3.11 Cycles Required for Microinstructions

Microinstructions dictate the sequence of events in the processor for each cycle of execution. The columns of Table 3.11 provide a picture of this – not the rows as might be expected. Therefore, six microinstructions would be needed to execute the code and so the total cycles required for this arrangement would be I\*6. The overhead cost, C, is 6 + 2\*6 + 6 + 15 = 39 cycles. Therefore the total cycles for one iteration and the overhead is (39 + 6) 45 cycles. The number of iterations required to overcome the overhead costs can thus be determined by solving for the break-even point between assembly code and microcode – anything above this is a speedup. Let A be the number of Microcode cycles. I be the number of iterations, O the overhead, and M be the number of Microcode cycles.

Then

$$A * I = O + M * I$$

$I = O \div (A - M)$

$I = 39 \div (23 - 6) = 2.29$

Therefore, at least 3 iterations of the loop must occur in order to recoup the cycles lost in overhead.

Microcode Space Requirements. The space requirements must be met for microcoding the WCM as well. The WCM is capable of containing 64 microinstructions. Since each cycle required represents one microinstruction, the example above of six cycles would fit into the WCM and so pass the space test.

*Example Summary.* This type of comparison would need to be done for each loop. Due to the time constraints for this effort, automatically determining which loops are microprogrammable will be a follow on effort. It is not a simple issue since the microcode must be generated first by the compiler/scheduler to determine what pipelining and combining will occur. Based on this, the analysis to use microcode or not can be carried out. For this thesis, each loop will be manually evaluated to determine if a speedup is obtained through microcoding and if the loop will fit within the WCM. Since the percentage of combining cannot be determined prior to compilation, 80% combining will be assumed.

### 3.5 Methods to Load the WCM

Methods to load the WCM were discussed in the previous chapter and focus on the efforts of Liu and Mowle. The method chosen for this thesis is the user-aided with dynamic overlay. Each microcoded loop will be loaded into the WCM as needed during runtime. Any previous loops, including the same loop, will be overwritten. Time constraints for this effort are the only reasons this method was chosen since it is unnecessary to overwrite a loop which already exists in the WCM. One way of preventing this overwrite is a trap that gets called if the opcode for the loop exists in the microcode map to prevent loading the data again. Other methods exist, and should be the focus of a follow-on effort.

#### 3.6 The VHDL Simulator

The VHDL simulator to be used in this effort was developed by a contractor for Rome Labs. It exists only at Rome Labs and only two copies are available. It's designed to handle simulating not only the assembly code but the microcode as well. This is the simulator to be used to verify the correct operation of the WSSP code generator. A few benchmarks, each heavy in floating point execution since this is the primary purpose of the WSSP signal processor, will be compiled into assembly code and executed gathering the number of cycles executed. It will then be compared with the performance of its microcoded counterpart. The speed of the simulator limited what benchmarks were used.

#### 3.7 The Impact Compiler

The Impact compiler is a VLIW compiler and so can optimize and schedule multiple instructions per cycle. The scheduling portion of the compiler operates on an intermediate instruction language known as Lcode to provide a unified interface to the code optimizers and code generators. Lcode stands for low-level intermediate code. In order to generate the assembly and microcode instructions required by the WSSP, the current assembly code generator must be modified.

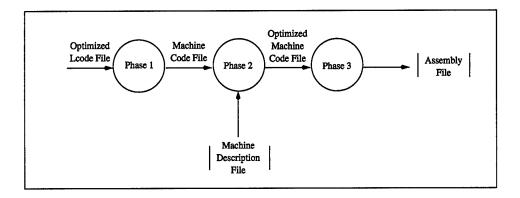

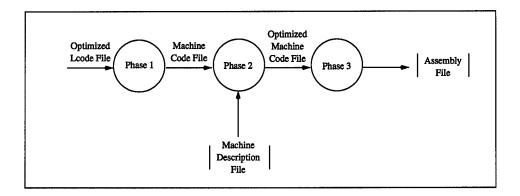

3.7.1 Impact Code Generators. As a background, code generators for impact are comprised of three phases to bring the basic Lcode intermediate form of a program into the machine specific instruction format required by the target processor. This flow from Lcode to machine assembly code can be seen in Figure 3.2.

Impact generates optimized Lcode from a program that was originally written in the C programming language and places it in a file, <filename>.O. Phase 1 takes this file and begins the process of moving the Lcode into machine specific code. In this particular phase, instructions are created which map one-to-one to instructions the target processor

Figure 3.2 Code Generation Instruction Flow

can execute. As an example, Phase 1 would take the following Lcode instruction

sub\_f R1, R2, 1.0

and change it into two instructions of the form

mov\_f R3, 1.0

sub\_f R1, R2, R3

since the WSSP doesn't have a floating point subtract with immediate instruction. The WSSP also has an instruction that changes its mode of operation from integer, to single precision floating point, to double precision floating point. This is due to the use of the FP ALU and FP Multiplier (which is also used for integer multiplies). This instruction, SETFP, is inserted as needed during this phase. <filename>.mc is the output file of Phase 1.

Phase 2 then takes the output of Phase 1 and performs four operations on the code: instruction scheduling, register allocation, optimization, and changes offset references from four areas in the stack (incoming parameters, outgoing parameters, local variables, and register spill space) to offsets off the stack pointer (SP). Phase 2 sets up the stack for each function in the program as well. The output of this phase is an optimized machine code file <filename>.mco which becomes the input file for the next and last phase of the code generator.

Phase 3 is the simplest of the three phases and makes no changes to the code other than simple translation from intermediate form to assembly code. By this time, the input stream is in the format to simply print out to a file, <filename>.s, as assembly instructions. All that is left is to assemble and link the code and execute it on the target processor, or in this case, on the simulator.

#### 3.8 Dual Target Code Generator for Microcoding

Generating assembly code for the WSSP with Impact has already been accomplished using the above format as the template. However, the WSSP requires microcode in order to exploit the WCM - which in essence is generating code for two target architectures simultaneously. A method needed to be devised to generate the microcode as well as the assembly code in a single pass compilation step. The same three phases are used, but modifications needed to be made to each. Before discussing these modifications, recall that the marking of the microcode portions of code (control blocks) will be performed prior to Phase 1, and so <filename>.O, which is the input file to this phase, will already have these control blocks tagged.

3.8.1 Phase 1 Modifications. Phase 1 will still perform the same purpose, which is to create a one-to-one mapping of Lcode instructions to match the target processor's ISA. Due to microcoding, new issues emerge that must be dealt with. For example, when creating assembly code, labels and their absolute addresses aren't a concern since the addresses are generated by the assembler when machine binary code is created just before runtime. This poses a problem when trying to move this code into microcode and the absolute address isn't available yet. In order to combat this and prevent labels from making it to Phase 3 where the microcode will be generated, each label must be moved once into a register in assembly code so that these addresses are available to the microcode. This is only done when microcoding is being accomplished and does add to the overhead cost (three cycles for each label) for moving assembly code into microcode.

A potential optimization would be to do address calculations for loads and stores outside of microcode which would be a one-time two cycle overhead. Loads and stores would then only be a two cycle operation (rather than the current three cycle operation) in microcode saving one cycle per iteration. If a new address calculation is needed while in microcode, however, this optimization would be nullified. No other changes are necessary for Phase 1. However, it is anticipated that follow-on work will likely need to make further changes to aid optimization.

3.8.2 Phase 2 Modifications. Phase 2 requires sweeping changes, or actually additions, in order to handle the dual compilation requirement. Since both types of code are to be created, each "target code" requires its own machine description file. This is true because the latencies, resource usages, and in some cases even the instruction format of assembly instructions change when creating a microinstruction from the corresponding assembly instruction. Defining every instruction's characteristics to ensure proper scheduling and optimization is a major undertaking. The target processor architecture must be fully understood in order to correctly create the mapping of latencies, resources, and formats per instruction. In addition to this, since the code generator is set up to go through one function at a time, and a function may contain portions targeted for assembly and portions to microcode, two passes must be made in order to handle both instances. The first pass schedules and optimizes those instructions destined for assembly code using the corresponding machine description file, while the second pass does the same for instructions to be microcoded using its machine description file. The truly amazing point behind this is that with the machine description files, the scheduler and optimizer will create extremely efficient, conflict free machine code. When programs get very large, this is a tremendous benefit. The scheduler then creates a table of these resources and determines which instructions can be issued simultaneously to gain the greatest speedup. For an individual to perform this task would be time consuming on a staggering scale. However, with the computer, this is a simple task.

In this particular instance, using the Lcode instructions for resource mapping wasn't sufficient, since resource mapping for microcode must get down to busses, functional units, and mutually exclusive fields required for each cycle. This being the case, a new opcode must be created for each corresponding Lcode instruction which takes into consideration whether the registers assigned are upper or lower registers and whether instructions using immediates require 16 bits or 32 bits to represent the immediate field (32 bit immediates require an extra cycle to load the upper 16 bits first followed by the lower 16 bits). Due to this level of detail, each Lcode instruction explodes into two to eight possible instruction

formats, depending on the mix of upper and lower registers in the instruction assigned during register allocation. The register allocator could be improved in this area by performing a dependence chain of code and assigning registers based on reduced conflict versus the current "minimal register use" algorithm it employs.

Another important point is that there may be a number of different ways to execute any given instruction due to the many paths the data may take. This is a tremendous opportunity to exploit the parallelism not always inherent in instruction flow. Provided the cycle and resources are mapped together correctly in the machine description file, the scheduler will choose the instruction option that will allow the greatest amount of instruction level parallelism (ILP). This allows for a greater chance of speedup. The difficulties associated with this potential will be dealt with in the next chapter, where more detail to these modifications will be explained.

The result of Phase 2 is that each instruction now carries with it the cycle it is to be issued in. This information is essential for Phase 3.

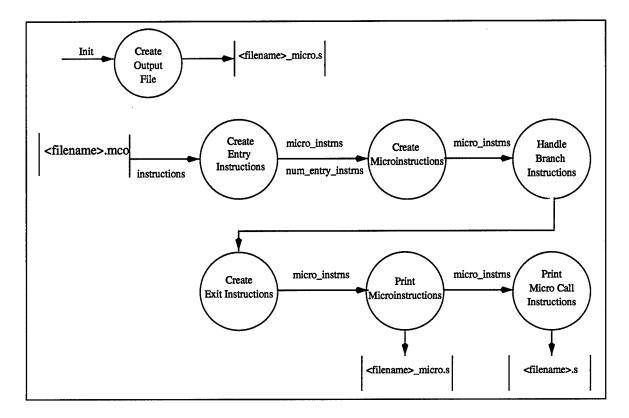

3.8.3 Phase 3 Modifications. Phase 3 still retains the purpose of printing out the instructions in the format the assembler needs to generate binary machine code. However, a simple printing scheme is no longer sufficient. Phase 3 underwent sweeping changes as well due to the complexity of generating microcode (see Figure 3.3).

Initially, a microinstruction output file is created and initialized. It's given the program name with "\_micro.s" appended to it (Create Output File process). All portions of microcode are printed to this file. Once the output file initialization is accomplished, "entry" and "exit" instructions are inserted into the microinstruction stream (Create Entry and Create Exit Instructions processes). These instructions perform the prefetching of the next assembly instruction that will be executed upon exit of this loop. The assembly instructions tagged for microcoding are then converted into microinstructions (Create Microinstructions process). Since the last assembly instruction is a branch instruction, care must be taken here so as to ensure the branch is not executed before preceding instructions have completed executing (Handle Branch Instructions process). The resulting microinstructions are printed to the output file (Print Microinstructions process) in a for-

Figure 3.3 Phase 3 Process Overview

mat detailed in the next chapter. Finally, a few assembly instructions are inserted into the assembly code stream to set up the jump to microcode (Print Micro Call Instructions process). These instructions are already a part of the WSSP ISA and consist of the LOADMAP and LOADRAM. The first of these maps a newly defined opcode for the microcode loop to the address in microcode it will be loaded so that when this opcode is fetched in assembly language, the processor knows to jump to the corresponding address in the WCM. The LOADRAM is the instruction which will move the code from memory into the WCM before execution. In order to execute the microcode, an inline assembly instruction is created with the corresponding opcode and inserted in the assembly stream following the LOADRAM and LOADMAP instructions. When program execution reaches this point, a jump occurs to the WCM in order to execute the microcode stored there. Upon completion, execution returns to the assembly code following the jump. This sequence of instructions appears in the assembly code as follows: R1 and R2 contain the opcode and WCM address of the microcode respectively. Register R3 contains the number of microinstructions to load into the WCM. The .int statements are the inline assembly instruction stating to execute opcode 127, "111111", which causes the jump to the location in the WCM pointed to by R2.

#### 3.9 Conclusion

This is the method chosen for creating the dual targetted compiler for the WSSP. Although some of the discussion was at a detail level to get a good handle on the task at hand and what will be accomplished, much of the specific details were left out in the implementation of the code for the code generator. The following chapter will remedy this situation for the benefit of the interested reader and any follow-on efforts building upon this foundation.

### IV. Impact and the WSSP Code Generator: A Closer Look

### 4.1 Introduction

Whereas Chapter 2 described the background to using VLIW techniques to generating microcode and Chapter 3 explained the method chosen to solve the problem in some detail, this chapter delves into the specifics of the code generator implementation. It describes the key features and design decisions of the actual code that generates the microcode for the WSSP. As a reminder of the process, Figure 4.1 provides the Code Generator Flow. Only specific areas need to be explained in more depth, however. The first is the format and overall design of each code generation phase. The format of the source code files will be described and why a functional design was chosen. The Phase 1 discussion details the setting of the mode for the processor using an implementation already built into Impact, the creation of preheader control blocks for removing labels from microcode and placing the LOADMAP and LOADRAM instructions outside the loop. The details of the instruction flow in Phase 2 is expanded upon. This includes the separation of assembly code and microcode. A detailed explanation of the heart of Phase 2, the machine description file (MDF) is presented here as well. Finally, an explanation of Phase 3's method of generating microcode and the data structures used caps off the description of the code generator for the WSSP. A hardware description of the WSSP is somewhat limited due to patents pending on portions of the design.

Figure 4.1 Code Generation Instruction Flow

# 4.2 Overall Design Decisions

The major design decision was to continue use of the existing functional design of the code generators rather than attempt a differing approach. The purpose of the code generator actually lends itself to a functional approach since its primary purpose is to handle incoming data, process it in some fashion, and pass it on to the next step. The end result is a series of functions that permit a continuous flow of data. This is not so much an interaction between objects, as would be the case for an Object Oriented approach. More important reasons for this choice, however, are derived from the purpose of the completed tool. It is planned to be used on the market for the WSSP. As such, there isn't enough time to perform a major re-engineering effort on the code. The desire is to design and code the tool to be complete and correct but to get to market quickly - this meant using the current design and delaying any major re-engineering efforts until a later time as needed. A final point to be made is that since the design method currently used has proven effective to many successful code generators already in existence, no convincing argument could be thought of to cause a choice to redesign the current architecture.