## Distributed Time-Predictable Memory Interconnect for Multi-Core Architectures

Haitong Wang

Doctor of Philosophy

University of York Computer Science September 2019

## Abstract

Multi-core architectures are increasingly adopted in emerging real-time applications where execution time is required to be bounded in the worst case (i.e., time predictability) and low. Memory access latency is the main part forming the overall execution time. A promising approach towards time predictability is to employ distributed memory interconnects, either *locally arbitrated* interconnects or *globally arbitrated* interconnects, with arbitration schemes, and the pipelined tree-based structure can break the critical path of multiplexing into short steps with small logic size. It scales to a large number of processors that high clock frequency can be synthesised. This research explores timing behaviour of multi-core architectures with shared distributed memory interconnects and improves distributed time-predictable memory interconnects for multi-core architectures. The contributions are mainly threefold. First, the generic analytical flow is proposed for time-predictable behaviour of memory accesses across multi-core architectures with *locally arbitrated* interconnects. It guarantees time predictability and safely bound the worst case without exact memory access profiles. Second, the root queue modification with the root queue management is proposed for multi-core architectures with *locally arbitrated* interconnects that variation of memory access latency is reduced and timing behaviour analysis is facilitated. Third, Meshed Bluetree is proposed as the distributed time-predictable multi-memory interconnect, enabling multiple processors to simultaneously access multiple memory modules.

## Acknowledgements

I would like to give my sincere gratitude to my supervisor Prof. Neil C. Audsley for his guidance, patience and encouragement through my journey. I would also like to express special thanks to my research colleagues for their help and support.

## Declaration

I declare that this thesis is a presentation of original work and I am the sole author. This work has not previously been presented for a degree or other qualification at this university or elsewhere. All sources are acknowledged as references. The content of some of the chapters in this thesis has already been published within the following publications.

- H. Wang, N. C. Audsley and W. Chang. Addressing Resource Contention and Timing Predictability for Multi-Core Architectures with Shared Memory Interconnects. IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS), Sydney, Australia, 2020, pp. 70-81. [1]

- H. Wang, N. C. Audsley, X. S. Hu and W. Chang. Meshed Bluetree: Time-Predictable Multimemory Interconnect for Multicore Architectures. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 39, no. 11, pp. 3787-3798, Nov. 2020. [2]

# Contents

| 1        | $\operatorname{Intr}$ | troduction |                                                |    |

|----------|-----------------------|------------|------------------------------------------------|----|

|          | 1.1                   | Resear     | ch Questions                                   | 6  |

|          | 1.2                   | Thesis     | Structure                                      | 8  |

| <b>2</b> | Lite                  | erature    | Review                                         | 11 |

|          | 2.1                   | Real-7     | Time System                                    | 11 |

|          | 2.2                   | Memo       | ry                                             | 14 |

|          |                       | 2.2.1      | Cache                                          | 19 |

|          |                       | 2.2.2      | Prefetch                                       | 24 |

|          |                       | 2.2.3      | Scratchpad Memory                              | 29 |

|          |                       | 2.2.4      | Summary                                        | 34 |

|          | 2.3                   | Shared     | d Memory Multi-Core Architecture               | 35 |

|          |                       | 2.3.1      | Memory Arbitration                             | 37 |

|          |                       | 2.3.2      | Distributed Memory Interconnect                | 40 |

|          |                       | 2.3.3      | Critical Resource Contention                   | 49 |

|          |                       | 2.3.4      | Summary                                        | 55 |

|          | 2.4                   | Summ       | ary and Discussion                             | 56 |

| 3        | Mu                    | lti-Cor    | e Architectures with Shared Distributed Memory |    |

|          | Inte                  | erconne    | ects                                           | 59 |

|          | 3.1                   | Basic      | Architecture                                   | 60 |

|          | 3.2                   | Proble     | em Analysis                                    | 64 |

|          |                       | 3.2.1      | Time Predictability                            | 64 |

|          |                       | 3.2.2      | Varying Memory Access Latency                  | 65 |

|   |                                                           | 3.2.3          | Increasing Memory Access latency                        | 68   |  |

|---|-----------------------------------------------------------|----------------|---------------------------------------------------------|------|--|

|   | 3.3                                                       | Resea          | rch Hypothesis                                          | 70   |  |

| 4 | Ana                                                       | lysing         | g Timing Behaviour of Multi-Core Architectures          |      |  |

|   | witl                                                      | n Shar         | ed Distributed Memory Interconnects                     | 71   |  |

|   | 4.1                                                       | Time           | Predictability of Multi-Core Architectures with Shared  |      |  |

|   |                                                           | Distri         | buted Memory Interconnects                              | 72   |  |

|   |                                                           | 4.1.1          | Bluetree-based Architecture                             | 73   |  |

|   |                                                           | 4.1.2          | Timing Behaviour Analysis                               | 76   |  |

|   |                                                           | 4.1.3          | Worst-Case Analysis                                     | 79   |  |

|   | 4.2                                                       | Timin          | g Behaviour of Multi-Core Architectures with Shared     |      |  |

|   |                                                           | Distri         | buted Memory Interconnects                              | 87   |  |

|   |                                                           | 4.2.1          | Locally Arbitrated Architecture and Globally Arbitrated |      |  |

|   |                                                           |                | Architecture                                            | 89   |  |

|   | 4.3                                                       | Summ           | nary and Discussion                                     | 104  |  |

| 5 | Reducing Variation of Memory Access Latency across Multi- |                |                                                         |      |  |

| - |                                                           | 0              | nitectures with Shared Distributed Memory Inter-        |      |  |

|   |                                                           | nects          | · ·                                                     | 106  |  |

|   | 5.1                                                       | Proble         | em Analysis                                             | 107  |  |

|   | 5.2                                                       |                | Queue Modification                                      |      |  |

|   |                                                           | 5.2.1          | Timing Behaviour Analysis                               |      |  |

|   |                                                           | 5.2.2          | Root Queue Management                                   |      |  |

|   | 5.3                                                       | Evalua         | ation: Hardware Simulations                             |      |  |

|   | 5.4                                                       |                |                                                         |      |  |

|   |                                                           | 5.4.1          | -                                                       |      |  |

|   |                                                           |                | · · ·                                                   | 1.05 |  |

|   |                                                           |                | loads                                                   | 125  |  |

|   |                                                           | 5.4.2          | loads                                                   |      |  |

|   |                                                           | 5.4.2<br>5.4.3 | loads                                                   |      |  |

|   | 5.4                                                       |                | ation: FPGA Experiments                                 |      |  |

|              | 5.5   | Summary and Discussion                                  | 134 |

|--------------|-------|---------------------------------------------------------|-----|

| 6            | Mes   | shed Bluetree: Distributed Time-Predictable Multi-Memor | ry  |

|              | Inte  | erconnect for Multi-Core Architectures 1                | 36  |

|              | 6.1   | Problem Analysis                                        | 137 |

|              | 6.2   | Meshed Bluetree                                         | 139 |

|              |       | 6.2.1 Timing Behaviour Analysis                         | 146 |

|              | 6.3   | Evaluation: Hardware Consumption                        | 154 |

|              | 6.4   | Evaluation: Synthetic Memory Workloads                  | 155 |

|              |       | 6.4.1 Memory Access Latency with Multiple Homogeneous   |     |

|              |       | Memory Modules                                          | 156 |

|              |       | 6.4.2 Memory Access Latency with Mixed Memory Modules   | 158 |

|              | 6.5   | Evaluation: Benchmarks                                  | 160 |

|              | 6.6   | Summary and Discussion                                  | 167 |

| 7            | Cor   | cluding Remarks 1                                       | 170 |

|              | 7.1   | Research Summary                                        | 170 |

|              | 7.2   | Main Contributions                                      | 173 |

|              | 7.3   | Future Work                                             | 174 |

| R            | efere | nce 1                                                   | 74  |

| $\mathbf{A}$ | ppen  | ldix 1                                                  | 90  |

|              | А     | Request Interval                                        | 191 |

|              |       | A.1 Varying Request Interval [1, 64]                    | 191 |

|              |       | A.2 Varying Request Interval [1, 256]                   | 193 |

# List of Figures

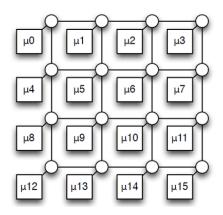

| 1.1  | Network-on-Chip Architecture                           | 2  |

|------|--------------------------------------------------------|----|

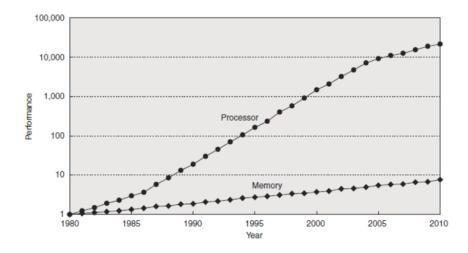

| 1.2  | Performance Gap Memory and Processor                   | 3  |

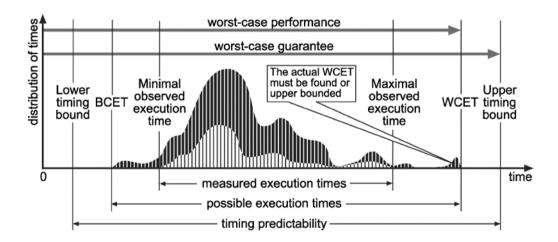

| 2.1  | Task Execution Time                                    | 13 |

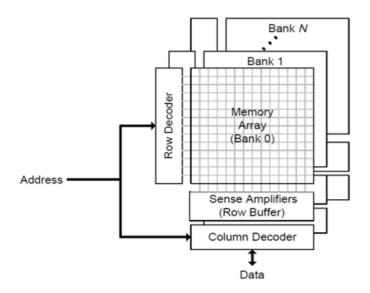

| 2.2  | DRAM Organisation                                      | 15 |

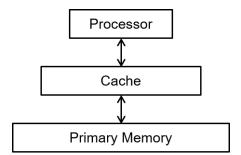

| 2.3  | Memory Hierarchy                                       | 18 |

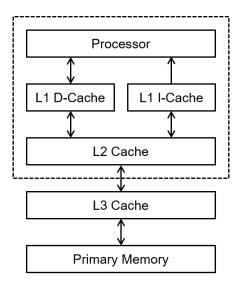

| 2.4  | Cache Hierarchy                                        | 21 |

| 2.5  | Markov Prediction Table                                | 27 |

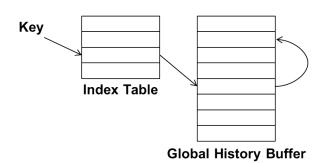

| 2.6  | Global History Buffer                                  | 28 |

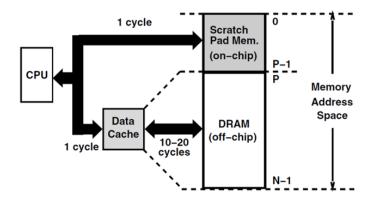

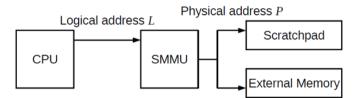

| 2.7  | Scratchpad Memory Address Configuration                | 29 |

| 2.8  | Memory Configuration with Scratchpad Memory Management |    |

|      | Unit                                                   | 33 |

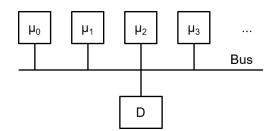

| 2.9  | Bus-based Multi-Core Architecture                      | 35 |

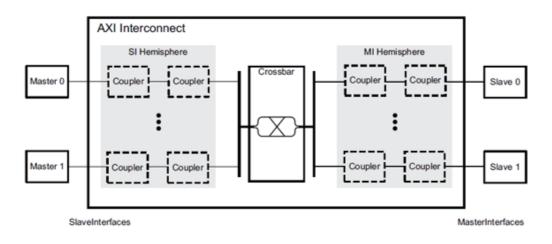

| 2.10 | AXI Interconnect                                       | 36 |

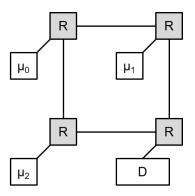

| 2.11 | Shared Memory Network-on-Chip Architetcure             | 37 |

| 2.12 | MoT                                                    | 41 |

| 2.13 | Arbitration Tree                                       | 43 |

| 2.14 | Bluetree                                               | 45 |

| 2.15 | TDM Tree                                               | 46 |

| 2.16 | GAMT                                                   | 48 |

| 2.17 | Memory Centric Scheduling                              | 50 |

| 3.1  | 8-Client Basic Architecture                            | 60 |

| 4.1  | Bluetree Multiplexer                                   | 74 |

| 4.2  | Bluetree Communication Packet Format                           |

|------|----------------------------------------------------------------|

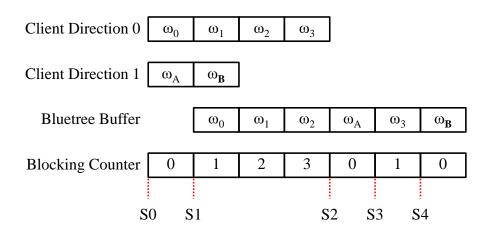

| 4.3  | Blocking Behaviour of Bluetree Multiplexer                     |

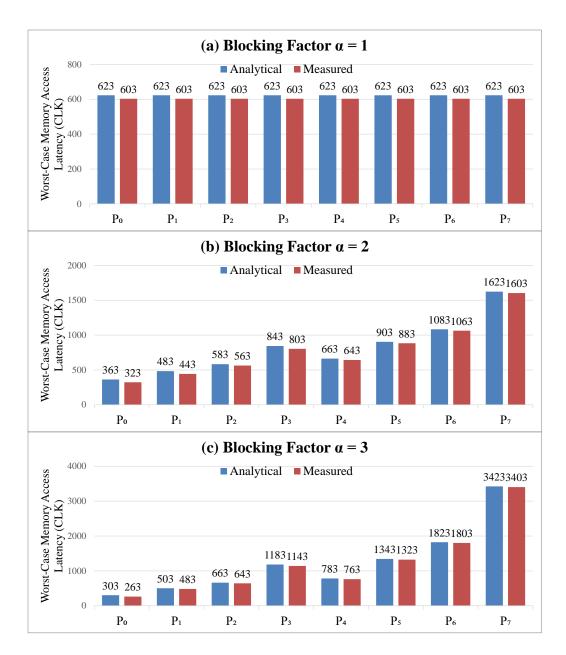

| 4.4  | Worst-Case Memory Access Latency across Bluetree-based Ar-     |

|      | chitecture                                                     |

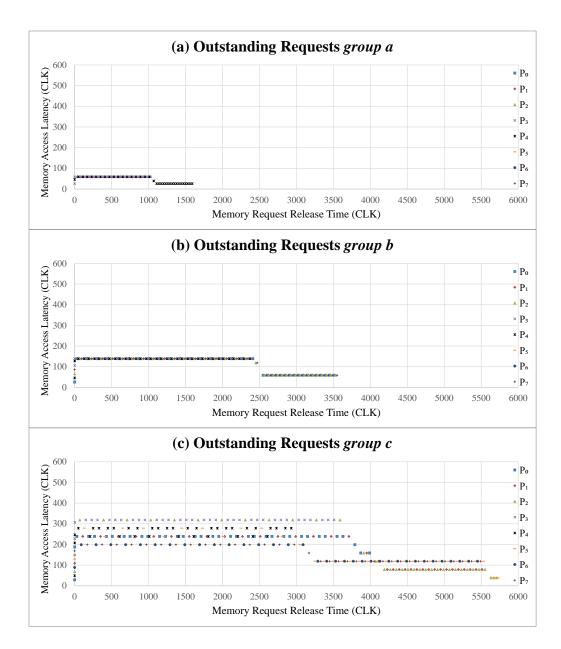

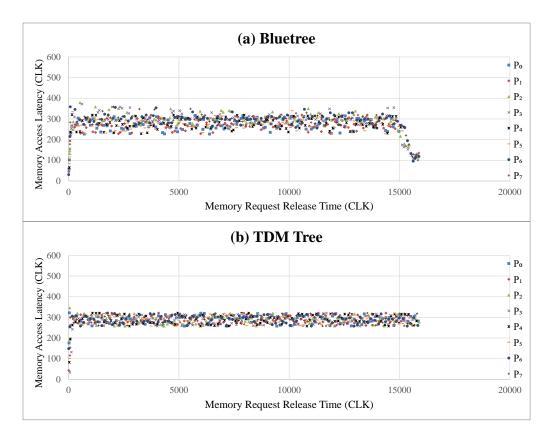

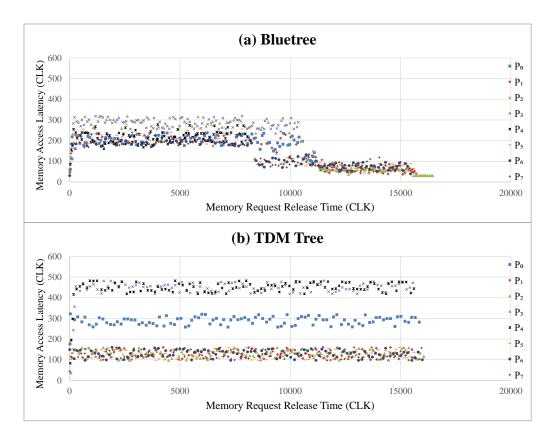

| 4.5  | Memory Access Latency across 8-Client Bluetree-based Archi-    |

|      | tecture                                                        |

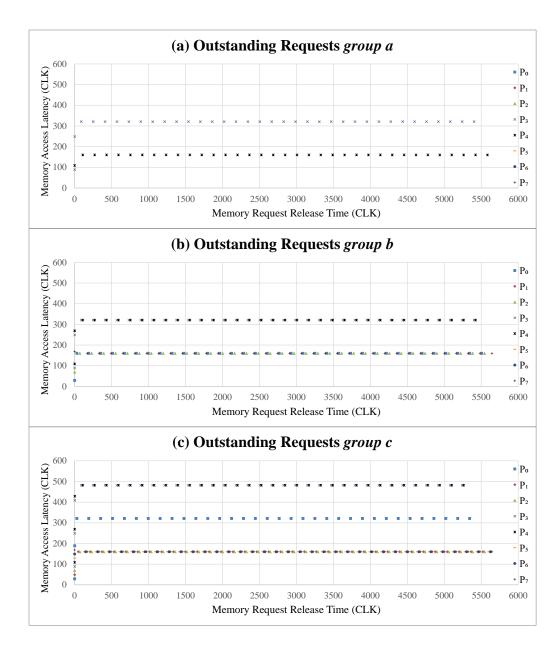

| 4.6  | Memory Access Latency across 8-Client TDM Tree-based Ar-       |

|      | chitecture                                                     |

| 4.7  | Memory Access Latency with Balanced Path Workloads across      |

|      | 8-Client Bluetree-based Architecture and 8-client TDM Tree-    |

|      | based Architecture                                             |

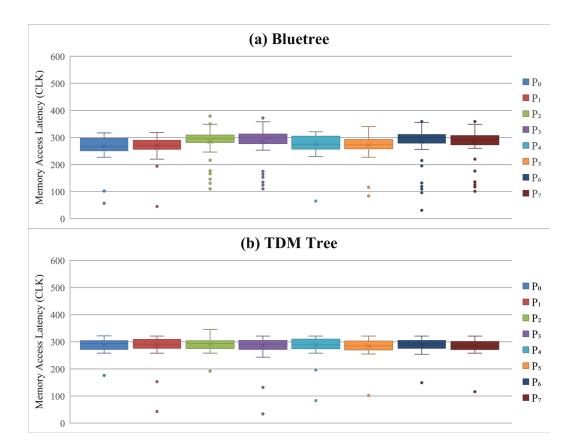

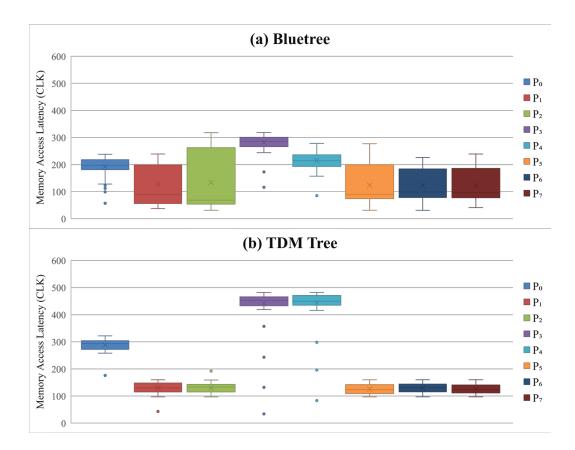

| 4.8  | Boxplot of Memory Access Latency with Balanced Path Work-      |

|      | loads across 8-Client Bluetree-based Architecture and 8-client |

|      | TDM Tree-based Architecture                                    |

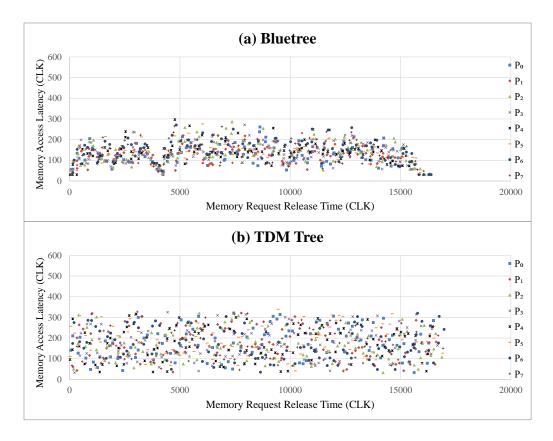

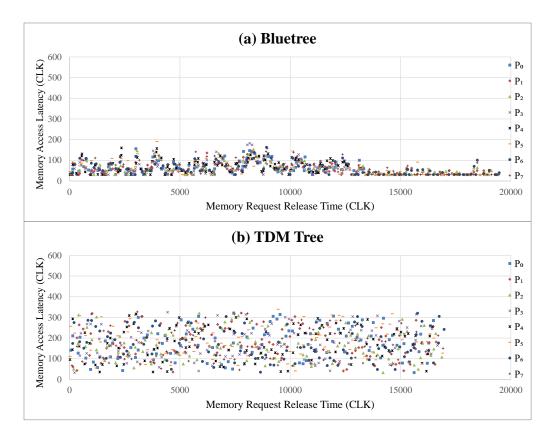

| 4.9  | Memory Access Latency with Increasing Request Intervals across |

|      | 8-Client Bluetree-based Architecture and 8-client TDM Tree-    |

|      | based Architecture                                             |

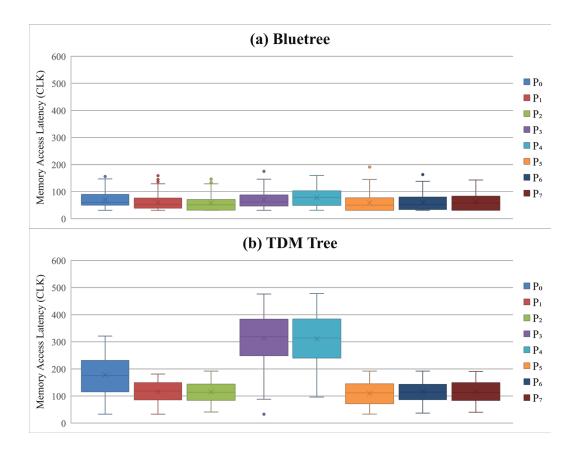

| 4.10 | Boxplot of Memory Access Latency with Increasing Request       |

|      | Intervals across 8-Client Bluetree-based Architecture and 8-   |

|      | client TDM Tree-based Architecture                             |

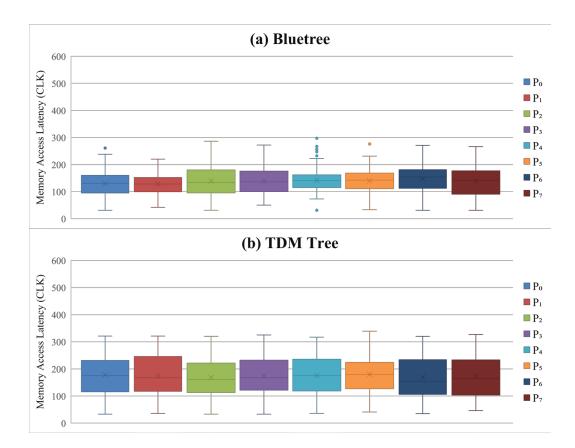

| 4.11 | Memory Access Latency with Unbalanced Path Workloads across    |

|      | 8-Client Bluetree-based Architecture and 8-client TDM Tree-    |

|      | based Architecture                                             |

| 4.12 | Boxplot of Memory Access Latency with Unbalanced Path          |

|      | Workloads across 8-Client Bluetree-based Architecture and 8-   |

|      | client TDM Tree-based Architecture                             |

| 4.13 | Memory Access Latency with Varying Request Intervals across    |

|      | 8-Client Bluetree-based Architecture and 8-client TDM Tree-    |

|      | based Architecture                                             |

| 4.14                                                                                                               | 4 Boxplot of Memory Access Latency with Varying Request In-           |                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                                                                                                    | tervals across 8-Client Bluetree-based Architecture and 8-client      |                                                                                                       |

|                                                                                                                    | TDM Tree-based Architecture                                           | 103                                                                                                   |

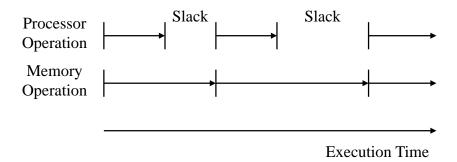

| 5.1                                                                                                                | Processor Operation vs. Memory Operation                              | 107                                                                                                   |

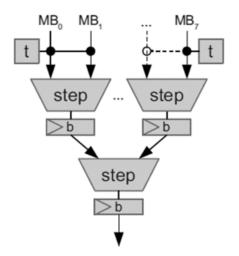

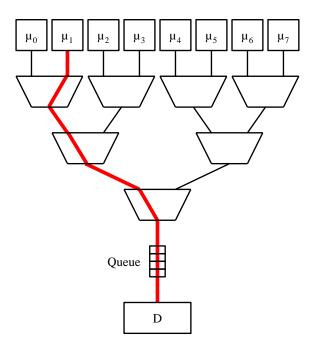

| 5.2                                                                                                                | Bluetree-based Architecture with Root Queue Modification              | 111                                                                                                   |

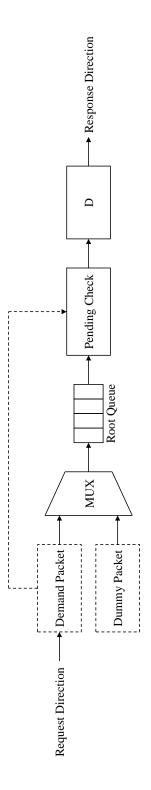

| 5.3                                                                                                                | Root Queue Management with Hardware Design                            | 117                                                                                                   |

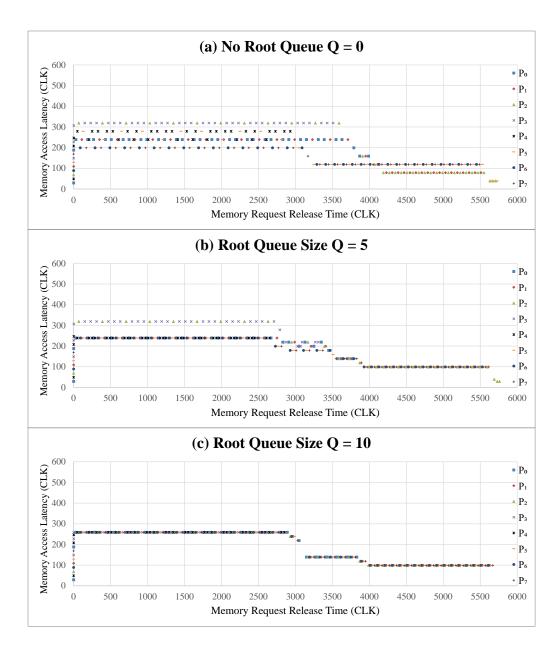

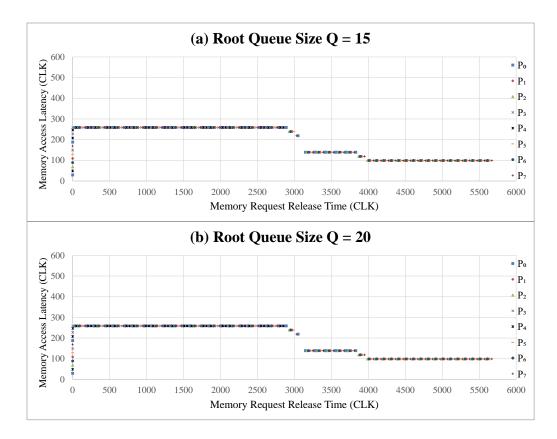

| 5.4                                                                                                                | Memory Access Latency with Increasing Root Queue Size                 | 121                                                                                                   |

| 5.5                                                                                                                | Memory Access Latency with Increased Root Queue Size                  | 122                                                                                                   |

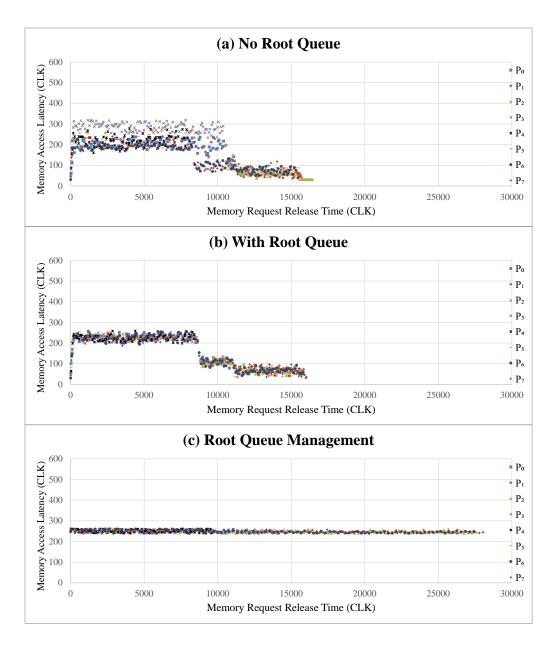

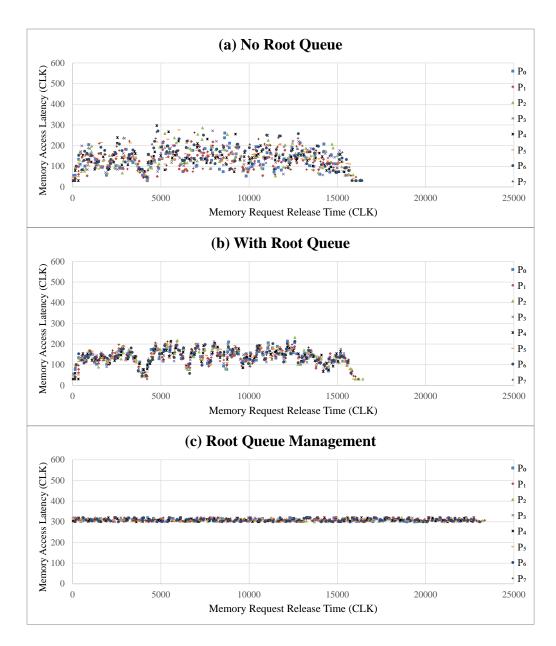

| 5.6                                                                                                                | Memory Access Latency with Varying Workloads                          | 126                                                                                                   |

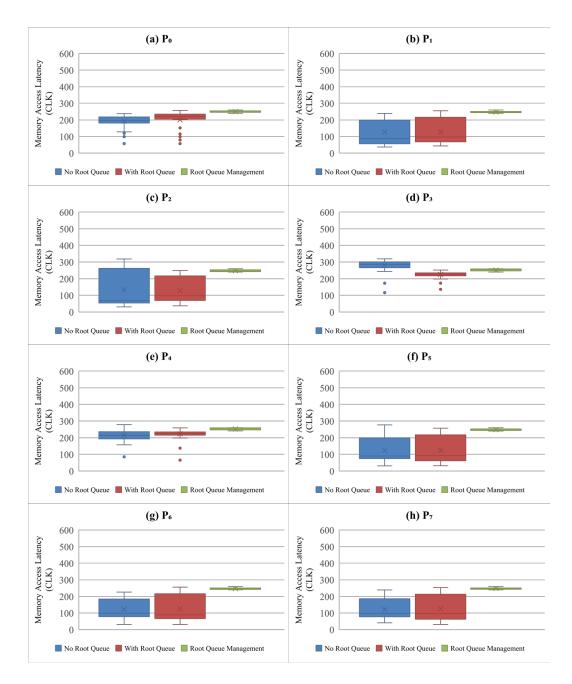

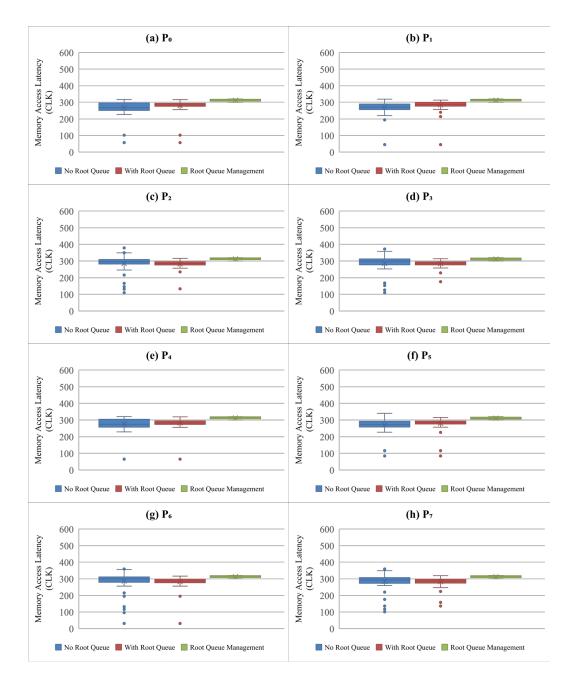

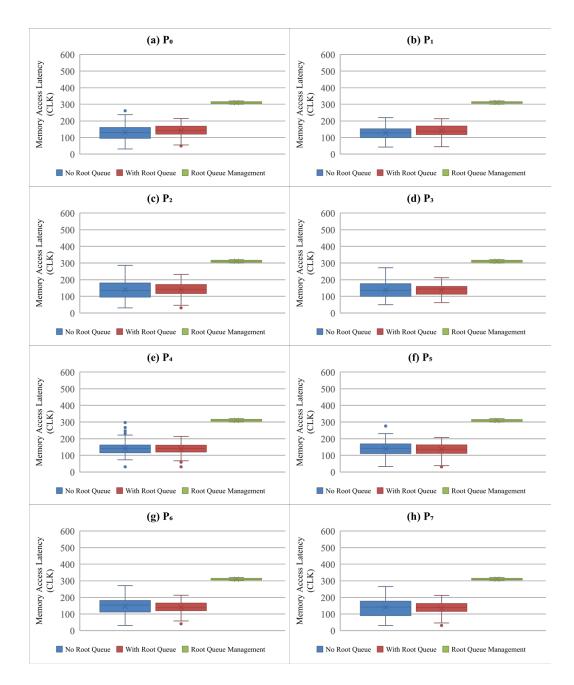

| 5.7                                                                                                                | Boxplot of Memory Access Latency with Varying Workloads .             | 127                                                                                                   |

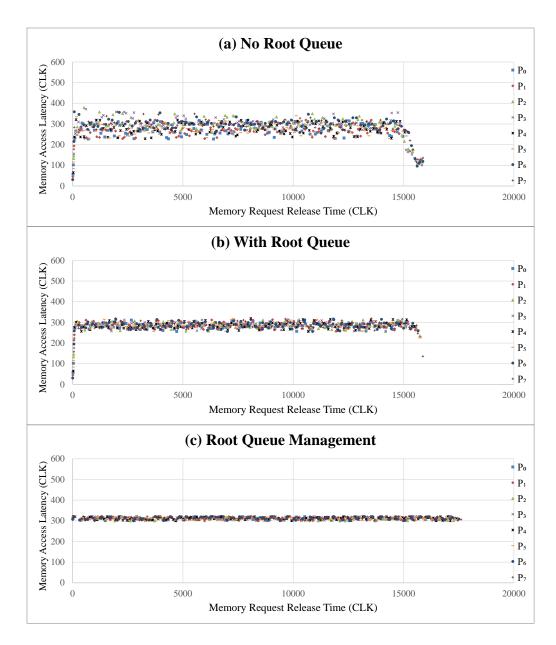

| 5.8                                                                                                                | Memory Access Latency with Balanced Path Workloads                    | 129                                                                                                   |

| 5.9                                                                                                                | Boxplot of Memory Access Latency with Balanced Path Work-             |                                                                                                       |

|                                                                                                                    | loads                                                                 | 130                                                                                                   |

| 5.10                                                                                                               | Memory Access Latency with Increasing Request Intervals               | 131                                                                                                   |

|                                                                                                                    |                                                                       |                                                                                                       |

| 5.11                                                                                                               | Boxplot of Memory Access Latency with Increasing Request              |                                                                                                       |

| 5.11                                                                                                               | Boxplot of Memory Access Latency with Increasing Request<br>Intervals | 132                                                                                                   |

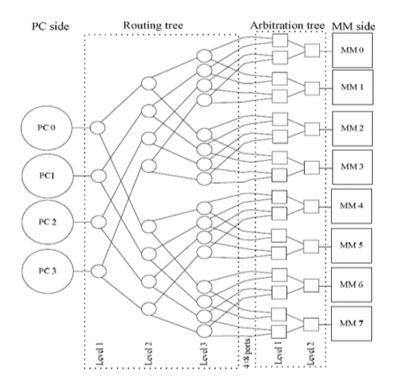

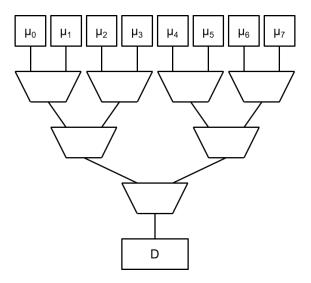

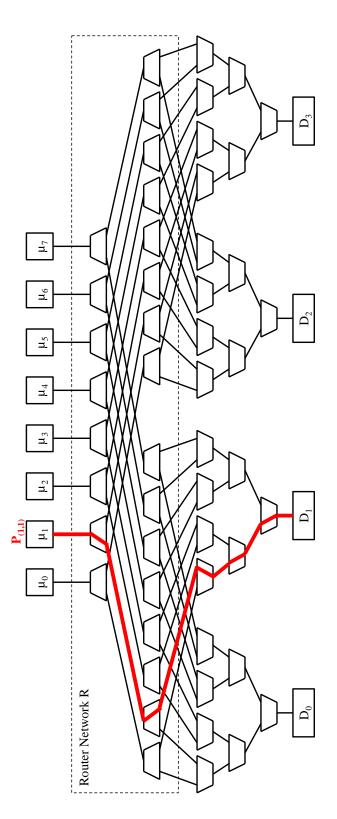

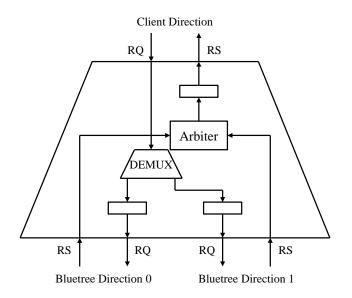

| 5.11<br>6.1                                                                                                        |                                                                       |                                                                                                       |

|                                                                                                                    | Intervals                                                             | 141                                                                                                   |

| 6.1                                                                                                                | Intervals                                                             | 141<br>142                                                                                            |

| 6.1<br>6.2                                                                                                         | Intervals                                                             | 141<br>142                                                                                            |

| <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                      | Intervals                                                             | 141<br>142<br>145                                                                                     |

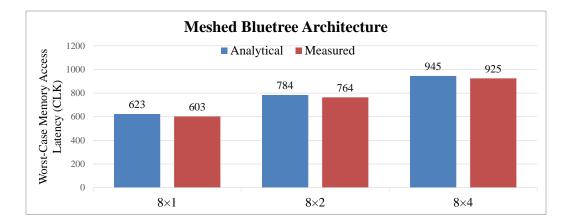

| <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                      | Intervals       8×4 Meshed Bluetree         8×4 Meshed Bluetree       | <ol> <li>141</li> <li>142</li> <li>145</li> <li>151</li> </ol>                                        |

| <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                                                          | Intervals       8×4 Meshed Bluetree         8×4 Meshed Bluetree       | <ol> <li>141</li> <li>142</li> <li>145</li> <li>151</li> <li>153</li> </ol>                           |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul>                                        | Intervals                                                             | <ol> <li>141</li> <li>142</li> <li>145</li> <li>151</li> <li>153</li> <li>153</li> </ol>              |

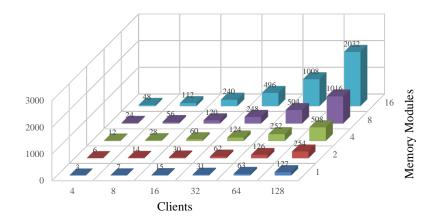

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul>                           | Intervals                                                             | <ol> <li>141</li> <li>142</li> <li>145</li> <li>151</li> <li>153</li> <li>153</li> <li>153</li> </ol> |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> </ul>              | Intervals                                                             | <ol> <li>141</li> <li>142</li> <li>145</li> <li>151</li> <li>153</li> <li>153</li> <li>153</li> </ol> |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> </ul> | Intervals                                                             | <ol> <li>141</li> <li>142</li> <li>145</li> <li>151</li> <li>153</li> <li>153</li> <li>156</li> </ol> |

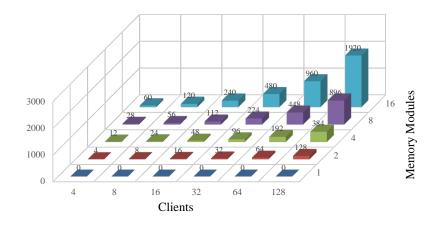

| 6.11 | Average Memory Access Latency with Mixed Memory Modules 159        |

|------|--------------------------------------------------------------------|

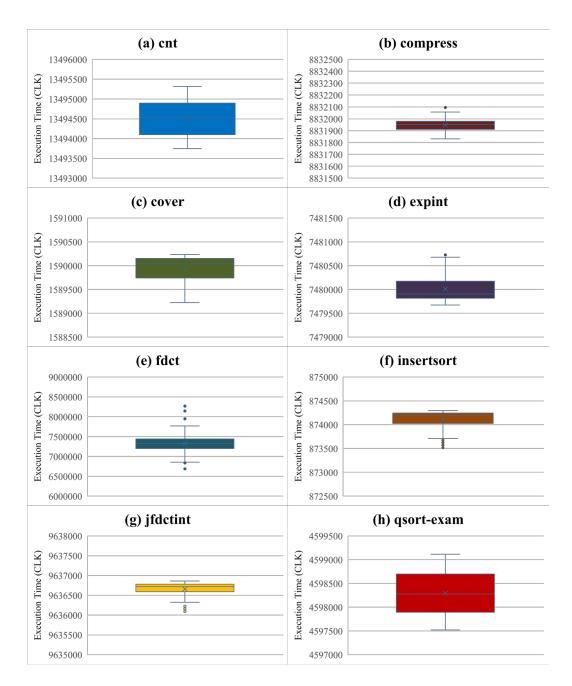

| 6.12 | Boxplot of Execution Time in $8\times 1$ Meshed Bluetree Architec- |

|      | ture with Single DRAM Module                                       |

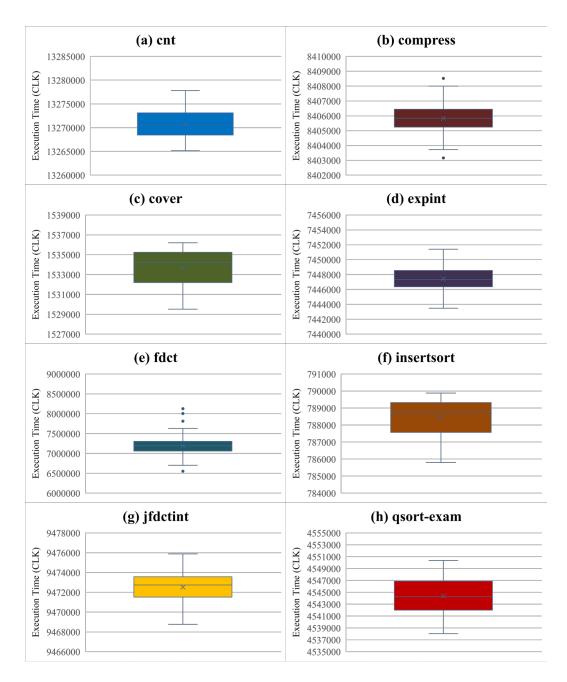

| 6.13 | Boxplot of Execution Time in $8\times 2$ Meshed Bluetree Architec- |

|      | ture with Instruction DRAM Module and Data DRAM Module $162$       |

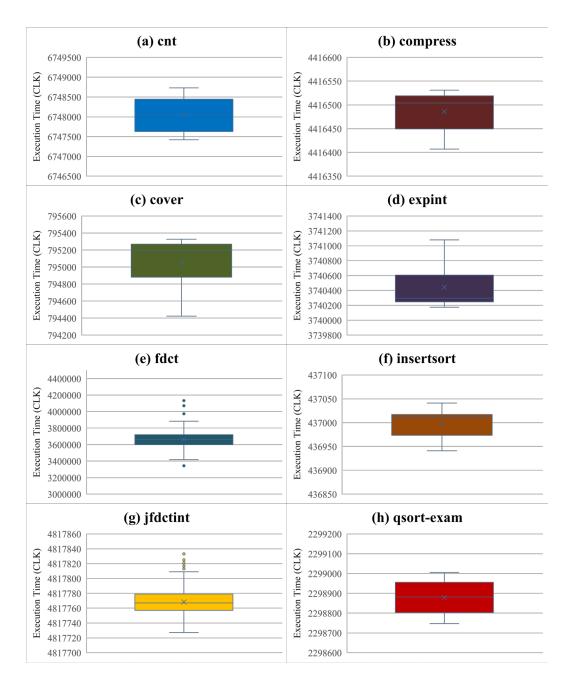

| 6.14 | Boxplot of Execution Time in $8\times 2$ Meshed Bluetree Architec- |

|      | ture with Dual DRAM Modules $\ldots$                               |

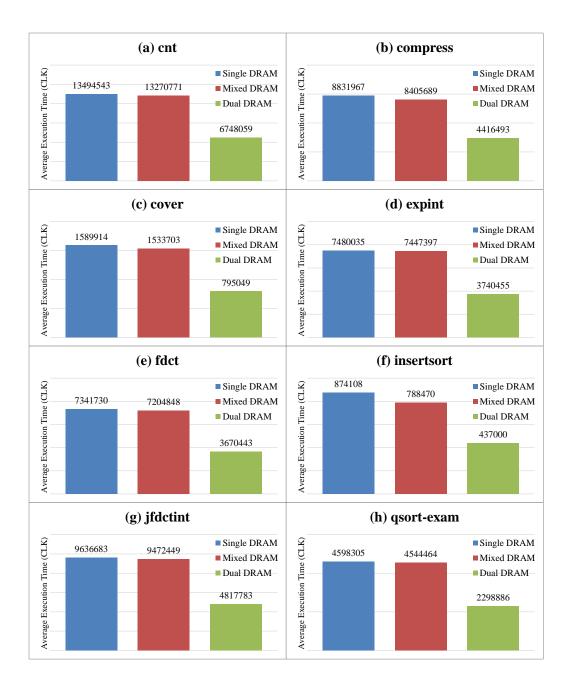

| 6.15 | Average Execution Time in Meshed Bluetree Architectures $164$      |

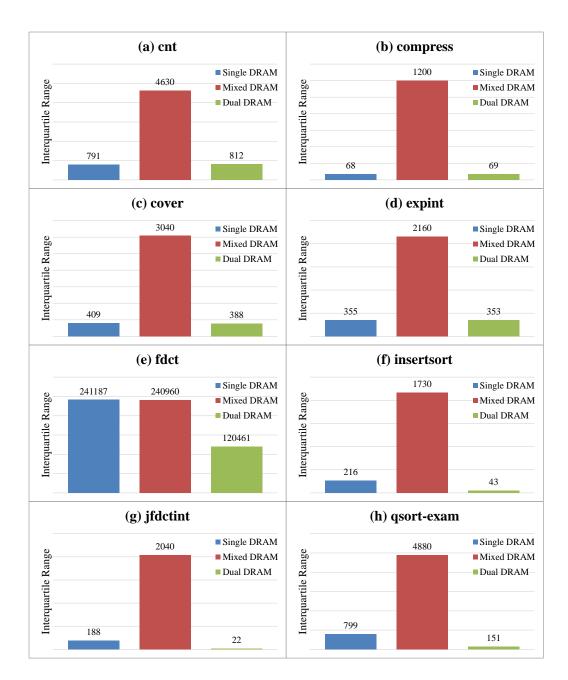

| 6.16 | Interquartile Range of Execution Time in Meshed Bluetree Ar-       |

|      | chitectures                                                        |

# List of Tables

| 2.1 | Summary of Methods to Alleviate Critical Resource Contention | 57  |

|-----|--------------------------------------------------------------|-----|

| 3.1 | Summary of Distributed Memory Interconnects                  | 63  |

| 4.1 | Maximum Blocking Number in 8-Client Bluetree-based Archi-    |     |

|     | tecture                                                      | 83  |

| 4.2 | Increasing Outstanding Requests for 8-Client Architectures   | 91  |

| 4.3 | Balanced Outstanding Requests for 8-Client Architectures     | 95  |

| 6.1 | Hardware Consumption at RTL Level                            | 154 |

# List of Symbols

| Symbol           | Description                                               |

|------------------|-----------------------------------------------------------|

| $\mu_i$          | a client with index i                                     |

| $N_{\mu}$        | number of client                                          |

| $B_j$            | a distributed memory interconnect with index <b>j</b>     |

| $N_B$            | number of distributed memory interconnect                 |

| $N_{eta}$        | depth of distributed memory interconnect                  |

| $eta_{m k}$      | a stage of distributed memory interconnect with           |

|                  | index $k$                                                 |

| $D_{j}$          | a shared root memory module with index j                  |

| $N_D$            | number of shared root memory module                       |

| $t(D_j)$         | latency of shared root memory module $D_j$                |

| $P_i$            | memory access path for client $\mu_i$                     |

| $P_{(i,j)}$      | memory access path from client $\mu_i$ to shared root     |

|                  | memory module $D_j$ (in multi-memory architecture)        |

| $P(\beta_k)$     | local priority of a memory access path at stage $\beta_k$ |

| lpha             | Bluetree blocking factor                                  |

| ω                | a memory access                                           |

| $t(\omega)$      | latency of memory access $\omega$                         |

| $t_{RQ}(\omega)$ | request path latency of memory access $\omega$            |

| $t_{RS}(\omega)$ | response path latency of memory access $\omega$           |

| $t^{BC}(\omega)$           | best-case latency of memory access $\omega$               |

|----------------------------|-----------------------------------------------------------|

| $t_{RQ}^{BC}(\omega)$      | best-case request path latency of memory access $\omega$  |

| $t^{BC}_{RS}(\omega)$      | best-case response path latency of memory access $\omega$ |

| $t^{WC}(\omega)$           | worst-case latency of memory access $\omega$              |

| $t_{RQ}^{WC}(\omega)$      | worst-case request path latency of memory access $\omega$ |

| $t_{RS}^{WC}(\omega)$      | worst-case response path latency of memory access         |

|                            | ω                                                         |

| $N_{RQ}^{WC}(\omega)$      | maximum blocking number in request path of                |

|                            | memory access $\omega$                                    |

| $N_{RQ}^{WC}(\beta_k)$     | maximum blocking number iterative up to stage $\beta_k$   |

| $N^{WC}_{\alpha}(\beta_k)$ | maximum arbiter blocking number at stage $\beta_k$        |

| au                         | a sequence of memory requests                             |

| $N_{RQ}^{WC}(	au)$         | maximum blocking number in request path of                |

|                            | sequence $\tau$                                           |

| $N_{RQ}^{\mu}(\mu_i)$      | outstanding request number from client $\mu_i$            |

| $N^{\mu}_{RQ}(D_j)$        | outstanding request number to shared root                 |

|                            | memory $D_j$                                              |

| $T^{\mu}_{RQ}(\mu_i)$      | request interval from client $\mu_i$                      |

| Q                          | root queue size                                           |

| $Q_S$                      | minimum size of the root queue for queued service         |

| R                          | a router network                                          |

| $N_R$                      | depth of router network                                   |

| $N_{mux}$                  | number of Bluetree multiplexer                            |

| $N_{router}$               | number of Bluetree router                                 |

| $N_{wire}$                 | number of Bluetree wire                                   |

|                            |                                                           |

# List of Acronyms

| Acronym  | Description                       |

|----------|-----------------------------------|

| NoC      | Network-on-Chip                   |

| TDM      | Time Division Multiplexing        |

| BCET     | Best-Case Execution Time          |

| WCET     | Worst-Case Execution Time         |

| HRT      | Hard Real-Time                    |

| FRT      | Firm Real-Time                    |

| SRT      | Soft Real-Time                    |

| RAM      | Random Access Memory              |

| SRAM     | Static Random Access Memory       |

| DRAM     | Dynamic Random Access Memory      |

| DDR DRAM | Double Data Rate synchronous DRAM |

| FIFO     | First-In-First-Out                |

| LRU      | Least Recently Used               |

| MRU      | Most Recently Used                |

| SPM      | Scratchpad Memory                 |

| AHB      | Advanced High-Performance Bus     |

| AXI      | Advanced eXtensible Interface     |

| MoT      | Mesh-of-Tree                      |

| GAMT     | Globally Arbitrated Memory Tree   |

\_

| RQ    | Request Path            |

|-------|-------------------------|

| RS    | Response Path           |

| MUX   | Multiplexer             |

| DEMUX | Demultiplexer           |

| L     | Low Priority            |

| Н     | High Priority           |

| RTL   | Register-Transfer Level |

| LUT   | Look-Up Table           |

## Chapter 1

## Introduction

Recently, Moore's law [3][4] is still relevant, while Dennard Scaling [5] has broken down. Moore's law states that the number of transistors per unit area doubles for each technology generation. Dennard Scaling states that the power density stays roughly constant as transistors get smaller, and thus the power consumption stays in proportion with area. Combined Moore's law with Dennard Scaling, computing performance per watt doubles about every two years. However, the breakdown of Dennard Scaling limits the improvement of the computing performance by increasing the processor clock frequency directly. Instead, the current trend is to scale the number of processing cores to achieve high performance.

The conventional method tends to employ multiple processing cores within a single chip. This promotes the multi-core architecture where the multiple processing cores are constructed and interconnected with a shared bus. Compared with the coupling of multiple single core processors, the multi-core processor executes threads concurrently, providing higher performance with less power consumption. However, this introduces the bus contention issue.

Figure 1.1. Network-on-Chip Architecture

The communications between the processing cores, or between the processing core and the memory module or the peripheral such as I/O peripheral, must be delivered through the shared bus, leading to contention delays. This becomes the bottleneck as the number of processing cores increases. In this case, the multi-core architecture is not scalable.

An alternative method is network-on-chip (NoC) [6][7]. It employs a packet switching communication network to connect the separate processing cores. As shown in Figure 1.1, each processing core connects through a router to the network. Then the communication packets can be delivered across the network with the routing traffic. In this way, NoC allows easy data sharing that a processing core can communicate with its target directly. This promotes the many-core architecture. Compared with the multi-core architecture, NoC provides faster communications with less bus contention. This potentially improves the performance and reduces the power consumption. However, the NoC design burden lies on the router architecture and the communication mechanism [8][9]. It also involves research on topology and layered protocols.

While the processor performance keeps improving, the memory performance remains the system bottleneck. High memory latency leads to expensive pro-

Figure 1.2. Performance Gap between Memory and Processor [10]

cessor stalls, and this directly degrades the overall system performance. The memory wall [11] is introduced to indicate that the performance of the system is decided by the memory speed but no longer by the processor speed. Figure 1.2 shows the processor speed against the memory speed over time. The vertical axis is the logarithmic scale to record the performance gap between the processor and the memory, and the memory performance baseline is 64KB DRAM in 1980. As shown in the graph, the speed of the processor after 1990 can improve more than 60% every year, while the memory can only improve about 7% [10]. The performance gap between the memory and the memory about 7% [10].

With the aim to alleviate the memory latency issue, several solutions have been explored, such as the multi-threading. With enough support from both the processor architecture and the OS, the multi-threading allows the switching from a thread to another concurrent thread instead of just waiting. This avoids the processor stalls caused by the memory latency. However, this requires large amounts of resources and introduces overheads. By contrast, the architectural solution is the memory hierarchy design, and the processor may still easily lose performance within the memory hierarchy. Further improvement methods mainly rely on the cache to better exploit the locality. Prefetch methods can also be employed with the aim to prepare next data or instructions for the processor ahead of time. As for embedded systems, scratchpad memory is introduced as as alternative for cache. It exploits the application behaviour and manages the memory using explicit instructions.

With a growing number of applications being integrated into modern embedded systems, it places a heavy request on memory subsystem, especially within the multi-core and many-core architecture such as GPU application [12]. As the number of processors to access a single memory module increases, memory access latency inevitably increases. Besides that, multi-core architectures are also increasingly adopted in the emerging real-time applications, such as autonomous vehicles and robotics, where the memory access latency is required to be bounded both in the worst case (i.e., time predictability) and low. With the trend of integrating more applications or employing more processors, the potential contention over memory accesses gets more severe within such architectures. This harms time predictability which is highly undesirable for real-time applications.

#### **Distributed Time-Predictable Memory Interconnect**

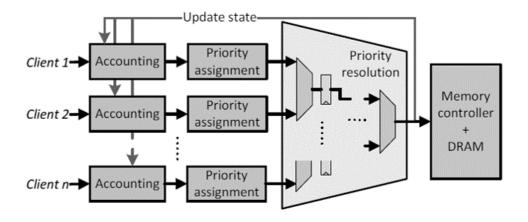

With the aim to achieve time predictability (or simply predict the timing behaviour of memory accesses), multi-core and many-core architectures typically utilise an arbitration scheme to provide timing guarantees. The potential memory arbitration schemes include time division multiplexing (TDM) scheme, round-robin scheme and priority-based schemes (e.g., static-priority arbitration). The conventional centralised implementation of an arbitration scheme is to deploy a single arbiter, allowing arbitration decisions to be made at the central location. However, as the number of processors grows, the logic size of the arbiter hardware increases, which limits the maximum synthesisable clock frequency.

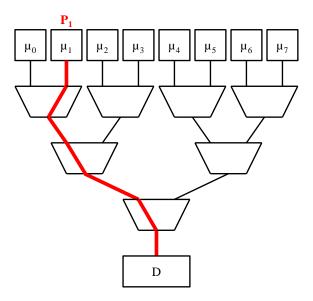

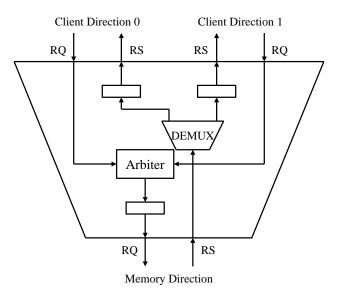

A promising approach recently investigated is to employ distributed memory interconnects that the tree-based structure with pipelined stages can break the critical path of the multiplexing into multiple shorter steps with smaller logic size. Although this introduces additional delays in terms of clock cycles, the latency across such interconnect is actually reduced that much higher synthesisable clock frequency is allowed on the distributed hardware. It scales to a large number of processors. The critical path of the distributed interconnect remains constant as it is duplicatedly constructed with the growing number of processors. In addition, pipelining is also supported.

The distributed memory interconnects can be classified as the *locally arbitrated* interconnect and the *globally arbitrated* interconnect. The *locally arbitrated* interconnect is simply constructed upon a distributed binary arbitration tree which multiplexes the memory requests from processors to the shared root memory module through the distributed data paths. By comparison, based on a distributed binary arbitration tree, the *globally arbitrated* interconnect integrates the global scheduling to the distributed data paths.

In general, the *locally arbitrated* interconnect allows the average-case latency to be much lower than the worst case, however making time predictability challenging. By contrast, the *globally arbitrated* interconnect essentially limits the average-case behaviour to be similar to the worst case, facilitating the timing behaviour analysis. However, the processor utilisation within such architecture is potentially reduced, degrading the overall system performance. Besides that, the *globally arbitrated* interconnect requires complex scheduling as well as strict coordination, potentially suffering synchronisation issue. The detailed analysis is shown in following research.

### 1.1 Research Questions

The focus of this research is to explore the timing behaviour of the multicore architectures with shared distributed memory interconnects and improve the distributed time-predictable memory interconnect for multi-core architectures.

As multi-core architectures are increasingly being adopted for real-time applications, the execution time of such application is required to be both bounded in the worst case and low. However, the multi-core architecture is typically designed for good average-case performance, and the resource contention within such architecture is inevitable. It potentially causes contention over memory accesses across the multi-core architecture, and this complicates the analysis of memory access latency which is the main part forming the overall program execution time. With the deployment of distributed memory interconnect, the analysis of memory access behaviour across the multi-core architecture further complicates that such architecture appears to be more sensitive to the resource contention due to the introduction of the tree-based structure.

It is to be noted that this research focuses on the memory accesses issued by processors to access the shared memory within the multi-core architecture. In this case, memory access latency is the latency of memory request issued to access the shared memory across the multi-core architecture, including the time consumed across the memory access path, the time consumed for the response of the shared memory, and the time consumed due to the resource contention within the shared memory multi-core architecture.

Based on the above analysis, the following research questions are related and formed. First, it is crucial to guarantee time predictability in multi-core architectures for real-time applications. In this research, time predictability requires to statically analyse the timing behaviour of memory accesses across the multi-core architecture and bound the worst-case memory access latency within such architecture. Achieving time predictability within the multi-core architecture is challenging that software components or tasks can contend for the shared hardware resources, such as memory modules, with varying status. Such contention gets more severe with the deployment of distributed memory interconnect due to the tree-based structure. This complicates timing behaviour analysis and harms time predictability, leading to the first research question Q1 which is summarised as follows.

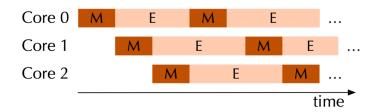

Q1: Can analytical method predict timing behaviour of memory accesses and bound the worst-case memory access latency in multi-core architectures with shared distributed memory interconnects?

Second, the multi-core architecture inevitably leads to contention over memory accesses. Within the multi-core architectures with shared distributed memory interconnects, the contention to the shared hardware resources, especially the contention to the overlapped data paths across the tree-based interconnect, causes resource sharing issue that memory requests are not fairly served. This potentially causes substantial varying memory access latency. Wide variation of memory access latency leads to wide fluctuation of the overall system performance that the processor can stall with the varying memory response time. In this case, conservative system design has to be considered with pessimistic timing assumptions. This leads to the second research question Q2 which is summarised as follows.

Q2: Can multi-core architectures with shared distributed memory interconnects be modified at the hardware level to reduce variation of memory access latency? Third, with the trend of integrating more applications or employing more processors into a system, memory workloads within the multi-core architecture potentially keeps increasing, and the contention over memory accesses aggravates. This increases memory access latency, and high memory access latency degrades the overall system performance. Within the multi-core architecture with the distributed memory interconnect, the architectural bottleneck is either the shared memory resource or the shared tree-based interconnect which connects multiple data paths however overlapped at the tree root. This leads to the third research question Q3 which is summarised as follows.

Q3: Can multi-core architectures with shared distributed memory interconnects be improved by architectural enhancement for increasing memory workloads?

This research attempts to explore a relevant topic in hardware-software integration. It addresses resource contention and time predictability across the multi-core architectures with shared distributed memory interconnects, contributing towards real-time multi-core systems. It is to be noted that the timing behaviour analysis of memory accesses involves the integration of the shared root memory module into the multi-core architecture. The efficiency of such memory resource directly impacts memory access latency which can be harmed by either varying response time or high response time of this shared memory module. In this case, improvement on independent memory module or memory subsystem is equally necessary.

### **1.2** Thesis Structure

The reminder of the thesis is structured as follows.

Chapter 2 presents the literature review related to this research. First, it provides the background knowledge and basic concepts of real-time systems. Second, memory or memory subsystem is reviewed with the focus on time predictability and memory latency, including cache, prefetch and scratchpad memory. Third, the shared memory multi-core architecture is reviewed, including memory arbitration schemes and distributed memory interconnects. It also includes a review of state-of-the-art methods to alleviate resource contention within the shared memory multi-core architecture.

Chapter 3 presents the basic architecture and analyses the given research questions. Afterwards, the research hypothesis is summarised based on the problem analysis.

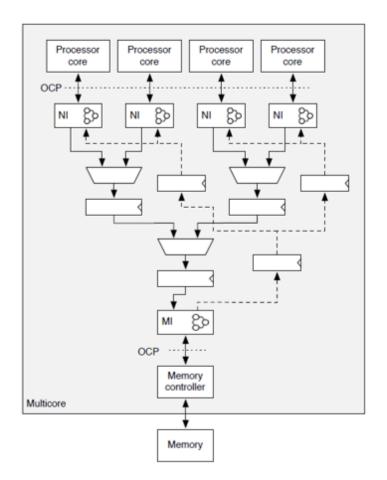

Chapter 4 analyses timing behaviour of the multi-core architectures with shared distributed memory interconnects. First, it proposes the generic analytical flow to predict the timing behaviour of memory accesses by fully exploring the architectural features and statically bound the worst-case memory access latency. This aims to solve the research question Q1. Second, it continues to explore and analyse timing behaviour of the *locally arbitrated* interconnect and the *globally arbitrated* interconnect.

Chapter 5 aims to solve the research question Q2. It analyses varying memory access latency across the multi-core architectures with shared distributed memory interconnects and proposes an architectural enhancement to reduce variation of memory access latency. Experimental results from hardware simulations and FPGA implementations evaluate the effectiveness of the proposed work.

Chapter 6 aims to solve the research question Q3. It analyses resource contention over the multi-core architectures with increasing memory workloads and proposes an architectural extension of the tree-based interconnect to enhance the multi-core architecture. Experimental results from FPGA implementations with synthetic memory workloads and real-world benchmarks evaluate the effectiveness of the proposed work.

Chapter 7 draws the concluding remarks and proposes the future work.

## Chapter 2

## Literature Review

This chapter presents literature review related to this research. Section 2.1 provides background knowledge and basic concepts of real-time systems, including time predictability and worst-case execution time (WCET). Section 2.2 reviews memory and memory subsystem with the focus on time predictability and memory latency. The potential improvement methods are also reviewed, including cache, prefetch and scratchpad memory. Section 2.3 presents the review of shared memory multi-core architectures. It includes time-predictable memory interconnects and critical resource contention within multi-core architectures. Afterwards, Section 2.4 summarises and discusses these contents based on the given research questions.

### 2.1 Real-Time System

Real-time systems must guarantee the system response within specified time constraints thus to provide accuracy and reliability. The term deadline defines the time that the system must produce response results. Real-time systems can be classified by the consequence of missing the deadline [13] as hard (HRT) where deadline miss with late delivered system response causes disastrous consequences, firm (FRT) where deadline can be occasionally missed but there is no benefits with the late delivered system response, and soft (SRT) where deadline can be occasionally missed and the system response can be late delivered.

Applications with HRT requirements, such as the flight control system, must guarantee no deadline misses. By contrast, applications with FRT or SRT requirements can have an upper limit on the number of deadline misses. For example, radio applications (in terms of software) with HRT requirements have to guarantee no deadline misses to prevent significant quality degradation. By contrast, video decoding applications with SRT requirements can tolerate occasional deadline misses. There will be the modest reduction of video quality with deadline misses as the consequence. In addition, applications can have both HRT requirements and SRT requirements [13].

As the nature of real-time systems, it is crucial to guarantee time-predictable behaviour. It is to determine the range of time that a task executes for and thus prove that a task can meet the time constraints. The common method is to predict the worst-case execution time (WCET) of the task. Figure 2.1 shows task execution times. The shortest execution time is the best-case execution time (BCET), and the longest is WCET. As for the applications with hard real-time requirements, WCET has to be equal to or less than the deadline. WCET analysis actually bounds the limit of execution times, and the related analysis is both application-dependent and hardware-dependent [14].

WCET can be determined by static analysis. In general, it is to analyse the target model to determine the critical execution path and apply timing factor

Figure 2.1. Task Execution Time [15]

to the path flow [16]. However, with complicated system architecture, the accurate timing model can be difficult to predict precisely due to the limited predictability of the critical components, such as cache and DDR DRAM. This can also be aggravated by varying state of the system. Therefore, the upper bound on the WCET has to be determined as estimated worst case execution time [16]. In this case, the static analysis leads to pessimistic results.

An alternative is to determine WCET by dynamic time analysis. It is to measure the end-to-end execution times from a number of executions [15]. This actually determines the minimal observed execution time and maximal observed execution time with test case. As shown in Figure 2.1, measurements potentially overestimate BCET and underestimate WCET. Even though the measurement-based method is not that safe for the HRT systems, it is commonly applied in most industry scenarios. The potential measurement can be either to test with the worst-case initial state (determined from execution flow), or to exhaustively test all possible system states.

Based on WCET, task execution is also influenced by the interference or the blocking effects in the system. For example, the execution of the task can be blocked by other tasks due to the shared resources. This contributes to the worst-case response time, and the worst-case response time of the task has to be guaranteed less than the deadline. Further system design or analysis requires effective scheduling algorithm, such as fixed priority scheduling [17], to order the usage of systematic resources and guarantee the time constraints.

### 2.2 Memory

Within a system, memory or memory subsystem is to temporarily store the instructions and data that are currently being used or likely to be used by the processor. The hardware module random access memory (RAM) can be both read and written to support the varying instructions and data. The contents in the RAM module can be maintained as long as the power is supplied. It is commonly employed to compose the memory subsystem. RAMs are differentiated by the mechanisms in maintaining their contents. The dynamic RAM (DRAM) uses a single MOS transistor and capacitor to store a single bit data. It has to regularly refresh its content, or the charge leak may lead to the loss of the data. By contrast, the static RAM (SRAM) uses a single flip-flop to store a single bit data. As the SRAM does not have to be refreshed, its access time is close to its cycle time.

Compared with DRAM, SRAM is much faster. However, SRAM is much more expensive than DRAM in terms of the required number of transistors to store data. For example, SRAM with the flip-flop circuit which requires 6 transistors to store a single bit data, while DRAM requires only 1. In this case, a single DRAM module can have much more capacity than a single SRAM module with the same number of transistors. Due to the trade-off between the performance the economical considerations, DRAM is constructed as the

Figure 2.2. DRAM Organisation [18]

primary memory. Modern systems employ the double data rate synchronous DRAM (DDR DRAM) technology. DDR DRAM performs memory access in lower cycle time and provides a higher data transfer rate. For example, DDR3-800E can support 10ns cycle time and 800 megabytes per second transfer rate, with the capacity up to 16 gigabytes.

Figure 2.2 show the modern DRAM organisation. DRAM stores data in a number of banks. Each bank contains a memory array of rows with columns. To access DRAM, the requested bank is first activated. Then the requested row will be selected and loaded into the row buffer which only stores the most recently accessed row. After that, the read or the write can be operated to the columns in the row buffer. Finally, the row in the buffer will be stored back to the memory array. In addition, all the banks will be refreshed regularly to maintain the stored data by the pre-charge.

Due to the latency required to select a row and to pre-charge the row, the internal controller is designed to leave the selected row open for next accesses [19]. This benefits the performance for the task to access sequential data, however it harms the time predictability. The access time to the primary memory depends on the previous access. It is variable that the same row access requires much less time than the access to a different row. Besides that, the bus turnaround between memory read operation and memory write operation increases the latency. It also requires additional delays if the internal controller issues the pre-charge at the time.

With the analysis above, considering the interference between tasks, DRAM module provides the varying access latency that fluctuates with memory access patterns. This unpredictable timing seriously impacts real-time systems. It is possible to bound the latency of every single memory access with the pessimistic worst-case assumptions. However, this definitely leads to very pessimistic timing results. The efficiency of memory subsystem drops, and execution time increases.

#### **Time-Predictable Memory Access**

Chang et al. [20] explores latency variation of DRAM with memory operations caused by access patterns. It also proposes Flexible-LatencY DRAM with the mechanism to balance latency variation across DRAM banks. This also reduces DRAM access latency which suffered from related memory operations. Alternatively, Hassan et al. [21] proposes Reduced Latency DRAM. This type DRAM employs the SRAM-like non-multiplexed address mode instead of the row and column selection. Besides that, the pre-charge is handled by the automatic hardware mechanism rather than the internal controller. Compared with the conventional DRAM, Reduced Latency DRAM provides much lower access latency [22]. It also facilitates the design of time-predictable memory controller. On the other hand, Akesson et al. [23] develops predictable memory access pattern. It defines the memory accesses into read group, write group, and refresh group. The read or write group only contains the read or write burst to the corresponding banks in sequence. Then the memory groups can be scheduled in pipelined manner referring to the memory operations. Besides that, an amount of additional delay is also imposed between accesses to the same bank. This eliminates the interference among memory accesses, and guarantees a maximum latency bound. Based on this idea, Akesson et al. [23] also develops the predictable memory controller Predator.

Similarly, Paolieri et al. [24] proposes the design of analysable memory controller. It exhaustively analyses the upper bound of each task. Then this controller schedules HRT task considering the worst-case interference and non-HRT task with low priority to eliminate the interference. It actually allocates memory accesses with enough bandwidth to guarantee the time bound. In addition, Goossens et al. [25] develops memory controller to schedule concurrent memory requests by exploiting memory bank parallelism to reduce conflicts. Based on TDM scheme, the bandwidth is shared according to task criticality level at the cost of non-critical task performance.

#### Memory Latency

Memory latency becomes the major bottleneck in system performance. It potentially leads to expensive processor stalls, and this effect has been aggravated by modern digital products, especially those computationally intensive applications with increasing demand to access high bandwidth data.

To reduce the memory write latency is not a fundamental problem. Methods such as write buffer can be employed to reduce the latency. The processor

Figure 2.3. Memory Hierarchy

writes the data with address into the buffer. Then the memory write process is completed from the perspective of the processor. It can continue execution with no stalls. By contrast, to reduce the memory read latency is the real challenge. The processor has to wait for the requested data ready before continuing any execution.

The potential solution is multi-threading. With enough support from processor architecture and OS, multi-threading allows the processor switching from a thread to another concurrent thread instead of just waiting. This avoids the expensive processor stalls caused by the memory latency. However, multithreading requires a large amount of resources and introduces overheads. It may not suit embedded systems.

Alternatively, the design of memory hierarchy is employed to maximise the overall system performance at an acceptable cost. Figure 2.3 shows the general memory hierarchy, with fast, small and expensive cache module at the top, and slow and large primary memory at the bottom. However, the processor still easily loses performance within the memory hierarchy. Further improvement mainly relies on the cache methods to better exploit the locality. In addition, the prefetch methods can also be employed to prepare next data or instructions for processor ahead of time. As for embedded systems, scratchpad memory is introduced as as alternative for cache. The intuition is

to exploit the application behaviour and manage the memory using explicit instructions.

### 2.2.1 Cache

Cache is constructed using the fast and expansive SRAM in small size. It stores the copies of likely to be used contents from the primary memory, delivering data and instructions to the processor with much faster access time.

Programs follow principle of locality either temporally or spatially. The temporal locality is that if a data location is accessed, it tends to be accessed again very soon. The spatial locality is that if a data location is accessed, its nearby locations tend to be accessed in the near feature. Therefore, the processor tends to access data and instructions from cache more frequently than from the primary memory. This bridges the performance gap between the primary memory and the processor.

The cache operation is controlled by its automatic hardware mechanism. It stores data in a number of blocks or lines. A single cache block can be divided into the valid bit, the tag field and the data field. The valid bit, with the value either 0 or 1, explicitly indicates whether the data is valid or not. The tag field is used to identify the current data. The data field stores a single word or more.

To read data from cache, the processor requests the data with address. The address (physical address) consists of the tag field, the index field and the offset field. The index field is used to locate a specific block from the cache. The tag field is used to be compared with the cache block tag field. If there is a match with the valid flag, the located cache block is desired. Then the word can be selected from the cache block field using the address offset field.

Cache organisation can be classified according to the schemes in placing cache blocks. If a cache block can only be placed at an exact location, the cache is direct-mapped. If a cache block can be placed at any location, the cache is fully-associative. Otherwise, the cache is set-associative, and the cache block can be placed at a set number of locations. For example, two-way setassociative cache provides two locations to place a single cache block. This also introduces the degree of associativity. The direct-mapped cache is oneway set-associative, and the fully-associative cache is n-way set-associative where n is the total number of its cache blocks.

To write data to cache, the processor supplies the data with address. Then the cache checks for the matching cache block with valid bit 0. It stores the data into this cache block and sets valid bit to 1. However, if the cache block is occupied with the valid flag, the situation differs. As for direct-mapped cache, there is no choice but to discard the original data in the block and replace with the new data.

By contrast, there are several replacement policies for fully-associative and set-associative cache when there is no spare block in the cache or in the set. For example, the random policy randomly discards a cache block thus to store the new data. The first-in-first-out (FIFO) policy is to loop through possible cache blocks, and the data stored earliest will be discarded first. An alternative is the least recently used (LRU) policy. It tracks relative order that cache blocks are accessed. The block which has not been accessed for the longest time will be discarded first. In addition, there are also the bit pseudo LRU policy with an additional most recently used (MRU) bit for each cache block, and the tree-based pseudo LRU policy with binary decision [26].

Figure 2.4. Cache Hierarchy

In general, processor issues requests to cache. If desired data is in the cache, it provides good runtime efficiency. If not, cache miss occurs. The processor has to wait for the data transfer delays from primary memory to cache as miss penalty. The miss rate expresses the ratio of cache accesses results in a miss. With high cache miss rate, memory subsystem performance degrades. The compulsory miss occurs in cold starting with an empty cache. The capacity miss occurs when cache is not large enough to store all useful data. The conflict miss occurs in direct-mapped cache or set-associative cache when a useful cache block is discarded but later desired. With the analysis above, both cache organisations and cache replacement polices impact the memory performance [27]. Further improvement is to optimise cache utilisation by better exploiting the principle of locality.

### Cache Optimisation

The architectural optimisation is to comprehensively combine the above aspects. It is to employ multiple levels of caches to structure the cache hierarchy, such as Intel i7 processor with 3 levels as shown in Figure 2.4. For example, the first level employs separate direct-mapped caches in parallel. Although there can be conflict misses due to the lack of associativity, direct-mapped cache provides fastest access as it requires merely the time to access SRAM module. By contrast, a next level is with higher associativity. It is slower and larger to void misses, considering miss penalty between on-chip and off-chip. The cache coherence can be tracked by the snooping or the directory-based scheme.

Alternatively, compiler can improve the performance of the application program by well exploiting the memory hierarchy features with no hardware modifications. It is the most effective method to minimise cache misses and develop data reuse possibility [28]. For example, loop transformation can optimise the data access thus to improve the temporal locality. Then the iteration executions within a loop nest will be optimised but not affecting the execution results. It also provides good data parallelism. The potential methods include loop permutation to exchange the execution order of inner loops in a loop nest, loop fusion to merge separate loops, and loop fission to reversely split a single loop. In addition, loop tiling [16] is to split a loop to iterate over several smaller tiles of data with the array size to fit cache. It significantly improves data efficiency that the data can be more repeatedly reused rather than repeatedly reloaded.

On the other hand, data transformation optimises data layout thus to improve the spatial locality. It actually reorganises data to better fit into cache to reduce conflict misses. For example, inter array padding [29] is to insert unused pads between arrays thus to separate the base addresses, and the pad size is dependent on the array size. This can void cross interference. In addition, data copying [30] is to copy non-contiguous data into consecutive locations. Although it requires necessary processor overheads, data copying can avoid self interference. This can improve blocked algorithm and guarantee data reuse in tiles. Panda et al. [31] addresses dynamic memory allocation with the integration of memory architecture and processor register. It models memory access and optimises data organisation.

Although cache improves the average-case performance for general purpose applications, it provides unpredictable access time. The execution time even varies for multiple runs of the same program. WCET does not benefit from the employment of cache due to the pessimistic worst-case assumptions. The potential solution is cache partitioning. It divides the cache in partitions, and then assigns specific partitions to tasks exclusively. This reduces interference between tasks. For example, Liedtke et al. [32] reduces cache contention with OS support. It utilises page colouring to partition set-associative cache among applications, and each application is reserved with a partition of cache.

Alternatively, contention locking is to flag specific contents as locked to prevent these contents from being replaced. For example, Aparicio et al. [33] develops instruction locking based on integer linear programming. It analyses a single task and interference among tasks to dynamically load and lock the most relevant cache blocks. Arnaud et al. [34] divides a task into partitions. It exclusively assigns and locks each task partition to a cache partition. Similarly, Vera et al. [35] develops a complier framework for data cache. It eliminates inter-task interference with cache partitioning and ensures predictable intra-task interference with cache locking. This alleviates cache unpredictability and reduces the worst-case memory access time.

In addition, embedded systems also employ SRAM module directly for special purposes, such as FIFO array. This introduces software-managed cache. It is to disable the automatic hardware caching mechanism and explicitly manage the cache operation by software. For example, Hallnor et al. [36] develops indirect index cache. With the aim to avoid tag search, it uses the pointer with a simple hash table to locate cache block. This allows the the fully-associative memory structure to be managed by software with less time. Miller et al. [37] develops a software system that allows SRAM module to be automatically managed as cache. Even though the software managed cache requires additional complexity with overheads, it guarantees time predictability that the memory access is with no cache miss.

### 2.2.2 Prefetch

Prefetch is to prepare next data or instructions ready before they are requested by processor thus to hide long memory latency. Software prefetch is supported by the compiler to appropriately insert explicit instructions at runtime. This requires the application program knowledge. A similar prefetch method is to pre-execute a piece of specific program thus to support the primary program. Obviously, it is difficult to apply for general applications. By contrast, hardware prefetch is to observe and predict future data or instructions, and then fetch the corresponding blocks sufficiently far ahead of the execution. It requires extra memory module, such as buffers, to store the prefetched blocks without polluting cache contents.

If the prefetched block matches the memory request, it significantly reduces the memory access latency. This can benefit BCET. However, the prefetched blocks can be useless, or sometimes the prefetched contents can fail to be ready in time. In this case, prefetch provides unpredictable behaviour. WCET does not benefit from the employment of prefetch due to the pessimistic worst case assumptions. Besides that, prefetch has to overlap with the demand memory operation. As a speculative execution utilising spare memory bandwidth, it is necessary to keep the demand memory access with no stalls. If prefetch interferes with memory execution, it instead degrades the memory performance. The following section presents potential prefetch schemes.

### Locality-based Prefetch

The simplest prefetch scheme is tagged prefetch [38]. It is to prefetch the next block when the current block is accessed. By contrast, Jouppi et al. [39] proposes stream prefetch. It is to prefetch the next consecutive blocks if the current blocks are accessed in sequence. For example, if blocks with addresses n - 2, n - 1 and n are accessed, the blocks with address n + 1 and n + 2 will be prefetched. If a prefetched block is accessed, a new one will be prefetched. Stream prefetch performs well for instruction. It is ideal for program which follows purely sequential access pattern. However, programs trend to access multiple data arrays rather than only a single data array even in a single process. These interleaved data arrays interference with steam prefetch, polluting prefetch buffer contents. Palacharla et al. [40] develops multiple stream prefetch buffers in parallel. It allows interleaved data arrays to be prefetched concurrently for programs with regular access patterns.

Based on this, Fu et al. [41] proposes stride prefetch. It is to prefetch the next consecutive blocks with an arbitrary stride. The stride is the number of successive array elements, and it can be detected by a branch prediction table and a lookahead program counter [42]. The table tracks the access pattern which is dynamically updated by the branch prediction relying on the processor state and branch history. The counter increments the lookahead amount for the consecutive data array, and sets to 1 for instruction. Prefetch addresses are then decided by adding the lookahead mount to the last addresses. Alternatively, the stride can be decided using block addresses [43]. A reference prediction table is employed to record last accessed addresses.

Then the stride will be decided by calculating the distance between the addresses. When a single blocked is loaded, the first future block address will be decided as n + d where n is the current block address and d is the stride.

### Pointer-based Prefetch

The steam prefetch and the stride prefetch rely on good data locality, and the performance is limited to blocks with closeby addresses. However, it is difficult to deal with data on irregular accesses, such as large jumps in addresses. Such data access pattern is to follow pointers in a linked data structure. It is a common way to build a large data structure, such as database. Nodes in the data structure are linked together through pointers. A pointer at a node points to another node, and the new address is decided by calculations on the current node address. In this way, a linked data structure can be considered as a chain of nodes which are dependent of each other.

A prefetch scheme is to straightforward utilise the natural pointers which already exist at nodes [44]. It is to identify the data structure and discover the way to traverse the data structure by the complier. Then the prefetch instructions will be inserted where the node addresses are available and prefetch all possible future nodes. From the perspective of the compiler, it is actually to prefetch the elements to be executed at the start of an iteration. In addition, Roth et al. [45] employs additional artificial pointers at nodes to link non-successive nodes. For example, root jumping is to deploy root pointers between the roots of different data structures which benefits iterations.

Similarly, content-directed prefetch [46] discovers potential pointers by hardware and fetches all possible future blocks. The basic logic is that the address of a block with the pointer will possibly be used to calculate the addresses

| Miss Address | Next Probable Address  |                        |  |

|--------------|------------------------|------------------------|--|

| Addr 1       | 1 <sup>st</sup> P Addr | 2 <sup>nd</sup> P Addr |  |

| Addr 2       | 1 <sup>st</sup> P Addr | 2 <sup>nd</sup> P Addr |  |

|              | 1 <sup>st</sup> P Addr | 2 <sup>nd</sup> P Addr |  |

| Addr N       | 1 <sup>st</sup> P Addr | 2 <sup>nd</sup> P Addr |  |

Figure 2.5. Markov Prediction Table [47]

of future blocks which are pointed to. These future addresses are definitely within the range of the same data structure and share the common base addresses. The effectiveness of content-directed prefetch is affected by the prediction accuracy, and the compiler can help to decide the most beneficial blocks at runtime.

#### **History-based** Prefetch

As for more irregular accesses with no particular pattern, the prefetch scheme is to utilise the access history. For example, Joseph et al. [47] employs Markov prediction. It utilises miss history to obtain correlations between addresses, provides possible future addresses and prioritises these blocks. Figure 2.5 shows the correlation table that two temporally successive miss addresses can be paired with each other. The first address of a pair is the parent, and the latter is the child. As a parent address may have any number of child addresses, the parent is considered as the key to select the child afterwards. When a particular address is accessed, its correlative addresses are decided by checking the history with the table. Then the blocks will be prefetched in sequential queue according to their weight. Markov prediction performs well for programs with repeated irregular accesses, but the prediction is only made with limited history of current parent addresses.

Figure 2.6. Global History Buffer [48]

By contrast, Nesbit et al. [48] develops global history buffer to improve the accuracy of the correlation. Rather than storing fixed amount of history for each address, global history buffer only stores the history for the most recent miss addresses. As shown in Figure 2.6, history addresses are stored indirectly. The index table is accessed by a key, and it indexes global history buffer through a hash map. The buffer is to store the most recent miss addresses. The link pointer is also employed to link each buffer block with the same key from the index table. In this way, these related addresses are chained. The key can be selected as a piece of related information which is useful in these links, such as a miss address or the program counter. This allows better predictions with more complete knowledge of the addresses.

In addition, Srinath et al. [49] proposes feedback-directed prefetch to dynamically utilise the access history. It monitors the last prefetch performance thus to adjust the current prefetch execution. For example, it can tack whether the prefetched blocks are useful. If the ratio of the useful blocks to the total blocks is high, the number of blocks to prefetch for a next time can be increased. If low, the number can be reduced or even stops with an unacceptably high number of useless blocks. The feedback-directed method can support any prefetch scheme above. It contributes to hybrid prefetch scheme. For example, stride prefetch can be improved to adjust its prediction region

Figure 2.7. Scratchpad Memory Address Configuration [51]

at runtime. If necessary, it can predict addresses at n + 2d, n + 3d or even n + 4d ahead of program execution rather than just n + d.

## 2.2.3 Scratchpad Memory

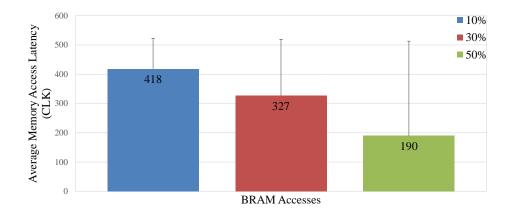

Scratchpad Memory (SPM) is introduced to embedded systems as a design alternative for cache [50]. It is small high speed on-chip SRAM operated by software. Similar to L1 cache, SPM resides on-chip locally to the processor. It is to temporarily store data or instructions for processor with fast access. Compared with cache, SPM only contains data field, with no tag field or the tag comparator to acknowledge hit or miss. SPM operation is in full control by software.