**Doctoral Thesis**

# Design of Efficient Symmetric-Key Cryptographic Algorithms

by Kosei Sakamoto

March 2023

Graduate School of Applied Informatics University of Hyogo

### Abstract

Cryptography plays a crucial role in the modern internet communication system. Especially, thanks to the development of communication technology, we can see variety of its applications everywhere, and the importance of cryptography is getting more and more enhanced. The main role of cryptography, especially symmetric-key cryptography which is treated in this thesis, is to provide data confidentiality and integrity by a block cipher, stream cipher, hash function, message authenticated codes and authenticated encryption scheme.

With the rapid development of communication technology for a latest few decades, such symmetric-key cryptographic algorithms need to meet not only the security requirement but also implementation requirement on resource-constrained devices such as RFIDs and medical devices. Studying on such resource-constrained algorithms is called *lightweight cryptography*, and have get the most attention in the field of symmetric-key cryptography for the latest decade. Another area of interest is designing ultra-high throughput cryptographic algorithms for the rapid advancement of mobile communication systems like 5G and beyond 5G. In these systems, it is necessary to design ultra-high throughput and high-security cryptographic algorithms due to the increasing of the data transmission speed.

This thesis is dedicated to the design of symmetric-key cryptographic algorithms, including a lightweight block cipher, lightweight tweakable block cipher, block cipher-based low-katency pseudo-random function, and ultra-high throughput uthenticated encryption with associated data scheme. Specifically, we introduce four algorithms: a tweakable block cipher Tweakable TWINE, lightweight block cipher WARP, lightweight PRP Orthros, and an ultra-high throughput AEAD Rocca and investigate how to design them along with the background of why these new algorithms is necessary.

### Table of Contents

| 1 | Intr | oductio                   | n                                                                  | 1        |

|---|------|---------------------------|--------------------------------------------------------------------|----------|

|   | 1.1  | Motivation and Background |                                                                    |          |

|   |      | 1.1.1                     | Applications and Requirements of Efficient and Lightweight Crypto- |          |

|   |      |                           | graphic Algorithms                                                 | 2        |

|   | 1.2  | Our C                     | Contribution and Outline                                           | 3        |

| 2 | Sym  | metric                    | -Key Cryptography                                                  | 6        |

|   | 2.1  | Block                     | Cipher                                                             | 6        |

|   |      | 2.1.1                     | Modern Block Cipher Construction                                   | 7        |

|   |      | 2.1.2                     | Tweakable Block Cipher                                             | 11       |

|   | 2.2  | Authe                     | enticated Encryption                                               | 12       |

|   |      | 2.2.1                     | Construction of a Sponge-Based AEAD                                | 13       |

|   | 2.3  | Crypt                     | analysis of Symmetric-Key Cryptographic Algorithms                 | 14       |

|   |      | 2.3.1                     | Attack Models                                                      | 15       |

|   |      | 2.3.2                     | Goal of Attack                                                     | 16       |

|   |      | 2.3.3                     | Cryptanalysis Techniques                                           | 18       |

| 3 | MII  | .P-Aide                   | ed Security Evaluation                                             | 26       |

|   | 3.1  | Securi                    | ity Evaluation of Differential/Linear Cryptanalysis                | 27       |

|   |      | 3.1.1                     | Constraints                                                        | 27       |

|   |      | 3.1.2                     | Objective Function                                                 | 31       |

|   | 3.2  | Securi                    | ity Evaluation of Impossible differential Cryptanalysis            | 31       |

|   | 3.3  | Securi                    | ity Evaluation of Integral Cryptanalysis                           | 32       |

|   |      | 3.3.1                     | Constraints                                                        | 33       |

|   |      | 3.3.2                     | Objective Function                                                 | 34       |

| 4 | Twe  | akable                    | TWINE: Building a Tweakable Block Cipher on Generalized Feistel    |          |

|   | Stru | icture                    |                                                                    | 35       |

|   | 4.1  | Introd                    | luction                                                            | 35       |

|   | 1.1  | 1110100                   |                                                                    |          |

|   | 1.1  | 4.1.1                     | Organization of this section                                       | 37       |

|   | 4.2  | 4.1.1                     | Organization of this section                                       | 37<br>37 |

|   |      | 4.1.1                     | -                                                                  |          |

|   |     | 4.2.3   | Tweak Scheduling Function                                 | 39 |

|---|-----|---------|-----------------------------------------------------------|----|

|   |     | 4.2.4   | Key Scheduling Function                                   | 40 |

|   |     | 4.2.5   | Test Vectors                                              | 40 |

|   | 4.3 | Design  | n Rational                                                | 42 |

|   |     | 4.3.1   | Design Goals                                              | 42 |

|   |     | 4.3.2   | How to Design Permutation-Based Tweak Scheduling Function | 43 |

|   |     | 4.3.3   | Reducing Candidates                                       | 44 |

|   | 4.4 | Securi  | ty Evaluation                                             | 46 |

|   |     | 4.4.1   | Differential/Linear Attack                                | 46 |

|   |     | 4.4.2   | Impossible Differential Attack                            | 47 |

|   |     | 4.4.3   | Integral Attack                                           | 48 |

|   | 4.5 | Hardw   | vare Implementation Results                               | 48 |

|   | 4.6 | Conclu  | usion                                                     | 49 |

| 5 | WAI | RP : Re | visiting GFN for Lightweight 128-Bit Block Cipher         | 51 |

|   | 5.1 | Introd  | uction                                                    | 51 |

|   | 5.2 | Specifi | ication                                                   | 54 |

|   | 5.3 | Design  | n Rationale                                               | 56 |

|   |     | 5.3.1   | Branch Size and Permutation                               | 56 |

|   |     | 5.3.2   | S-box                                                     | 57 |

|   |     | 5.3.3   | Key Schedule                                              | 57 |

|   |     | 5.3.4   | Round Constants                                           | 58 |

|   | 5.4 | Securi  | ty Evaluation                                             | 58 |

|   |     | 5.4.1   | Differential/Linear Attack                                | 58 |

|   |     | 5.4.2   | Impossible Differential Attack                            | 59 |

|   |     | 5.4.3   | Integral Attack                                           | 59 |

|   |     | 5.4.4   | Meet-in-the Middle Attack                                 | 60 |

|   |     | 5.4.5   | Invariant Subspace Attack                                 | 60 |

|   | 5.5 | Hardw   | vare Performance                                          | 61 |

|   |     | 5.5.1   | Nibble Serial Architecture                                | 61 |

|   |     | 5.5.2   | Performance Results                                       | 63 |

|   |     | 5.5.3   | Round Based and Round Unrolled Designs                    | 63 |

|   |     | 5.5.4   | More Details about Hardware Implementations               | 64 |

|   | 5.6 | Softwa  | are Performance                                           | 68 |

|   |      | 5.6.1    | On 8-bit AVR Microcontrollers                                                                    | 68 |

|---|------|----------|--------------------------------------------------------------------------------------------------|----|

|   | 5.7  | On Hi    | gh-end Processors                                                                                | 68 |

|   |      | 5.7.1    | More Details of Software Implementations                                                         | 69 |

|   | 5.8  | Conclu   | asion                                                                                            | 71 |

| 6 | Ortl | nros: A  | Low-Latency PRF                                                                                  | 74 |

|   | 6.1  | Introd   | uction $\ldots$ | 74 |

|   |      | 6.1.1    | Low-Latency Encryption                                                                           | 74 |

|   |      | 6.1.2    | Our Design                                                                                       | 75 |

|   | 6.2  | Specifi  | ication                                                                                          | 76 |

|   |      | 6.2.1    | Key Scheduling Function                                                                          | 76 |

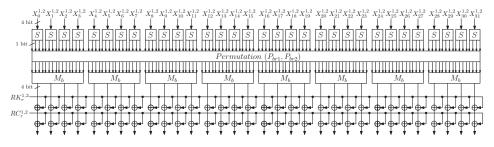

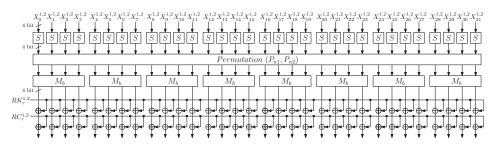

|   |      | 6.2.2    | Round Function of Branch1 and Branch2                                                            | 77 |

|   |      | 6.2.3    | Test Vectors                                                                                     | 80 |

|   | 6.3  | Design   | n Rationale                                                                                      | 80 |

|   |      | 6.3.1    | General Construction                                                                             | 80 |

|   |      | 6.3.2    | Toy Ciphers                                                                                      | 84 |

|   |      | 6.3.3    | Linear Layer                                                                                     | 87 |

|   |      | 6.3.4    | S-box                                                                                            | 92 |

|   |      | 6.3.5    | Key Scheduling Function                                                                          | 93 |

|   | 6.4  | Securi   | ty Evaluation                                                                                    | 93 |

|   |      | 6.4.1    | Differential/Linear Attack                                                                       | 93 |

|   |      | 6.4.2    | Impossible Differential Attack                                                                   | 94 |

|   |      | 6.4.3    | Integral Attack                                                                                  | 97 |

|   |      | 6.4.4    | Invariant Subspace Attack                                                                        | 00 |

|   |      | 6.4.5    | Meet-in-the-Middle Attack                                                                        | 00 |

|   |      | 6.4.6    | Yoyo and Mixture-Differential Attacks                                                            | 01 |

|   |      | 6.4.7    | Difficulty of Key-Recovery Attacks                                                               | 01 |

|   | 6.5  | Hardw    | vare Evaluation                                                                                  | 02 |

|   | 6.6  | Conclu   | usions                                                                                           | 08 |

| 7 | Roc  | ca: An ] | Efficient AES-Based Encryption Scheme for Beyond 5G 1                                            | 09 |

|   | 7.1  | Introd   | uction                                                                                           | 09 |

|   |      | 7.1.1    | Background                                                                                       | 09 |

|   |      | 7.1.2    | Our Design                                                                                       | 10 |

|   |      | 7.1.3    | Organization                                                                                     | 11 |

|    | 7.2    | Prelim   | ninaries                                              | . 111 |

|----|--------|----------|-------------------------------------------------------|-------|

|    |        | 7.2.1    | Notations                                             | . 111 |

|    |        | 7.2.2    | The Round Update Function                             | . 112 |

|    |        | 7.2.3    | Specification of Rocca                                | . 113 |

|    | 7.3    | Design   | n Rationale                                           | . 116 |

|    |        | 7.3.1    | General Construction                                  | . 116 |

|    |        | 7.3.2    | Criteria for Performance and Security                 | . 119 |

|    |        | 7.3.3    | Finding Efficient Structures                          | . 121 |

|    |        | 7.3.4    | Loading the Nonce and Key                             | . 122 |

|    |        | 7.3.5    | Generating the Ciphertext Blocks                      | . 123 |

|    | 7.4    | Securi   | ty Evaluation                                         | . 124 |

|    |        | 7.4.1    | Differential Attack                                   | . 124 |

|    |        | 7.4.2    | Forgery Attack                                        | . 124 |

|    |        | 7.4.3    | Integral Attack                                       | . 125 |

|    |        | 7.4.4    | State-recovery Attack                                 | . 126 |

|    |        | 7.4.5    | The Linear Bias                                       | . 127 |

|    |        | 7.4.6    | The State-recovery Attack Using the Decryption Oracle | . 128 |

|    |        | 7.4.7    | Other Attacks                                         | . 128 |

|    |        | 7.4.8    | No Claims                                             | . 128 |

|    | 7.5    | Softwa   | are Implementation                                    | . 128 |

|    |        | 7.5.1    | Software Implementation Results on Other CPUs         | . 129 |

|    | 7.6    | Conclu   | usions                                                | . 132 |

| 8  | Con    | clusions | S                                                     | 133   |

| Ac | cknow  | ledgem   | nents                                                 | 134   |

| Re | eferen | ces      |                                                       | 135   |

## List of Figures

| 2.1  | Overview of a block cipher.                                                      | 7  |

|------|----------------------------------------------------------------------------------|----|

| 2.2  | Overview of an iterated block cipher. $R$ denotes one round of the round         |    |

|      | function                                                                         | 8  |

| 2.3  | Overview of Feistel network                                                      | 10 |

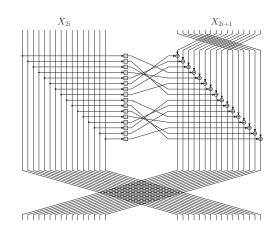

| 2.4  | Construction of type-2 generalized Feistel network.                              | 10 |

| 2.5  | Overview of a tweakable block cipher                                             | 11 |

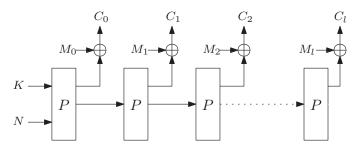

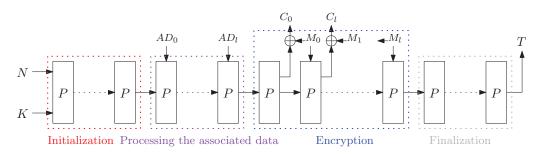

| 2.6  | Overview of an AEAD                                                              | 13 |

| 2.7  | Duplex sponge encryption                                                         | 14 |

| 2.8  | Sponge-based stream cipher                                                       | 14 |

| 2.9  | Sponge-based AEAD                                                                | 14 |

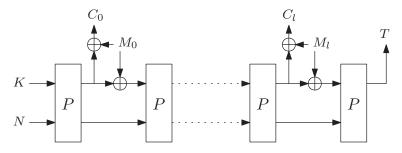

| 2.10 | Entire encryption/decryption process of AEGIS, Tiaoxin, and Rocca                | 15 |

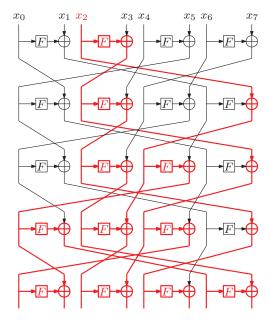

| 2.11 | $DR_2 = 5$ on type-2 GFN. Red lines mean to be affected by the input difference  |    |

|      | of $x_2$                                                                         | 22 |

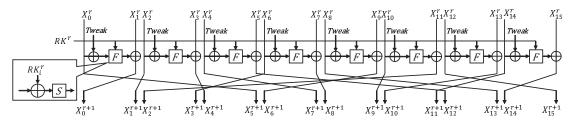

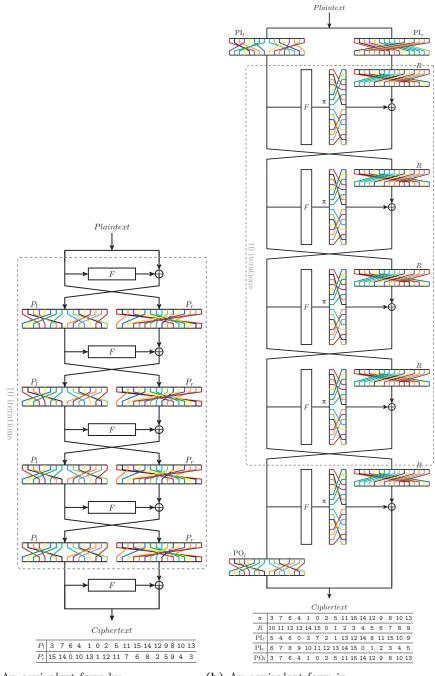

| 4.1  | Overview of Tweakable TWINE                                                      | 37 |

| 4.2  | Encryption and decryption of Tweakable TWINE $\ldots$                            | 38 |

| 4.3  | S-box S and nibble shuffle $\pi$                                                 | 39 |

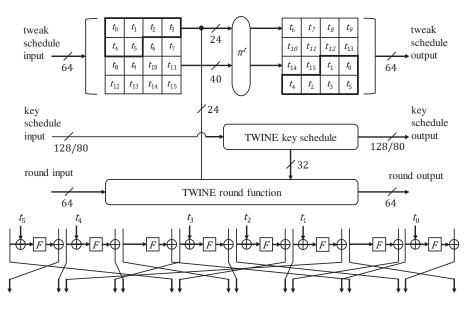

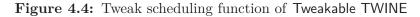

| 4.4  | Tweak scheduling function of Tweakable TWINE $\ldots$                            | 39 |

| 4.5  | Key schedules of Tweakable TWINE, for 80-bit and 128-bit keys. S-box $S$ is      |    |

|      | the same as Fig. 4.2, and key schedule constants, $CON^i$ , are described in the |    |

|      | bottom                                                                           | 41 |

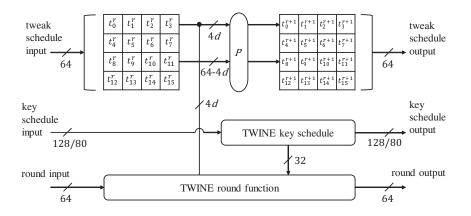

| 4.6  | Permutaion-based tweak scheduling function                                       | 43 |

| 4.7  | Permutation of $d = 4$                                                           | 44 |

| 4.8  | Positions for tweak inputs                                                       | 44 |

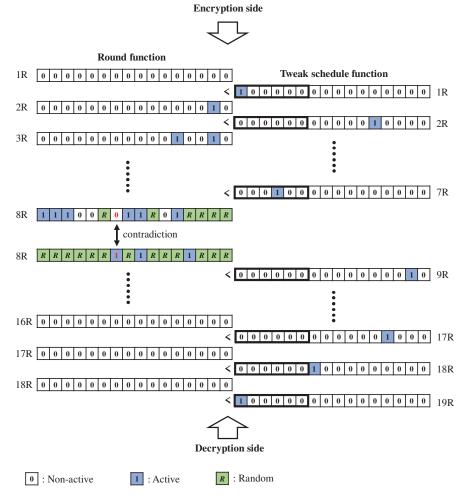

| 4.9  | 18-round impossible differential characteristic                                  | 47 |

| 4.10 | 18-round integral characteristic                                                 | 48 |

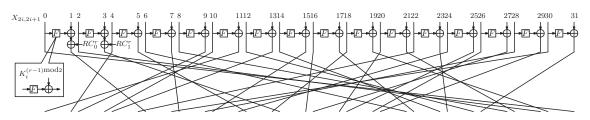

| 5.1  | Round Function of WARP                                                           | 54 |

| 5.2  | Encryption algorithm of WARP                                                     | 55 |

| 5.3  | General LBlock-like round function.                                              | 58 |

| 5.4  | Equivalent round function of WARP in LBlock-like structure                       | 58 |

| 5.5  | Alternative definition of Round Function                                         | 61 |

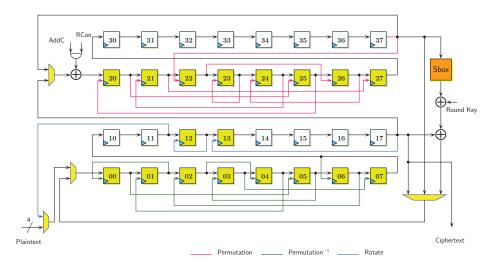

| 5.6  | Nibble serial architecture for WARP. The filter that feeds the permuted          |    |

|      | roundkey is omitted in the diagram                                               | 62 |

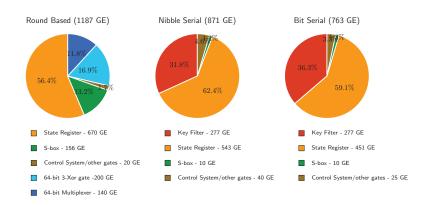

| 5.7  | Breakdown of component-wise area figures for 3 versions of WARP. Nibble                            |     |

|------|----------------------------------------------------------------------------------------------------|-----|

|      | and Bit-serial circuits require lesser scan flip-flops which require more area $\ .$               | 65  |

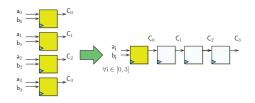

| 5.8  | Nibble to bit serial transformations                                                               | 65  |

| 5.9  | Sketch of the 3 share nibble serial architecture for $WARP$                                        | 67  |

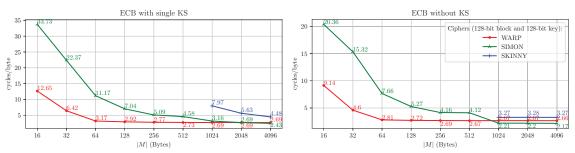

| 5.10 | Software performance of $WARP,SIMON$ and $SKINNY$ on the same processor.                           | 71  |

| 5.12 | Another equivalent form using four permutations for round functions and                            |     |

|      | eight permutations for round keys (omitted addition round constants)                               | 73  |

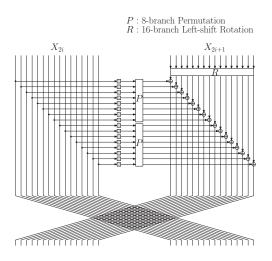

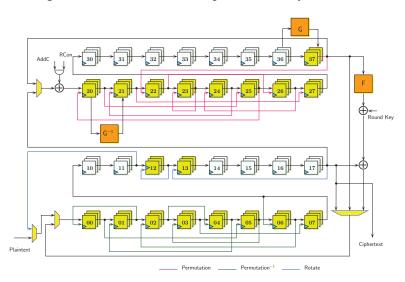

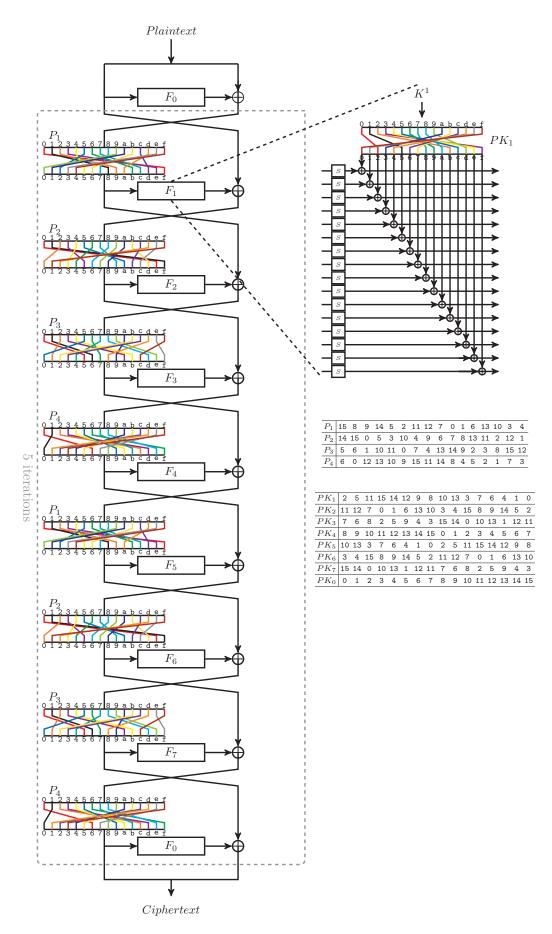

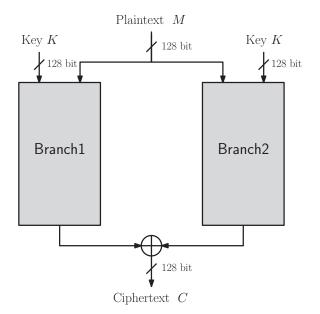

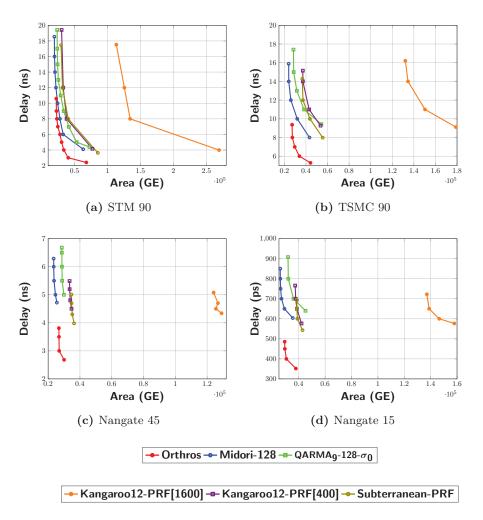

| 6.1  | Overview of Orthros.                                                                               | 77  |

| 6.2  | Algorithms of $KSF1$ and $KSF2$                                                                    | 78  |

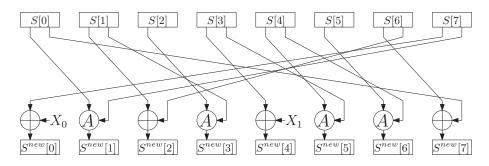

| 6.3  | The round function of Branch1 and Branch2 in the first 4 rounds. $\ldots$ .                        | 79  |

| 6.4  | The round function of Branch1 and Branch2 in the last 8 rounds. The nibble                         |     |

|      | permutation and the matrix multiplication in the last round will be omitted.                       | 80  |

| 6.5  | Algorithms of Branch1 and Branch2, where $N \in \{1, 2\}$                                          | 81  |

| 6.6  | Processing algorithm of Orthros                                                                    | 82  |

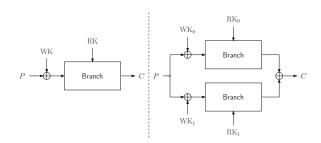

| 6.7  | (Left) The toy cipher using a single branch and (Right) that using double                          |     |

|      | branches, where WK and RK are the whitening key and round key, respectively.                       | 84  |

| 6.8  | 4-GFS. Dotted lines denote (random) round keys.                                                    | 86  |

| 6.9  | Transition of a state after applying $P_{bk1}$                                                     | 89  |

| 6.10 | The 4 active bits after the bit permutation in the first round, as marked in red.                  | 91  |

| 6.11 | The 12 active nibbles after $MatrixMul$ in the first round, marked in red                          | 91  |

| 6.12 | The 48 active bits after bit permutation in the second round, marked in red.                       | 91  |

| 6.13 | The active nibbles after bit permutation in the second round, marked in red.                       | 91  |

| 7.1  | Illustration of the round function                                                                 | 112 |

| 7.2  | The procedure of Rocca                                                                             | 114 |

| 7.3  | The process of aesenc for Intel Ice-lake.                                                          | 117 |

| 7.4  | The general construction considered of the round function in [103]. Dash                           |     |

|      | lines mean that it can be possible to be absent or present in the design $\ensuremath{\mathbbm I}$ | 118 |

| 7.5  | General construction of the round function. Dash lines mean that it can be                         |     |

|      | possible to be absent or present in the design                                                     | 118 |

| 7.6  | The round function whose $\#$ of blocks is 8                                                       | 119 |

| 7.7  | The round function whose $\#$ of blocks is 9                                                       | 120 |

| 7.8  | The round function whose $\#$ of blocks is 10.                                                     | 120 |

### List of Tables

| 4.1  | Permutation in the tweak scheduling function $\pi^t$                                                                          | 40 |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2  | The number of active S-box of each round for 32 tweak scheduling functions                                                    |    |

|      | with $d = 6$ that achieve 32 active Sbox in 19 rounds                                                                         | 45 |

| 4.3  | Lower bound on the number of differentially and linearly active S-boxes in                                                    |    |

|      | each model                                                                                                                    | 47 |

| 4.4  | Hardware results for round-based, enc-only implementations                                                                    | 49 |

| 4.5  | Hardware results for multi-round, enc-only implementation of $T-TWINE-80.$                                                    |    |

|      | (Top) ASIC (Yosys with osu018_stdcells.lib) (Bottom) FPGA (Intel/Al-                                                          |    |

|      | tera 10CL120YF780I7G, Quartus 18.1)                                                                                           | 50 |

| 5.1  | 4-bit S-box $S$                                                                                                               | 54 |

| 5.2  | Shuffle $\pi$ on 32 nibbles                                                                                                   | 54 |

| 5.3  | Round constants (listed in hexadecimal)                                                                                       | 55 |

| 5.4  | Test vectors                                                                                                                  | 56 |

| 5.5  | Four equivalent classes of 32-branch permutations with 9-round full diffusion [73].                                           | 57 |

| 5.6  | Lower bounds on the number of Active S-boxes for WARP and four permuta-                                                       |    |

|      | tions of $\pi'_0(x)$ , $\pi'_1(x)$ , $\pi'_2(x)$ , and $\pi'_3(x)$                                                            | 57 |

| 5.7  | The lower bound for the number of differentially and linearly active S-boxes                                                  |    |

|      | in the single-key setting                                                                                                     | 59 |

| 5.8  | Comparison of performance metrics for serial implementations synthesized                                                      |    |

|      | with STM 90nm Standard cell library. Figures separated by / indicate $$                                                       |    |

|      | corresponding metrics for encryption/decryption. *Synthesized with the IBM $$                                                 |    |

|      | 130 nm process/Power at 100 KHz $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                       | 63 |

| 5.9  | Comparison of performance metrics for round based implementations synthe-                                                     |    |

|      | sized with STM 90nm Standard cell library (1R, 2R, 4R refer to 1, 2, and 4 $$                                                 |    |

|      | round unrolled circuits).                                                                                                     | 64 |

| 5.10 | Comparison of performance metrics for serial implementations synthesized                                                      |    |

|      | with STM 90nm Standard cell library. (RB denotes round based circuit,                                                         |    |

|      | 3s, 4s denotes circuits with 3, 4 shares respectively) *Synthesized with the                                                  |    |

|      | UMC 180nm process/Power at 100 KHz. **Synthesized with the IBM 130nm $$                                                       |    |

|      | process/Power at 100 KHz                                                                                                      | 67 |

| 5.11 | Different performance characteristics of $WARP$ on 8-bit AVR                                                                  | 69 |

| 5.12 | Performance of block ciphers (128-bit block and 128-bit key) on 8-bit AVR $% \left( 128-128-128-128-128-128-128-128-128-128-$ | 70 |

|      |                                                                                                                               |    |

| 5.13 | Software performance profile of $WARP$ with various message length (including                                     |     |

|------|-------------------------------------------------------------------------------------------------------------------|-----|

|      | the time took by packing/unpacking messages)                                                                      | 71  |

| 6.1  | S-box in Branch1 and Branch2                                                                                      | 77  |

| 6.2  | Specification of the round constants $RC_r^1$ and $RC_r^2$                                                        | 79  |

| 6.3  | Bit permutation $P_{bkN}$ for key scheduling $KSFN$ , where $N \in \{1, 2\}$                                      | 82  |

| 6.4  | Bit permutation $P_{brN}$ for round function Branch N, where $N \in \{1, 2\}$                                     | 83  |

| 6.5  | Nibble permutation $P_{nN}$ for round function <b>Branch</b> $N$ , where $N \in \{1, 2\}$                         | 83  |

| 6.6  | Test vectors for Orthros in hex. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 84  |

| 6.7  | The maximal differential probability of SPN-based toy ciphers                                                     | 85  |

| 6.8  | The maximal differential probability for each GFS-based construction                                              | 86  |

| 6.9  | The upper bound of the number of active bits after each operation                                                 | 88  |

| 6.10 | Comparison of lower bounds of the number of active S-boxes. $\hdots$                                              | 92  |

| 6.11 | Comparison of S-boxes                                                                                             | 93  |

| 6.12 | The lower bounds of the number of active S-boxes in the single-key setting.                                       | 94  |

| 6.13 | The differential distribution table of S-box                                                                      | 95  |

| 6.14 | The propagation of the division property for the S-box                                                            | 98  |

| 6.15 | The mapping of the binary matrix.                                                                                 | 98  |

| 6.16 | The propagation of the division property for the binary matrix. $\ldots$ .                                        | 99  |

| 6.17 | Results for the STM 90nm library. Power measured at 10 MHz. *The core                                             |     |

|      | implementation of the underlying permutations in these constructions were                                         |     |

|      | taken from $[35, 64]$                                                                                             | 104 |

| 6.18 | Results for the Nangate 15nm library. Power measured at 10 MHz. $\ldots$ .                                        | 105 |

| 6.19 | Results for the TSMC 90nm library. Power measured at 10 MHz                                                       | 106 |

| 6.20 | Results for the Nangate 45nm library. Power measured at 10 MHz                                                    | 107 |

| 7.1  | Test vectors                                                                                                      | 116 |

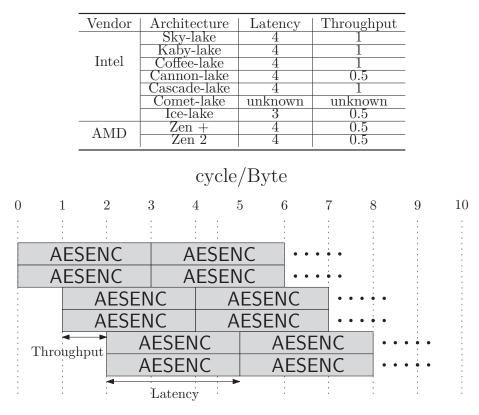

| 7.2  | Latency and throughput of $aesenc$ for some architectures by Intel and AMD                                        |     |

|      | referred by [148]                                                                                                 | 117 |

| 7.3  | Comparison of the performance of the round function having different number                                       |     |

|      | of blocks at the same <i>rate</i> .                                                                               | 120 |

| 7.4  | Round functions of AEGIS family and Tiaoxin-346                                                                   | 121 |

| 7.5  | Candidates of round functions which we search.                                                                    | 122 |

| 7.6  | Speed (in cycles / Byte) of round functions of Rocca, AEGIS-128, AEGIS-                                           |     |

|      | $128L,AEGIS\text{-}256,\mathrm{Tiaxion}\text{-}346,\mathrm{and}\mathrm{JN16}$ (not include a generation part of a |     |

|      | ciphertext).                                                                                                      | 122 |

| 7.7  | The lower bound for the number of active S-boxes in the initialization phase        |

|------|-------------------------------------------------------------------------------------|

|      | where $AS_{sk}$ and $AS_{rk}$ mean an active S-box in the single-key setting and in |

|      | the related-key setting, respectively                                               |

| 7.8  | Performance Evaluation                                                              |

| 7.9  | Performance on Intel<br>(R) Core(TM) i9-12900K CPU with 64 GB RAMs 130              |

| 7.10 | Performance on Intel<br>(R) Core(TM) i9-11900 CPU@2.50GHz with 64 GB RAMs.130       |

| 7.11 | Performance on Intel<br>(R) Core(TM) i9-10910 CPU@3.60GHz with 64 GB RAMs.130       |

| 7.12 | Performance on Apple M1                                                             |

| 7.13 | Performance on Apple A15 Bionic                                                     |

| 7.14 | Performance on Qualcomm Snapdragon 888                                              |

#### 1 Introduction

Cryptography is a mathematical science aiming at realizing secure communication systems. Its study has a long history, dating back over 4000 years, and has resulted in the development of numerous cryptographic algorithms. These algorithms can be divided into modern ciphers and other types. The distinguishing characteristic of modern ciphers is that their encryption and decryption algorithms are made public, while the algorithms used by other types of ciphers are not. This criterion was used in the selection of the *Data Encryption Standard* (DES), a former American standard block cipher, and remains a fundamental requirement for modern cipher design. The study of modern cryptography has undergone significant advancement, thanks to the tireless efforts of numerous cryptographers.

Cryptography has played a vital role in modern internet communication society, and we can see its technology in a wide range of devices and systems, including smartphones, personal computers, and cloud servers to name a few. Thus, studying modern cryptography is essential to maintain and progress the security of our internet society. The primary role of modern cryptographic technology is to provide not only *confidentiality* but also *integrity* and *authenticity*.

- **Confidentiality** An unauthorized third party must not be able to obtain any knowledge of the original content of the communication by intercepting the messages during transmission. In addition, stored data must be protected from unauthorized access.

- Integrity The recipient must be able to verify that the content of the transmitted information was not modified during transmission.

- Authenticity The recipient must be able to verify the origin of the message, ensuring that it was indeed sent by the expected sender.

In general, we can roughly classify the study of cryptography into design and cryptanalysis. In the field of symmetric-key cryptography, researchers typically approach it from both design and cryptanalysis perspectives and strive to advance both areas by sharing insights with one another. In this thesis, we primarily focus on the design of symmetric-key cryptography.

#### 1.1 Motivation and Background

The rapid development of communication technology has made cryptography increasingly important in a variety of fields, including automotive communication, RFID, and industrial control networks to name a few. This rapid development brought about some new interests in the field of symmetric-key cryptography. Over the past decade, a major area of focus in the field of symmetric-key cryptography has been the design of efficient cryptographic algorithms that meet certain constraints, such as circuit area, memory, energy, and latency. This research area is known as "lightweight cryptography," and "lightweight cryptographic algorithms" are in high demand across a range of industries, including automotive communication, RFID, and industrial control networks to name a few. In fact, the National Institute of Standards and Technology (NIST) has initiated the standardization of lightweight cryptographic algorithms (LWC) since 2018<sup>1</sup>, as a concern that the current standard block cipher AES cannot meet the requirement in some applications has come up. This standardization process is open, meaning that a standard lightweight cryptographic algorithm will be selected from among many candidates submitted by cryptographic researchers worldwide similar to the standardization process of AES and SHA3. As of November 2022, the process has progressed to Round 3 (the final round), and 10 out of 57 submissions have been selected as final-round candidates. Since going forward the limits of lightweight cryptography for both industry and academia is valuable and important, many researchers dedicate significant effort to this area.

Another area of interest in this field is the design of ultra-efficient symmetric-key cryptographic algorithms that take full advantage of the functions provided by modern popular devices, such as SIMD instructions and AES new instruction sets (AES-NI). Fifth-generation mobile communication systems (5G) and beyond systems, called beyond 5G or 6G, can achieve ultra-high-speed data transmission, with the 6G system expected to achieve speeds exceeding 100 Gbps [117]. To prevent cryptographic algorithms from becoming a bottleneck in achieving such ultra-high speeds, it is crucial that the cryptographic algorithms used in these systems also be able to perform encryption and decryption at speeds exceeding 100 Gbps on a pure software environment. However, the current standard symmetric-key cryptographic algorithms for the 4G system only achieve speeds of 30 Gbps [178], falling short of the requirements for beyond 5G systems. Additionally, these systems must also have a key length of at least 256 bits to ensure sufficient security against quantum computers. In general, performance and security are the relation of trade-off in symmetric-key cryptographic algorithms, making it a challenging task for algorithm designers to enhance both simultaneously.

#### 1.1.1 Applications and Requirements of Efficient and Lightweight Cryptographic Algorithms

As mentioned before, with the recent rapid development of communication technology, various applications that require such as ultra-low latency and high throughput are coming up. In addition,

<sup>&</sup>lt;sup>1</sup>https://csrc.nist.gov/Projects/lightweight-cryptography

the recent IoT devices have strict resource restrictions for hardware area and memory size, and it makes the resource that cryptographic algorithms can utilize really few in those devices. We here give some of their applications and their requirements for symmetric-key cryptographic algorithms as examples. While there are many other applications that have other restrictions about, such as memory and energy, we here focus on applications that have requirements about hardware area, latency, and high throughput all of which are treated in this thesis.

- Small hardware area One of the most famous applications that requires a small hardware area is RFID. RFID is primarily used for uniquely identifying an object, animal, or person through wireless communication and is utilized in a variety of settings, such as unmanned cash registers and IC cards. In fact, the designer of the first lightweight block cipher PRESENT mentioned that AES is not suitable for using in RFID tags and sensor networks in their paper [51], and this is one of motivations that they proposed PRESENT. According to some works [156, 172], the cryptographic system in RFID should be realized with a circuit of 3000-4000 Gate Equivalents (GEs) or less.

- Low latency There are many applications requiring a quick response, such as encryption of memory bus, storage systems, and automotive communication. In particular, it is said that several technologies realized in beyond 5G system, such as edge computing, require a cryptographic system with an encryption/decryption process of less than 1ns at most. As the current de facto standard block cipher AES is hard to achieve its latency of less than 1.5 ns [8], the new symmetric-key cryptographic algorithm is essential.

- High throughput The upcoming beyond 5G system is expected to achieve ultra-high data transmission speeds for a range of applications. For instance, multi-sensory XR requires 20 times the data transmission speed of the 5G system (100 400 Gbps), and real-time remote applications such as telesurgery and ultra-high quality holograms require data transmission speeds of 0.5 1 Tbps. As the current standard symmetric-key cryptographic algorithms for the 5G system only achieve around 50 Gbps of encryption/decryption speed, it is clear that a new ultra-high throughput cryptographic algorithm is necessary.

#### 1.2 Our Contribution and Outline

In this thesis, we present strategies for designing efficient symmetric-key cryptographic algorithms. Our focus is on the design of block ciphers, a dedicated AEAD, and the introduction of strategies for designing efficient symmetric-key algorithms. Before providing the main parts, we provide definitions, security requirements, and cryptanalysis techniques for symmetric-key cryptographic algorithms. Additionally, we present an automatic security evaluation method with Mixed Integer Linear Programming (MILP). The main part of this thesis consists of four sections: design of a tweakable lightweight block cipher Tweakable TWINE [155], lightweight block cipher WARP [10], block cipher-based low-latency pseudo-random function Orthros [18], and ultra-high throughput encryption with associated data (AEAD) scheme Rocca [154]. The details of these main sections are as follows:

- Section 4 We first introduce the lightweight tweakable block cipher Tweakable TWINE, which aims to minimize hardware circuit area. A tweakable block cipher is a variant of a block cipher, a symmetric-key cryptographic algorithm, that has an additional public input called a "tweak." The key feature and difference of a tweakable block cipher from an ordinary block cipher is that the attacker can know and control the tweak during the attack process, as the tweak is a public input. As a result, designers of a tweakable block cipher must take this attack scenario into consideration. Generally, this extra input weakens the cipher and presents a greater challenge for the designers to evaluate its security. In Sect. 4, we demonstrate how to build a new tweakable block cipher on an existing block cipher with the proposal of Tweakable TWINE. As an initial security evaluation for Tweakable TWINE, we evaluate its security against differential, linear, integral, and impossible differential attacks, which are the prime attacks against symmetric-key cryptographic algorithms and are commonly used as initial security evaluations when designing a new cipher. In terms of hardware implementation results, Tweakable TWINE performs competitively in terms of hardware circuit area, as measured by gate equivalent (GE), compared to other tweakable and ordinary block ciphers.

- Section 5 As another lightweight block cipher targeting low hardware implementation area, we introduce a 128-bit lightweight block cipher WARP. WARP is based on the Feistel structure, one of the prime constructions for block ciphers. The main challenge in designing WARP is selecting a good permutation in a linear layer from numerous candidates. Since WARP is designed as a nibble operation-oriented cipher, with all operations following a nibble-wise operation, we must choose a good permutation from  $(16!)^2$  candidates, which is discussed more detailly in Sect 5. To address this challenge, we convert the general construction of WARP into a Lblock-like construction that is equivalent in terms of security. This conversion significantly reduces the number of permutation candidates from  $(16!)^2$  to 8!, allowing us to find the best one among them. The initial security evaluation for WARP is similar to that of Tweakable TWINE, with the addition of evaluations against invariant and meet-in-the-

middle attacks. In terms of hardware implementation results, WARP achieves the smallest hardware circuit area among all 128-bit block ciphers, with a hardware circuit area of fewer than 1000 GEs for the first time.

- Section 6 In addition to designing a cipher with a low hardware implementation area, it is also interesting to explore how low-latency a cipher can be developed. To this end, we introduce a low-latency pseudo-random function (PRF) called Orthros. A distinctive feature of Orthros is that it does not have a decryption procedure, which this type of cipher is referred to as PRF. This feature is derived from Orthros being based on a two-branch construction, in which the branches are relatively weak pseudo-random permutations (PRPs) and the output is calculated by XORing the outputs of the two branches. With this two-branch construction, Orthros achieves the lowest latency among other ciphers. A major challenge in designing Orthros is the selection of a good permutation, as well as in WARP. The primary difference between the two is the number of candidate permutations and the approach used to find a suitable one. For Orthros, which is a bit-oriented cipher with a 128-bit block, the number of candidate permutations is 128!. To reduce the search space, we employ a two-step approach. We provide the detailed method for finding a good permutation in Orthros-type ciphers through an explanation of Orthros.

- Section 7 Lastly, we present Rocca, an ultra high-throughput authenticated encryption with associated data (AEAD) scheme. Rocca is designed for beyond 5G applications and includes a 256-bit key to protect against attacks by quantum computers. Unlike the previously mentioned block ciphers, which only provide confidentiality, Rocca is an AEAD that ensures both confidentiality and integrity. The main feature of Rocca is the use of a sponge-based round function to achieve ultra-high throughput. Additionally, Rocca takes full advantage of SIMD instructions and AES-NI, which allow for efficient execution of basic operations like XOR and multiplication, as well as an AES round function, on a pure software environment. As a result, Rocca achieves over 200 Gbps on the latest CPU, meeting the requirements for beyond 5G in terms of both performance and security, throughput of over 100 Gbps and support for a 256-bit key. Note that Rocca is the first dedicated symmetric-key cryptographic algorithm meeting these requirements for beyond 5G.

#### 2 Symmetric-Key Cryptography

Symmetric-key cryptography plays a crucial role in contemporary internet communication systems. One of the defining features of symmetric-key cryptographic algorithms is their use of identical secret keys for both encryption and decryption processes, meaning that two parties must previously share a secret key in order to securely communicate. Contrastingly, public-key cryptography (or asymmetric cryptography) does not require the pre-sharing of secret information. In symmetric-key cryptography, the unencrypted (original) information is referred to as plaintext, and the encrypted information that is transmitted through public channels such as the internet is referred to as ciphertext. If a plaintext M is encrypted using a secret key K, the resulting ciphertext C can be decrypted back into the original plaintext P using the same secret key K, as follows:

$C = \operatorname{Enc}(K, M), M = \operatorname{Dec}(K, C),$

where Enc() and Dec() denote the encryption and decryption algorithms, respectively.

Generally, symmetric-key cryptography encompasses a range of algorithms including block ciphers, stream ciphers, hash functions, message authenticated codes (MAC), and authenticated encryption with associated data (AEAD). Among them, we deal with block ciphers and AEADs in this thesis.

#### 2.1 Block Cipher

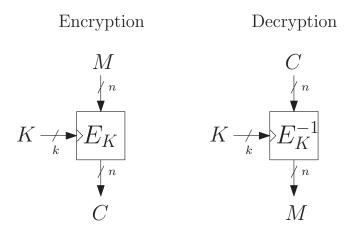

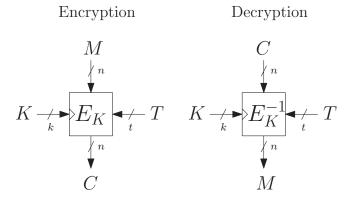

A block cipher is utilized to ensure data confidentiality. As can be seen in the name of "block cipher", a block cipher converts a plaintext of a certain length, referred to as a block, typically 64 or 128 bits in many block ciphers, into a ciphertext of the same length using a secret key. Fig 2.1 illustrates an overview of a block cipher. More formally, it can be defined as follows:

**Definition 1** Block cipher: An *n*-bit block cipher  $E_K$  with a *k*-bit secret key  $K \in \mathbb{F}_2^k$  is a keyed *function:*

$$E_K : \mathbb{F}_2^n \times \mathbb{F}_2^k \to \mathbb{F}_2^n,$$

$$\{M, K\} \to C,$$

where  $M \in \mathbb{F}_2^n$ ,  $C \in \mathbb{F}_2^n$  denote a plaintext and ciphertext, respectively. The inverse function of  $E_K$  is expressed as  $E_K^{-1}$  if a block cipher is inversible.

Most block ciphers have a corresponding decryption procedure, making them bijective functions. Since these block ciphers can be viewed as deterministic permutations that depend on a

Figure 2.1: Overview of a block cipher.

secret key, they are known as pseudo-random permutations (PRP). On the other hand, some block ciphers do not have a decryption procedure and are therefore not bijective functions. In this case, these ciphers are referred to as pseudo-random functions (PRF).

#### 2.1.1 Modern Block Cipher Construction

The design concept of symmetric-key cryptographic algorithms is grounded in the principles of confusion and diffusion, as introduced by Shannon and abstracted by Massey [122, 159]:

- **Confusion** The statistical properties of the ciphertext should depend on the statistical properties of the plaintext in a way that is too complex for an attacker to distinguish.

- **Diffusion** Each bit of the plaintext and each bit of the secret key should influence as many bits of the ciphertext as possible.

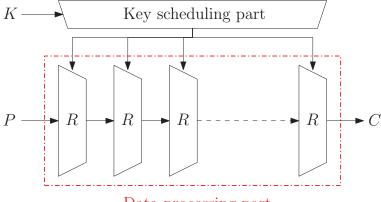

Generally, a block cipher can be divided into a data processing part and a key scheduling part. The key scheduling part expands a given secret key, also known as a master key, into several round keys which are inserted one by one throughout the cipher. The data processing part uses the round keys generated by the key scheduling part to encrypt a given plaintext and produce a ciphertext. Almost all modern block ciphers have an iterated construction, meaning that the data processing part is composed of a simple function called a round function, which is called multiple times in the data processing part.

**Definition 2** Iterated block cipher: A block cipher constructed as an iterated construction is referred to as an iterated block cipher. The data processing part of an iterated block cipher  $E_d$

can be expressed as follows:

$$E_d(\cdot) = f_r(\cdot) \circ \cdots \circ f_2(\cdot) \circ f_1(\cdot),$$

where  $f_i$  and  $rk_i$  denote the *i*-th round function and the round keys.

A round function usually consists of very simple mathematical operations, such as an XOR, AND, modular addition, and look-up table called *S-box*. Fig. 2.2 illustrates the overview of an iterated block cipher.

Data processing part

**Figure 2.2:** Overview of an iterated block cipher. R denotes one round of the round function.

It should be mentioned that some block ciphers do not consist of a single round function in their data processing part, but rather a few similar round functions. Strictly speaking, these ciphers are not iterated ciphers, but in the context of symmetric-key cryptography, they can be also considered as iterated block ciphers.

As popular structures of a block cipher, there are three ones called *Substitution Permutation Network* (SPN), *Feistel network*, and *And rotation XOR* (ARX). The SPN and Feistel structures will be discussed in the next section.

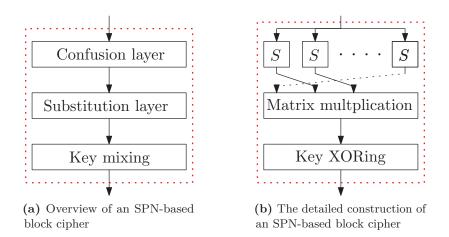

**2.1.1.1** Substitution Permutation Network The fundamental idea behind this type of construction can be traced back to Shannon's cipher design principle [159], in which a block cipher is constructed by substitution and diffusion layers. With this idea, the round function in SPN-based block ciphers consists of a key mixing, diffusion layer, and substitution layer.

**Definition 3** Substitution permutation network (SPN): A substitution permutation network is a structure for block ciphers that is based on a series of key mixing layers, substitution layers, and diffusion layers.

Key mixing is often realized through an XOR operation in modern ciphers. The diffusion layer is implemented through simple linear operations such as XOR, permutation, and matrix multiplication. The substitution layer is typically implemented using a substitution box (S-box), which is a look-up table. Many modern SPN-based block ciphers apply these operations on a word-by-word basis (nibble-wise, byte-wise), and these operations are typically performed in parallel. Fig.2.3a and 2.3b provide an overview and detailed depiction of SPN-based ciphers.

Many SPN-based block ciphers follow this design strategy. One of the most notable examples is the Advanced Encryption Standard (AES) [67], which is the standard block cipher algorithm of the United States. In this thesis, we introduce a low-latency pseudo-random function (PRF) Orthros [18], as an SPN-based block cipher.

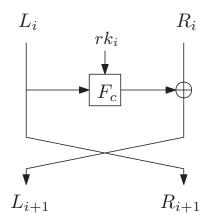

**2.1.1.2** Feistel Network In Feistel network-based block ciphers (referred to as Feistelbased block ciphers in this thesis), the basic operations applied are the same as those in an SPNbased block cipher, such as XOR, permutation, matrix multiplication, and S-boxes. The main difference from SPN is the way these basic operations are applied to the plaintext (internal state). In the case of a Feistel network, the plaintext is first divided into two internal states, and these states are alternately applied to linear and non-linear operations in each round.

**Definition 4** Feistel network: A Feistel network is a structure for block ciphers that divides a plaintext M into two states, denoted  $M = L_i ||R_i$ , where i denotes the round number. The divided states  $L_i$  and  $R_i$  are alternatively applied to a cryptographic function  $F_c$  in each round as follows:

$$R_{i+1} = L_i,$$

$$L_{i+1} = F_c(R_i, rk_i) \oplus L_i$$

where  $rk_i$  denotes the round key in the *i*th round.

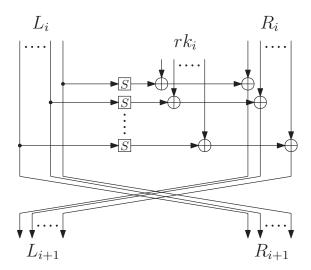

Fig. 2.3 illustrates the overview of Feistel network.

Figure 2.3: Overview of Feistel network.

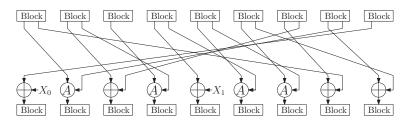

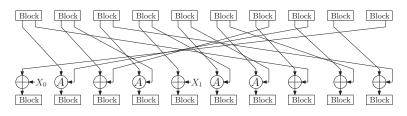

Like SPN-based block ciphers, most Feistel-based block ciphers also apply basic operations in parallel on a nibble and byte-wise basis. Fig. 2.4 shows the detailed construction of a type-2 generalized Feistel network, a popular variant of the Feistel network, as an example of the parallel application of basic operations.

Figure 2.4: Construction of type-2 generalized Feistel network.

It is clear that the number of rounds for Feistel-based block ciphers tends to be larger than that of SPN-based block ciphers, as the internal state in a Feistel network is encrypted half by half in each round. However, Feistel-based block ciphers have merit in terms of hardware implementation that Feistel-based block ciphers only require an encryption circuit for both encryption and decryption procedures in hardware implementation, while SPN-based block ciphers require both encryption and decryption circuits individually. There are fewer Feistel-based block ciphers compared to SPN-based block ciphers. However, several important block ciphers are based on the Feistel network, such as the Data Encryption Standard (DES) [48], the previous standard block cipher algorithm of the United States. In this thesis, we introduce two Feistel-based block ciphers: Tweakable TWINE [155] and WARP [10]. Note that Tweakable TWINE is not a typical block cipher, but a "tweakable block cipher" that will be described in the next section.

#### 2.1.2 Tweakable Block Cipher

A tweakable block cipher (TBC) is a variant of a block cipher, which has an extra input called *tweak*. The primary purpose of introducing a TBC is to provide beyond-birthday bound security [62]. The formal concept of a TBC was introduced by Rivest and Wagner [118]. We give the definition of a TBC as follows:

**Definition 5** Tweakable block cipher: An *n*-bit tweakable block cipher  $E_T$  with a *k*-bit secret key  $K \in \mathbb{F}_2^k$  and a *t*-bit tweak  $T \in \mathbb{F}_2^t$ , which a tweak is a public value, is a cryptographic function as follows:

$$E_T: \mathbb{F}_2^n \times \mathbb{F}_2^k \times \mathbb{F}_2^t \to \mathbb{F}_2^n$$

$$\{M, K, T\} \to C,$$

where  $M \in \mathbb{F}_2^n$  and  $C \in \mathbb{F}_2^n$  denote a plaintext and ciphertext, respectively. The inverse function of  $E_T$  is expressed as  $E_T^{-1}$ .

Fig 2.5 illustrates the overview of a tweakable block cipher.

Figure 2.5: Overview of a tweakable block cipher.

One drawback of a TBC is that tweak can be leveraged for cryptoanalysis because a tweak is public. Consequently, the designers of TBCs must consider the possibility of an attacker leveraging a tweak. Despite numerous studies on block cipher-based TBCs [57, 104, 115, 130], there remains a significant efficiency gap between ordinary block ciphers and TBCs. Nevertheless, TBCs remain popular due to their ability to provide beyond-birthday bound security, and one of the finalists in the NIST LWC competition Romulus [100] employs a tweakable block cipher SKINNY [26] as its underlying primitive. In this thesis, we will introduce a tweakable block cipher Tweakable TWINE [155].

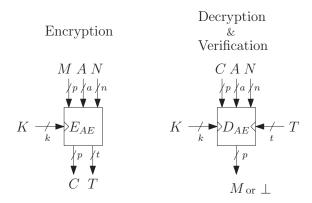

#### 2.2 Authenticated Encryption

Authenticated encryption (AE) scheme ensures both data confidentiality and integrity, while a block cipher only ensures data confidentiality. In general, AE schemes take an unrestricted plaintext, a secret key, and a nonce (a randomly generated value) as inputs, and produce a ciphertext of the same size as the plaintext along with a tag that is used to verify the integrity of the plaintext. The tag is dependent on the plaintext, meaning it is a unique value for a given secret key, plaintext, and nonce.

Authenticated encryption with associated data (AEAD) is a variant of AE that has an additional input called associated data. Associated data is not encrypted, unlike plaintext, but is used in generating the tag, that is, a value of the tag is unique for a plaintext, associated data, secret key, and nonce. This thesis focuses on AEAD, and thus we provide the following definition:

**Definition 6** Authenticated encryption with associated data (AEAD): An authenticated encryption function  $E_{AE}$  is a cryptographic function that takes a k-bit secret key K, an *n*-bit nonce N, a plaintext M with arbitrary size p, and associated data A with arbitrary size a as inputs, and produces a ciphertext C with the same size as the plaintext and a t-bit authentication tag T:

$$E_{AE} : \mathbb{F}_2^k \times \mathbb{F}_2^n \times \mathbb{F}_2^p \times \mathbb{F}_2^a \to \mathbb{F}_2^p \times \mathbb{F}_2^t$$

$$\{K, N, M, A\} \to \{C, T\},$$

Note that associated data A is not encrypted during the encryption process. The inverse function  $D_{AE}$  is defined as follows:

$$D_{AE} : \mathbb{F}_2^k \times \mathbb{F}_2^n \times \mathbb{F}_2^p \times \mathbb{F}_2^a \times \mathbb{F}_2^t \to \mathbb{F}_2^p \cup \{\bot\},\$$

$$\{K, N, C, A, T\} \to M \text{ or } \bot,$$

where  $\perp$  denotes an error for all other inputs.

As can be seen in this definition, the integrity of the data can be verified as the owner of the secret key K is the only person who can generate a correct tag T. Fig.2.9 shows an overview of AEAD and secret key confidentiality.

Figure 2.6: Overview of an AEAD.

Currently, there are two popular methods for constructing an AEAD. One approach involves using a block cipher with an additional outer function to provide data confidentiality, i.e., using a block cipher to provide data confidentiality and an additional outer function to provide data integrity. This is the most popular approach since these schemes can claim their security in the context of provable security under a secure block cipher and stream cipher. AES-GCM [1] and ChaCha20-Poly1305 [138] are well-known AEADs followed this approach.

Another approach is to design a dedicated AEAD from scratch. In this approach, it is not possible to claim security in the context of provable security. However, these dedicated AEADs can be much more efficient than the previously mentioned AEADs. In fact, several dedicated AEADs submitted to the CAESAR competition<sup>2</sup> demonstrate impressive throughput for their encryption/decryption process, such as AEGIS, the final portfolio for high-performance applications, and Tiaoxin. This thesis introduces an AEAD called Rocca, which follows this approach. The basic construction of this type of AEAD is explained in the next section.

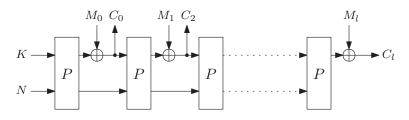

#### 2.2.1 Construction of a Sponge-Based AEAD

Sponge-based AEADs have a large-state permutation as its core component. The idea behind this construction was introduced by Bertoni et al. [37] as the form of a *duplex sponge encryption* shown in Fig. 2.7. The basic construction of ultra-high throughput dedicated AEADs such as AEGIS, Tiaoxin, and Rocca can be seen as a combination of a duplex sponge encryption and a sponge-based stream cipher introduced by Bertoniet al. [36] as shown in Fig. 2.8. The advantage of this construction is that it allows for simultaneous absorbing of a plaintext and squeezing of ciphertext. It leads to faster encryption/decryption procedures compared to constructions that divide the process into separate absorbing and squeezing phases. We show this sponge-based

<sup>&</sup>lt;sup>2</sup>https://competitions.cr.yp.to/caesar.html

AEAD construction in Fig. 2.9.

Figure 2.7: Duplex sponge encryption.

Figure 2.8: Sponge-based stream cipher.

Figure 2.9: Sponge-based AEAD.

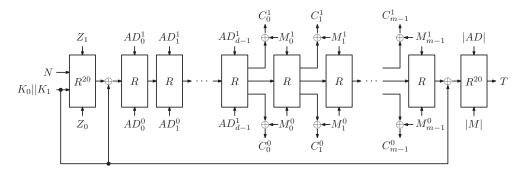

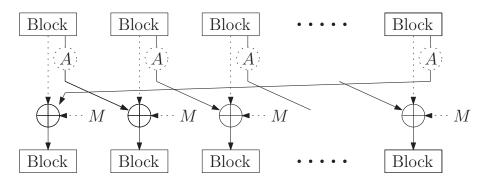

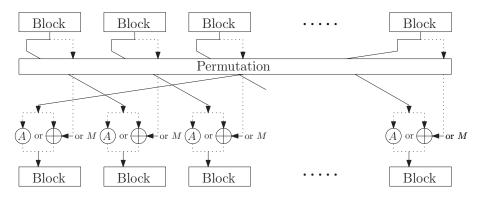

The encryption/decryption process of AEGIS, Tiaoxin, and Rocca consists of four phases: initialization, processing the associated data, encryption, and finalization as shown in Fig. 2.10. The core permutation P is initialized in the initialization phase, and the associated data is absorbed in the processing the associated data phase. Ciphertext blocks are then generated by absorbing message blocks, and the tag is generated in the finalization phase.

#### 2.3 Cryptanalysis of Symmetric-Key Cryptographic Algorithms

Cryptanalysis aims at not only breaking symmetric-key cryptographic algorithms, but also evaluating their security. Over the past few decades, various cryptanalysis techniques have been developed and have played a significant role in shaping design strategies.

Cryptanalysis to modern symmetric-key cryptographic algorithms such as block ciphers, stream ciphers, and AEADs can be used to estimate their security margin by evaluating the gap between

Figure 2.10: Entire encryption/decryption process of AEGIS, Tiaoxin, and Rocca.

the full number of rounds and the number of rounds that can be attacked. For example, the current best attack against AES-128, which has 10 rounds as the full number of rounds, can attack the 7-round reduced AES-128 [142], indicating a security margin of 3 rounds for AES-128. Once an attack is able to reach the full number of rounds, the cipher is considered fully broken. Evaluating the security margin is important for designers in determining security claims for their ciphers and in estimating the current level of security of a cipher.

Currently, there are various cryptanalysis techniques that can be generally classified into generic attacks and dedicated attacks that exploit specific structural properties of algorithms. A generic attack is an inevitable attack for all symmetric-key cryptographic algorithms, such as *brute force attack*, which tries all key candidates and find a correct one. Therefore, the efficiency of dedicated attacks is evaluated by comparing with a generic attack, and the dedicated attack regards as success if the efficiency outperforms that of a generic attack. Therefore, a secure symmetric-key cryptographic algorithm must be resistant to all attack vectors except for generic attacks. In the following sections, we will describe the goals of attacks, attack models, and several popular cryptanalysis techniques.

#### 2.3.1 Attack Models

There are several attack models that are classified based on the level of knowledge and capabilities of the attacker.

- **Ciphertext-only attack** In this type of attack, the attacker only has access to the ciphertext produced by the encryption system. It is assumed that the ciphertext is uniformly random, given that the plaintext is also uniformly random.

- Known plaintext attack In this type of attack, the attacker has access to pairs of plaintext and corresponding ciphertext. It is important to note that the attacker does not have control over the plaintext.

- Chosen plaintext/ciphertext attack In this type of attack, the attacker has access to an encryption/decryption system and can choose the plaintext/ciphertext to be encrypted/decrypted. This means that the attacker can obtain pairs of arbitrarily chosen plaintext/ciphertext and the corresponding ciphertext/plaintext.

- Adaptively chosen plaintext/ciphertext attack This type of attack is similar to the chosen plaintext/ciphertext attack, with the added capability for the attacker to obtain pairs of arbitrarily chosen plaintext/ciphertext and the corresponding ciphertext/plaintext even after the chosen plaintext/ciphertext has been encrypted/decrypted by the system.

In general, the attack models become increasingly advantageous for the attacker as they progress in the above list. In symmetric-key cryptography, symmetric-key cryptographic algorithms must be resistant to all known attack vectors in all of the above attack models.

#### 2.3.2 Goal of Attack

The primary goal of attacks on symmetric-key cryptographic algorithms is to recover the secret key. However, the specific goals of an attack may vary depending on the variant of the symmetric-key cryptographic algorithm. In this section, we will discuss the goals of attacks on block ciphers and AEADs separately.

**2.3.2.1** For Block Ciphers According to Kerckhoffs's principle [107], block ciphers should be resistant to any attack vector even if the encryption/decryption algorithm is public. In this context, the goal of attacks on block ciphers are as follows:

- Key recovery attack Let k denote the size of the secret key. The attacker aims to recover the secret key from the key space  $2^k$ . Once the secret key has been recovered, the attacker can access the plaintext and internal states of the block cipher.

- Distinguishing attack Let k and n denote the size of the secret key and block, respectively. The attacker aims to distinguish the block cipher, which is a set of  $2^k$  n-bit permutations without any knowledge of a secret key, from a random permutation, which is a set of  $2^n$ ! n-bit permutations.

A secure block cipher should be resistant to both key recovery and distinguishing attacks within a practical time, assuming that the encryption/decryption algorithm is public. A block cipher is considered secure if there is no effective way with a fewer cost than an exhaustive search to recover the secret key or distinguish it from a random permutation. It should be mentioned that a distinguishing attack does not directly lead to the recovery of the secret key. However, the success of a distinguishing attack implies that a block cipher has a non-randomness property (such a nonrandomness property called *distinguisher*), and it may lead to the success of a key recovery attack in the end. In many cases, a key recovery attack is built on a certain distinguisher by extending the number of attacked rounds.

Since evaluating the longest round of distinguishers for any attack vector is a general approach to estimating the security of a new block cipher design, we focus on distinguishing attacks in this thesis.

**2.3.2.2** For AEAD The primary purpose of attacks on AEADs is to violate data confidentiality and integrity. As mentioned in Section 2.2, block-cipher-based AEADs can claim their security followed by provable security, while dedicated AEADs, such as sponge-based AEADs, are hard to claim it on provable security. Therefore, these AEADs typically provide their security through a detailed analysis of existing attack vectors. In terms of data confidentiality, the security of sponge-based AEADs relies on the randomness of the keystream (output). To ensure data integrity, these AEADs must resist forgery attacks in which the attacker attempts to create a counterfeit authentication tag or a valid message with an original authentication tag. Before outlining the goal of attacks, we first provide the common requirement for the use of sponge-based AEADs.

**Definition 7** Nonce respecting: A nonce or IV is used only once to protect a message and associated data, meaning that the same pair of a nonce and secret key cannot be used to encrypt two different pairs of message and associated data.

In the nonce-respecting setting, the attacker is only able to query a single ciphertext that corresponds to a chosen message with the same nonce. This means that the majority of queries in the attack procedure are for chosen ciphertexts.

- Key recovery attack The attacker recovers a secret key of size k selected from any choice in the key space  $2^k$ . Once a secret key is recovered, the attacker can do anything, such as recover plaintexts and internal states. This attack directly violates both data confidentiality and integrity.

- State recovery attack The attacker recovers an internal state. In sponge-based AEADs, the permutation is often constructed with simple operations to maintain efficiency, and therefore an attacker may be able to recover the secret key by computing the inverse permutation once the internal state has been recovered. Hence, the success of the state recovery attack leads to violating both data confidentiality and integrity.

- Distinguishing attack The attacker distinguishes the output from a random output in an encryption phase. It aims to violate a pseudo-randomness of an output, which leads to recover a plaintext.

- Forgery attack The attacker produces a quartet of a ciphertext C, nonce N, associated data A, and authentication tag T that the decrytion oracle does not return  $\bot$ , with no encryption request of the same  $\{N, A\}$  corresponding  $\{C, T\}$ . the success of the forgery attack leads to violating data integrity. Many AEADs assume that the attacker can produce the pair of a message and tag for any given message with a nonce-respecting setting. This type of forgery is called *universal forgery*.

A secure AEAD needs to resist these attacks with the assumption that an encryption/decryption algorithm is public as well as the case of a block cipher. An AEAD can be considered secure if there is no method for recovering the secret key or internal state except through an exhaustive search, and if a forgery attack requires a number of decryption queries greater than the security claim for such an attack.

#### 2.3.3 Cryptanalysis Techniques

Currently, there are several techniques to analyze symmetric-key cryptographic algorithms. In this section, we introduce several techniques related to this thesis.

2.3.3.1**Differential Cryptanalysis** The differential cryptanalysis is a chosen plaintext attack proposed by Biham and Shamir [43]. Nowadays, the differential cryptanalysis is the one of most popular and powerful cryptanalysis techniques available for symmetric-key cryptographic algorithms. The current American standard block cipher AES [5] was designed to have resistance against the differential cryptanalysis (and linear cryptanalysis), and all modern symmetric-key cryptographic algorithms not only block ciphers follow this principle. The idea of this technique is to exploit the difference between the pair of two plaintexts and the difference between the pair of the corresponding two ciphertexts. More specifically, in the differential cryptanalysis, the attacker attempts to find a pair of input and output differences with a high probability, i.e.,  $E_K(\Delta M) = \Delta C$ ,  $(\Delta C = C \oplus C', \Delta M = M \oplus M')$  occurs with high probability on symmetrickey primitives  $E_k$ , where (M, M') and (C', C) denote a pair of plaintexts and ciphertexts, respectively. A pair of input and output differences  $(\Delta M, \Delta C)$  is called a *differential* in the context of the differential cryptanalysis. The probability of a differential, which is called a *differential* probability, is calculated by investigating all pairs of plaintext following  $\Delta M = M \oplus M'$  on  $E_K$ . We define a differential and its probability on a symmetric-key primitive  $E_K$  as follows.

**Definition 8** Differential A differential is a pair of input and output differences. The probability of a differential  $(\Delta P, \Delta C)$  is calculated as follows:

$$DP(\Delta M \xrightarrow{E_K} \Delta C) = \frac{\#\{x \in \mathbb{F}_2^n | E_K(M) \oplus E_K(M \oplus \Delta M) = \Delta C\}}{2^n}$$

where M and n denote chosen from a uniformly distributed random variable and the size of block, respectively.

In an ideal block cipher, the differential probability for any differential has to be  $2^{-n}$ . Therefore, the attacker succeeds in the distinguishing attack if she obtains the differential with a probability more than  $2^{-n}$ .

Generally, calculating the exact differential probability is computationally infeasible in most symmetric-key primitives. Therefore, a *differential characteristic* is usually employed to estimate a differential probability. Let  $E_K$  be a *r*-round iterated block cipher as  $E_K(\cdot) = f_r(\cdot) \circ f_{r-1}(\cdot) \circ$  $\cdots \circ f_1(\cdot)$ . A differential characteristic can be defined as a sequence of differences over all rounds in  $E_K$ , and its probability can be estimated as a product of differential probabilities of each round under the well-known Markov cipher assumption.

**Definition 9 Markov cipher** [113] An iterated cipher with round function  $x_o = F_R(x_i, rk)$ , where x and k denote the internal state and round key respectively, is a markov cipher if there is a group operation  $\oplus$  for differences such that for all choices of  $\alpha$  and  $\beta$  ( $\alpha \neq e, \beta \neq e$ ),  $DP(\Delta x_o = \beta | \Delta x_i = \alpha, x_i = \gamma)$  is independent of  $\gamma$ , where a round key is uniformly random.

We give the definition of a differential characteristic and its probability on a block cipher  $E_K$  as follows.

**Definition 10** Differential characteristic A differential characteristic is a sequence of differences over all rounds in a block cipher  $E_K$  as follows:

$$C = (c_0 \xrightarrow{f_1} c_1 \xrightarrow{f_2} \cdots \xrightarrow{f_r} c_r) \coloneqq (c_0, c_1, \cdots, c_r),$$

where  $(c_0, c_1, \dots, c_r)$  denotes differences of the output of each round, i.e.,  $c_0$  and  $c_r$  denote differences of plaintext and ciphertext, respectively. The probability of a differential characteristic C is estimated as follows:

$$DP(C) = \prod_{i=1}^{r} DP(c_{i-1} \xrightarrow{f_i} c_i).$$

From the perspective of the designer, it is sufficient to ensure that the upper bound of DP(C) is achieved, rather than finding the optimal differential characteristic.

Since the probabilistic operations in symmetric-key primitives are generally an S-box and modular addition, and this thesis focuses on S-box-based primitives, we can estimate the maximum differential probability for a differential characteristic by counting the number of active S-boxes (AS), which is an S-box with a non-zero input difference. Let  $DP_s$  be the maximum differential probability of an S-box. We can estimate the upper bound of DP(C) by the lower bound for the number of AS, i.e.,  $2^{-(DP_s \times \#AS)} \leq 2^{-n}$  is sufficient to resist against the distinguishing attack for any input (plaintext) difference.

Nowadays, it is common to use automatic search tools based on MILP, SAT/SMT, and CP to evaluate the optimal differential characteristic and the lower bound for the number of AS. In this thesis, we employ a MILP-based automatic search method described in Section 3.

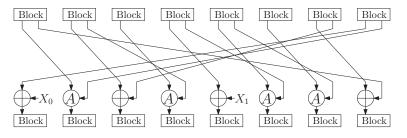

**2.3.3.2** Linear Cryptanalysis The linear cryptanalysis is a known plaintext attack proposed by Matsui [123]. With the linear cryptanalysis, Matsui broke the previous American standard block cipher DES, this cryptanalysis technique is considered to the two prime cryptanalysis techniques available for symmetric-key cryptographic algorithms as well as the differential cryptanalysis. The idea of this technique is to approximate the output Boolean function of symmetric-key primitives into one's input Boolean function as a probabilistic equation. More specifically, the attacker attempts to express the relation of the plaintext M, ciphertext C, and secret key K as a probabilistic equation, i.e.,  $\Gamma_{\alpha}(M) \oplus \Gamma_{\beta}(C) = \Gamma_{\gamma}(K)$  where  $\Gamma_{\alpha}$ ,  $\Gamma_{\beta}$ , and  $\Gamma_{\gamma}$  are called the liner masks. In many cases, we can see  $\Gamma_{\gamma}(K)$  as a constant value  $c \in \mathbb{F}_2$  since a secret is usually assumed as a fixed value. Hence, the main aim is to find  $\Gamma_{\alpha}$  and  $\Gamma_{\beta}$  to satisfy  $\Gamma_{\alpha}(M) \oplus \Gamma_{\beta}(C) = c$  with a high probability. This probability is called an *absolute linear bias* and defined as follows.