This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e. g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Development of pyroelectric sensor integrated with

# two-dimensional transistor

# Stephen Chukwuemeka Mbisike

A Thesis Submitted for the Degree of Doctor of Philosophy (PhD)

The University of Edinburgh 2022

# **DECLARATION**

I hereby declare that this thesis has been produced entirely by myself from research I have carried out from 2017 – 2022 at the University of Edinburgh under the supervision of Prof. Rebecca Cheung. The work in this thesis has not been submitted for another qualification or to any other University.

Stephen C. Mbisike

University of Edinburgh

June 2022

## **ACKNOWLEDGMENT**

My sincere gratitude to my PhD supervisor Prof. Rebecca Cheung for all her guidance and support throughout my studies. I also thank my assistant supervisor Dr. Alister Hamilton, my first teaching and demonstration (T&D) role in 2018 was at his digital systems laboratory A MSc class. I sincerely appreciate the petroleum technology development fund (PTDF) and the Nigerian government for funding my PhD.

I cannot thank enough the clean room staff of the Scottish Microelectronics Centre for training and guidance throughout my laboratory research; Dr. Camelia Dunare, Stewart Ramsay, Ewan Mcdonald, Dr. Graham Wood and Dr. Peter Lomax. Other notable assistance from staff at the university includes Dr. Andrey Gromov for Raman and Photoluminescence spectroscopy and Dr. Nicola Cayzer for SEM and EBSD studies. My PhD colleagues also made the journey worthwhile; Andrew Mugisha, Yulin Geng to name a few.

My sincere appreciation also goes to Dr. John Phair, CTO of Pyreos Ltd. I collaborated with Pyreos on one of their technologies from which I benefited immensely from the exposure. The wafer manger Lutz Eckart provided valuable insight and direction on the technology and his trusted technician Gavin Logan was always happy to help.

I am pleased to acknowledge the Engineering Graduate School (EGS) for hosting programs like Firbush. Firbush was not only a recreational activity but also an avenue to get to know other research students and develop professional relationships. My sincere appreciation also goes to the EGS for the support I received during the COVID-19 pandemic.

Finally, I want to thank my family and friends for their support throughout this journey and believe that I would complete the PhD satisfactorily.

# Lay Summary of Thesis

The lay summary is a brief summary intended to facilitate knowledge transfer and enhance accessibility, therefore the language used should be non-technical and suitable for a general audience. <u>Guidance on the lay summary in a thesis</u>. (See the Degree Regulations and Programmes of Study, General Postgraduate Degree Programme Regulations. These regulations are available via: <u>www.drps.ed.ac.uk</u>.)

| Name of student:  | Stephen Chukwuemeka Mbisike                            | U                                  | JUN     | S1791725       |

|-------------------|--------------------------------------------------------|------------------------------------|---------|----------------|

| University email: |                                                        |                                    |         |                |

| Degree sought:    | Doctorate                                              | No. of words in<br>main text of th |         | 26539          |

| Title of thesis:  | Development of high performance dimensional transistor | infrared sensor                    | integra | ated with two- |

#### Insert the lay summary text here - the space will expand as you type.

Progress in the complementary metal-oxide semiconductors (CMOS) integrated circuit technology and the acceptance of silicon based microelectronics have revolutionized the electronics world. Advancement in human endeavor relies on the improvement of our processes and the discovery of new materials with beneficial properties. The advent of two dimensional (2D) materials has created exciting new possibilities. Possibilities that not only include the replacement of silicon in microelectronics but also for application in other areas such as photonics. Also, the quest to move beyond silicon and its oxide has seen increased interest in potential high dielectric and/or pyroelectric materials.

The primary motivation for this work is to improve the output of a lead zirconium titanate (PZT) based pyroelectric sensor by integrating the device with a 2D WSe<sub>2</sub> field effect transistor (FET). A systematic approach has been taken to realize this goal by exploring the material properties individually.

From varied literature, two dimensional (2D) materials have shown promise in both electrical and optical properties. In this work, studies have been conducted on a 2D material WSe<sub>2</sub>, which has been deposited via exfoliation and pulse laser deposited (PLD). Though the PLD WSe<sub>2</sub> offers good control during deposition, findings show that the exfoliated WSe<sub>2</sub> has better electrical and optical properties. A mask-less lithographic method has been employed for the fabrication of the devices and tests have been carried out using a Keithley parameter analyser, Raman and Photoluminescence spectroscopy.

Analysis have also been conducted on the PZT pyroelectric device to understand its surface profile using energy back scatter diffraction (EBSD) and a factorial design of experiment. The result and understanding from the studies have enabled the integration of PZT with a WSe<sub>2</sub> FET and the result shows improvement in the overall current output. Thus, we have succeeded in amplifying the output of the PZT pyroelectric based sensor by integrating with a WSe<sub>2</sub> FET.

#### Document control

| K:\AAPS\D-AcademicAdministration\02-CodesOfPractice,Guidelines&Regulations\24-MainRefere<br>Current\Assessment BOE SCC & Feedback\Forms\ThesisLaySummary | ncesCopiesPolicies\01-         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| ii you require and accument in an alternative format picase                                                                                              | Date last revised:<br>20.06.19 |

## **ABSTRACT**

Progress in the complementary metal-oxide semiconductors (CMOS) integrated circuit technology and the acceptance of silicon based microelectronics have revolutionised the electronics world. Advancement in human endeavour relies on the improvement of our processes and the discovery of new materials with beneficial properties. The advent of two dimensional (2D) materials has created exciting new possibilities. Possibilities that not only include the replacement of silicon in microelectronics but also for application in other areas such as photonics. Also, the quest to move beyond silicon and its oxide has seen increased interest in potential high dielectric and/or pyroelectric materials.

The primary motivation for this work is to improve the output of Pyreos's lead zirconium titanate (PZT) based pyroelectric sensor by integrating the device with a 2D tungsten diselenide (WSe<sub>2</sub>) field effect transistor (FET). A systematic approach has been taken to realise this goal by first exploring the material properties individually.

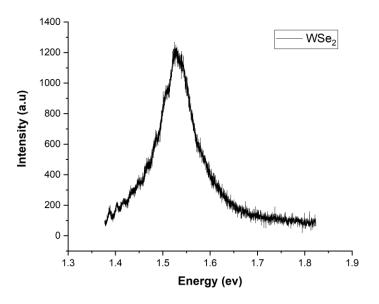

From varied literature, two dimensional (2D) materials have shown promise in both electrical and optical properties. In this work, studies have been conducted on the 2D material WSe<sub>2</sub>, which has been deposited via exfoliation and pulse laser deposition (PLD). Though PLD WSe<sub>2</sub> offers good control during deposition, our findings show that the exfoliated WSe<sub>2</sub> has better electrical and optical properties. The field effect mobility calculated for the exfoliated WSe<sub>2</sub> and PLD-WSe<sub>2</sub> FET is 12.06 cm<sup>2</sup>/Vs and 5.66 × 10<sup>-2</sup> cm<sup>2</sup>/Vs respectively. A maskless lithography method has been employed for the fabrication of the devices and tests were carried out using a Keithley parameter analyser, Raman and photoluminescence (PL) spectroscopy. The PL spectra showed that the

exfoliated WSe<sub>2</sub> has a bandgap of 1.6 eV while the PLD WSe<sub>2</sub> possessed no bandgap, thereby limiting its applications.

We studied the breakdown characteristics of a 20 nm anodic tantalum, a potential high dielectric gate oxide. At an electric field of 1.5 MV/cm, the leakage current extracted for the as-deposited, 200 °C and 400 °C annealed anodic tantalum are 10<sup>-5</sup>, 10<sup>-2</sup> and 1 A/cm<sup>2</sup> respectively while the breakdown field is 5.4, 5.1 and 3.3 MV/cm respectively. Upon integration of the anodic tantalum with a WSe<sub>2</sub> FET, a field effect mobility of 0.9 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> has been realised.

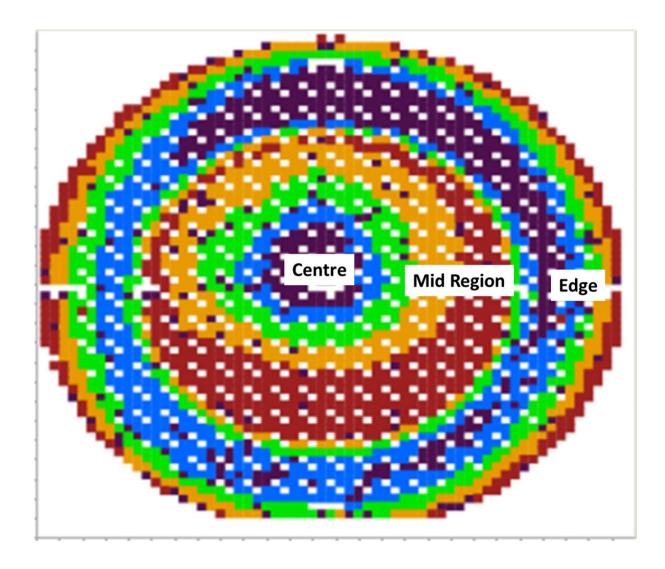

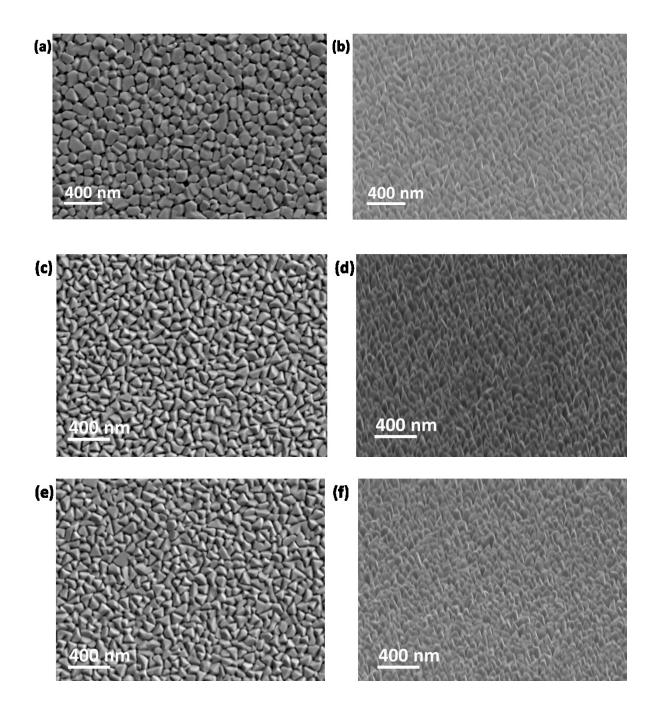

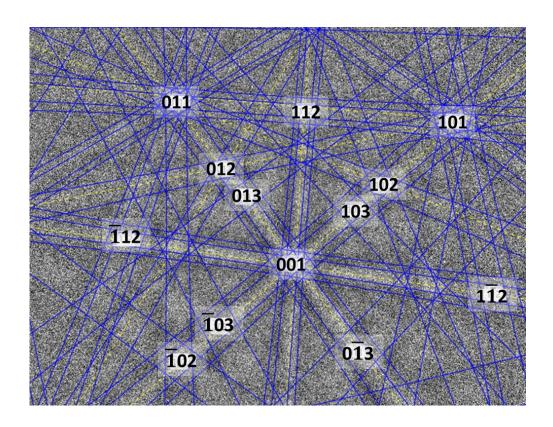

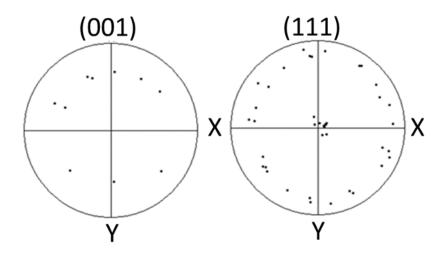

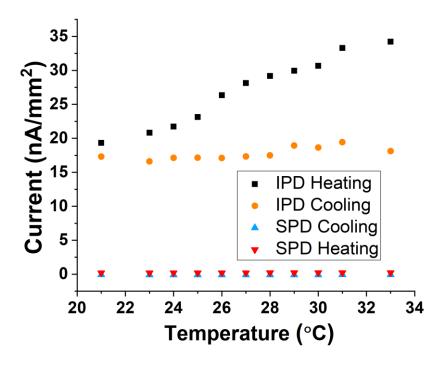

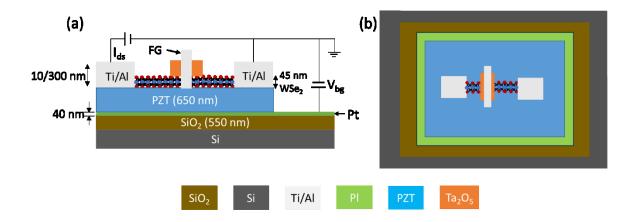

Analysis has also been conducted on the PZT pyroelectric device to understand its surface profile using energy backscatter diffraction (EBSD) and a factorial design of experiment. From the EBSD analysis, the sputtered PZT possesses a grain size of about 100 nm and exists in tetragonal crystals having good correlation for an orientation along the [111] direction normal to the surface. Results and understanding from the factorial design of the experiment enabled the integration of PZT with a WSe<sub>2</sub> FET. While the standalone PZT based sensor possesses a 1 nA/mm<sup>2</sup> current density output, the integrated PZT based WSe<sub>2</sub> FET has an output of 16 nA/mm<sup>2</sup>. This improvement in the overall current output is over ten orders of magnitude. Thus, we have succeeded in amplifying the output of the PZT pyroelectric based sensor.

The experimental outcomes of this thesis would help the research community in developing higher performing integrated sensors and possibly exposing other areas of interest on inexpensive and simple methods for producing materials with high dielectric constants.

# **Journal Publications**

- **S. C. Mbisike**, S. Seo, S. Lee, J. Phair, and R. Cheung, "Parametric study of pulsed laser deposited (PLD) WSe<sub>2</sub> 2D transistors," Microelectron. Eng., vol. 230, p. 111368, Jun. 2020, doi: 10.1016/j.mee.2020.111368.

- **S. C. Mbisike**, L. Eckart, J. W. Phair, P. Lomax, and R. Cheung, "Amplification of pyroelectric device with WSe<sub>2</sub> field effect transistor and ferroelectric gating," J. Appl. Phys., vol. 131, no. 14, p. 144101, Apr. 2022, doi: 10.1063/5.0086216

- **S. C. Mbisike**, Andreas Tsiamis, Peter Lomax and Rebecca Cheung, "Anodic Tantalum: Fabrication, Breakdown Characteristics of Capacitor and Integration with a WSe<sub>2</sub> Field Effect Transistor", Solid-state electronics, Vol.196, p.108423, 2022, DOI: 10.1016/j.sse.2022.108423

# **Table of Contents**

| DECLARATION                                                                | i   |

|----------------------------------------------------------------------------|-----|

| ACKNOWLEDGMENT                                                             | ii  |

| ABSTRACT                                                                   | v   |

| Journal Publications                                                       | vii |

| List of Figures                                                            | xii |

| List of Tables                                                             | XV  |

| Abbreviations and Acronyms                                                 | xvi |

| Chapter 1                                                                  | 1   |

| Introduction                                                               | 1   |

| 1.1 Overview                                                               | 1   |

| 1.2 Aims and Objectives                                                    | 3   |

| 1.3 Research Review                                                        | 4   |

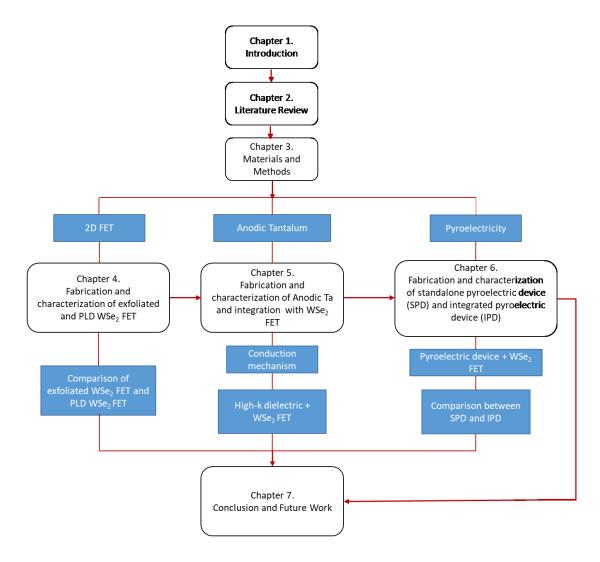

| 1.4 Thesis Structure                                                       | 5   |

| Chapter 2                                                                  | 8   |

| Literature Review                                                          | 8   |

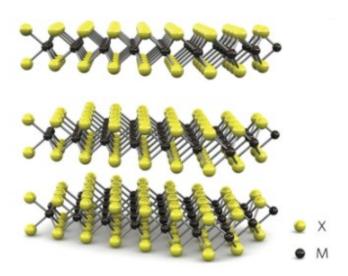

| 2.1 Background of two dimensional (2D) materials                           | 8   |

| 2.1.1 Exfoliated tungsten diselenide (X-WSe <sub>2</sub> )                 | 9   |

| 2.1.2 Pulsed laser deposition (PLD) WSe <sub>2</sub>                       | 11  |

| 2.1.3 Timeline of 2D Materials                                             | 12  |

| 2.2 Dielectrics                                                            | 15  |

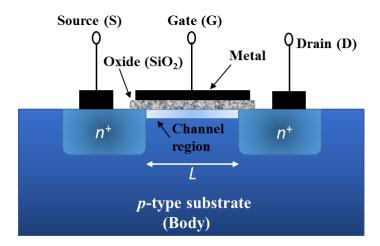

| 2.2.1 Silicon dioxide (SiO <sub>2</sub> ) - The gate dielectric            | 15  |

| 2.2.1.1 Scaling and performance                                            | 17  |

| 2.2.1.2 Scaling challenges of SiO <sub>2</sub>                             | 19  |

| 2.2.2 High-κ dielectric                                                    | 20  |

| 2.2.2.1 Characteristics of high-κ dielectric required for CMOS application | 21  |

| 2.2.2.2 Anodization                                                        | 23  |

| 2.2.3 Application of novel high-κ dielectric                               | 24  |

| 2.2.3.1 Ferroelectric gate field effect transistor (FeFET)                 | 24  |

| 2.3 Pyroelectricity                                                        | 26  |

| 2.3.1 Ferroelectricity                                                     | 29  |

| 2.3.1.1 Perovskites                                                        | 30  |

| 2.3.1.2 Lead Zirconate Titanate (PZT)                                      | 31  |

| 2.3.2 Applications of Polar Materials                                      | 32  |

| 2.4 Conclusions                                                            | 37  |

| Chapter 3                                                                                                                                                                     | 37                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Materials and Methods                                                                                                                                                         | 37                 |

| 3.1 Preparation and deposition of exfoliated WSe <sub>2</sub> (X-WSe <sub>2</sub> )                                                                                           | 37                 |

| 3.1.1 Substrate preparation                                                                                                                                                   | 38                 |

| 3.1.2 WSe <sub>2</sub> deposition                                                                                                                                             | 38                 |

| 3.2 Deposition of pulse laser deposited (PLD) WSe <sub>2</sub>                                                                                                                | 39                 |

| 3.3 Atomic Force Microscopy (AFM)                                                                                                                                             | 41                 |

| 3.4 Raman and photoluminescence (PL) spectroscopy tool                                                                                                                        | 42                 |

| 3.4.1 Raman spectroscopy                                                                                                                                                      | 43                 |

| 3.4.2 Photoluminescence (PL) spectroscopy                                                                                                                                     | 46                 |

| 3.5 Anodic tantalum development                                                                                                                                               | 47                 |

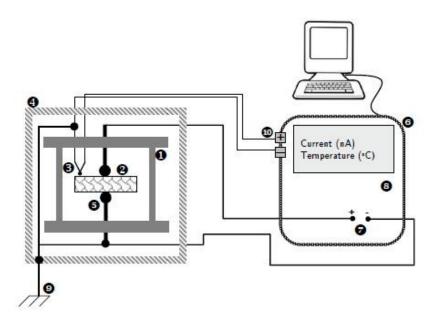

| 3.6 Pyroelectric current measurement                                                                                                                                          | 50                 |

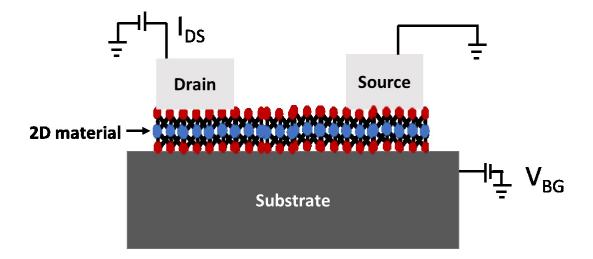

| 3.7 Two-dimensional (2D) material field effect transistor (FET) Test Setup                                                                                                    | 54                 |

| 3.8 Conclusions                                                                                                                                                               | 55                 |

| Chapter 4                                                                                                                                                                     | 56                 |

| Fabrication and electrical characterization of pulsed laser deposited WSe <sub>2</sub> (PLD-WSexfoliated WSe <sub>2</sub> (X-WSe <sub>2</sub> ) field effect transistor (FET) |                    |

| 4.1 Introduction                                                                                                                                                              | 56                 |

| 4.2 Experimental                                                                                                                                                              | 57                 |

| 4.2.1 Deposition of exfoliated WSe <sub>2</sub> (X-WSe <sub>2</sub> ) and pulse laser deposited (PLD-WSe                                                                      | e <sub>2</sub> )57 |

| 4.2.2 Fabrication of WSe <sub>2</sub> field effect transistor (FET)                                                                                                           | 60                 |

| 4.2.3 Electrical characterization of X-WSe <sub>2</sub> and PLD-WSe <sub>2</sub> FET's                                                                                        | 62                 |

| 4.3 Results and Discussion                                                                                                                                                    | 63                 |

| 4.3.1 Optical Characteristics                                                                                                                                                 | 63                 |

| 4.3.1.1 Raman spectroscopy                                                                                                                                                    | 64                 |

| 4.3.1.2 Photoluminescence spectroscopy                                                                                                                                        | 68                 |

| 4.3.2 Transfer Characteristics                                                                                                                                                | 70                 |

| 4.3.2.1 Exfoliated WSe <sub>2</sub> (X-WSe <sub>2</sub> ) FET                                                                                                                 | 70                 |

| 4.3.2.2 Pulsed Laser Deposited (PLD-WSe <sub>2</sub> ) FET                                                                                                                    | 73                 |

| 4.3.2.3 Transfer Length Measurement (TLM)                                                                                                                                     |                    |

|                                                                                                                                                                               |                    |

| 4.4 Conclusions                                                                                                                                                               |                    |

| Chapter 5                                                                                                                                                                     |                    |

| Anodic tantalum: fabrication, breakdown characteristics of capacitor and integration WSe <sub>2</sub> field effect transistor                                                 |                    |

| 5.1 Introduction                                                                                                                                                              | 78                 |

| 5.2 Experimental                                                                                                                                     | 79          |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 5.2.1 Anodic tantalum                                                                                                                                | 79          |

| 5.2.2 Fabrication of Ta <sub>2</sub> O <sub>5</sub> capacitor                                                                                        | 81          |

| 5.2.3 Fabrication of WSe <sub>2</sub> FET based on Ta <sub>2</sub> O <sub>5</sub>                                                                    | 83          |

| 5.3 Results and Discussion                                                                                                                           | 85          |

| 5.3.1 Anodic tantalum (Ta <sub>2</sub> O <sub>5</sub> ) capacitor                                                                                    | 85          |

| 5.3.1.1 Current voltage (I-V) asymmetry for the Ta <sub>2</sub> O <sub>5</sub> capacitor                                                             | 86          |

| 5.3.1.2 Capacitor-voltage (CV) hysteresis                                                                                                            | 87          |

| 5.3.1.3 Capacitor-voltage (CV) electrode area test for calculating dielectric const                                                                  | ant (к)89   |

| 5.3.2 Conduction mechanism                                                                                                                           | 91          |

| 5.3.3 WSe <sub>2</sub> FET based on anodic tantalum                                                                                                  | 97          |

| 5.4 Conclusions                                                                                                                                      | 100         |

| Chapter 6                                                                                                                                            | 101         |

| Integration of pyroelectric device with WSe <sub>2</sub> field effect transistor                                                                     | 101         |

| 6.1 Introduction                                                                                                                                     | 101         |

| 6.2 Experimental                                                                                                                                     | 102         |

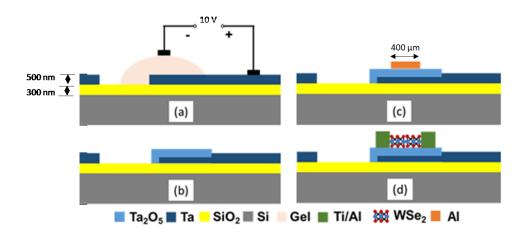

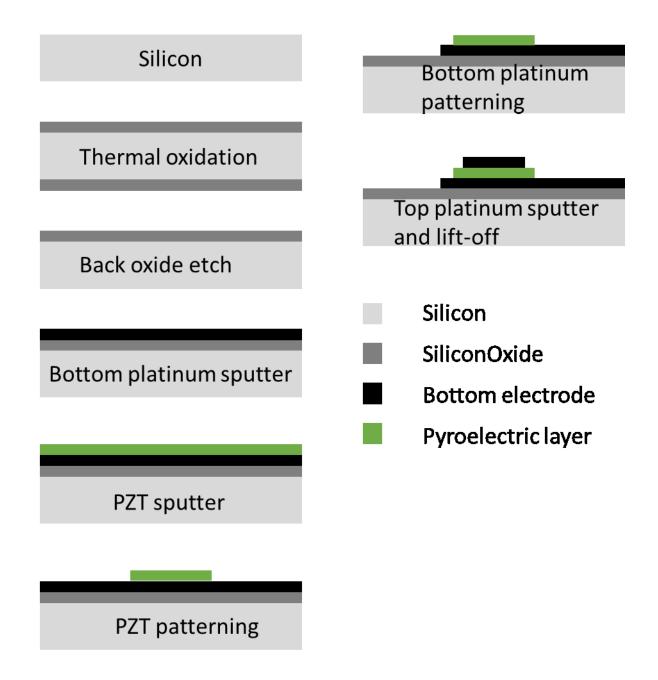

| 6.2.1 Fabrication of standalone pyroelectric device (SPD)                                                                                            | 102         |

| 6.2.2 Fabrication of integrated pyroelectric device (IPD)                                                                                            | 104         |

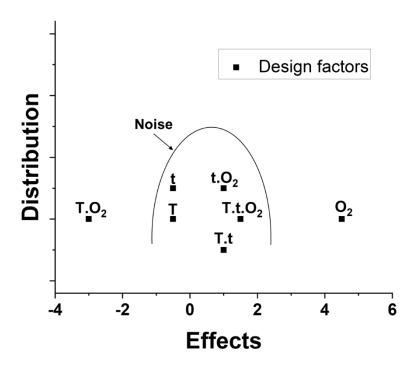

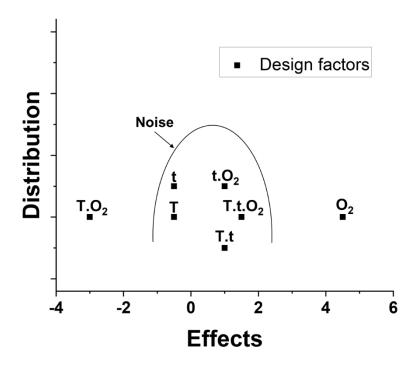

| 6.2.2.1 Design of experiment (DoE) to improve WSe <sub>2</sub> adhesion on PZT                                                                       | 105         |

| 6.3 Results and Discussions.                                                                                                                         | 109         |

| 6.3.1 PZT Surface characteristics - investigation of PZT surface using a scanni microscope (SEM) and electron backscatter diffraction (EBSD) imaging | _           |

| 6.3.2 Electrical Characteristics                                                                                                                     | 114         |

| 6.3.2.1 Standalone Pyroelectric Device (SPD)                                                                                                         | 114         |

| 6.3.2.2 Integrated Pyroelectric Device (IPD)                                                                                                         | 118         |

| 6.4 Conclusions                                                                                                                                      | 124         |

| Chapter 7                                                                                                                                            | 124         |

| Conclusions and future work                                                                                                                          | 124         |

| 7.1 Final Conclusion                                                                                                                                 | 124         |

| 7.2 Achieved Objectives                                                                                                                              | 125         |

| 7.3 Future Work                                                                                                                                      | 126         |

| 8. References                                                                                                                                        | 128         |

| Appendix A – Run sheet of WSe <sub>2</sub> FET fabrication – Chapter 4                                                                               | 140         |

| Appendix B - Run sheet of anodic tantalum production and capacitor fabrication - Ch                                                                  | apter 5 143 |

| Appendix C - Full factorial computation                                                                                                              | 144         |

| Appendix D – AFM Graphs (X-WSe <sub>2</sub> and PLD WSe <sub>2</sub> )                                                                               | 147         |

| Appendix E - | Fits of Raman plot | s (X-WSe <sub>2</sub> and PLD | ) WSe <sub>2</sub> ) | 149 |

|--------------|--------------------|-------------------------------|----------------------|-----|

|--------------|--------------------|-------------------------------|----------------------|-----|

# **List of Figures**

| Figure 1.1: Thesis Structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |

| Figure 2.1: Hexagonal structure of a TMD [14]                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                    |

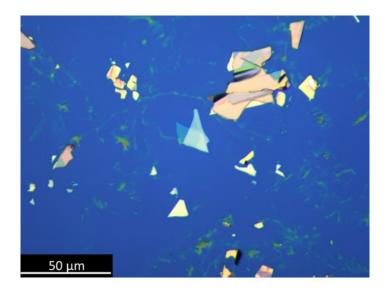

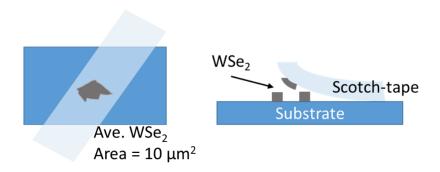

| Figure 2.2: Picture of exfoliated WSe <sub>2</sub> on a SiO <sub>2</sub> /Si substrate (SMC cleanroom, University of Exercise 2.2) Picture of exfoliated WSe <sub>2</sub> on a SiO <sub>2</sub> /Si substrate (SMC cleanroom, University of Exercise 2.2)                                                                                                                                                                                                                        | -                                    |

| Edinburgh).                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                   |

| Figure 2.3: The n-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

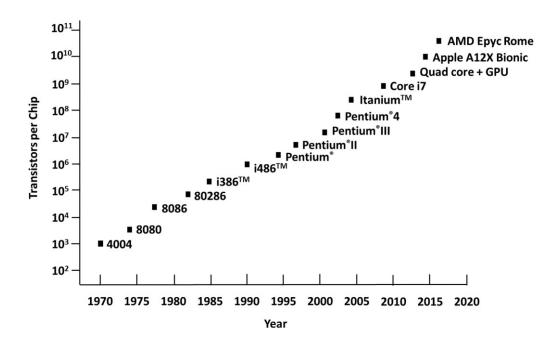

| Figure 2.4: Moore's Law [45], [51]                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |

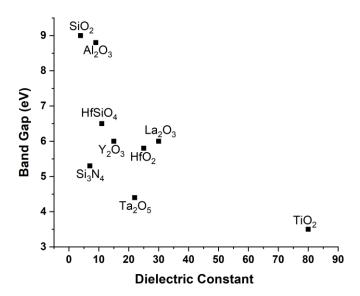

| Figure 2.5: Relationship between bandgap and dielectric constant for some high-κ materia                                                                                                                                                                                                                                                                                                                                                                                         |                                      |

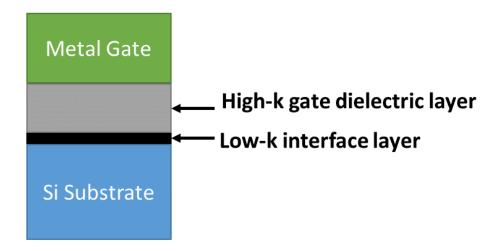

| Figure 2.6: Low-κ interface layer formed between high-κ gate and silicon substrate                                                                                                                                                                                                                                                                                                                                                                                               |                                      |

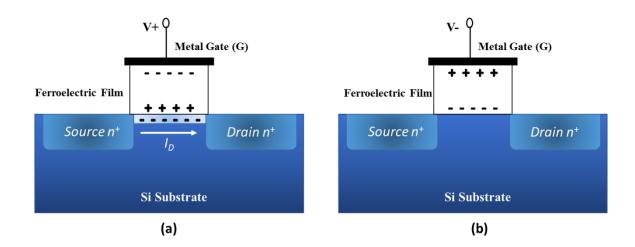

| Figure 2.7: Schematic of a FeFET: (a) on state (b) off state                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      |

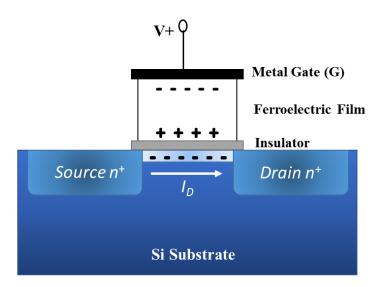

| Figure 2.8: Schematic of the MFIS.                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |

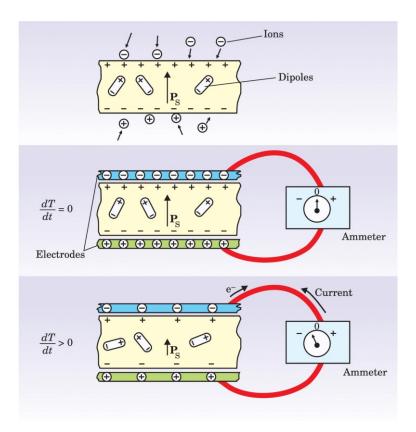

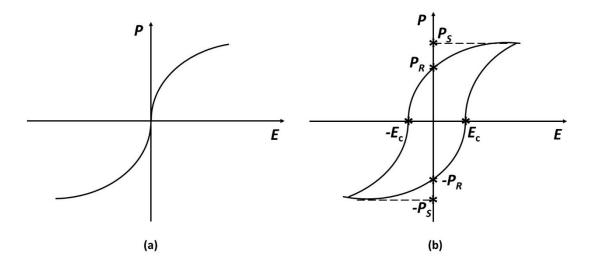

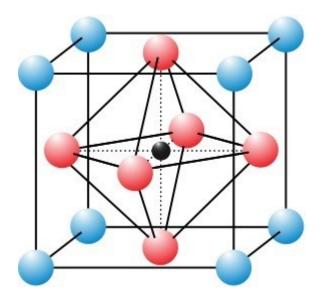

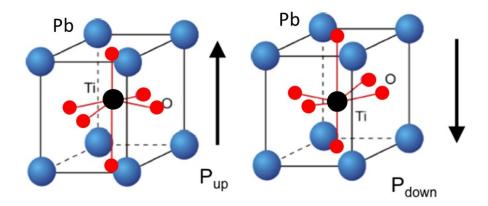

| Figure 2.9: The pyroelectric effect [71]. Dipole of a pyroelectric material (top), showing distribution on the material surface. Electrodes placed on opposite surfaces of the materia a circuit with an ammeter (middle) showing no flow of current. Current begins to flow as of a change in temperature of the pyroelectric material (bottom).  Figure 2.10: (a) Polarisation vs electric field ( <i>P-E</i> ) of a polar dielectric (b) Hysteresis logerroelectric material. | l forms<br>a result<br>27<br>op of a |

| Figure 2.11: The perovskite structure. The blue spheres represent the monovalent or divalent                                                                                                                                                                                                                                                                                                                                                                                     |                                      |

| at the (A sites), the red spheres are the tetra- or pentavalent cation (B sites) and the black sp                                                                                                                                                                                                                                                                                                                                                                                |                                      |

| the oxygen ion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |

| Figure 2.12: Schematic of PZT unit cell [78].                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |

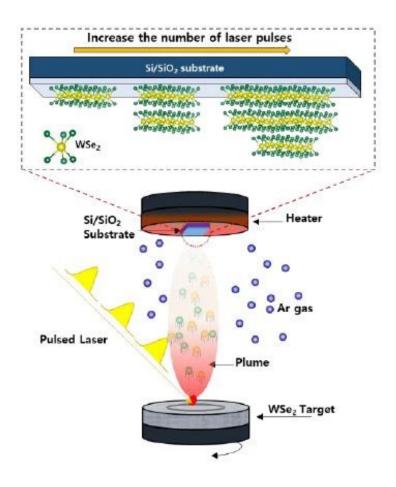

| Figure 3.1: Schematic of exfoliation and transfer of 2D WSe <sub>2</sub> onto a SiO <sub>2</sub> /Si substrate Figure 3.2: Schematic illustrating the working principle of PLD [20]. Performed at the clean                                                                                                                                                                                                                                                                      | n room                               |

| of the Gwangju Institute of Science and Technology, Korea                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |

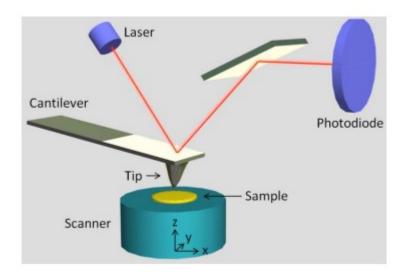

| Figure 3.3: Schematic illustration of the working principle of an AFM [118]. The laser by                                                                                                                                                                                                                                                                                                                                                                                        |                                      |

| deflected off the back of the cantilever and onto a photodiode detector. The bending                                                                                                                                                                                                                                                                                                                                                                                             |                                      |

| cantilever displaces the laser spot on the photodiode                                                                                                                                                                                                                                                                                                                                                                                                                            |                                      |

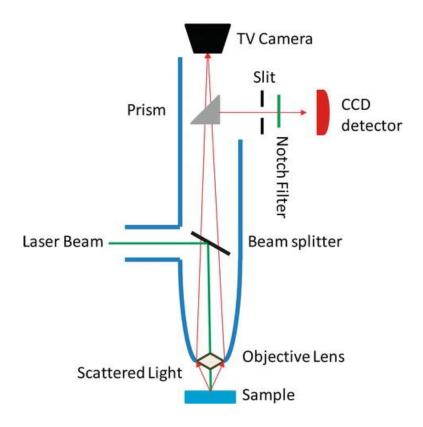

| Figure 3.4: Conventional Raman / PL Microscope [119].                                                                                                                                                                                                                                                                                                                                                                                                                            |                                      |

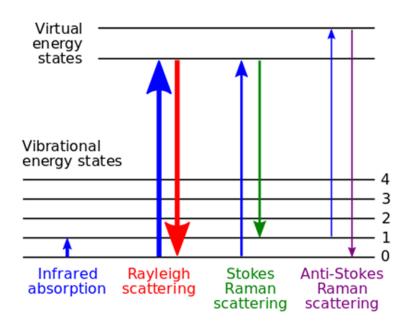

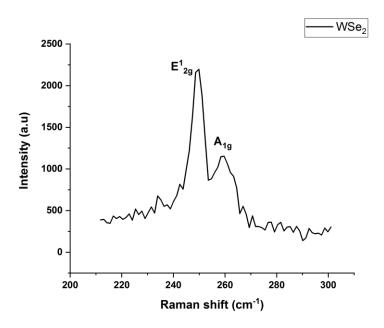

| Figure 3.5: Energy level diagram showing the states involved in Raman spectra [121] Figure 3.6: Raman Spectrum of X-WSe <sub>2</sub> .                                                                                                                                                                                                                                                                                                                                           |                                      |

| Figure 3.7: Photoluminescence Spectrum of X-WSe <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      |

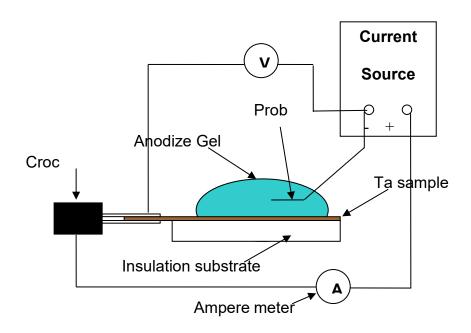

| Figure 3.8: Diagram of tantalum anodization System [130].                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |

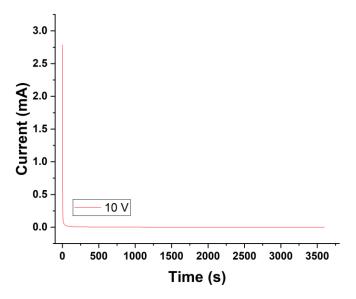

| Figure 3.9: Anodization current vs time graph.                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |

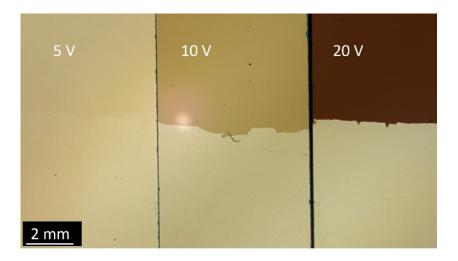

| Figure 3.10: Anodic tantalum prepared with an applied potential of 5 V, 10 V and 20 V                                                                                                                                                                                                                                                                                                                                                                                            |                                      |

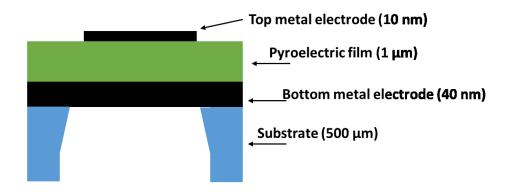

| Figure 3.11: Typical pyroelectric IR sensor.                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51                                   |

| Figure 3.12: Setup used for measuring pyroelectric current showing probe connection to the                                                                                                                                                                                                                                                                                                                                                                                       | device                               |

| [133]                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52                                   |

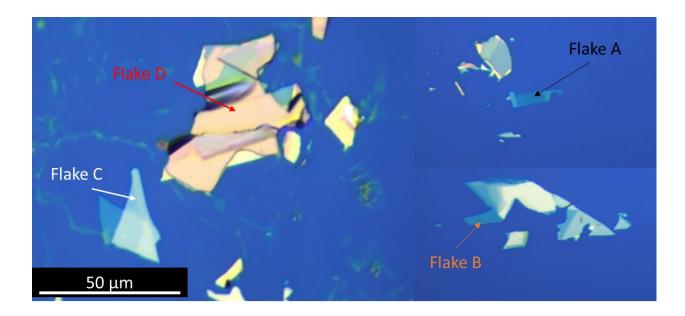

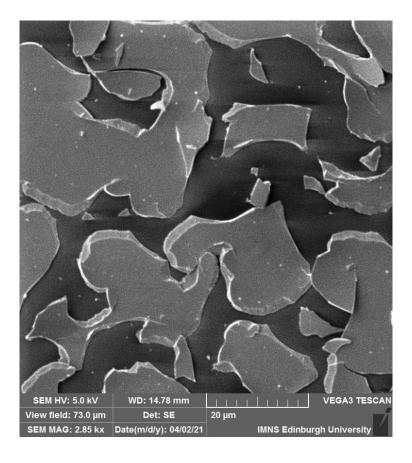

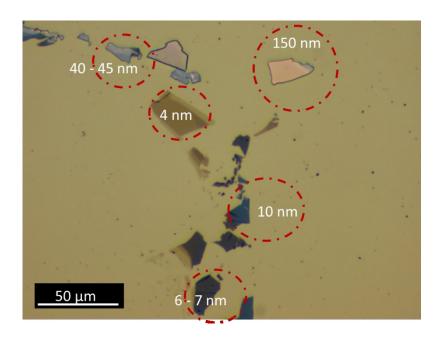

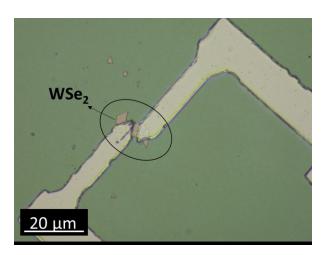

| Figure 4.1: X-WSe <sub>2</sub> flake of various thicknesses and dimensions on SiO <sub>2</sub> substrate57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

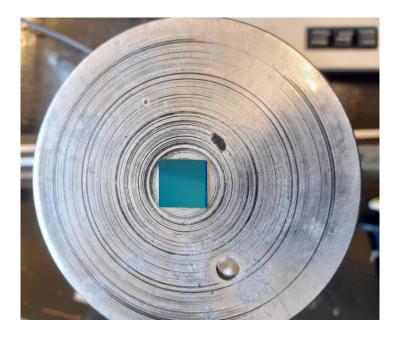

| Figure 4.2: PLD WSe <sub>2</sub> deposited across a 1.5 by 1.5 cm chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

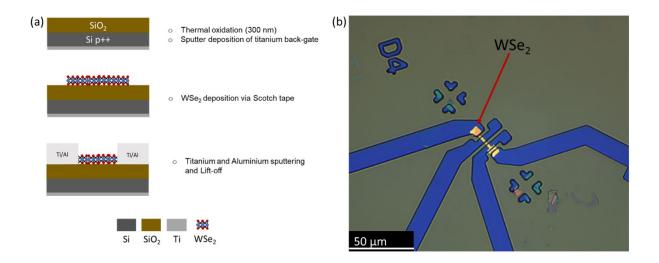

| Figure 4.3: Fabrication of X-WSe <sub>2</sub> FET: (a) Schematic outlining the fabrication process (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Lithographic pattern prior to metal deposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

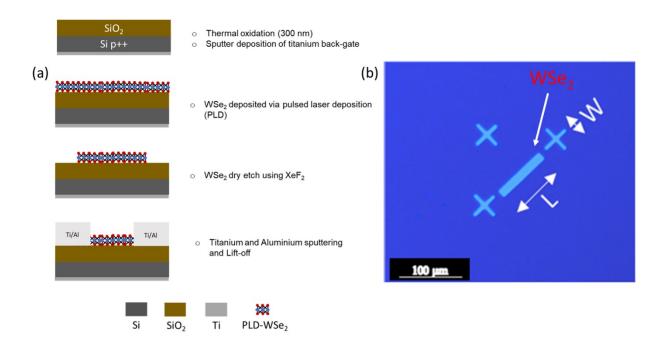

| Figure 4.4: (a) Schematic outlining the fabrication process of PLD-WSe <sub>2</sub> FET (b) Patterned PLD-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| WSe <sub>2</sub> channel using vapour XeF <sub>2</sub> 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

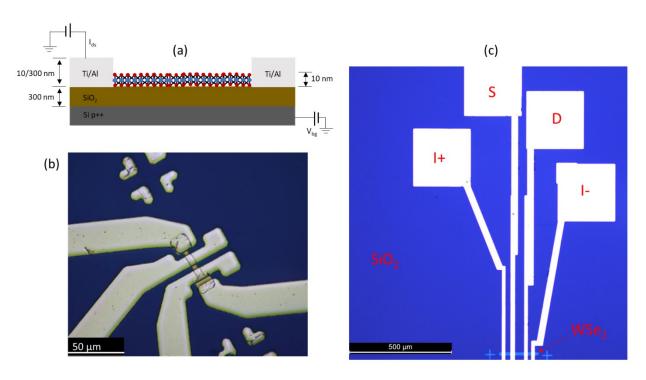

| Figure 4.5: (a) Schematic of the fabricated WSe <sub>2</sub> FET showing geometrical dimensions; Actual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| device fabricated on SiO <sub>2</sub> / Si substrate: (b) X-WSe <sub>2</sub> FET (c) PLD-WSe <sub>2</sub> FET62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

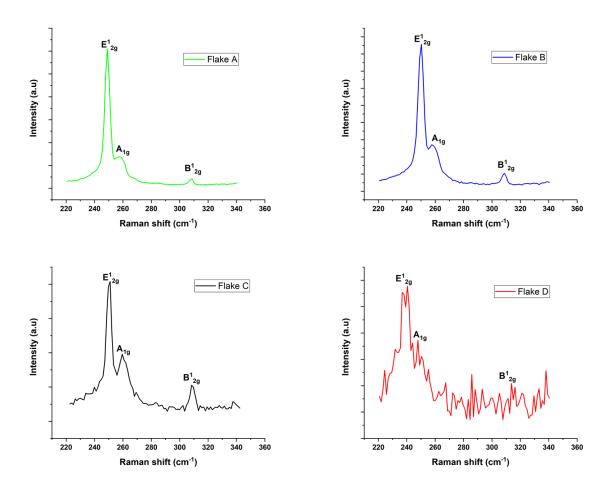

| Figure 4.6: Raman spectroscopy of singular plots of exfoliated WSe <sub>2</sub> flakes A, B, C and D64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

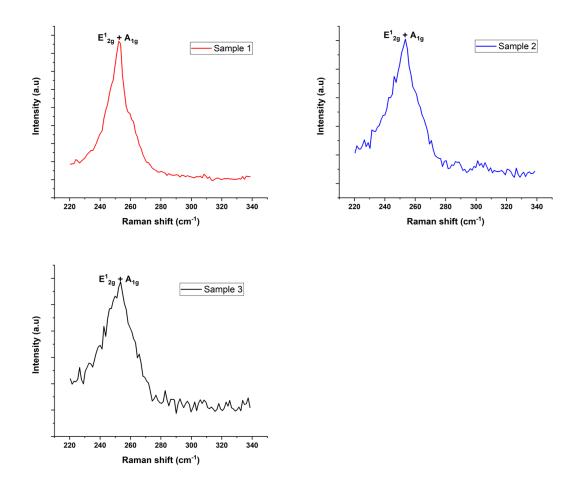

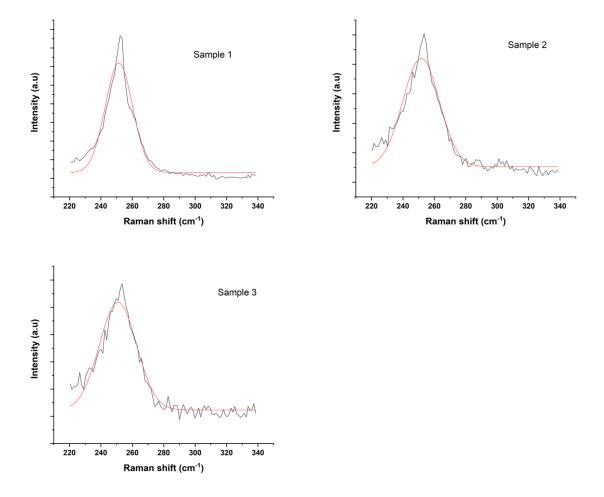

| Figure 4.7: Raman spectroscopy of singular plots of PLD sample 1, 2 and 365                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

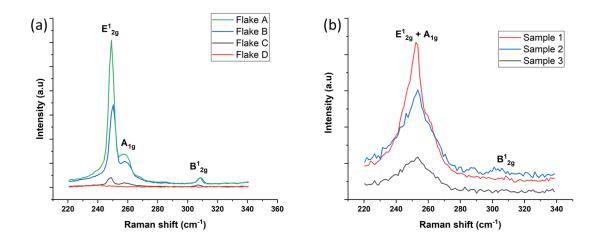

| Figure 4.8: Raman Spectroscopy of combined (a) X-WSe <sub>2</sub> (b) PLD-WSe <sub>2</sub> 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

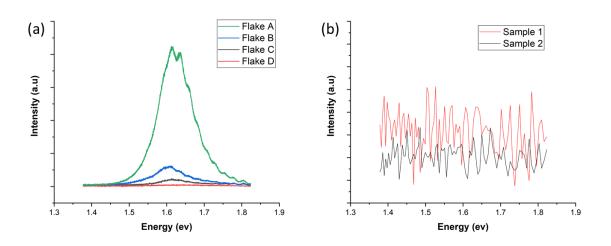

| Figure 4.9: PL Spectroscopy of (a) X-WSe <sub>2</sub> and (b) PLD-WSe <sub>2</sub> 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

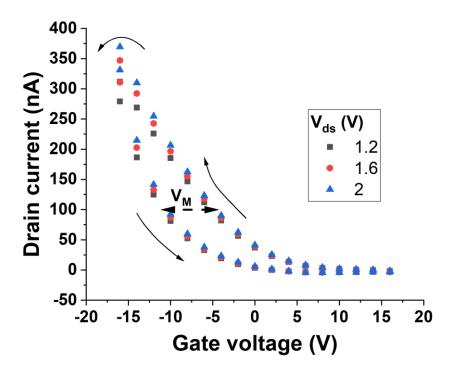

| Figure 4.10: Transfer Characteristics of X-WSe <sub>2</sub> FET with a channel area of 5 by 2 μm. (a) Pristine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| (b) XeF <sub>2</sub> treated70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

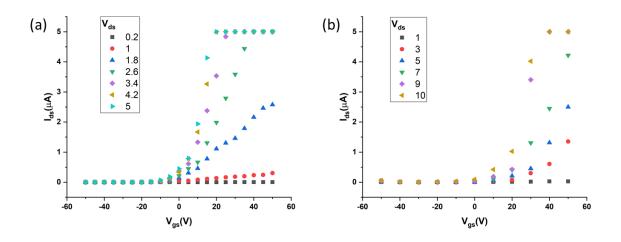

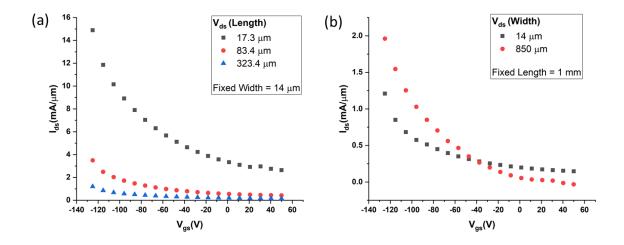

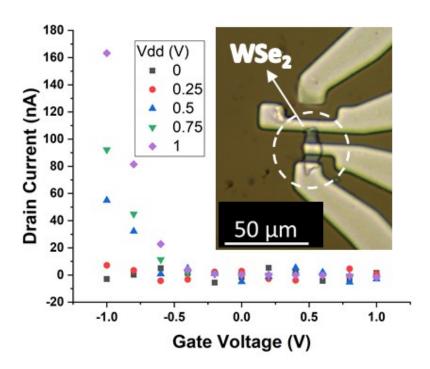

| Figure 4.11: Transfer characteristics for PLD WSe <sub>2</sub> transistor; (a) for different lengths (17.3, 83.4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| and 323.4 µm) and fixed width (14 µm); (b) for different widths (14 and 850 µm) and fixed length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $(1000 \ \mu m)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

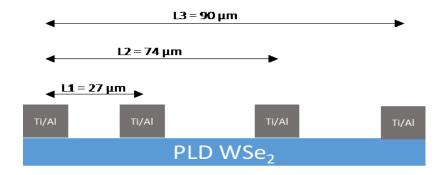

| Figure 4.12: TLM electrode spacing76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

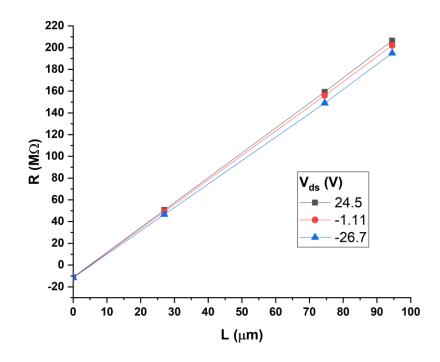

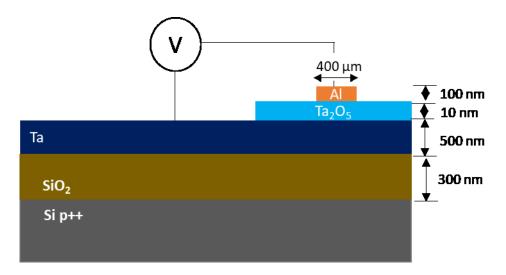

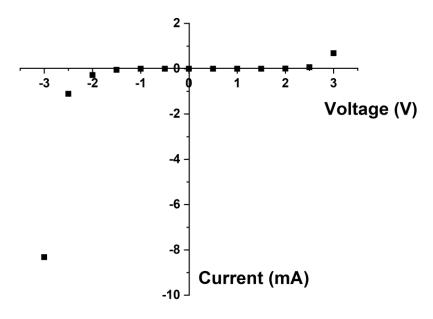

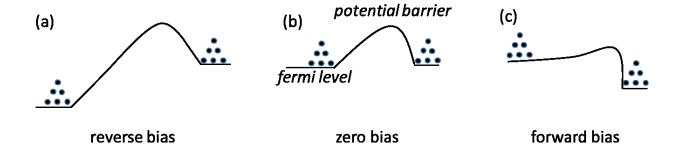

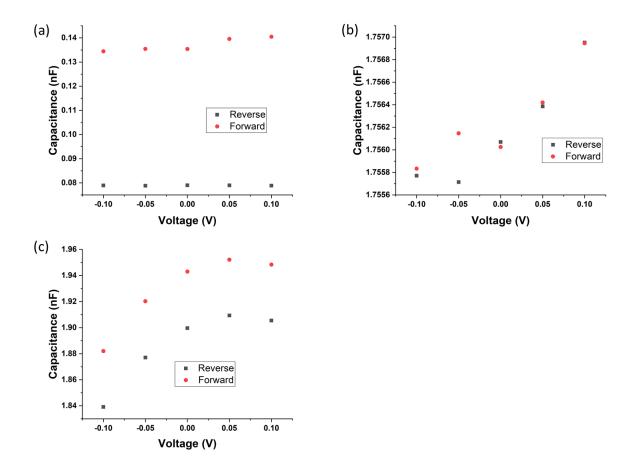

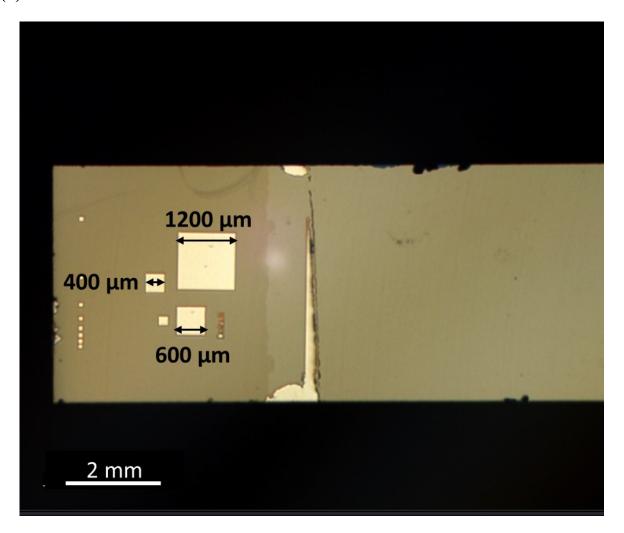

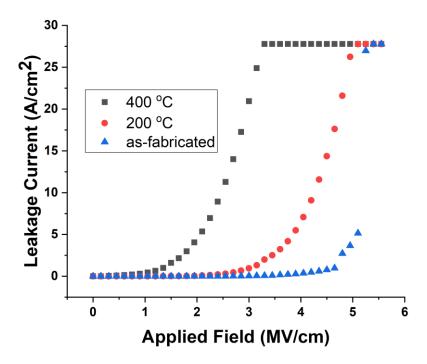

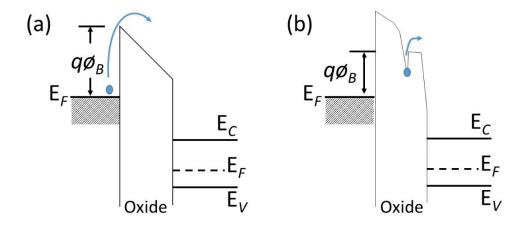

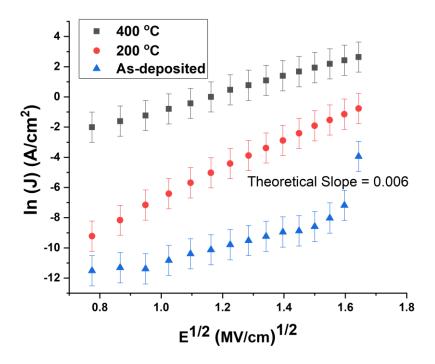

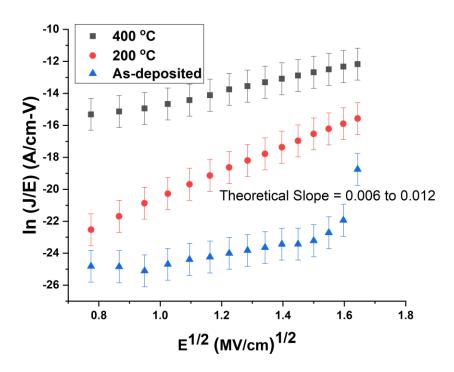

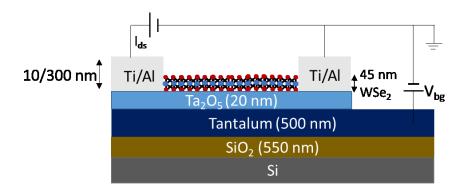

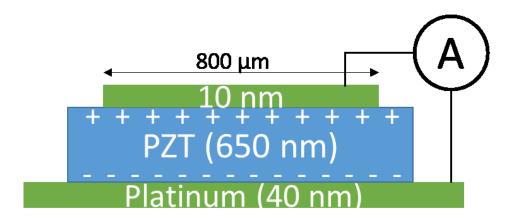

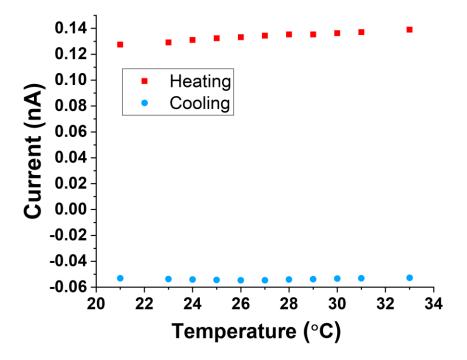

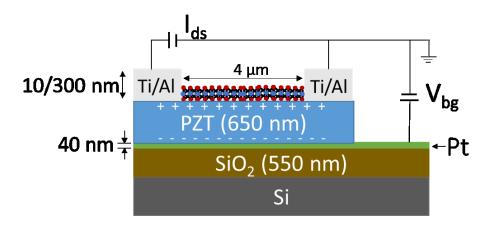

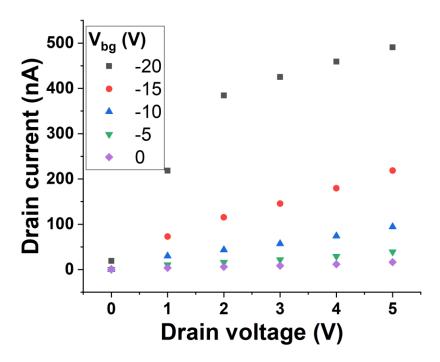

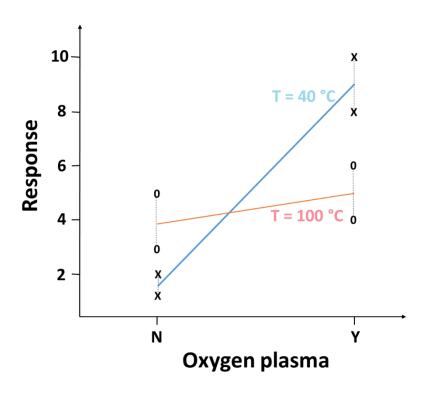

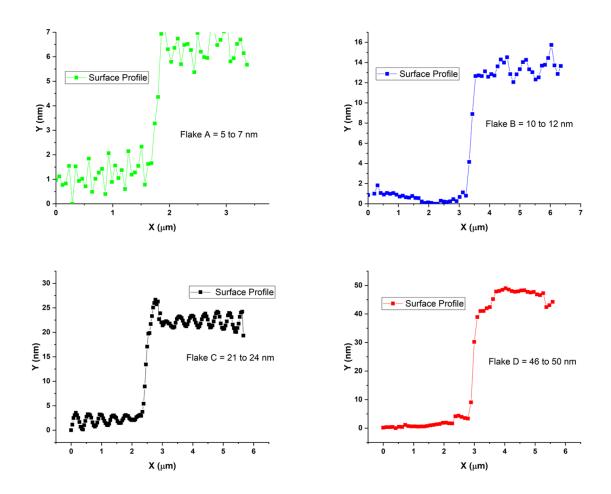

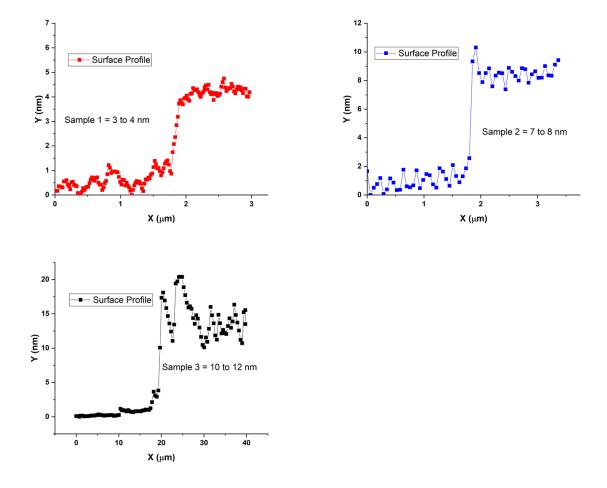

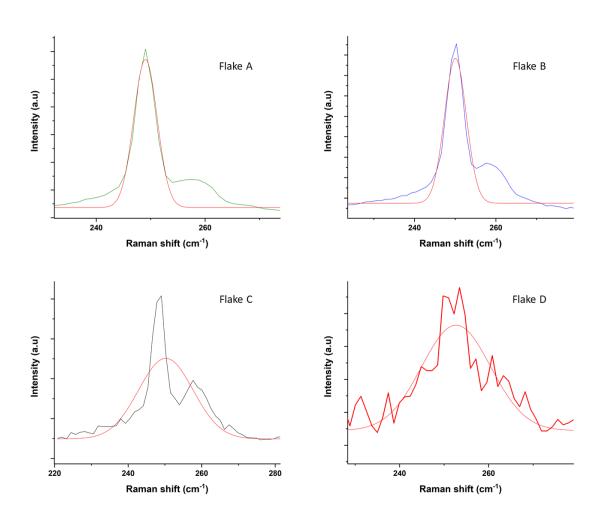

| Figure 4.13: Resistance values of the transistors plotted against their electrode spacing at various                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |