Wayne State University

Wayne State University Dissertations

1-1-2016

# Substrate Effects And Dielectric Integration In 2d Electronics

Bhim Prasad Chamlagain *Wayne State University,*

Follow this and additional works at: https://digitalcommons.wayne.edu/oa\_dissertations Part of the <u>Materials Science and Engineering Commons</u>, <u>Nanoscience and Nanotechnology</u> <u>Commons</u>, and the <u>Physics Commons</u>

#### **Recommended** Citation

Chamlagain, Bhim Prasad, "Substrate Effects And Dielectric Integration In 2d Electronics" (2016). *Wayne State University Dissertations*. 1631. https://digitalcommons.wayne.edu/oa\_dissertations/1631

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

# SUBSTRATE EFFECTS AND DIELECTRIC INTEGRATION IN 2D ELECTRONICS

by

# **BHIM PRASAD CHAMLAGAIN**

# DISSERTATION

Submitted to the Graduate School

of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

# **DOCTOR OF PHILOSOPHY**

2016

MAJOR: PHYSICS

Approved By:

Advisor Date

# © COPYRIGHT BY

# **BHIM PRASAD CHAMLAGAIN**

2016

All Rights Reserved

# DEDICATION

Dedicated to the memory of my mother

Tika Devi Chamlagain who gave me everything

#### ACKNOWLEDGEMENTS

First of all, I want to give thanks to Wayne State University, Department of Astronomy for providing opportunity to fulfill my and my family dream. It is my good fortune to get very cooperative supervisor Prof. Dr. Zhixian Zhou. I would like to extend my deep sense of gratitude to my supervisor for providing me all research facilities as well as the valuable guidance, help and advice. During my projects in progress, his scientific support, helpfulness, encouragement and valuable suggestions kept me constantly motivated to do research work. He showed great generosity in carrying out the all works and examination of every steps of process. I learnt not only the various techniques to carry out different research works in nano-fabrication fields but also get suggestions to tackle difficult situations. I would like to thank committee members Dr. Ashis Mukhopadhyay, Dr. Jian Huang, Dr. Mark Ming-Cheng Cheng for their valuable time and advice. I would also extend my sincere gratitude to all the teachers especially Prof. Z. Zhou, Prof. A. Majumder, Prof. P. Keyes, Prof. S. Voloshin, Prof. G. Lawes, Prof. R. Naik, Prof. B. Nadgorny who taught me and helped me in understanding the fundamentals of physics, its related disciplines and even advise me to tackle my personal problems. I would like to extend my deep gratitude to Prof. J. Wadehra who gave me guidance as a graduate advisor from the beginning day at Wayne State University.

It is impossible to list name of all of my friends who have given me help, encouragement, advice and well wishes during the time of work and taking classes in Wayne State University. I wish to express my sincere thanks to all my friends who help me directly or indirectly to achieve my goal. I could not remain without giving thanks to my friends Dr. M. W. Lin, Mr. H .J. Chuang, Mr. M. M. Perera, Mr. S. Paudal and other colleagues in our research group. Special thank goes to Dr. Qingsong Cui for sharing ideas and working together to make it happened of

some challenging projects. I appreciate Dr. Xuebin Tan, Mr. Bill Funk and Mr. Dan Durisin from ECE for the help in clean room. Thanks to Mr. Ehab AbdElhamid for helping me to use PPMS. I received a tremendous amount of co-operation from them. Special thanks to all collaborators who played vital role in my research work, progress and publications. I am also thankful to all other friends who did teamwork to solve homework problems and sharing educational knowledge.

I thank my parents and family who are my greatest belief and best mentor. My mother always encouraged me to step up and do something extra more. Perfect expression of remembrance is beyond my humble ability in this short acknowledgement and her image always shakes me to hold her dream tightly. I would like to dedicate to this entire work to the memory of my mother who gave me everything. I am grateful to my wife Saraswoti who managed to take care of everything in home to make me free to engage in research work entirely and two little flowers, Subhi and Subha, who gave me smile when I left & came back home. Finally, I would like to express sincere thanks to all my teachers who taught me from beginning of school to university and all people who directly/indirectly, positively/negatively inspired me to achieved goal.

| DEDICATION ii                                                           |

|-------------------------------------------------------------------------|

| ACKNOWLEDGEMENTS iii                                                    |

| LIST OF TABLE ix                                                        |

| LIST OF FIGURES x                                                       |

| LIST OF ABBRIVATIONS xv                                                 |

| CHAPTER 1: GENERAL INTRODUCTION                                         |

| 1.1 TWO DIMENSIONAL MATERIALS1                                          |

| 1.1.1 TRANSITION METAL DICHALCONIDES (TMDs)                             |

| 1.1.1.1 MOLYBDENUM DISULFIDE                                            |

| 1.1.1.2 MOLYBDENIUM DISELENIDE                                          |

| 1.1.2 BLACK PHOSPHORUS 6                                                |

| 1.2 SYNTHESIS OF 2D MATERIALS7                                          |

| 1.3 TRANSPORT PROPERTIES AND DEVICE PERFORMANCE OF 2D<br>SEMICONDUCTORS |

| 1.4 FACTORS RELATED TO TRANSPORT PROPERTIES OF 2D<br>SEMICONDUCTORS     |

| 1.4.1 SEMICONDUCTOR AND ELECTRODE (METAL) CONTACT 11                    |

| 1.4.2 CARRIERS SCATTERING MECHANISMS 11                                 |

| 1.5 DIELECTRIC INTEGRATION                                              |

| 1.6 SCOPE OF THE DISSERTATION 18                                        |

| CHAPTER 2: MAJOR EXPERIMENTAL TECHNIQUES                                |

| 2.1 OPTICAL MICROSCOPE                                                  |

| 2.2 ATOMIC FORCE MICROSCOPE (AFM)                                       |

# **TABLE OF CONTENTS**

| 2.3 SCANNING ELECTRON MICROSCOPE (SEM)22                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.4 BJD 1800 e-BEAM METAL EVAPORATOR24                                                                                                                                          |

| 2.5 ULVAC MILA-5000 ANNEALING TOOL                                                                                                                                              |

| 2.5 KEITHLEY 4200 SEMICONDUCTOR PARAMETER ANALYSER26                                                                                                                            |

| 2.6 PHYSICAL PROPERTY MEASUREMENT SYSTEM 27                                                                                                                                     |

| 2.7 LCR METER                                                                                                                                                                   |

| <b>CHAPTER 3</b> : STUDY OF INTRINSIC AND SUBSTRATE DEPENDENCE TRANSPORT<br>PROPERTIES OF MoS <sub>2</sub> FIELD EFFECT TRANSISTOR                                              |

| 3.1 INTRODUCTION                                                                                                                                                                |

| 3.2 EXPERIMENTAL DETAILS                                                                                                                                                        |

| 3.2.1 TRANSFER MoS <sub>2</sub> THIN FLAKES ON SiO <sub>2</sub> SUBSTRATE                                                                                                       |

| 3.2.2 TRANSFER MoS <sub>2</sub> THINFLAKES ON SiO <sub>2</sub> SUBSTRATE MODIFIED BY<br>OTMS SAM                                                                                |

| 3.2.3 TRANSFER MoS <sub>2</sub> THIN FLAKES ON Al <sub>2</sub> O <sub>3</sub> SUBSTRATE                                                                                         |

| 3.2.4 TRANSFER MoS <sub>2</sub> THIN FLAKES ON h-BN SUBSTRATE                                                                                                                   |

| 3.3 RESULTS AND DISCUSSION                                                                                                                                                      |

| 3.4 SUMMARY53                                                                                                                                                                   |

| <b>CHAPTER 4</b> : STUDY THE TEMPERATURE DEPENDENCE TRANSPORT PROPERTIES<br>OF MoSe <sub>2</sub> FIELD EFFECT TRANSISTOR ON PARYLENE – C AND Si/SiO <sub>2</sub> SUBSTRATES<br> |

| 4.1 INTRODUCTION                                                                                                                                                                |

| 4.2 EXPERIMENTAL DETAILS                                                                                                                                                        |

| 4.2.1 CRYSTAL GROWTH57                                                                                                                                                          |

| 4.2.2 CLEANING THE SUBSTRATE57                                                                                                                                                  |

| 4.2.3 PREPARATION OF SAMPLE                                                                                                                                                     |

| 4.2.3.1 PREPARATION OF SAMPLE ON Si/SiO <sub>2</sub> SUBSTRATE58                                               |

|----------------------------------------------------------------------------------------------------------------|

| 4.2.3.2 PREPARATION OF SAMPLE ON PARYLENE – C<br>SUBSTRATE                                                     |

| 4.2.4 FABRICATION OF MoSe <sub>2</sub> FET DEVICES                                                             |

| 4.3 RESULTS AND SISCUSSION                                                                                     |

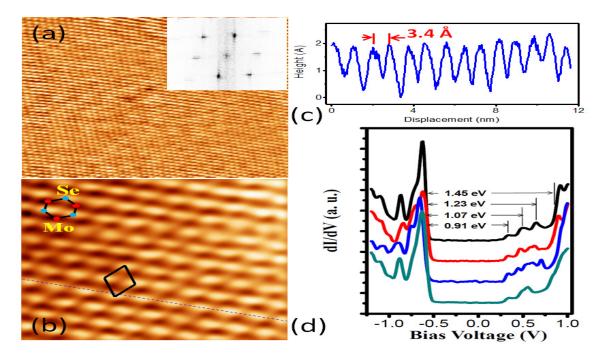

| 4.3.1 STM/STS STUDY OF MoSe <sub>2</sub> CRYSTAL AND BAND GAP<br>ESTIMATION62                                  |

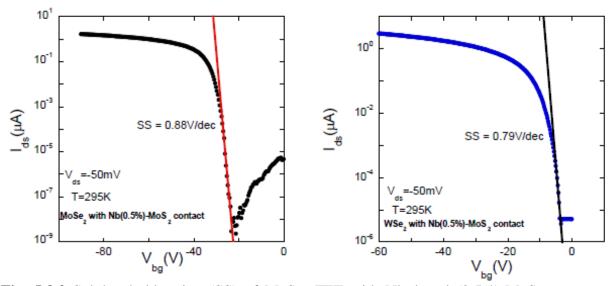

| 4.3.2 ELECTRICAL TRANSPORT PROPERTIES AT ROOM TEMPERATURE                                                      |

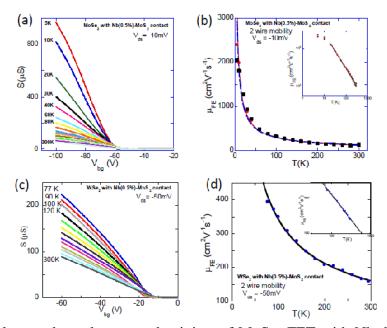

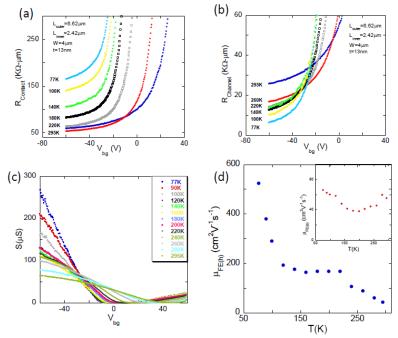

| 4.3.3 ELECTRICAL TRANSPORTPROPERTIES AT LOW TEMPERATURES<br>AND DIFFERENT SCATTERING MECHANISMS                |

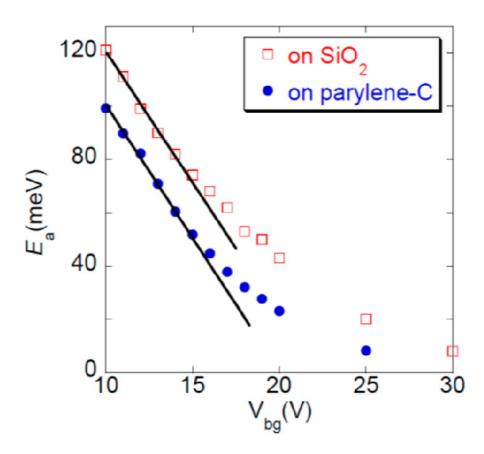

| 4.3.4 ACTIVATION ENERGY AND SCHOTTKY BARRIER76                                                                 |

| 4.4 SUMMARY77                                                                                                  |

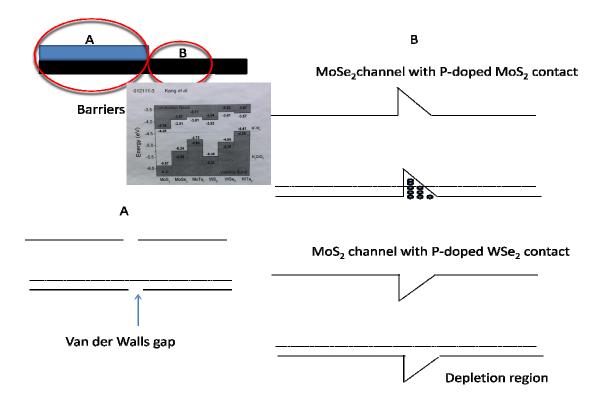

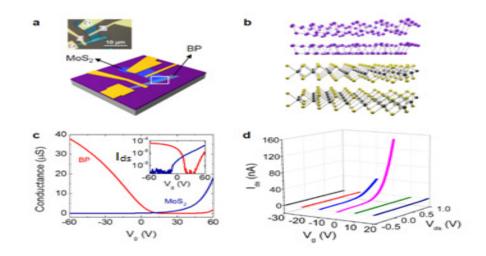

| <b>CHAPTER 5</b> : FACILE 2D/2D MATERIALS VERTICAL VAN DER WAALS ASSEMBLYTO ACHIEVELOW RESISTANCEOHMIC CONTACT |

| 5.1 INTRODUCTION                                                                                               |

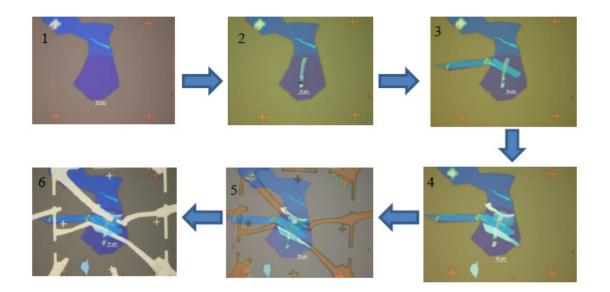

| 5.2 EXPERIMENTAL DETAILS81                                                                                     |

| 5.2.1 TMDs HETERO CONTACT                                                                                      |

| 5.2.2 TMDs HOMO CONTACT                                                                                        |

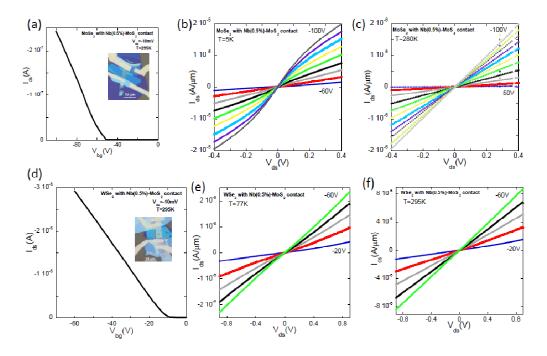

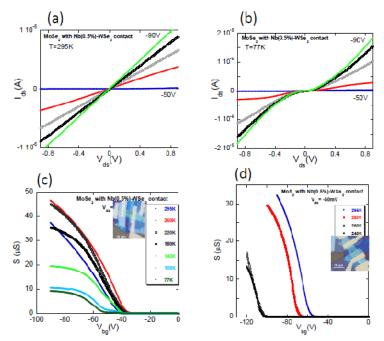

| 5.3 RESULTS AND DISCUSSION                                                                                     |

| 5.4 SUMMARY                                                                                                    |

| CHAPTER 6: STUDY THE FUNDAMENTAL PROPERTIES OF BLACK PHOSPHORUS 90                                             |

| 6.1 INTRODUCTION90                                                                                             |

| 6.2 FABRICATION PROCESS                                                                                        |

|                                                                                                                |

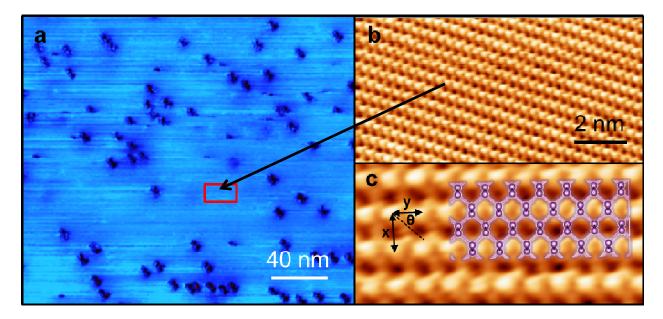

| 6.3.1 SCANNING TUNNELING MICROSCOPY STUDY OF BLACK<br>PHOSPHORUS CRYSTAL                      |

|-----------------------------------------------------------------------------------------------|

| 6.3.2 AMBIENT DEGERATION TEST OF BLACK PHOSPHORUS93                                           |

| 6.3.3 TRANSPORT PROPERTIES OF BLACKPHOSPHORUS FIELD-EFFECT<br>TRANSISTOR                      |

| 6.3.4 BLACK PHOSPHORUS MOLYBDENUM DISULFIDE JUNCTION DIODE                                    |

| CHAPTER 7: DIELECTRIC INTEGRATION                                                             |

| 7.1 INTRODUCTION                                                                              |

| 7.2 EXPERIMENTAL DETAILS105                                                                   |

| 7.2.1 C-V MEASUREMENT DESIGN105                                                               |

| 7.2.2 FET DESIGN AND ELECTRICAL TRANSPORT MEASUREMENTS.106                                    |

| 7.3 RESULTS AND DISCUSSION                                                                    |

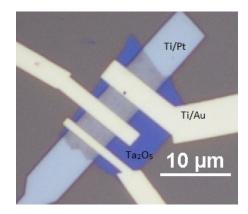

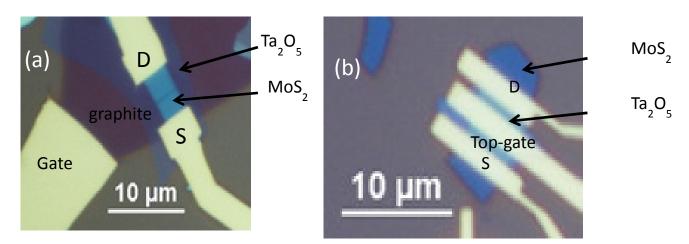

| 7.3.1 THERMAL ASSISTED SYNTHESISAND CHARACTERIZATION OF Ta <sub>2</sub> O <sub>5</sub> FLAKES |

| 7.3.2 C-V MEASUREMENT                                                                         |

| 7.3.3 TRANSPORT MEASUREMENTS IN BACK GATE CONFIGURATION                                       |

| 7.3.4 TRANSPORT MEASUREMENTS IN DUAL GATE CONFIGURATION                                       |

| 7.4 SUMMARY114                                                                                |

| FUTURE WORK                                                                                   |

| REFERENCES                                                                                    |

| ABSTRACT                                                                                      |

| AUTOBIOGRAPHICAL STATEMENT                                                                    |

# LIST OF TABLES

| <b>Table 1.1.1</b> Some of the semiconducting TMD materials and their band gap                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Table 3.1.1</b> A survey of mobilities of different thickness MoS <sub>2</sub> reported in literature by using different contact materials and different dielectric in back gate and top gate configurations 32 |

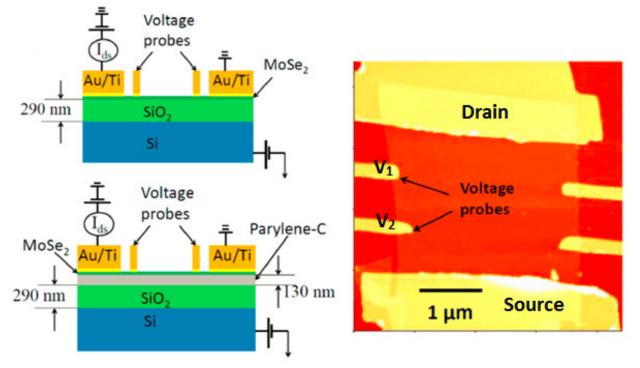

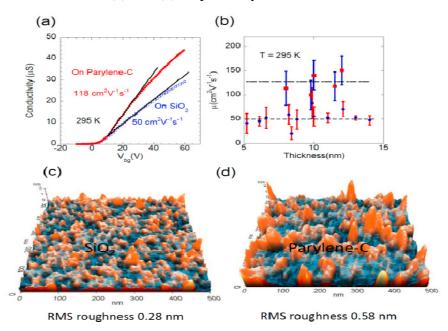

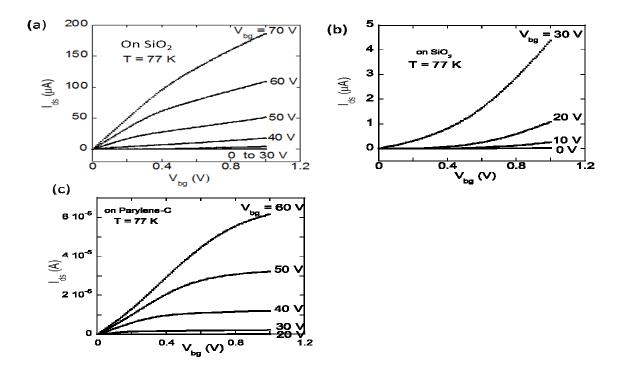

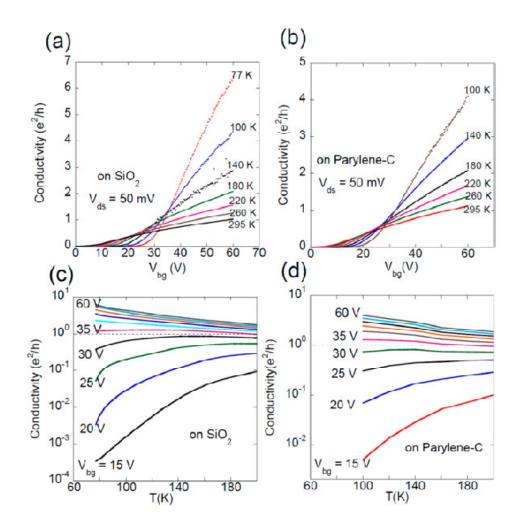

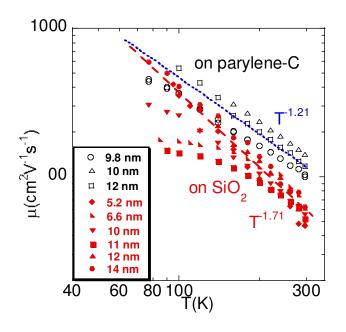

| <b>Table 4.3.1</b> Different thickness $MoSe_2$ FET devices mobilities fabricated on (a) 290nm $SiO_2$ (b)130 nm Parylene-C on the top of 290nm $SiO_2$ 70                                                         |

# LIST OF FIGURES

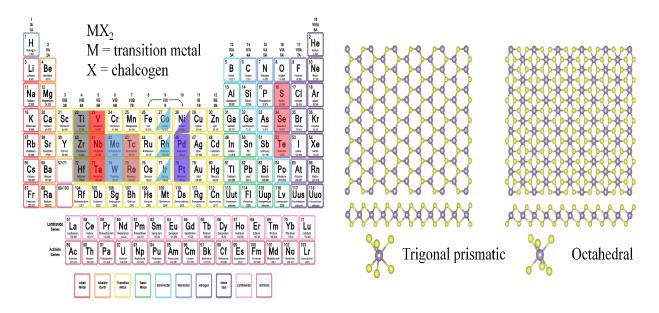

| <b>Fig.1.1.1</b> The left picture is periodic table which shows the transition metals and the three chalcogen elements that predominantly crystallize in those layered structure are highlighted in the periodic table. Middle and right pictures are the axis and section view of single-layer TMD with trigonal prismatic and octahedral structures in which purple color represents transition metal atom and yellow color represents chalcogen atom |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

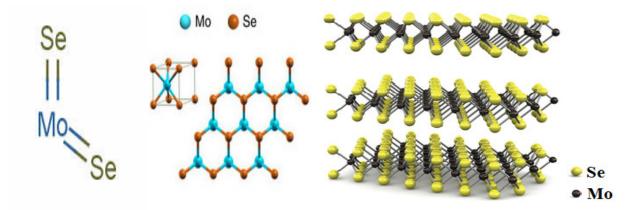

| <b>Fig.1.1.2</b> MoSe <sub>2</sub> general bond formation structure, schematic representation of unit cell and honey comb structure of MoSe <sub>2</sub> structure and three-dimensional schematic representation of MoSe <sub>2</sub> structure                                                                                                                                                                                                        |

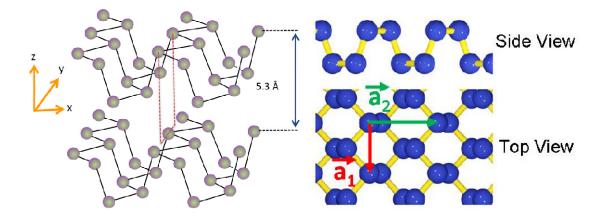

| <b>Fig.1.1.3</b> Layered crystal structure of black phosphorus with two adjacent puckered sheets. Side and top view of few layer black phosphorus is on the right side of the figure                                                                                                                                                                                                                                                                    |

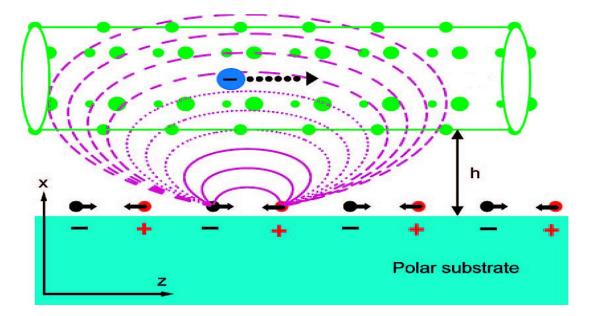

| <b>Fig. 1.4.1</b> Schematic diagram of electric field developed in the vicinity of polar substrate surface.                                                                                                                                                                                                                                                                                                                                             |

| Fig.2.1.1 Optical microscope                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fig.2.2.1 Atomic force microscope (Park Systems XE 70) and block diagram of AFM                                                                                                                                                                                                                                                                                                                                                                         |

| <b>Fig.2.3.1</b> Scanning electron microscope (SEM) set up for e-beam lithography23                                                                                                                                                                                                                                                                                                                                                                     |

| <b>Fig.2.3.2</b> The schematic diagrams show the integrated processes with electron beam lithography and metal deposition,BJD 1800 e-beam metal evaporator                                                                                                                                                                                                                                                                                              |

| Fig.2.4.1 BJD 1800 e-beam metal evaporator25                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fig.2.5.1 Ulvac mila-5000 annealing tool                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>Fig.2.6.1</b> The cryogenic probe station, its top inner view and Keithley 4200 semiconductor parameter analyzer                                                                                                                                                                                                                                                                                                                                     |

| <b>Fig.2.7.1</b> Physical Property Measurement System (PPMS) and Keithley 4200 semiconductor parameter analyzer                                                                                                                                                                                                                                                                                                                                         |

| Fig.2.8.1 Alignment 4284A precision LCR meter                                                                                                                                                                                                                                                                                                                                                                                                           |

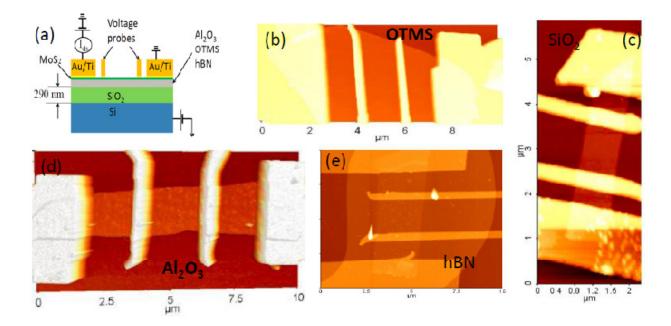

| <b>Fig.3.3.1</b> (a) Schematic diagram of $MoS_2$ FET on different dielectric substrates. AFM image of $MoS_2$ devices on (b) OTMS SAM (c) silicon dioxide (d) aluminum oxide (e) hexagonal boron nitride                                                                                                                                                                                                                                               |

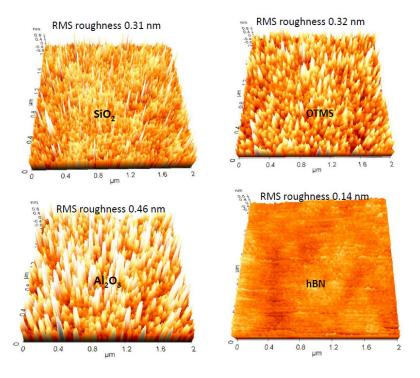

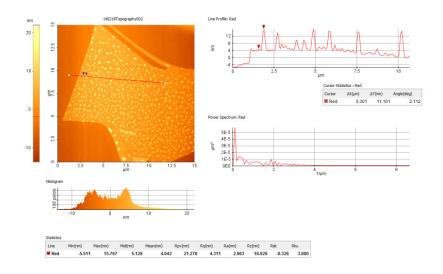

| <b>Fig.3.3.2</b> AFM image of surface roughness of (a) silicon dioxide (b) OTMS SAM (c) aluminum oxide (d) hexagonal boron nitride                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

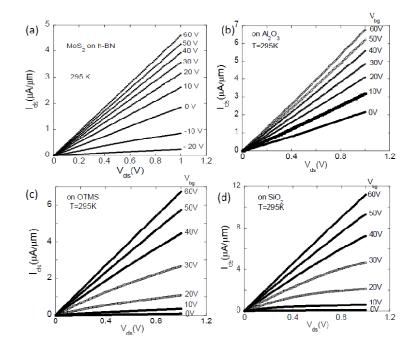

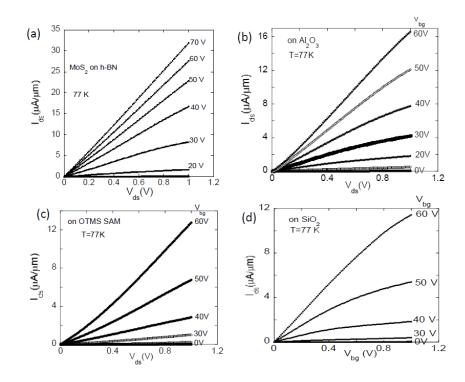

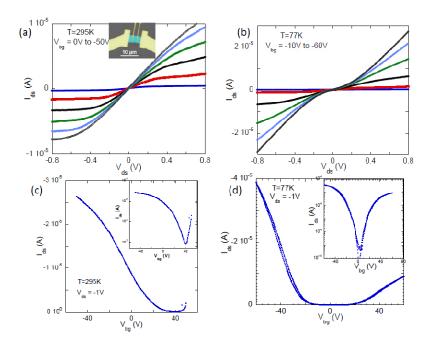

| <b>Fig.3.3.3</b> Room temperature output characteristics of MoS <sub>2</sub> FET on (a) hexagonal boron nitride (b) aluminum oxide (c) OTMS SAM (d) silicon dioxide                                                                                                                                                                                                                  |

| <b>Fig.3.3.4</b> Output characteristics of MoS <sub>2</sub> FET at 77K on (a) hexagonal boron nitride (b) aluminum oxide (c) OTMS SAM (d) silicon dioxide                                                                                                                                                                                                                            |

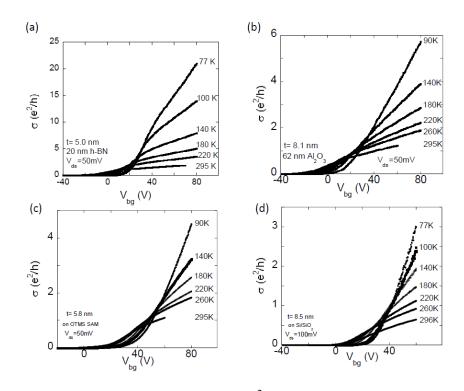

| <b>Fig.3.3.5</b> Temperature dependence conductivity $(e^2/h)$ vs V <sub>bg</sub> of MoS <sub>2</sub> FET on (a) hexagonal boron nitride (b) aluminum oxide (c) OTMS SAM (d) silicon dioxide                                                                                                                                                                                         |

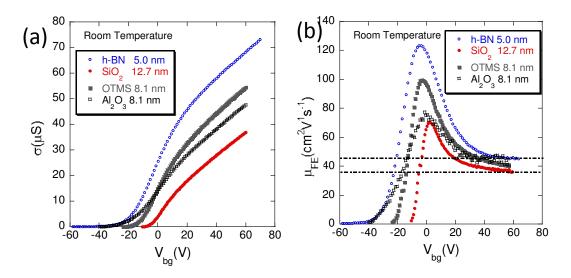

| <b>Fig.3.3.6</b> (a) Room temperature (295K) conductivity vs $V_{bg}$ of MoS <sub>2</sub> FET on different substrates (b) Back gate dependence field effect mobility of MoS <sub>2</sub> FET on different substrates at room temperature                                                                                                                                             |

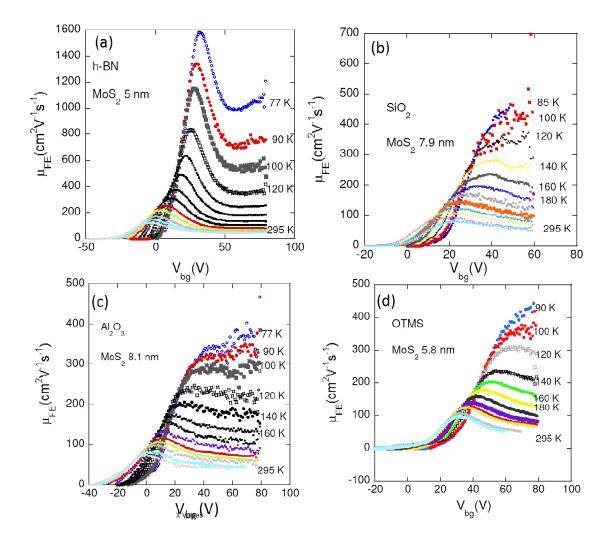

| <b>Fig.3.3.7</b> Back gate dependence field effect mobility of $MoS_2$ FET at different temperatures on (a) h-BN (b) SiO <sub>2</sub> (c) Al <sub>2</sub> O <sub>3</sub> (d) OTMS SAM treated SiO <sub>2</sub>                                                                                                                                                                       |

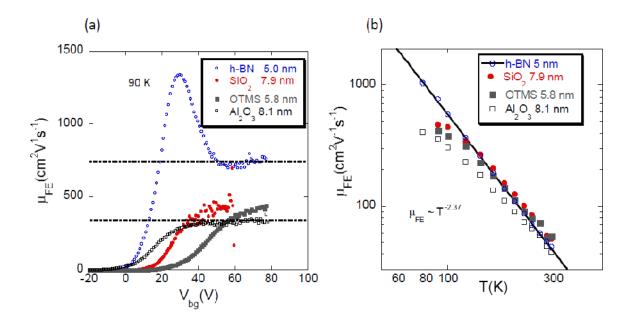

| <b>Fig.3.3.8</b> (a) Back gate dependence field effect mobility of $MoS_2$ FET on different substrates at 77K (b) Temperature dependence field effect mobility of $MoS_2$ FETs on different substrates 47                                                                                                                                                                            |

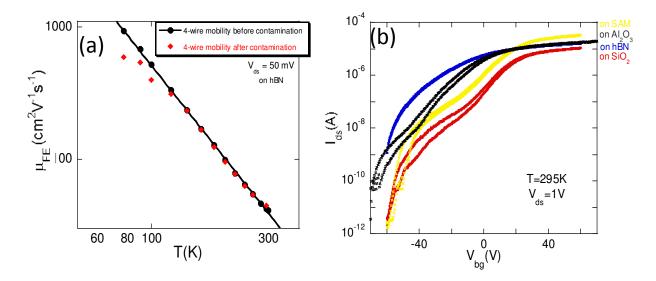

| <b>Fig.3.3.9</b> (a) Temperature dependence field effect mobility of $MoS_2$ FETs on hBN before contamination (black circle) & after contamination (red square) (b) comparison of hysteresis of $MoS_2$ FETs on different substrates                                                                                                                                                 |

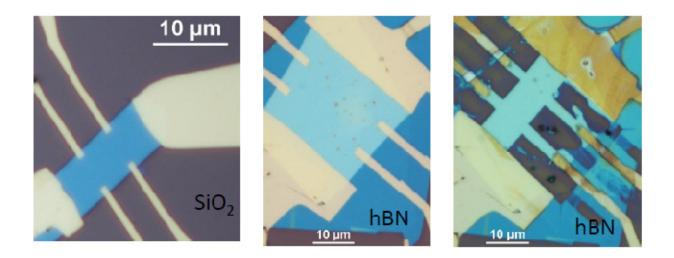

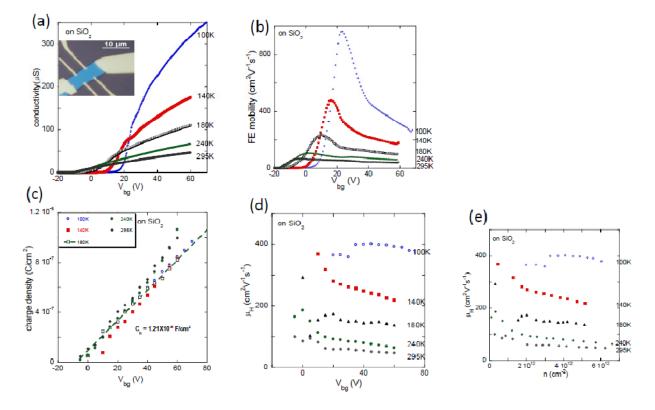

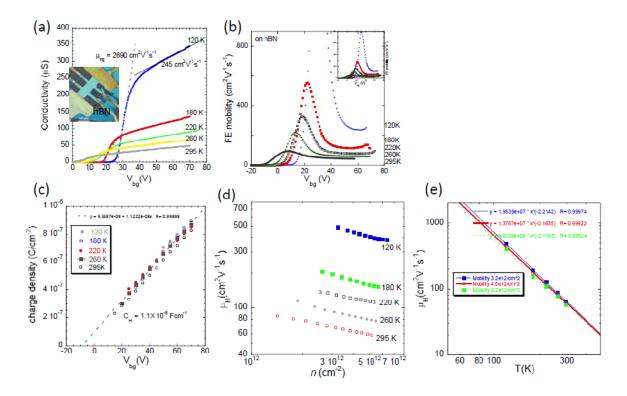

| <b>Fig.3.3.10</b> Hall bar devices, on SiO <sub>2</sub> , on hBN and after etching with hall bar on hBN (to study the evasive effect of inner gold electrodes)                                                                                                                                                                                                                       |

| <b>Fig.3.3.11</b> Gate dependence four (a) probe conductivity (b) four probe field effect mobility (c) charge carrier density and (d) hall mobility at different temperatures on $SiO_2$ and hall bar device on $SiO_2$ (in inset (a)) (e)carrier concentration dependence hall mobility at different temperatures on $SiO_2$ 50                                                     |

| <b>Fig.3.3.12</b> Gate dependence four (a) probe conductivity (b) four probe field effect mobility (c) charge carrier density at different temperatures on h-BN and hall bar device on h-BN (in inset (a)) (d) carrier concentration dependence hall mobility at different temperatures on h-BN (e) temperature dependence hall mobility at different carrier concentrations on h-BN |

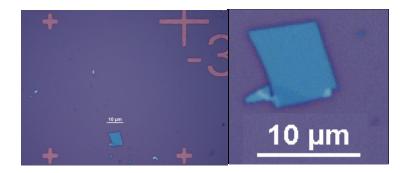

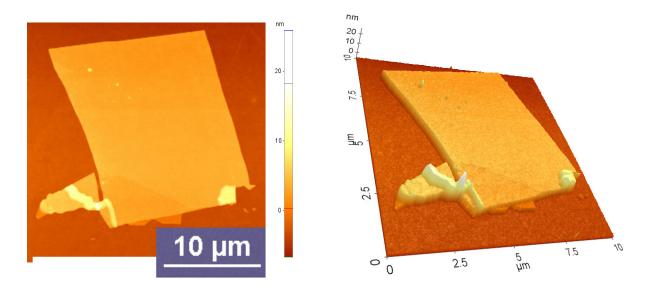

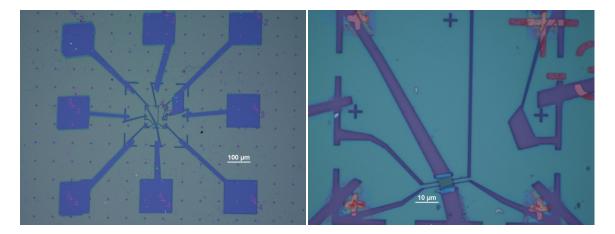

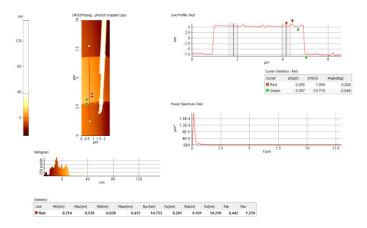

| <b>Fig.4.2.1</b> The left picture indicates the optical microscope image of MoSe <sub>2</sub> sample with gold (Au) alignment marks and the right is close-up image of same sample on Si/SiO <sub>2</sub> substrate 58                                                                                                                                                               |

**Fig.4.2.4** The schematic diagrams show the integrated processes with electron beam lithography and metal deposition, BJD 1800 e-beam metal evaporator and the device after gold deposition . 61

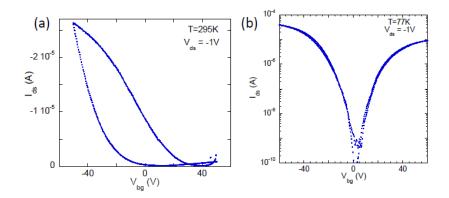

Fig. 6.3.5 Hysteresis of output characteristics of BP FET at (a) 295K and (b) 77K respectively 96

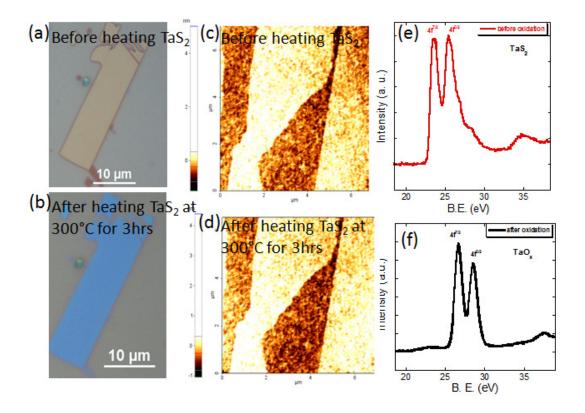

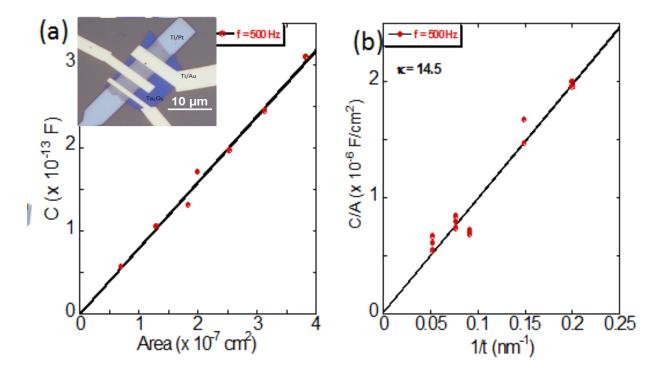

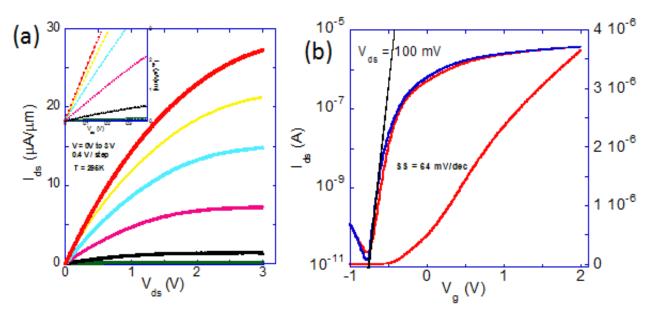

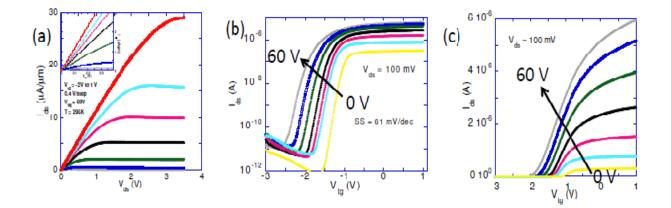

**Fig.7.3.1** (a, b) Optical image of thin  $TaS_2$  template on Si/SiO<sub>2</sub> substrate after transfer form scotch tape with repeated splitting of bulk 1T  $TaS_2$  and corresponding optical image of template after heating at 300°C for 3hrs in ambient environment. (c, d) AFM image of  $TaS_2$  template before heating and after heating at 300°C for 3hrs in ambient environment (e, f) XPS spectra of  $TaS_2$  and synthesized  $Ta_2O_5$ \_\_\_\_\_108

# LIST OF ABBRIVATIONS

- TMD: transition metal dichalcogenide

- 2D: two-dimensional

- FET: field-effect transistor

- hBN: hexagonal boron nitride

- OTMS: octadecyltrimethoxysilane

- SAM: self-assembled monolayer

- SiO<sub>2</sub>: silicon dioxide

- Al<sub>2</sub>O<sub>3</sub>: aluminum oxide

- Ta<sub>2</sub>O<sub>5</sub>: Tantalum oxide

- TiO<sub>2</sub>: titanium dioxide

- MoS<sub>2</sub>: molybdenum diselenide

- MoSe<sub>2</sub>: molybdenum disulphide

- WSe<sub>2</sub>: tungsten disulphide

- BP: black phosphorus

- Si: silicon

- PPMS: physical property measurement system

- SEM: scanning electron microscope

- AFM: atomic force microscope

- CVD: chemical vapor deposition

- ALD: atomic layer deposition

- NPGS: nano patterning generation system

- PMMA: polymethyl methacrylate

HSQ: hydrogen silsesquioxane

IPA: isoproponal

DFT: density functional theory

STM: scanning tunneling microscope

STS: scanning tunneling spectroscope

MIBK: methyl isobutylketone

MEK: methyl ethyl ketone

SS: subthreshold swing

PDMS: Poly-dimethylsiloxane

RT: room temperature

MIT: metal insulator transition

SB: Schottky barrier

- CMOS: complementary metal-oxide semiconductor

- ROP: remote optical phonon

- XPS: X-ray photoelectron spectroscopy

- EDS: Energy dispersive spectroscopy

UHV: ultra-high vacuum

# **CHAPTER 1 GENERAL INTRODUCTION**

### **1.1 TWO DIMENSIONAL MATERIALS**

Two dimensional (2D) materials with atomic thicknesses have recently attracted tremendous interest from the scientific and engineering communities. The most studied 2D materials to date are graphene, hexagonal boron nitride (h-BN), black phosphorus (BP) and transitional metal dichalcogenides (TMDs) such as molybdenum disulphide (MoS<sub>2</sub>), tungsten diselenide (WSe<sub>2</sub>) and molybdenum diselenide (MoSe<sub>2</sub>). These 2D materials have displayed varying electronic properties ranging from metal, to semiconductor, insulators and even superconductor. Among 2D semiconductors, different band gaps, charge neutrality levels, and spin properties have been observed, which offers the versatility for the development of 2D electronics, optoelectronics and spintronics.2Dmaterialsare promising candidates for a wide range of applications from nanoelectronics, optoelectronics, sensing, photonic<sup>1</sup>. Particularly, these atomically thin films are ideal channel materials for nanoscale flexible electronics applications, such as low power, high-frequency, and flexibledevices.<sup>1-3</sup> Graphene is the most widely explored 2D material because of its extremely high carrier mobility and unique physical properties. In addition, the synthesis of large area graphene films using chemical vapor deposition (CVD) is also feasible. In spite of the favorable mechanical, thermal, electronic and optical properties, graphene is a zero band-gap semiconductor. As a result, graphene transistors typically exhibit a very low on/off current ratio, which makes grapheme a poor channel material in logic electronics. Sustained efforts to open up a band gap in graphene have either caused severe mobility degradation or require prohibitively high bias voltages.<sup>4</sup>Solayered transition metal dichalcogenides (TMDs) and black phosphorous (BP) have emerged as a viable alternative to grapheme because they combine a semiconducting gap with mechanical flexibility, chemical

& thermal stability and absence of dangling bonds. Low energy devices, digital electronics & optoelectronics based on these materials have been demonstrated in recent studies.<sup>5-19</sup> Similar to graphene, atomically thin layers can be easily produced by mechanical exfoliation from their bulk crystals because of the weak van der Waals forces between adjacent layers.

# 1.1.1 TRANSITION METAL DICHALCONIDES (TMDs)

The transition metal dichalcogenides have chemical composition described by the formula MX<sub>2</sub> (M = Ti, Zr, Hf, V, Nb, Ta, Cr, Mo, W, Pt and X = S, Se, Te). The properties of transition metal dichalcogenidesvaries from metal (NbS<sub>2</sub>, TiS<sub>2</sub>, TaS<sub>2</sub>, VSe<sub>2</sub>), semimetal (like WTe<sub>2</sub>, TeS<sub>2</sub>), semiconductor (like MoS<sub>2</sub>, MoSe<sub>2</sub>, WSe<sub>2</sub>) to insulator (like HfS<sub>2</sub>).<sup>20</sup> The transition metal dichalcogenides (TMDs) have layered structure with two general configuration of either trigonal prism or octahedron having different lattice symmetries.<sup>21</sup> MX<sub>2</sub>crystals are hexagonally packed with stacking layers of X-M-X. The bond between two-dimensional X-M-X layers is covalent type and stronger than the interaction between the atoms residing on different planes, which is van der Waals type and is relatively weak. The strong covalent bonds between transition metal and chalcogen atoms on the plane and weak van der Waals bond between layers allows making atomically thin layer by micromechanical cleavage method by splitting the layer by layer structure. The unique properties of TMDs including chemical & thermal stability, mechanical flexibility, ultra-smooth atomic thickness, absence of dangling bonds& interface traps, sizeable band-gap, reasonably high carrier mobility and fast growing synthesis techniques have been attracted researchers a lot of interest to implement the revolutionary applications in novel transparent & flexible electronics<sup>1, 22</sup>, optoelectronics<sup>1</sup>, stacked van der Waal superlattices & heterojunctions<sup>23</sup>, spintronics (valleytronics)<sup>24-27</sup> and ultimate atomically thin field effect transistors.<sup>2, 28</sup> Fig.1.1.1 shows the periodic table with highlighted columns for transitional

metals and chalcogens, by combining them about 40 different layered TMD compounds exists and their possible crystal structures. Only some dichalcogenides of partial highlights of transitional metals form layered structure. For example, NiS<sub>2</sub> is found to have apyrite structure which is not layered structure but NiTe<sub>2</sub> is a layered dichalcogenide. Right side of Fig.1.1.1 shows the two possible crystal structures of transitional metal dichalcogenides. The layer structure has hexagonally packed layer of metal atoms sandwiched between two hexagonally close packed chalcogen atoms with intra-layer bonds are covalent and interlayer bound force is van der Waals. The thickness of single layer TMD is about 6 to 7 Å. Each metal atom provides four electrons to two chalcogen atoms to form TMD layer structure such that the oxidation state of metal is +4 and the oxidation state of chalcogen is -2. The TMD layer structure has absence of dangling bond because the lone pair electrons of chalcogen atoms terminate on the surfaces of layers. Bulk TMDs exhibit a wide variety of polymorphs in which most common polymorphs are 1T, 2H and 3R where the letters stand for trigonal, hexagonal and rhombohedral, respectively. For instance, natural MoS<sub>2</sub> is commonly found in the 2H phase where the stacking sequence is aBabAb in which the upper case letters represent metal atoms and lower case letters represent chalcogen.On the other hand, synthetic MoS<sub>2</sub>often contains the 3R phase where the stacking sequence is aBacAcbCb. In both phases, the metal coordination is trigonal prismatic. Some of the TMDs such as TiS<sub>2</sub>are 1T phase where the stacking sequence is aBcaBc and the coordination of the metal is octahedral. Recent experimental report demonstrated that the metallic 1T phase of MoS<sub>2</sub> can be locally induced on semiconducting 2H phase nanosheets.<sup>29</sup> Because of its layer structure, single layer/few layers TMDs can be easily exfoliated from bulk crystal by mechanical cleavage method.

**Fig.1.1.1** The left picture is periodic table which shows the transition metals and the three chalcogen elements that predominantly crystallize in those layered structure are highlighted in the periodic table. Middle and right pictures are the axis and section view of single-layer TMD with trigonal prismatic and octahedral structures in which purple color represents transistion metal atom and yellow color represents chalcogen atom.

**Table 1.1.1** shows the some of the possible transitional metal dichalconides. The bulk form of these materials form indirect band gap and changed to direct band gap for monolayer due to quantum confinement.<sup>1, 30</sup> Due to the difference of band gap and direct gap nature of monolayer TMDs compared to its bulk form opens up platform to investigate different interesting properties of monolayer TMDs and their possible applications.

Material

$E_g$  in bulk (eV)

$E_g$  monolayer (eV)

$MoS_2$  1.2

1.8

$MoSe_2$  1.2

1.5

$WS_2$  1.4

1.9-2.1

$WSe_2$  1.2

1.7

WSe21.21.7MoTe211.1WTe20.71.1

Table 1.1.1 Some of the semiconducting TMD materials and their band gap

# **1.1.1.1 MOLYBDENUM DISULFIDE**

Molybdenum is a transition metal element from group VI and sulphide is chalcogen (oxygen group). The mineral of  $MoS_2$  called *molybdenite* is exists in nature.  $MoS_2$  has three different structural phases. The first one is 2H-phased  $MoS_2$  which has hexagonal symmetry and semiconducting properties. It is found in nature and having layer structure which can be easily mechanically exfoliated into few layers to single layer. The second one is 1T-phased  $MoS_2$  having tetragonal symmetry which has metallic properties. The third one is 3R-phased  $MoS_2$  with rhombohedral symmetry which has semiconducting properties like 2H-phased  $MoS_2$ . Semiconducting  $MoS_2$  has indirect band gap with 1.2 eV in bulk form and change into direct band gap 1.8 eV for monolayer due to quantum confinement.<sup>1</sup> In the past,  $MoS_2$  is used as a lubricant because of its lubricating property.

#### **1.1.1.2 MOLYBDENIUM DISELENIDE**

Molybdenum is a transition metal element from group **VI** and Selenium is chalcogen (oxygen group). Molybdenum diselenide (MoSe<sub>2</sub>) is a transition metal dichalcogenides having similar structure as other TMDs. MoSe<sub>2</sub> forms layered structured of the form Se - Mo - Se with selenium atoms in two hexagonal planes separated by a plane of Molybdenum atoms. The strong covalent bond exists between Molybdenum & Selenium with weak interlayer coupling by weak van der Waal force. In MoSe<sub>2</sub>, the metal atom has trigonal prismatic coordination within the sandwich layer and a number of stacking polytypes are possible depending upon the way in which the sandwich layers are stacked one upon the other. Bulk MoSe<sub>2</sub> shows semiconducting behavior with indirect band gap 1.1 eV. The indirect band gap of bulk MoSe<sub>2</sub> changed into direct band gap 1.5 eV for monolayer MoSe<sub>2</sub>.<sup>1</sup>

**Fig.1.1.2** MoSe<sub>2</sub> general bond formation structure, schematic representation of unit cell and honey comb structure of  $MoSe_2$  structure and three-dimensional schematic representation of  $MoSe_2$  structure.

## **1.1.2 BLACK PHOSPHORUS**

Black phosphorus (BP) is thermodynamically stable allotrope of phosphorus at room temperature and pressure. It is elemental semiconductor with anisotropic crystal structure. It is looks like black in color and orthorhombic, buckled structure with each phosphorous atom have one bond along armchair direction and two bonds along zigzag direction as shown in **Fig.1.1.3**. It forms layer structure as like graphite and can be exfoliated to monolayer called phosphorene by mechanical exfoliation method. The band gap of bulk BP is 0.3 eV and increase up to 2 eV for monolayer while its few-layer structures have thickness-dependent direct band gaps between 2 eV to 0.3 eV.<sup>31-34</sup> With advancement of mechanical exfoliation method BP opens up new opportunities for electronic and optoelectronic applications. Especially reported high mobility reported favorable for electronic application. Unlike other 2D materials, the electrical, optical, mechanical and thermal properties of BP show anisotropic nature due to its anisotropic crystal structure.<sup>32, 35, 36</sup>It has been found that the BP reacts with air in presence of water vapor which degrades its electrical properties gradually. The degradation enhances in presence of light.<sup>37, 38</sup>

The chemical degradation of BP at ambient condition challenges the researchers to prevent to contact with air, water and light for preserving it pristine properties.

**Fig.1.1.3** Layered crystal structure of black phosphorus with two adjacent puckered sheets. Side and top view of few layer black phosphorus is on the right side of the figure.

#### **1.2 SYNTHESIS OF 2D MATERIALS**

Reliable and reproducible synthesis of atomically thin 2D materials with uniform properties is essential to study their intrinsic and extrinsic properties. High purity and cleanliness of flakes/films are essential to study fundamental properties of 2D materials. Complex fabrication process and materials/chemicals used in fabrication process might introduce impurities on the 2D flakes which might alter the intrinsic properties. Some of the common established methods to get 2D materials are as follow:

**Top-down method**: This is the method of preparation of atomically thin 2D materials from bulk crystal. Atomically thin layer as well as few layers of 2D material from its bulk crystal can be prepared by micromechanical cleave method as first time done to prepare graphene.<sup>16</sup> The bulk crystal is kept on scotch tape and exfoliates by using another scotch tape. By cleaving multiple times using adhesive scotch tape, thin enough flakes can get on scotch tape. By introducing substrate on the scotch tape having thin layers of 2D materials, sufficiently thin 2D flakes can be transferred to substrate. 2D materials having different thickness on a substrate

show different optical contrast with visible light. This property is used to find the atomically thin flakes with interference of visible light on it by using optical microscope.<sup>39, 40</sup> The light interference is caused by reflection/refraction of thickness of 2D layer and substrate thickness. This method produces atomically thin 2D flakes of high purity and cleanliness as bulk crystal but it is not control over dimensions. So, it is hard to control thickness and size of 2D flakes systemically. More strictly speaking, it is hard to get large thin flakes with appropriate size and dimensions. Another top-down method to get atomically thin 2D material from its multilayer is laser-induced thinning.<sup>41</sup> The multilayer of crystal is exposed by laser with required exposition dose which is controlled by adjusting the incident laser power, the step size and the exposure time. This is a reliable method to get atomically thin 2D layers with user-defined shape and size but the roughness of the laser scanning surface is main problem and the requirement of adjustment of parameters of laser scanning is challenging. The interaction of chemical with bulk crystal is used to exfoliate the bulk crystal into atomically thin 2D flakes called chemical exfoliation method. This method produces required monolayer but the resulting 2D material may have different structure and electronic properties from the bulk material.<sup>13</sup> The chemical used to exfoliate the sample might change the intrinsic properties by introducing charges and other impurities.

**Bottom-up method**: The process of getting atomically thin layer of 2D materials starting from zero thickness is bottom-up method. Chemical vapor deposition (CVD) is one of the well-known preparation of 2D material layer.<sup>42,43</sup> This method gives large flake size. But the control over flake thickness and quality of the flake is challenging. Repetition of the process to get similar flakes with right size and thickness is still challenging. The crystal growth depends upon different parameters including the external environment which creates challenges to keep same

condition during growth process. Particular recipe for CVD grown of certain 2D material is substrate dependence. Different recipe should be used to grow same material on different substrates.

# **1.3 TRANSPORT PROPERTIES AND DEVICE PERFORMNCE OF 2D SEMICONDUCTORS**

Transport properties of 2D semiconductor shows wide variation depending up on their materials, type of charge carriers and dielectric used. The studies of graphene have revealed its exceptional electronic properties based on the unique band structure including the observation of ambipolar behavior. The charge carriers in graphene can be described as relativistic particles called Dirac fermions by Dirac equation for this 2D crystal, providing a way to explore quantum electrodynamics (QED).Graphene has reported high mobility, exceed 15000cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature with ballistic transport, and shows quantum Hall effect.<sup>8, 44</sup> On the other hand, the electron mobility values of monolayer and multilayer MoS<sub>2</sub> devices on SiO<sub>2</sub> reported by multiple groups were substantially below the Hall mobility of bulk MoS<sub>2</sub> (100 - 200 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>).<sup>2, 45, 46</sup> Bao at. al. reported ambipolar multilayer MoS<sub>2</sub> with two terminal field-effect mobility attained to 470cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at room temperature on PMMA but the improvement of mobility is still unclear.<sup>47</sup> S. L. Li et.al. presented thickness dependent interfacial charge scattering of MoS<sub>2</sub> FET and showed the improvement of field effect mobility with increase of thickness by suppressing the Coulomb scattering originated from SiO<sub>2</sub> surface and MoS<sub>2</sub> /SiO<sub>2</sub> interfaces.<sup>48</sup> Different efforts to modify the SiO<sub>2</sub> surface, using high-k dielectric such as HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> and h-BN encapsulation have been done for graphene and TMDs field effect transistor but the mobility values never reached to theoretical phonon limited mobility<sup>45, 49-53</sup>, which indicates the carrier mobility of 2D channel materials is limited by extrinsic scattering from charged impurities at the channel/substrate interface and charge traps in dielectric, substrate surface roughness, and remote surface optical phonons originating from substrate.

A good transistor layer material should have enough high charge carrier mobility for high on state current and fast operation of transistor. The layered materials should have reasonable band gap to maintain enough on/off current for the operation of transistor by electrostatically switching on and off state. On the other hand, sharp switching characteristic is equally important to allow high degree of electrostatic control over devices. To achieve all of these ideal properties, selection of channel materials and dielectric materials is exceptionally important. In addition, devices structures, designs and modification are also important to optimize and modify the 2D thin layer transistor devices properties.

# 1.4 FACTORS RELATED TO TRANSPORT PROPERTIES OF 2D SEMICONDUCTORS

The channel of 2D materials is thin which needs substrate to support and for the investigation of its properties we have to connect with metal electrodes. The contact metal form barrier with semiconductor channel of 2D materials and the dielectric on substrate plays important role to determine the channel properties of the thin 2D materials. Basically there are following main challenges which have to address to investigate the channel properties and optimize the 2D based semiconductor electronics.

- 1. contact effect

- 2. interface effect

- 3. dielectric integration

My main focus of the work is details interface effect study of 2Ds based semiconductors field effect transistor (FET) and 2D heterostructure integration to optimize the performance of FET with dielectric integration. To reveal these effects, we have to start the basic concept of common scattering mechanisms of 2D materials and external factors which affect to investigate the intrinsic properties of 2D thin flakes.

#### 1.4.1 SEMICONDUCTOR AND ELECTRODE (METAL) CONTACT

Metals leads need to be connected to study the channel properties of 2D semiconductor flakes. But there is formation of schottky barrier at metal semiconductor junction. The schottky barrier can be successfully eliminated by adopting the transfer line method or four terminal measurements but practical FETs are two terminal electrodes as drain and source which greatly affected by schottky barrier and limit the performance of the device. Scottky barrier due to band off set of metal semiconductor, Fermi level pining due to the interface states of semiconductors and current crowding effect due to non-uniform injection of charge carriers along the entire metal/semiconductor length are the main problems to device performance of 2D semiconductors FET.

#### **1.4.2 CARRIERS SCATTERING MECHANISMS**

In 2 dimensional TMDs layers, transport and scattering phenomena of the charge carriers are confined to the plane of the material and on the surface of the substrate. In these ultrathin 2D channels, the interface effects are particularly important. The mobility of charge carriers is mainly determined by following mechanisms: <sup>51, 54-57</sup>

(a) Lattice or phonon (acoustic & optical phonon) scattering.

Energized phonons within the 2D materials couple with charge carriers and affect the motion of charge carriers. Optical phonon scattering is dominated factor at high temperature. So the charge carrier mobility is largely affected by phonon scattering with increase of temperature.<sup>58</sup> The phonon vibrations within the TMD channel includes out of plane homo-polar mode and in plane phonon vibration. Depending upon its vibration energy, it can be excited by

thermal energy. Some of the phonon has enough low excitation energy which is sufficient to excite by thermal energy at room temperature or even lower. The quenching of thermally excited phonon is efficient method to reduce its effect on transport property of 2D TMDs. The out of plane homo-polar phonon mode vibration can be quenched by sandwiching the vibration between top gate dielectric and back gate substrate.

#### (b) Atomic and structural defects scattering

It is really challenging to grow a crystal without defects. Although naturally occurred TMDs crystals are relatively low lattice defects, the commercially grown TMDs monolayer TMDs crystals have abundant crystal defects.<sup>59</sup> The lattice defects form scattering centers for charge carriers and scatter the accelerated charge on the channel. Lattice defects also promote the foreign materials to add and form scattering centers for accelerated charge particles.

#### (c) Coulomb scattering.

It is common to introduce charge impurities during the fabrication process of 2D materials since it is in contact with other materials like PDMS, PC, PMMA and many other chemicals in the process of making devices. Moreover, the substrate itself introduces trap charges between 2D materials channel and substrate. The substrate surface and 2D materials may trap the water, air bubble and other foreign materials as a source of charge impurities. Due to the Coulomb force between the charge carriers and random charge impurities which are located within the layered TMDs & on its surface causes the Coulomb scattering. Coulomb scattering is also caused due to charge impurities and charge traps at the interface between TMDs & substrate. The polar molecules on the surface of the substrate set up electric field around it which creates additional Coulomb scattering of charge carriers along TMDs channel. It has dominant effect at relatively low temperatures at which the phonon scattering is insignificant.<sup>60, 61</sup> Gate

dielectric materials play an important role to modify the effect of coulomb scattering due to charge impurities. Non-polar dielectric having inert and smooth surface is an ideal material to decrease the Coulomb scattering. Argument of dielectric screening of Coulomb scattering on charge impurities is recently introduced for MoS<sub>2</sub> transistor by using gate dielectric material having high dielectric constant.<sup>2</sup> The coulomb scattering from the interface of substrate and TMDs channel and coulomb scattering introduced for most substrate is crucial for thin layer of TMDs channel. Recently more severe scattering from charge impurities on single layer MoS2 channel is reported from the study thickness dependence coulomb scattering.<sup>61</sup>

# (d) Surface roughness scattering.

Different substrate has different roughness depending upon its atomic arrangement on the surface, surface growth quality etc. It is important to consider the effects of smoothness of the substrate to study the channel properties of ultrathin 2D materials in back gate configuration. The charge carriers, which are concentrated close to the substrate due to the applied back gate, are scatter from the surface of the substrate. Rougher surface enhances the charge carriers scattering from the surface. The roughness of the substrate and the sample surface roughness as ripples can play important role for mobility deterioration of charge carriers in 2D materials as well as its transport properties.<sup>62</sup>

### (e) Surface interfacial phonon scattering

Surface phonons are particular lattice vibration modes associated with vibration of molecules/atoms of substrate surface. Surface phonons on the surface of the substrate can couple with charge carriers through TMD channel and affect the electrical and optical properties of devices. Since the thickness of 2D TMDs is atomically thin, the effect of surface polar phonon scattering is also significant. The polar molecules on the surface of the polar substrate (as SiO<sub>2</sub>)

create electric field as shown in **Fig. 1.3.1**. The charge carriers inside this field can be scattered by the polar phonons.<sup>54</sup> The effects of surface phonon can be investigated by using different dielectric materials having various surface phonon energies like SiO<sub>2</sub>, PMMA, Al<sub>2</sub>O<sub>3</sub>, hBN, HfO<sub>2</sub>, TiO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>.

Fig. 1.4.1 Schematic diagram of electric field developed in the vicinity of polar substrate surface

Substrate dielectric has great influence to determine the transport properties of TMDs channel. So it is better to distinguish the charge carriers scattering factors in terms surface induce and channel induce. Scattering mechanisms are classified into two categories in terms of the scattering factors from channel and substrate.

Scattering mechanisms from the channel materials

- Optical phonons scattering due to intrinsic phonon

- Acoustic phonons scattering due to intrinsic phonon

- Scattering due to structural defects in the channel material

- Coulomb scattering due to impurities in the channel

Scattering mechanisms from the channel materials

- Coulomb scattering due to charged impurities at the interfaces/substrate

- Phonon scattering due to remote surface optical phonons

- Roughness scattering due to interface roughness

Substrate plays crucial role to deviate from intrinsic properties of the channel material. So it is worth to study the details of different scattering mechanism caused by substrate.

Besides these factors, the schottky barrier height plays important role to deteriorate the extrinsic mobility of the charge carriers. The extent of effect to the mobility of charge carrier by these mechanisms is also influenced by other factors like temperature, dielectric environment, effective mass of charge carrier, electronic band structure, thickness of the layer, charge carrier density.<sup>1</sup>

One of the most promising applications of thin 2D materials is field effect transistor (FET). The most desirable features of FETs are high carrier mobility, high ON-OFF current ratio, presence of both electron and hole conduction, high optical transparency, thermal & chemical stability, and mechanical flexibility.<sup>63</sup> The 2D layered materials might be best candidates for the FETs in order to meet these requirements.

Low resistance contacts and substrate effects are critical to investigating the channel properties of ultrathin 2D materials. Also we are using the four-wire method which demands low contact resistance for the validity of measurements. Choice of different substrate helps to reveal the substrate effects on channel of ultrathin 2D materials.

In my study, I mainly focus on the study of substrate effects, dielectric environment effects, contact effects and thickness dependence on electrical transport properties of ultrathin TMDs FET and dielectric integration of 2D materials. I focus on 2D materials MoS<sub>2</sub>, MoSe<sub>2</sub>, Black Phosphorus as channel materials with different types of dielectric combinations of SiO<sub>2</sub>,

OTMS SAM modified SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, hBN, parylene-C and other dielectric synthesis from 2D layer structure to study the substrate effects, dielectric environment effects and thickness dependence on electrical transport properties of ultrathin TMDs FET. For the contact effect study, I chose 2D materials MoS<sub>2</sub>, MoSe<sub>2</sub>, WSe<sub>2</sub> as channel materials and their p (n) doping as 2D contact materials.

#### **1.5 DIELECTRIC INTEGRATION**

Dielectric is extremely crucial for 2D semiconductor. Both scientific and technological issues like the choice of dielectric material, their deposition, their structural and metallurgical behavior, atomic diffusion, interface structure and reactions, their electronic structure, bonding, band offsets, electronic defects, charge trapping and conduction mechanisms, mobility degradation and flat band voltage shifts are the essentials factors to consider for selecting the appropriate dielectric. Vacancy state in dielectric is the dominant electron traps which directly and indirectly responsible for external scattering of charge carriers in 2D semiconductor channel. A systematic consideration of the required properties of gate dielectrics indicates that the key guidelines for selecting an alternative gate dielectric are permittivity, interface quality, interface properties, band gap, and band alignment to 2D semiconductor, thermodynamic stability, film morphology, compatibility with the current or expected materials to be used in processing for complementary metal oxide semiconductor (CMOS) devices, process compatibility, reliability, and maintenance of a high charge carriers mobility in the channel and minimization of electrical defects in the film/interface. Few layer 2D materials have extremely sensitive large area. The charge impurities introduce on the surface at the dielectric interfaces causes coulomb scattering which significantly degrades the transport properties especially carriers mobility. The ambient exposure of the 2D materials surface shows completely different transport mechanism and also

causes surface chemical degradation. Defects in crystal like grain boundaries and point defects severely change the properties of the 2D materials devices. Numerous challenges exist for 2D materials that prevent large-scale integration into its applications.

On the other hand, a practical transistor channel material should have high charge carrier mobility, reasonable band-gap, and low subthreshold swing (SS) to compete with complementary metal oxide semiconductor. High charge carrier mobility is needed for high speed operation of transistor with high on current. In the meantime, it should have reasonable band-gap to get a very low current at off state. In addition, lower subthreshold swing is extremely desirable for much needed electrostatic control of transistor. Moreover, the size of the transistor should be very small for the fast growing industrial market.

If the size of the transistor is decreased, then the encroachment of electric field lines from drain/source causes the undesirable distribution of electric fields on channel by competing the available depletion charge. This attributes the decrease on/off ratio (increase off current) and subthreshold swing degradation (reduce the electrical control) called short channel effect. In this case, the electric field in the channel can be modeled using the Poisson distribution.<sup>64</sup>

$$\frac{d^2\phi(x,y,z)}{dx^2} + \frac{d^2\phi(x,y,z)}{dy^2} + \frac{d^2\phi(x,y,z)}{dz^2} = qN/\epsilon_{ch}$$

The solution of the Poisson equation gives characteristics length called natural length  $\lambda$ ,

$$\lambda = \sqrt{\frac{\kappa_{ch}}{N\kappa_{ox}}} t_{ch} t_{ox}$$

Where  $\kappa_{ch}$  and  $\kappa_{ox}$  are dielectric constants of the channel and the dielectric oxide,  $t_{ch}$  and  $t_{ox}$  are the thicknesses of the semiconducting channel and the oxide, N is the effective gate number.

Natural length represents the penetration distance of the electric field lines from the drain/source in the channel of the device. It also represents the amount of control the drain/source region has on the depletion region, as both the gate and the drain compete for that control. So it gives a measure of the short-channel effect of the device structure. A device can be considered free of short-channel effects if the gate is at least six (5-10) times longer than  $\lambda$ .

As transistors have decreased in size, the thickness of gate dielectric has steadily decreased to increase the gate capacitance and thereby drive current, raising device performance by high degree of electrical control. But the decrease of gate dielectric thickness sets lower natural length which significantly increases the subthreshold swing as well as significantly degrades the electrical control over device. The implementation of high- $\kappa$  gate dielectrics is one of strategy to overcome the problems. Using high- $\kappa$  gate dielectrics gives higher natural length and helps to reduce the short channel effect. In addition gate dielectric with a high- $\kappa$  material allow increased gate capacitance without the associated leakage effects and improve the field-effect charge carriers mobility of the channel by reducing Coulomb scattering.<sup>11</sup>

Besides these factors, we have to consider the surface optical phonon energy of the dielectric materials. The surface phonons can interact with charge carriers in the channel and cause severe remote surface phonon scattering. This external scattering significantly degrades the transport properties of the 2D semiconductor channel and reduces the charge carrier mobility. Selection of dielectric materials having high phonon excitation energy is the safest solution to reduce the surface phonon scattering.

#### **1.6 SCOPE OF THE DISSERTATION**

This dissertation focuses on fundamental properties of layered semiconductors, particularly, effects of dielectric properties, extrinsic impurities, and ambient absorbates on the

transport properties of ultrathin layered semiconductors. Chapter 2 introduces the working principles of the major characterization tools and techniques used throughout this research. To reveal the detailed extrinsic and intrinsic scattering mechanisms in MoS<sub>2</sub>, we have fabricated MoS<sub>2</sub>FETs on a wide range of substrates with different dielectric and surface properties and carried out variable temperature measurements in four-wire and Hall bar configuration as presented in chapter 3. In chapter 4, we present the structural characterization MoSe<sub>2</sub> crystal, FET device fabrication and detailed transport properties of MoSe<sub>2</sub>. Chapter 5 introduces a novel 2D/2D vertical ven der Waals assembly method to achieve low-resistance ohmic contacts for TMD electronic devices. Chapter 6 reports the fundamental properties of black phosphorus (BP), which has drastically different band gap size and charge neutrality level than TMDs. Finally, chapter 7 includes the fabrication process for integration of high- k dielectric to TMDs based FETs and devices electrical characterizations.

#### **CHAPTER 2 MAJOR EXPERIMENTAL TECHNIQUES**

#### 2.1 OPTICAL MICROSCOPE

An optical microscope uses visible light to magnify objects for observation. It uses a small and spherical objective lens which has a shorter focal length and another longer focal length lens called eyepiece. Object is placed near to objective lens and observes through eyepiece. The microscope brings an object's image into focus at a close distance within the tube by objective lens and eyepiece magnifies the image. Aside from a light source, a microscope also has a condenser which focuses light from the source to a small, bright spot of the specimen. It has fixed eyepieces and interchangeable objective lenses with different magnification. It can magnify incredibly small areas or object when the objective lenses are changed from flat with low magnification lenses to rounder with high magnification ones. The image quality seen by using an optical microscope is assessed based on brightness, resolution and contrast.

Optical microscope shows different contrast for different thickness 2D materials. The TMDs flake and other 2D flakes transfer on the substrate is observed under optical microscope to identify rough thickness of the better flakes. The optical microscope is used to estimate the thickness and identify the cleanness and uniformity of the sample.

## Fig.2.1.1 Optical microscope

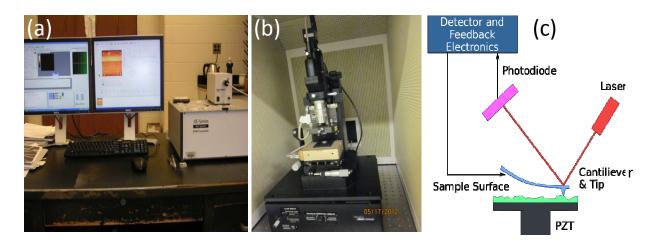

# 2.2 ATOMIC FORCE MICROSCOPE (AFM)

AFM is a kind of scanning probe microscope. A sharp probe called tip is moved close to the surface of sample under study in non-contact mode. The tip is connected to a cantilever. The tip scans across the sample surface and comes into force of interactions. As the cantilever is displaced by its interactions with the surface, the reflection of the laser beam will be displaced on the surface of the photodiode and the image is constructed. The surface topography is fully determined by the interacting forces during scan. AFM can measure a roughness of a sample surface, help to determine shape & the dimensions of sample, identify atoms at a surface, evaluate an interaction between a specific atom and its neighboring atoms, distinguish change in physical properties arisen from a change in an atomic arrangement through the atomic manipulation, help to distinguish cancer cells and normal cells based on a hardness of cells, evaluate an interaction between a specific cell and its neighboring cells in a competitive culture system. The identified better sample flakes under optical microscope is characterized by noncontact mode XE-70 atomic force microscope (AFM). The surface topography of AFM image is analyses to determine the dimensions (length, width, thickness etc.), surface cleanness and surface roughness of the identified sample. XEI image processing software is used to process the AFM image. The surface smoothness is compare by root mean square value of PSD.

**Fig.2.2.1** Atomic force microscope (Park Systems XE-70) (a) software system (b) the optical microscope and X-Y scanner as the main body(c) block diagram of AFM

## 2.3 SCANNING ELECTRON MICROSCOPE (SEM)

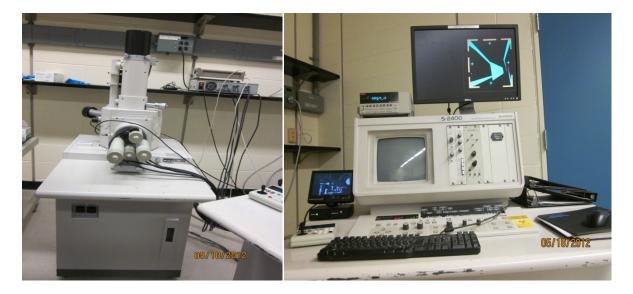

Although photo lithography is widely used in semiconductor industry, there are several other lithography methods developed in the past few decades such as X-ray lithography, electron beam lithography and ion beam lithography. E-beam lithography seems to provide appropriate way using electron as a source for making smaller feature size regarding feasibility and resolution since the diffraction limit has been an issue for photo lithography in current semiconductor technology in small feature size. Although slow speed and little costly are the drawbacks for e-beam lithography system, it has already been commonly used in semiconductor industry for patterning a smaller feature size.

In a SEM, a highly focused beam of electrons emitting from an electron gun is travel through a vacuum and are guided by electromagnetic lenses. The electrons beam hit the substrate surface coated by polymer and interact with it to break its bond. The polymer area which is interacted with electrons beam is easily soluble in organic solvent. We used Hitachi S-2400 SEM system with 25 kV maximum accelerating voltage to write the lithography patterns.

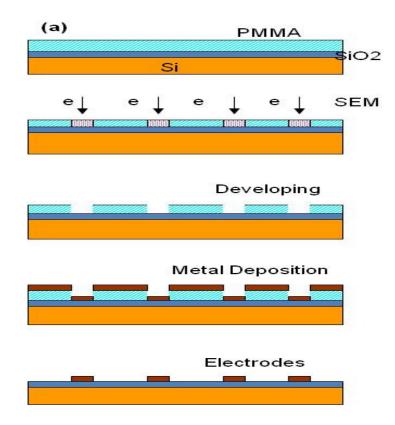

The selected better flake image is transferred to nano patterning generation system (NPGS) sketch and draws the desire electrodes as needed for different measurements configuration. Two layers of Polymethyl methacrylate (PMMA) polymer is coated on the substrate having sample and hit the collimated electrons beam to the specific area with specific design electrodes. In this work, we used Polymethyl methacrylate (PMMA) having two different molecular weight (PMMA 495-A4, PMMA 950-A2) as a positive resist and hydrogen silsesquioxane (HSQ) as negative resists for e-beam lithography. Then the substrate is dipped in MIBK/MEK solution (if PMMA as a resist) or CD-26 (if HSQ as a resist) to dissolve and open the specific design electrodes area PMMA polymer. The e-beam patterned substrate is coated by metal and defines metal electrodes to connect the measurement system.

Fig.2.3.1 Scanning electron microscope (SEM) (Hitachi S-2400) set up for e-beam lithography.

**Fig.2.3.2** The schematic diagrams show the integrated processes with electron beam lithography and metal deposition, BJD 1800 e-beam metal evaporator

In terms of response to the electrons, polymers used in e-beam lithography are divided into two types, positive and negative. Positive resists are easily removed in the solvent on the ebeam exposed areas due to broken cross link polymer by e-beam like polymethyl methacrylate (PMMA) which is the most commonly used polymer for e-beam lithography. Negative resists do not dissolve in the solvent on the e-beam exposed area. Negative resist like hydrogen silsesquioxane (HSQ) is sometimes used for the protective mask of written electrodes.

#### 2.4 BJD 1800 e-BEAM METAL EVAPORATOR

BJD-1800 metal evaporator is used to evaporate the metals to tailor the electrodes. The electrodes defined device is adjusted horizontally on BJD chamber and pumps it down to pressure about  $\sim 10^{-6}$ torr and deposit metal electrodes with sufficient slow deposition rate. The

metal deposition is done by evaporating the metal normal to the substrate without rotation for easy lift off. E-beam with proper frequency and current to hit the targets metals (contained in crucible) and get the metal evaporated to deposited on the target areas.

Fig.2.4.1 BJD 1800 e-beam metal evaporator

## 2.5 ULVAC MILA-5000 ANNEALING TOOL

The residue introduces during the fabrication process is crucial to alter the transport properties of 2D channel materials. We use different organic polymer like PMMA, PDMS, PC during fabrication process as well as blue tape for mechanical exfoliation of the sample. The substrate and sample may absorb moister and air during fabrication process timeline which depends upon humidity of the lab along with time to fabricate devices. To remove the organic residues, moister absorbed and other residues during the sample/device fabrication process, annealing is done in high vacuum. Bare Si/SiO<sub>2</sub> substrate was annealed at 600°C for 10 minutes with ramping up and ramping down time 10 minutes to reach the desired temperature. The substrate with 2D materials flakes and devices was annealed at lower temperature (250°C for 30 minutes) to minimize the thermal treatment effects in 2D materials. We adopted multiple transfer steps to stack the 2D materials for complex device structure. Every step in the transfer process is crucial which can easily introduce impurities from PDMS stamp and form wrinkles during transfer process. To remove impurities and wrinkles during transfer process, the substrate was annealed at 400°C for 30 minutes in every steps of transfer. The substrate was annealed at 250°C for 30 minutes after transfer of TMDs flakes to minimize the thermal defects in TMDs channel. Non-contact mode AFM was used to determine dimensions and cleanness of the sample. Transport properties of the FET devices were measured by a Keithley 4200 semiconductor parameter analyzer in a Lakeshore Cryogenic probe station under high vacuum (~ 1×10<sup>-6</sup>Torr) and in a Physical Property Measurement System (PPMS) from Quantum Design.

Fig.2.5.1 Ulvac mila-5000 annealing tool

## 2.6 KEITHLEY 4200 SEMICONDUCTOR PARAMETER ANALYSER

The device after defined Ti/Au electrodes is kept in Lakeshore cryogenic probe station chamber and pumps it overnight to reach the pressure down to  $\sim 1 \times 10^{-6}$  torr. The Keithley 4200

parameter analyzer is used to characterize its electrical properties at different temperatures varying from 77K to 300K by using liquid nitrogen.

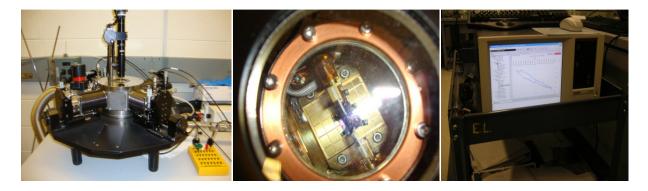

Fig.2.6.1 The cryogenic probe station, its top inner view and Keithley 4200 semiconductor parameter analyzer

## 2.7 PHYSICAL PROPERTY MEASUREMENT SYSTEM

The PPMS is used to measure transport properties of our sample in magnet field at room temperature down to cryogenic temperatures. The Quantum Design PPMS (Model 6000) used for characterizing our field effect transistors have the following specifications:

- 1. Magnetic Field Range: -9T to +9T

- 2. Temperature Range: 1.8-400 K

- 3. AC Frequency Range: 10 Hz to 10 kHz

- 4. AC Field Amplitude Range: 2 mOe to 15 Oe

- 5. Sensitivity of DC magnetization measurements:  $2.5 \times 10^{-5}$  emu

- 6. Sensitivity of AC susceptibility measurements:  $2 \times 10^{-8}$  emu

The physical property measurement system by quantum design is used to measure device transport properties at different temperature ranging from 4K to 300K in a helium cryogenic system. Magnetic field is applied in Hall bar configuration to perform Hall measurements for our Hall bar devices.

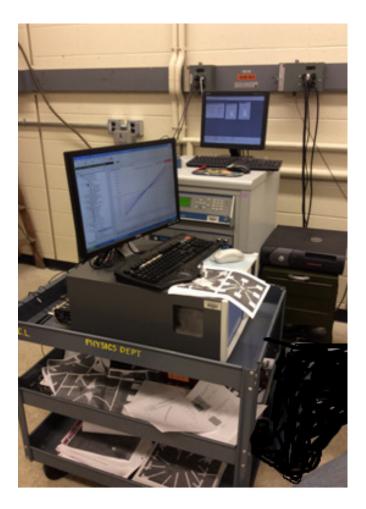

Fig.2.7.1 Physical Property Measurement System (PPMS) and Keithley 4200 semiconductor parameter analyzer

## 2.8 LCR METER

We used HP 4284A precision LCR meter for our measurements. HP 4284A precision LCR meter measures two components of the complex parameters at the same time of a measurement cycle. The primary measurement parameters are: absolute value of impedance (|Z|), absolute value of admittance (|Y|), inductance (L), capacitance (C), resistance (R), conductance (G) and the secondary measurement parameters are: dissipation factor (D), quality factor (Q), equivalent series resistance ( $R_s$ ), equivalent parallel resistance ( $R_P$ ), reactance (X), susceptance (B), phase angle ( $\theta$ ).

The HP 4284A precision LCR meter is used to measure the capacitance of the dielectric used to fabricate devices. It has frequency range from 20 Hz to 1 MHz with different mode of measurements. MIM junction is designed by sandwiching dielectric between two metal electrodes. Capacitance is measured with sweeping the bias voltage at different frequencies level by applying low AC system voltage (50 mV to 100mV). The capacitance is measured in  $C_p$ :D configuration to minimize the parasitic capacitance effects. To measure the capacitance more precisely, the recorded measure value is set at least average of 8 consecutive measurements.

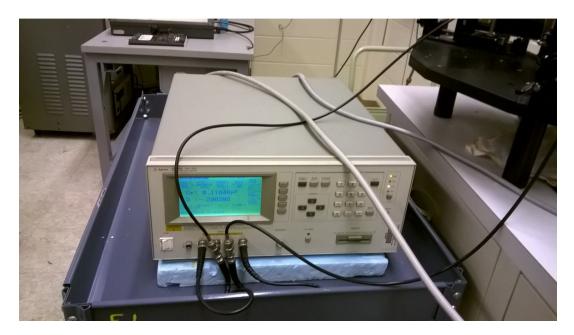

Fig.2.8.1 Alignment 4284A precision LCR meter

## CHAPTER 3 STUDY OF INTRINSIC AND SUBSTRATE DEPENDENCE TRANSPOR TPROPERTIES OF M<sub>0</sub>S<sub>2</sub> FIELD EFFECT TRANSISTOR

#### **3.1 INTRODUCTION**

Two dimensional (2D) layered crystals have become one of the most attractive materials for future electronics and optoelectronics due to their unique properties. Graphene has shown extremely high charge-carrier mobility, optical transparency, and broadband absorption.<sup>65-69</sup> However, a zero band gap in grapheme limits its potential in digital and optical applications.<sup>70, 71</sup> Monolayer and multilayer metal dichalcogenides (TMDs) such asMoS<sub>2</sub>, MoSe<sub>2</sub>, WSe<sub>2</sub> and WS<sub>2</sub> have exhibited desirable "graphene like" properties including a reasonably high carrier mobility, mechanical flexibility, chemical and thermal stability.<sup>5-19</sup> Moreover, unlike grapheme they offer the advantage of a substantial band gap, which is needed for digital electronic applications. In addition, pristine surfaces of TMDs are free of dangling bonds, which reduces surface roughness scattering and interface traps. The properties of TMDs have made them stand out as twodimensional materials beyond graphene for electronic and optoelectronic applications. As one of the most studied members of the TMD family, MoS<sub>2</sub> FETs have demonstrated promising device characteristics including a high ON/OFF ratio of >10<sup>8</sup> and a nearly ideal low subthreshold swing (SS) of ~ 70mV/dec.<sup>3,9</sup>

In order to optimize the performance of  $MoS_2$  FETs for electronic applications, it is essential to understand the dominant intrinsic and extrinsic scattering mechanisms that limit the carrier mobility, especially at room-temperature. However, the electron mobilities of monolayer and multilayer  $MoS_2$  devices reported so far by multiple groups vary widely. Experimentally observed room-temperature mobility values of monolayer  $MoS_2$  has been reported vary from less than 1 to ~ 80 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, <sup>7, 11, 12, 14, 72-74</sup> which are significantly below than the theoretical limit of ~410 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> when only the intrinsic phonon scattering is considered.<sup>58</sup> On the other hand,