Wayne State University

Wayne State University Dissertations

1-1-2011

# Qos-aware fine-grained power management in networked computing systems

Jiayu Gong Wayne State University,

Follow this and additional works at: http://digitalcommons.wayne.edu/oa\_dissertations

Part of the Computer Engineering Commons

#### Recommended Citation

Gong, Jiayu, "Qos-aware fine-grained power management in networked computing systems" (2011). Wayne State University Dissertations. Paper 349.

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

## QOS-AWARE FINE-GRAINED POWER MANAGEMENT IN NETWORKED COMPUTING SYSTEMS

by

#### JIAYU GONG

#### **DISSERTATION**

Submitted to the Graduate School of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

## DOCTOR OF PHILOSOPHY

2011

MAJOR:

| EN           | IGINEERING |

|--------------|------------|

| Approved by: |            |

|              |            |

| Advisor      | Date       |

|              |            |

|              |            |

|              |            |

COMPUTER

## ©COPYRIGHT BY JIAYU GONG

2011

All Rights Reserved

#### **ACKNOWLEDGEMENTS**

First and foremost I would like to thank my advisor, Dr. Cheng-Zhong Xu. It has been an honor to work with him. I appreciate all his invaluable guidance, support, and encouragement throughout this work. The joy and enthusiasm he has for the research was contagious and motivational for me in the Ph.D. pursuit, even during tough times.

I am also grateful to my committee members: Dr. Song Jiang, Dr. Nabil Sarhan, and Dr. Hongwei Zhang for their time, interest, and helpful suggestions to improve this work.

The memebers in Cloud and Internet Computing (CIC) group have contributed immensely to my personal and professional time at Wayne State University. The group has been a source of friendships as well as great advice and collaboration. I am privileged for having Xiliang Zhong, Song Fu, Jia Rao, Bojin Liu, Bo Yu, Xiangping Bu, Kun Wang, Zhen Kong, Xuechen Zhang, Yizhe Wang, Yuehai Xu, Haikun Liu, Yaqin Luo, Cheng Wang, Yudi Wei, Duan Hu, and Mumtaz Dawoodi as my colleagues and friends.

Finally, I would like to thank my family for all their love, encouragement and understanding. I wish to thank my parents supporting me in all my pursuits. I wish to express my gratitude to my wife, Jing Qian, for her continuous love, understanding and support for these days and nights. Especially, the time she spared for me on our little Alvin (son) and from her own studies was precious.

## TABLE OF CONTENTS

| Ackno   | wledge  | ements                                                | ii  |

|---------|---------|-------------------------------------------------------|-----|

| List of | Figur   | es                                                    | vii |

| List of | Table   | s                                                     | ix  |

| Chapt   | er 1 I  | Introduction                                          | 1   |

| 1.1     | Backg   | ground and Motivation                                 | 1   |

| 1.2     | Proble  | ems and Objectives                                    | 4   |

| 1.3     | Summ    | nary of Contributions                                 | 6   |

|         | 1.3.1   | Outline                                               | 9   |

| Chapt   | er 2 I  | Related Work                                          | 11  |

| 2.1     | Trans   | mission Speed Adaptation in Communication Systems     | 11  |

| 2.2     | Power   | Management in Enterprise Environments                 | 14  |

|         | 2.2.1   | Power Consumption Measurement, Modeling and Profiling | 14  |

|         | 2.2.2   | Power Management Mechanism                            | 16  |

|         | 2.2.3   | Power Management Scope                                | 18  |

|         | 2.2.4   | Power Management Objectives                           | 20  |

|         | 2.2.5   | Power Management Methodologies                        | 25  |

| Chapt   | er 3    | Maximizing Rewards in Wireless Networks with Energy   | 7   |

| and     | l Timiı | ng Constraints                                        | 29  |

| 3.1     | System  | m Model and Problem Formulation                       | 30  |

|         | 3.1.1   | Data Model                                            | 30  |

|         | 319     | Power Consumption Model                               | 39  |

|       | 3.1.3  | Problem Formulation                                | <b>3</b> 4 |

|-------|--------|----------------------------------------------------|------------|

| 3.2   | Branc  | h-and-Prune for the Optimal Solutions              | 37         |

|       | 3.2.1  | Branch-and-Prune Algorithm                         | 38         |

|       | 3.2.2  | Algorithm Analysis                                 | 42         |

| 3.3   | Time-  | Efficient Approximation                            | 43         |

|       | 3.3.1  | Polynomial-time Approximated Approach (Clustering) | 44         |

|       | 3.3.2  | Algorithm Analysis                                 | 46         |

| 3.4   | Perfor | mance Evaluation                                   | 47         |

|       | 3.4.1  | Simulation Setup                                   | 48         |

|       | 3.4.2  | Simulation Results                                 | 49         |

| Chapt | er 4 l | PPM: A Power Management Middleware for Networked   |            |

| -     |        |                                                    |            |

| Cor   | nputin | ng Systems                                         | 61         |

| 4.1   | Overv  | iew                                                | 62         |

| 4.2   | Real-  | Time Power Metering                                | 63         |

|       | 4.2.1  | Design of Power Metering Tool                      | 63         |

|       | 4.2.2  | Power Model                                        | 65         |

|       | 4.2.3  | Power Model Evaluation                             | 71         |

|       | 4.2.4  | Integration with DSP                               | 74         |

| 4.3   | Power  | Management Middleware                              | 76         |

|       | 4.3.1  | Architecture                                       | 76         |

|       | 4.3.2  | Design of Power Management Client (PMC)            | 78         |

|       | 4.3.3  | Design of Power Management Server (PMS)            | 79         |

|       | 4.3.4  | Cross-Layer Message Passing                        | 80         |

| Chapt | er 5 S | System-Level Peak Power Management                 | 82         |

| 5.1   |        | -box Feedback Control for Power Management         | 83         |

|        | 5.1.1   | Overview of Feedback Control                             |  |

|--------|---------|----------------------------------------------------------|--|

|        | 5.1.2   | Design of the PID Controller                             |  |

| 5.2    | A Gra   | y-box Approach                                           |  |

|        | 5.2.1   | Architecture                                             |  |

|        | 5.2.2   | Controller Design                                        |  |

|        | 5.2.3   | Model Prediction                                         |  |

| 5.3    | Model   | Construction                                             |  |

|        | 5.3.1   | Experiment Environment                                   |  |

|        | 5.3.2   | Model Parameters Estimation                              |  |

| 5.4    | Evalua  | ation                                                    |  |

|        | 5.4.1   | Experimental Methodology                                 |  |

|        | 5.4.2   | Model Validation                                         |  |

|        | 5.4.3   | Controller Responsiveness                                |  |

|        | 5.4.4   | Impact on Performance of Application                     |  |

| Chapte | er 6 A  | automated Coordination of Power and Performance in Vir-  |  |

| tual   | lized D | Oata centers                                             |  |

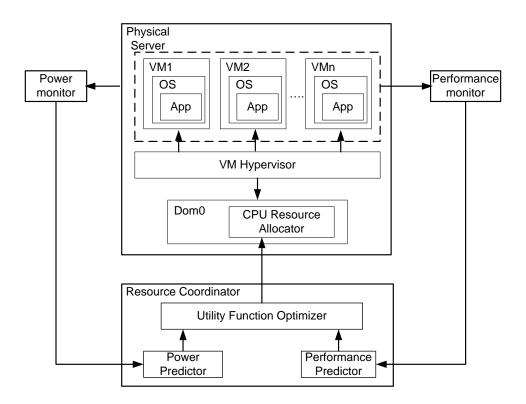

| 6.1    | System  | m Architecture                                           |  |

|        | 6.1.1   | Control Power and Performance with VCPU Caps 103         |  |

|        | 6.1.2   | Design of vPnP                                           |  |

| 6.2    | System  | n Implementation                                         |  |

| 6.3    | Evalua  | ation                                                    |  |

|        | 6.3.1   | Experimental Methodology                                 |  |

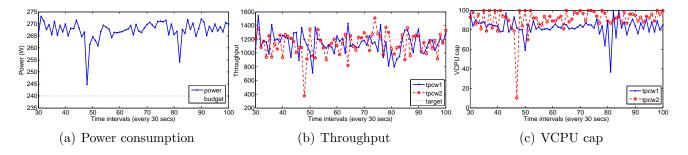

|        | 6.3.2   | Experimental Results                                     |  |

| Chapte | er 7 S  | tatistical QoS Guarantee on Processing Delay in BBUs 120 |  |

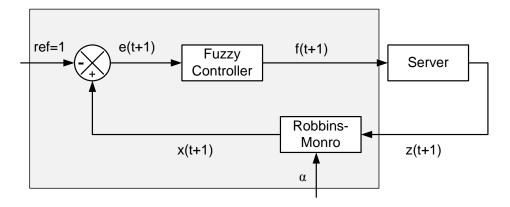

| 7.1    | Policy  | Design                                                   |  |

|        | 7.1.1 Robbins-Monro Method       | 22 |

|--------|----------------------------------|----|

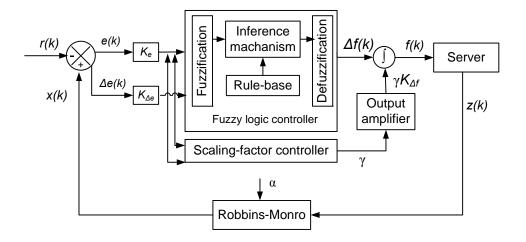

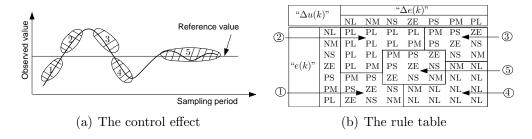

|        | 7.1.2 Fuzzy Controller           | 24 |

| 7.2    | Implementation                   | 28 |

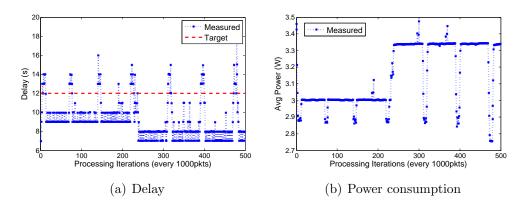

| 7.3    | Experimental Results             | 29 |

| Chapte | er 8 Conclusions and Future Work | 2  |

| 8.1    | Conclusions                      | 32 |

| 8.2    | Future Work                      | 35 |

| Refere | nces                             | 7  |

| Abstra | act                              | 0  |

| Autob  | iographical Statement            | .3 |

## LIST OF FIGURES

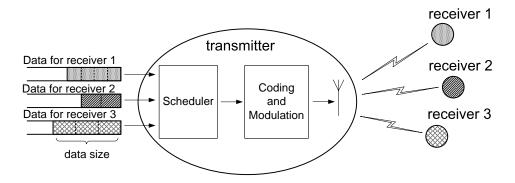

| 3.1  | One-transmitter-multiple-receiver model in a single-hop wireless network. | 30 |

|------|---------------------------------------------------------------------------|----|

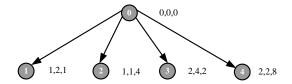

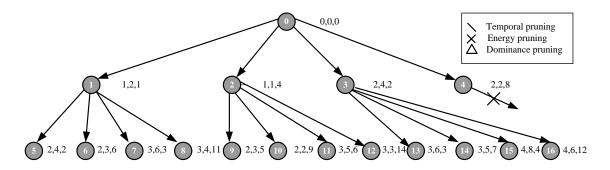

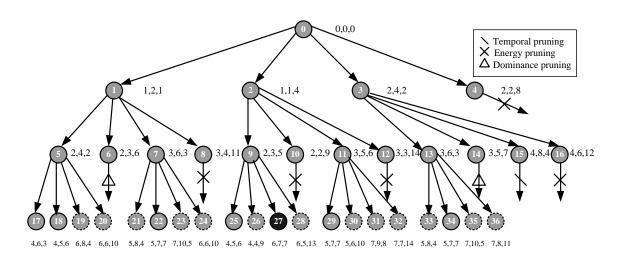

| 3.2  | Partial state space tree after one enumeration                            | 40 |

| 3.3  | Partial state space tree after two enumerations                           | 41 |

| 3.4  | The complete state space tree by pruning                                  | 41 |

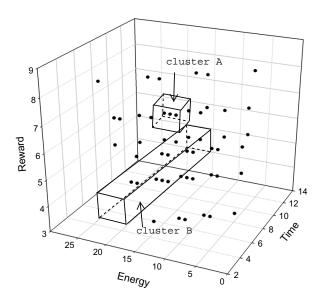

| 3.5  | The reward-time-energy relationship in a 3-D space                        | 45 |

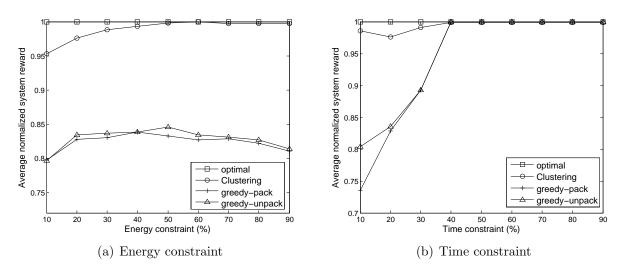

| 3.6  | Reward under different time and energy constraints                        | 50 |

| 3.7  | Reward and execution time with different numbers of receivers             | 51 |

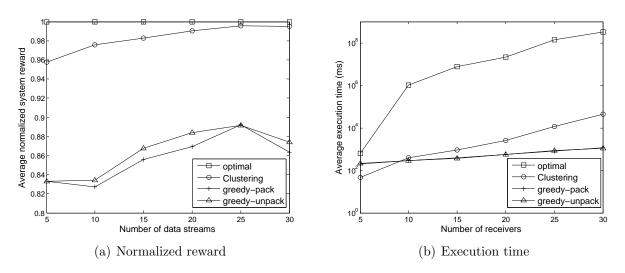

| 3.8  | Effectiveness of states pruning with 10 periodic data steams              | 54 |

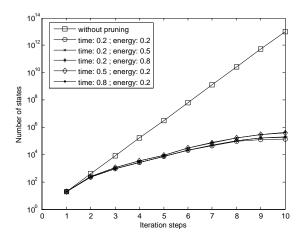

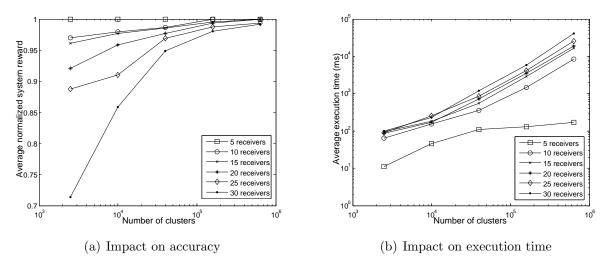

| 3.9  | Impact of number of clusters                                              | 55 |

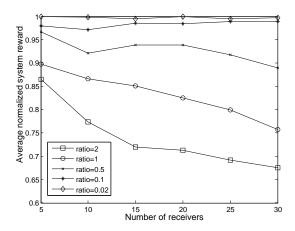

| 3.10 | Impact of ratio of problem size over cluster number                       | 57 |

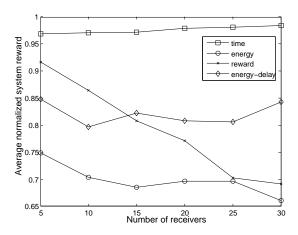

| 3.11 | Impact of different strategies selecting representative node              | 58 |

| 4.1  | Power metering design                                                     | 64 |

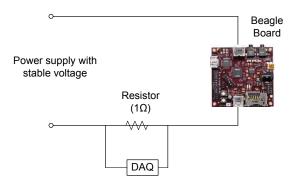

| 4.2  | Power measurement circuit                                                 | 66 |

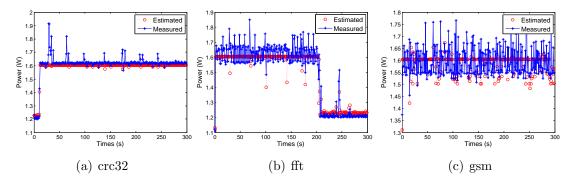

| 4.3  | Power estimation of selected applications                                 | 73 |

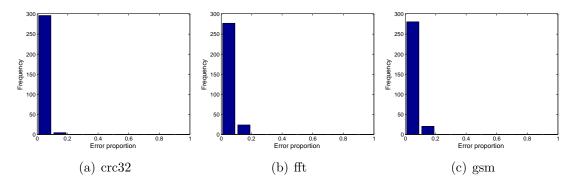

| 4.4  | Power estimation error proportion of selected applications                | 74 |

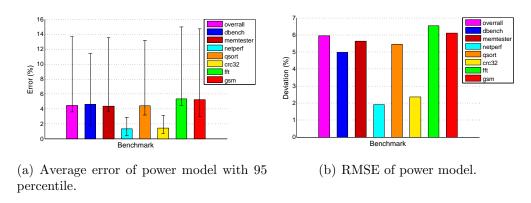

| 4.5  | Average error and RMSE of power model                                     | 74 |

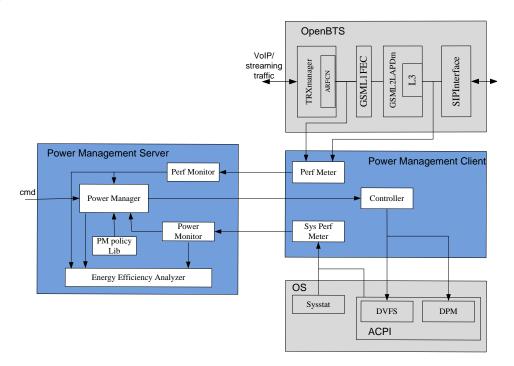

| 4.6  | Architecture of PMM                                                       | 77 |

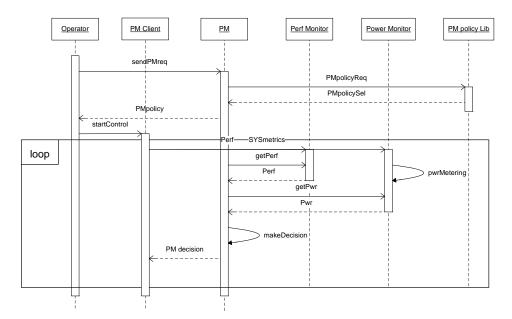

| 4.7  | Sequence diagram of PM decision making                                    | 81 |

| 5.1  | Example of a long settling time of P controller                           | 85 |

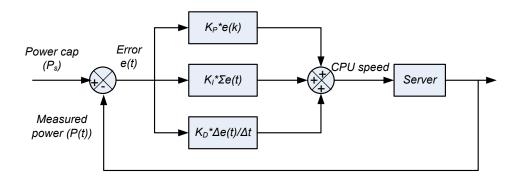

| 5.2  | PID based power cap controller                                            | 86 |

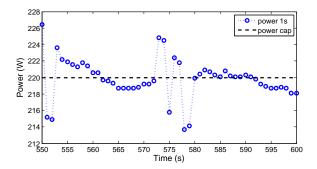

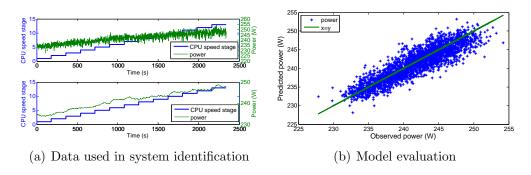

| 5.3  | Data for system identification and model evaluation                       | 86 |

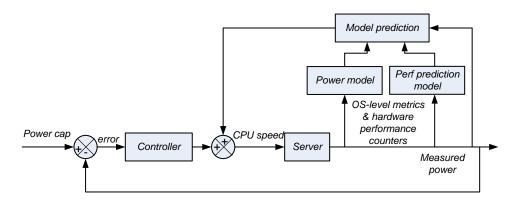

| 5.4  | Power control loop                                                        | 89 |

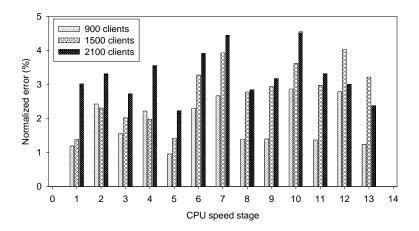

| 5.5  | Average error of power model                                              | 96 |

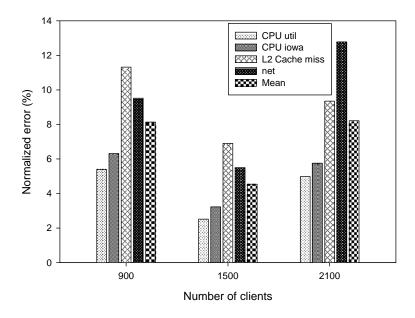

| 5.6  | Average error of performance prediction model                                    | 97  |

|------|----------------------------------------------------------------------------------|-----|

| 5.7  | System power without power controller: 900 clients                               | 98  |

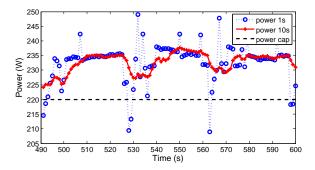

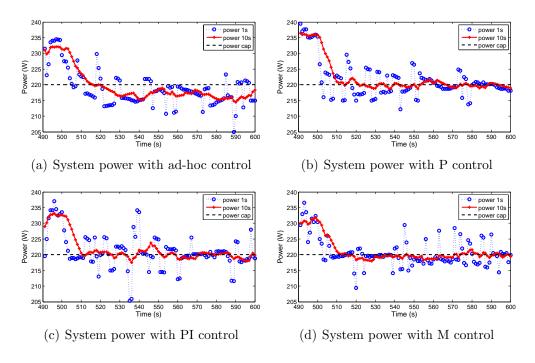

| 5.8  | Performance of controllers: 900 clients                                          | 98  |

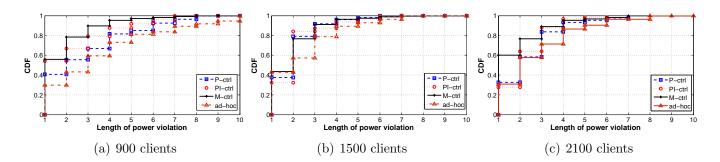

| 5.9  | CDF of length of power violations                                                | 99  |

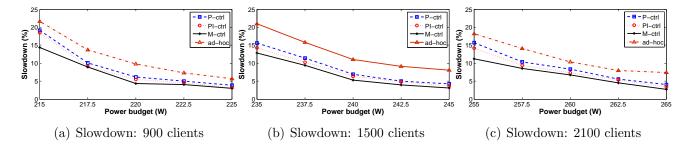

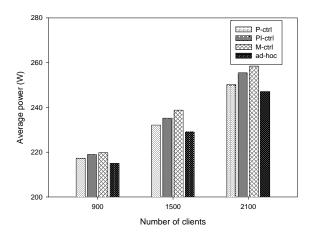

| 5.10 | Impact on application performance                                                | 100 |

| 5.11 | Average power                                                                    | 101 |

| 6.1  | System architecture of vPnP                                                      | 105 |

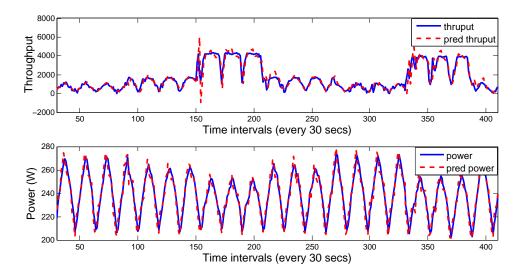

| 6.2  | Performance and power prediction                                                 | 113 |

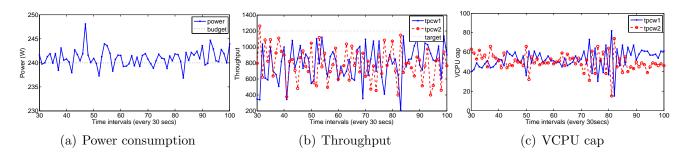

| 6.3  | Results of utility function $U_1$ with performance-preferred policy ( $\alpha =$ |     |

|      | 0.9)                                                                             | 115 |

| 6.4  | Results of utility function $U_1$ with power-preferred policy ( $\alpha=0.1$ )   | 115 |

| 6.5  | Results of utility function $U_2$ with power-preferred policy ( $\alpha=0.1$ )   | 116 |

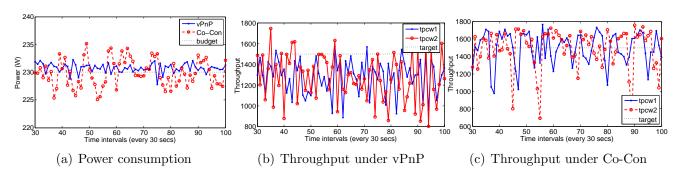

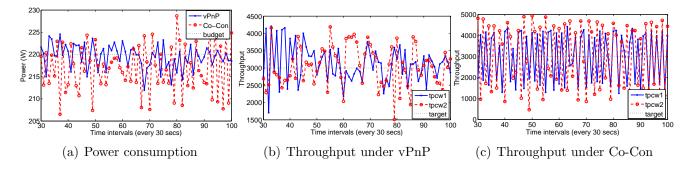

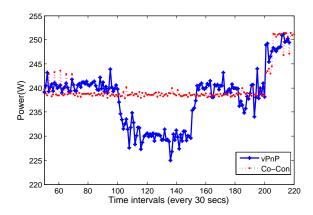

| 6.6  | Comparison between vPnP and Co-Con running TCPW shopping work-                   |     |

|      | load                                                                             | 116 |

| 6.7  | Comparison between vPnP and CoCon running TPC-W ordering work-                   |     |

|      | load                                                                             | 117 |

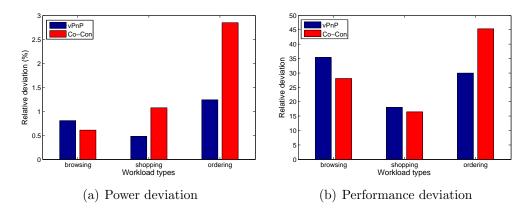

| 6.8  | Performance of vPnP and Co-Con                                                   | 118 |

| 6.9  | Reaction to power budget change                                                  | 119 |

| 7.1  | Power management controller design                                               | 124 |

| 7.2  | Fuzzy controller design                                                          | 125 |

| 7.3  | Design of the fuzzy control rules                                                | 127 |

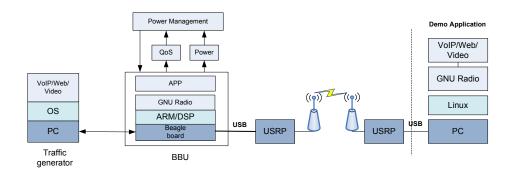

| 7.4  | System Overview                                                                  | 129 |

| 7.5  | Statistic QoS controller on streaming on BBU                                     | 129 |

## LIST OF TABLES

| 3.1 | An example for 4 data streams with 2 data size levels and 2 transmis- |     |

|-----|-----------------------------------------------------------------------|-----|

|     | sion rate levels                                                      | 39  |

| 4.1 | Beagle Board major hardware components specification                  | 66  |

| 4.2 | Power consumption and execution time of DSP (in comparison with       |     |

|     | ARM)                                                                  | 75  |

| 6.1 | Prediction accuracy                                                   | 114 |

| 7.1 | Comparison of three settings (streaming on BBU)                       | 130 |

| 7.2 | Comparison of three target delay with same QoS quantile (streaming    |     |

|     | on BBU)                                                               | 130 |

| 7.3 | Comparison of three running scenarios (TPC-W on server)               | 131 |

## Chapter 1

## Introduction

Power is emerging to be the key challenge in networked computing systems, from real-time embedded systems to enterprise server environments. Meanwhile, a guaranteed level of Quality-of-Service (QoS) is required to be provided. Our work is motivated by the challenge of power management with demands of QoS guarantee in networked computing systems. In this chapter, we first introduce the background and motivation of our work in power management in networked computing systems. Then, we discuss the major design challenges and present the features of our solution. We will outline the rest of the dissertation in the end of this chapter.

## 1.1 Background and Motivation

Power management is one of the key design issues in networked computing systems. The motivation of the proposed research will be discussed from the perspectives of both real-time embedded and enterprise environments.

In the context of real-time embedded systems, energy is a critical resource, especially for the networked portable systems such as PDAs, pocket PCs, and cellu-

lar phones. On one hand, many popular applications designed for these systems consume significantly high energy, such as video processing and wireless communications. On the other hand, most of these devices are power by batteries which is finite. Limitations in battery capacities and demands for longer device operation time have motivated research for networked real-time systems, which can be interpreted as minimizing total energy consumption for a given workload. However, some wireless devices may rely on renewable energy sources. These devices often work in periodic cycles during which the energy collection is limited. In this case, the most important considerations is not to minimize energy consumption but to maximize the utility of energy available during each cycle [72].

The energy expenditure on networked real-time systems consists of two parts: the expenditure on the circuit board and the expenditure for wireless communication. With advances on semiconductor and circuit design, the power dissipation on circuit board is becoming less significant in the overall system power consumption. But the power consumption in wireless communications, especially the radio power components, does not benefit much from Moore's Law and has become a major source of power consumption in low-power networked real-time systems [87]. This motivates our work to be emphasized on seeking energy efficiency on wireless communication rather than on circuit board for networked real-time systems.

The concern of power consumption is not limited to the real-time embedded systems only. Such a concern rises in the enterprise server environments as well. Modern enterprise servers are featured with increasing performance capabilities accompanied by a dramatic rise in power consumption. For enterprise systems, online power management is necessary due to several significant reasons. First, the electricity bill keeps increasing in data centers and online power management can reduce this cost. By 2011, U.S. data centers will consume 100 billion kWh at a cost of \$7.4 billion in

contrast to 61 billion kWh in 2006 [38]. Second, power provisioning is constrained by the cooling and power delivery limitations. It shows the nearly 60 Amps per rack provisioned currently in data centers could be a bottleneck for high density configuration [94]. Third, high power consumption in a data center can lead to tremendous environment pollutions. According to the U.S. Environmental Protection Agency (EPA), each 1000 kWh of energy consumption generates 0.72 tons of CO<sub>2</sub> emission. The CO<sub>2</sub> emission due to U.S. data centers in 2006 was estimated to be 44 million tons, which is equivalent to the output of 8 million passenger vehicles [38]. Additionally, power consumption can impact reliability and availability of the systems as well.

Thus, there are two key design issues existing for effectively operating today's enterprise servers. First, power consumption has to be capped within the capacity of the power supplies and cooling facilities in order to reduce operating costs and avoid system failures caused by power capacity overload or system overheating. Second, service owners need to be assured by meeting their required Service-Level Agreements (SLAs), such as response time and throughput. However, there are a few challenges in power and performance management in enterprise server environments. The challenge of power budgeting remains on how to dynamically plan system resource or transition the hardware components from high-power states to low-power states in a responsive and accurate manner whenever the system power consumption exceeds a given power budget. As the characteristics of workloads in servers are usually heterogeneous and time-varying, the impact on system performance due to power management varies greatly. Improving energy efficiency without significant effect on performance as possible becomes challenging. Hence, both performance and power management algorithms must be self-adaptive to workload variations for optimal overall system performance. With proliferation of virtualization, the density of server configuration can be higher using consolidation. It leads to a more severe power provisioning problem. Furthermore, power and performance management becomes more challenging due to resource sharing and interference among co-residing virtual machines (VMs).

Although there are a number of existing work providing power management strategies to meet different requirements, the lack of a general framework of power management solutions motivates us to design and implement a power management middleware for networked computing systems.

## 1.2 Problems and Objectives

In this dissertation, we aim to build power-efficient networked computing systems. Nowadays, one general principle in system design is to design the systems based on their peak performance requirement. However, their capacities often exceed the average throughput demand and their busy time usually accounts for only a small fraction of the application time. For example, in [14], the authors analyzed average CPU utilization of a sample of 5,000 Google servers over a period of 6 months. Though the distribution of CPU utilization may vary across different clusters and workloads, a common trend is that that servers spend most of time within the 10-50% CPU utilization range and relatively little aggregate time at high utilization levels. This makes it possible for processor or transmitter slowdown to reduce the processing speed and still ensure no tasks miss their deadlines. Both processor speed slowdown and wireless transmitter slowdown save energy with the penalty of performance loss.

In real-time systems, applications are usually delay sensitive. More and more wireless real-time systems are being built with renewable energy resources. These devices often work in periodic cycles during which the energy collection is limited.

Due to the real-time and energy limitation, it is not always possible for a wireless node to deliver all data in its transmission buffer at a time. It is more desirable to transit more valuable data first in case a wireless node cannot send all its data. To quantify the level of importance of a packet, we associate a reward to each packet transmitted. Thus, the object becomes to maximize system rewards under given time and energy constraints.

The power consumption from circuit board is a major resource of power consumption of the entire system thus it affect the system-wide power consumption significantly. In server environments, processor is still one dominant energy-consuming components although its significance is decreasing. Dynamic Voltage and Frequency Scaling (DVFS) is the most effective slowdown technique to reduce power consumption by scaling the processor voltage and frequency when the system is not fully loaded. Ideally, processor slowdown leads to cubic power saving on processor with a linear performance loss. DVFS can thus regulate system-level power consumption effectively. Generally, system-level power consumption increases with system processing, networking and storage usage. It is difficult to plan the system usage in advance in a networked computing system due to the nature of variability. To regulate the power consumption within the power cap in an accurate, stable and responsive manner is necessary to reduce operating costs and avoid system failures without significant performance loss. As the existing black-box method may not be responsive over a variety of workloads, we provide responsive control over system-level power consumption using information of system behaviors.

On the other track, performance could be the first-class constraint to meet. Thus, servers are often over-provisioned significantly to meet target performance constraints under peak loads. However, this design leads to poor overall energy efficiency since servers are typically underutilized. Thus, power consumption is desirable to be re-

duced in order to improve energy efficiency. Soft real-time services require to maintain QoS quantile to a set point. The challenges rely on the difficulty on planning system usage to meet the set point while minimizing power consumption.

Additionally, it is also desirable to provide guarantees on both power and performance. As the characteristics of workloads in servers are usually heterogeneous and time-varying, it is required that power management scheme should be self-adaptive to workload variations for optimal overall system performance. Virtualization technologies bring Due to resource sharing of VMs, the techniques imposed on shared hardwares, such as DVFS, may not be applicable. Instead, re-allocating CPU resources by limiting processing time to VMs can both regulate power consumption and retain performance isolation.

We notice there is few work providing a general-purposed, practical and comprehensive power management middleware for networked computing systems. We develop a power management middleware, named PMM. PMM has the functionalities of power and performance monitoring, power management (PM) policy selection and control, as well as energy efficiency analysis. PMM is a general framework of power management middleware for different platforms, from servers to real-time embedded systems. We deploy PMM on Base Band Units (BBUs) to supply the gap of lack of power management solutions in BBUs.

## 1.3 Summary of Contributions

We have studied power management for wireless transmitters, enterprise servers, virtual machines, and Base Band Units (BBUs) under different power and workload models. The main contributions of this dissertaion are as following:

1. For real-time embedded system, we formulated the reward maximization prob-

lem in wireless networks under delay and energy constraints as a Multidimensional Multi-Choice Knapsack Problem (MMKP). We developed a branch-and-prune algorithm to solve this problem optimally in pseudo-polynomial running time. Then we proposed a heuristic approach, named Clustering to approximate the optimal solution with polynomial time complexity. Simulation results show the effectiveness of proposed optimal solution and Clustering algorithm. Meanswhile, the Clustering approach can closely approximate the optimal solution at a much smaller computational cost. The results were presented in [50].

2. Circuit board power consumption is still the major resource of system power consumption and needs to be managed. Thus, to provide a general-purposed and practical power management solution to networked computing system, we developed a power management middleware, named PMM, to regulate system power using circuit board actuators. A real-time power metering tool is developed and integrated in PMM. This tool can estimate system-level power consumption in a real-time and accurate manner with high accuracy. Meanwhile, it provides the information of power consumption of subsystems as well. Such a software-based power metering solution is crucial for the deployment of PMM in a large scale. We designed PMM using a client-server model. PMM has the functionalities of power and performance monitoring, power management (PM) policy selection and control, as well as energy efficiency analysis. A PM policy library is included in PMM to provide PM policies for different purposes. This library is flexible to extend. A prototype of PMM is implemented and deployed on BBUs. To the best of our knowledge, this middleware is the first software to provide comprehensive and practical solution to power management in BBUs. Three PM policies for different purposes have been included in the PM pol-

- icy library of this prototype. These policies have been validated on different platforms, such as enterprise servers, virtual environments and BBUs.

- 3. In the enterprise environments, we proposed a system-level power estimation model for different CPU running speeds and a performance impact model for a web server by using performance events. Based on these two models, we developed a model-predictive feedback controller to control system-level power consumption while maximizing system performance. In contrast to the exiting feedback control, our proposed approach is more responsive by restricting more than 75% of power overloading settle to power cap within 2 control periods. Meanwhile, the system performance degradation is minimal. Details have been published in [48].

- 4. To coordinate power and performance in virtualized data centers, we developed vPnP, a feedback control based coordination system, to provide guarantees on a service level agreement (SLA) with respect to both performance and power. In this system, we proposed self-tuning model predictors to estimate the performance and power, respectively and a utility function optimizer to achieve different levels of tradeoff between power and performance. We implemented vPnP in a Xen-based infrastructure. The experimental results show the flexibitilty of vPnP to achieve different levels of tradeoff between performance and power. Our proposed vPnP system is more robust than existing two-layer feedback controller over a variety of workloads by reducing as large as 15% performance deviation. The results were published in [49].

- 5. To improve energy efficiency in BBUs, we proposed a power management strategy for controlling delay and minimizing power consumption using DVFS. We use the Robbins-Monro (RM) stochastic approximation method to estimate de-

lay quantile. We couple a fuzzy controller with the RM algorithm to obtain the CPU frequency for the receiver side BBU that will maintain performance within the specified QoS. This controller is non-workload-specific and self-adaptive.

#### 1.3.1 Outline

The rest of this plan is organized as follows. Chapter 2 reviews the existing work of power management techniques for wireless transmitters, server environments and virtual machines.

In Chapter 3, we study the reward maximization problem for wireless real-time systems. We prove this problem is NP-hard. But by exploiting the properties of the reward optimization problem, we propose the optimal solution in pseudo-polynomial time. And we provide a sub-optimal approach with polynomial time complexity.

We developed a power management middleware in Chapter 4 for networked computing systems. It can be easily adapted to different platforms, such as servers and real-time embedded systems. This power management middleware has the functional-ities of power and performance monitoring, power management (PM) policy selection and PM control, as well as energy efficiency analysis. More details of the PM policies in this middleware will be discussed in Chapter 5, 6, and 7, under different contexts.

In the context of enterprise environments, we develop a model-predictive feedback controller to control system-level power consumption in Chapter 5. This controller can dynamically adapt processor frequency to limit system-wide power consumption within power budget in a responsive manner.

In Chapter 6, we propose a feedback control based coordination system to provide guarantee in SLA with respect to power and performance in virtualized data centers. This coordination system includes two adaptive predictors to correlate CPU resource allocation to power and performance. It employs an optimizer to find solution optimizing the utility function of power and performance.

In Chapter 7, We propose a power management strategy for controlling delay and minimizing power consumption using DVFS for BBUs. We use the Robbins-Monro (RM) stochastic approximation method to estimate delay quantile. We couple a fuzzy controller with the RM algorithm to obtain the CPU frequency for the receiver side BBU that will maintain performance within the specified QoS.

Chapter 8 concludes the dissertation with summary of our work and directions for future work.

## Chapter 2

## Related Work

This chapter reviews recent research work on power management in networked computing systems. In the context of real-time embedded system, we discuss the delay-constrained packet transmission in wireless communications by using packet transmission speed adaptation. In the enterprise environments, we give an overview of existing results on controlling system-level power consumption and system performance.

## 2.1 Transmission Speed Adaptation in Communication Systems

Power consumption in packet transmission can be reduced significantly by transmitting packets at a lower bit rate. Most existing studies on energy-efficient packet transmission focused on minimizing the energy expenditure subject to a time constraint. The time constraint can be in terms of average response time [16, 29, 91] and a single deadline [44, 104, 121] to all packets. Collins and Cruz proposed optimal transmission scheme in a fading channel with average delay constraint and a peak

transmitter power [29]. They used a simplistic channel model with two-state Markov chain and assumed the energy expediture is linear with transmitted data. Berry and Gallager considered the energy minimization problem with average buffer delay in a block-fading channel [16]. The energy minimization was turned into a convex optimization problem and dynamic programming was used to find the optimal solution. When the time constraint is considered as a single deadline for all packets, the indirect bound on packet delay requires all packets arrive before T to be transmitted no later than T. Uysal-Biyikoglu et al. [104] proposed off-line optimal and on-line near-optimal algorithms for a single transmitter-receiver pair. Same delay constraint was used in their later extension to multiple users [44].

However, both of the above time constraints do not put a limit to response time of individual packets, which may lead to unexpected large delay. To guarantee timely packet deliveries, it is more desirable to put a delay constraint to each packet [26, 67, 91, 98, 119, 124]. For example, Khojastepour and Sabharwal considered strict maximum delay constraint for each packet [67]. They established the connection between maximum delay scheduling and a linear filter for an i.i.d. input. Two optimal scheduling approaches were proposed. One is a time-variant policy which makes scheduling decisions according to each new packet arrival and uncompleted arrivals in the queue backlog. Zhong and Xu [124] studied delay constrained packet scheduling with a focus on quality of service control. They derived relation between maximum packet transmission rate and packet arrival patterns so as to provide statistical response time and packet drop control.

There are a few existing work studying packet transmission with individual delay constraints to guarantee packet transmission time. A general scenario could be a wireless transmitter communicates with multiple receivers. The transmitter generates data periodically and send the data to corresponding receivers. The wireless transmitter is powered by renewable energy sources such as solar panel. As a result, the transmitter needs to finish packet transmission subjected to both delay and energy constraints. Due to the constraints, it may not be able to send all the data. To ensure that the most valuable information is transmitted to the receivers, a reward (value) is associated to each packet. The objective is reduced to maximizing the total reward under the time and energy constraints. This kind of problems have been investigated in existing studies [109, 43, 110, 121].

Wang and Mandayam [109] tried to maximize throughput in a block fading channel under time/energy constraints. They considered a binary rate control with only an on/off model in which the transmitter either transmits with a constant power or remains silent. Under the same model and constraints, the authors later considered the transmission of a fixed size file with the objective to maximizing the probability of successful delivery of the entire file [110]. Fu et al. tried to maximize throughput in a fading channel by considering the effect of variable transmission rates [43]. All the three studies are limited to a single-transmitter-single-receiver scenario. Zhang and Chanson [121] presented optimal scheduling algorithms for the reward maximization problem in a scenario of multiple receivers under given time limits and energy constraints. They assumed all packets are ready to transmit at beginning time and this assumption is not applicable to the periodic data model where messages are released in a regular interval. In addition, they assumed a wireless transmitter with continuous transmission rate while it may only work at a limited number of rate levels in practice.

## 2.2 Power Management in Enterprise Environments

We will first review the approaches for power consumption measurement, modeling and profiling. Then we introduce power management mechanisms. After that, we discuss the related work from the perspectives of objectives, scopes and methodologies.

## 2.2.1 Power Consumption Measurement, Modeling and Profiling

External power meters (analyzers) connected with the power source can be used to measure power consumption online. External power measurement may not achieve a high sampling rate. For example, WattsUp Pro [3] measures RMS power with a sampling rate of 1Hz and Extech 380801 [4] has a sampling rate of 2Hz. In some today's blade, a power measurement circuitry is employed. This kind of in-blade power monitor firmware can measure the blade's power with a sampling rate of as large as 1000Hz [70]. The power consumption can also be measured by employing resistors connected with the power source and capturing voltage drop across the resistor using data acquisition (DAQ) hardware.

In addition to measuring the power consumption of a computer in total, we may also need to know where and when the power/energy has been spent [15]. A variety of power consumption profiling techniques have been proposed.

Simulation has already employed in profiling power consumption of microprocessors [21], memories [20], disks [88], and system-level [51]. However, the main draw-backs of simulation approaches rely on that the simulation models cannot match the real systems accurately and simulation itself is time-costly.

Online power measurement can profile the system-level power consumption [70,

83, 111]. Bircher and John [18] measured power in five subsystems by employing resistors connected in series with the power source. The voltage drop across the resistor is captured by data acquisition (DAQ) hardware with a sampling rate of 10000Hz. However, the online power measurement may not be practical as it needs dedicated measuring equipments for each machine or physical decomposition of a machine.

Performance Monitoring Counters (PMCs) can assist power consumption profiling and modeling, which can be traced back to [15]. Contreras et al. [31] proposed a linear power estimation model using hardware performance counters to estimate run-time CPU and memory power consumption using Intel PXA255 processor. The number of counters used is more than that the processor can provide concurrently thus this model is not feasible for online power estimation. Fan et al. [40] proposed a linear model considering CPU utilization and an empirical term which minimize squared root to improve accuracy. Heath et al. [52] presented a linear model using disk utilization in addition to CPU utilization. Both models ignore the impact on power consumption from other subsystems. Bircher and John [18] proposed power models for entire systems and subsystems using PMCs. It needs to decompose the measurement of power for each subsystem physically. Economous et al. [36] presented Mantis providing a full-system power prediction model by adding CPU performance counters to the OS-reported CPU and disk utilization. Notice although PMCs are embedded into most current commodity processors, the number of hardware counters that can be counted concurrently is quite limited without multiplexing technique.

### 2.2.2 Power Management Mechanism

Essentially, power management is done by transitioning hardware components back and forth between high and low-power states or modes. The components are fully active and operational in high-power mode while the functionality associated with the low-power modes depends on the particular component. Switching between power modes may introduce non-negligible overhead in terms of both energy and performance [55].

Multiple classes of execution states are supported in today's server processors for the purpose of power management. These states include the frequency and voltage (P-state) in active mode, sleep states (C-states) in idle time, and throttle state (Tstate). Dynamic Voltage and Frequency Scaling (DVFS) is used to switch among different P-states. DVFS relies on the fact that the dynamic power consumed by microprocessor is a cubic function of its operating voltage. Thus, reducing the operating voltage/frequency provides substantial saving in power at the cost of slower execution [105]. Most of today's processors have well-documented interfaces for DVFS, such as AMD's Cool'n'Quiet technology [10] and Intel's Enhanced SpeedStep technology [59]. However, the number of voltage or frequency stages is very limited. In multi-core processors, it is not flexible to manipulate P-states due to the dependencies among the cores residing in the same die. T-states can further throttle down a CPU by inserting stop clock signals and thus omitting duty cycles. The mechanism to enter different T-states is to manipulate the processor clock modulation setting (throttling) by modulating the duty cycle of the processor clock, which changes the effective frequency of the processors [60]. Sleeping states (C-state) can be utilized when the CPU is idle. In ACPI standard, C0 is the active state and the sleep states are called C1, C2, ..., Cn [55]. The deeper C-state is, the more power the processor can save. C-states can cause relatively large switch overhead and might not be effective when the system is not idle but in a low utilization state.

Current disks also enable power management by deactivation. In active mode, the disk is being actively used and consumes more power. In idle mode, the disk can still spin at its regular speed and accesses can be performed without delay. In low-power mode, relatively high transition overhead will be involved, such as turning the spindle motor off (standby) and turning the disk interface off (sleep) [28, 90]. Multi-speed disk [22] can also be employed to manage power consumption of disk subsystems.

Power dissipated by a memory subsystem largely depends on its capacity and bus frequency. In practice, the power consumed by periodic refresh is very small. Most of the power is consumed by row and column decoders, sense amplifiers, and external bus drivers due to large arrays with very long and high capacitance internal bus lines. To reduce power consumption, one or more of these subcomponents can be disabled by switching a device to one of several pre-defined low-power states when it is not being actively accessed. Memory controllers and chipsets can switch the subcomponents to low-power states [62] or switch a memory rank's power on and off [86]. The non-negligible performance penalty, called re-synchronization cost, is incurred to transition from current low-power state to an active state before access. In addition, multi-frequency memory can dynamically scale the working frequency and consequently the data rate [58].

At system-level, the entire computer can be managed as active, sleep (suspended, hibernated), and power-off states with time and energy overhead for the transitions between these states [55].

In virtualized environments, although P-states are still useful to regulate power consumption when they are enabled, problems might occur when manipulating Pstates. Since multiple virtual machines may share a single core, tuning P-states of a core could threaten desired performance isolation. T-states can further throttle down a CPU by inserting stop clock signals and thus omitting duty cycles. However, T-states are not always well documented; access to the T-states may need to modify the clock modulation register. In contrast, C-states can be utilized when the CPU is idle. But it incurs relatively large switch overhead and might not be effective when the system is low utilized. Instead, in virtualized environments, re-allocating CPU resources, by limiting processing time, to virtual machines can both regulate power consumption and meanwhile retain performance isolation brought by virtualization. This functionality is provided by a hypervisor scheduler, such as Credit Scheduler [2] in Xen [13]. One more important power management mechanism introduced by virtualization is virtual machine migration. Virtual machine migration lead to power consumption migration. Consolidation enabled by migration can idle servers so that the idle servers can enter low-power states for more power saving.

## 2.2.3 Power Management Scope

A lot of existing work focused on how to reduce power consumption by improving the energy-efficiency of individual server components [69], from processors [54], memory [39, 86], to disk [126].

At system-level, Lu et al. [76] presented a power reduction technique at OS-level using task-based power management. Zeng et al. [120] proposed to build an explicitly energy-aware operating system by introducing a system-wide abstraction for the energy used. Both work budget the energy available to individual processes. Felter et al. [41] studied power shifting, a technique to reduce peak power with minimal performance impact that is based on dynamically re-allocating power to the most performance critical components. Carrera et al. [22] focused on the disk subsystems,

proposed four disk energy management techniques which includes combining laptop and server-class disks and the use of multi-speed disks.

Previous work [19] shows that the power consumption of processors is usually the dominant factor of power in servers. This is particular true in dense blade server environments. Thus, a large number of research work on system-level power management manipulate system power by DVFS or processor throttling. Elnozahy et al. [37] presented a soft real-time feedback control-based DVFS policy combined with request batching. Sharma et al. [99] investigated adaptive algorithms for DVFS in QoS-enabled web servers to minimize energy consumption subject to service delay constraints. The control is done at session-level by using synthetic utilization bounds as control set point for DVFS. The authors also address the impact on energy and performace due to turning on/off a server in addition to DVFS. In [81], a feedback controller is developed to manage the average power consumption of a laptop to prolong battery lifetime by DVFS. This study relies on experiments to find the best control parameters regardless of current system usage which can affect power consumption. Lefurgy et al. [70] presented a technique to control the peak power consumption of a server using a feedback controller using processor throttling and precise, systemlevel power measurement. This controller is based on the nominal model without awareness of system behavior, which may lead to a longer settling time in a dynamic system.

At the cluster or datacenter-level, the goals of power management can be categorized into two classes: improving energy-efficiency and power capping. These two categories of work will be discussed later.

### 2.2.4 Power Management Objectives

In general, there are two types of objectives in power management. One focuses on average power optimization by minimizing the power needed to achieve the performance target. This can be translated to a tracking problem which means the consumed power should track the resource demands of the applications. This optimization problem can be translated as improving energy efficiency. Power management for improving energy efficiency can be conducted for different objectives: minimizing energy consumption with performance guarantee, maximizing performance under power budget, and making tradeoff between power and performance. The other category emphasizes on peak power in order to optimize the power provisioning delivery and cooling in data centers. This is essentially a capping problem that ensures the power consumption of a system will not violate a power budget.

#### **Energy Minimization with Performance Guarantee**

To improve energy efficiency of a data center, a popular design methodology is to minimize the energy consumption for processing applications. From data center administrators' perspective, a primary concern is application performance, which can be represented as Quality of Service (QoS), Service-Level Agreement (SLA), etc. It is required to meet performance target and meanwhile minimize energy consumption.

Early power management study focused on power-on/off scheme. Pinheiro et al. [89] proposed a load concentration strategy to manage cluster-wide power consumption, in which the nodes in a cluster are turned on or off to ensure the expected performance is just about acceptable according to the workload.

Recently, DVFS became widely employed because it could provide significant energy saving while avoiding the comparatively large switching overhead between power-

on and power-off states. Sharma et al. [99] investigated adaptive algorithms for DVS in QoS-enabled web servers to minimize energy consumption subject to service delay constraints which can be represented by different deadlines for different client classes. Further, for multi-tier server clusters, for example, a 3-tier web server Horvath et al. [56] presented a coordinated DVFS strategy.

Horvath et al. extended the work [56] to combine both DVFS and power-on/off mechanism in a cluster with dynamic configuration [57]. They made performance and power tradeoff decisions using end-to-end delay as a simple SLA metric and took into account the overheads for each transition between multiple sleep modes and standby power levels.

It is observed that the portion of power due to processors is small in comparison with total system power in some recent clusters. There are still a number of work using power-on/off mechanism only due to the non-trivial power consumption for active idle servers. Chen et al. [24] proposed a dynamic provisioning technique to turn on a minimum number of servers required to satisfy application-specific SLA with consideration of time taken for turning on/off a server and load dispatching algorithms.

In virtualization environments, the resource allocation, such as CPU, memory and disk I/O, to each virtual machine should be taken into account as well in order to achieve performance guarantee. Wang et al. [113] proposed a two-layer control architecture to provide response time guarantees for virtualized enterprise servers. The primary control loop uses a multi-input-multi-output (MIMO) control over CPU resources to balance load among virtual machines so that they can achieve roughly the same normalized response time. The secondary loop controls the normalized response time of all virtual machines to a desired level by DVFS for power efficiency.

There are a few work studying statistical QoS guarantee for power management

schemes [118, 56, 71]. Both [56, 71] consider multi-tier web servers enabling DVFS. However, in [56], the statistical performance guarantee is achieved by a queueing model which requires a priori knowledge of workload arrival rate and service rate. In [71], stochastic approximation is coupled with PID feedback controller to guarantee delay quantile of an unknown distribution. In [118], the statistic correlation between resource allocation and QoS was studied but this work was limited to the a priori workload knowledge and simulation.

In addition to control-theoretic approach, there are few work in an attempt to solve this problem using direct methods, such as reinforcement learning. For example, Tan et al. [102] proposed an approach to learn the power management policy to minimize power consumption for a given performance constraint by RL in a model-free manner. We still believe the indirect methods should be more efficient for this kind of problems.

#### Performance Maximization under Power Budget

In addition to reducing energy consumption, another energy-efficient design obejective is to control power consumption to adapt to a given power budget so as to reduce the power (then the performance) of the components when actual power consumption of the server or cluster exceeds the budget [70]. As a result of controlling power consumption, the performance should be maximized without using power more than the budget.

For example, given a budget of power, Gandhi et al. [45] studied the problem of how to allocate power among a server farm so that the performance can be optimized. A queueing theoretic model is developed to predict the optimal power allocation in a variety of scenarios. The optimal power allocation scheme depends on many factors, such as power-to-frequency relationship, the arrival rate of jobs, etc.

Most of the work of performance maximization under power budget have overlap

with the solutions to power capping, which will be discussed later.

#### Tradeoff between Power and Performance

In data centers, it is required to enable resource provisioning in accordance with flexible SLAs that specify dynamic tradeoff between performance and cost that can be translated as power consumption. Indirect methods are mostly employed towards this purpose.

The work [23] by Chase *et al.* is one of the earliest focusing on energy-conscious cluster-wide resource management. It is based on an economic model in which the amount of resource is a function of service quality.

Chen et al. [27] used SLA to direct tradeoff between energy and performance as well. Unlike [23], they considered power-on/off as well as DVFS. They proposed three online strategies based on steady state queuing analysis, feedback control theory, and a hybrid mechanism of both.

Kephart *et al.* [66] proposed an approach to address tradeoff between power and performance, which designed an agent to deal with each aspect of system behavior, such as power, performance and availability. Such a multi-agent approach employs a utility function defined as a joint of power and performance for tradeoff decision.

Kusic et al. [68] presented an online resource provisioning framework for combined power and performance management with consideration of switching costs incurred when provisioning virtual machines. The authors formulated this management problem as one of sequential optimization under uncertainty and provided a limited lookahead control approach. This work relies on the workload-specific performance models requiring a priori workload knowledge.

On another track, virtual machine migration provides an alternative way to save energy by consolidation which reduces number of hosts. Verma et al. [106, 107, 108]

investigated static/semi-static/dynamic job placement to achieve different goals in power and performance, such as power minimization and performance maximization, enabled by virtual machine migration.

#### Power Capping

There are a few work that proposed control-theoretic approaches for power capping at system-level [70, 48]. Wang and Chen [111] extended the work [70] from single server to multiple servers. A Multi-Input-Multi-Output (MIMO) control algorithm is developed to control multiple servers simultaneously. In each control period, the controller collects the power measurement and CPU utilization of each server, computes a new CPU frequency for each server, and directs the servers to scale CPU frequencies in a coordinated manner.

At cluster-level, Femal et al. [35] noticed the uneven distribution of workload among nodes. Thus they allocated power non-uniformly according to demands. A cluster-level manager collects information of all nodes and allocates power to each node while satisfying total power budget. A node-level manager allocates power to each device at a fine level of granularity.

Further, the long-term data from real-world servers have been studied in [94]. Two trends were summarized: 1) low resource utilization with infrequent and short-lived bursts; 2) the probability of synchronized spikes on all servers at the same time is rather low. Based on these observations, Ranganathan *et al.* [94] proposed a power budgeting approach across an ensemble of servers by leveraging statistical properties of concurrent resource usage.

In virtualized environments, the power capping problem is also addressed. Multilayer control approach is widely used in this scenario. Nathuji *et al.* [82] developed a two-layer feedback controller for power budgeting with QoS management in virtualCPU allocation to meet power budget. The other loop is distributed across virtual machines to bid resource based on shadow price for each virtual machine. In [112], both power budget and performance are guaranteed. The power consumption is constrained in a cluster-level power control loop by scaling CPU frequency. The performance guarantee is achieved by allocating CPU resources among virtual machines in a performance control loop.

### 2.2.5 Power Management Methodologies

Power management methodologies can be categorized into two classes: indirect methods and direct methods.

#### **Indirect Methods**

An indirect method assumes an explicit model to capture the behaviors of a target system. This method is model-based. It mostly relies on a system identification procedure to build analytical models of the controlled system and determine the control rule from the model. Such models can abstract the power consumption and performance as analytic functions on a set of system and application parameters. These model can even be used for prediction. Base on the models, both optimization and control approaches can be applied for power management. The most widely-used indirect method is the control-theoretic approach. Control theory provides a powerful mechanism to handle disturbances, uncertainties, and unpredictable changes in systems using feedback [127].

Lu et al. [77] described a formal feedback control algorithm combined with DVFS for multimedia systems. Zhu and Muller [128] combined feedback control theory with

DVFS schemes for hard real-time systems with dynamic workloads. Both work are on the processor level without considering system-level power consumption.

Sharma et al. [99] applied control theory to control application-level quality of service requirements. Chen et al. [27] developed a controller to control SLA, which is response time, in a server cluster. Both of these work provide no guarantee to the power consumption of a computing system.

Single-input-single-output (SISO) controller is mostly used when there is only a single control output employing control over a single resource. Lefurgy et al. [70] designed a Proportional (P) controller to cap the peak power of a server by throttling processor. Wu et al. [116] managed power by controlling the synchronizing queues in multi-clock-domain processors. Zhang et al. [122] adjusted the resource demands of virtual machines based on resource availability.

Multi-input-multi-output (MIMO) control can be employed when there are multiple control outputs in power management for enterprise servers, which might need control over multiple resources. The MIMO control can be translated to an optimization problem. Extending the power capping technique in [70] from a single server to a cluster, Wang et al. [111] developed a MIMO control algorithm for cluster-level power control in a non-virtualized environment. Kusic et al. [68] presented a power and performance management strategy using lookahead control. In addition, Kephart et al. [66] have proposed a coordinated management scheme to achieve tradeoffs between power and performance by optimizing a utility function for a non-virtualized server.

Multilayer control can be applied to address similar problems. Representative work includes [113, 82, 112], which employ two-layer feedback controller. In [113], one loop controls the CPU resource to each virtual machine to guarantee performance while the other one controls CPU frequency for power efficiency. In [82], one loop lim-

its the power consumption and the other one bids resource based on shadow price for each virtual machine. However, the work in [113, 82] are either performance-oriented or power-oriented without explicit coordination of power and performance. In [112], power and performance can be coordinated using a two-layer feedback controller depending on off-line system identification.

Model Predictive Control (MPC) is quite useful when the control action has dead times, such as performance impact of an application due to resource re-allocation. Xu et al. [117] presented an end-to-end QoS provisioning framework to monitor and control user-perceived QoS. Both work rely on queueing model. To manage power consumption of enterprise servers, Wang et al. [113] designed a MIMO power control algorithm based on MPC control theory. Kusic et al. [68] used Limited Lookahead Control (LLC) to formulate models for the cost of control.

Adaptive control copes with the dynamic of a system by modifying the control law. To meet the performance SLA, a self-tuning admission controller was designed for a 3-tier web sites in [64]. In [115], a self-tuning fuzzy controller was proposed to guarantee client-perceived end-to-end QoS. To manage resource in virtualized environments, Padala et al. [85] proposed an adaptive estimator to capture the relationship between allocated system resource and performance. In [63], the Kalman filter was integrated into feedback controllers to dynamically allocate CPU resources to virtual machines.

There are also a number of challenges when applying control theory to power management. Modeling is difficult because most inter-relationships in the system are non-linear. Modeling itself requires system identification which may not cover all relevant correlations. Classical control theory only deals with continuous inputs while the input variables for power management can only take on discrete values. Though adaptive control can deal with dynamic, a limitation still exists on how fast the workloads or system behaviors can change. In addition, using dynamic models

may not provide theoretic guarantee on the properties of controllers.

#### **Direct Methods**

In contrast, direct methods determine control rules without needs for an explicit model of a system. One representative example is reinforcement learning (RL), which learns the impact on system behaviors, such as performance and power consumption, due to the action taken on the system, such as power state change. Compared with control theory, reinforcement learning is model-free. RL is fundamentally a sequential decision theory that properly treats dynamics in the system. It can improve decision-making policy over time, similar to adaptive control [101].

Rao et al. [95] proposed a reinforcement learning based approach for virtual machine configuration which is adaptive to heterogeneous virtual machines. Tesauro et al. [103] presented a reinforcement learning approach to developing effective control policies for real-time power management in application servers. Tan et al. [102] proposed a online power management technique using reinforcement learning. The best power management policy can be learned without knowing the workload information a priori.

However, there are also a few challenges in reinforcement learning. One is the tradeoff between exploitation, which is to select from what it already knows, and exploration, which is to make better action selection from unknowns in the future. Performance of the initialization phase that explores without any knowledge during live online training may be unacceptably poor. The convergence is hard to prove and the convergence rate is low. In addition, RL can suffer from poor scalability in large state spaces.

# Chapter 3

# Maximizing Rewards in Wireless Networks with Energy and Timing Constraints

Energy is a critical resource of wireless devices powered by battery with limited capacity. Reliable content delivery over a wireless channel is a major source of energy expenditure. The increasing wireless transmission rate results in an exponential increase of the energy consumption of wireless devices [16]. However, applications are usually delay-sensitive. With renewable energy resources, such as solar power, wind power, and mechanical power from the environments, wireless nodes are subjected to limited amount of energy collected in each period. Meanwhile, wireless nodes powered by renewable battery often generate a significant amount of data during each cycle. Due to the limitation of energy and delay, it is often impossible to deliver all the data generated during each period. Instead, the data with higher level of importance should have high priority to deliver. A reward is associated to each packet to qualify the level of importance. In this chapter, we will present our solutions to reward

Figure 3.1: One-transmitter-multiple-receiver model in a single-hop wireless network. maximization problem in a single-transmitter-multiple-receiver wireless networks with energy and delay constraints.

## 3.1 System Model and Problem Formulation

In this part, we first define data and energy consumption models for the reward maximization problem. Then we present a formulation of the reward maximization problem under given time and energy constraints.

#### 3.1.1 Data Model

Early studies of energy-efficient problem in wireless networks were largely targeted at communication channels over a single-transmitter-single-receiver model; see [29] [16] [104] [43] for examples. A single-transmitter-single-receiver model is also known as point-to-point communication where there is only one transmitter which will communicate with a single receiver. In recent years, we have seen the extension of the studies to a more general single-transmitter-multiple-receiver model [44] [121] [84] [125] in which a wireless transmitter communicates with multiple receivers periodically, as shown in Fig. 3.1. In this model, the transmitter can only communicate with

one receiver at a time and has an energy budget in each transmit cycle. Each receiver will receive data from the transmitter periodically. Every transmitter-receiver pair has a maximal amount of data to be transmitted in each time period. The receivers are located with distances from the transmitter. The data to different receivers can be transmitted at different transmission rates.

We regard the transmission between each transmitter-receiver pair as a periodic data stream and refer this as a task. It is a sequence of packet transmissions with the same characteristics that occurs at a regular interval. We use  $Task = \{\tau_1, \tau_2, \dots, \tau_N\}$  to denote the set of N tasks. The number of tasks is always equal to the number of receivers in our model. All the transmission tasks are assumed to be independent and preemptive, scheduled by the Earliest Deadline First (EDF) policy [74].

EDF is a popular scheduling policy for delay sensitive wireless packet scheduling [42][119]. We choose EDF as the underlying policy because it has been shown to be optimal for deadline constrained scheduling over optimal link conditions under various modeling assumptions [47][75]. The preemption can take place between transmissions of packets of different tasks. Practically, it can be implemented in a transmitter by re-arranging packets in the transmission buffer by choosing those with the earliest deadlines. Similar preemptive model was assumed in [42][47][100].

We characterize a task  $\tau_i$  by a tuple  $\{C_i, T_i, D_i, P_i, R_i\}$ , where  $C_i$  denotes the size of data to be transmitted,  $T_i$  is the task period,  $P_i$  and  $R_i$  are power function and reward function respectively. The relative deadline  $D_i$  is assumed to be equal to task period  $T_i$ . We assume for each data stream i, there are several discrete levels of sizes of data to be transmitted, denoted by  $\{c_i^1, c_i^2, \ldots, c_i^K\}$ . We have  $C_i \in \{c_i^1, c_i^2, \ldots, c_i^K\}$ , which means the actual amount of data to be transmitted is not always the maximum and should be determined due to time and energy constraints. In general, the data stored in the transmit buffer can be either generated by local host or forwarded from

other nodes. Different data may have different priorities and rewards related to the corresponding receiver and data size. For notional brevity, we use  $\tau_i^j$  to represent the task when data  $c_i^j$  is selected for transmission.

The transmitter has a set of discrete levels of transmission rates. We define the set of available transmission rates of a transmitter as  $Speed = \{s_1, s_2, \ldots, s_M\}$  in which the available rates are indexed in an ascending order.

#### 3.1.2 Power Consumption Model

The power consumption of a wireless transmitter can be divided into two parts: circuit power and transmission power. The transmission power usually dominates since long-range communications (over 100m) are common in wireless networks. In order to maintain the same transmission rate, the required transmission power needs to increase with the distance between the transmitter-receiver pair to offset the propagation loss. In addition, the circuit power is expected to decrease as the IC technology advances. This part of power only occupies a small portion of the whole power consumption. So in our work, we assume the transmission power dominates the negligible circuit power.

In our power model, we assume the channel is slowly time-varying, which means the channel condition will not change during transmission. Proper channel coding can reduce the energy consumption effectively during transmission. We take the Additive White Gaussian Noise (AWGN) channel model as an example, which explains how energy, rate, and data size are related. With optimal channel coding, the maximum transmission rate is [32]:

$$S = \frac{B}{2}\log_2(1 + \frac{P'}{N_0 B}),\tag{3.1}$$

where S is the transmission rate, P' is the received signal power,  $N_0$  is the spectral density, and B is the channel bandwidth. From this equation, we can describe the relationship between the transmission rate S and the received power P' by the following equation:

$$P' = N_0 B \cdot (2^{\frac{2S}{B}} - 1). \tag{3.2}$$

As we aforementioned, the power will increase with distance between transmitter and receiver in order to maintain the same transmission rate. Considering this power attenuation, we have:

$$P = \frac{P'}{A} = \frac{N_0 B}{A} \cdot (2^{\frac{2S}{B}} - 1), \tag{3.3}$$

where P is the transmission power and A is the attenuation factor for the transmitterreceiver pair. The attenuation factor A is generally inversely proportionally to a function of the distance, denoted by l. For example, this function could be a square function,  $A \propto 1/l^2$ , in [32]. In this work, we do not assume any specific form of the relationship between attenuation factor and distance except that all transmitterreceiver pairs have the same fading functions which are only affected by distance. It is easy to see that the required transmission power P is strictly increasing and strictly convex in the transmission rate S. This power function P(S) is continuous in S though we only consider the discrete cases for this function in this work.

Let  $P_i$  denote the power consumption function for task  $\tau_i$ . Let  $C_i$  and  $S_i$  represent the size and rate of data transmission for  $\tau_i$ , respectively. The transmission time to transmit data  $C_i$  equals to  $\frac{C_i}{S_i}$ . Therefore it consumes  $P_i(S_i)\frac{C_i}{S_i}$  units of energy. The energy consumed for  $\tau_i$  for transmission in one period, denoted by  $E_i$ , with data size  $C_i$  at transmission rate  $S_i$  becomes

$$E_i(C_i, S_i) = P_i(S_i) \frac{C_i}{S_i} = \frac{N_0 B}{A_i} \cdot (2^{\frac{2S_i}{B}} - 1) \cdot \frac{C_i}{S_i}, \tag{3.4}$$

where the coefficient  $A_i$  for each transmitter/receiver pair differs depending on the distance between them. Similar power models were defined in [121] [125], as well. As the channel states and receiving nodes are assumed to be static during the transmission period, the power attenuator factor  $A_i$  is also static. We fix the bandwidth B and assume it is the same for all the streams. To simplify the problem, we assume the overhead of switch among different transmission rates is tiny and can be ignored.

#### 3.1.3 Problem Formulation

We consider the transmission in a hyper-period T which is defined as the Least Common Multiple (LCM) of task periods  $T_1, T_2, ..., T_N$ . The consideration of a hyper-period ensures all tasks can finish their periodic transmissions at least once. Let  $E_{max}$  represent the units of energy budget allocated to the transmitter during this hyper-period T. Our objective is to maximize the total reward while all tasks meet their deadlines and the total energy consumption does not exceed the budget  $E_{max}$ . In other words, the optimization problem in this work is to find a speed and a data size for each task to maximize the overall rewards while satisfying delay and energy constraints.

The reward  $R_i$  can be a function of multiple variables such as data size, transmission rate, etc. In this work, we define reward function  $R_i$  as a generic function of data size  $c_i^j$  to be transmitted, represented by  $R_i(c_i^j)$ . It is conceptually the same as the reward functions in [11][33] and the utility function in [92]. In this work, however, we do not assume any specific form of the reward function. It can be reduced to different forms in different application contexts. In its simplest form, the reward function  $R_i$  can be interpreted as the amount of data transmitted, with respect to the data size; the reward maximization problem is then reduced to throughput maximization, as in [43] [121]. In an image sensing application, it could be interpreted as the amount of information transmitted using different image formats [73]. In a file transferring application, it can be reduced to the probability of successful file delivery [110].

In general, we formulate the reward maximization problem as

$$\text{maximize } \sum_{i=1}^{N} \frac{T}{T_i} R_i(C_i) \tag{3.5}$$

subject to

$$\sum_{i=1}^{N} \frac{T}{T_i} \cdot \frac{C_i}{S_i} \le T$$

(3.6)

$$\sum_{i=1}^{N} \frac{T}{T_i} E_i(S_i, C_i) \le E_{max} \tag{3.7}$$

$$S_i \in \{s_1, s_2, \dots, s_M\}, 1 \le i \le N$$

(3.8)

$$C_i \in \{c_i^1, c_i^2, \dots, c_i^K\}, 1 \le i \le N.$$

(3.9)

Constraint (3.6) guarantees that all the data streams can be completed under the EDF scheduling [74]. Whenever there is a schedule that maximizes the reward and can guarantee all streams transmitted under constraints, we can always convert that

schedule to EDF scheduling with the same reward, according to the proof of EDF optimality in [75]. When all the packets in a hyper period are ready for transmission at time 0, (3.6) reduces to a discrete case as in [121]. If we enable continuous data size and transmission rate in (3.8) and (3.9), respectively, this problem is reduced to a continuous case, similar to that in [121]. In constraint (3.9), we enable multiple choices of data sizes; the problem is reduced to the one in [97] when we fix available data size of each task i in constraint (3.9) to be  $\{c_i^1, c_i^2\}$ , with  $c_i^1 = 0$  and  $c_i^2 \neq 0$ , for all  $1 \leq i \leq N$ . Theorem 1 shows the reward-maximization problem for periodical tasks defined by (3.5)-(3.9) is NP-hard.

**Theorem 1.** The reward-maximization problem for periodical tasks defined by (3.5)-(3.9) is NP-hard.

Proof. Let  $x_{ij}$  and  $x_{il}$  denote two 0-1 decision variables, respectively. Let  $\Omega_i = \{s_1, s_2, \ldots, s_M\}$  and  $\Lambda_i = \{c_i^1, c_i^2, \ldots, c_i^K\}$  for all  $1 \le i \le N$ . If a task i is assigned to transmit data at rate  $j \in \Omega_i$ , then  $x_{ij} = 1$ ; otherwise,  $x_{ij} = 0$ . If a task i is assigned to transmit data with data size  $l \in \Lambda_i$ , then  $x_{il} = 1$ ; otherwise,  $x_{il} = 0$ . The optimal problem ((3.5)-(3.9)) can be rewritten as:

maximize

$$\sum_{i=1}^{N} \sum_{l \in \Lambda_i} \frac{T}{T_i} R_i(C_{il}) x_{il}$$

(3.10)

subject to

$$\sum_{i=1}^{N} \sum_{j \in \Omega_i} \sum_{l \in \Lambda_i} \frac{T}{T_i} \cdot \frac{C_{il}}{S_{ij}} x_{ij} x_{il} \le T$$

(3.11)

$$\sum_{i=1}^{N} \sum_{j \in \Omega_i} \sum_{l \in \Lambda_i} \frac{T}{T_i} E_i(S_{ij}, C_{il}) x_{ij} x_{il} \le E_{max}$$

(3.12)

$$\sum_{j \in \Omega_i} x_{ij} = 1, 1 \le i \le N \tag{3.13}$$

$$\sum_{l \in \Omega_i} x_{il} = 1, 1 \le i \le N. \tag{3.14}$$

By viewing  $\frac{T}{T_i}R_i(C_{il})$  as the profit of item l out of class i, terms  $\frac{T}{T_i} \cdot \frac{C_{il}}{S_{ij}}$  and  $\frac{T}{T_i}E_i(S_{ij},C_{il})$  as the corresponding weights, the optimal problem formulation ((3.10)-(3.14)) becomes to an instance of well-known NP-hard Multidimensional Multiple-Choice Knapsack Problem (MMKP) [65].

# 3.2 Branch-and-Prune for the Optimal Solutions