Wayne State University

Wayne State University Theses

4-9-2002

# Implementation of Viterbi decoder on Xilinx XC4005XL FPGA

Nabil Abu-Khader Wayne State University

Follow this and additional works at: http://digitalcommons.wayne.edu/oa\_theses Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Abu-Khader, Nabil, "Implementation of Viterbi decoder on Xilinx XC4005XL FPGA" (2002). *Wayne State University Theses*. 540. http://digitalcommons.wayne.edu/oa\_theses/540

This Open Access Thesis is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Theses by an authorized administrator of DigitalCommons@WayneState.

### IMPLEMENTATION OF VITERBI DECODER ON XILINX XC4005XL FPGA

by

### NABIL ABU-KHADER

#### THESIS

Submitted to the Graduate School

of Wayne State University,

Detroit, Michigan

In partial fulfillment of the requirements

for the degree of

MASTER OF SCIENCE

2002

MAJOR: ELECTRICAL ENGINEERING

Approved by:

4/29/02 Advisor Date 1/

#### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my supervisor, Dr. Pepe Siy for his encouragements and guidance during my graduate studies. His trust in my capabilities allowed me to pursue the research of my choice. I thank him for encouraging me to dwell into the dual topic of Viterbi Decoding and FPGA's.

I would also like to thank Wayne State University for providing all the necessary support in completing this work. Last but not the least I would like to acknowledge the constant encouragement and support by my mother throughout the course of my master's studies.

| TABLE OF CONTENTS                                |                                           |                                   |

|--------------------------------------------------|-------------------------------------------|-----------------------------------|

|                                                  | . ~ .                                     |                                   |

| ACKNOWLEDGMENTS                                  | •••••••••••••••••••••••••••••••••••••••   |                                   |

| LIST OF TABLES                                   |                                           | ÎV                                |

| LIST OF FIGURES                                  |                                           | vi                                |

| CHAPTERS                                         | х - 139<br><sub>1</sub> 7а х              | $\frac{p_{0,0}}{p} = \frac{1}{2}$ |

| CHAPTER 1 – Introduction                         |                                           | 1                                 |

| 1.1 Motivation                                   |                                           | 1                                 |

| 2.2 Approach to the solution                     |                                           | 2                                 |

| CHAPTER 2 – Preliminaries                        |                                           | 4                                 |

| 2.1 A Model of Digital Communication System      |                                           | 4                                 |

| 2.2 Convolutional Codes                          |                                           | 5                                 |

| 2.3 Mapping the Channel Symbols to Signal Levels | 그는 것 같은 것 같 | 10                                |

| CHAPTER 3 – Viterbi Algorithm                    |                                           | 11                                |

| 3.1 How Viterbi Decoder Works?                   |                                           | 11                                |

| 3.2 Viterbi Decoder Features                     |                                           | 16                                |

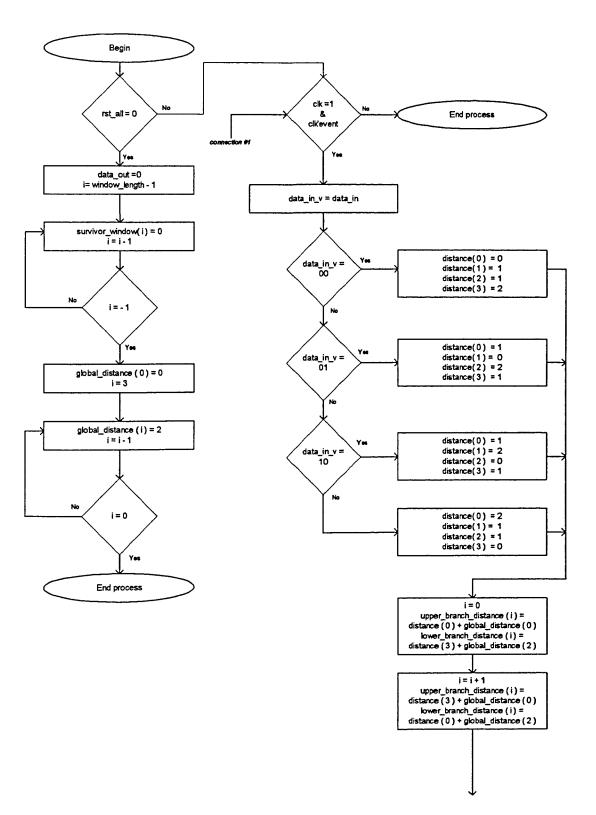

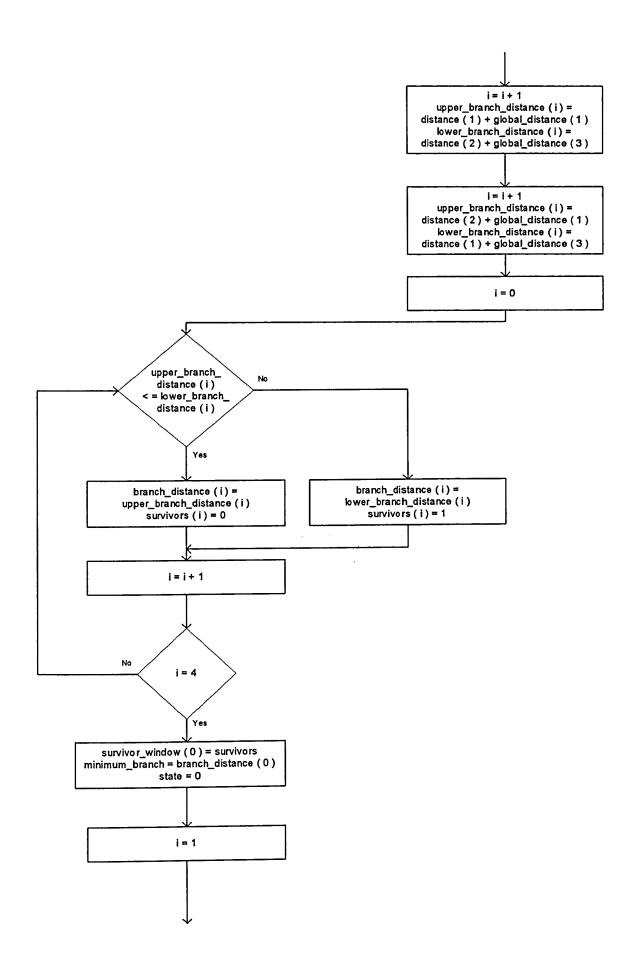

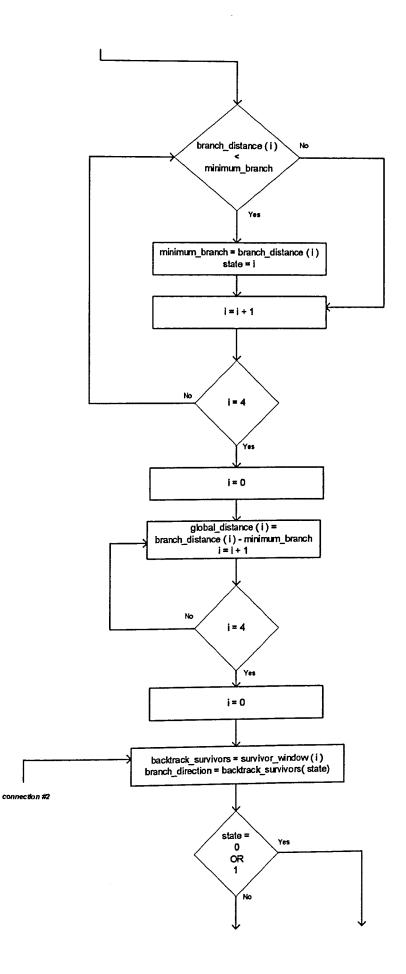

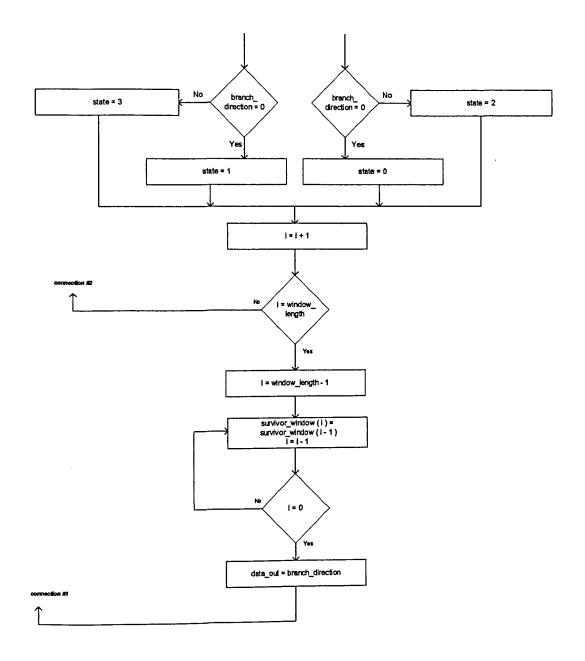

| 3.3 Design Flow Chart                            |                                           | 17                                |

| 3.4 The VHDL Code                                | CARO A JA                                 | 21                                |

| 3.5 An Example                                   |                                           | 24                                |

| CHAPTER 4 – Field Programmable Gate Arrays (FPGA | As)                                       | 31                                |

| 4.1 What is an FPGA?                             |                                           |                                   |

| 4.2 What does a logic cell do?                   |                                           | 31                                |

| 4.3 What does 'Field Programmable' mean?         |                                           | 32                                |

|                                                  |                                           |                                   |

| 4.4 Xilinx XC4000 Family Logic Block                 |    |

|------------------------------------------------------|----|

| 4.5 More About XC4005XL Board                        |    |

| 4.6 How To Program The PFGA Board?                   |    |

| CHAPTER 5 – Experimental Results                     | 35 |

| 5.1 What Did We Do?                                  | 35 |

| 5.2 Using OrCAD Capture To Implement Viterbi Decoder | 35 |

| CHAPTER 6 – Conclusion And Future Work               | 53 |

| Bibliography                                         | 55 |

| Abstract                                             | 57 |

| Autobiographical Statement                           | 59 |

### LIST OF TABLES

| TABLE                                       | PAGE |

|---------------------------------------------|------|

| Table 2.1 A random bit stream of data       | 8    |

| Table 5.1 The applied random stream of data | 39   |

| Table 5.2 Our final optimum results         | 44   |

### LIST OF FIGURES

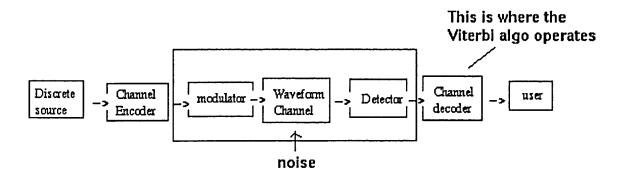

| Figure 1 : A model of digital communication system                                        | 4   |

|-------------------------------------------------------------------------------------------|-----|

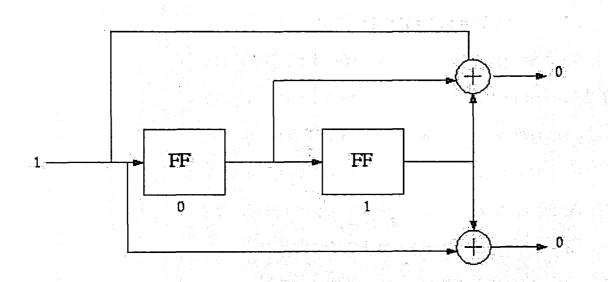

| Figure 2 : An example of a 1/2 rate convolutional encoder with K=3 (4 states)             | 7   |

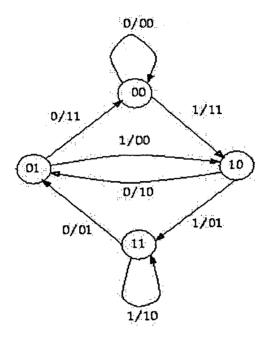

| Figure 3 : The state transition diagram for the $K = 3$ , $r = 1/2$ convolutional encoder | 8   |

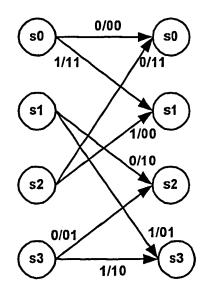

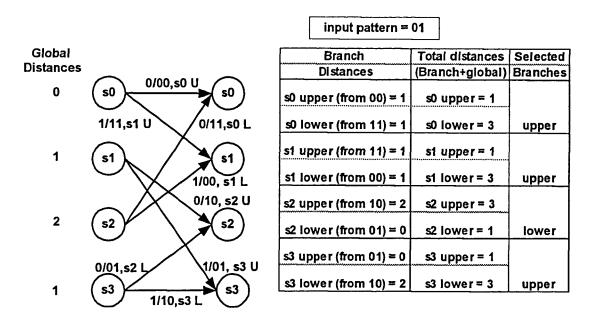

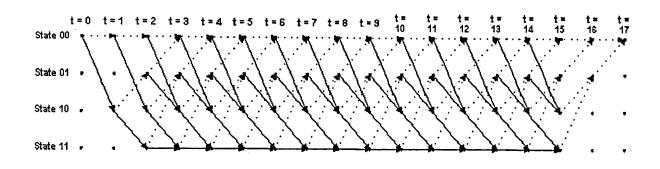

| Figure 4a : A window of the trellis diagram showing a sample of data stream               | 9   |

| Figure 4b : Trellis diagram showing a sample of data stream                               | 10  |

| Figure 5 : Possible transitions into state S0                                             | 12  |

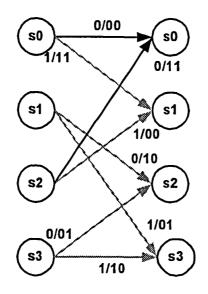

| Figure 6 : Branch selection based on global and branch distances                          | 13  |

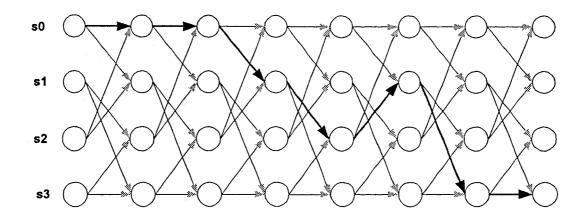

| Figure 7 : Backtracking through the survivor window                                       | 15  |

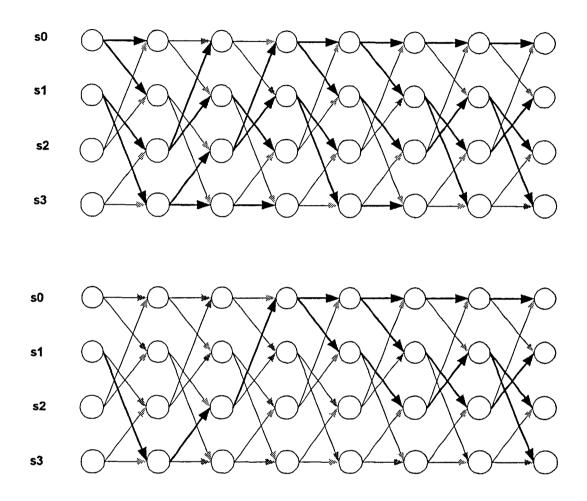

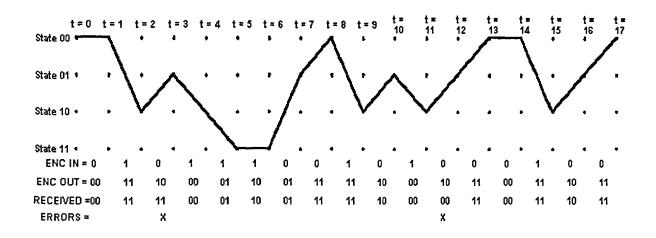

| Figure 8 : A trellis diagram                                                              | 25  |

| Figure 9 : Encoded message with a couple of bit errors                                    | 25  |

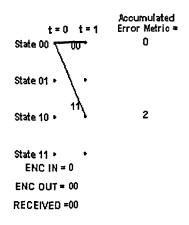

| Figure 10 : The trellis diagram between t = 0 and t = 1                                   | 26  |

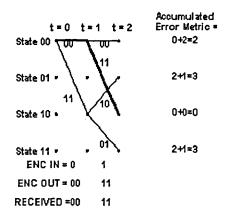

| Figure 11 : The trellis diagram between t = 0 and t = 2                                   | 27  |

| Figure 12 : The trellis diagram between t = 0 and t = 3                                   | 28  |

| Figure 13 : The trellis diagram between t = 0 and t = 4                                   | 28  |

| Figure 14 : The trellis diagram between t = 0 and t = 5                                   | 29  |

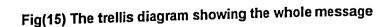

| Figure 15 : The trellis diagram showing the whole message                                 | 29  |

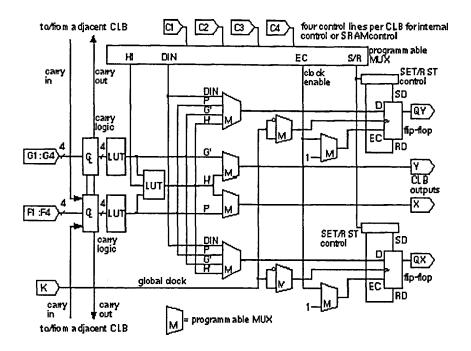

| Figure 16 : The Xilinx XC4000 family CLB                                                  | 33  |

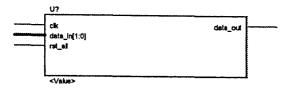

| Figure 17 : Our Virerbi decoder symbol                                                    | 38  |

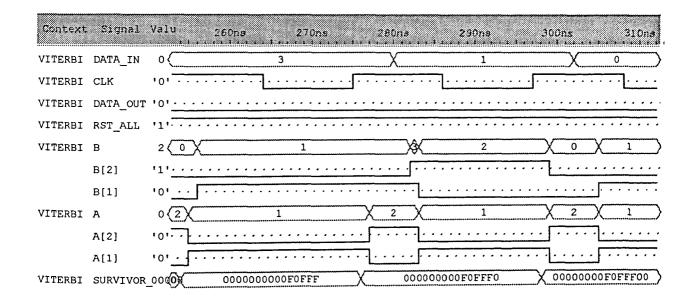

| Figure 18 : The simulation result after applying the random stream of data                | 39  |

| Figure 19 : Data moves in the survivor window                                             | 40  |

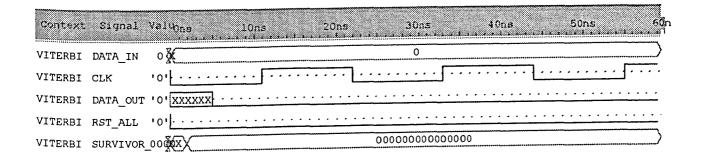

| Figure 20 : The delay for the whole system                                                | .40 |

| Figure 21 : A noise inserted at time 192ns                 | 41 |

|------------------------------------------------------------|----|

| Figure 22 : Showing the previous change                    | 41 |

| Figure 23 : Inserting more noise                           | 42 |

| Figure 24 : Inserting more noise                           | 42 |

| Figure 25 : Observing a change at the output               | 43 |

| Figure 26 : Showing the change that happened at the output | 43 |

| Figure 27 : IC-station LVS check result                    | 52 |

## CHAPTER 1 INTRODUCTION

#### 1.1 Motivation:

The use of error-correcting codes has proven to be an effective way to overcome data corruption in digital communication channels. The Viterbi decoding algorithm is used to decode convolutional codes and is found in many systems that receive digital data that might contain errors. Viterbi decoding, also known as maximum-likelihood decoding, is comprised of the two main tasks of updating the trellis and trace-back. The trellis used in Viterbi decoding is essentially the convolutional encoder state transition diagram with an extra time dimension. The Viterbi Algorithm (VA) was first described in 1967 by Andrew J. Viterbi as a method for efficiently decoding convolution codes. In most modern communication systems, channel coding is used to increase bandwidth, add error detection and correction capabilities, and provide a systematic way to translate logical bits of information to analog channel symbols used in transmission. Convolutional coding and block coding are the two major forms of channel coding used today. As their names imply, in convolutional coding the algorithms work on a few bits at a time while in block coding big chunks of data are processed together [SWA02]. Generally, convolutional coding is better suited for processing continuous data streams with relatively small latencies. Also, since convolutional forward error correction (FEC) works well with data streams affected by the atmospheric and environmental noise (Additive White Gaussian Noise) encountered in satellite and cable communications, they have found widespread use in many advanced communication systems. Viterbi decoding is one of the most popular FEC techniques used today and is therefore the main focus here.

Viterbi decoding and sequential decoding are the two main types of algorithms used with convolutional codes. Although sequential decoding performs very well with long-constraint based convolutional codes, it has a variable decoding time and is less suited for hardware implementations. On the other hand, the Viterbi decoding algorithm has fixed decoding times and is well suited for hardware implementations.

On the trellis of a convolutional code, the VA finds the shortest path that leads to a particular state. Metrics are associated with each branch and they can be calculated as the Hamming distance of the corresponding code word over the received word for hard decoding or as the Euclidean distance (using a quantizer) in the case of soft decoding. Many paths can lead to the same state. The VA selects the path whose summation of all metrics is the lowest. This refers to the add-compare-select (ACS) operation [GAR00].

At the receiver, the stream of data (which may now contain errors) is passed through a Viterbi decoder, which attempts to extract the most likely sequence of the transmitted data.

Projects and researches previously done did not follow the new IEEE 802.16 specifications, but here, we followed the specifications as can be seen in chapter (5).

#### **1.2Approach to the solution:**

Viterbi decoders are generally implemented using programmable digital signal processors (DSPs) or special purpose chip sets and application-specific integrated circuits (ASICs) [DU00]. Here, we aim to implement such decoder on an FPGA.

The specific aims are:

- Understand the principles of convolutional coding and Viterbi decoders.

Design and code parameterisable, behavioural VHDL models for a Viterbi decoder according to the new IEEE 802.16 specifications.

Test the VHDL code then Synthesise the decoder onto an FPGA.

Programmable Logic is ideal for implementing error control coding (ECC) functions for two main reasons. First, PLDs are flexible, easing the modification of coding methods and improving algorithms. Second, the performance and density of PLDs align optimally with industry requirements. Unlike Application Specific Standard Products (ASSPs) designed specifically for ECC, programmable logic devices offer the designers the speed of hardware and the flexibility of software while implementing ECC functions.

ECC is a methodology that detects and in some cases corrects errors induced in digital data during transmission over a noisy channel (digital video/audio broadcast, satellite communications) or during storage in an unreliable medium (compact disc, digital tape). Some of the common ECC functions ideally suited for programmable logic are Reed-Solomon, Viterbi, Trellis Coded Modulation (TCM), etc.

FPGAs can speed time to market for the particular design of telecommunication applications because of their quick turnaround time [ALT01].

3

#### **CHAPTER 2**

#### PRELIMINARIES

In the following two sections we describe some basics towards our implementation. The first section describes a model of digital communication system and where the Viterbi algorithm is applied. The second section describes the convolutional encoding process.

#### 2.1 A model of digital communication system:

A model of digital communication system is shown in fig (1) [NETCOM]:

Fig(1) A model of digital communication system

The discrete source generates information in the form of binary symbols. The channel encoder adds redundancy to it according to a prescribed rule before transmission. The channel decoder in the receiver uses this redundancy to decide which message bits were actually transmitted. The combined goal of the encoder and decoder is to minimize the effect of channel noise. There are many different error-correcting codes. They have been classified into "block codes", or "convolutional

codes". In block coding, an encoder generates a n - bit code word with a k - bit message block, so code words are produced on a block-by-block basis. But if we want to process the incoming bits serially rather than in large blocks, we will use convolutional coding.

#### 2.2 Convolutional codes

Convolutional codes are used to add redundancy to a stream of data. The addition of redundancy (extra bits) allows for the detection and possible correction of incorrectly transmitted data.

The input bits are convolved in such a way that each bit influences the output more than once. Each input bit enters a shift register and the output of the encoder is derived by combining the bits in the shift register in a way determined by the structure of the encoder in use. Therefore, every bit transmitted will influence as many of the outputs as there are stages in the shift register. For example if a three bit shift register is used then, each encoded bit will influence three output bits of the encoder. The input bits could be fed in more than once at a time and the encoder could produce more than one output at each step [MEN98].

The output of a convolution encoder is dependent upon the current data and previously transmitted data. A convolutional code is characterized by its rate, constraint length, and its generator polynomials.

The code rate (k/n) of a convolution code is the ratio of the size of the input stream to the size of the output stream. The convolutional code used here has a rate of 1/2, which means that each input bit produces two output bits.

The constraint length (K) indicates the number of previous input data that must be examined along with the current input data to determine the output data, or simply, The number of stages in the shift register. The convolution code used here has a constraint length of 3. We need 2<sup>(K-1)</sup> states. Also, The constraint length K is directly related to the number of registers in the encoder. These shift registers hold the previous data values that are systematically convolved with the incoming data bits. This redundancy of information in the final transmission stream is the key factor enabling the error correction capabilities that are necessary when dealing with transmission errors. Systems with higher constraint lengths are generally more robust. However, the complexity of the Viterbi decoder increases exponentially with the constraint length, so it is unusual to find constraint lengths greater than nine [MEN98].

The generator polynomials describe how past and current input data are used to determine the output data. The generating polynomials denote the convolutional encoder state bits, which are mathematically combined to produce an encoded bit. There is one generating polynomial per encoded bit. The convolution code used here uses the following generator polynomials:

$OUT_{low} = In(t) \oplus In(t-2)$

$OUT_{high} = In(t) \oplus In(t-1) \oplus In(t-2)$

Fig(2) shows an example of a ½ rate convolutional encoder with K=3 (4 states).

Fig(2) An example of a 1/2 rate convolutional encoder with K=3 (4 states)

As shown in the figure inputs enter from the left end and two outputs are generated for every input bit. The incoming bit as well as the bits in the two flipflops together form the "shift register". One output is produced by XORing all the bits of the shift register and the other is XOR output of two of them. Initially we can assume that the flipflops contain zeroes and subsequently they take on values depending on the input bits. The bit values represented by the flipflops is called the "state" of the system. In the example shown, the state of the encoder is "01".

In fig(2) [NETCOM], a particular situation is shown where the incoming bit is a 1 and the two previous bits were 0 and 1. The output of this situation would be 0 at both the outputs. The output bits are transmitted through a communication channel and are decoded by employing the Viterbi decoder at the receiving end.

7

The polynomials described above can be represented as a state machine (state transition diagram). The state transition diagram for the K = 3, r = 1/2 encoder is shown in fig(3).

Fig(3) The state transition diagram for the K = 3, r = 1/2 convolutional encoder

Table 2.1 shows a random bit stream of data along with the output stream and the next state.

| Input Stream  | 0   | 0  | 1  | 0  | 1  | 1  | 1          |

|---------------|-----|----|----|----|----|----|------------|

| Next State    | SO  | S0 | S1 | S2 | S1 | S3 | <b>S</b> 3 |

| Output Stream | 0 0 | 00 | 11 | 10 | 00 | 01 | 10         |

Table 2.1 A random bit stream of data

The values inside the circle of fig(3) represent the current state. The values along the arrow represent the input and output bits of the encoder. For example the top circle indicates State 00. If the next input bit is a 0 then the output of the encoder will be 00 and the next state will again be 00. If the next input was a 1 instead, then the output of the encoder would be 11 and the next state would be 10. Each arrow in the above figure represents a possible transition from one state to another and is called a "branch". The Viterbi decoder will generate a branch metric value for each of the possible branches based on the input actually received by the encoder. This branch metric is the Hamming distance between the received value at the decoder and the output value associated with the branch. A trellis diagram can be used to represent the operation of a state machine over time. In a trellis diagram, the states are listed vertically; time advances from left to right. Fig(4) shows the same input data of table 2.1, represented in a trellis diagram [MEN98]. Note that upper branches are followed when the input is '0'; lower branches are followed when the input is '1'.

Fig(4a) A window of the trellis diagram showing a sample of data stream

Fig(4b) Trellis diagram showing a sample of data stream

### 2.3 Mapping the Channel Symbols to Signal Levels

Mapping the one/zero output of the convolutional encoder onto an antipodal baseband signaling scheme is simply a matter of translating zeroes to +1 and ones to -1. This can be accomplished by performing the operation y = 1 - 2x on each convolutional encoder output symbol [ACT97].

#### CHAPTER 3

#### VITERBI ALGORITHM

#### 3.1 How Viterbi decoder works?

The Viterbi algorithm is based on the fact that there are only a finite number of possible states of the encoder, and that given two consecutive states we can predict the input bit(s) that would have caused that state transition.

The Viterbi decoder comprises of three major parts, namely the branch metric generator (BMG), the add-compare-select unit (ACS) and the survivor memory unit.

The branch metric generator, which is used to calculate the branch metrics for every stage, is a single unit which is repeatedly used by all the stages of the trellis. The add-compare-select unit calculates the path metrics of all the states in a stage and the number of ACS units depends on the constraint length [SWA02]. The survivor memory unit is used to store the path history of all the surviving paths and is finally used to retrieve the original input sequence.

A Viterbi decoder attempts to reconstruct a path through a trellis diagram based on a potentially corrupted stream of data. This is accomplished by selecting the most likely path through the trellis. In the decoding process, legal transitions are considered much more likely than illegal transitions. Not all transitions between states are legal. For example there is no legal transition from state S0 to state S2.

When new input data arrives, a probability value is calculated for every path between two sets of states. The probability is determined by calculating the distance between state, which is the number of bits that would have to be incorrect for the path to be taken. For example, consider the state S0 in fig(5) [MEN98]. There are two possible paths to this state: one from state S0 and one from state S2. These paths are highlighted in fig(5).

Fig(5) Possible transitions into state S0

If the input pattern is "00", the distance for the upper branch is 0, since the pattern associated with this branch is the same as the input pattern. The distance associated with the lower branch is 2, since the pattern associated with the branch differs from the input pattern for both bits. In this manner, distances are calculated for all 8 possible branches.

These distances are added to a set of global distances that are maintained for each state [MEN98]. These values represent the likelihood of being in a particular state at the time the new input data arrives.

The global distances are added to the branch distances in order to select, for each state, the most likely branch that would reach that state. The most likely branch is the branch that has the lowest distance – a larger the distance number indicates that a greater number of errors would have to occur for the path to be the correct one. This process is best illustrated by an example.

For example, given a set of current global distances and an input pattern, fig(6) shows the 8 branch distances, the 8 total distances, and the 4 selected branches [MEN98].

#### Fig(6) Branch selection based on global and branch distances

If the metrics of two paths are the same, then we choose one of them arbitrarily (based on chance).

Once the total distances have been calculated and branches have been selected, the branch selections are stored in a survivor memory.

The survivor memory stores the most likely branches for some number of previous input data. The number of previous branch selections stored in the survivor

memory is typically 4 to 5 times the constraint length. This is usually sufficient to adequately correct errors.

After the branches have been selected, the survivor memory is backtracked to determine the most likely error free input value. For each state, the survivor memory is used to determine the most likely previous state.

Since the survivor memory indicates the most likely branch that was used to get to each state, it similarly indicates the most likely previous state. The Viterbi algorithm asserts that the process of backtracking will tend to correct input sequences that contain errors because the paths tend to converge as the survivor memory is traversed.

The backtracking process continues until the beginning of the survivor memory is reached. Assuming the paths had all converged in one path, the direction of the last branch determines the decoded value. If the last branch was an upper branch, the output is '0', otherwise the output is '1'. If the paths have not converged, then some other decision-making process must be used to select the output value. At this point, we might see errors at the output [SCI02].

The backtracking process is best illustrated by an example. For simplicity, assuming a survivor window depth of 7. There are four values stored for each entry in the survivor window. These values represent the most likely path (upper or lower) that was used to reach that state. Backtracking begins at the end of the survivor window and uses this information to trace backwards.

Fig(7) shows two representations of a trellis [MEN98]. The bottom diagram shows the backtracked paths and how those paths tend to converge.

Fig(7) also shows that all the paths have converged by the forth step in backtracking. The final branch represents a lower branch, so the output would be a '1'.

Fig(7) Backtracking through the survivor window

Note that the backtracking process introduces a delay between the input data stream and the output data stream. This delay is equal to the depth of the survivor memory. In the previous example, the decoded output is delayed by 7 data samples.

After backtracking, the global distance values are updated to reflect the new total distances to be used for the next input data. Since the global distances represents a

running total that steadily increases as data arrives, the values must be periodically normalized to avoid overflow. This is accomplished by determining the smallest global distance and subtracting that value from all of the global distances.

For example, if the global distances are 1,2,3, and 2, they would become 0,1,2, and 1 after normalization. Normalization maintains the relative difference between the values, but avoids overflow.

Finally, the contents of the survivor memory is shifted to the left in preparation for the next input data that will enter the survivor memory from the right.

#### 3.2 Viterbi Decoder Features:

- Hard Decision Decoder: This means that the incoming data symbol will be '0' or '1', i.e. there are two quantization levels in A/D converter (normally the received data is analog, and it will be converted to digital). In a soft decision Viterbi decoder there are more than two quantization levels. Here we implemented the hard decision approach [XIL01].

- Trace-back method for survivor memory: This is the method to select the smallest path. Traceback method means that all the possible paths are stored in RAM, and this method selects the most likely path.

- Branch Metrics computations can be added for different applications: Branch metric computation makes the error calculation between the received symbol (2 bits in our case) and the symbol in the table. In hard-decision Viterbi, the Hamming distance is calculated.

### 3.3 Design Flow Chart

17

#### 3.4 The VHDL code

library ieee; use ieee.std\_logic\_1164.all; use ieee.std\_logic\_arith.all; use ieee.std\_logic\_signed.all;

entity viterbi is

```

port (

clk :in std_logic;

rst_all :in std_logic;

data_in :in std_logic_vector (1 downto 0);

data_out :out std_logic

);

```

end viterbi;

architecture behavioral of viterbi is

begin

process (cik, rst\_all)

constant window\_length : integer :=32;

-- IEEE802.16 specifies a window length of 32

```

subtype survivor_elements is std_logic_vector (0 to 3);

type survivor_window_type is array (integer range <> ) of survivor_elements;

variable survivor_window : survivor_window_type (window_length-1 downto 0);

variable survivors : survivor_elements;

variable backtrack_survivors : survivor_elements;

```

type distance\_array\_type is array (0 to 3) of integer range 0 to 3; variable distance : distance\_array\_type; variable global\_distance : distance\_array\_type;

variable data\_in\_v : std\_logic\_vector (1 downto 0);

typebranch\_distance\_array\_type is array (0 to 3) of integer range 0 to 7;variableupper\_branch\_distance : branch\_distance\_array\_type;variablelower\_branch\_distance : branch\_distance\_array\_type;variablebranch\_distance : branch\_distance\_array\_type;variablebranch\_distance : branch\_distance\_array\_type;variableinteger range 0 to 7;

```

subtype state_type is integer range 0 to 3;

variable state : state_type;

variable branch_direction : std_logic;

```

begin

```

if rst_all = '0' then

data_out <='0';

for i in window_length -1 downto 0 loop</pre>

```

survivor\_window(i) := (others => '0' ); end loop;

```

for i in 3 downto 1 loop

global_distance(i) := 2;

end loop;

global_distance(0) := 0;

```

else

```

if (clk'event and clk = '1') then

```

data\_in\_v := data\_in;

-- calculate distances

```

case data in v is

when "00" =>

distance (0) := 0;

distance (1) := 1;

distance (2) := 1;

distance (3) := 2;

when "01" =>

distance (0) := 1;

distance (1) := 0;

distance (2) := 2;

distance (3) := 1;

when "10" =>

distance (0) := 1;

distance (1) := 2;

distance (2) := 0;

distance (3) := 1;

when "11" =>

distance (0) := 2;

distance (1) := 1;

distance (2) := 1;

distance (3) := 0;

when others =>

null:

end case:

-- Add-compare-select (ACS)

```

for i in 0 to 3 loop

-- calculate distances for upper and lower branches

```

case i is

```

```

when 0 => upper_branch_distance(i) := distance(0) + global_distance(0);

```

```

lower_branch_distance (i) := distance(3) + global_distance(2);

```

when 1 => upper\_branch\_distance(i) := distance(3) + global\_distance(0);

lower\_branch\_distance (i) := distance(0) + global\_distance(2);

when 2 => upper\_branch\_distance(i) := distance(1) + global\_distance(1);

lower\_branch\_distance (i) := distance(2) + global\_distance(3);

when 3 => upper\_branch\_distance(i) := distance(2) + global\_distance(1);

lower\_branch\_distance (i) := distance(1) + global\_distance(3);

end case;

-- select the surviving branch and fill appropriate value

-- into the survivor window

if ( upper\_branch\_distance(i) <= lower\_branch\_distance(i) ) then

```

branch_distance(i) := upper_branch_distance(i);

survivors(i) := '0';

```

else

```

branch_distance(i) := lower_branch_distance(i);

survivors(i) := '1';

```

end if;

end loop;

```

survivor_window(0) := survivors;

```

-- find the minimum branch distance and the ending state

```

minimum_branch := branch_distance(0);

state := 0;

```

for i in 1 to 3 loop

```

if (branch_distance(i) < minimum_branch) then

minimum_branch := branch_distance(i);

state := i;

end if;</pre>

```

end loop;

-- to avoid overflow we substract the min branch

for i in 0 to 3 loop

```

global_distance(i) := abs (branch_distance(i) - minimum_branch);

```

end loop;

-- backtrack the survivor window

for i in 0 to window\_length -1 loop

```

backtrack_survivors := survivor_window(i);

branch_direction := backtrack_survivors( state );

```

```

case state is

```

```

when 0 | 1 => if ( branch_direction ='0' ) then

state := 0;

else

state := 2;

end if;

when 2 | 3 => if ( branch_direction ='0' ) then

state := 1;

else

state := 3;

end if;

```

end case;

end loop;

-- shifting the survivor window values to allow the next input -- to enter the trellis from the right hand

for i in window\_length -1 downto 1 loop

```

survivor_window(i) := survivor_window(i - 1);

```

end loop;

-- output generation

data\_out <= branch\_direction;

end if;

end if;

end process;

end behavioral;

#### 3.5 An Example:

Now let's start looking at how the Viterbi decoding algorithm actually works [NETCOM]. The main goal of illustrating this example is to show that even if we received a wrong sequence at the input of the Viterbi decoder, we still get the correct

output sequence. We will review the error rate insertion matter in chapter (5). A trellis diagram is shown in fig(8).

Fig(8) A trellis diagram

For our example, we're going to use hard-decision decoding. Suppose we received the following encoded message with a couple of bit errors:

Fig(9) Encoded message with a couple of bit errors

Going from t = 0 to t = 1, there are only two possible channel symbol pairs we could have received:  $00_2$ , and  $11_2$ . That's because we know the convolutional encoder was initialized to the all-zeroes state, and given one input bit = one or zero, there are only two states we could transition to and two possible outputs of the encoder. These

possible outputs of the encoder are  $00_2$  and  $11_2$ . The Hamming distance is computed by simply counting how many bits are different between the received channel symbol pair and the possible channel symbol pairs. The results can only be zero, one, or two. The accumulated error metrics will be computed by adding the previous accumulated error metrics to the current branch metrics. At t = 1, we received  $00_2$ . The only possible channel symbol pairs we could have received are  $00_2$  and  $11_2$ . The Hamming distance between  $00_2$  and  $00_2$  is zero. The Hamming distance between  $00_2$  and  $11_2$  is two. Therefore, the branch metric value for the branch from State  $00_2$  to State  $00_2$  is zero, and for the branch from State  $00_2$  to State  $10_2$  is two. Since the previous accumulated error metric values are equal to zero, the accumulated metric values for State  $00_2$  and for State  $10_2$  are equal to the branch metric values. The accumulated error metric values for the other two states are undefined. The figure below illustrates the results at t = 1:

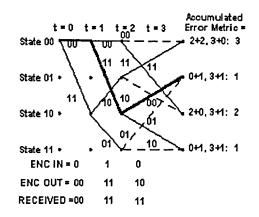

#### Fig(10) The trellis diagram between t = 0 and t = 1

At each time instant t, we will store the number of the previuos state that led to each of the current states at t.

26

Now let's look what happens at t = 2. We received a  $11_2$  channel symbol pair. The possible channel symbol pairs we could have received in going from t = 1 to t = 2 are  $00_2$  going from State  $00_2$  to State  $00_2$ ,  $11_2$  going from State  $00_2$  to State  $10_2$ ,  $10_2$  going from State  $10_2$  to State  $01_2$ , and  $01_2$  going from State  $10_2$  to State  $11_2$ . The Hamming distance between  $00_2$  and  $11_2$  is two, between  $11_2$  and  $11_2$  is zero, and between  $10_2$  or  $01_2$  and  $11_2$  is one. We add these branch metric values to the previous accumulated error metric values associated with each state that we came from to get to the current states. At t = 1, we could only be at State  $00_2$  or State  $10_2$ . The accumulated error metric values associated with those states were 0 and 2 respectively. The figure below shows the calculation of the accumulated error metric associated with each state, at t = 1

2.

#### Fig(11) The trellis diagram between t = 0 and t = 2

Now lets look at the figure for t = 3. Things get a bit more complicated here, since there are now two different ways that we could get from each of the four states that were valid at t = 2 to the four states that are valid at t = 3. We compare the accumulated error metrics associated with each branch, and discard the larger one of each pair of branches leading into a given state.

Fig(12) The trellis diagram between t = 0 and t = 3

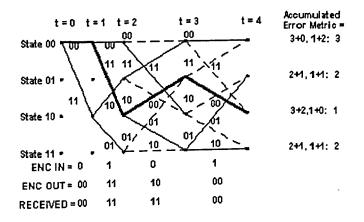

Note that the third channel symbol pair we received had a one-symbol error. The smallest accumulated error metric is a one, and there are two of these. Let's see what happens now at t = 4 [NETCOM]. The processing is the same as it was for t = 3. The results are shown in the figure:

Fig(13) The trellis diagram between t = 0 and t = 4

Notice that at t = 4, the path through the trellis of the actual transmitted message, shown in bold, is again associated with the smallest accumulated error metric. Let's look at t = 5:

#### Fig(14) The trellis diagram between t = 0 and t = 5

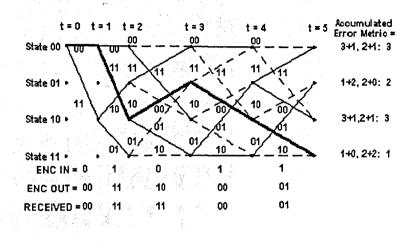

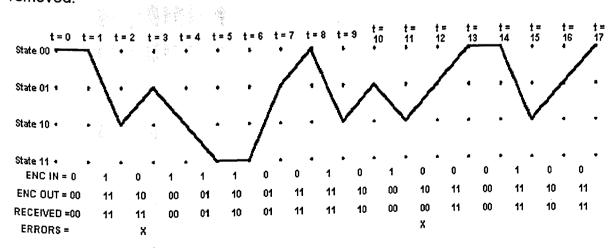

At t = 5, the path through the trellis corresponding to the actual message, shown in bold, is still associated with the smallest accumulated error metric. This is the thing that the Viterbi decoder exploits to recover the original message. Now, Let's skip to the end. At t = 17, the trellis looks like this, with the clutter of the intermediate state history removed:

Here's an insight into how the traceback algorithm eventually finds its way onto the right path even if it started out choosing the wrong initial state. This could happen if more than one state had the smallest accumulated error metric, for example. We will use the figure for the trellis at t = 3 again to illustrate this point. We saw how at t = 3. both States 01<sub>2</sub> and 11<sub>2</sub> had an accumulated error metric of 1. The correct path goes to State 01<sub>2</sub> -notice that the bold line showing the actual message path goes into this state. But suppose we choose State 112. The previous state for State 112, which is State  $10_2$ , is the same as the previous state for State  $01_2$ ! This is because at t = 2, State 102 had the smallest accumulated error metric. So after a false start, we are almost immediately back on the correct path. For the 15-bit message example, we built the trellis up for the entire message before starting traceback. For longer messages, or continuous data, this is neither practical or desirable, due to memory constraints and decoder delay. Research has shown that a traceback depth of (K x 5) is sufficient for Viterbi decoding with the type of codes we have been discussing [MEN98]. Any deeper traceback increases decoding delay and decoder memory requirements, while not significantly improving the performance of the decoder. The exception is punctured codes, which is not in our scope. They require deeper traceback to reach their final performance limits.

According to IEEE 802.16 specifications [ALT01], the traceback depth should equal 32, and that is more than  $(K \times 5) = 15$ . Here, we tried to follow the specifications. We also compiled our design with a traceback of 16, and it was sufficient for correcting the errors.

#### **CHAPTER 4**

### FIELD PROGRAMMABLE GATE ARRAYS (FPGAs)

#### 4.1 What is an FPGA?

Before the advent of programmable logic, custom logic circuits were built at the board level using standard components, or at the gate level in expensive application-specific integrated circuits. The FPGA is an integrated circuit that contains many (64 to over 10,000) identical logic cells that can be viewed as standard components. Each logic cell can independently take on any one of a limited set of personalities. The individual cells are interconnected by a matrix of wires and programmable switches. A user's design is implemented by specifying the simple logic function for each cell and selectively closing the switches in the interconnect matrix. The array of logic cells and interconnect form a fabric of basic building blocks for logic circuits. Complex designs are created by combining these basic blocks to create the desired circuit [XILINX].

#### 4.2 What does a logic cell do?

The logic cell architecture varies between different device families. Generally speaking, each logic cell combines a few binary inputs (typically between 3 and 10) to one or two outputs according to a Boolean logic function specified in the user program. In most families, the user also has the option of registering the combinatorial output of the cell, so that clocked logic can be easily implemented. The cell's combinatorial logic may be physically implemented as a small look-up table memory (LUT) or as a set of

multiplexers and gates. LUT devices tend to be a bit more flexible and provide more inputs per cell than multiplexer cells at the expense of propagation delay.

### 4.3 What does 'Field Programmable' mean?

Field Programmable means that the FPGA's function is defined by a user's program rather than by the manufacturer of the device. A typical integrated circuit performs a particular function defined at the time of manufacture. In contrast, the FPGA's function is defined by a program written by someone other than the device maufacturer. Depending on the particular device, the program is either 'burned' in permanently or semi-permanently as part of a board assembly process, or is loaded from an external memory each time the device is powered up. This user programmability gives the user access to complex integrated designs without the high engineering costs associated with application specific integrated circuits.

#### 4.4 Xilinx XC4000 family Logic Block

Figure (16) shows the CLB (Configurable Logic Block) used in the XC4000 series of Xilinx FPGAs. This is a fairly complicated basic logic cell containing 2 four-input LUTs that feed a three-input LUT. The XC4000 CLB also has special fast carry logic hard-wired between CLBs. MUX control logic maps four control inputs (C1–C4) into the four inputs: LUT input H1, direct in (DIN), enable clock (EC), and a set / reset control (S/R) for the flip-flops. The control inputs (C1–C4) can also be used to control the use of the F' and G' LUTs as 32 bits of SRAM.

Fig(16) The Xilinx XC4000 family CLB

The Xilinx CLB is the functional element from which user logic is constructed in an FPGA. I/O blocks (IOB) serve as the interface between the external package pin of the device and the internal user logic.

### 4.5 More about XC4005XL board

The XS4005XL Board is perfect for experimenting with FPGA designs, microcontroller programming, or hardware/software codesign [XESS]. The 9,000-gate XC4005XL FPGA operates at 5V so we can connect it to commonly available TTL chips. Digital logic designs can be loaded into the FPGA. The microcontroller can use the FPGA as a coprocessor. The 32-KByte SRAM can store microcontroller programs/data or serve as general-purpose storage for FPGA-based designs.

#### 4.6 How to program the FPGA board?

Individually defining the many switch connections and cell logic functions would be a hard task. Fortunately, this task is handled by special software. The software translates a user's schematic diagrams or textual hardware description language code then places and routes the translated design. Most of the software packages have hooks to allow the user to influence implementation, placement and routing to obtain better performance and utilization of the device [XILINX].

Using the appropriate software tool, a (.bit) file was generated. This file contains all the information that the FPGA needs to be programmed. Using XSTOOLS software package, we should drag the (.bit) file into the GXSLOAD area. Also, In the "build" process, we should specify the pin assignment file, which defines the pins that the FPGA will use to connect to the outside world. Our FPGA has 84 pins. The pin assignment file is stored as (.ucf) file. Our (.ucf) file is shown below:

net clk loc =p13; net rst\_all loc=p44; net data\_in(0) loc=p45; net data\_in(1) loc=p46; net data\_out loc=p25;

This file means that the clock input is pin number 13 of the PFGA, and the rst\_all pin is number 44. Also, the encoded data will enter the FPGA through pins 45 and 46, and the output is pin number 25 of the FPGA.

#### CHAPTER 5

### **EXPERIMENTAL RESULTS**

#### 5.1 What did we do?

We used VHDL hardware description language to implement the algorithm [SKA96]. We also used OrCAD Capture V9.1 to implement and find the simulation results. In our design, we tried to meet with IEEE 802.16 standard. IEEE 802.16 standard specifies the air interface of fixed point-to-multipoint broadband wireless access (BWA) systems providing multiple services. This standard is intended to enable rapid worldwide deployment of broadband wireless access products. The new IEEE 802.16 specifications requires a Viterbi decoder with constraint length of 3, traceback length of 32, and minimum throughput requirement of 44.8 Mbps.

Our specifications are a constraint length of 3, traceback length of 32, and a throughput of 45.4 Mbps.

We wrote down a random bit stream of data, then using the generator polynomials mentioned in chapter 2, we encoded these bits to get a randomly encoded input for our design. Random errors were then inserted into the encoded data stream. This represents the errors that might occur during transmission of the data through the wires or through the airwaves. The data stream, with errors, was processed by the Viterbi decoder. Finally, we compared the results to check whether or not the output of our Viterbi decoder (data\_out) is the same as the original signal.

# 5.2 Using OrCAD Capture to implement Viterbi Decoder:

The Build tool automates the translation of schematics and/or VHDL into the programming files required for the programmable device and provides an interface to Xilinx Alliance Series software. Placement and routing may be run at anytime after design entry is complete. The Build tool detects source VHDL or schematic files that may be "out of date" relative to the post-route simulation model file and if necessary, reruns logic synthesis to refresh the EDIF 2 0 0 (Electronic Data Interchange Format) netlist [ORCAD].

The Build tools uses the settings specified by the dialog box to build a Xilinx Alliance Series command file (with the extension .CMD) and series of command lines for the Xilinx Alliance Series NGDBuild program. The Build tool creates a subdirectory called TIMED below the subdirectory of the OrCAD project file (OPJ), copies all EDIF 2 0 0 netlist files from the COMPILED subdirectory, then runs NGDBuild. All results and reports are saved into the TIMED subdirectory and referenced by the project.

Each Xilinx place and route stage automated by the Build tool is described here:

**Translate** – converts the EDIF 2 0 0 files created by logic synthesis into a binary database used by the Xilinx software. This option causes the build process to stop after the Xilinx EDIF2NGD netlist translation program and writes one or more NGO files into the .\TIMED subdirectory. The translation report is saved as a .BLD file.

MAP – structures the incoming logical design to the target device we specify on the Part Type field of the NGDBuild tab. This option causes the build process to stop

36

after the Xilinx MAP program allocates CLBs, IOBs, and other Xilinx FPGA resources to logical elements of a design. Results are reported in the MRP file.

**Place and Route** – places and routes the physical design. This option causes the build process to stop after the Xilinx PAR program optimizes the layout using the timing constraints we may specify. Results of the timing analysis performed by PAR are available in the TIMED.DLY file and pin assignments in the TIMED.PAD file.

**Re-entrant Place and Route** – runs the Xilinx PAR program independently of Translate, MAP, and Implement. This option is useful to experiment with logic optimization and guide modes to arrive at a superior implementation.

**Implement** – generates a bitstream (.bit) file, which is required to program the FPGA. This option causes the build process to stop after the Xilinx BitGen program creates a configuration bitstream from the fully routed NCD (Native Circuit Description) created by PAR. Results from the BitGen run are available in the BGN and DRC files.

The Build tools uses the Xilinx Alliance Series program NGD2VHDL to create simulation models for timing simulation and adds them to the Timed folder of the Simulation Resources after place and route. The files required for a timing simulation include the netlist and standard delay format (with extension .SDF) file. Delay characteristics and performance rules of the SDF are applied by the simulator to emulate the propagation delays introduced by routing and logic block delays.

At this stage we simulate the post-place and route state of the project (Timed) to confirm that the PLD will meet our performance specifications. We apply input stimuli to the design. Our Viterbi decoder looked as follows after gererating the part:

Fig(17) Our Virerbi decoder symbol

The applied random stream of data is shown below as a table:

| Time (ns)        | 0  | 82 | 104 | 126 | 148 | 170 | 192 | 214 | 236 | 258 | 280 | 302 | 324 | 346 | 368 |

|------------------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Transmitted Data | 0  | 0  | 1   | 0   | 1   | 1   | 1   | 0   | 0   | 1   | 0   | 1   | 0   | 0   | 0   |

| Encoded Data     | 00 | 00 | 11  | 10  | 00  | 01  | 10  | 01  | 11  | 11  | 10  | 00  | 10  | 11  | 00  |

### cont.

| Time (ns)        | 390 | 412 | 434 | 456 | 478 | 500 | 522 | 544 | 566 | 588 | 610 | 632 | 654 | 676 | 698 |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Transmitted Data | 1   | 1   | 0   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 1   |

| Encoded Data     | 11  | 01  | 01  | 00  | 01  | 10  | 01  | 11  | 00  | 00  | 11  | 01  | 01  | 00  | 01  |

#### cont.

| Time (ns)        | 720 | 742 | 764 | 786 | 808 | 830 | 852 | 874 | 896 | 918 | 940 | 962 | 984 | 1006 | 1028 |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|

| Transmitted Data | 1   | 0   | 1   | 0   | 0   | 1   | 1   | 0   | 0   | 0   | 1   | 1   | 0   | 1    | 1    |

| Encoded Data     | 10  | 01  | 00  | 10  | 11  | 11  | 01  | 01  | 11  | 00  | 11  | 01  | 01  | 00   | 01   |

cont.

| Time (ns)        | 1050 | 1072 | 1094 | 1116 | 1138 | 1160 | 1182 | 1204 | 1226 | 1248 | 1270 | 1292 | 1314 | 1336 | 1358 |

|------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Transmitted Data | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    |

| Encoded Data     | 01   | 11   | 00   | 00   | 00   | 11   | 01   | 01   | 11   | 00   | 11   | 10   | 11   | 00   | 11   |

cont.

| Time (ns)        | 1380 | 1402 | 1424 | 1446 | 1468 | 1490 | 1512 | 1534 | 1556 | 1578 | 1600 | 1622 |

|------------------|------|------|------|------|------|------|------|------|------|------|------|------|

| Transmitted Data | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0    |

| Encoded Data     | 01   | 01   | 00   | 10   | 00   | 10   | 11   | 11   | 01   | 01   | 11   | 00   |

| Table 5.1 | The | applied | random | stream | of data |

|-----------|-----|---------|--------|--------|---------|

|-----------|-----|---------|--------|--------|---------|

The clock period was set to 22ns (45.4 MHz). Also the rst\_all input was set to be 0 until 70ns to reset the system, then we forced it to be 1 after that time to skip the reset operation. The applied random stream of data is shown below with the most important signals in the system:

| Context Signal       | Valuq <sub>DS</sub>                                                                                                       | 500ns                        | 1000ns | 1500ns                                  | 2000ns  | 2500      |

|----------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------|--------|-----------------------------------------|---------|-----------|

| VITERBI DATA_IN      |                                                                                                                           | ())).<br>A MARE (MARENAE) () |        |                                         | 0       | )         |

| DATA_IN[1]           | $\circ \circ \cdot \cdot$ |                              |        | MF <u>1. F</u>                          |         |           |

| DATA_IN[0]           | ᠃᠃└᠂ᡗ᠕ᠮ                                                                                                                   | MANA                         |        |                                         |         |           |

| VITERBI CLK          | o' MARAANA                                                                                                                |                              |        | MANNERMANNER                            |         | URIHHHII  |

| VITERBI DATA_OUT     | 101                                                                                                                       |                              |        | 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - | Linitin | 11        |

| VITERBI RST_ALL      | '1'                                                                                                                       |                              |        |                                         |         |           |

| VITERBI SURVIVOR_WIN | ND000000000000000000000000000000000000                                                                                    |                              |        |                                         |         | 00000     |

| VITERBI GND          | '0'                                                                                                                       |                              |        |                                         |         | · · · · · |

| VITERBI VCC          | '1'                                                                                                                       |                              |        |                                         |         |           |

# Fig(18) The simulation result after applying the random stream of data

As it appears, the output data is delayed by the depth of the memory. The first bit to come out from the traceback window is at time 807ns.

[32 (traceback window) +1 (clock cycle to generate the output)] x 22 (period) +76ns (delay to allow reset) + 5ns (output delay shown in fig(20)) = 807ns. Another graph showing how the data moves through the survivor window:

Fig (19) Data moves in the survivor window

Now showing the delay for the whole system:

We did the following cases:

1. Inserting a noise to the signal (Data\_in(1)) at 192ns (from 0 to 1):

| Context Signal      | Value                                          | 500ns                                   | 1000ns                   | 1500ns | 2000ns                                  | 250ğn           |

|---------------------|------------------------------------------------|-----------------------------------------|--------------------------|--------|-----------------------------------------|-----------------|

| VITERBI DATA_IN     |                                                |                                         |                          |        | 0                                       |                 |

| DATA_IN[1]          | '°' <u>· · · · · ·</u>                         | NEWICIA                                 |                          |        |                                         |                 |

| DATA_IN[0]          | '°' <u>··</u> ···                              | FIL-INLA-I-                             | $\overline{\mathcal{A}}$ |        |                                         |                 |

| VITERBI CLK         | '0' <b>                                   </b> |                                         | MULTIN HILLING           |        | M M M M M M M M M M M M M M M M M M M   | HUHMALKUL       |

| VITERBI DATA_OUT    | '0' <u></u>                                    |                                         |                          |        |                                         | <u><u> </u></u> |

| VITERBI RST_ALL     | 101                                            |                                         |                          |        | • • • • • • • • • • •                   |                 |

| VITERBI SURVIVOR_WI | IND000000000000000000000000000000000000        | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |                          |        | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX | 000000          |

| VITERBI GND         | '0' <i></i>                                    | <u></u>                                 |                          |        | <u></u> .                               | <u> </u>        |

| VITERBI VCC         | '1'                                            |                                         |                          |        | • • • • • • • • • • •                   | • • • • •       |

### Fig(21) A noise inserted at time 192ns

We observe no change at the output. Zooming the change that we did:

| Context | Signal        | Valuq             | Dns       |         | ns.     | 1 1     | 00ns        |              | 150n       | s<br>      | 4 + + 4    | 200ns | <b>.</b>  |            | 250      | ns<br>•••• |          |

|---------|---------------|-------------------|-----------|---------|---------|---------|-------------|--------------|------------|------------|------------|-------|-----------|------------|----------|------------|----------|

| VITERBI | DATA_IN       | o 🦹               |           |         | 0       |         | X           | <u> </u>     | <u>1 (</u> | <u>ο χ</u> | 2          | (3    | X         | 2χ         |          | 3          |          |

|         | DATA_IN[1]    | '0'Ŀ              |           |         |         |         |             | ••••         |            |            |            |       |           |            |          |            | • • F    |

|         | DATA_IN[0]    | '0' L             |           |         |         |         | · · · ·     |              | · · ] ·    |            |            |       | <u>۰.</u> | <u>···</u> |          |            | ••       |

| VITERBI | CLK           | י סי נ            |           | · · · · | <u></u> | <u></u> | <u>····</u> | <u>···</u> · | · · · ·    | · · [· ·   | <u>]</u> [ | •••   | • • •     | • • •      | ·]· ·    | · · ·      | <u>.</u> |

| VITERBI | DATA_OUT      | '0' [ <u>&gt;</u> | } <i></i> |         |         |         |             |              |            |            |            |       |           |            |          |            |          |

| VITERBI | RST_ALL       | '0' L             |           |         | [       |         |             |              |            |            |            |       |           |            |          |            |          |

| VITERBI | SURVIVOR_WINI | 0000              | { 00      | 00000   | 00000   | 000000  | 00000       | 00000        | 00         | Xoc        | 0000       | 0000  | 0000      | 0000       | 0000     | 0000       | 2000     |

| VITERBI | GND           | '0' L             |           |         |         |         |             |              |            |            |            |       |           |            | <u> </u> |            |          |

| VITERBI | VCC           | יני [-            |           |         |         |         |             |              |            |            |            |       |           |            |          |            | ••       |

# Fig(22) Showing the previous change

2. Changing the status at the following times for data\_in (1) : To 1 @ 192ns, to 0 @ 522ns, to 1 @ 676ns, to 1 @ 918ns, to 1 @ 1248 ns.

| Context Signal      | Valueons 500ns 1000ns 1500ns 2000ns 2500                                                                                              |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| VITERBI DATA_IN     |                                                                                                                                       |

| DATA_IN[1]          |                                                                                                                                       |

| DATA_IN[0]          | $`\circ` \sqcup f \land f$                                            |

| VITERBI CLK         |                                                                                                                                       |

| VITERBI DATA_OUT    | $```  \cdots $ |

| VITERBI RST_ALL     | '0'                                                                                                                                   |

| VITERBI SURVIVOR_WI |                                                                                                                                       |

| VITERBI GND         | 101                                                                                                                                   |

| VITERBI VCC         | · _ · · · · · · · · · · · · · · · · · ·                                                                                               |

### Fig(23) Inserting more noise

We observe no change at the output.

3. Now, inserting up to 8 errors in data\_in (0) by Changing the status at the following times : To 1 @ 214ns, to 0 @ 390ns, to 1 @ 566ns, to 1 @ 588ns, to 1 @ 852ns, to 1 @ 874ns, to 0 @ 1072ns, to 1 @1336ns.

| Context | Signal        | /alı | itons                                   | 500ns     |         | 1000               | ns<br> | 150   | )Ons<br>111.,  | * 1 * *        | 2000n | 5<br>4 1.4 1. | 25           | 500ns | ,<br>     |   |

|---------|---------------|------|-----------------------------------------|-----------|---------|--------------------|--------|-------|----------------|----------------|-------|---------------|--------------|-------|-----------|---|

| VITERBI | DATA_IN       | х    | 0 (5003)0                               | ie wie    |         | 3 )((9)            | 2(0)30 | MAR W | AL X           |                |       | 0             |              |       |           |   |

|         | DATA_IN[1]    | 'U'  |                                         | I-II-     | FNU     | $\overline{\cdot}$ | 7.0    | MLT   | $\mathbf{F}$   |                |       |               | • • •        |       | <u> </u>  | • |

|         | DATA_IN[0]    | 'U'  |                                         | l. l.     | ĿIJ     | ··II·              | اللغن  | FI    | FIŁ            |                |       |               |              | • • • | <u> </u>  |   |

| VITERBI | CLK           | יצי  |                                         | UURIURI   | NARAU   | HAHAM              | HARAN  | HATTA | UAIFIE         |                |       | ILIA          |              |       | · Lan     | • |

| VITERBI | DATA_OUT      | 'U'  | <u></u>                                 | . <u></u> |         | AF JA              | IJĿ    | Ŀſŀ   | II II          | <u>nn:</u>     | Лŀ    | JUU           | <u>] · ·</u> |       | · · · · · | , |

| VITERBI | RST_ALL       | 'X'  | 4                                       |           |         |                    |        |       |                |                |       |               |              |       | •••       |   |

| VITERBI | SURVIVOR_WIND | Х    | 000000000000000000000000000000000000000 |           |         | XEEDICA            | 100000 |       | <b>dáit</b> tí | <b>XXXXXXX</b> |       | pairto        | <b>1</b> 000 | 0000  | 000       |   |

| VITERBI | GND           | 'U'  |                                         |           | <u></u> |                    |        |       |                |                |       |               |              |       | <u> </u>  |   |

| VITERBI | vcc           | 'U'  |                                         |           |         |                    |        |       |                |                |       |               |              |       | • • •     |   |

#### Fig(24) Inserting more noise

As we can see the output signal still keeping its shape, even though we changed the input signal.

4. Now, Adding 3 more errors to the previous change ; to 0 @ 1490ns, to 0 @ 1512ns, to 0 @ 1534ns (Total number of errors introduced = 11 error). In this case we observe a 1 bit change in the output at time 2237ns.

| Context Signal      | Valuens 500ns 1000ns 1500ns 2000ns 2500ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|