## Study on Impact of Random Telegraph Noise on Scaled MOSFETs

| 著者       | 手賀 直樹                               |

|----------|-------------------------------------|

| year     | 2014                                |

| その他のタイトル | ランダム・テレグラフ・ノイズの微細MOSFETへの影          |

|          | 響に関する研究                             |

| 学位授与大学   | 筑波大学 (University of Tsukuba)        |

| 学位授与年度   | 2013                                |

| 報告番号     | 12102甲第6820号                        |

| URL      | http://hdl.handle.net/2241/00123312 |

# Study on Impact of Random Telegraph Noise on Scaled MOSFETs

Naoki Tega

## Study on Impact of Random Telegraph Noise on Scaled MOSFETs

### Naoki Tega

Doctoral Program in Nano-Science and Nano-Technology

Submitted to the Graduate School of

Pure and Applied Sciences

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy in

Engineering

at the

University of Tsukuba

### Content

| 1.  | Introduction·····                                                           | 3  |

|-----|-----------------------------------------------------------------------------|----|

| 1.1 | Device scaling and reliability                                              | 3  |

| 1.2 | Random telegraph noise (RTN) in MOSFET······                                | 7  |

| 1.3 | References                                                                  | 13 |

| 2.  | Development of statistical method of RTN                                    | 16 |

| 2.1 | Introduction                                                                | 16 |

| 2.2 | Device fabrication                                                          | 16 |

| 2.3 | Experimental                                                                | 16 |

| 2.4 | Statistical analysis RTN $V_{th}$ variations                                | 18 |

| 2.5 | Conclusions                                                                 | 25 |

| 2.6 | References                                                                  | 26 |

| 3   | Increasing threshold voltage variation due to RTN in MOSFETs                | 27 |

| 3.1 | Introduction                                                                | 27 |

| 3.2 | Device fabrication                                                          | 27 |

| 3.3 | Experimental                                                                | 27 |

| 3.4 | Statistical analysis on $V_{\rm th}$ variation in 22 nm MOSFETs······       | 31 |

| 3.5 | Gate-width and gate-length dependences of RTN $V_{th}$ variation            | 33 |

| 3.6 | Conclusions                                                                 | 35 |

| 3.7 | References                                                                  | 35 |

| 4   | Impact of RTN on high-κ / metal-gate stacks and future device scaling       | 37 |

| 4.1 | Introduction                                                                | 37 |

| 4.2 | Device fabrication                                                          | 37 |

| 4.3 | Measurement and analysis methods                                            | 38 |

| 4.4 | Inhibitory effect of HK / MG techniques on RTN                              | 40 |

| 4.5 | Conclusions                                                                 | 44 |

| 4.6 | References                                                                  | 44 |

| 5   | Investigation of RTN using MOSFETs fabricated on Si(100), (110), and (111). | 46 |

| 5.1 | Introduction                                                                | 46 |

| 5.2 | Samples Preparation and Experimental Methods                                | 46 |

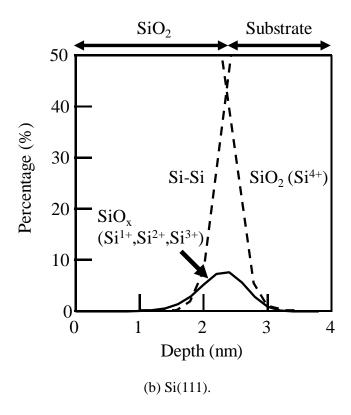

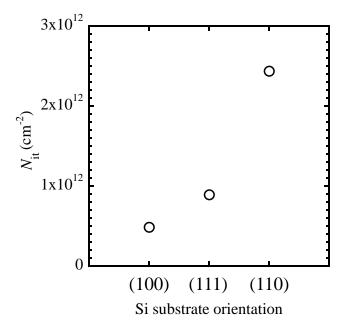

| 5.3 | Dependence of Si/SiO <sub>2</sub> Interface State on Si Surface Orientation | 48 |

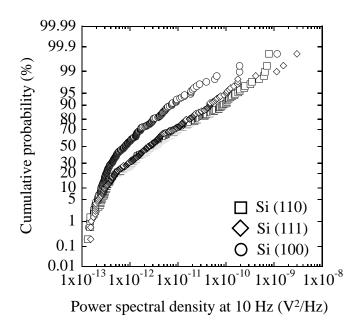

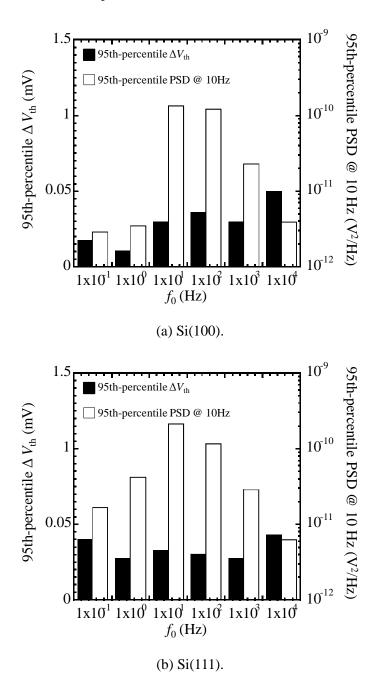

| 5.4 | Relationship between Si Orientation and RTN                                 | 51 |

| 5.5 | Conclusions                                                                 | 57 |

| 5.6 | References                                                                  | 57 |

| 6   | Impact of RTN $V_{th}$ variation on CMOS·······                             | 60 |

| 6.1 | Introduction                                                                | 60 |

| 6.2       | Experimental setup for noise measurement·····                                    | 60   |

|-----------|----------------------------------------------------------------------------------|------|

| 6.3       | Observation of RTN in n- and pMOSFETs·····                                       | 60   |

| 6.4       | Impact of RTN on SRAM operation                                                  | 66   |

| 6.5       | Conclusions                                                                      | 68   |

| 6.6       | References····                                                                   | 69   |

| 7         | Statistical analysis of relationship between NBTI and RTN in small pMOSFETs····· | ··71 |

| 7.1       | Introduction                                                                     | ··71 |

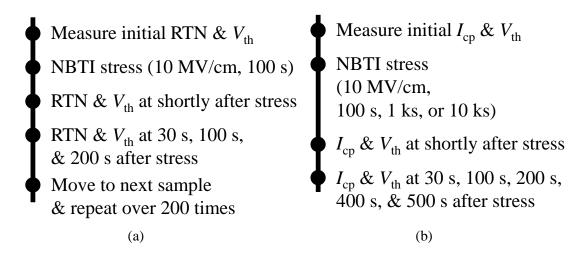

| 7.2       | Samples preparation and experimental methods·····                                | ··71 |

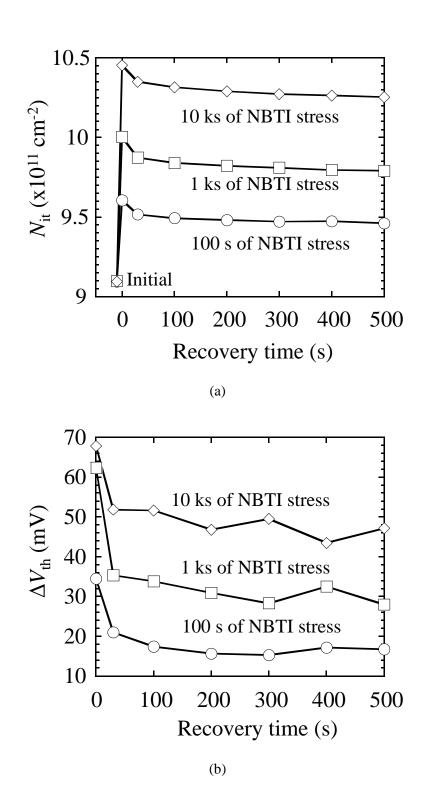

| 7.3       | $V_{\rm th}$ shift and change of $N_{\rm it}$ before and after NBTI stress······ | 74   |

| 7.4       | NBTI-stress-induced RTN                                                          | 74   |

| 7.5       | Conclusions                                                                      | 81   |

| 7.6       | References                                                                       | 81   |

| 8         | Physical model of RTN in MOSFET·····                                             | 84   |

| 8.1       | Introduction                                                                     | 84   |

| 8.2       | Experimental                                                                     | 86   |

| 8.3       | Modeling RTN in MOSFET                                                           | 90   |

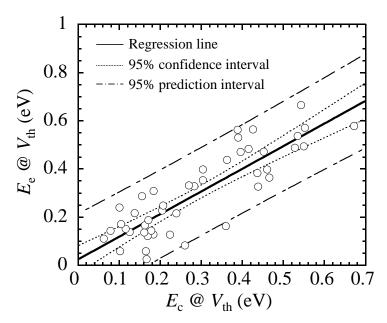

| 8.4       | Analysis of electrical properties ·····                                          | 98   |

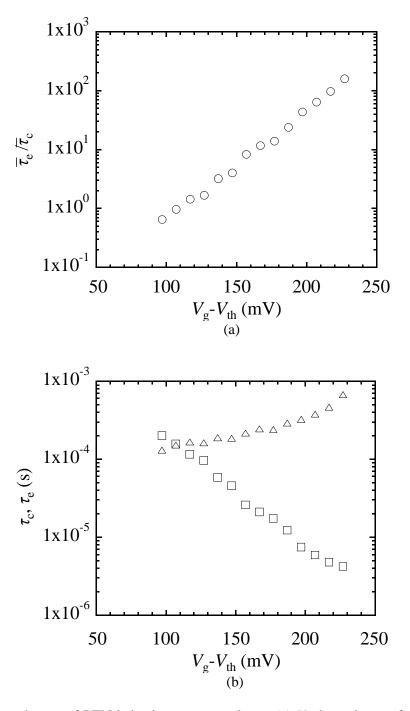

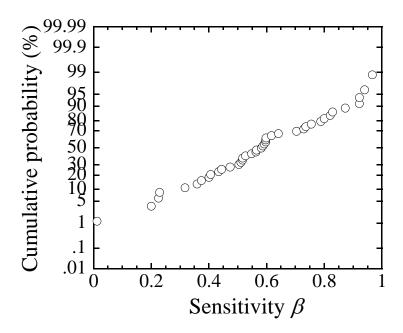

| 8.4.1     | Gate-bias sensitivity of $\bar{\tau}_e/\bar{\tau}_c$                             |      |

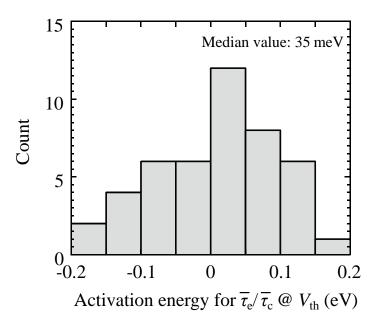

| 8.4.2     | Activation of $\bar{\tau}_e/\bar{\tau}_e$                                        | 99   |

| 8.4.3     | Influence of non-radiative multi-phonon emission                                 | 100  |

| 8.5       | Conclusions                                                                      | 103  |

| 8.6       | References                                                                       | 104  |

| 9         | Conclusions                                                                      | 106  |

| 9.1       | Contributions                                                                    | 106  |

| 9.2       | Future prospects and remaining problems                                          | 108  |

| 9.3       | References ····                                                                  | 109  |

| Acknow    | vlegment·····                                                                    | 110  |

| List of j | publications·····                                                                | 111  |

#### 1. Introduction

#### 1.1 Device scaling and reliability

The scaling of metal-oxide-semiconductor field-effect transistor (MOSFET) has played the role of an engine for an expansion of semiconductor industry for forty years [1, 2]. According to the Moore's law, the number of transistors on an integrated–circuits (IC) chip is expected to double every two years [1]. The Moore's law is a prediction and a rule of thumb in the history of computing hardware. Presently, this increase in density of transistors is achieved by constant-field scaling of complementary MOS (CMOS) [2]. In the constant-field scaling, keeping the electric-field constant makes it possible to reduce power-supply voltage and device dimensions, and as a result, it leads to greater density of MOSFETs on ICs, higher clock speed, and reduction of power consumption.

The scaling law greatly contributes to development of the semiconductor industry and, in the broad sense, development of an information society. However, in fact, many researchers and engineers faced various challenges and had to overcome them to achieve the scaling of MOSFET. Table 1.1 summaries a trend of MOSFET structures from 250 nm node, their characteristics, and their challenges. Especially, the author focuses on reliability challenges for each technology. After the 250 nm node, high-concentration extension has been applied to source and drain regions under sidewall spacers, and furthermore, heavy halo implantation has been locally formed close to the source/drain junctions [3-6]. Once a hot-carrier-induced degradation (HCD) was a serious problem and a lightly-doped-drain (LDD) structure was adjusted to improve HCD, however HCD was not a big challenge for the scaled MOSFETs because a voltage drain (Vdd) became lower than 2.5 V in the 250 nm generation and beyond.

In contrast to HCD, a short channel effect (SCE) has arisen, and the extension and the halo structures have been applied to suppress a threshold voltage ( $V_{th}$ ) roll-off and drain-induced-barrier lowering (DIBL) due to SCE. However, the heavy halo implantation posed a degradation of channel mobility, and then, some effective ways for keeping high drive current, for example, thinner gate dielectrics, were used [5, 7, 8]. In 250 nm generation and beyond, a dual-poly gate technique, in which each dual-poly gate includes an n-type polycrystalline silicon as a gate of nMOSFET and a p-type polycrystalline silicon as a gate of pMOSFET, was also required for reduction of SCE [9, 10].

Changes occurred at the gate dielectric with the dual-poly gate technique, and a silicon oxynitride (SiON) came into wide use as gate dielectric to suppress the boron diffusion from the poly gate of pMOSFET from the 180 nm generation [11]. SiON as the gate dielectric brought in a thinner equivalent oxide thickness (EOT) and good time-dependent dielectric breakdown (TDDB) characteristics. On the other hand, SiON raised severe other reliability issue, namely negative bias temperature instability (NBTI) in pMOSFET [12]. Even today, NBTI is one of the

Table 1.1 Trend of MOSFET structure and challege

| Technology node  | 250 nm ~                                                   | 130 nm ~                         |

|------------------|------------------------------------------------------------|----------------------------------|

| Device structure | Source (S)  Poly-Si gate  SiON  Drain (D)  Extension  Halo | Stress linear  Embedded stressor |

| Characteristics  | Source / Drain extension &                                 | Stressors (Stress linear,        |

|                  | Halo, Dual-poly gate                                       | Embedded SiGe and Si:C)          |

|                  | SiON gate dielectric                                       | Thin gate dielectric ( < 1.5nm)  |

| Challenges       | short channel effect (SCE)                                 | SCE                              |

|                  | Degraded mobility                                          | NBTI                             |

|                  | Negative bias temperature                                  | Gate leakage current             |

|                  | instability (NBTI)                                         | Random dopant fluctuation        |

| Technology node  | 45 nm ~                                                  | 22 nm ~                |

|------------------|----------------------------------------------------------|------------------------|

| Device structure | Metal gate Hf-based high-к dielectrics Interfacial layer | Gate D Cate D Covide   |

| Characteristics  | Hf-based high-κ dielectric                               | Multiple gate          |

|                  | Metal gate                                               | 3D structure           |

| Challenges       | SCE                                                      | NBTI                   |

|                  | NBTI                                                     | Variability            |

|                  | Variability                                              | Random telegraph noise |

major reliability issues for the scaled pMOSFET. NBTI degradation worsen at high temperature, causing a large negative threshold voltage shift and decrease in drain current  $(I_d)$  and transconductance  $(G_m)$ . Consequently, it causes a decrease in circuit speed and an increase in energy consumption. The mechanism of the NBTI degradation is less certain. Two NBTI

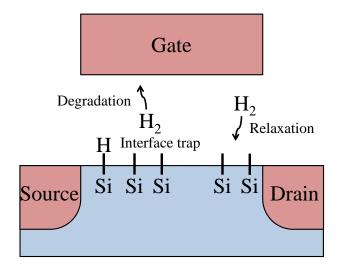

(a) Reaction-diffusion model.

(b) Switching trap model.

Fig. 1.1 Candidate models of NBTI degradation and recovery.

physics have been proposed to understand NBTI degradation so far as shown in Fig. 1.1. One is the reaction-diffusion (R-D) model [13]. The other is the switching trap model [14]. The R-D model is widely accepted as the most likely explanation for the NBTI degradation until quite recently. In the R-D model, the physics of interface trap generation is based on electrochemical reaction. The R-D model states that the NBTI stress induced degradation of pMOSFET is derived by breaking of hydrogen-passivated silicon bonds at the interface and subsequent diffusion of hydrogen as illustrated in Fig. 1.1(a). One of the significant features of the NBTI

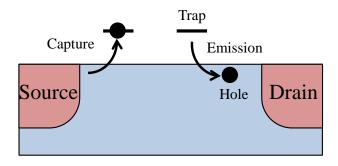

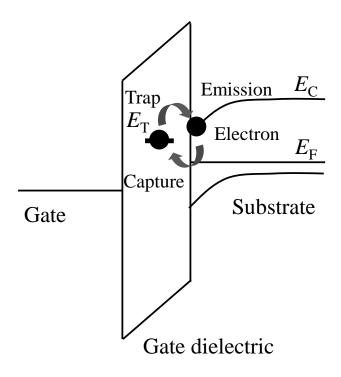

behavior is a fast recovery. The fast-recovery component is explained by hydrogen moving back to the interface again in the R-D model. However, recently, the main component in relaxation state is regarded as not the electrochemical reaction stated in the R-D model, as but the hole detrapping phenomenon [14]. On the other hand, T. Grasser introduces the switching trap model more simply to understand the NBTI degradation and recovery. In the switching trap model, the NBTI degradation and recovery are understood by combination of random telegraph noises (RTN) with different time constants as shown in Fig. 1.1(b). RTN is observed as binary fluctuation in  $V_{th}$  or  $I_{d}$  in response to the capture and emission of carrier at single trap in the gate oxide. The author focuses on an impact of RTN on scaled MOSFET and intends to introduce RTN in more detail in the next section 1.2.

There are challenges of the 130 nm generation and beyond CMOS technology besides the NBTI degradation. They are gate leakage current and random dopant fluctuation (RDF) [15, 16]. Gate leakage current increasingly posed severe problem to the scaled MOSFET because thickness of the gate dielectric ( $T_{\rm ox}$ ) became about 1.5 nm. Moreover, the impact of the discrete dopant profiling on the variability of  $V_{\rm th}$  in small device became obvious from the 130 nm generation because scaling speed of  $T_{\rm ox}$  is not so much fast as gate area, and accordingly, the technology faced a severe problem with  $V_{\rm th}$  variability. The two challenges remained a serious threat to the 90 nm and the subsequent 65 nm generations. When new gate stacks structure incorporating Hf-based high- $\kappa$  dielectric and metal gate (HK / MG) began to be put to practical use in some advanced processers at the 45 nm generation, the adaption of HK / MG stacks led to a significant improvement of the gate leakage current and RDF [17, 18]. On the other hand, some variability problems, for example, line edge roughness (LER), work-function variation comes from the orientation of grains in metal gate, have been remained in scaled MOSFETs to this day [19, 20].

By the way, HK / MG stacks include an interfacial layer (IL) between substrate and Hf-based high-κ dielectric, which usually consists of SiON, because it is expected to prevent or at least minimize an interfacial reaction between the high-κ oxide and the underlying Si [21]. SiON film is likely to be required for the thermal stability for some time in the future. In other words, the above-mentioned NBTI degradation will remain as one of the severe problems until the effect of the SiON film is not needed.

The first processer chips on the 45-nm HK/MG technology were released in 2007. Manufactures worked in research and development of technology for the 45 nm generation and beyond. At around the same time, 2009 International technology roadmap for semiconductors (ITRS), for the first time, mentioned that an attention is needed to be paid to RTN for static random access memory (SRAM) scaling because its acceptable noise margins are becoming narrower due to increasing  $V_{th}$  variability including RTN [22]. 2011 ITRS also took up the issue

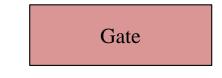

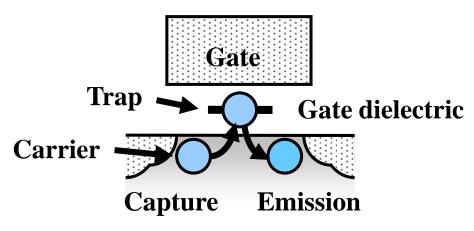

**Substrate**

Fig. 1.2 RTN behavior is caused by single trap at gate dielectric.

of RTN for SRAM scaling [23]. The RTN behavior is the most fundamental property of trap at gate dielectric. There are not enough measures yet to improve the RTN problem.

The Manufactures are accelerating research and development of a multi-gate transistor after the practical application of the HK/MG technique to overcome SCE due to the device size decrease. At the moment, 2014, Intel Corporation commercially released the multi-gate transistor called Tri-gate on the 22-nm technology [24]. The other manufactures will be expected to release their multi-gate transistors in the immediate future. However, variability such as LER and RDF, the NBTI degradation, and RTN will be likely to remain as the reliability challenges even in the age of the multi-gate transistor.

#### 1.2 Random telegraph noise (RTN) in MOSFET

The discrete switching in the current in semiconductor has been already known in 1950s and 1960s [25]. The first observation of the single-switching event as RTN is conducted using junction field effect transistor (JFET) in 1978 [26]. The RTN behaviors on semiconductor devices have been reported since early times. However, an observation of RTN behavior on MOSFET and identifying the cause of RTN, namely, interface trap and bulk trap at gate oxide, have not been reported until 1984 [27]. The first report by K. S. Rails et al. indicated that 1/f noise on MOSFET is likely to consist of many RTNs from observation. Before that time, A. McWhorter suggested the number fluctuation model using Ge filament in 1957 [28]. This model states that 1/f noise is composed of a large number of RTNs.

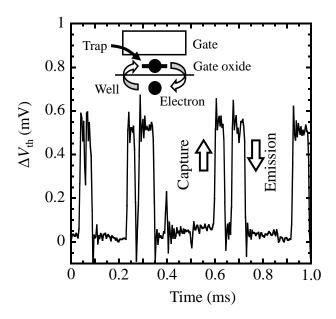

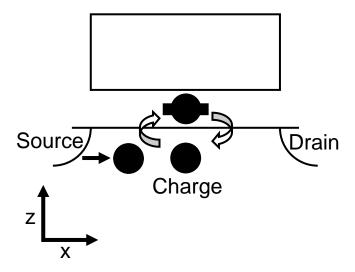

RTN is caused by single trap at gate dielectric capturing and emitting a carrier as shown in

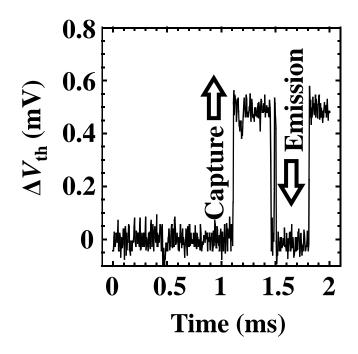

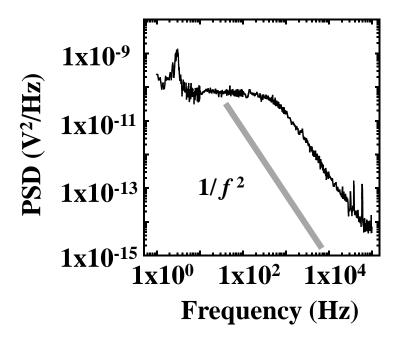

Fig. 1.3 Binary threshold voltage fluctuation due to RTN.

Fig. 1.4 Lorentzian power spectrum density based on RTN waveform in Fig. 1.3.

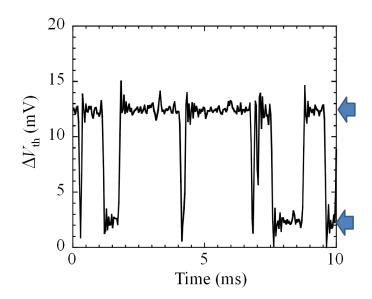

Fig. 1.2. Figure 1.3 is binary  $V_{\rm th}$  variation due to single RTN trap in nMOSFET. The lower states are the duration time to capture  $(\tau_{\rm c})$  and the upper states are the duration time to emission  $(\tau_{\rm e})$ .

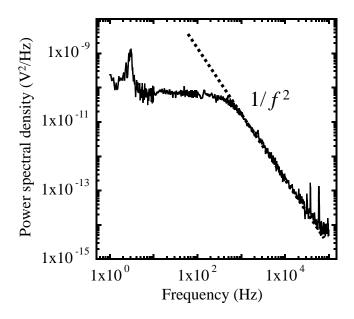

$\tau_c$  and  $\tau_e$  are known to show exponential distribution. An important property of the exponential distribution is "memorylessness". The name "Random" in Random telegraph noise comes from this memoryless characteristic. The relationship between the exponential function and the Lorentzian function is known as duality in Fourier transform. Therefore, the power spectrum density (PSD) of RTN is shown as below.

$$S(f) = \frac{4(\Delta V)^2}{(\bar{\tau}_c + \bar{\tau}_e)[(1/\bar{\tau}_c + 1/\bar{\tau}_e)^2 + (2\pi f)^2]}$$

(1.1)

f is the frequency,  $\Delta V$  is the amplitude of RTN,  $\bar{\tau}_c$  and  $\bar{\tau}_e$  are the average of  $\tau_c$  and  $\tau_e$ , respectively. Figure 1.4 is an example of PSD calculated using the data in Fig. 1.3. In general, the plateau part and  $1/f^2$  part can be separated from the Lorentzian power spectrum as shown in Fig. 1.3. When  $\bar{\tau}_c$  is equal to  $\bar{\tau}_e$  and  $\bar{\tau}$ , Equation (1.1) can be deformed as shown in Eq. (1.2)

$$S(f) = \frac{\Delta V^2}{2} \cdot \frac{\overline{\tau}}{1 + \pi^2 f^2 \overline{\tau}^2} \quad (1.2)$$

S. Christensson et al. successfully applied Eq. (1.2) to 1/f noise on MOSFET on the assumption that the traps at gate oxide are source of noise, and the trap depth determines the time constant ( $\bar{\tau}$ ) in 1968 [29].  $\bar{\tau}$  is simply expressed as Eq. (1.3) from the trap depth y because  $\bar{\tau}$  follows the tunneling probability.

$$\bar{\tau} = \tau_0 \exp(\gamma y)$$

(1.3)

$\tau_0$  and  $\gamma$  are a constant. If the RTN traps uniformly spread in gate oxide, and the trap depths distribute from the interface between channel and gate oxide to d, the power spectrum density of 1/f noise is shown by the integral from zero to d of Eq. (1.2).

$$S(f) = \frac{\Delta V^2}{2} \int_0^d \frac{\overline{\tau}}{1 + \pi^2 f^2 \overline{\tau}^2} dy$$

$$= \frac{\Delta V^2}{2} \int_0^d \frac{\tau_0 \exp(\gamma y)}{1 + \pi^2 f^2 [\tau_0 \exp(\gamma y)]^2} dy$$

$$= \frac{\Delta V^2}{2\alpha\pi f} \{\arctan[\tau_0 \pi f \exp(\gamma d)] - \arctan(\tau_0 \pi f)\} \quad (1.4)$$

S. Christensson et al. noted that  $\tau_0$  is of order of  $10^{-8}$  sec,  $\exp(\gamma d)$  is nearly equal to  $10^{17}$ . The

range of f is usually from 1 Hz to 100 kHz in the measurement of low-frequency noise. Accordingly,  $\arctan[\tau_0\pi f\exp(\gamma d)]$  is approximately  $\pi/2$ , and  $\arctan(\tau_0\pi f)$  is about zero. Finally, the power spectrum density of 1/f noise is

$$S(f) = \frac{\Delta V^2}{4\gamma f} \quad (1.5).$$

This 1/f noise model and the experimental result reported by K. S. Rails et al. help understanding of the low frequency noise in MOSFET. Furthermore, M. J. Kirton and M. J. Uren paved the way for the development of physics of 1/f noise and RTN in MOSFET from the Rails' discussion [30]. Until now, many reports' discussions about dependences of RTN on process, device structure, technology node, and etc. are basically based on the Kirton-Uren model. The capture 8 is attempt to advance the RTN physical model to explain a wide distribution of the RTN activation energy and a dependences of RTN time constant on gate voltage more logically and more accurately.

In analog devices, since smallest detectable signal, signal to noise ratio (SNR), and dynamic range are determined by noises, many researchers have earnestly made an investigation about 1/f noise as one of the low frequency. In contrast to 1/f noise, the attention has not been paid to RTN because the variation of RTN is acceptable level in both analog and digital devices. Researchers were interested in RTN as fundamental characteristics of trap at gate dielectric and, however, placed low priority on RTN as the reliability issue until 2000s.

It was, for the first time, reported at 2006 that the RTN became the reliability issue in high-capacity flash memory [31]. Why did RTN suddenly pose a serious threat to the flash memory? The answers are four points.

1) The RTN impact increases with scaling as indicated in Eq. (1.6).

$$\Delta V_{\rm th} = -\frac{q}{L_{\rm g} W_{\rm g} C_{\rm ox}} \quad (1.6)$$

$\Delta V_{\rm th}$  is the threshold voltage variation, q is the elementary charge,  $L_{\rm g}$  is the gate length,  $W_{\rm g}$  is the gate width, and  $C_{\rm ox}$  is the gate oxide capacitance of unit area.

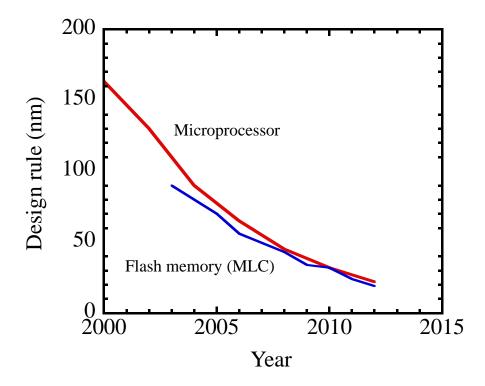

2) The flash memory is fabricated by leading-edge technology and its technology continues to drive minimum feature size.

Fig. 1.5 Scaling trends of microprocessor and flash memory. The trend of flash memory with multi-level cell (MLC) technique is based on announcements by Toshiba at International Solid-State Circuits Conference (ISSCC). The trend of microprocessor is based on Intel announcements.

- 3) High-capacity flash memory adopts the multi-level technique to increase bits per cell, and its  $V_{th}$  margin decreases as negative effect.

- 4) A high field stress on thin oxide, for example, less than  $9 \sim 10$  nm, increases the current density at low electric field. This problem is known as stress-induced leakage current (SILC) and obstructs decreasing gate-oxide thickness with scaling [32]. Therefore, RTN  $V_{\rm th}$  variation in high-capacity flash memory is likely to be large in comparison with the other digital devices with same technology as indicated in Eq.(1.6).

RTN is still one of the reliability issues in high-capacity flash memory.

The author predicted that RTN also has an impact not only on the high-capacity flash memory but also on the scaled logic devices and SRAM in the immediate future because the CMOS technology shows the same scaling trend as the high-capacity flash memory as show in Fig.1.5. The area of the latest 22-nm technology is less than one-tenth of the 90-nm technology in which RTN became obvious in high-capacity flash memory. Therefore, the author needed to plan to accurately study the impact of RTN on scaled CMOS, especially scaled SRAM with

narrow margin, beforehand.

This paper consists of nine chapters. The outline of each chapter is described below.

Chapter 2: The author suggests new statistical method to analyze RTN  $V_{th}$  variation. RTN  $V_{th}$  variation follows Gumbel distribution, which is one of the extreme value distributions. In this chapter, the author also discusses whether the Gumbel law or the Fréchet law is more suitable for investigation of the impact of RTN on scaled MOS by regression analysis.

Chapter 3: The statistical distribution of RTN  $V_{\rm th}$  variation was measured and characterized by use of scaled PDSOI MOSFETs with SiON / polycrystalline Si gate down to 20 nm gate length. Moreover, the dependences of the RTN variation on  $L_{\rm g}$  and  $W_{\rm g}$  are shown.

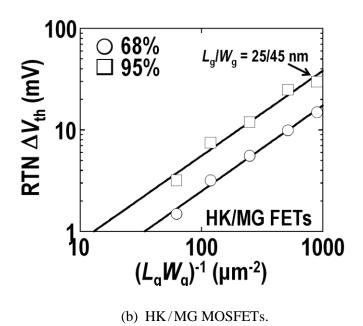

Chapter 4: The author demonstrates the reduction of RTN in high- $\kappa$  / metal gate (HK / MG) stacks incorporated in 22 nm generation MOSFETs. Many thousands of such MOSFETs have been fabricated, measured, and analyzed using a statistical technique. Based on a statistical comparison of these MOSFETs, the author finds that high temperature forming gas annealing (HTFGA) can suppress RTN  $\Delta V_{th}$ . In addition, properly annealed HK FETs have smaller RTN  $\Delta V_{th}$  than SiON / poly-Si MOSFETs due to fewer traps and to thinner inversion thickness in HK / MG.

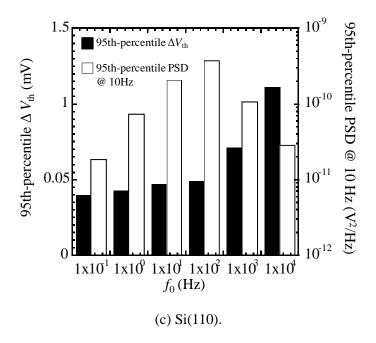

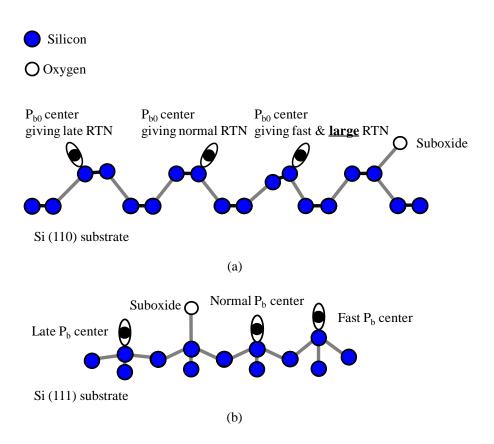

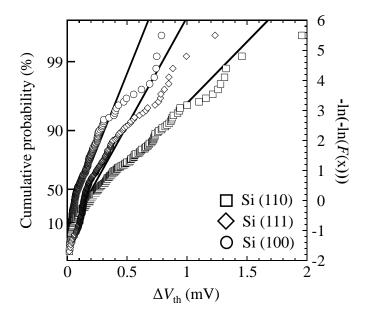

Chapter 5: It is clarified that suboxides and interface traps are closely linked to  $\Delta V_{th}$  due to RTN from an investigation of dependence of  $\Delta V_{th}$  on silicon-surface orientation: Si(100), (110), and (111). The amount of RTN traps increases with increasing amount of suboxides in the interfacial transition layer. With regard to the total amount of suboxides, the Si(110) surface orientation gives a larger amount than Si(100) and Si(111). Furthermore, the author found that Si(110) has the potential to give fast RTNs with a larger amplitude than Si(111). Accordingly,  $\Delta V_{th}$  for Si(110) is larger than those of Si(100) and Si(111).

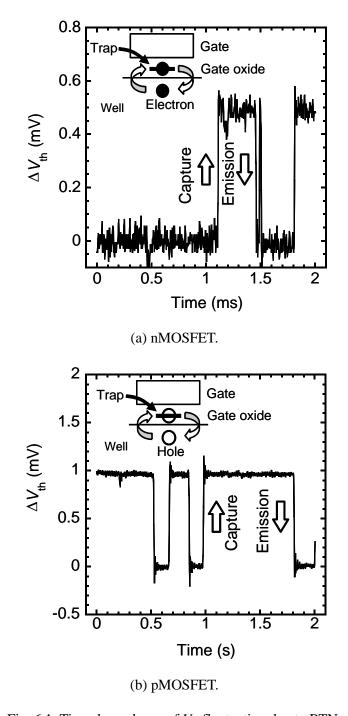

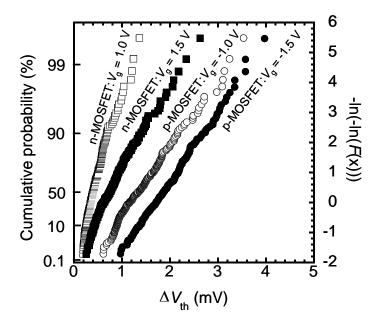

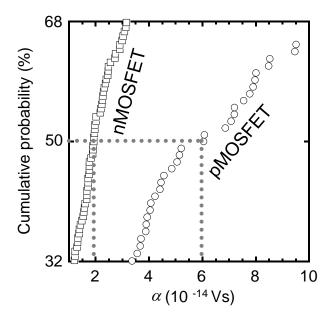

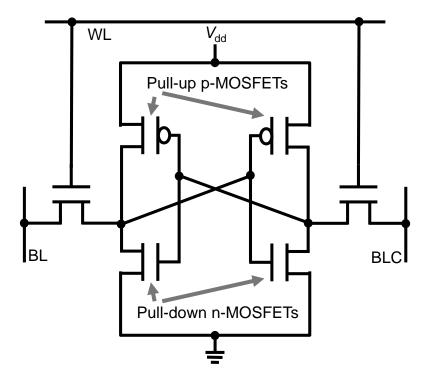

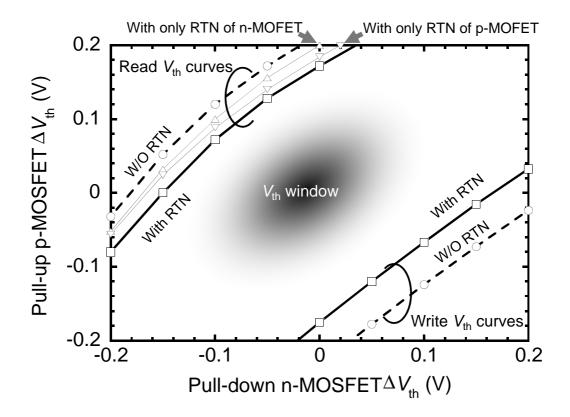

Chapter 6: The impact of RTN on a scaled-down SRAM is shown. To estimate the impact on SRAM, the author statistically analyzed  $V_{th}$  variation of n- and pMOSFETs. It is revealed that  $\Delta V_{th}$  of pMOSFET is larger than that of nMOSFET. This difference can be explained by taking into account both the number- and mobility-fluctuation models of RTN.

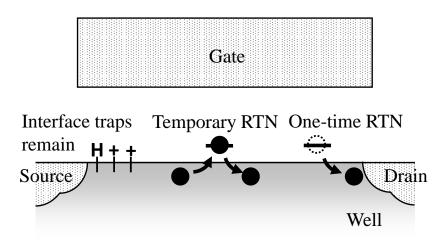

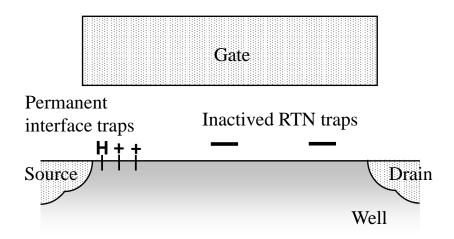

Chapter 7: Change in generation of RTNs before and after NBTI stress is demonstrated to reveal NBTI degradation and recovery from statistical perspective. The NBTI stress generates a large number of permanent interface traps and, at the same time, the temporary and the one-time

RTNs. The two types of traps show different features. A re-passivation of interface states is minority in recovery process after the NBTI stress, and in contrast, rapid disappear of the temporary and the one-time RTNs mainly causes the recovery phenomenon. Distinguishing characteristic is that the RTN traps are less likely to become permanent traps in contrast to the interface traps. This two-type trap model simply explains NBTI degradation and recovery in scaled pMOSFET.

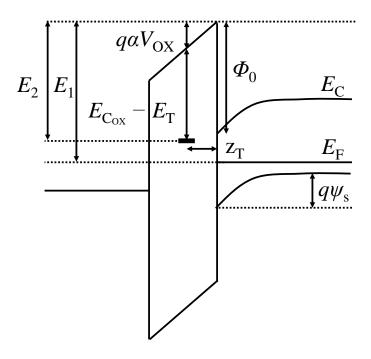

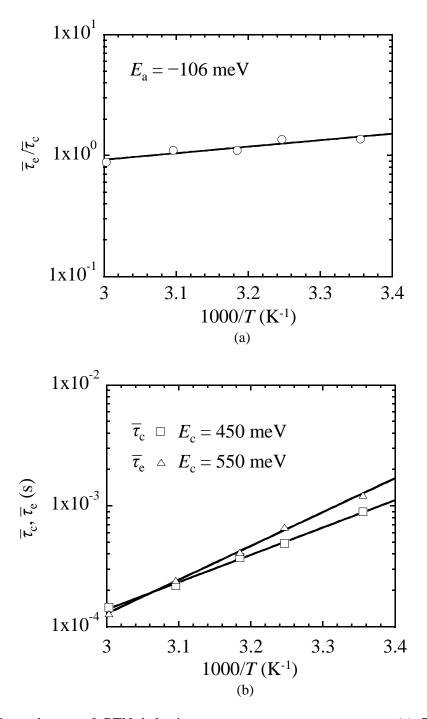

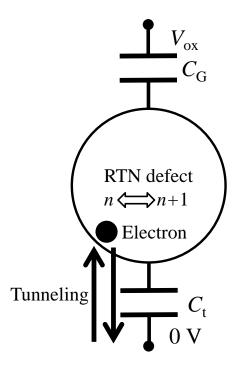

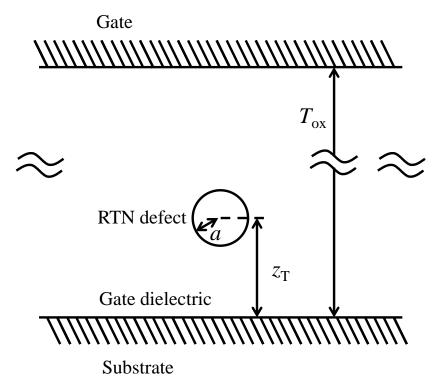

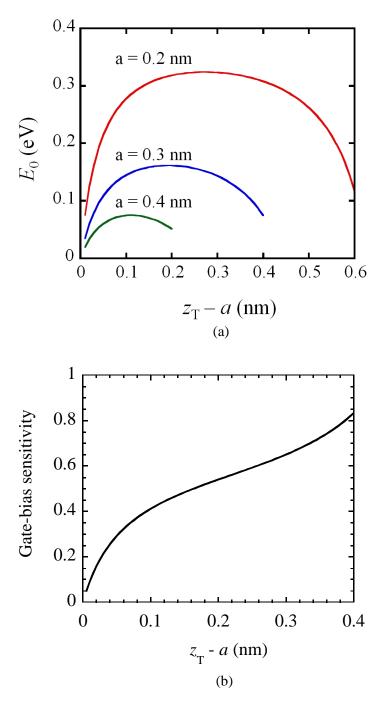

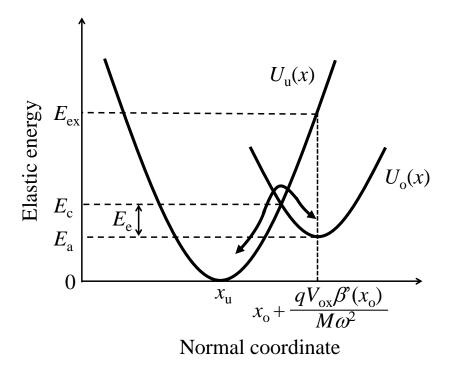

Chapter 8: Physical model of RTN is proposed to explain large activation energies for  $\bar{\tau}_e/\bar{\tau}_c$ ,  $\bar{\tau}_e$ , and  $\bar{\tau}_c$  respectively and large gate bias sensitivity of  $\bar{\tau}_e/\bar{\tau}_c$ . In this chapter, to propose a physical model of RTN in MOSFET, the author newly introduces the coulomb blockade theory, a relationship between a conducting sphere and parallel plates, and an advanced non-radiative muliti-phonon theory (NMP).

Chapter 9: The author summarizes the impact of RTN on technologies for scaling, the relationship between NBTI and RTN, and the proposed RTN physical model. Moreover, the author shows future prospects and remaining problems

#### 1.3 References

- [1] G. E. Moore, "Cramming More Components onto Integrated Circuits," *Electronics*, vol. 38, 19, Apr., 1965.

- [2] R. H. Dennard, F. H. Gaensslen, H-N Yu, V. L. Rideout, E. Bassous, and A. R. Leblanc, "Design of Ion-Implanted MOSFET's with very small physical dimensions," *IEEE J. Solid-Sate Circuits*, vol. 9, pp.256-268, Oct., 1974.

- [3] C. F. Codella, and S. Ogura, "Halo Doping Effects in Submicron DI-LDD Device Design," in *IEDM Tech. Dig.*, pp. 230–233, 1985.

- [4] S. Thompson, P. Packan, T. Ghani, M. Stettler, M. Alavi, I. Post, S. Tyagi, S. Ahmed, S. Yang, and M. Bohr, "Source/Drain Extension Scaling for 0.1 μm and Below Channel Length MOSFETS," in *VLSI Symp. Tech. Dig.*, pp. 132–133, 1996.

- [5] H. Hwang, D-H. Lee, and J. M. Hwang, "Degradation of MOSFETs Drive Current Due to Halo Ion Implantation," in *IEDM Tech. Dig.*, pp. 567–570, 1996.

- [6] M. Bohr, S. S. Ahmed, S. U. Ahmed, M. Bost, T. Ghani, J. Greason, R. Hainsey, C. Jan, P. Packan, S. Sivakumar, S. Thompson, J. Tsai, and S. Yang, "A High Performance 0.25 μm Logic Technology Optimized for 1.8 V Operation," in *IEDM Tech. Dig.*, pp. 847–850, 1996.

- [7] H. S. Momose, M. Ono, T. Yoshitomi, T. Ohguro, S. Nakamura, M. Saito, and H. Iwai, "Tunneling Gate Oxide Approach to Ultra-High Current Drive in Small-Geometry MOSFETs," in *IEDM Tech. Dig.*, pp. 593–596, 1994.

- [8] M. Rodder, S. Hattangady, N. Yu, W. Shiau, P. Nicollian, T. Laaksonen, C. P. Chao, M. Mehrotra, C. Lee, S. Murtaza, and S. Aur, "A 1.2 V 0.1 μm Gate Length CMOS Technology: Design and Process Issues," in *IEDM Tech. Dig.*, pp. 623–626, 1998.

- [9] W-H. Chang, B. Davari, M. R. Wordeman, Y. Taur, C. C-H. Hsu, and M. D. Rodriguez, "A High-Performance 0.25-μm CMOS Technology: I-Design and Characterization," *IEEE Trans. Electron Devices*, vol. 39, no. 4, pp. 959–966, Apr., 1992.

- [10] B. Davari, W-H. Chang, K. E. Petrillo, C. Y. Wong, D. Moy, Y. Taur, M. R. Wordeman, J. Y-C. Sun, C. C-H. Hsu, and d M. D. Rodriguez, "A High-Performance 0.25-μm CMOS Technology: II-Design and Characterization," *IEEE Trans. Electron Devices*, vol. 39, no. 4, pp. 967–975, Apr., 1992.

- [11] D. Wristers, L. K. Han, T. Chen, H. H. Wang, and D. L. Kwong, M. Allen, and J. Fulford, "Degradation of oxynitride gate dielectric reliability due to boron diffusion," *Appl. Phys. Lett.*, vol. 68, no. 15, pp. 2094–2096, Apr., 1996.

- [12] J.H. Stathis, and S. Zafar, "The negative bias temperature instability in MOS devices: A review," *Microelectron. Reliab.*, vol. 46, pp. 270–86, 286, Feb. –Apr. 2006.

- [13] M. A. Alam, "A critical examination of the mechanics of dynamic NBTI for PMOSFETs," in *IEDM Tech. Dig.*, pp. 14.4.1–14.4.4, 2003.

- [14] T. Grasser, "Switching oxide traps as the missing link between negative bias temperature instability and random telegraph noise," in *IEDM Tech. Dig.*, pp. 1–4, 2009.

- [15] Y-C. Yeo, T-J. King, and C. Hu, "Direct tunneling leakage current and scalability of alternative gate dielectrics," *Appl. Phys. Lett.*, vol. 81, pp. 2091–2093, Sep., 2002.

- [16] A. Asenov, "Random Dopant Induced Threshold Voltage Lowering and Fluctuations in Sub-0.1 m MOSFET's: A 3-D"Atomistic" Simulation Study," *IEEE Trans. Electron Devices*, vol. 45, no. 12, pp. 2505–2513, Dec., 1998.

- [17] K. J. Kuhn, "Reducing Variation in Advanced Logic Technologies: Approaches to Process and Design for Manufacturability of Nanoscale CMOS," in *IEDM Tech. Dig.*, pp. 471–474, 2007.

- [18] K. Mistry et al., "A 45 nm logic technology with high-k+ metal gate transistors, strained silicon, 9 cu interconnect layers, 193 nm dry patterning, and 100% Pb-free packaging," in *IEDM Tech. Dig.*, pp. 247–250, 2007.

- [19] H. Dadgour, V. De, and K. Banerjee, "Statistical Modeling of Metal-Gate Work-Function Variability in Emerging Device Technologies and Implications for Circuit Design," in *Proc. ICCAD*, pp. 270–277, 2008.

- [20] A. Asenov, S. Kaya, and A. R. Brown," Intrinsic Parameter Fluctuations in Decananometer MOSFETs Introduced by Gate Line Edge Roughness," *IEEE Trans. Electron Devices*, vol. 50, no. 5, pp. 1254–1260, May, 2003.

- [21] G. D.Wilk, R. M.Wallace, and J. M. Anthony, "High-k gate dielectrics: Current status and materials properties considerations," *J. Appl. Phys.*, vol. 89, pp. 5243–5275, May, 2001.

- [22] ITRS 2009 web site: <a href="http://www.itrs.net/Links/2009ITRS/Home2009.htm">http://www.itrs.net/Links/2009ITRS/Home2009.htm</a>

- [23] ITRS 2011 web site: <a href="http://www.itrs.net/Links/2011ITRS/Home2011.htm">http://www.itrs.net/Links/2011ITRS/Home2011.htm</a>

- [24] C. Auth et al., "A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors," in *VLSI Symp. Tech. Dig.*, pp. 12–14, 2012.

- [25] M.J. Buckingham, *Noise in electronic devices and systems*, Wiley, 1983.

- [26] K. Kandiah, and F.B. Whiting, "Low frequency noise in junction field effect transistors," *J. Appl. Phys.*, vol. 66, pp. 937-948, 1989.

- [27] K. S. Rails, W. J. Skocpol, L. D. Jackel, R. E. Howard, L. A. Fetter, R. W. Epworth, and D. M. Tennant, "Discrete Resistance Switching in Submicrometer Silicon Inversion Layers: Individual Interface Traps and Low-Frequency (1/f?) Noise," *Phys Rev. Lett.*, vol. 52, pp. 228–231, 1984.

- [28] A. L. McWhorter, "1/f noise and germanium surface properties," in Semiconductor Surface Physics, R. H. Kingston, Ed. Philadelphia, PA: Univ. Pennsylvania Press, pp. 207–228, 1957.

- [29] S. Christensson, I. Lundström, and C. Svensson, "Low frequency noise in MOS transistors-I theory," *Solid-State Electron*, vol. 11, pp. 797–812, 1968.

- [30] M J Kirton and M J Uren, "Noise in Solid-State Microstructures: A New Perspective on Individual Defects, Interface States and Low-Frequency (1/f) Noise," *Advances in Physics*, vol. 38, p. 367–468, 1989.

- [31] H. Kurata, K. Otsuga, A. Kotabe, S. Kajiyama, T. Osabe, Y. Sasago, S. Narumi, K. Tokami, S. Kamohara, and O. Tsuchiya, "The impact of random telegraph signals on the scaling of multilevel Flash memories," in *VLSI Symp. Circuit Dig.*, pp. 112–113, 2006.

- [32] D. Ielmini, A. S. Spinelli and A. L. Lacaita, "Recent developments on Flash memory reliability," *Micro. Engineering*, vol. 80, pp. 321–328, 2005.

#### 2. Development of statistical method of RTN

#### 2.1 Introduction

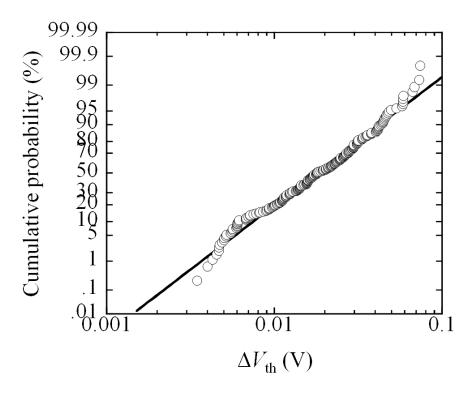

To estimate the impact of RTN on the digital devices, especially SRAM, statistical viewpoint is required because, in general,  $V_{\rm th}$  variations above  $5\sigma$  (standard deviation), that is, about 99.9999%, must be considered if the  $V_{\rm th}$  variations follow a Gaussian distribution. For example, it was reported that RDF show the Gaussian distribution to at least  $5\sigma$ [1]. Hence, the researchers make it relatively easy to analyze the  $V_{\rm th}$  variations on the basis of the Gaussian distribution because the five- $\sigma$  value is large as five as the one- $\sigma$  value. Since  $V_{\rm th}$  variations due to RTN, however, show a long-tailed non-Gaussian distribution [2], it is difficult to estimate the  $\Delta V_{\rm th}$  above the cumulative probability of 99.9999% without new statistical method of RTN. Furthermore, prior to estimate the impact of RTN on technology and scaling, the author introduces a suitable statistical theory for RTN  $V_{\rm th}$  variations.

In this chapter, the extremely value distribution, especially the Gumbel distribution, is introduced to the analysis RTN  $V_{\rm th}$  variations.

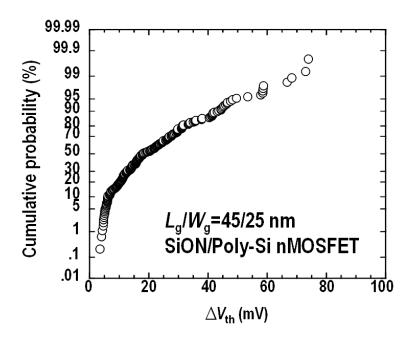

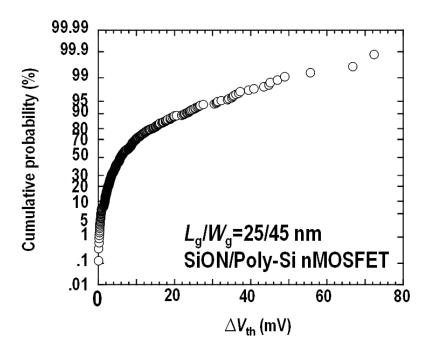

#### 2.2 Device fabrication

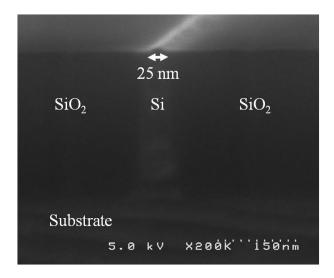

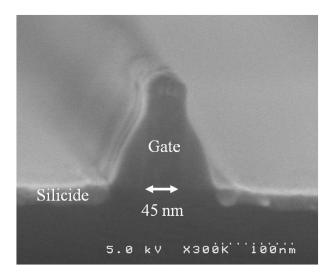

A small transistor gate of less than 100 nm can provide clear  $\Delta V_{th}$  of more than 10 mV, and more than 100 transistors with same size are needed to investigate critical values above 95% cumulative probability. Narrow-channel nMOSFETs with SiON/poly-Si gate stacks, which are designed to clearly show RTN behavior, were prepared. actual gate length and width were 45 nm and 25 nm, respectively, and the number of measured devices was over two hundreds. Figure 2.1 shows the cross-sectional scanning-electron-microscope (SEM) image of a shallow trench isolation (STI) with the actual width of 25 nm. Figure 2.2 shows the cross-sectional SEM image of a MOS structure with the actual gate length of 45 nm. Both the STI and the MOS structures are fabricated by mix-and-match lithography process, which uses electron beam system and KrF stepper. The gate dielectric is fabricated by dry oxidation process and oxidation anneal in nitric oxide. Numbers of nitrogen are 4 atom% near interface between gate dialectic and substrate.

#### 2.3 Experimental

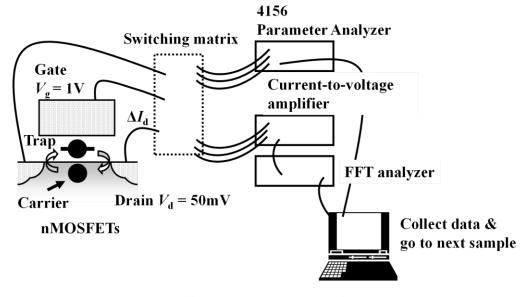

As shown in Fig. 2.3, the RTN measurement system consists of a fast-Fourier-transform (FFT) analyzer (Ono Sokki CF-5210) for observing a time series of  $\Delta I_d$ , a current to voltage amplifier with gain of  $10^5$  (This amplifier is powered by a battery to suppress power-supply noise), a semiconductor parameter analyzer (Agilent 4156C) for measuring  $V_{th}$ , a switching matrix (Agilent B2200A fA leakage switch mainframe), a prober (Cascade S300), and a control PC. This measurement system has been set up at Central Research Laboratory, Hitachi. RTN

Fig. 2.1. Cross-sectional SEM image of STI with actual gate width of 25 nm.

Fig. 2.2. Cross-sectional SEM image of MOS structure with actual gate length of 45 nm.

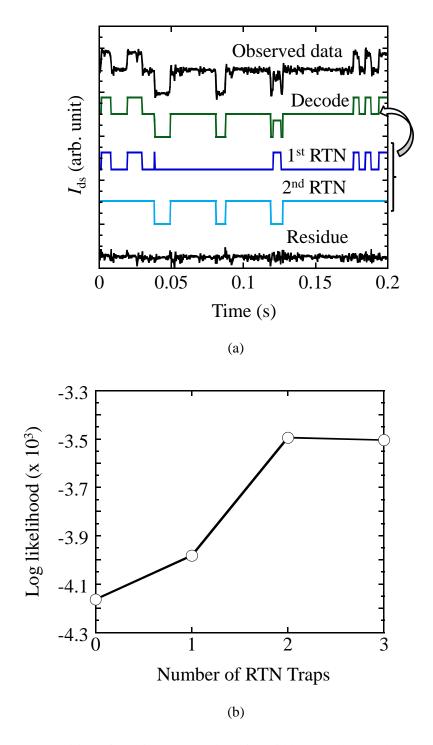

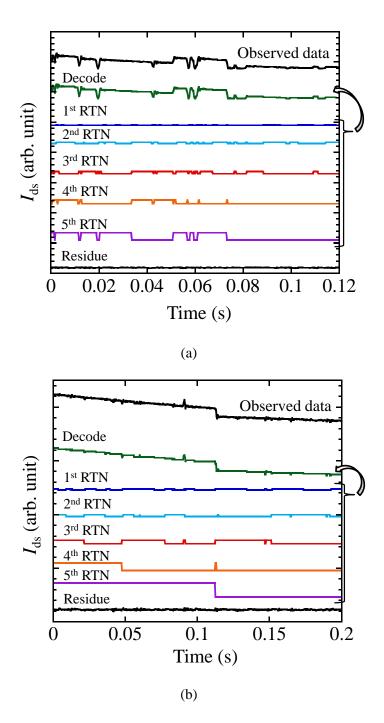

was measured under the following conditions: gate voltage ( $V_{\rm g}$ ) of 1.0 V and drain voltage ( $V_{\rm d}$ ) of 50 mV in the linear region, measurement frequency from 1 Hz to 100 kHz and measurement temperature of 25 °C. For statistical analysis, this measurement was automatically repeated 244 times (i.e., for 244 different devices). With regard to data analysis, a hidden Markov model is used for extracting  $\Delta I_{\rm d}$  and decomposing overlapped RTNs [3]. The detailed hidden Markov model is introduced in chapter 7. The overlapped RTNs can be decomposed into up to 5 single RTNs and residue.  $I_{\rm d}$  variation is defined as total amplitude of extracted single RTNs.  $\Delta I_{\rm d}$  is transformed into  $\Delta V_{\rm th}$  by using transconductance. In addition to Hitachi's MOSFETs, I prepared IBM's MOSFETs. The IBM's MOSFETs are introduced in the next chapter.

**Automatically repeat over 200 times**

Fig. 2.3. Automatic measurement system for observation of RTN  $\Delta V_{th}$ .

#### 2.4 Statistical analysis RTN $V_{\rm th}$ variations

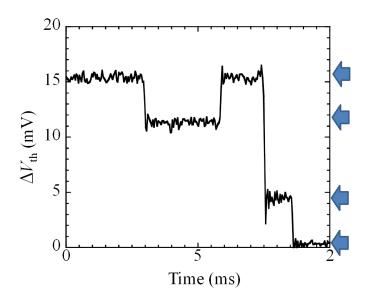

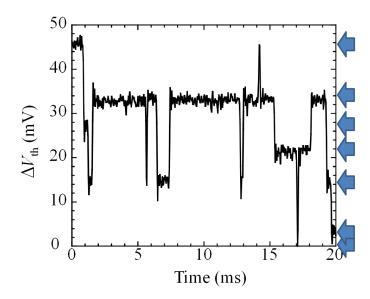

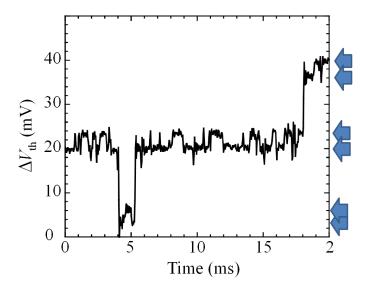

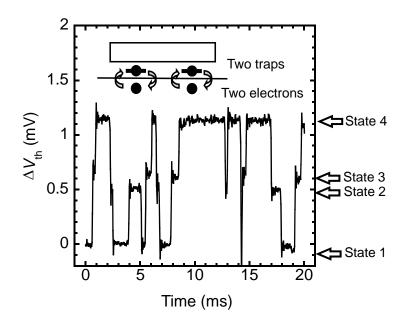

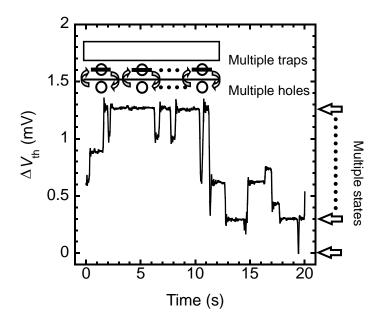

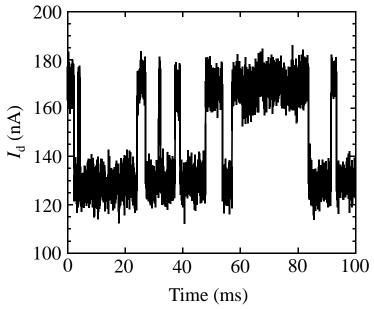

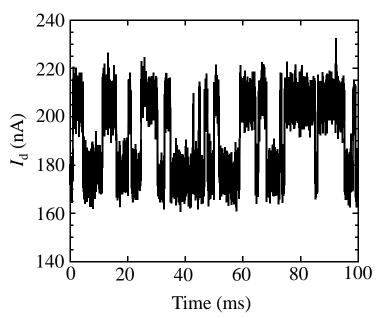

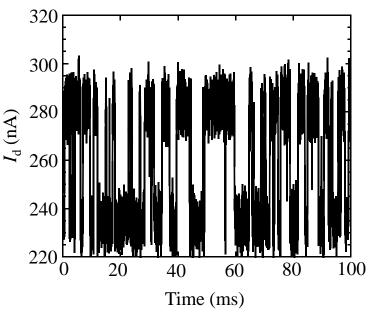

Examples of RTN waveforms are shown in Figs. 2.4 to 2.7. The typical binary fluctuation due to single RTN trap at gate dielectric is clearly shown in Fig. 2.4. The arrows indicate clear states. The amplitude depends on a location of RTN trap and discreteness of impurities in channel [4, 5]. According to these reports, RTN  $V_{th}$  variation maximizes in the case of the trap location at the center of channel and the edge of shallow trench isolation (STI). Moreover,  $\Delta V_{th}$  becomes bigger if channel width becomes narrower due to the discreteness of impurities. That is, the binary  $V_{th}$  variations due to single RTN trap are not constant and are distributed. Figure 2.5 shows that complex RTN with 4 states is caused by two RTN traps, and each RTN has different  $V_{th}$  variations. The author defined the difference between the upper state and the lower state as RTN  $V_{th}$  variation to estimate the impact of RTN accurately. Multiple levels states because of more than 3 RTN traps appear in the time series as indicated Fig. 2.6. The RTN fluctuations with the different amplitudes and the different time constants are overlapped in this figure. Figure 2.7 demonstrates that a large-amplitude RTN and a small-amplitude RTN are overlapped.  $V_{th}$  variations due to RTNs are often complicated by multiple factors including the RTN trap positions and the discreteness of impurities around the RTN trap.

From these data, a useful statistical theory to meet the multiple factors should be introduced to compare the effectiveness of process for suppression of RTN  $V_{th}$  variation. First of all, the RTN  $V_{th}$  variations are plotted on a Gaussian distribution as demonstrated on Figs 2.8 and 2.9. The devices, which are used in the demonstration of Fig. 2.8, were fabricated in Hitachi

Fig. 2.4. Binary RTN due to single trap.

Fig. 2.5. Complex RTN with four states due to two RTN traps.

laboratory, and on the other hand, Ones, which are used in Fig. 2.9, were fabricated and measured in IBM laboratory. Both data shows a long-tailed non-Gaussian distribution and my conclusion is that the curious distribution is universal. The long tail on Gaussian plot is a quite characteristic of RTN distribution. The events on the tail are rare. These large RTN  $V_{\rm th}$  variations cannot be explained by Gaussian distribution. For example, the large RTN  $V_{\rm th}$  variations as demonstrated in Figs. 2.6 and 2.7 are rare events above 90 % cumulative probability. The causes of the large  $V_{\rm th}$  variations look like complex RTN with multiple states and narrower channel due to the discreetness of impurities. Determining a suitable statistical

Fig. 2.6. Complex RTN with multiple states due to more than three RTN traps

Fig. 2.7. Complex RTN consisted of both small- and large-amplitude RTNs.

distribution is required for a comparison of processes and an estimation of a critical value above high cumulative probability of 99.9999%.

My goal in this chapter is what I suggest a suitable statistical distribution which can show how often extremely large RTN  $V_{\rm th}$  variations appear. One of the possible statistic theories for showing extremely rare and large RTN  $V_{\rm th}$  variations is an extreme value theory. Extreme value distributions are the limiting distributions for the minimum or the maximum of a very large collection of random observations in each sample. Extreme value theory is useful theory of

Fig. 2.8. RTN  $V_{\rm th}$  variations on Gaussian plot using SiON / Poly-Si nMOFET with  $L_{\rm g}$  /  $W_{\rm g}$  of 45 / 25 nm. These devices were fabricated at Central Research Laboratory, Hitachi.

Fig. 2.9. RTN  $V_{\rm th}$  variations on Gaussian plot using SiON / Poly-Si nMOFET with  $L_{\rm g}$  /  $W_{\rm g}$  of 25 / 45 nm. These devices were fabricated at T. J. Watson Research Center, IBM.

modeling rare event with extremely large or small values. This theory is also effective for assessing risk, namely rare events with extremely large or small values.

The extreme value distributions are categorized into three types: specifically, the Gumbel, the Fréchet, and the Weibull distributions, whose cumulative distribution functions are described below.

The Gumbel distribution: Type I extreme value distribution

$$F(x) = \exp\left\{-\exp\left[-\left(\frac{x-\mu_1}{\sigma}\right)\right]\right\}, \ -\infty < x < \infty \quad (2.1)$$

$$f(x) = \frac{\partial F(x)}{\partial x} = \frac{1}{\sigma} \exp\left[-\left(\frac{x-\mu_1}{\sigma}\right)\right] \exp\left\{-\exp\left[-\left(\frac{x-\mu_1}{\sigma}\right)\right]\right\} \quad (2.2)$$

The Fréchet distribution: Type II extreme value distribution

$$F(x) = \exp\left[-\left(\frac{x-\mu_1}{\sigma}\right)^{-k_1}\right], \ \mu \le x \quad (2.3)$$

$$f(x) = \frac{\partial F(x)}{\partial x} = \frac{k_1}{\sigma} \left(\frac{x-\mu_1}{\sigma}\right)^{-k_1-1} \exp\left[-\left(\frac{x-\mu_1}{\sigma}\right)^{-k_1}\right] \quad (2.4)$$

The Weibull distribution: Type III extreme value distribution

$$F(x) = \exp\left\{-\left[\frac{-(x-\mu_1)}{\sigma}\right]^{k_1}\right\}, \ \mu \ge x \quad (2.5)$$

$$f(x) = \frac{\partial F(x)}{\partial x} = \frac{k_1}{\sigma} \left[\frac{-(x-\mu_1)}{\sigma}\right]^{k_1-1} \exp\left\{-\left[\frac{-(x-\mu_1)}{\sigma}\right]^{k_1}\right\} \quad (2.6)$$

F(x) is the cumulative distribution function. f(x) is the frequency function.  $k_1$  is the shape parameter.  $\mu_1$  is the location parameter.  $\sigma$  is the scaling parameter.

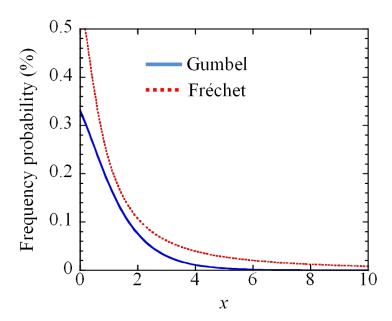

The Weibull distribution is used to show minimum values; that is, lifetimes and degradations of objects based on the weakest link theory. In reliability of MOSFET, the Weibull distribution is used to investigate the reliability of gate dielectric and, from the result of the statistical analysis, the percolation model was proposed [7]. The Gumbel distribution is used in the field of science and hydrology for extreme event. For example, in hydrology, the Gumbel distribution is used to analyze variations with rare events as monthly and annual maximum daily rainfall and river, [8] and also to describe droughts [9]. The Fréchet distribution is used for applications of

Fig. 2.10. Comparison of tail between Gumbel distribution and Fréchet distribution.

insurance and finance, which involve taking heavy risks because tail of the Fréchet distribution is heavier than that of the Gumbel distribution [10].

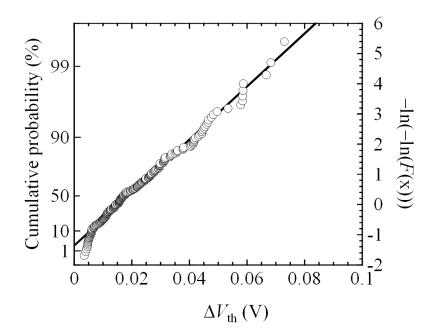

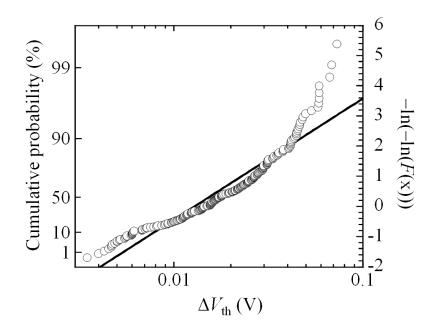

The Weibull distribution is the limiting distribution for the smallest observation in each sample. Hence, the Gumbel distribution or the Fréchet distribution is likely to show the impact of RTN  $V_{th}$  variations. Figure 2.10 demonstrates the comparison of tails between the Gumbel distribution and the Fréchet distribution. The shape, scaling and location parameters are 1, 1, and -0.5, respectively. The tailed component of the Fréchet distribution is definitely heavier than that of Gumbel distribution, and the Fréchet distribution is suitable to show higher risk. A regression analysis determines whether the Gumbel distribution or the Fréchet distribution is more likely to show RTN  $V_{th}$  variations. Equations (2.1) and (2.2) are deformed as described below

Linearity of the Gumbel plot

$$-\ln\left(-\ln(F(x))\right) = \frac{x-\mu_1}{\sigma} \quad (2.7)$$

Linearity of the Fréchet plot

$$-\ln\left(-\ln(F(x))\right) = k_1\ln(x-\mu_1) - k_1\ln\sigma \quad (2.8)$$

Fig. 2.11. RTN  $V_{\rm th}$  variations on Gumbel plot.

Fig. 2.12. RTN V<sub>th</sub> variations on Fréchet plot.

Equation (2.7) shows a linearity of the Gumbel distribution. And equation (2.8) shows a linearity of the Fréchet distribution. These equations are used to compute the regression analysis. Figure 2.11 shows RTN  $V_{\rm th}$  variations on the Gumbel plot. On the other hand, figure 2.12 shows RTN  $V_{\rm th}$  variations on the Fréchet plot. A multiple R squared of the Gumbel plot is 0.98, and on

Fig. 2.13. RTN  $V_{\rm th}$  variations on log normal plot.

the other hand, that of the Fréchet plot is 0.90; that is, the Gumbel plot more fit than the Fréchet plot. Furthermore, the Fréchet plot above 90% cumulative probability is out of the regression line. Consequently, the Fréchet plot over-estimates the impact of RTN  $V_{th}$  variations, and the Gumbel plot is more suitable to predict and judge RTN  $V_{th}$  variations.

It was reported that not only the Gumbel distribution but also log-normal distribution matches RTN  $V_{th}$  variations as shown in Fig. 2.13 [2, 4, 11]. The reason is clear. The cumulative probability distributions of the extreme value theory have properties which are called the domain of attraction. The domain of attraction is the specific distribution which approach asymptotically to the extreme value distribution. The log-normal distribution is one of the well-known domains of attraction of the Gumbel distribution and has moderately heavy tail to show RTN  $V_{th}$  variations.

#### 2.5 Conclusions

The extreme value theory is useful for showing RTN  $V_{th}$  variations. Especially, the Gumbel best meets to show the impact of RTN  $V_{th}$  variations. Moreover, the log-normal distribution also matches the tail components of RTN  $V_{th}$  variations because the log-normal distribution is the domain of attraction of the Gumbel distribution. The Gumbel distribution helps us estimate the impact of RTN  $V_{th}$  variations above 99.9999 on SRAM operation. From the dependence of the

slop and the intercept of the Gumbel distribution, we can identify effective processes for improvement of RTN  $V_{th}$  variations.

After this chapter, the Gumbel distribution and the log-normal distribution are used to discuss the impact of RTN on scaling, and moreover, the effect of processes on RTN  $V_{th}$  variations.

#### 2.6 References

- [1] T.Tsunomura, A.Nishida, F.Yano, A.T.Putra, K.Takeuchi, S.Inaba, S.Kamohara1, K.Terada, T.Mama, T.Hiramoto, T.Mogami, "Analysis of Extra VT Variability Sources in NMOS Using Takeuchi Plot," in *VLSI Symp. Tech. Dig.*, pp. 110–111, 2009.

- [2] H. Kurata, K. Otsuga, A. Kotabe, S. Kajiyama, T. Osabe, Y. Sasago, S. Narumi, K. Tokami, S. Kamohara, and O. Tsuchiya, "The impact of random telegraph signals on the scaling of multilevel Flash memories," in *VLSI Circuit Dig.*, pp. 112–113, 2006.

- [3] D. J. Frank, "Random Telegraph Noise Measurement, Analysis, and Consequences," in *Tutorial IRPS*, 2012.

- [4] K. Sonoda, K. Ishikawa, T. Eimori, and O. Tsuchiya, "Discrete Dopant Effects on Statistical Variation of Random Telegraph Signal Magnitude," *IEEE Trans. Electron Devices*, vol. 54, no. 8, pp. 1918–1925, Aug, 2007.

- [5] A. Ghetti, C. M. Compagnoni, F. Biancardi, A. L. Lacaita, S. Beltrami, L. Chiavarone, A. S. Spinelli, and A. Visconti, "Scaling trends for random telegraph noise in deca-nanometer Flash memories," in *IEDM Tech. Dig.*, pp. 1–4, 2008.

- [6] A. Ghetti, C. M. Compagnoni, A. S. Spinelli, and A. Visconti, "Comprehensive Analysis of Random Telegraph Noise Instability and Its Scaling in Deca–Nanometer Flash Memories," *IEEE Trans. Electron Devices*, vol. 56, no. 8, pp. 1746–1752, Aug, 2009.

- [7] J. H. Stathis, "Percolation models for gate oxide breakdown," *J. Appl. Phys.*, vol. 86, pp. 5757–5766, 1999.

- [8] S. Yue, "The Gumbel logistic model for representing a multivariate storm event," *Adv. Water Resour.* vol. 24, pp. 179–185, Nov., 2001.

- [9] E. J. Gumbel, "STATISTICAL FORECAST OF DROUGHTS," *International Association of Scientific Hydrology. Bulletin*, vol. 8, no. 1, pp.5–23, 1963.

- [10] R. Cont, "Empirical properties of asset returns: stylized facts and statistical issues," *QUANTITATIVE FINANCE*, vol. 1 pp.223–236, 2001.

- [11] K. Takeuchi, T. Nagumo, S. Yoko gawa, K. Imai and Y. Hayashi, "Single-Charge-Based Modeling of Transistor Characteristics Fluctuations Based on Statistical Measurement of RTN Amplitude," in VLSI Symp. Tech. Dig., pp. 54–55, 2009.

#### 3. Increasing threshold voltage variation due to RTN in MOSFETs

#### 3.1 Introduction

According to the 2009 and 2011 international technology roadmap for semiconductors (ITRS), maintaining adequate noise margin in SRAM is one of the difficult challenges for the 22 nm technology generation [1, 2]. In this context, most work has focused on RDF in very small MOSFETs and its impact on SRAM margin, and various countermeasures have been proposed [3-6] because  $V_{\rm th}$  variations due to RDF is inversely proportional to the square root of gate area [7].

In this chapter, the author, however, focuses on the statistical distribution of RTN and its impact on MOSFETs scaled down to the dimensions of the 22 nm technology node because RTN  $V_{th}$  variations is proportional to the gate area as indicated in Eq. (1.6), and moreover, the anomalously large  $V_{th}$  variations can be observed. The anomalously large  $V_{th}$  variations are rare events, and the enhancement is expected to be caused by complex RTNs and the percolation path due to discreteness of impurities in channel. Therefore, RTN is likely to have a larger impact on scaled MOSFETs than RDF. The author quantifies the impact of RTN  $V_{th}$  variation in scaled MOSFETs and shows that RTN is expected to have the impact SRAM design by using the statistical method, which was introduced from the extreme value theory in chapter 2.

#### 3.2 Device fabrication

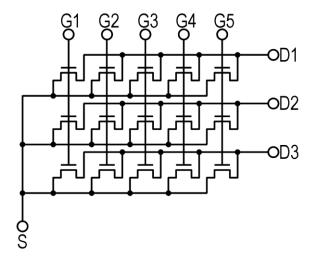

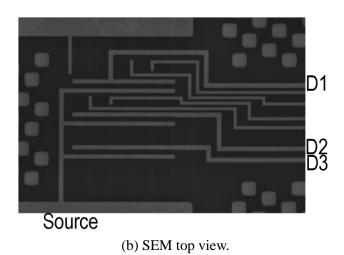

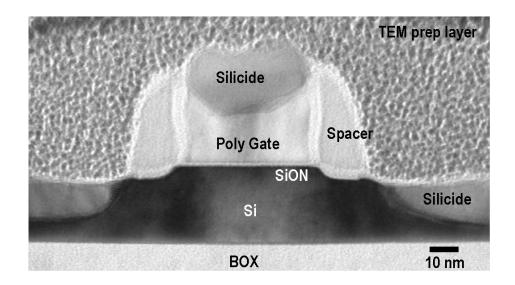

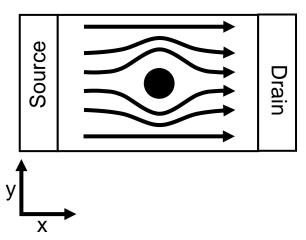

nMOSFETs used in chapters 3 and 4 were fabricated at T. J. Watson Research Center, IBM to research the impact of RTN on scaling in more detail. Mixed e-beam / optical processing has been used to provide devices with  $L_{\rm g}$  from 20 to 90 nm and  $W_{\rm g}$  from 25 to 180 nm. Test array structures were designed for easy measurement of large numbers of devices (27K/die) to enable statistical analysis of RTN  $V_{\rm th}$  variation as shown in Fig. 3.1. nMOSFETs were fabricated using standard poly-Si gate and SiON gate dielectric processes and a single shallow source / drain implant as indicated in Fig. 3.2.

#### 3.3 Experimental

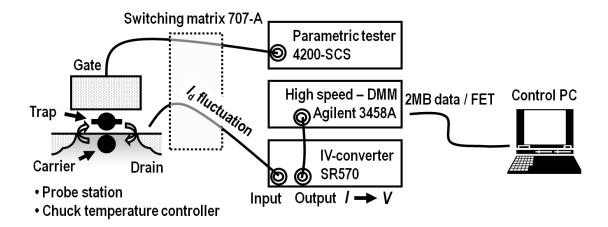

This section provides detailed explanation about measurement system for RTN characterization at T. J. Watson Research Center, IBM. Figure 3.3 shows a schematic diagram of measurement system for RTN characterization, and table 3.1 shows this system specifications. When setting up the system for measuring RTN in  $I_d$ , there are two important points. First point is a sampling speed and stability against environment. The author selected Agilent 3458A as a digital multi meter (DMM), which provides both speed and accuracy. This DMM has a reading rate of 100,000 readings / sec for maximal test throughput and achieves the highest levels of precision with up to 8.5 digits of measurement resolution and 0.1 ppm transfer accuracy. Second

(a) Circuit schematic of array for statistical analysis of RTN.

Fig. 3.1. Terminals of array: A matrix has 15 same-size devices.

point is an ability of IV converter. Since the DMM reads only voltage, the IV converter is needed for reading  $I_{\rm d}$ . Moreover, the IV converter should have a high-resolution current-to-voltage conversion. The author selected Stanford Research Systems SR 570 as the IV converter. Its features are 1pA / V maximum gain, 1 MHz maximum bandwidth, low noise and low drift. The combination of Agilent 3458A and SR 570 can provide wide frequency range from 1 Hz to 50 kHz and meets required specifications as shown in table 3.1. When measuring RTN in  $I_{\rm d}$ , the DMM applies a drain voltage to MOSFETs. On the other hand, gate voltage is applied by the Keithley semiconductor parametric tester 4200-SCS.

Each chip contains over 27,000 FETs. A probe card with 25 pin is needed for measuring many FETs with a same word line and data line. A switching matrix is needed for automatic switching. Keithley 707-A was selected as the switching matrix. All instruments, including a probe station

Fig. 3.2. TEM image of device after silicide: The device with  $L_{\rm g} = 45$  nm was fabricated by basic techniques such as poly gate and SiON gate dielectric.

Fig. 3.3. System for high-speed measurement of RTN.

Table 3.1. System specifications.

| Items              | Required specs         | Performances         |

|--------------------|------------------------|----------------------|

| Measuring speed    | 20sec / MOSFET         | About 20sec / MOSFET |

| Frequency range    | 1 ~ 50 kHz             | 1 ~ 50 kHz           |

| System noise level | Low noise level < 1 mV | < 1 mV               |

and a check temperature controller, are under computer control for automatic measurement as show in Fig. 3.3. As the result of making the system, it achieves high-speed measurement, around 20 sec / device, and can provide both high speed and resolution. The author checked a

Fig. 3.4. Single RTN in the small nMOSFET with  $L_{\rm g}/W_{\rm g}=30/45$  nm: A binary fluctuation is caused by trapping and detrapping of carrier at a single trap in near-interface gate oxide.

Fig. 3.5. Complex RTN in the small nMOSFET with  $L_{\rm g}/W_{\rm g}=30/45$  nm: 4-state fluctuation is caused by 2 traps in near-interface gate oxide.

noise floor level which comes from this system. As a result, it is less than 1 mV. The value is enough to measure RTN because  $V_{th}$  variability of more than 1 mV has the impact on the reliability of MOSFETs. The system estimates a suitable sensitivity of SR 570 and a transconductance of measurement point before measuring RTN in  $I_d$ .  $\Delta I_d$  is defined as the peak-to-peak value and is transformed into  $\Delta V_{th}$  by  $G_{m}$ .

Fig. 3.6. RTN  $V_{\rm th}$  variations on Gumbel distribution: The device sizes ( $L_{\rm g}/W_{\rm g}$ ) are 25 / 45, 30 / 65, and 90 / 180 nm, respectively.

#### 3.4 Statistical analysis on $V_{\rm th}$ variation in 22 nm MOSFETs

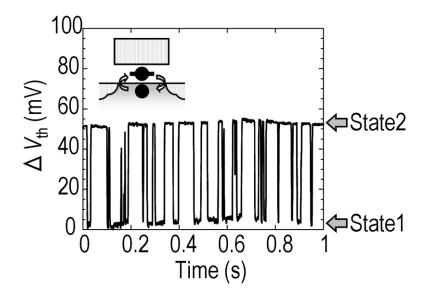

Figure 3.4 shows a typical binary fluctuation due to trapping and detrapping of a carrier at a single trap in near-interface gate oxide. Because of the small device with  $L_{\rm g}/W_{\rm g}=30/45\,\rm nm$ , the amplitude of this single RTN reaches around 50 mV. According to equation (1.6), a predictable  $V_{\rm th}$  variation is less than 10 mV. However, the actual  $V_{\rm th}$  variation is more than five time the predictable value. The likeliest model of the enhancement is the percolation path model; that is, RTN  $V_{\rm th}$  variation could be enhanced because the effective channel becomes narrower due to the discreteness of impurities.

Moreover, even though the average number of traps is less than one per 20 nm MOSFET, complex RTN with multiple simultaneous trapping events was also observed because traps are discretely distributed as shown in Fig. 3.5. Figures 3.4 and 3.5 are strong evidences that both single RTN and complex RTN have an impact on scaling.

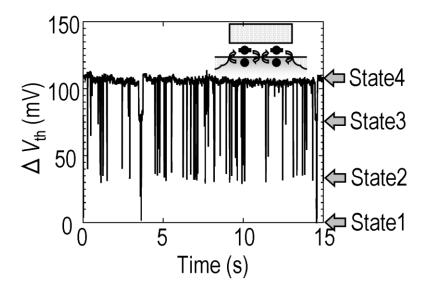

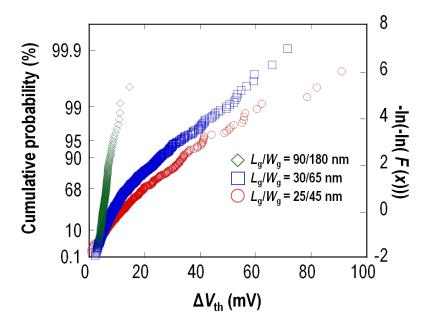

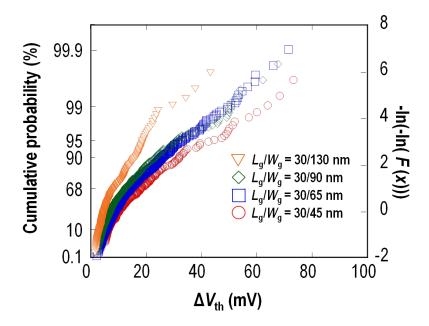

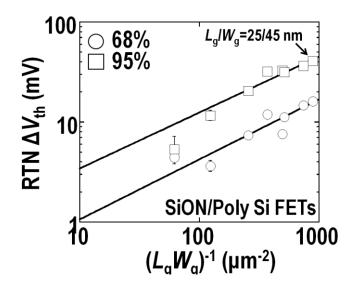

Figure 3.6 shows RTN  $V_{th}$  variations of approximately 1,000 MOSFETs per device size on the Gumbel distribution. The devices with  $L_{\rm g}$  /  $W_{\rm g}$  = 25 / 45 nm (25 nm MOSFET), 30 / 65 nm (30 nm MOSFET), and 90 / 180 nm (90 nm MOSFET) are used for 22, 32, 90 nm technology node, respectively. The 90 nm MOSFET has relatively small  $V_{th}$  variations, around 10 mV at 95% point (95% point is equivalent to  $2\sigma$  of Gaussian distribution). This level seems to have little effect on SRAM operation. In contrast, both the 30 nm and 25 nm MOSFETs have large  $V_{th}$  variations as a heavy tail above 68% point (68% point is equivalent to  $1\sigma$  of Gaussian

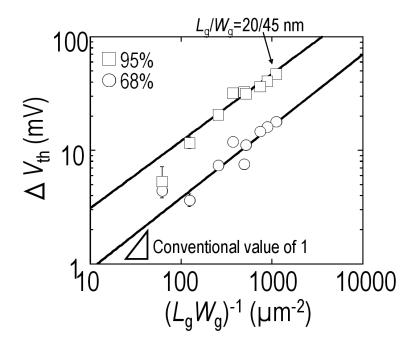

Fig. 3.7. Device-size dependences of  $\Delta V_{\text{th}}$ : The power law exponent is less than 1.

distribution). In fact, the 30 nm MOSFET's values reach around 50 mV at 95% point. In addition, the 25 nm MOSFET shows the heaviest tail of the three devices and its  $V_{th}$  variations reach more than 70 mV.

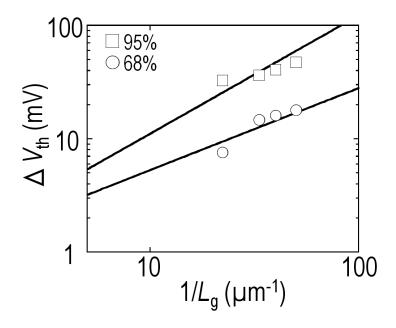

Figure 3.7 indicates the device-size dependence of RTN  $V_{\rm th}$  variation at 68% and 95% points. Regarding the power law exponent, RTN  $V_{\rm th}$  variation is thought to be inversely proportional to device size and the conventional power law exponent is 1. The power law exponent of 0.6, however, is less than the conventional value of 1 as shown in Fig. 3.7. This exponent is important because it determines the scaling of RTN. The reason for the small power law exponent of 0.6 compared to 1 is incompletely understood. However, according to the percolation path model, it was reported that the influence of gate-width scaling on RTN  $V_{\rm th}$  variation is relatively larger than that of gate-length scaling [8]. In fact, my data shows the same tendency as explained below. I may think that the difference in sensitivities for  $W_{\rm g}$ ,  $L_{\rm g}$ , and so on causes my result.

The power law exponent of RTN  $V_{th}$  variation is larger than that of RDF. The power law exponent of RDF is 0.5 as shown in the Pelgrom plot [9, 10]. Therefore, RTN has the potential to show larger impact on  $V_{th}$  margin in logic and SRAM than RDF. In the next chapter, the author demonstrates a comparison between RTN and RDF.

Fig. 3.8. RTN  $V_{\rm th}$  variations on Gumbel distribution for constant  $L_{\rm g}$  = 30 nm.

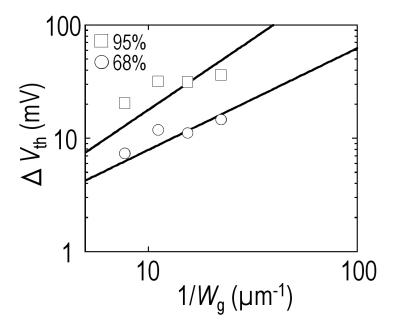

Fig. 3.9.  $W_{\rm g}$  dependences of  $\Delta V_{\rm th}$ : The percolation path depends on  $W_{\rm g}$  rather than  $L_{\rm g}$ .

# 3.5 Gate-width and gate-length dependences of RTN $V_{\rm th}$ variation

As mentioned above, the two mechanisms are proposed to explain the extremely large  $V_{\rm th}$  variations, which are rare even; that is, the simultaneous overlapped multiple RTNs, and the

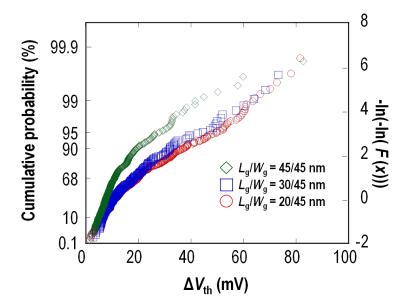

Fig. 3.10. RTN  $V_{\rm th}$  variations on Gumbel distribution for constant  $W_{\rm g} = 45\,{\rm nm}$ .

Fig. 3.11.  $L_{\rm g}$  dependences of  $\Delta V_{\rm th}$ :  $L_{\rm g}$  dependences are smaller than  $W_{\rm g}$  dependences.

interaction of traps with percolation paths. It was reported for the first time by A. Asenov *et al.* that one of the enhancement phenomena is the effect of discreteness of channel dopants [11]. Moreover, it was simulated by A. Ghetti *et al.* in detail that source-drain path is affected by

random dopant, and RTN variation depends on trap location in gate dielectric [8].

Complex RTN has been already confirmed as shown in Fig. 3.5. On the other hand, the gate-width and gate-length dependences are essential for confirming the percolation path model. As noted before, it was reported that the effect of gate-width scaling on RTN  $V_{th}$  variation is relatively larger than that of gate-length scaling [8]. However, this result came from the simulation and there is not strong evidence such as measurement data to support the percolation path theory. This work can support this theory by measurement data. First, figures 3.8 and 3.9 show the gate-width dependence of RTN  $V_{th}$  variation.  $W_{gS}$  are from 45 to 130 nm and  $L_{g}$  is a constant of 30 nm. Then, figures 3.10 and 3.11 show the gate-length dependence of RTN  $V_{th}$  variation.  $L_{gS}$  are from 20 to 45 nm and  $W_{g}$  is a constant of 45 nm. It is difficult to quantitatively discuss these dependences. However, data is likely to allow the comparison of the dependent difference. In fact, the gate-width dependence relatively large compared to the gate-length dependence as shown in Figs. 3.9 and 3.11. This result is consistent with the percolation path model. Thus, this work successfully shows that both complex RTN and percolation paths enhance  $V_{th}$  variation from experimental data.

#### 3.6 Conclusions

The author demonstrates that RTN  $V_{th}$  variations increase with scaling from large quantities of data. The RTN  $V_{th}$  variation is inversely proportional to device seize. This trend shows the power law. The enhanced mechanisms of RTN  $V_{th}$  variation are the simultaneously overlapped RTNs and the percolation of drain current due to the discreteness of impurities in channel.

- 3.7 References

- [1] ITRS 2009 web site: <a href="http://www.itrs.net/Links/2009ITRS/Home2009.htm">http://www.itrs.net/Links/2009ITRS/Home2009.htm</a>

- [2] ITRS 2011 web site: <a href="http://www.itrs.net/Links/2011ITRS/Home2011.htm">http://www.itrs.net/Links/2011ITRS/Home2011.htm</a>

- [3] D. Burnett, K. Erington, C. Subramanian, and K. Baker, "Implications of fundamental threshold voltage variations for high-density SRAM and logic circuits," in *VLSI Symp. Tech. Dig.*, pp. 15–16, 1994.

- [4] B. Cheng, S. Roy, and A. Asenov, "The impact of random doping effects on CMOS SRAM cell," *Proc. ESSCIRC*, pp. 219–222, 2004.

- [5] A. Asenov, S. Roy, R. A. Brown, G. Roy, C. Alexander, C. Riddet, C. Millar, B. Cheng, A. Martinez, N. Seoane, D. Reid, M. F. Bukhori, X. Wang, and U. Kovac, "Advanced simulation of statistical variability and reliability in nano CMOS transistors," in *IEDM Tech. Dig.*, pp. 15–17, 2008.

- [6] T.Tsunomura, A.Nishida, F.Yano, A.T.Putra, K.Takeuchi, S.Inaba, S.Kamohara1, K.Terada, T.Mama, T.Hiramoto, T.Mogami, "Analysis of Extra VT Variability Sources in NMOS Using Takeuchi Plot," in VLSI Symp. Tech. Dig., pp. 110–111, 2009.

- [7] M. J.M. Pelgrom, H. P. Tuinhout, and M. Vertregt, "Transistor matching in analog CMOS applications," in *IEDM Tech. Dig.*, pp. 915–918, 1998.

- [8] A. Ghetti, C. Monzio Compagnoni, F. Biancard, A. L. Lacaita, S. Beltrami, L. Chiavarone, A.S. Spinelli, and A. Visconti, "Scaling trends for random telegraph noise in deca-nanometer Flash memories," in *IEDM Tech. Dig.*, pp. 835–838., 2008.

- [9] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, "Matching properties of MOS transistors," *IEEE J. Solid-State Circuits*, vol. 24, no. 5, pp. 1433–1440, Oct., 1989.

- [10] M. J.M. Pelgrom, H. P. Tuinhout, and M. Vertregt, "Transistor matching in analog CMOS applications," in *IEDM Tech. Dig.*, pp. 915–918, 1998.

- [11] A. Asenov, A. R. Brown, J. H. Davies, S. Kaya, and G. Slavcheva, "Simulation of Intrinsic Parameter Fluctuations in Decananometer and Nanometer-scale MOSFETs," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1837–1852, Sept., 2003.

## 4. Impact of RTN on high- $\kappa$ / metal-gate stacks and future device scaling

## 4.1 Introduction

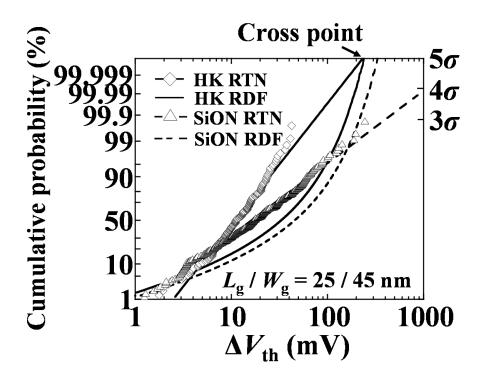

Variation due to RTN is becoming a new threat to the future devices because  $V_{th}$  variation of RTN rapidly rises with scaling, just as variation due to random dopant fluctuation (RDF) as discussed in chapter 3 [1]. The distinctive features of RTN are the size dependence and statistical distribution of  $V_{th}$  variation. The size dependence of RTN is relatively stronger than RDF. Moreover RTN  $V_{th}$  variation shows the Gumbel distribution and log-normal distribution with extremely large  $V_{th}$  variations, which are rare event, whereas RDF has a Gaussian distribution. Therefore RTN  $\Delta V_{th}$  could exceed that of RDF at high cumulative probability, in especially advanced devices. RTN is one of the newly envisioned challenges to SRAM stability at the next generations such as 15 nm and beyond.

High- $\kappa$  / metal-gate (HK / MG) stacks will be incorporated in these generations as standard technique because of their more optimal power and performance compared to SiON / Poly-Si gate stacks [2, 3]. Study on the reliability of HK / MG stacks has made progress in recent years. The HK / MG stacks have a great advantage not only for gate leakage current, but also for variability such RDF because the HK / MG stacks can provide thinner EOT than the conventional SiON / Poly-Si gate stacks [4]. This effect is expected to reduce RTN  $V_{th}$  variations as well as RDF. In contrast, HK / MG stacks have a serious problem associated with an interfacial layer (IL) between the high- $\kappa$  dielectric and the substrate. IL is expected to prevent or at least minimize an interfacial reaction between the high- $\kappa$  oxide and the underlying Si [5]. However, since IL often consists of SiON film, the many researchers express concern about its potential to reduce the reliability, especially its potential to degrade BTI characteristics [6]. On the other hand, a relationship between RTN and HK / MG stacks has been unknown because the thin EOT of HK / MG stacks is likely to contribute to suppressing the impact of RTN as well as RDF, and in contrast, IL including SiON film has a potential to degrade RTN  $V_{th}$  variations as well as the BTI characteristics.

The author evaluates the RTN impact on HK/MG MOSFETs and future device scaling from a statistical viewpoint and demonstrates an effect of high temperature forming anneal (HTFGA) on an improvement of HK/MG stacks.

#### 4.2 Device fabrication

In this work, mixed e-beam / optical processing has been used to fabricate small devices, nMOSFETs, with gate length from 20 to 90 nm and width from 25 to 180 nm. And these small devices incorporate  $HfO_2$ -based HK / MG stacks. For a comparison, devices with  $SiO_2$  and SiON / Poly-Si gate stacks were also fabricated. The HK MOSFETs have smaller  $T_{inv}$  and larger transconductance than the pure- $SiO_2$  and SiON MOSFETs, as shown in Table 4-1. To evaluate

Table 4.1 Features of nMOSFETs.

| Gate dielectric                                                                          | $SiO_2$     | High-κ      |  |  |

|------------------------------------------------------------------------------------------|-------------|-------------|--|--|

| Gate                                                                                     | Poly Si     | Metal Gate  |  |  |

| Split N conditions                                                                       | With or W/O |             |  |  |

| Split HTFGA                                                                              |             | With or W/O |  |  |

| $T_{\rm inv}$ (nm)                                                                       | 1.83(SiON)  | 1.49        |  |  |

| $\overline{G_{\mathrm{m}}}$                                                              | Small       | Large       |  |  |

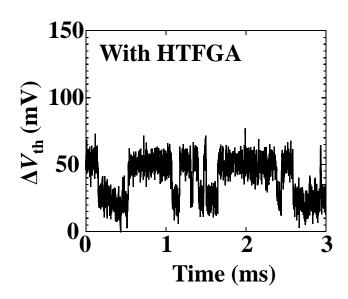

| Sampling rate = 1 M/s $L_{g}/W_{g} = 20/45 \text{ nm}$ 100 0 0.2 0.4 0.6 0.8 1 Time (ms) |             |             |  |  |

Figure 4.1. Typical RTN dependence on time.

the effect of hydrogen passivation of interface traps [7], HTFGA was performed on some HK MOSFETs. The annealing temperature of HTFGA is 475 °C. It was reported by K. Onishi et al., that HTFGA can reduce the interface trap density of HK MOSFET [8, 9]. HTFGA is, therefore, expected to passivate RTN traps and suppress RTN  $\Delta V_{th}$ . On the other hand, since RTN shows the extreme value distribution such as the Gumbel distribution, statistical analysis of many MOSFETs is vital. Test array structures were designed for easy measurement of large numbers of devices (27000 / die) to enable statistical analysis of RTN  $\Delta V_{th}$  variation the same way as SiON MOSFETs in chapter 3.

## 4.3 Measurement and analysis methods

A fast measurement unit (Agilent 1530A) which enables a wide band width of up to 1 M/s was used to measure the RTN signals. Figure 4.1 shows the typical RTN dependence on time obtained by high sampling rate  $1\,\mathrm{M/s}$ .  $10^5$  sampling points were used for the measurement. A sampling interval was 1  $\mu$ s. Drain current fluctuation was measured under 50 mV of drain voltage. This RTN behavior has two obvious states due to trapping and detrapping of a carrier at a single

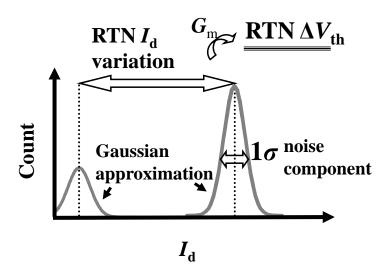

Figure 4.2. Separation between RTN and other noise components.

Figure 4.3. Comparison of RTN in 25 nm MOSFETs with or without HTFGA.

trap in gate dielectric. Figure 4.2 illustrates the histogram separation method. RTN  $I_{\rm d}$  variation is defined as the peak-to-peak value in this figure. Other noise components are removed from the RTN component by this extraction. RTN variation is transformed from  $\Delta I_{\rm d}$  to the input-referred RTN voltage noise ( $\Delta V_{\rm th}$ ) using  $G_{\rm m}$ , in addition to the separation.

(a) With HTFGA.

(b) Without HTFGA.

Figure 4.4. RTNs at 95% level in 25 nm MOSFET.

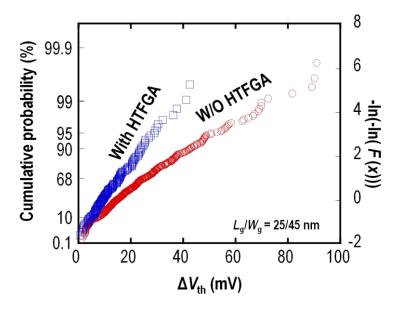

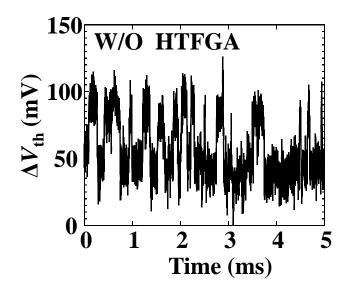

## 4.4 Inhibitory effect of HK / MG techniques on RTN

As mention above, HTFGA is expected to passivate RTN traps and suppress RTN  $\Delta V_{th}$ . Figure 4.3 demonstrates the effect of HTFGA on the distributions of RTN  $\Delta V_{th}$  in 25 nm MOSFETs. As expected, RTN is well suppressed by HTFGA. HTFGA can reduce  $\Delta V_{th}$  at the cumulative probability of 95% from 40 mV to 20 mV. For instance, Figure 4.4 shows the samples with and without HTFGA at the 95% level. The RTN magnitude at the 95% level for

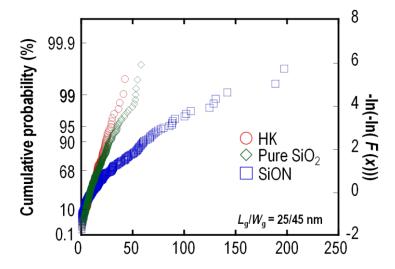

Figure 4.5. Comparison of RTN between HK with HTFGA, pure-SiO<sub>2</sub>, and SiON FETs.

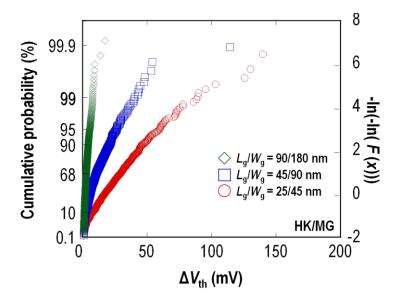

Figure 4.6. Device-size dependence of RTN  $\Delta V_{\text{th}}$  distributions.

these two cases differs by  $\sim$ 2 times because hydrogen is capable of passivating traps. As I will discuss again in the after chapters, the RTN  $V_{th}$  variations is affected significantly by the processes which can reduce the interface trap density. Consequently, I am sure that the RTN trap is located very near the interface between gate dielectric and substrate. I will prove my hypotheses in chapter 8. By the way, R .J. Carter et al. reported the reason that the HTFGA is useful for passivating interface traps in the case of HfO<sub>2</sub>-based HK dielectric [10]. They revealed

(a) SiON/poly-Si MOSFETs.

Figure 4.7. Device-size dependences of RTN  $\Delta V_{\text{th}}$ .

that HTFGA is not necessary for the hydrogen to diffuse through the conventional gate dielectric, SiON, but through HfO<sub>2</sub>-based material. The best annealing temperature is 520 °C. The interface trap density ( $D_{it}$ ) controlled by HTFGA at 520 °C is one tenth that uncontrolled by FGA at 420 °C. Thus, I succeed in controlling the RTN traps near interface by HTGA at 475 °C in the same way as  $D_{it}$  and believe that HTFGA will be able to be optimized much further.

Figure 4.8. Comparison between RTN and RDF impacts on log-normal distribution.

\* RDF data are based on the reference 11.

Figure 4.5 compares RTN  $\Delta V_{th}$  between HTFGA HK, pure-SiO<sub>2</sub> and SiON MOSFETs. RTN  $\Delta V_{th}$  of HK and pure-SiO<sub>2</sub> MOSFETs are quite comparable. On the other hand, both the median value and the variation of HK MOSFETs are obviously smaller than those of SiON MOSFETs. The main reason is that trap density in our optimized HK MOSFETs becomes lower because of HTFGA. A secondary reason is that the  $T_{inv}$  of HK MOSFETs is 25% smaller than that of SiON MOSFETs. Optimizing HK/MG stacks is useful for not only the RDF variation but also the RTN variation in the advanced MOSFETs.

Figure 4.6 indicates the cumulative distribution of RTN  $\Delta V_{th}$  of HK MOSFETs with strong device-size dependence. All measured devices were fabricated on same wafer, so process variation is suppressed as much as possible to evaluate only the impact of scaling on RTN. As mentioned above, the RTN  $V_{th}$  variations at high cumulative probability are of greatest importance. The MOSFET with  $L_g$  and  $W_g$ =90/180 nm has small  $\Delta V_{th}$  of approximately 4 mV at 95% point.  $\Delta V_{th}$  of the MOSFET with 45/90 nm is more than 20 mV. And the smallest device with 25/45 nm has approximately 40 mV of  $\Delta V_{th}$ . Thus, the variation increases with device scaling.

The comparison of the device-size dependence of  $\Delta V_{th}$  between SiON and HK MOSFETs is seen in Fig. 4.7. RTN  $\Delta V_{th}$  steeply increases with device size in both HK MOSFETs and SiON MOSFETs. However, the RTN  $V_{th}$  variations of HK MOSFETs are smaller than these of SiON

MOSFETs anywhere in the generations because of the effect of HTFGA and the thinner EOT of HK MOSFET than that of SiON MOSFET.

The statistical distribution of RTN  $V_{th}$  variation shows the Gumbel or the log-normal based on the extreme value theory, while the statistical distribution of RDF has been shown to be Gaussian out to at least  $5\sigma$  [11]. This work compares RTN with RDF in HK MOSFET by arranging data of reference 11 as demonstrated in Fig. 4.8. The data are plotted on the log-normal distribution. 22 nm generation RTN  $V_{th}$  variations exceed RDF  $V_{th}$  variations at the  $3\sigma$  level in the SiON MOSFET, while the cross point can be extended to more than  $5\sigma$  level in the case of the HK MOSFET. The author, therefore, concludes that the influence of RTN is less than that of RDF in the 22 nm generation. Considering the size dependence of RTN as shown in Fig. 4.8, however, RTN may pose a difficult challenge for the 15 nm generation.

## 4.5 Conclusions

The RTN  $V_{th}$  variation in HK MOSFET can be suppressed by suitable annealing, such as HTFGA, and by thin  $T_{inv}$ . As a consequence, properly annealed HK MOSFETs can have smaller RTN variation than SiON MOSFETs. The RTN  $\Delta V_{th}$  dependence on scaling was demonstrated using both SiON MOSFETs and HK MOSFETs. RTN impact may, however, become severe in 15 nm generation and beyond because even though HK appears to offer lower RTN, the dimensions will be so small that RTN will become large.

#### 4.6 References

- [1] K. Takeuchi, T. Nagumo, S. Yokogawa, K. Imai, and Y. Hayashi, "Single-Charge-Based Modeling of Transistor Characteristics Fluctuations Based on Statistical Measurement of RTN Amplitude," in *VLSI Tech. Dig.*, pp.54–55, 2009.

- [2] C. H. Diaz et al., "32nm Gate-First High-k/Metal-Gate Technology for High Performance Low Power Applications" in *IEDM Tech. Dig.*, pp. 629–632, 2008.

- [3] C.-H. Jan, M. Agostinelli, H. Deshpande, M. A. El-Tanani, W. Hafez, U. Jalan, L. Janbay, M. Kang, H. Lakdawala, J. Lin, Y-L Lu, S. Mudanai, J. Park, A. Rahman, J. Rizk, W.-K. Shin, K. Soumyanath, H. Tashiro, C. Tsai, P. VanDerVoorn, J.-Y. Yeh, and P. Bai, "RF CMOS Technology Scaling in High-k/Metal Gate Era for RF SoC (System-on-Chip) Applications," in *IEDM Tech. Dig.*, pp. 604–607, 2010.

- [4] K. Mistry et al., "A 45nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning, and 100% Pb-free Packaging," in *IEDM Tech. Dig.*, pp.247–250, 2007.

- [5] G. D.Wilk, R. M.Wallace, and J. M. Anthony, "High-k gate dielectrics: Current status and materials properties considerations," *J. Appl. Phys.*, vol. 89, pp. 5243–5275, May, 2001.

- [6] C. Choi, C.-S. Kang, C. Y. Kang, S. J. Rhee, M. S. Akbar, S. A. Krishnan, M. Zhang, and J. C. Lee, "Positive Bias Temperature Instability Effects of Hf-Based nMOSFETs With Various Nitrogen and Silicon Profiles," *IEEE Electron Devic Lett.*, vol. 26, no. 1, pp. 32–34, Jan., 2005.

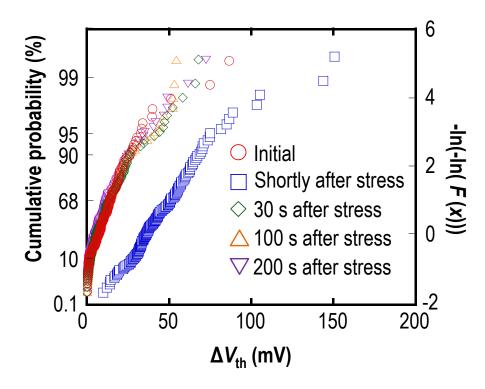

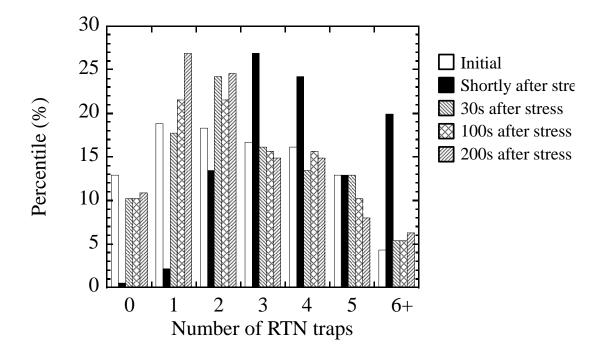

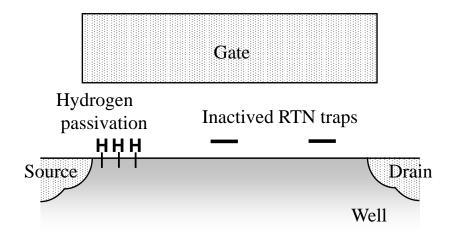

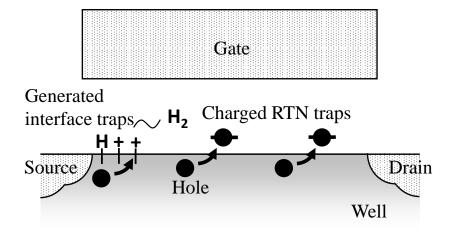

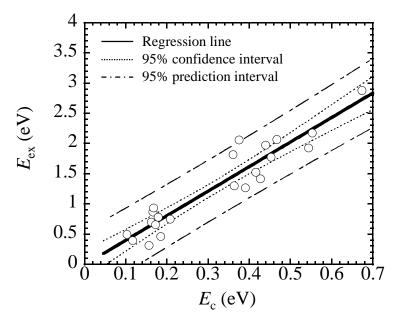

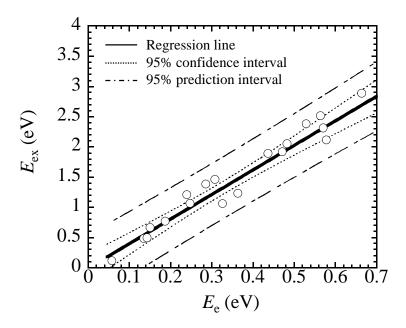

- [7] H. Aono, E. Murakami, K. Shiga, F. Fujita, S. Yamamoto, M. Ogasawara, Y. Yamaguchi, K. Yanagisawa, and K. Kubota, "A STUDYOF SRAM NBTI BY OTF MEASUREMENT," in *IRPS Proc.*, pp. 67–71, 2008.